### **Lawrence Berkeley National Laboratory**

### **Recent Work**

### **Title**

RUN-TIME PARTITIONING OF SCIENTIFIC CONTINUUM CALCULATIONS RUNNING ON MULTIPROCESSORS

### **Permalink**

https://escholarship.org/uc/item/9w67v000

### **Author**

Baden, S.B.

### **Publication Date**

1987-06-01

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

## Physics Division

**Mathematics Department**

RUN-TIME PARTITIONING OF SCIENTIFIC CONTINUUM CALCULATIONS RUNNING ON MULTIPROCESSORS

S.B. Baden (Ph.D. Thesis)

June 1987

# TWO-WEEK LOAN COPY

This is a Library Circulating Copy which may be borrowed for two weeks.

### **DISCLAIMER**

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

### RUN-TIME PARTITIONING OF SCIENTIFIC CONTINUUM CALCULATIONS RUNNING ON MULTIPROCESSORS<sup>1</sup>

Scott B. Baden

Lawrence Berkeley Laboratory University of California Berkeley, California 94720

Ph. D. Dissertation, Computer Science Division University of California, Berkeley

June 1987

The United States Department of Energy has the right to use this thesis for any purpose whatsoever including the right to reproduce all or any part thereof.

<sup>&</sup>lt;sup>1</sup> This work was supported in part by a California Fellowship in Microelectronics and in part by the Applied Mathematical Sciences subprogram of the Office of Energy Research, U.S. Department of Energy, under contract DE-AC03-76SF00098.

### Run-Time Partitioning of Scientific Continuum Calculations Running on Multiprocessors

Copyright © 1987

Scott Benjamin Baden

### Run-Time Partitioning of Scientific Continuum Calculations Running on Multiprocessors

### Scott Benjamin Baden

### Abstract

A wide range of scientific continuum calculations typically concentrate computational effort non-uniformly over localized regions of physical space. We present a run-time partitioning strategy, intended for such methods, that distributes work evenly across a team of processors and that can exploit the spatial localization present in the original computation in order to avoid high overhead costs. We tried out our strategy on Anderson's Method of Local Corrections, a type of vortex method for computational fluid dynamics. Because computational effort follows particles that congregate and disperse irregularly about the domain, this problem is hard to partition in a way that distributes the work evenly among the processors. We ran experiments on 32 processors of an Intel Personal Scientific Computer — a message-passing hypercube multiprocessor — and on 4 processors of a Cray X-MP — a shared-memory vector architecture — and achieved good parallel speedups of 22 and 3.6, respectively. The partitioner may

be implemented as a virtual machine (VM) and made available to the programmer as a library of run-time utilities. The semantics of the VM are insensitive to the application and to the computer architecture on which the VM is implemented. The VM works with ordinary programming languages, incurs modest overhead costs, and requires no special hardware support. It should apply to diverse applications, including finite difference methods, and to diverse architectures without requiring that the application be reprogrammed extensively for each new architecture.

### Acknowledgements

I feel privileged to have worked with my advisor, W. Kahan. True to his word, Vel will graduate no student before his time; but, the rewards of meeting Vel's challenges will be with me always. A special word of thanks goes to Phil Colella, who was my fourth committee member. The distinction as fourth member is exceptional, but so is Phil; he made a special effort to show me the wonders of what had once seemed the dark and mysterious side of computer science – computational mathematical physics – while asking very little in return. I have fond memories of our lively discussions at the Cafe Roma, where our friendship was kindled. And yes, many thanks go to Phil's wife, Sue Londerville, for her good spirit.

Others have taken a keen interest in this research and I also wish to extend a warm thanks to them, too. Professors Paul Hilfinger and Beresford Parlett were my official readers, and dutifully waded through the final drafts of my dissertation. Professors Alexandre Chorin and Paul Concus provided constant encouragement and offered a pleasant working environment at Lawrence Berkeley Laboratory. Chris Anderson, a Berkeley graduate and now on the faculty at UCLA, offered insight and moral support, and also provided an initial version of the local corrections code. Cleve Moler arranged for employment at Intel Scientific Computers, where my work was met with great enthusiasm. Cleve's good humor helped brighten the hard work that accompanied this research. I am also grateful to Chris C. Hsiung of Cray Research, Inc. for providing access to the Cray X-MP/416 at the Cray facility in Mendota Heights, Minnesota. Philippe de Forcrand, John L. Larson, and Jeff Nicholson, all of Cray Research, cheerfully advised me on the finer points of the X-MP. Professor Alberto Sangiovanni-Vincentelli generously provided access to the iPSC at Berkeley.

To my office mates here at Berkeley – Ricki Blau, Paul Hansen, and Erling Wold – it's been wonderful sharing a cabin with you during our long cruise together.

To Ann Di Fruscia, thank you for the concern you showed me these past years, and for the graceful dances you performed.

Thank you Kathryn Crabtree, for reminding me to hand this in.

A final word of thanks go to my parents, Ruth Kramer Baden and Howard P. Baden, who watched from afar as I worked my way through to the finish.

This work was supported in part by a California Fellowship in Microelectronics and in part by the Applied Mathematical Sciences subprogram of the Office of Energy Research, U.S. Department of Energy, under contract DE-AC03-76SF00098. Additional support for this work was sponsored by: the National Science Foundation, grant # DMF84-03223; the State of California, California Microelectronics grant # 532429-19900; Intel Scientific Computers, a division of the Intel Corporation; Cray Research Incorporated; and the Defense Advance Research Projects Agency (DoD), Arpa Order No. 4871, Monitored by Naval Electronic Systems Command under Contract No. N00039-84-C-0089. AFOSR helped with travel expenses.

# TABLE OF CONTENTS

| Chap   | ter 1:  |                                                |    |

|--------|---------|------------------------------------------------|----|

| Intro  | duction | ······································         | 1  |

|        | 1.1:    | Run-Time Partitioning and Software Portability | 1  |

|        | 1.2:    | A Programming Methodology                      | 4  |

|        | 1.3:    | Results                                        | 5  |

|        | 1.4:    | References                                     | 7  |

| Chap   | ter 2:  |                                                |    |

| Past \ | Work    |                                                | 8  |

|        | 2.1:    | Introduction                                   | 8  |

| •      | 2.2:    | Implicit Load Balancing                        | 10 |

|        | 2.2.1:  | Non-Traditional Computer Architectures         | 10 |

|        | 2.2.2:  | Processor Self-Scheduling                      | 11 |

|        | 2.2.3:  | Scatter Decomposition                          | 13 |

|        | 2.3:    | Explicit Load Balancing                        | 14 |

|        | 2.3.1:  | Indirect Methods                               | 14 |

|        | 2.3.2:  | Direct Methods                                 | 16 |

|        | 2.4:    | Comparison with Our Approach                   | 17 |

|        | 2.5:    | References                                     | 18 |

| Chap   | ter 3:  |                                                |    |

| A Mo   | del Com | putation                                       | 21 |

|      | 3.1:     | Mathematical Background                         | 21 |

|------|----------|-------------------------------------------------|----|

|      | 3.2:     | The Calculation                                 | 22 |

|      | 3.3:     | Anderson's Method of Local Corrections          | 25 |

|      | 3.4:     | Accuracy and Parameter Selection                | 30 |

|      | 3.5:     | References                                      | 35 |

| Chap | ter 4:   |                                                 |    |

| User | Abstract | ions for Run-Time Partitioning                  | 37 |

|      | 4.1:     | Underlying Assumptions                          | 37 |

|      | 4.2:     | A Virtual Machine                               | 40 |

|      | 4.3:     | VM Utilities                                    | 42 |

|      | 4.3.1:   | Mapper                                          | 42 |

|      | 4.3.2:   | Partitioner                                     | 45 |

| • .  | 4.4:     | Portability Considerations                      | 46 |

|      | 4.5:     | MLC Implementation                              | 49 |

|      | 4.5.1:   | Data Partitioning                               | 53 |

|      | 4.5.2:   | Local Communication                             | 57 |

|      | .4.6:    | Implementation Strategy for the Virtual Machine | 61 |

|      | 4.6.1:   | Partitioner                                     | 62 |

|      | 4.6.2:   | Mapper                                          | 64 |

|      | 4.7:     | Summary                                         | 66 |

|      | 4.8:     | References                                      | 70 |

| Chap | oter 5:  |                                                 |    |

| iPSC | Implem   | entation                                        | 71 |

|      | £ 1.     |                                                 | 71 |

|      | 5.2:    | The iPSC                             | 72         |

|------|---------|--------------------------------------|------------|

|      | 5.3:    | Implementation                       | <b>7</b> 7 |

|      | 5.3.1:  | Overview                             | 77         |

|      | 5.3.2:  | Virtual Machine Implementation       | 77         |

|      | 5.3.3:  | Global Computation and Communication | 78         |

|      | 5.3.4:  | Arithmetic                           | 80         |

|      | 5.4:    | Evaluation Strategy                  | 81         |

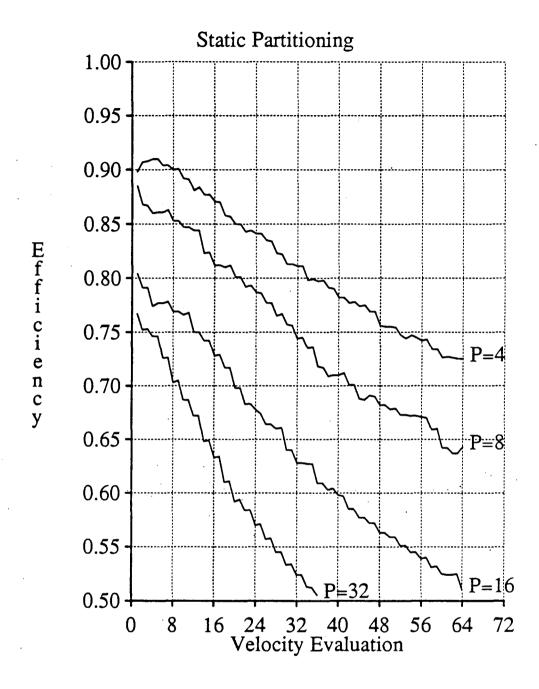

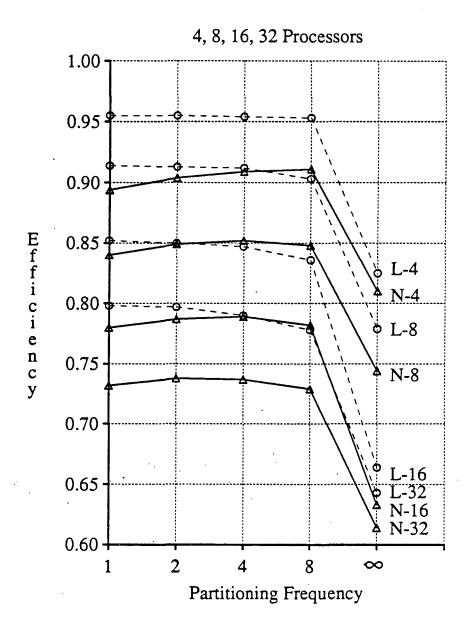

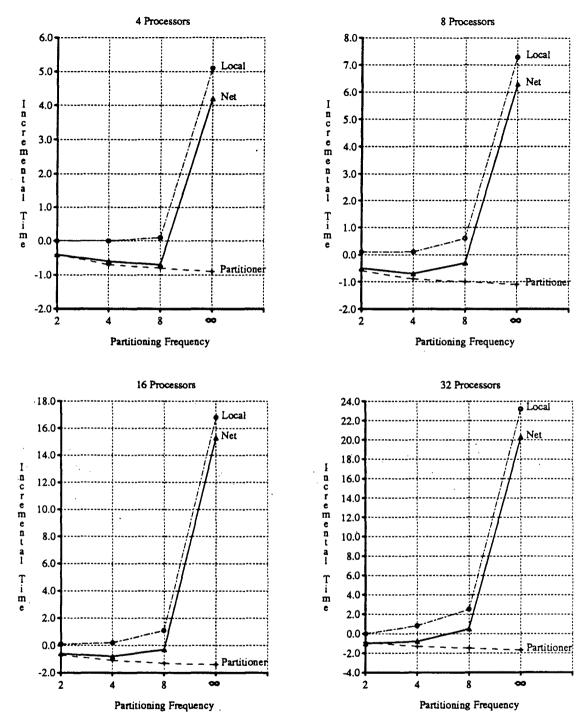

|      | 5.5:    | The Experiments                      | 83         |

|      | 5.6:    | Discussion                           | 92         |

|      | 5.7:    | References                           | 99         |

| Chap | ter 6:  |                                      |            |

| Cray | X-MP II | nplementation and Evaluation         | 101        |

|      | 6.1:    | Overview                             | 101        |

|      | .6.2:   | The Cray X-MP Multiprocessing System | 102        |

|      | 6.2.1:  | Arithmetic and Registers             | 103        |

|      | 6.2.2:  | Memory                               | 105        |

|      | 6.2.3:  | Shared Registers                     | 106        |

|      | 6.2.4:  | X-MP System Software                 | 107        |

|      | 6.3:    | Implementation                       | 110        |

|      | 6.3.1:  | Parallelization                      | 111        |

|      | 6.3.2:  | VM Implementation                    | 117        |

|      | 6.3.3:  | Vectorization                        | 119        |

|      | 6.4:    | Evaluation                           | 120        |

|      | 6.4.1:  | Simulation Parameter Selection       | 120        |

|                            | 6.4.2: | Computational results            | 123 |

|----------------------------|--------|----------------------------------|-----|

|                            | 6.5:   | Conclusions                      | 129 |

|                            | 6.6:   | References                       | 129 |

| Chapter 7:                 |        |                                  |     |

| Discussion and Conclusions |        |                                  | 131 |

|                            | 7.1:   | What Has Been Accomplished       | 131 |

|                            | 7.2:   | Comparison with Other Approaches | 135 |

|                            | 7.3:   | Future Work                      | 137 |

|                            | 7.4:   | References                       | 138 |

| Appendix A                 |        |                                  | 139 |

# LIST OF FIGURES

| Chapter 3:  |    |

|-------------|----|

| Figure 3.1  | 29 |

| Figure 3.2  | 31 |

| Chapter 4:  |    |

| Figure 4.1  | 39 |

| Figure 4.2  | 41 |

| Figure 4.3  | 43 |

| Figure 4.4  | 47 |

| Figure 4.5  | 51 |

| Figure 4.6  | 52 |

| Figure 4.7  | 54 |

| Figure 4.8  | 56 |

| Figure 4.9  | 58 |

| Figure 4.10 | 59 |

| Figure 4.11 | 60 |

| Figure 4.12 | 63 |

| Figure 4.13 | 65 |

| Figure 4.14 | 67 |

| Figure 4.15 | 69 |

Chapter 5:

|       | Figure 5.1 | 73  |

|-------|------------|-----|

|       | Figure 5.2 | 79  |

|       | Figure 5.3 | 86  |

|       | Figure 5.4 | 91  |

|       | Figure 5.5 | 93  |

|       | Figure 5.6 | 94  |

|       | Figure 5.7 | 95  |

|       | Figure 5.8 | 98  |

| Chapt | er 6:      |     |

|       | Figure 6.1 | 121 |

# LIST OF TABLES

| Chapter 3: |     |

|------------|-----|

| Table 3.1  | 2:  |

| Table 3.2  | 30  |

| Table 3.3  | 3-  |

| Table 3.4  | 3-  |

| Chapter 5: |     |

| Table 5.1  | 82  |

| Table 5.2  | 8.  |

| Table 5.3  | 8′  |

| Table 5.4  | 89  |

| Table 5.5  | 89  |

| Table 5.6  | 90  |

| Table 5.7  | 90  |

| Chapter 6: |     |

| Table 6.1  | 123 |

| Table 6.2  | 120 |

| Table 6.3  | 12  |

| Table 6.4  | 12  |

| Table 6.5  | 12  |

1

### Introduction

... It took me years to write it, They were the best years of my life. It was a beautiful song, But it ran too long ... So they cut it down to three-o-five.

-Billy Joel, "The Entertainer"

### 1.1. Run-Time Partitioning and Software Portability

Ideally a multiprocessor system would satisfy two conditions: (1) its performance would be linearly proportional to the number of processors in use and (2) programs that run well on it may be written nearly independently of how its processors communicate. In practice, however, work can accumulate on only some of the processors, leaving the rest to sit mostly idle. Unless some kind of run-time partitioning strategy is employed to mitigate such load imbalance, the overall throughput of the system will be proportional not to the number of available processors, but to the small fraction that can be utilized effectively. A large number of run-time partitioning strategies already exist, but the overhead costs they incur can depend heavily upon the system on which they are implemented. Therefore a major difficulty remains: how to construct software that can run on diverse architectures without entailing substantial reprogramming for each implementation. For example, a program that runs well on a shared-memory architecture can

look very different from a program implementing the same calculation but optimized for a message-passing architecture with only local memories.

I believe that a good run-time partitioning strategy for load balancing should have three characteristics. First, it should be versatile over some reasonable range of applications, and should not have to be reimplemented for each new combination of multiprocessor system and application. Second, a good strategy should incur modest overhead. A strategy that introduces excessive communication costs, for example, may be unable to improve throughput even if it does mitigate load imbalance; idleness caused by communication latency is no more productive than idleness caused by imbalanced workloads. Third, the low operating costs of the strategy should not depend on excessive hardware support. Owing to physical limitations in circuit packaging, any extra hardware devoted to support for load balancing activity must impinge on the hardware devoted to numerical computation; we would hope that the extra needed hardware would not impinge too much, lest a machine do an excellent job of load balancing at the cost of having the arithmetic run at an unreasonably slow rate, and thereby perform worse than a machine that did a poorer job of load balancing but had faster arithmetic.

This dissertation presents a programming methodology for implementing, on multiprocessors, numerical algorithms exhibiting a spatial localization property that will be described shortly. Non-numerical computations, communication-intensive computations, or implementations on distributed multicomputer systems are not within the scope of this research. It is my thesis that a simple set of programming abstractions provided by a virtual machine (VM) can be effective in maintaining balanced workloads and, to some extent, in insulating the programmer from how a particular multiprocessing system handles communication. The abstractions have a low operating cost and require no extraordinary system support, either hardware or software, to operate efficiently. Though my approach requires that the programmer be aware of task decomposition and interprocessor communication activities, I believe that the amount of attention he must pay to them will be modest.

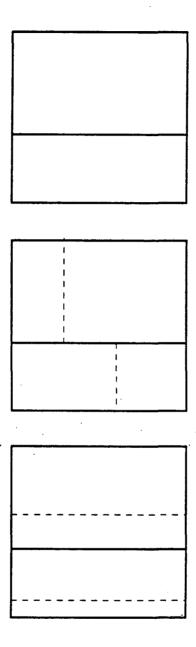

Many scientific continuum calculations use some form of spatial discretization to represent a continuous distribution of data. A specific example would be a method that takes finite differences on a grid to compute the electric field induced by a continuous charge distribution. Such algorithms work by transforming a collection of state variables through a succession of states, beginning with an initial state supplied as input. For an important subset of computational methods, the dependencies between discrete state-variables are localized in space. In this dissertation I formalize these properties in the following way:

- (1) The computation consists of two parts: a local part and a relatively inexpensive global part.

- (2) In the local part, each variable changes state only under the influence of variables lying within a small neighborhood. If we subdivide space by a fine mesh, then variables interact *locally* only if they they lie in boxes of the mesh whose indices differ by at most some specified small integer.

- (3) The time taken to update the state of the variables in the local part can be estimated from the current state by an inexpensive auxiliary computation.

My programming methodology is intended for numerical algorithms that fit this simple model of spatial localization. Specific examples of calculations that fit this algorithmic model include:

- particle methods for fluid dynamics, astrophysics, and plasma physics (as described by Hockney and Eastwood [4]);

- explicit finite difference methods for hyperbolic partial differential equations, including adaptive grid methods (as described by Berger and Bokhari [3]);

Each state-variable is assigned an initial point in problem-space which will often, though not always, have a physical significance. State transformations are localized; though each variable may change state under the influence of the others, it is more strongly influenced by nearby variables than by distant ones, where the notion of nearness is a parameter of the algorithm. More formally, nearby points communicate far more frequently with respect to the computation

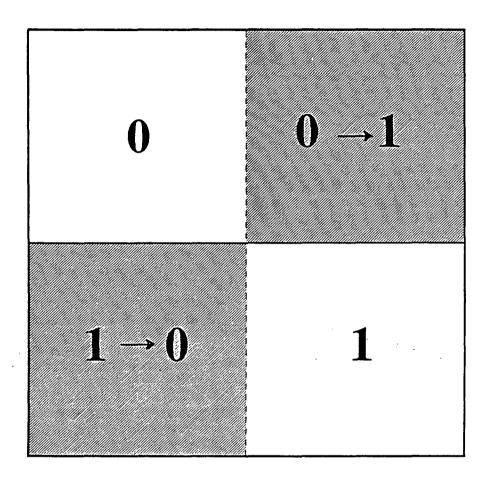

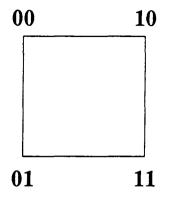

done on them than do the more distant ones. As a result of this localization property, state transformations divide into two parts: a local part and a relatively inexpensive global part. Consider the local part. If problem-space is subdivided by a fine, regular lattice of boxes, then each variable communicates only with others that lie within a small surrounding square neighborhood of boxes. Variables that are not nearby are locally independent, but may communicate in an unconstrained manner during global computation. State variables are free to move about the lattice as the result of a state-change. The cost of updating a state variable may change from one state transition to the next, and vary non-uniformly over problem-space. The cost depends primarily on the distribution of locally dependent variables and may be predicted with a simple formula involving the current values of those variables.

Numerical algorithms that fit my model apply computational effort non-uniformly over the spatial domain of the problem, and the amount of effort they apply to a point in space is a function of time. Unless dynamically repartitioned when implemented on a multiprocessor, they could cause work to accumulate on some of the processors, with the result that the others would sit mostly idle.

### 1.2. A Programming Methodology

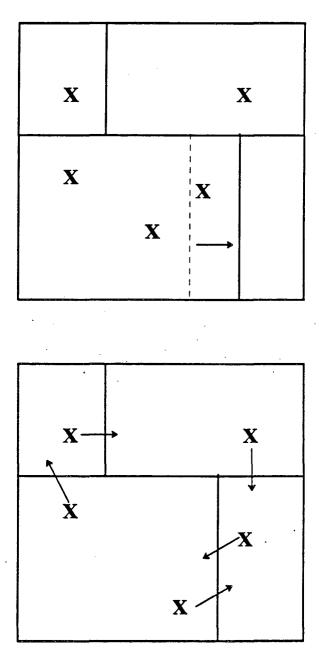

The user of my strategy for implementing spatially localized numerical algorithms adopts the following programming discipline:

- (1) He employs a local-memory execution model for local computation, in which processors communicate by passing messages.

- (2) He handles communication during global computation himself.

- (3) He calls a few utilities that decompose the computation into rectangular subproblems and handle the local communication across the edges of the subproblems. The utilities' semantics are independent of the application and of the architecture on which the utilities have been implemented.

- (4) He writes a few subroutines that depend solely on the application and passes them as arguments to the utilities.

The programmer who adopts such a discipline will be well rewarded by software that is relatively insensitive to changes in the number of processors, to interconnection structure, and to whether or not memory is shared. The parts of his software that pertain to task decomposition and localized communication will be isolated from the numerical parts of the code and confined to subroutines most of which he will use without ever reading. I believe that software modularized in this way will transport much more easily among different architectures than software written in a style in which decomposition and communication activities are woven inextricably within the program.

Computations that are spatially localized usually exhibit spatial coherency; locally interacting variables tend to form dense structures. In constraining computations to work within the framework of a mesh, we can take advantage of spatial coherency in order to reduce the cost of task decomposition and partitioning activities. Because they scatter heavily communicating variables unpredictably among processors, partitioning strategies that do not conserve spatial coherency usually incur high communication and administrative overheads. Variables that have been coherently partitioned need to communicate far less information per unit of computation to keep track of one another than do incoherently partitioned variables. In addition, such information may be communicated *en masse*, rather than a word at a time, to exploit any fast block modes of transfer provided by the underlying architecture. Another reason to exploit spatial coherency is that algorithms exist for partitioning lattices into coherent rectangular regions that can do a reasonable job of balancing workloads at low extra cost.

#### 1.3. Results

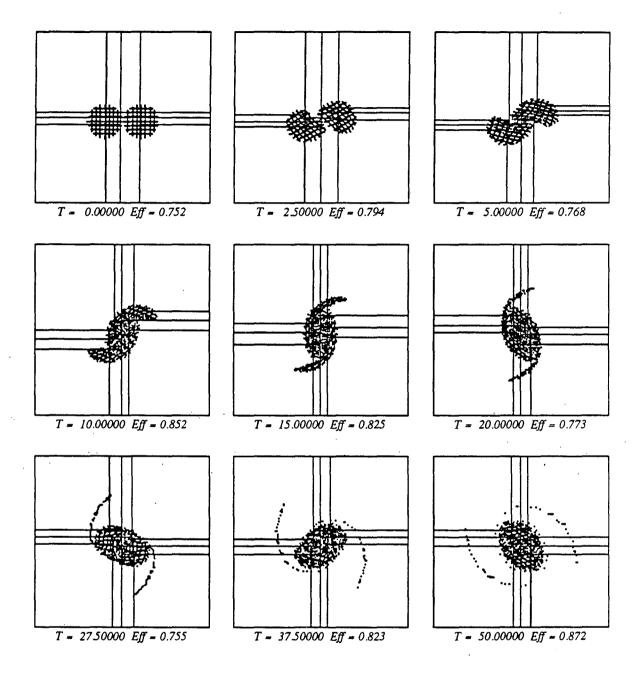

To test out my hypothesis I have implemented my load balancing utilities on the Intel Personal Scientific Computer (iPSC), a hypercube-type multiprocessor, and on the Cray X-MP/416, a shared-memory architecture with vector arithmetic capabilities. I applied them to an implementation of Anderson's Method of Local Corrections [1], a two dimensional vortex method for

incompressible inviscid flow. This particle method is typical of various problems that are spatially localized—thus appearing well suited to parallel computation—but which are hard to partition because they expend effort that varies non-uniformly both over the spatial domain of the problem and over time.

Parallel speedups of 22 were attained on the iPSC with 32 processors. The overhead of the load balancing utilities was less than 10% including interprocessor communication. This is surprisingly low in light of concerns voiced that the recursive bisection strategy would introduce high communication overhead on message-passing architectures [3,5]. Speedups of 3.6 were attained on the Cray with 4 processors. The overhead of load balancing utilities was less than 5%. Computations vectorized as well as they did on the best uniprocessor implementation, and executed floating point operations at the rate of 250 megaflops/second on 4 processors.

I speculate that the utilities will apply not only to particle methods like the Method of Local corrections but more generally to a diversity of mathematical physics calculations that fit my algorithmic model. Some elliptic problems may also fit this model owing to a local regularity property, noted by Colella, that will be discussed in a forthcoming publication [2].

This dissertation contains 7 chapters. The next chapter reviews past work. Chapter 3 briefly summarizes the important details of the model problem. Chapter 4 presents a set of programming abstractions and then applies them to the model problem, and may be thought of as a programmer's manual for my VM. It also presents an implementation strategy for the VM. Chapters 5 and 6 present experimental results obtained, respectively, from the iPSC and the Cray X-MP, and discuss some implementation details. Chapter 7 presents the major findings of the dissertation.

### 1.4. References

- C. R. Anderson, "A Method of Local Corrections for Computing the Velocity Field Due to a Distribution of Vortex Blobs," J. Comput. Phys. 62(1986), pp. 111-123.

- 2. S. B. Baden, M. J. Berger and P. Colella, "Multitasking Strategies for Adaptive Fluid Dynamics Calculations," in preparation, 1987.

- 3. M. J. Berger and S. Bokhari, "A Partitioning Strategy for Non-Uniform Problems on Multiprocessors," Technical Report 85-55, ICASE, Langley, Va., November 1985.

- 4. R. W. Hockney and J. W. Eastwood, Computer Simulation Using Particles, McGraw-Hill, 1981.

- 5. S. McCormick and D. Quinlan, Multilevel Load Balancing for Multiprocessors An Outline, University of Colorado, Denver, 1986. Grant proposal.

2

### Past Work

Я не то что позабыла о былом, нет, я не могла этого забыть, я как-то отдалилась от него.

-- Чингиз Айтматов, <u>Первый</u> <u>Учитель</u>, перевод с киргизского

... I did not forget the past, no. I couldn't have forgotten it. I sort of drifted away from it.

-Chingiz Aytmatov, "Duishen", (translation into Russian from the Kirghiz)

### 2.1. Introduction

Until very recently – the early 1980's – most results concerning run-time partitioning were obtained from simulations. Few studies were conducted on working hardware. Most of these considered simple computations, such as successive overrelaxation (SOR), that use simple regular data structures and are not heavily compute bound. As a result, communication overhead was more troublesome than workload imbalance.

Since run-time partitioning entails assigning pieces of work to processors, the immediate question is how big the pieces should be. Task size, often referred to as task granularity, can range from microscopic—on the order of a single machine instruction—to very coarse—a process, say, executing billions of instructions. Oleinick's study [16] of a speech recognition system

running on the C.mmp shared-memory multiprocessor gave early empirical evidence that load imbalance can be improved by decreasing the granularity and hence increasing the number of the tasks. Our explanation is fairly simple: the sums of the completion times of tasks can be made more even over the processors.

Oleinick's study also showed that the process of reducing task granularity will eventually reach a point of diminishing returns where the cost of managing the more numerous tasks will exceed any savings that result from having them more evenly balanced. This happens because as tasks shrink in size the fixed overhead in managing them becomes relatively expensive. We can also infer from this that fine-grained tasks do more communication relative to computation. We call this a surface effect and explain it in terms of a data dependency graph. Let the nodes of the graph correspond to the variables used in the computation, and the edges connect each pair of variables that interact. The partitioning process embeds a surface into the graph that cuts the edges, and communication overhead is roughly proportional to the number of cuts. As the number of tasks increases, the surface area of the embedded surface increases, and so does the number of cuts. Hence, communication overhead increases. Viewed differently, when surface effects are benign, nearby points are likely to be assigned to the same processor, so frequent communication between them will be inexpensive. Distant points will likely be assigned to different processors between which communication is expensive; but communication between such points turns out to be infrequent for a broad class of mathematical physics calculations of interest here that have the spatial localization property.

Having introduced the important issues, we next present a survey of run-time partitioning strategies. We roughly group the strategies into two categories, according to whether they balance workloads implicitly or explicitly.

### 2.2. Implicit Load Balancing

In an implicit strategy no attempt is made either to measure workload imbalance or to improve it. Instead, processors obtain work by sampling a pool of tasks. Although tasks may carry varying amounts of work, on average all processors will be equally loaded, so long as the work-pool is sufficiently large. The various implicit strategies differ in the way they construct the work-pool and divide it among the processors.

### 2.2.1. Non-Traditional Computer Architectures

An ideal multiprocessing system would handle all the details of task decomposition and communication for the user. Dataflow implementations [2,5] are examples of novel "non-von Neumann" systems that rely on special architectural and compiler support to distribute work automatically among the processors. See Treleaven's survey [21] for examples of others. Programs in dataflow are graphs of partially ordered operations that have no central program counter. Unlike the totally ordered operations specified in traditional uniprocessor systems, partially ordered operations can execute in an arbitrary order, so long as the data they need to execute is available. A dataflow machine therefore has the freedom to execute many operations concurrently. Nodes of a data flow graph have a microscopic granularity and represent simple primitive operations like addition or subtraction. For reasons previously stated, each processor will get a fair share of available work but for a price: the cost to administer to the fine grains of work can easily exceed the amount of work the grain does.

Gajski, Padua, and Kuck [9] have characterized the high overhead of dataflow in a different way: a dataflow machine is a very long pipeline; calculations must exhibit extreme levels of parallelism — on the order of several hundred independent instructions — to keep the pipe busy; only certain kinds of calculations in fact do so. As a result of their high overhead costs, dataflow implementations tend to require considerable hardware aimed to reducing the cost of administrative activities. This hardware could be unnecessary were the grains of work coarser,

e.g. on the order of subroutines, but then the machine would have to balance workloads explicitly. We discuss one non-traditional architecture that uses an automatic, explicit strategy in section 2.3.1.

In an ideal dataflow multiprocessor, communication overhead as well as administrative overheads would be negligible. In classic dataflow implementations, however, communication is expensive: tasks, which are small and numerous, do a lot of communication relative to the computation they do. Part of the problem is that tasks that share the same processor cannot communicate via processor registers, as would the equivalent machine instructions on traditional architectures. This happens because there is no notion of explicit storage in dataflow: a task's state is bound to a processor only for the duration of task execution and leaves the processor once the task terminates. The information must travel expensively through to higher levels of the memory hierarchy to a special repository where other instructions look for their arguments. Gajski, Padua, and Kuck [9] have cited the lack of explicit storage as one of the major shortcomings of dataflow. Such problems have motivated Hwu, Patt, and Shebanow [17] to propose the HPS restricted data flow microarchitecture with special-purpose hardware support for allowing heavily dependent tasks to communicate through processor registers. Their strategy is loosely based on the Tomasulo algorithm [1] used in the IBM 360/91.

#### 2.2.2. Processor Self-Scheduling

Processor self-scheduling is a popular technique for doing load balancing. Instead of relying on the operating system to make work assignments, each processor obtains work on its own by sampling a shared data structure. A common application is an iterative finite difference method that processes the rows of an array independently of one another, but which must finish with all the rows in one iteration before processing any rows in the next. A shared row counter keeps track of the next available row to be processed. When a processor finishes with a row, it samples and increments the row counter to get a new assignment. The sample and increment

code executes as a critical section to ensure mutually exclusive access to the counter. When the counter reaches its limit, processors without work must wait at a barrier synchronization point for the active processors to finish. So long as the number of rows is large compared with the number of processors, the wait time usually won't be noticed.

In processor self-scheduling the programmer is aware of task decomposition activity. On commercial multiprocessor systems such as the Sequent Balance [20] and the Cray X-MP and Cray-2 multiprocessors [4], the programmer annotates his program with special commands that tell the compiler to emit the code required to implement the counters, critical sections, and barrier synchronization used in processor self scheduling.

Processor self-scheduling has also been considered for research multiprocessor systems such as the IBM RP3 [18], the University of Illinois's Cedar [23], and the NYU Ultracomputer [10]. All these systems support shared-memory-based communication. Processor self-scheduling applies primarily to shared-memory architectures. On message-passing architectures both the counters and the program data structures have to shuffle between the processors. This complicates the code and introduces a high communication overhead. Counters must be sent in short messages, which are expensive owing to a high message startup cost. When tasks shuffle between processors they must leave behind forwarding trails for other processors to follow. A processor must send and receive short messages to follow such trails in order to obtain data it needs from tasks that have migrated. And, because several tasks reside on each processor, communication overhead can be further compounded by the difficulty in assigning heavily communicating tasks to the same processor.

Processor self-scheduling can incur a high communication latency on shared-memory architectures because processors must concurrently access the same memory locations to obtain new work assignments. Kumar [13] has recently noted that certain memory access patterns can severly degrade the performance of some kinds of staging networks over which the processors access memory. Even on networks for which such hot spots may not be problematic, the effect

of access conflicts— for example, on shared task queues— can be intolerable. In their studies of the MSPLICE circuit simulator running on the BBN Butterfly Multiprocessor, Jacob et al. [11] have found that use of multiple queues can help reduce memory contention delays, but at the cost of increasing the workload imbalance. They ran with up to 99 processors and obtained maximal speedups of about 25 on a machine that had no floating point hardware.

### 2.2.3. Scatter Decomposition

Fox [8] has advocated a scatter decomposition strategy for the Caltech Hypercube. The technique is currently being tried on diverse applications: a finite element method [15], ray tracing for computer graphics, and matrix decomposition. Unlike most load balancing strategies, the scattered decomposition strategy is static rather than dynamic. It begins by partitioning the domain into a fine lattice of tasks, called templates, that are far more numerous than processors, and then systematically scatters each processor's work assignments throughout the domain. Scattered decomposition for the special case of 2 processors corresponds to a red-black ordering on a checkerboard. The programmer may adjust the size of the templates, and hence the granularity of tasks, in order to trade off load imbalance against communication overhead due to surface effects.

Scatter decomposition works because each processor samples diverse regions of the problem and so obtains a fair cross section of a distribution of various task-sizes. The advantage of scattered decomposition lies in its simplicity: it partitions work statically and into simple shapes. So long as tasks don't interact over distances greater than the spacing of the templates, the underlying communication structure of the computation will involve only nearest neighbors in a mesh. This is a desirable because messages that travel only between nearest neighbors are both less expensive and easier to program than messages that involve intermediate hops. If the templates become too small, however, then message traffic may not always be simple, in which case communication would no longer be restricted to involve only nearest neighbors. In addition, as the tasks become smaller, they will send shorter, more numerous messages.

### 2.3. Explicit Load Balancing

Explicit load balancing strategies use a work metric as part of a decision-making process for assigning work to processors. The various strategies differ both in the work metric they use and in the process by which they arrive at work assignments. Unlike implicit methods, which split work into many fine-grained tasks, explicit methods tend to split work into relatively small numbers of coarse-grained chunks. As a result, explicit strategies can incur much lower overhead costs than implicit methods. Explicit load balancing strategies come in two varieties: indirect and direct. We discuss two indirect methods— pressure gradient methods and simulated annealing— and two direct methods— each based on recursive bisection.

#### 2.3.1. Indirect Methods

Pressure Gradient Methods. One kind of indirect method computes local gradients in a "work potential function" and then shifts work incrementally in the direction of the gradients. To compute a local work gradient, each processor estimates the amount of work assigned to it, exchanges the information with nearest neighbors, and then differences the information. The signs of the resultant numbers identify which processors have excess work to give up and which suffer from a work deficit, and the magnitude gives the intensity of these quantities. Such a strategy has been used in Keller's novel rediflow architecture [12], but also in more traditional implementations. Saltz [19] has used the technique for block iterative methods running on a simulated shared-memory multiprocessor with "substantial local memory." Swensen and Dippé [6] have used it for a three dimensional ray tracing graphics application, used to produce realistic artificial images, on a paper design of a mesh-connected multiprocessor.

Pressure gradient strategies are attractive because of their low overhead costs: (1) they are distributed and can exploit the concurrent resources of the machine; (2) they incur modest

amounts of communication since loads shift gradually among processors. However, use of a distributed load balancing strategy complicates the process of deciding which work to shuffle among the processors; decisions must be coordinated to avoid unstable work assignments that would periodically starve some processors while overloading others. Pressure gradient strategies that interleave load balancing activity with computation have the added disadvantage of having to maintain forwarding trails when implemented on message-passing architectures, as with processor self-scheduling.

Simulated Annealing. Simulated annealing is a probabilistic technique that has been successfully applied to various optimization problems, such as VLSI circuit placement, over the past 30 years. Recently Fox [8] and Williams [22] have discussed another application for simulated annealing – dynamic load balancing on multiprocessors. In simulated annealing, the first step is to subdivide the computational domain finely into numerous subproblems and then to initially assign the subproblems randomly to the processors. An annealing algorithm then probabilisticly readjusts the work assignments until all processors have roughly the same amount of work to do. The algorithm is biased to ignore work reassignments that would worsen workload imbalance.

The criteria for selecting desirable reassignments can be expressed as minimizing an objective function describing the energy of a system of particles. We can think of the computational elements in the calculation as charged particles that interact within a "processor space" that is distinct from the spatial domain of the problem. Particles repel one another at close distances and will tend to disperse evenly among the processors. There generally exists more than one balanced configuration of particles, though some configurations incur a lower communication overhead than others. If communication overhead were of concern, then the objective function could be augmented by a term that took into account communication costs. This term would consist of long-range attractive forces to prevent work from being moved off a processor if, as a result of the move, communication incurred during the course of computation would increase.

It is not clear how much effort is required to construct the Hamiltonian nor to evaluate it.

Indeed, Fox alludes to these problems [8]:

"... simulated annealing is a non-trivial undertaking; if we could find a simple method which gave decompositions almost as good, we would be happy".

With simulated annealing, partitions can take on irregular shapes. The software required to handle such shapes can be cumbersome, complicating the application-code. These shapes are also prone to surface effects that increase communication overhead. Though the use of simpler shapes such as rectangles could reduce communication overhead, how severely this would impede the annealer's ability to balance workloads isn't clear.

#### 2.3.2. Direct Methods

In direct methods the computation is mapped onto a regular lattice. The lattice is often rectangular though other tessellations such as hexagons could be used if appropriate. For the case of rectangular tessellations the task is to partition the lattice into rectangular regions, using a work estimate mapping that gives the cost of computing on an arbitrary sublattice. Direct methods for balancing workloads have a major advantage over indirect methods in that tasks they generate tend to form simple convex polygonal shapes without holes, and therefore tend to suffer from only modest surface effects. The reason is that the load balancer knows how to produce the smallest possible number of "nice" shapes (equal to the number of processors) that carry roughly the same amount of work. Load imbalance could probably be lowered if work were split into a swarm of tasks, or if tasks could have ragged shapes, but probably not enough to justify the effort.

We discuss three strategies based on recursive bisection. Recursive bisection works by splitting the domain into two parts that represent roughly equal amounts of work, and then recursively splitting each part until the desired number of subproblems have been rendered. The strategy has been applied to the traveling salesman problem and various problems in computer

graphics. More recently, Berger and Bokhari applied it to a two-dimensional adaptive mesh refinement calculation for hyperbolic partial differential equations [3]. Analytic results were discussed, in particular the cost of communication on various kinds of processor interconnection topologies.

McCormick and Quinlan [14] propose a variant of recursive bisection called multi-level load balancing. Their innovation is to implement recursive bisection concurrently and to incorporate communication loading into the work estimation mapping used to determine a fair subdivision of labor. They propose the following 2-stage partitioning process that generalizes to higher-dimensional problems. Assume P processors that form a perfect square. First recursively bisect the domain into  $\sqrt{P}$  strips. Then apply the procedure to each strip concurrently, making orthogonal cuts that split each strip into  $\sqrt{P}$  pieces.

Fox [7] discusses the Orthogonal Recursive Bisection strategy for decomposing sparse matrix problems. Unlike the first two recursive bisection strategies, ORB partitions space into irregular shapes, and may not apply to applications that work best when partitioned into more simple shapes like rectangles. Fox shows that ORB partitionings incur a favorable communication overhead as compared to optimal partitionings produced by simulated annealing, and for a much lower cost.

### 2.4. Comparison with Our Approach

We take a direct approach to dynamically balancing workloads that uses recursive bisection to handle task decomposition. Though recursive bisection has already been discussed in the literature, past applications of the strategy have been primarily theoretically oriented, i.e. what kind of communication overhead would be incurred on multiprocessor xyz, and how might it be avoided. In contrast, our results are based on empirical measurements of a substantial calculation running on real multiprocessors.

How recursive bisection works, or how it may be efficiently implemented is relatively unimportant in this study. Any strategy that is fast and accurate, and that can render spatially coherent partitionings would be equally well-suited to the task at hand. We are more concerned with the consequences of using run-time data partitioning to do dynamic load balancing— with communication and programming methodology— than with the mechanics of the partitioning process itself. Our contribution is a programming methodology that allows the user to remain aloof from dynamic task decomposition, and the communication that comes as a side effect. The user of such a methodology can write software that runs on different kinds of multiprocessor systems without necessarily encountering major difficulties in reprogramming for each new system.

### 2.5. References

- D. W. Anderson, F. J. Sparacio and F. M. Tomasulo, "The IBM system/360 Model 91: Machine Philosophy and Instruction-Handling," in *Computer Structures: Principles and Examples.*, D. P. Siewiorek, C. G. Bell and A. Newell (editor), McGraw-Hill, New York, 1982, pp. 276-292. Also appeared in the *IBM Journal*, Vol. 11, Jan. 1967, pp. 8-24.

- Arvind and R. E. Bryant, "Design Considerations for a Partial Differential Equation Machine," Scientific Computer Information Exchange Meeting, Livermore, California, 12-13 September 1979, pp. 94-102.

- 3. M. J. Berger and S. Bokhari, "A Partitioning Strategy for Non-Uniform Problems on Multiprocessors," Technical Report 85-55, ICASE, Langley, Va., November 1985.

- CRAY X-MP Multitasking Programmer's Manual, Cray Research, Inc., March 1986.

Order number SN-0222.

- 5. J. B. Dennis, G. Gao and K. W. Todd, "Modelling the Weather with a Data Flow Supercomputer," *IEEE Trans. Comput. C-33*,7 (July 1984), pp. 592.

- M. E. Dippé and J. A. Swensen, "An Adaptive Subdivision Algorithm and Parallel Architecture for Realistic Image Synthesis," SIGGRAPH '84 Conference Proceedings, Minneapolis, July 1984, pp. 149-158.

- G. C. Fox, "Load Balancing and Sparse Matrix Vector Multiplication on the Hypercube," C3P-327, Caltech Concurrent Computation Program, California Institute of Technology, Pasadena, California, July 1986.

- G. C. Fox and S. W. Otto, "Concurrent Computation and the Theory of Complex Systems," C3P-255, Caltech Concurrent Computation Program, California Institute of Technology, Pasadena, California, March 1986. Also CALT-68-1343.

- 9. D. D. Gajski, D. A. Padua and D. J. Kuck, "A Second Opinion on Data Flow Machines and Languages," *Computer*, February 1982, pp. 58-69.

- A. Gottlieb, B. D. Lubachevsky and L. Rudolph, "Coordinating Large Numbers of Processors," Proc. 1981 Intl. Conf. on Parallel Processing, pp. 341-349.

- G. K. Jacob, A. R. Newton and D. O. Pederson, "An Empirical Analysis of the Performance of A Multiprocessor-Based Circuit Simulator," ACM/IEEE Design Automation Conference, June 1986.

- 12. R. M. Keller and C. H. Lin, "Simulated performance of a Reduction-Based Multiprocessor," Computer, July 1984, pp. 70.

- M. Kumar and G. F. Pfister, "The Onset of Hot Spot Contention," Proc. 1986 Intl. Conf. on Parallel Processing, August 1986, pp. 28-34.

- S. McCormick and D. Quinlan, Multilevel Load Balancing for Multiprocessors An Outline, University of Colorado, Denver, 1986. Grant proposal.

- R. Morison and S. Otto, "The Scattered Decomposition for Finite Elements," C3P-286,

Caltech Concurrent Computation Program, California Institute of Technology, Pasadena,

California, May 1985.

- P. N. Oleinick, "The Implementation and Evaluation of Parallel Algorithms on C.mmp,"

CMU-CS-78-151, Dept. of Computer Science, Carnegie Mellon University, November

1978. Ph. D. Dissertation.

- 17. Y. Patt, W. Hwu and M. Shebanow, "HPS, A New Microarchitecture: Rationale and Introduction," *Proc. of the 18th Annual Workshop on Microprogramming*, Pacific Grove, California, December 1985.

- 18. G. F. Pfister and al., "The IBM RP3 Introduction and Architecture," *Proc. 1985 Intl. Conf. on Parallel Processing*, August 1985, pp. 764-771.

- 19. J. H. Saltz, Parallel and Adaptive Algorithms for Problems in Scientific and Medical Computing, Dept. of Computer Science, Duke University, 1985. Ph. D. Dissertation.

- Balance Guide to Parallel Programming, Sequent Computer Systems Inc., Beaverton,

OR, June 1986. Order Number 1003-42508 Rev. A.

- 21. P. C. Treleaven, "Data-Driven and Demand-Driven Computer Architecture," Computing Surveys 14,1 (March 1982).

- R. D. Williams, "Minimisation by Simulated Annealing: Is Detailed Balance Necessary?," C3P-354, Caltech Concurrent Computation Program, California Institute of Technology, Pasadena, California, 1986.

- C. Zhu and P. Yew, "A Synchronization Scheme and its Applications for Large Multiprocessor Systems," Proc. 4th International Conf. on Distributed Computing Systems, May 1985, pp. 486-493.

3

# **A Model Computation**

From the beginning it was never anything but chaos: it was a fluid which enveloped me, which I breathed in through the gills.

-Henry Miller, Tropic of Capricorn

## 3.1. Mathematical Background

The model calculation solves a time dependent, non-linear partial differential equation that arises in fluid mechanics— the *vorticity-stream function formulation* of Euler's equation for two dimensional, incompressible inviscid flow.

Let  $\mathbf{u}(\mathbf{x}(t),t)$  be the velocity of the fluid at position  $\mathbf{x}(t)$  at time t. Owing to the incompressibility condition,  $\nabla \cdot \mathbf{u} = 0$ ,  $\mathbf{u}$  may be expressed in terms of the stream function  $\psi$ :

$$\mathbf{u} = (u, v) = (-\partial \psi / \partial y, \partial \psi / \partial x) \tag{3.1a}$$

where u and v are the x and y components of velocity. Finally define vorticity,  $\omega$ , as the curl of velocity:

$$\omega = \frac{\partial u}{\partial y} - \frac{\partial v}{\partial x}.$$

(3.1b)

Applying (3.1a) to the (3.1b):

$$\omega = -\left[\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2}\right] \tag{3.1c}$$

The Euler equations describe the motion of an incompressible inviscid fluid. The vorticity stream function form of the equations is:

$$\frac{\partial \omega}{\partial t} + \mathbf{u} dp \, \nabla \omega = \frac{D\omega}{Dt} = 0 \tag{3.2a}$$

$$\omega = -\Delta \psi \text{ in } \Omega,$$

(3.2b)

where  $\frac{D}{Dt} = \frac{\partial}{\partial t} + udp \nabla$  is the material derivative, and  $\Delta = \frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2}$  is the two dimensional Laplacian operator. The first equation is a hyperbolic equation, the second elliptic. The flow satisfies free-space boundary conditions:  $\mathbf{u} = 0$  at  $\mathbf{x} = \infty$ . This will be satisfied if

$$\psi \sim C \log(r), \quad C = \frac{1}{2\pi} \int_{\mathbb{R}^2} \omega(r) dr$$

(3.2c)

The coupled equations (3.2) completely specify the flow. Equation (3.2a) governs the evolution of  $\omega$ ; vorticity is transported by its own velocity field  $\mathbf{u}$ , and it does not decay. Equation (3.2b) tells how to find that velocity field  $\mathbf{u}$  given  $\omega$ : solve (3.2b) for  $\psi$  subject to free-space boundary conditions (3.2c); then differentiate  $\psi$  using (3.1a). For a thorough discussion of these equations, see Chorin and Marsden's introductory text on fluid mechanics [6].

#### 3.2. The Calculation

A vortex blob method [5] will be used to solve the equations (3.2). It describes the flow of the fluid by computing the motion, over a series of timesteps, of a set of particle-like computation elements called "vortex blobs." The vortices in vortex methods are treated like the particles in astrophysics or plasma physics calculations—they move under mutual interaction. However, they are not particles of fluid but an artifact of a mathematical discretization of the problem—tagged locations that carry information about the vorticity of the fluid. Vortex

methods have many desirable properties for solving incompressible flow problems; see Chorin's early paper [5] on the vortex blob method for the details, and Leonard's survey [11] for additional information.

The vortex blob method concentrates the vorticity field into discrete patches of vorticity represented by the blobs:

$$\omega(\mathbf{x}(t),t) = \sum_{j=1}^{N} K_{\sigma}(\mathbf{x}_{j}(t) - \mathbf{x}(t)) \,\omega_{j}, \tag{3.3}$$

where  $x_j(t)$  is the position of the jth vortex blob at time t,  $\omega_j$  is a signed constant giving its strength,  $K_{\sigma}$  is called called the vortex core function, and  $\sigma$  is the cutoff radius. The strength  $\omega_j$  is the total vorticity collected from a small surrounding neighborhood and concentrated on the vortex blob of radius  $\sigma$ , and must be a constant to satisfy the vorticity evolution equation (3.2a). The core function is determined by accuracy considerations. The one used here is given by Chorin [5]:

$$K_{\sigma}(\mathbf{x}) = \begin{cases} (2\pi\sigma r)^{-1} & r < \sigma \\ 0 & r \ge \sigma \end{cases}$$

(3.4)

where  $r = |\mathbf{x}|$ . See Beale and Majda [3] or Hald [9] for other kinds of core functions. The vorticity vanishes outside the cutoff radius.

Using (3.2b) it can be shown that the *velocity* field induced by the vorticity distribution of (3.3) may be expressed as:

$$\mathbf{u}(\mathbf{x}(t),t) = \sum_{\substack{j=1\\\mathbf{x}_i \neq \mathbf{x}}}^{N} \chi_{\sigma}(\mathbf{x}_j(t) - \mathbf{x}(t)) \,\omega_j, \tag{3.5}$$

where  $\chi_{\sigma}$  is called an *influence function*. This function is like a basis function for the purpose of decomposing the velocity field and it is determined by the choice of core function. The influence function that corresponds to the core function of (3.4) is:

$$\chi_{\sigma}(\mathbf{x}) = \begin{cases} (-y, x)/2\pi r \sigma & r < \sigma \\ (-y, x)/2\pi r^2 & r \ge \sigma \end{cases}$$

(3.6)

where  $x = (x, y), r = |x| = (x^2 + y^2)^{1/2}$ .

The vortex method consists of calculating the motion of the centers of a discrete set of vortices whose strengths never change. A system of ordinary differential equations describes the motion of the vortices:

$$\frac{d}{dt}\mathbf{x}_{i}(t) = \sum_{\substack{j=1\\i\neq j}}^{N} \chi_{\sigma}(\mathbf{x}_{j}(t) - \mathbf{x}_{i}(t)) \,\omega_{j}, \ i = 1, \cdots, N, i \neq j.$$

(3.7)

Equations (3.7) are an approximation to the Lagrangian form of (3.2a); for a derivation see Anderson and Greengard [1]. The differential equations may be discretized in time with a second order Runge-Kutta time integration scheme (Heun's method). Specifically, given the positions of the N vortices after the kth timestep by the vector  $\mathbf{X}^k = (\mathbf{x}_1(k\Delta t), \dots, \mathbf{x}_N(k\Delta t))$ , where  $\Delta t$  is the timestep, we are to compute  $\mathbf{X}^{k+1}$ , the positions at the k+1st timestep, in two steps:

$$\mathbf{Q}_1 = \Delta t \, \mathbf{U}(\mathbf{X}^k; k \, \Delta t) \tag{3.8a}$$

$$\mathbf{Q}_2 = \Delta t \, \mathbf{U}(\mathbf{X}^k + \mathbf{Q}_1; (k+1)\Delta t) \tag{3.8b}$$

$$\mathbf{X}^{k+1} = (\mathbf{X}^k + \mathbf{Q}_1) + \frac{(\mathbf{Q}_2 - \mathbf{Q}_1)}{2}$$

(3.8c)

where  $Q_1$  and  $Q_2$  are N-element displacements, and  $U(X;k\Delta t)$  is the vector of velocities of the N vortices located at positions X at time  $k\Delta t$ . In the first step, called the predictor step, the vortices move by the amount  $Q_1$ , which has magnitude  $\Delta t$ . In the second step, called the corrector step, the vortices move by a much smaller amount,  $\frac{Q_2-Q_1}{2}$ , which has magnitude  $\Delta t^2$ . Generally,  $\Delta t \ll 1$ .

The standard method for evaluating the velocities in (3.7) evaluates all N(N-1) summands, and has a running time of that is quadratic in the number of vortices. The method is expensive for larger problems when the vortices number ten thousand or more. For instance, a single velocity field evaluation of 12848 vortices takes about 1 minute on one processor of a Cray X-MP/416 (Table 3.1). Production runs comprising hundreds of timesteps—with 2 velocity field evaluations per timestep required for second order accuracy in time—would take several hours. The direct method is therefore impractical when  $N \ge 10,000$ .

#### 3.3. Anderson's Method of Local Corrections

Anderson's Method of Local Corrections, abbreviated as the "MLC," may be used to accelerate the computation of (3.7) with reasonable accuracy [2]. It can be ten to fifty times faster than the direct method when the vortices number  $10^4$  or more. The MLC divides vortex interactions into two components: (1) N-body interactions computed accurately for vortices close enough to one another; (2) long-range interactions approximated by solving a discrete Poisson equation on a finite-difference grid. When they number in the thousands or more, the calculation spends most of its time computing local N-body interactions between nearby vortices. Vortices that are not so close to one another interact indirectly through the relatively inex-

| N     | Time  |  |  |

|-------|-------|--|--|

|       | (sec) |  |  |

| 1590  | 1.77  |  |  |

| 3180  | 6.99  |  |  |

| 6414  | 28.2  |  |  |

| 12848 | 113   |  |  |

Table 3.1. The direct method has an  $O(N^2)$  running time. Times are reported for a single timestep of the two-FAV problem used throughout this dissertation. Vortices are distributed uniformly within two circular patches of radius 0.13. The centers are separated by 0.25. Times were measured on a single processor of a Cray X-MP/416.

pensive global finite difference computation. The MLC is much faster than the naive method because it exploits a locality property inherent in the elliptic part of the Euler's equation (3.2b). A logarithmic potential that governs the motion of the vortices diminishes rapidly with increasing distance from a vortex so that distant interactions may effectively be averaged over large distances. The MLC is more accurate than Christiansen's vortex-in-cell method [8], which doesn't treat local interactions specially.

The MLC computes the velocity on a set of vortices in two steps:

- (1) Solve Poisson's equation for an approximate velocity field on the finite difference grid and interpolate to the centers of the vortices.

- (2) Locally correct the velocity of each vortex by undoing the portion of the approximate velocity due to nearby vortices and substituting in their place local direct interactions.

To simplify matters consider only the the x component of velocity, u; the y component, v, is computed in a similar fashion.

Step 1 calculates  $\vec{u}$ , an approximation to u on a grid, in four sub steps. Assume a single vortex centered at the origin. This simple case generalizes to arbitrary collections of vortices by superposition and linearity. The first step divides into 4 parts:

- (1.a) Set up the right hand side for Poisson's equation exclusive of Dirichlet boundary conditions.

- (1.b) Set up the boundary conditions for (1.a).

- (1.c) Solve.

- (1.d) Interpolate.

Setting up the right hand side entails smearing the influence of the vortex onto a small square neighborhood of the mesh centered on the box covering the vortex. Specifically, evaluate the spread function  $g_D(ih, jh)$  at a discrete set of points on a grid:

$$g_D(ih, jh) = \begin{cases} \Delta^h u(ih, jh) & 0 < |ih| \text{ and } |jh| \le D\\ 0 & \text{otherwise} \end{cases}$$

(3.9)

where  $\Delta^h$  is the discrete Laplacian, and u is the x component of the *point* vortex velocity function, modified to avoid self-induced velocities at the origin (the blob velocity function could also be used but is more expensive to compute):

$$\mathbf{u}(x,y) = \begin{cases} (-y,x)/2\pi r^2 & r > 0\\ 0 & r = 0 \end{cases}$$

(3.10)

Computing the Dirichlet boundary conditions for the right hand side entails evaluating the point vortex velocities at the discrete positions on the grid's boundary. This grid is then passed to the Poisson solver. The first step finishes by interpolating the velocity field returned by the solver onto the center of the vortex. We used the Lagrange interpolation formula for complex analytic functions used by Anderson [2].

The second major step of the MLC does the local corrections on the vortices distributed among the bins. Consider correcting the vortices lying in a single bin. These vortices are influenced by others lying in the correction neighborhood, a square region of space of radius C surrounding the bin (Although this square neighborhood is slightly larger than a circular neighborhood of radius C that would be good enough, the extra vortices included there can't hurt the accuracy of the calculation nor slow it down much). The local corrections divide into two parts:

- (2.a) Undo the effect of the smearing for all the vortices in the correction neighborhood of that bin.

- (2.b) Compute local interactions with those same vortices.

Step (2.a) entails, for each bin, locally reconstructing the velocity field induced by the vortices in the correction neighborhood, and interpolating onto the bin's vortices. These interpolated velocities are subtracted from what has already been accumulated on the vortices to cancel out the locally induced component of the approximate velocity field.

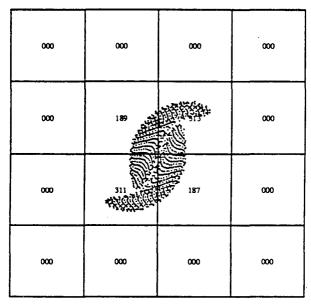

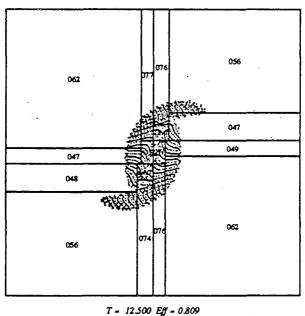

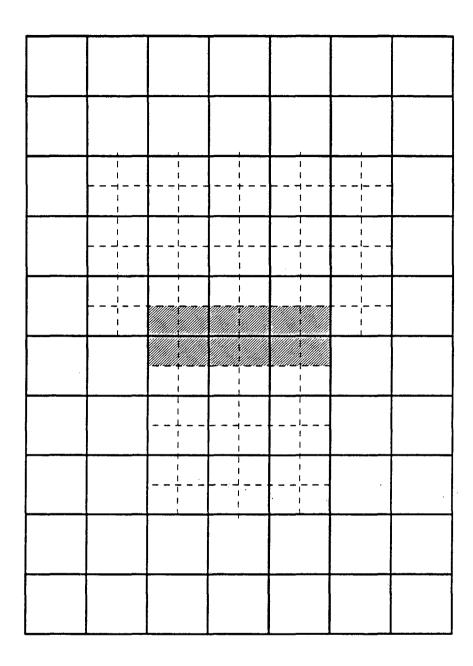

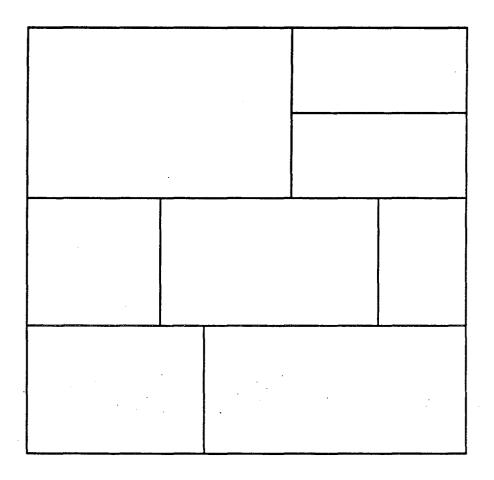

The local interactions in the MLC are computed in much the same way as direct interactions involving charged particles. The MLC requires that a "correction radius" C be chosen by the method's user to distinguish nearby vortices, closer than C, from distant ones. These nearby vortices, once identified at any time, are the ones that participate in the local part of the computation. To speed up the search for nearby vortices, space is customarily subdivided into a few thousand fairly small bins, and then the vortices are sorted into the bins, as shown in Figure 3.1. This technique is discussed in the text [10] on particle-based calculations by Hockney and Eastwood. The local interactions are handled a bin at a time. Convenience dictates setting the correction radius C to a small multiple of the bin width, say 1 or 2. Let C now stand for that multiple. Then, all the vortices influencing bin (i,j) are found in the bins whose indices differ from i and j by integers no bigger than C. These bins form shaded regions in Figure 3.1 where C = 1. In practice the bins used in the MLC are much smaller than shown in the figure, so the vortices interact directly only over short distances. The pseudo-code of Figure 3.2 summarizes the MLC.

The MLC runs in time  $O(N^2/M^4) + O(NM) + O(f(M))$ , where N is the number of vortices, M is the linear dimension of the grid used to solve Poisson's equation, and f is bounded by a polynomial of degree 3. The first term gives the running time for the local interactions, the second for the evaluation of boundary conditions, and the third for the Poisson solver. Usually  $N \gg M$ , in which case the last two terms may be ignored. This happens because as N increases, the cost of doing the local corrections grows faster than the cost of doing the finite difference computations. This is shown in Table 3.2.

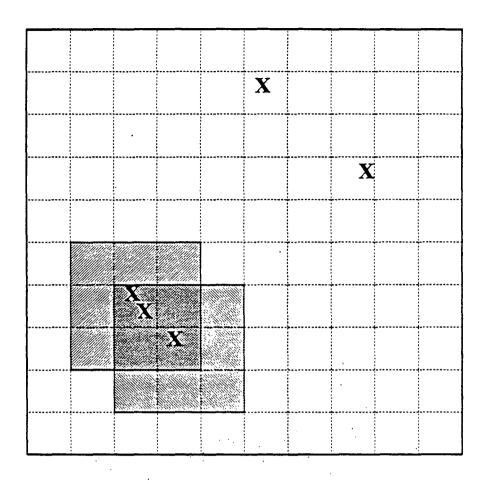

Figure 3.1. Vortices, shown as x's, get sorted into bins, demarcated here by hyphenated lines. Associated with each bin is a pointer to a list of vortices that lie within the bin's region of space. In practice, the bins are much smaller and more numerous than shown here. Each shaded region designates the domain of dependence for the bin at the region's center, with C = 1. The region contains all the vortices that influence those in the bin, and includes the bin itself.

| N     | С    | Time  | <b>%</b> | %<br>P.C. | %<br>Salara |

|-------|------|-------|----------|-----------|-------------|

|       |      | (sec) | Interact | BCs       | Solver      |

| 390   | 1/15 | 0.30  | 25.2     | 1.48      | 3.44        |

| 796   | 1/15 | 0.62  | 36.2     | 2.23      | 1.87        |

| 1590  | 1/15 | 1.39  | 51.8     | 2.96      | 1.26        |

| 3180  | 1/15 | 3.49  | 69.2     | 3.17      | 0.69        |

| 6414  | 1/30 | 6.51  | 54.8     | 4.97      | 1.18        |

| 12848 | 1/30 | 16.4  | 70.5     | 5.04      | 1.24        |

| 25702 | 1/60 | 29.3  | 53.3     | 7.95      | 3.85        |

Table 3.2. A breakdown of the times spent in various phases of the MLC calculation reveals that the local interactions computation predominates when the vortices number in the thousands. For N > 3180, we roughly scaled the interaction distance C with the square root of the number of vortices. This reduces the running time of the computation from a quadratic function of N to an almost linear function, and decreases the fraction of time spent computing local interactions. The time column gives the time to compute a single timestep. Measurements were taken from a single processor of a Cray X-MP/22 running version 114g of the CFT compiler (this is a dialect of CFT used at the National Magnetic Fusion Energy Computer Center at the Lawrence Livermore National Laboratory). This Cray runs about 15% slower than the X-MP/416 we used.

#### 3.4. Accuracy and Parameter Selection

The MLC is a subroutine that evaluates the velocity field at the centers of a collection of vortices. Like most particle methods, vortex calculations involve integrating the positions of the vortices with respect to time, i.e. "pushing" them over a discrete series of timesteps, doing one or more velocity field evaluations per timestep. As previously mentioned, the time integration scheme we used is accurate to second order, and does two velocity field evaluations per timestep. In addition to computing local interactions, the MLC also does some finite difference computations, including a global calculation to solve Poisson's equation. All finite difference calculations were accurate to fourth order.

A variety of parameters play an important role in determining the speed and the accuracy of the MLC. There is the cutoff radius  $\sigma$ , the finite difference mesh spacing h, the correction radius C, and the spreading radius D. For all the test problems used here vortices are initially set up on a lattice with spacing  $h_v$ . The following parameter settings were used for all the runs:

```

Compute the velocities induced on a set of vortices sorted into bins

Each bin is a pointer to a collection of vortices

The calculation uses a finite difference mesh g_D to speed up the computation

h is the spacing of the mesh

C is the correction distance, measured in mesh boxes, and is chosen by the user

Ignore any indices lying outside the domain

Compute an approximate velocity field \tilde{\mathbf{u}} on the grid g_D

First set up the RHS for the solver

foreach bin (i, j)

for each vortex (x,\omega) in bin (i,j)

\Delta u, the Laplacian of the velocity induced by a vortex,

vanishes with increasing distance from the vortex

We approximate this quantity in two parts: \Delta^h \hat{\mathbf{u}} inside a square neighborhood

centered on the box covering the vortex, and zero outside.

The neighborhood is 2D+1 boxes on a side.

\chi_{point}(\mathbf{r}) is the velocity induced at \mathbf{r} by a point vortex of unit strength at the origin \chi_{blob}(\mathbf{r}) is the velocity induced at \mathbf{r} by a vortex blob of unit strength at the origin

g_D(i,j) := g_D(i,j) + \Delta^h \chi_{point}(y-x) * \omega

\mathbf{y} = (-0.5 + (i + k)*h, -0.5 + (j + l)*h),

(k, l) \in [-C - 1 \dots 0 \dots C + 1] \times [-C - 1 \dots 0 \dots C + 1]

Compute the boundary conditions

foreach (i, j) on a boundary point y

g_D(i,j) := g_D(i,j) + \chi_{point}(\mathbf{y} - \mathbf{x}) * \omega

Find \tilde{\mathbf{u}} such that \Delta \tilde{\mathbf{u}} = g_D

call solver(g_D, \bar{\mathbf{u}})

-- Interpolate

foreach bin (i, j)

for each vortex (x,u) in bin (i,j)

update u by interpolating from \vec{u} onto x and adding

-- Local corrections

for each bin (i, j)

for each vortex (x,u) \in bin(i,j)

for each vortex (y, \omega) \in bin(k, l)

where (k, l) \in [-C + i ... i ... C + i] \times [-C + j ... j ... C + j]

Subtract off ū due to nearby vortices

update u by interpolating \chi_{point}(\tilde{x}-y)*\omega

onto x and subtracting

where \bar{x} ranges over the 5-point stencil

of points centered on bin(k, l)

Compute local interactions

update u by adding \chi_{blob}(x-y)*\omega

```

Figure 3.2. Anderson's Method of Local Corrections computes the velocity field induced at the centers of a collection of vortices.

$$\begin{array}{ccc}

\sigma & h_{\nu}^{0.75} \\

C & 2h \\

D & 2h

\end{array}$$

The values of  $h_v$  we used varied in magnitude from  $10^{-2}$  to  $10^{-3}$  while h ranged from 1/30 to 1/240. The timestep  $\Delta t$  used in our time integration scheme ranged from  $5\times10^{-2}$  to  $6.25\times10^{-3}$ . The settings for  $\sigma$ , C, and D  $\Delta t$  seem reasonable in light of other results by Anderson [2], Anderson and Greengard [1], Beale and Majda [4], Perlman [12], and Chorin [7].

The spreading radius D affects the accuracy of the global part of the solution and can be no smaller than  $\sigma$ . It cannot hurt to make D slightly too large, although the cost to set up the right hand size for Poisson's equation increases roughly as  $D^2$ . C can be no smaller than  $\sigma$  because the finite difference approximation to u isn't accurate inside the core of the vortex  $(r < \sigma)$  and must be corrected there. The answers get more accurate with increasing C, but for a price; the cost to do the local corrections varies roughly as the square of C, depending on the local density of vortices.

We did a three parameter study to gain a better understanding of the appropriate settings for some of the parameters. We varied  $h_v$ , h, and  $\Delta t$  over runs of a single test problem with a known exact solution, and compared the known solution with that computed by the MLC. The initial vorticity distribution for the test problem is radially symmetric and vanishes outside a circle of radius 0.25 centered about the origin. The vortices are distributed on a uniform mesh of points, with the strength of a vortex at  $\mathbf{x} = (x,y)$  given by  $4\pi(1-4(x^2+y^2))^7$ . The vortices rotate about the origin, with a angular velocity that increases with decreasing distance from the origin. See Perlman [12] for the details. The runs were stopped when the fastest moving vortices had rotated one revolution. The  $L_2$  norm of the error was reported. This error is defined as:

$$h_{\mathbf{v}} \left[ \sum_{j=1}^{N} (\text{computed } (x_j) - \text{exact } (x_j))^2 \right]^{1/2}$$

(3.11)

Three different values of  $h_v$  were used and correspond with N, the number of vortices, as

follows:

| N     | $h_{\nu}$ |

|-------|-----------|

| 1005  | 0.014     |

| 4020  | 0.007     |

| 16043 | 0.0035    |

The results of the study are presented in Table 3.3, and tell us three things:

- (1)  $\Delta t/h_{\nu}$  must remain constant, i.e. the time step must decrease as the vortices increase in number. The choice of appropriate time step can be inferred by moving across a row and noting when decreasing the timestep doesn't appreciably decrease the error.

- (2) The correction radius C scales with  $\sigma = h_{\nu}^{0.75}$ . Accuracy is insensitive to changes in C, so long as  $C > \sigma$ . This can be inferred by moving down a column and keeping the number of vortices fixed.

- (3) Accuracy improves significantly as the vortices are initially spaced more closely, so long as an appropriate timestep has been chosen.

The second result is significant since it tells us that the number of local interactions need not necessarily grow as  $N^2$ , if C and hence h are decreased with  $h_v$ . This is indeed what has been observed in practice, as shown in Table. 3.4.

| N     | h      | Δι                     |                        |                        |                        |                        |

|-------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|

| N     |        | 0.1                    | 0.05                   | 0.025                  | 0.0125                 | 0.00625                |

| 1005  | 1/30   | 9.090×10 <sup>-3</sup> | 4.566×10 <sup>-3</sup> | 3.497×10 <sup>-3</sup> | 3.243×10 <sup>-3</sup> | 3.175×10 <sup>-3</sup> |

|       | 1/60   | 9.082×10 <sup>-3</sup> | 4.556×10 <sup>-3</sup> | 3.488×10 <sup>-3</sup> | 3.233×10 <sup>-3</sup> | 3.165×10 <sup>-3</sup> |

| 4020  | 1/30   | $7.659 \times 10^{-3}$ | 3.648×10 <sup>-3</sup> | 1.476×10 <sup>-3</sup> | 1.216×10 <sup>-3</sup> | _                      |

|       | 1/60   | 7.661×10 <sup>-3</sup> | 3.650×10 <sup>-3</sup> | 1.478×10 <sup>-3</sup> | 1.218×10 <sup>-3</sup> | -                      |

|       | direct | 7.658×10 <sup>-3</sup> | 3.646×10 <sup>-3</sup> | 1.474×10 <sup>-3</sup> | 1.214×10 <sup>-3</sup> | _                      |

| 16043 | 1/30   | 7.172×10 <sup>-3</sup> | 1.971×10 <sup>-3</sup> | 7.479×10 <sup>-4</sup> | 4.828×10 <sup>-4</sup> | 4.219×10 <sup>-4</sup> |

|       | 1/60   | 7.173×10 <sup>-3</sup> | 1.974×10 <sup>-3</sup> | 7.500×10 <sup>-4</sup> | 4.850×10 <sup>-4</sup> | 4.241×10 <sup>-4</sup> |

|       | 1/120  | 7.174×10 <sup>-3</sup> | 1.974×10 <sup>-3</sup> | 7.506×10 <sup>-4</sup> | 4.856×10 <sup>-4</sup> | 4.247×10 <sup>-4</sup> |

Table 3.3. Results from a three parameter study show the effect of varying certain simulation parameters on the accuracy of the computed solution. For comparison, a result for the direct method is presented for the single case of 4020 vortices; accuracy is not significantly better than it is with the MLC.

|        |       | Time/ti |        |                |

|--------|-------|---------|--------|----------------|

| N      | С     | MLC     | Direct | MLC<br>Speedup |

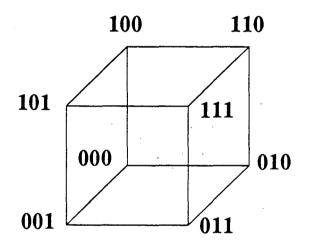

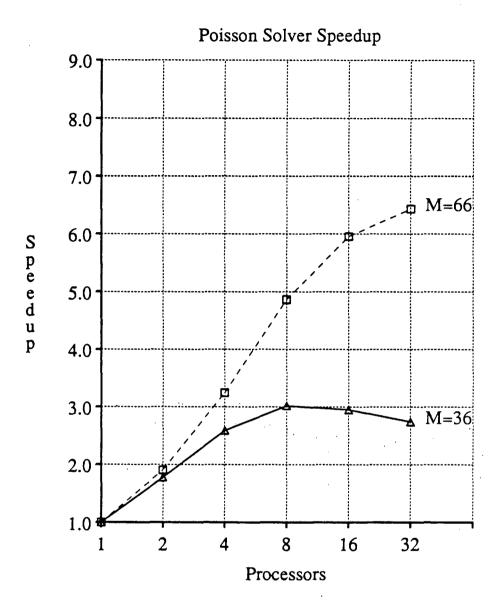

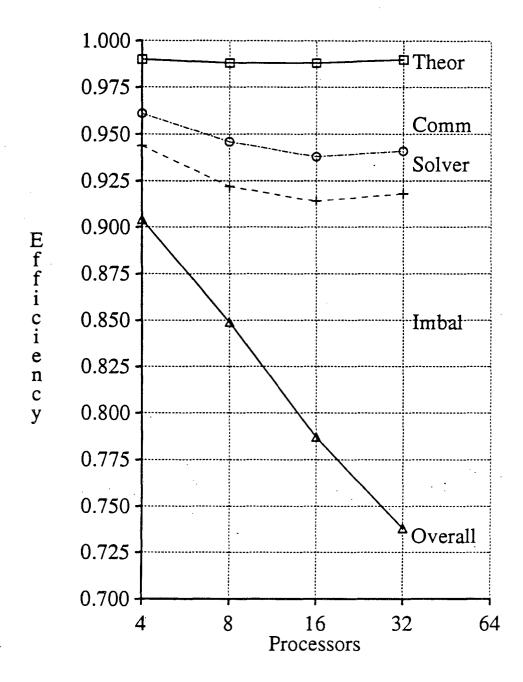

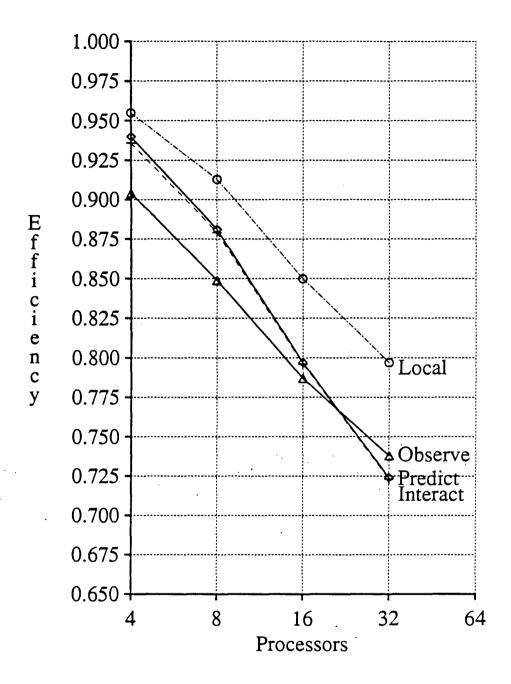

| 12848  | 1/30  | 0.25    | 1.9    | 7.6            |