### **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

### **Title**

System-Level Electromigration-Induced Dynamic Reliability Management

### **Permalink**

https://escholarship.org/uc/item/9tc8w0b9

### **Author**

Kim, Taeyoung

### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

System-Level Electromigration-Induced Dynamic Reliability Management

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Taeyoung Kim

June 2017

### Dissertation Committee:

Dr. Sheldon X.-D. Tan, Chairperson

Dr. Nael Abu-Ghazaleh

Dr. Zizhong Chen

Dr. Daniel Wong

University of California, Riverside

### Acknowledgments

This thesis could not have been completed without the great support that I have received from so many people over the years. I wish to offer my most heartful thanks to the following people.

I would like to thank my advisor, Dr. Sheldon X.-D. Tan for guiding and supporting me over years. He has set an example of excellence as researcher, mentor, instructor and role model. His kindness, insight and suggestions always lead me to the right way.

I would like to thank my thesis committee members, Dr. Nael Abu-Ghazaleh, Dr. Zizhong Chen, Dr. Daniel Wong for their direction, dedication and invaluable advice. In addition to committee members, I would like to thank two other faculties, Dr. Hyoseung Kim and Dr. Qi Zhu for the discussion, ideas and feedback on Chapter 7 and Chapter 3 in this thesis.

I would like to thank all the members in our VSCLAB (VLSI System & Computation Laboratory) at University of California at Riverside (UCR). I thank especially Xin, Kai, Hao-Bao, Yan, David, Yue, Hengyang, Zhongdong, Chase, Zeyu, Han, Lebo, and Shaoyi for the collaborative research works, discussion and help, which lead to the presented works in this thesis. I appreciate the friendship of my fellow students in UCR.

Last but not least, I would like to thank my family, Yunji, Jihu (Theodore), and Sunghu (Edward), and my parents for the love, support, and constant encouragement during the years of my study. I undoubtedly could not have done this without them.

#### ABSTRACT OF THE DISSERTATION

System-Level Electromigration-Induced Dynamic Reliability Management

by

#### Taeyoung Kim

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, June 2017 Dr. Sheldon X.-D. Tan, Chairperson

Technology scaling has led to further processor integration, and future manycore chips will have more cores integrated. However, due to the diminishing of Dennards scaling, the power density of chips starts to increase for current and future technology nodes. Because of this, only a certain percentage of a manycore processor can be powered on because of power and temperature limitations. These trends have resulted in so-called dark silicon manycore processors. Additionally, reliability is becoming a limiting constraint in high-performance nanometer VLSI chip designs due to the high failure rates in deep submicron and nanoscale devices. It is expected that future chips will show signs of reliability-induced aging much faster than the previous generations. Among of many reliability effects, electromigration (EM)-induced reliability has become a major design constraint due to the aggressive transistor and interconnect scaling and increasing power density.

This thesis focuses on developing new system level EM-induced dynamic reliability managements on many different systems. Specifically, first, I develop system level management for real-time embedded systems. I investigate a new lifetime optimization technique

for real-time embedded processors considering the electromigration-induced reliability. The new approach is based on a recently proposed physics-based electromigration (EM) model for more accurate EM assessment of a power grid network at the chip level. Second, I develop a new energy and lifetime optimization techniques for emerging dark silicon manycore microprocessors considering both hard long-term reliability effects (hard errors) and transient soft errors. To optimize EM-induced lifetime, I apply the adaptive Q-learning based method, which is suitable for dynamic runtime operation as it can provide cost-effective yet good solutions. Third, I develop a new dynamic reliability management (DRM) techniques at the system level for emerging low power dark silicon manycore microprocessors operating in near-threshold region. I mainly consider the electromigration (EM) recovery effects. To leverage the EM recovery effects, which was ignored in the past, at the system-level, I develop a new equivalent DC current model to consider recovery effects for general timevarying current waveforms so that existing compact EM model can be applied. Fourth, I develop a new approach for cross-layer electromigration (EM) induced reliability modeling and optimization at physics, system and data center levels. To speed up the online optimization for energy in a data center, I investigate a new combined data center power and reliability compact model using a learning based approach in which a feed-forward neural network (FNN) is trained to predict energy and long term reliability for each processor under data center scheduling and workloads. Lastly, I develop long-term reliability management for GPU architectures using spatial multitasking, which allows GPU computing resources to be partitioned among multiple applications. I find that the existing reliability-agnostic thread block scheduler for spatial multitasking is effective in achieving high GPU utilization, but poor in reliability. I develop and implement a long-term reliability-aware thread block scheduler in GPGPU-sim, and compare it against the existing reliability-agnostic scheduler.

# Contents

| Li | st of | Figures                                                              | xii |

|----|-------|----------------------------------------------------------------------|-----|

| Li | st of | Tables                                                               | χv  |

| 1  | Intr  | roduction                                                            | 1   |

|    | 1.1   | Motivation                                                           | 1   |

|    |       | 1.1.1 Reliability issue for real-time embedded systems               | 3   |

|    |       | 1.1.2 Reliability issue for dark silicon processors                  | 4   |

|    |       | 1.1.3 Reliability issue for near-threshold dark silicon processors   | 7   |

|    |       | 1.1.4 Reliability issue for data center systems                      | 8   |

|    |       | 1.1.5 Reliability issue for general-purpose graphics computing units | 10  |

|    | 1.2   | Dissertation contributions                                           | 11  |

|    | 1.3   | Organization                                                         | 16  |

| 2  | Elec  | ctromigration reliability model                                      | 17  |

|    | 2.1   | Review of the physics-based EM modeling                              | 17  |

|    |       | 2.1.1 Void dynamics: nucleation and growth phases                    | 20  |

|    |       | 2.1.2 EM assessment at power grid level                              | 24  |

|    | 2.2   | Summary                                                              | 26  |

| 3  | Reli  | iability-aware lifetime optimization for real-time embedded systems  | 27  |

|    | 3.1   | System-level EM-induced reliability model                            | 28  |

|    | 3.2   | Real-time embedded system models                                     | 29  |

|    | 3.3   | Proposed new lifetime optimization method                            | 31  |

|    |       | 3.3.1 The new lifetime optimization flow                             | 32  |

|    |       | 3.3.2 Formulation one: continuous constrained nonlinear optimization | 36  |

|    |       | 3.3.3 Formulation two: mixed-integer linear programming              | 37  |

|    | 3.4   | Numerical results and discussions                                    | 44  |

|    |       | 3.4.1 Experimental setup                                             | 50  |

|    |       | 3.4.2 Evaluation of proposed lifetime optimization                   | 51  |

|    |       | 3.4.3 Core utilization effects and trade-off on energy and lifetime  | 52  |

|    |       | 3.4.4. Solution quality study and analysis                           | 53  |

|   | 3.5  | 3.4.5 Trade-off between performance and lifetime                                                                                          | 54<br>55          |  |  |  |  |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| 4 | Lea  | rning-based reliability management and energy optimization for mary-                                                                      |                   |  |  |  |  |

| _ |      | e dark silicon processors                                                                                                                 | 57                |  |  |  |  |

|   | 4.1  | Review of system-level EM and soft error reliability models                                                                               | 58                |  |  |  |  |

|   |      | 4.1.1 System-level EM reliability model                                                                                                   | 58                |  |  |  |  |

|   |      | 4.1.2 Soft error reliability model considering DVFS impacts                                                                               | 59                |  |  |  |  |

|   |      | 4.1.3 Impact of process technology on soft error reliability model                                                                        | 61                |  |  |  |  |

|   | 4.2  | New dynamic lifetime and energy optimization methods for dark silicon                                                                     | 62                |  |  |  |  |

|   |      | 4.2.1 Q-learning based formulation and solution for lifetime and energy                                                                   |                   |  |  |  |  |

|   |      | optimizations                                                                                                                             | 63                |  |  |  |  |

|   |      | 4.2.2 MILP based formulation and solution for lifetime optimization                                                                       | 69                |  |  |  |  |

|   |      | 4.2.3 Implementation of the dark silicon evaluation platform                                                                              | 70                |  |  |  |  |

|   |      | 4.2.4 Time complexity analysis                                                                                                            | 74                |  |  |  |  |

|   |      | 4.2.5 Practical application of the proposed DRM with reliability models .                                                                 | 74                |  |  |  |  |

|   | 4.3  | Numerical results and discussions                                                                                                         | 76                |  |  |  |  |

|   |      | 4.3.1 Experimental setup                                                                                                                  | 76                |  |  |  |  |

|   |      | 4.3.2 Evaluation of the proposed Q-Learning lifetime optimization method                                                                  | 77                |  |  |  |  |

|   |      | 4.3.3 Accuracy and convergence rate of proposed Q-learning DRM method                                                                     | 78                |  |  |  |  |

|   |      | 4.3.4 Hard and soft errors in dark silicon manycore processor                                                                             | 83                |  |  |  |  |

|   |      | 4.3.5 Evaluation of proposed Q-Learning based energy optimization method                                                                  | 85                |  |  |  |  |

|   | 4.4  | Summary                                                                                                                                   | 94                |  |  |  |  |

| 5 |      | Recovery-aware dynamic reliability management for near-threshold dark                                                                     |                   |  |  |  |  |

|   |      | con processors                                                                                                                            | 96                |  |  |  |  |

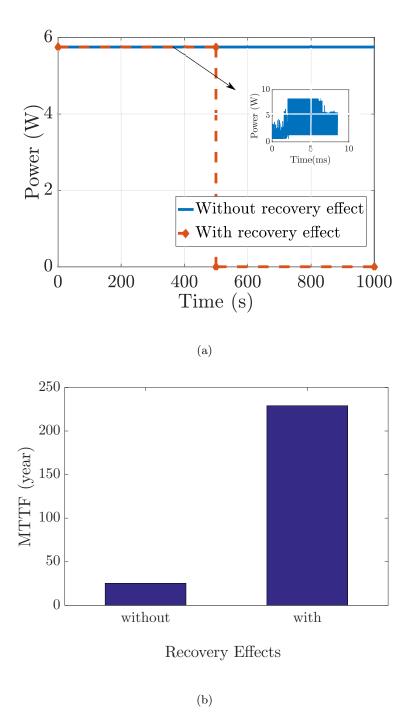

|   | 5.1  | Recovery-aware Electromigration modeling at system levels                                                                                 | 97                |  |  |  |  |

|   |      | 5.1.1 New equivalent DC current based modeling for EM recovery effects.                                                                   | 97                |  |  |  |  |

|   | - 0  |                                                                                                                                           | 103               |  |  |  |  |

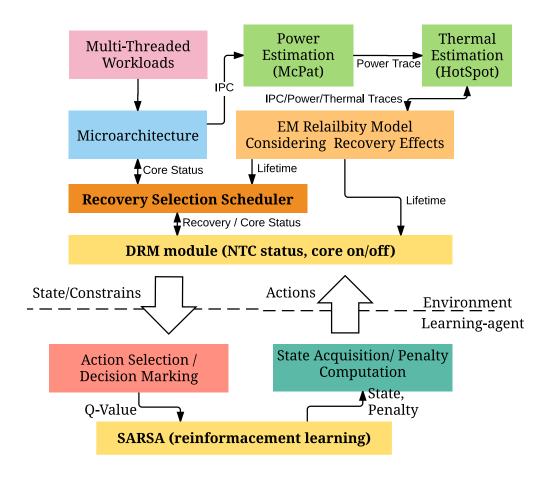

|   | 5.2  | New learning-based reliability management for near threshold dark silicon                                                                 | 100               |  |  |  |  |

|   |      | · ·                                                                                                                                       | 106               |  |  |  |  |

|   |      |                                                                                                                                           | $\frac{106}{107}$ |  |  |  |  |

|   |      | 5.2.2 Framework of dark silicon in near-threshold computing region 5.2.3 SARSA-based learning algorithm for DRM considering long-term re- | 107               |  |  |  |  |

|   |      |                                                                                                                                           | 110               |  |  |  |  |

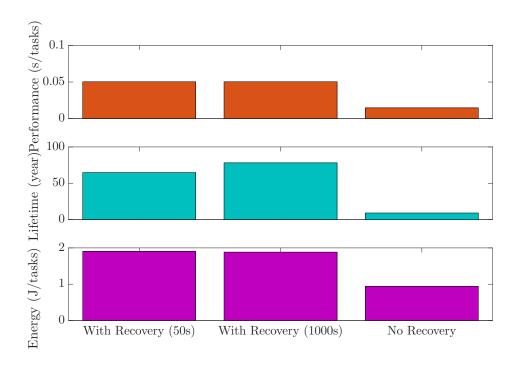

|   | 5.3  | v                                                                                                                                         | $110 \\ 115$      |  |  |  |  |

|   | 5.5  |                                                                                                                                           | $115 \\ 115$      |  |  |  |  |

|   |      | • • • • • • • • • • • • • • • • • • • •                                                                                                   | 116               |  |  |  |  |

|   |      | •                                                                                                                                         | $117 \\ 117$      |  |  |  |  |

|   | 5.4  |                                                                                                                                           | $117 \\ 117$      |  |  |  |  |

| 6 | Cro  | ss-layer modeling and optimization for electromigration-induced reli-                                                                     |                   |  |  |  |  |

|   | abil |                                                                                                                                           | 119               |  |  |  |  |

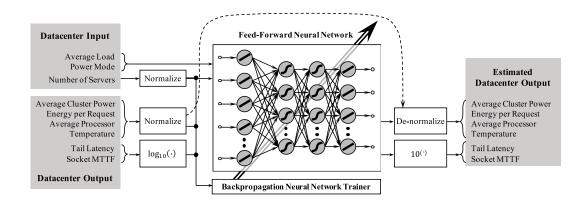

|   | 6.1  |                                                                                                                                           | 120               |  |  |  |  |

|   | 6.2  | v ž                                                                                                                                       | 121               |  |  |  |  |

|    | 6.3    | New reliability-constrained energy optimization for datacenter               | 123  |

|----|--------|------------------------------------------------------------------------------|------|

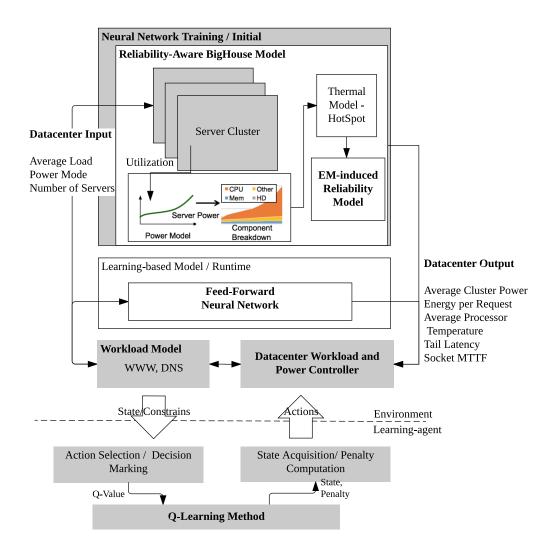

|    |        | 6.3.1 Neural networks for datacenter energy and reliability models           | 123  |

|    |        | 6.3.2 Q learning optimization for datacenter                                 | 126  |

|    |        | 6.3.3 Proposed new datacenter framework for energy and reliability           | 129  |

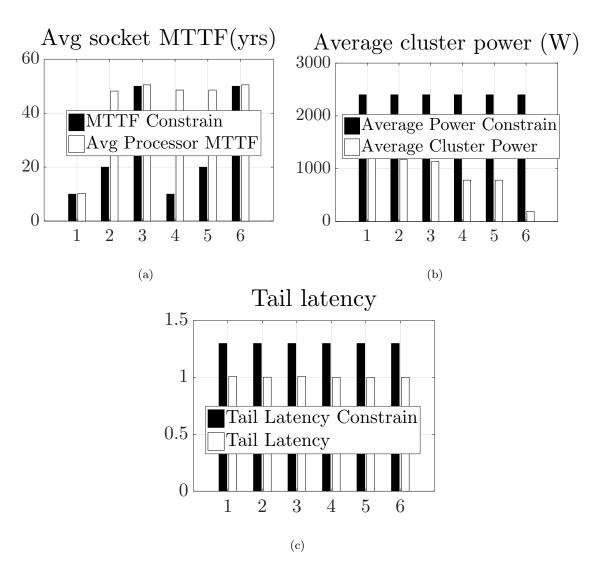

|    | 6.4    | Numerical results and discussions                                            | 130  |

|    |        | 6.4.1 Experimental setup                                                     | 130  |

|    |        | 6.4.2 Evaluations of proposed new modeling and optimization                  | 131  |

|    | 6.5    | Summary                                                                      | 133  |

| 7  | Lon    | g-term reliability management for multitasking GPGPUs                        | 135  |

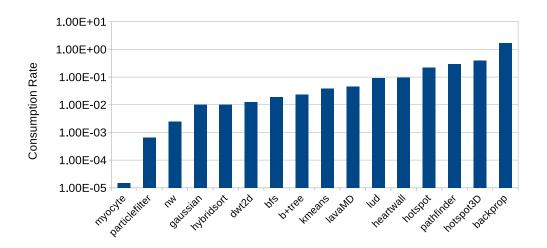

|    | 7.1    | System-level reliability resource consumption model                          | 135  |

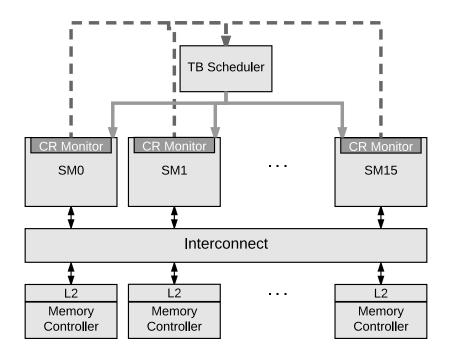

|    | 7.2    | GPGPU Architecture and Stream Multiprocessor Scheduling                      | 140  |

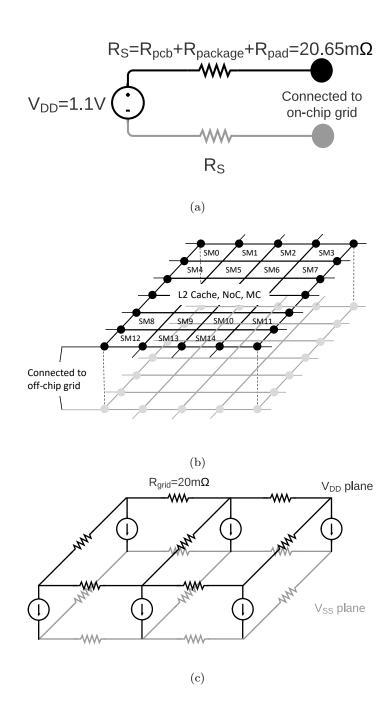

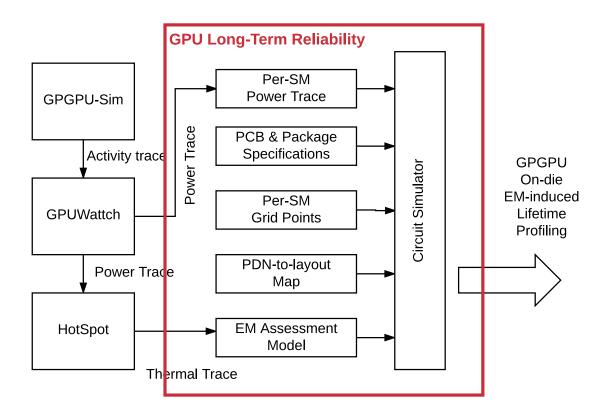

|    | 7.3    | Simulation Framework for EM Assessment on GPGPU                              | 141  |

|    | 7.4    | Resource consumption rate-aware thread block scheduler for long-term reli-   |      |

|    |        | ability                                                                      | 145  |

|    | 7.5    | Numerical results and discussions                                            | 149  |

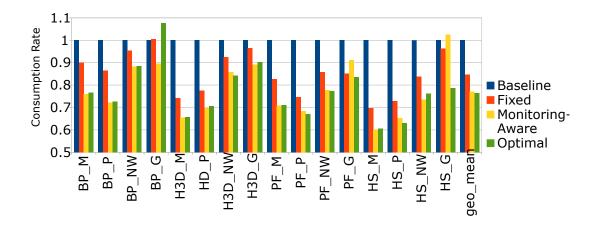

|    |        | 7.5.1 Fixed Scheduling Performance                                           | 150  |

|    |        | 7.5.2 Monitoring-Aware Scheduling Evaluation                                 | 151  |

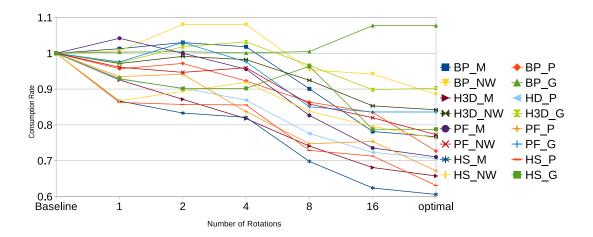

|    |        | 7.5.3 Sensitivity to SM partitioning                                         | 151  |

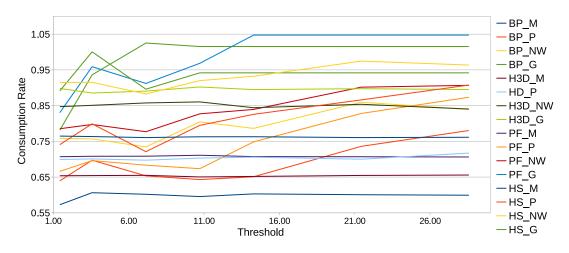

|    |        | 7.5.4 Threshold Exploration                                                  | 152  |

|    | 7.6    | Summary                                                                      | 154  |

| 8  | Cor    | nclusion                                                                     | 155  |

|    | 8.1    | Summary of research contributions                                            | 156  |

|    |        | 8.1.1 Reliability-aware lifetime optimization for real-time embedded systems | s156 |

|    |        | 8.1.2 Learning-based reliability management and energy optimization for      |      |

|    |        | mary-core dark silicon processors                                            | 157  |

|    |        | 8.1.3 EM Recovery-aware dynamic reliability management for near-threshold    |      |

|    |        | dark silicon processors                                                      | 158  |

|    |        | 8.1.4 Cross-layer modeling and optimization for EM-induced reliability in    |      |

|    |        | data center                                                                  | 159  |

|    |        | 8.1.5 Long-term reliability management for multitasking GPGPUs $\dots$ .     | 159  |

| Bi | iblios | graphy                                                                       | 161  |

|    |        | <b>5 I</b> √                                                                 |      |

# List of Figures

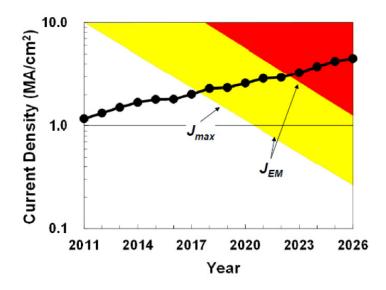

| 1.1        | Evolution of current densities: $J_{max}$ , the maximum equivalent DC current density and $J_{EM}$ , the current density for targeted lifetime [1] (a) Total datacenter cost by primary causes of unplanned outage (Thousand                                                                                          | 2        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

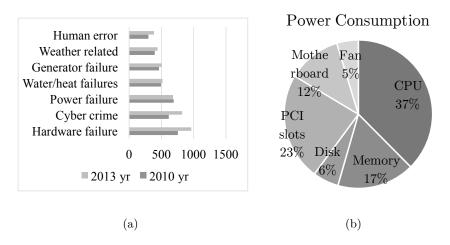

| 1.2        | dollars) (b) Power consumption breakdown for one server                                                                                                                                                                                                                                                               | 9        |

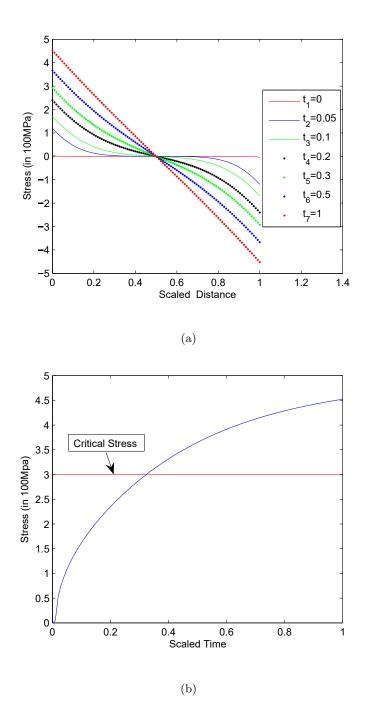

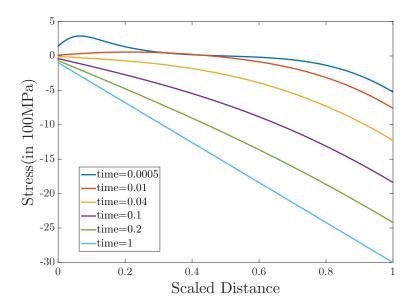

| 2.1<br>2.2 | Interconnect tree confined by diffusion barriers/liners [2]                                                                                                                                                                                                                                                           | 19<br>22 |

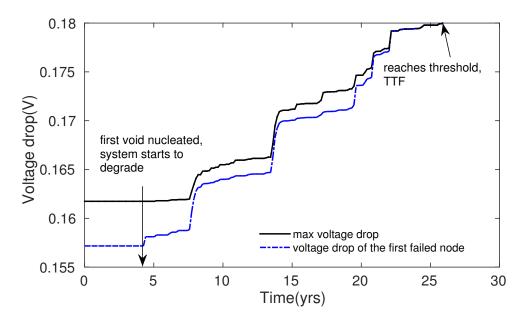

| 2.3<br>2.4 | EM-stress distribution change over time in simple metal wire for void growth [3]. Voltage of the first failed node in different simulation time [4]                                                                                                                                                                   | 23<br>25 |

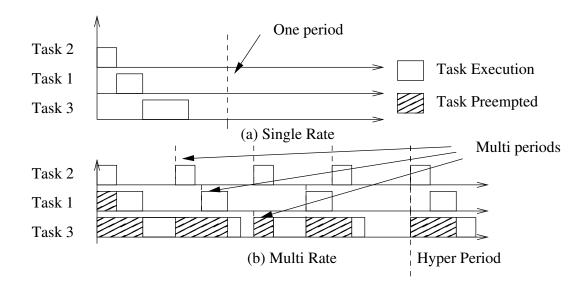

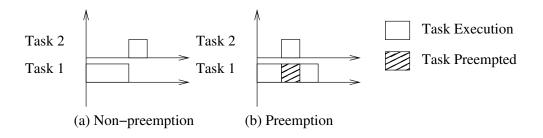

| 3.1        | Single-rate and multi-rate task scheduling models                                                                                                                                                                                                                                                                     | 31       |

| 3.2        | Multi-rate preemption                                                                                                                                                                                                                                                                                                 | 35       |

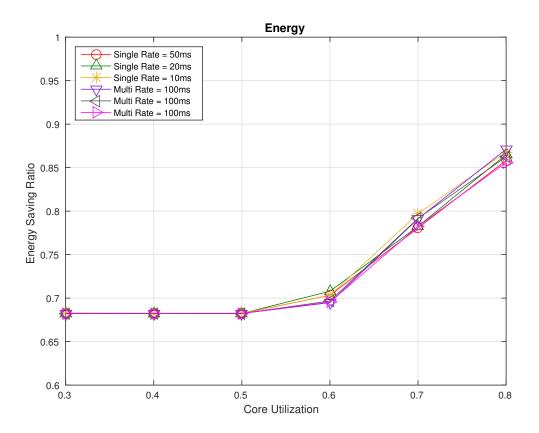

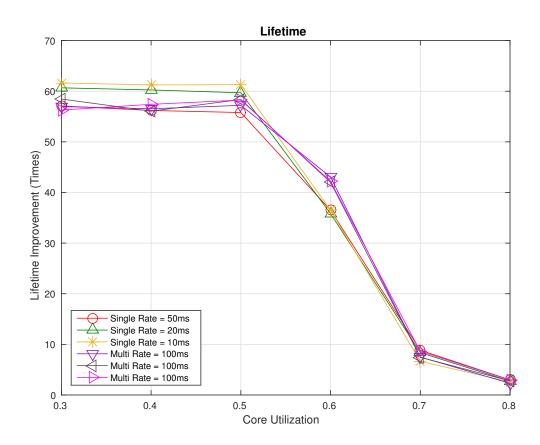

| 3.3        | Core utilization effect - energy savings                                                                                                                                                                                                                                                                              | 44       |

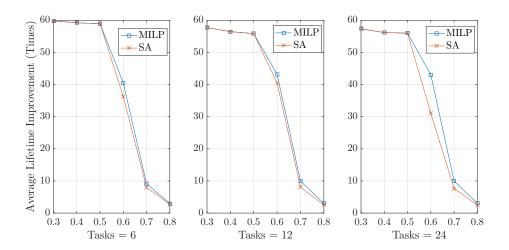

| 3.4<br>3.5 | Core utilization effect - lifetime improvement                                                                                                                                                                                                                                                                        | 46       |

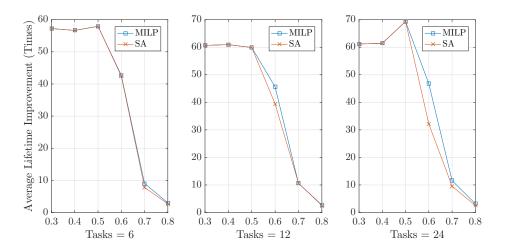

| 3.6        | tasks per one task set under different core utilizations (0.3 to 0.8 in x-axis)  The comparisons of simulated annealing and mixed-integer linear programming methods for the lifetime optimization for multi-rate with 6, 12, and 24  tasks per one task set under different gove utilizations (0.3 to 0.8 in x-axis) | 50<br>50 |

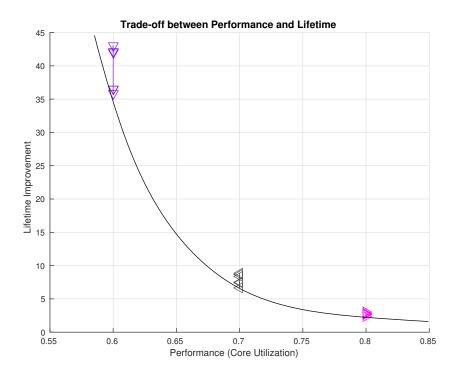

| 3.7        | tasks per one task set under different core utilizations (0.3 to 0.8 in x-axis)  Trade-off between lifetime and performance (each triangle is different set of                                                                                                                                                        | 90       |

|            | core utilization)                                                                                                                                                                                                                                                                                                     | 55       |

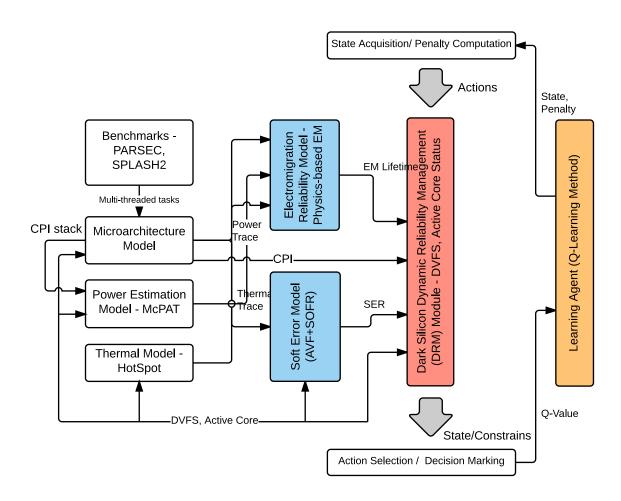

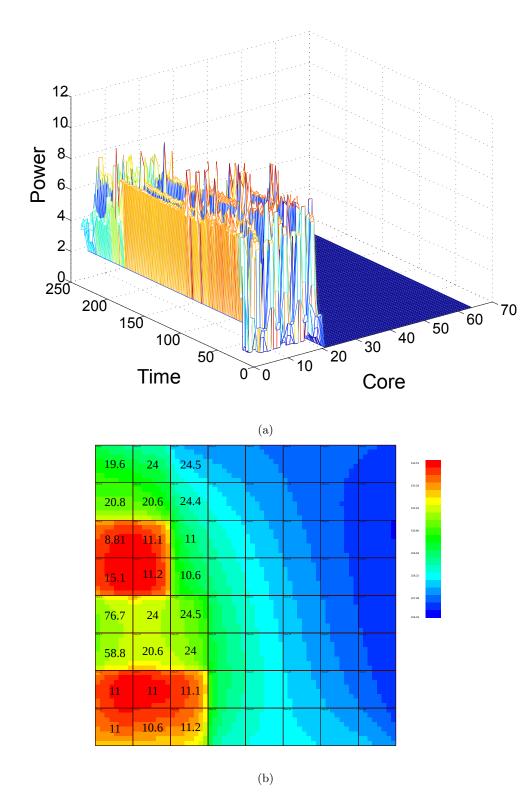

| 4.1<br>4.2 | Q-Learning model with reliability-aware dark silicon framework (a) SPLASH2 benchmark 64 multithreaded tasks power traces with 44 cores off(b) Thermal (color:degree) and EM lifetime (number:yrs) analysis on 64                                                                                                      | 65       |

| 4.3        | cores                                                                                                                                                                                                                                                                                                                 | 73<br>79 |

|            | set                                                                                                                                                                                                                                                                                                                   | - 19     |

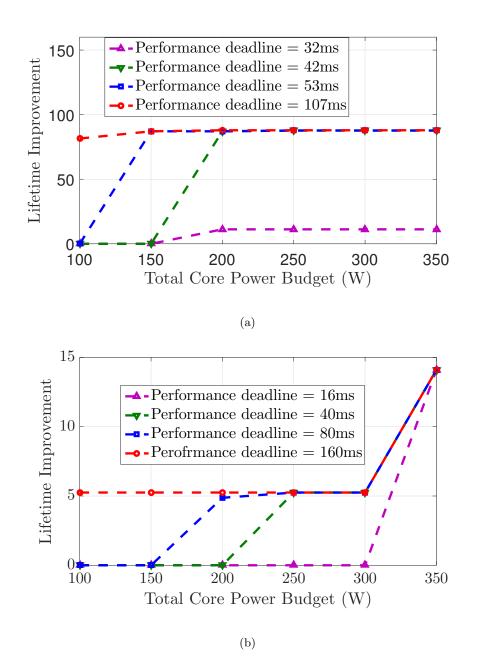

| 4.4  | Q-learning result for performance deadline from (a,b) PARSEC tasks and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | light (c,d) SPLASH-2 tasks in 64-core dark silicon chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80  |

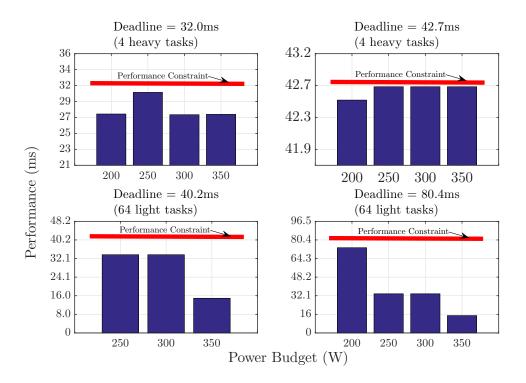

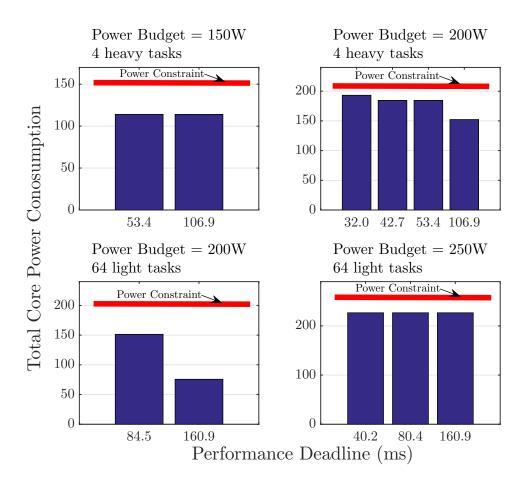

| 4.5  | Q-learning result for power constraints from heavy 4 PARSEC tasks and light                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | 64 SPLASH-2 tasks in 64-core dark silicon chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81  |

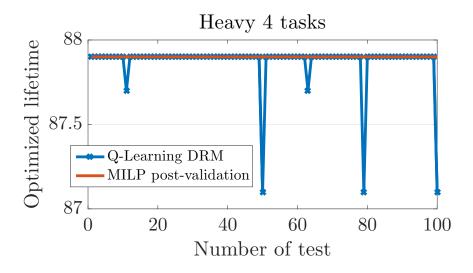

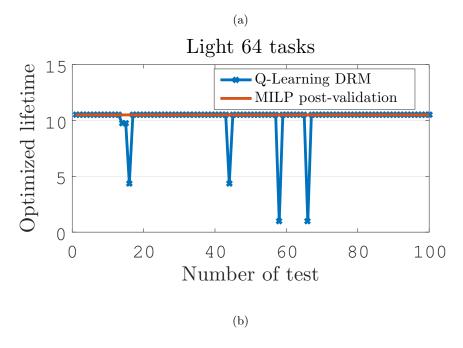

| 4.6  | Post-validation with MILP for Q-learning accuracy (a) 4 heavy task PARSEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | workloads (b) 64 light tasks SPLASH-2 workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82  |

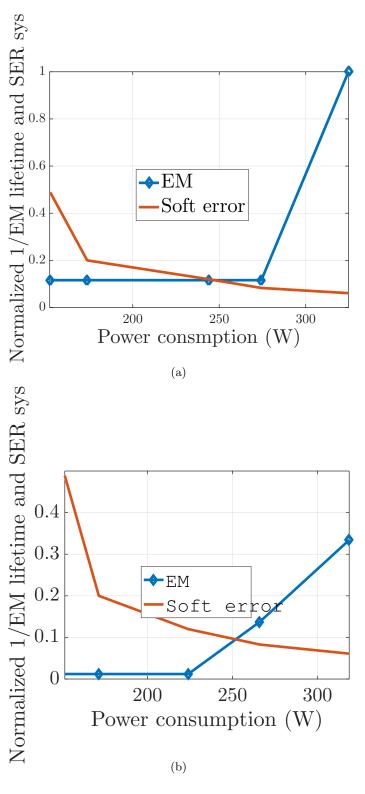

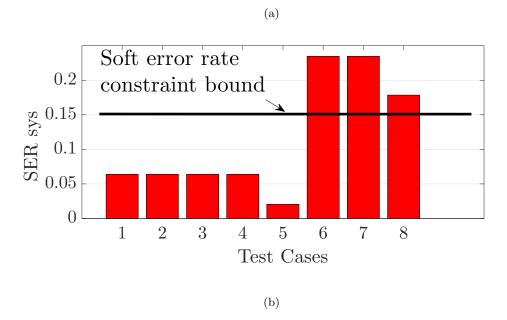

| 4.7  | Comparison between EM-induced lifetime and system-level soft error rate at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | different powers (by different DVFS configurations) on (a) PARSEC small                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | tasks and (b) SPLASH-2 tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84  |

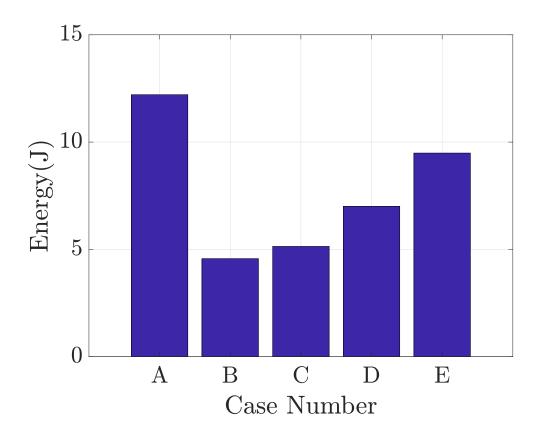

| 4.8  | Impact of different process technologies on system-level soft error rate, from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | left bar, case A) Global DVFS, case B) our proposed DRM with only EM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | constraint, our proposed DRMs with both EM and SER constraints of case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | C) 45nm, case D) 32nm, and case E) 22nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85  |

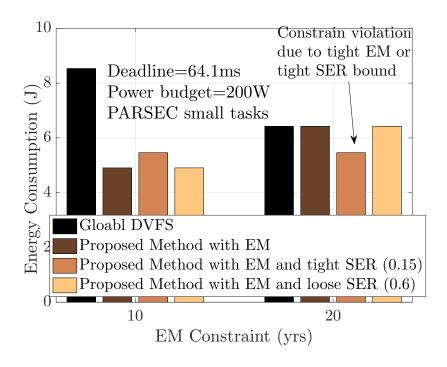

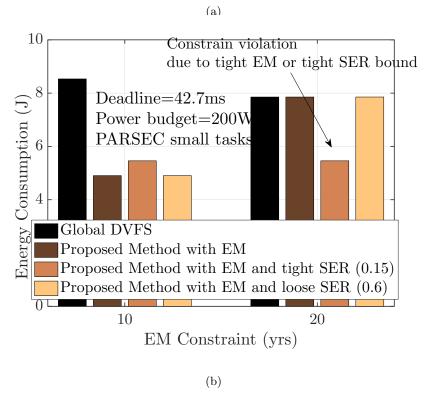

| 4.9  | Energy optimization results (Global DVFS, proposed with EM, and with/without the proposed with E | ıt  |

|      | tight and loose soft error constraint from small task set on PARSEC bench-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7 |

| 4.10 | marks (different performance deadlines in (a) and (b))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87  |

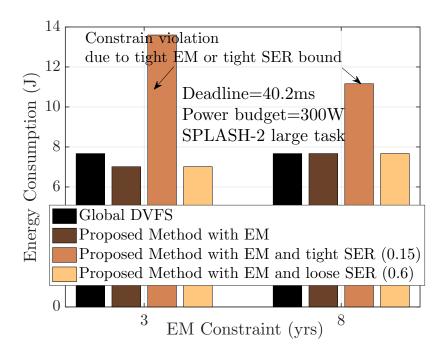

| 4.10 | Energy optimization results (Global DVFS, proposed with EM, and with/without it is a first of the control of th | 1t  |

|      | tight and loose soft error constraint from large task set on SPLASH-2 bench-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00  |

| 111  | marks (different power budgets in (a) and (b) )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88  |

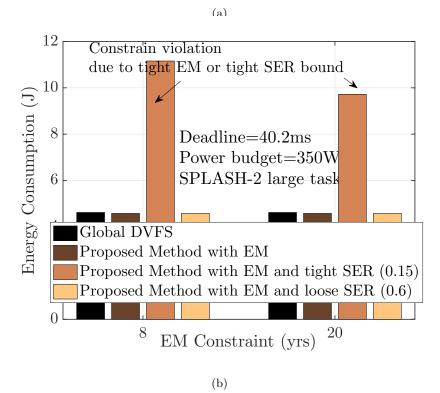

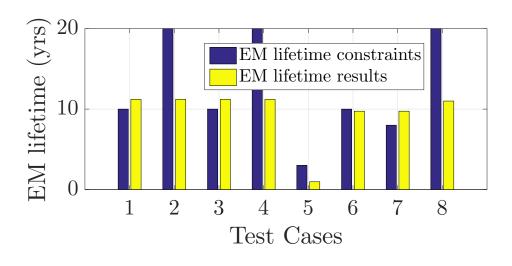

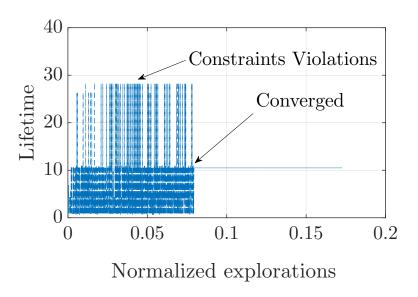

|      | Constraint violation cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90  |

| 4.12 | Convergence rate of proposed DRM method with EM-induced lifetime constraint in 64-core Dark Silicon (SPLASH-2 Tasks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91  |

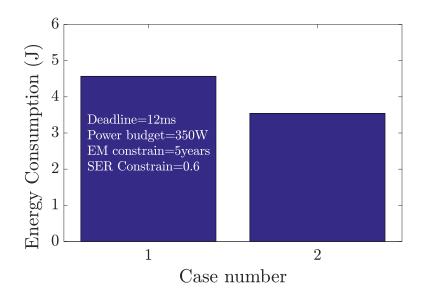

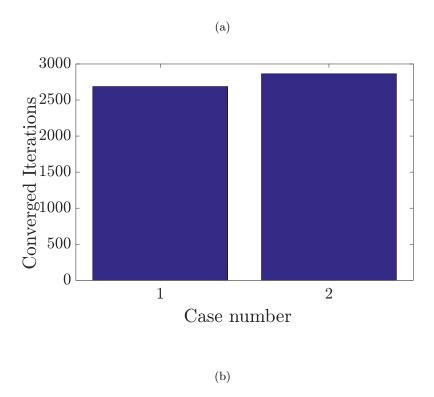

| 4.13 | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |

| 4.10 | with dark silicon, case 2: three p-states with dark silicon (b) Total average                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | iteration number for both two cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93  |

|      | iteration number for both two cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55  |

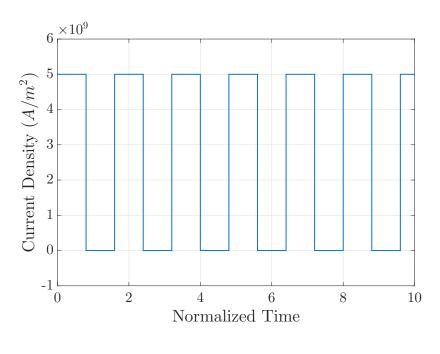

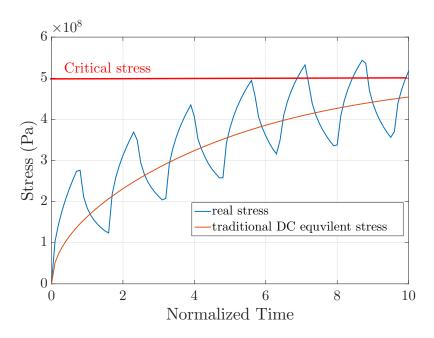

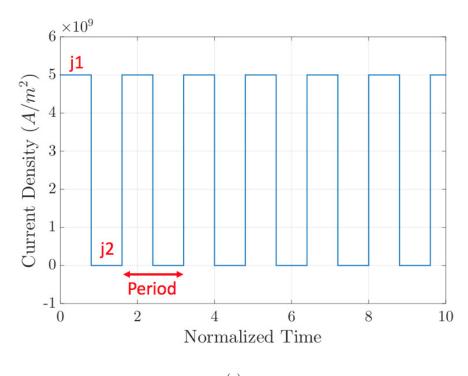

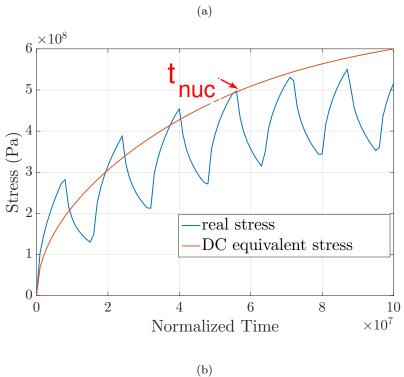

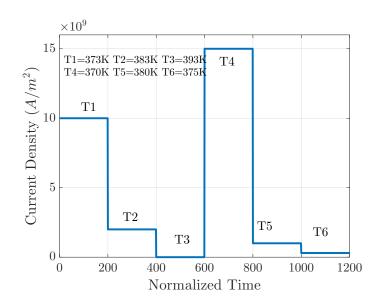

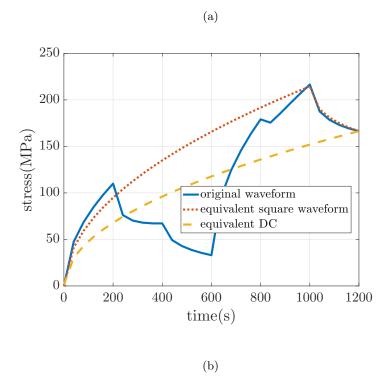

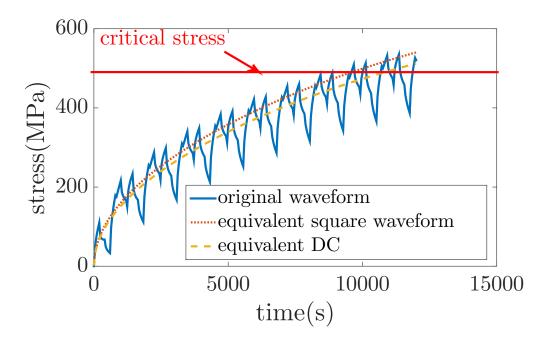

| 5.1  | Stress evolution caused by periodical current density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98  |

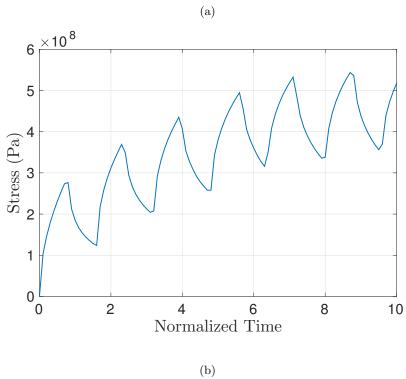

| 5.2  | Stress evolutions caused by actual currents and traditional effective DC current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99  |