#### **UC Irvine**

#### **ICS Technical Reports**

#### **Title**

Design process and human interface for a behavioral-synthesis environment

#### **Permalink**

https://escholarship.org/uc/item/9nm7k2m5

#### **Authors**

Gajski, Daniel D. Hadley, Tedd Chaiyakul, Viraphol et al.

#### **Publication Date**

1993-01-25

Peer reviewed

### Design Process and Human Interface for a Behavioral-Synthesis Environment

Daniel D. Gajski, Tedd Hadley, Viraphol Chaiyakul, Tadatoshi Ishii

> Technical Report 93-7 January 25, 1993

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

Dept. of Information and Computer Science University of California, Irvine Irvine, CA 92717 (714) 856-8059

Email: hadley@ics.uci.edu, viraphol@ics.uci.edu

#### Abstract

This report contains transparencies of a presentation on the design process in the University of California Irvine's Behavioral-Synthesis Environment. The human-interface aspects of the environment are discussed in detail and several design-process examples are given to demonstrate the power and usefulness of this environment for behavioral synthesis.

# Contents

| 1     | Int  | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | 1.1  | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  |

|       | 1.2  | Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |

|       | 1.3  | The Decision Support Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0  |

| 2     | De   | E Displace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 4     |      | E Displays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7  |

|       | 2.1  | The State-Actions Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|       | 2.2  | The State-Actions Table: An Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|       | 2.3  | Component Selection and Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

|       | 2.4  | The Connectivity Table and Floorplan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13 |

| 3     | Dis  | plays for State-Based Quality-Measures and Statistics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| teris |      | THE CONTRACTOR OF THE CONTRACT | 15 |

| hat   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| MIC   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

| 7 0   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

| 1.0   | 3.4  | Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21 |

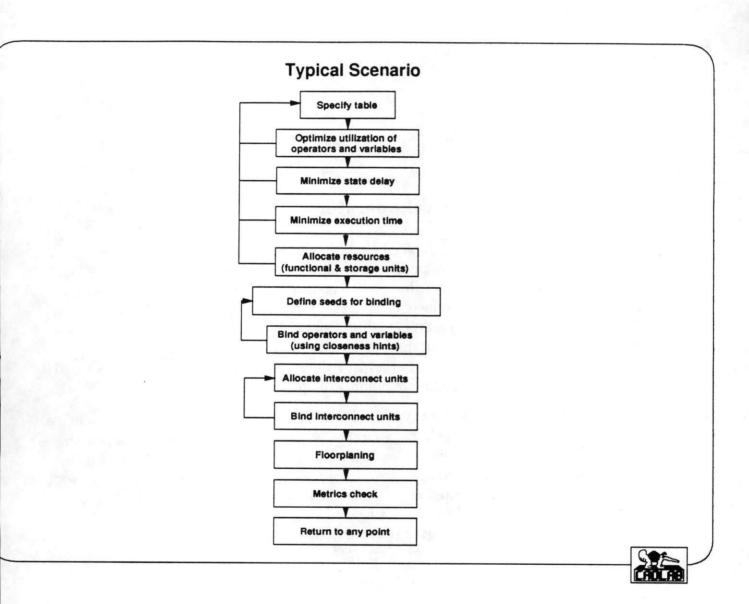

| 4     | Use  | r Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 |

|       | 4.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 |

|       | 4.2  | Reducing behavioral operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|       | 4.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|       |      | Reducing behavioral variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

|       | 4.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

|       | 4.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

|       | 4.7  | Selection of implementation style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

|       | 4.8  | Selection of bitwidth for allocated components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37 |

|       | 4.9  | Binding of functional and storage units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

|       | 4.10 | Allocating and binding of interconnect units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 |

|       | 4.11 | Final floorplanning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13 |

| 5 | Conclusion |  | 15 |

|---|------------|--|----|

|   |            |  | 45 |

|   |            |  |    |

| • | D 6        |  |    |

| 0 | References |  | 47 |

|   |            |  |    |

#### 1 Introduction

This presentation describes a decision support environment (DSE) for behavioral synthesis.

#### 1.1 Motivation

Two observations motivate the need for a decision support environment for behavioral synthesis:

- 1. Complete automation of the design process through every level of abstraction is not an immediately practical goal.

- 2. The human designer's insights into design strategy should be used to maximum effect in all phases of behavioral synthesis.

The first point is a conclusion derived more from the lack of observable uses of automated behavioral synthesis systems in commercial domains, rather than from the lack of existing systems in research and academia. Although it certainly can not be denied that progress has been considerable in this research area [Sh89] [DeRa86] [BrCa88], a practical solution to the problem of automating behavioral synthesis is still distant [CaWo91]. To develop a feasible approach to the problem, we have substituted the goal of a completely automated, "push-button" synthesis system with one which attempts to maximally utilize the human designer's methods and experience.

# Decision Support Environment Motivation

- Complete automation of the design process through every level of abstraction is not an immediately practical goal.

- The designer's insights into design strategy should be used to maximum effect in all phases of behavioral synthesis.

#### 1.2 Goals

There are two primary goals in the development of our environment for decision support in behavioral synthesis:

- 1. To allow user decisions and user control in every task of the design process. These tasks are but not limited to unit selection: the proper hardware components are selected from a library; scheduling: the behavior is divided into timesteps according to resources and timing constraints; binding: behavioral operators and variables are bound to physical components; and floorplanning: layout and routing techniques are performed on the physical design representation ([GDWL92]).

- 2. To provide rapid feedback of useable physical design characteristics and quality measures to every level of design abstraction. Area and delay quality measures tell the designer whether or not the design meets space and time constraints. Critical path estimation reduces design development time by focusing the designer's attention on critical performance areas. Clock period estimation is used in a variety of ways to provide the designer with the necessary information for decisions in scheduling, binding, and floorplanning.

Decisions made by the user should generate immediate feedback as to the quality and functionality of the resulting design. As the design process progresses to more detailed and less abstract descriptions, the designer's experience must be utilized to make the kinds of decisions no automated tool can perceive or predict.

#### **Decision Support Environment** Goals

- 1. To allow user decisions and user control throughout every phase of the design process.

- Unit selection

- Scheduling

- BindingFloorplanning

- 2. To provide rapid feedback of useable design characteristics and quality measures to the user at every level of design abstraction.

- Area

- DelayCritical pathClock period

### 1.3 The Decision Support Environment

The DSE supports three basic levels of interaction:

- 1. Graphical design capture, whereby the designer enters and/or modifies the desired behavior or structure with the aid of multiple design views,

- 2. Feedback of quality measures and design hints automatically derived by the system from the current design

- 3. The ability to incorporate automatic synthesis tools into the design process so that tedious, well-understood problems can be rapidly solved by automatic algorithms

# A Decision Support Environment for Behavioral Synthesis

- 1. Graphical design capture

- 2. Quality measures and hints

- 3. Combined interactive and automatic synthesis

#### 2 DSE Displays

#### 2.1 The State-Actions Table

The state-actions table displays the behavior and schedule of the design in a tabular format. A general definition of each column in the table follows (A more detailed description of the state-actions table can be found in [HaCG93]):

- 1. PS is the present state.

- 2. SCOND gives the condition for a next-state transition.

- 3. NS is the next state. The condition may be any valid expression resulting in a boolean result. The condition may be any valid expression resulting in a boolean value.

- 4. ACOND shows the assignment condition for each action. The condition may be any valid expression resulting in a boolean value.

- 5. ACTIONS lists all operations in the behavior.

- 6. ORDER gives a level ordering of the actions within a given state and may be used by the user to explicitly indicate a dependency between actions.

- 7. CV lists the condition vector under which the results of the action will be used.

- 8. The AC # field assigns numbers to actions and is needed to make actions easier to reference in other fields.

- 9. DEPENDENCY (INP DEP/OUT DEP) field describes global dependencies among actions in terms of the numbers given in the AC # field. Numbers to the left of the / list the input dependencies (writes) of the operands in the corresponding action. Numbers to the right of the / list the output dependencies (reads) of the action's output variable.

The PS, SCOND, NS, ACOND, ACTIONS, and ORDER fields are user-specified through use of the menus shown below the table. The remaining fields are automatically derived by the system once the behavior is complete. The QM/stats field represents different quality measures, statics, and metrics that will be described in more detail later on.

The state-actions graphical display is user-configurable in two ways.

- 1. Any column may be turned off at the user's discretion; for example, if screen-space limitations are a concern.

- 2. Any column may be interchanged with any other column

### State-Actions Table

### User Input

### System Derived

| PS  | SCOND     | NS   | ACOND       | ACTIONS       | ORDER | CV                  | AC# | INP DEP/OUT DEP | QM/stats                               |

|-----|-----------|------|-------------|---------------|-------|---------------------|-----|-----------------|----------------------------------------|

| 1   | 7         | 2    | T           | Z1 = b - 2    | 0     | (b==2)(!(b==2) & C2 | 1   | / 3,4           | TIMITIMI -                             |

| 25  | 25.0      | _    | Т           | F = D*E+E     | 0     | T                   | 2   | 1               | 1111111111                             |

| 2 Т | Section 1 | 1189 | (b==2)      | X = Y + Z1    | 0     | (b==2)              | 3   | 1 /             | 1///////////////////////////////////// |

|     | 1 1       |      | Т           | Z2 = Y - Z1   | 0     | !(b==2)             | 4   | 1 / 6           | 1                                      |

|     | T         | 1    | T           | C2 = (b == 1) | 0     | !(b==2)             | 5   | ,               | 111111111111111111                     |

|     | 1 1       |      | !(b==2)&C2  | X = Y * Z2    | 1     | T                   | 6   | 4 /             | 1                                      |

|     |           |      | !(b==2)&!C2 | X = 0         | 1     | T                   | 7   | 1               | 1111111111111111                       |

|              | PS | SCOND | NS |

|--------------|----|-------|----|

|              | 1  | т     | 2  |

| dd state     | 7  |       |    |

| Delete state | 1. | -     | 2  |

| Modify state | 2  | '     | 1  |

| Move state   |    |       |    |

|               | ACOND       | ACTIONS       |

|---------------|-------------|---------------|

|               | T           | Z1 = b - 2    |

|               |             | F = D*E+E     |

| Add Action    | (b==2)      | X = Y + Z1    |

| Delete Action |             | Z2 = Y - Z1   |

|               | T           | C2 = (b == 1) |

| Modify Action | !(b==2)&C2  | X = Y * Z2    |

| Move Action   | !(b==2)&!C2 | X = 0         |

### 2.2 The State-Actions Table: An Example

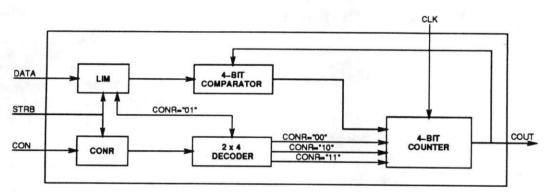

To get a feeling for how a behavioral description is specified in the state-actions table, let us look at a description of Armstrong's controlled counter. This is a 4-bit counter that consists of five main logic blocks: a 2-bit control register (CONR), a decoder, a 4-bit limit register (LIM), a 4-bit comparator, and a 4-bit counter (CNT). On the rising edge of the STRB signal, the counter stores the 2-bit control input signal CON. It then performs the following operations based on the value of the control signal:

- 1. Clear the counter (CON = "00").

- 2. Load inputs from the DATA signals into the LIM register on the falling edge of the STRB signal (CON = 01).

- 3. Increment the count on the rising edge of the CLK signal (CON = "10").

- 4. Decrement the count on the rising edge of the CLK signal (CON = "11").

The behavior of the controlled counter consists of both synchronous and asynchronous parts. The latching of storage units in the synchronous part is performed during the rising edge of the CLK signal. The asynchronous part is performed on the rising and falling edges of the STRB signal.

The first action in the state-table specifies the latching of the control input CON into a 2-bit control register CONR on the rising edge of the STRB signal. Since CONR is clocked with the STRB signal instead of the CLK signal, CONR acts as the asynchronous part of the design.

The second action specifies that whenever the value of CONR is "00", CNT should be cleared. Since there is no information about synchronization in the specification, CNT is cleared asynchronously.

The third action specifies the behavior of the counter when CONR is "01". Since LIM is also asynchronous, DATA is assigned to LIM without CLK in the assignment condition. Instead, the value is latched into LIM on the falling edge of the STRB signal.

The fourth action specifies the behavior of the counter when CONR is "10". The counter counts up by incrementing the value of CNT on the rising edge of the CLK signal. The increment is performed only if the limit LIM is not reached.

The fifth action specifies the behavior of the counter when CONR equals "11". The counter counts down by decrementing the value of CNT on the rising edge of the CLK signal. The decrement is performed only if the limit LIM is not reached.

The last action specifies the output of the counter COUT. The value of CNT is used for this output.

## Example: 4-bit Controlled counter (Armstrong)

| PS  | SCOND | NS                                       | ACOND                                     | ACTIONS            | ORDER                        |            |   |

|-----|-------|------------------------------------------|-------------------------------------------|--------------------|------------------------------|------------|---|

|     |       |                                          | STRB'rising                               | CONR = CON         | 0                            |            |   |

|     |       | CONR = "00"                              | CNT = "0000"                              | 0                  |                              |            |   |

| ST1 |       |                                          |                                           |                    | STRB'falling and CONR = "01" | LIM = DATA | 0 |

| 311 |       | CLK'rising and CONR = "10 and CNT I= LIM |                                           |                    | CNT = CNT + "0001"           | 0          |   |

|     | 1 1   |                                          | CLK'rising and CONR = "11" and CNT  = LIM | CNT = CNT - "0001" | 0                            |            |   |

|     |       |                                          | Т                                         | COUT = CNT         | 0                            |            |   |

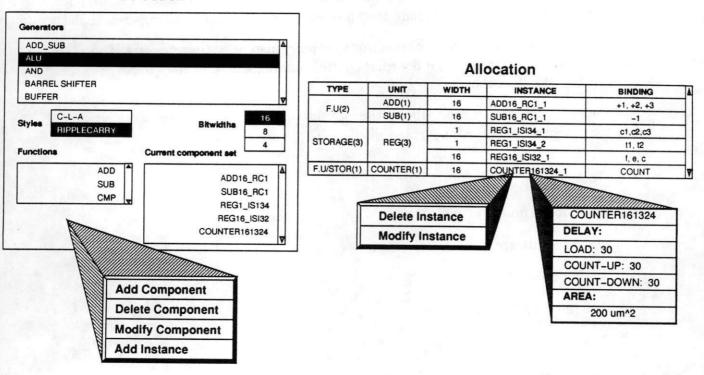

### 2.3 Component Selection and Allocation

The component selection and allocation display allows the designer to select components from a component library and add instances of those to the current design's component set. The **Selection** window lists the available component categories and the kinds and ranges of the parameters for each component. The designer must select parameters values, such as bitwidth, style and/or kinds of functions performed, in order to specify a unique component type. The **Current component set** window lists all component types currently in use in the design.

The allocation window lists all component instances physically present in the target design. Each instance is broken down into categories (type, unit, width), and the number of instances in each category is displayed in parentheses. Each instance may also be selected to display the list of function performed, pin-to-pin delay, and area information.

### **Component Selection and Allocation**

#### Selection

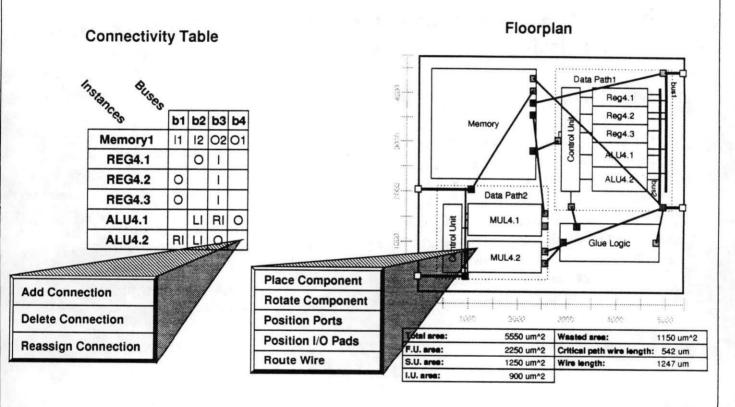

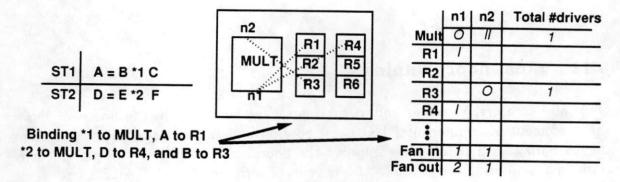

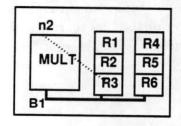

### 2.4 The Connectivity Table and Floorplan

The connectivity table lists component instances along the Y axis and buses (interconnections) along the X axis. A connection between an instance and a bus exists if an instance's input or output port is present in the corresponding entry. The user may add, delete, or reassign connections in order to optimize the number of interconnections needed.

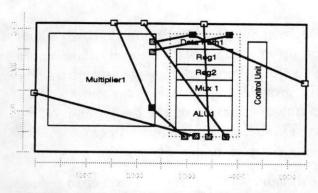

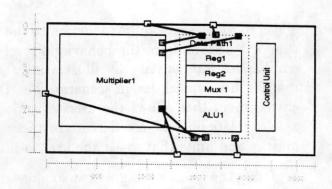

The floorplan display shows the floorplan of the target design. When an instance is allocated, its layout is positioned randomly within the display initially. Afterwards, the user may reposition the instance anywhere in the design within design rule limits. Rotating an instance's layout in 90 degree increments is also permitted. The user may also relocate external i/o pads along the chip boundary to reduce routing area or delay.

During the binding process, connections between instances are represented as point-to-point connections within the floorplan. After binding, the user may route or reroute wires within the floorplan.

A set of quality measures about the physical design are constantly updated and shown at the bottom of the floorplan display. These are

- 1. Total area

- 2. Functional unit area

- 3. Storage unit area

- 4. Interconnect unit area

- 5. Wasted area (white space)

- 6. The length of the critical path

- 7. Total wire length

The four displays described, the state-actions table, the component selection and allocation display, the connectivity table, and the floorplan display, are integrated tightly together such that actions or highlighting in one display is reflected (if relevant) in the others. For example, if the critical state is highlighted in the state-actions table (next slide), the floorplan display will highlight the components and connections involved.

The next section describes the state-based quality-measures and statistics available to the designer from the state-actions display.

### Connectivity Table and Floorplan

### 3 Displays for State-Based Quality-Measures and Statistics

#### 3.1 Delay

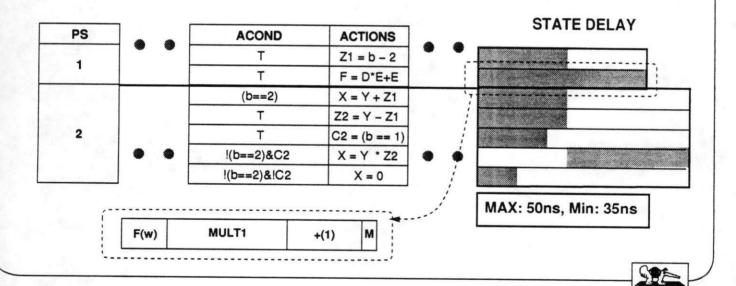

The DELAY menu causes a bar graph to be displayed alongside the state table showing information about state delay. Delay is represented graphically along the X axis, and delay statistics are shown below the graph. The thick-lined outer boxes show the maximum delay of each state. Within each box, the delay is further broken down by actions. For example, in state 1 the action F=D\*E+E is the longest path, so the width of its shaded box extends the length of the thick-lined state-delay box. Each action can also be further broken down by operator and operand delays if the user requests. For example, the same action is shown at the bottom of the slide with the delay for writing F, the delay of the multiply operation, and the delay of the addition shown.

### State-Based Quality-Measures and Statistics

#### 3.2 Occurrence

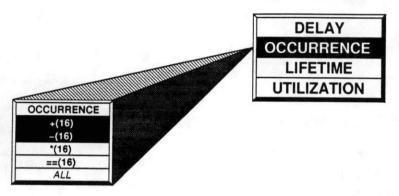

The OCCURRENCE menu lists operators along with their bitwidths and allows the user to select any subset to be displayed graphically. The slide shows the bar graph resulting from selecting "+(16)" (all occurrences of a 16-bit + operation) and -(16) (all occurrences of a 16-bit "-" operation).

## State-Based Quality-Measures and Statistics

|    |     |               |               |   |   | OCCURRENCE      |

|----|-----|---------------|---------------|---|---|-----------------|

| PS |     | ACOND         | ACTIONS       | _ | _ | +(16) and -(16) |

|    |     | Т             | Z1 = b - 2    | • | • |                 |

|    |     | Т             | F = D+E+E     |   |   |                 |

|    |     | (b==2)        | X = Y + Z1    |   |   |                 |

|    |     | T Z2 = Y - Z1 |               |   |   |                 |

| 2  |     | Т             | C2 = (b == 1) |   |   |                 |

|    | • • | !(b==2)&C2    | X = Y * Z2    | • | • |                 |

|    |     | !(b==2)&!C2   | X = 0         |   |   |                 |

|    |     |               |               |   |   | MAX: 3          |

#### 3.3 Lifetime

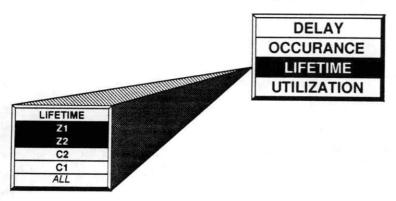

The LIFETIME menu lists the variables used in the behavior. The user may select a subset of these in order to display a lifetime graph, as shown at the bottom of the slide. The lifetime of a variable is defined as all states in which the variable holds a useful value. The final state in which a variable is read is not included in the set of states making up its lifetime. The graph is further annotated to indicate the actions where the variable is read (R) or written (W).

### State-Based Quality-Measures and Statistics