# UCLA UCLA Electronic Theses and Dissertations

### Title

Developing Through-Wafer Via (TWV) and Plasma Dicing Process for Silicon Interconnect Fabric (Si-IF)

### Permalink

https://escholarship.org/uc/item/9j90p352

## Author

Luo, Yandong

# Publication Date 2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Developing Through-Wafer Via (TWV) and Plasma Dicing Process for Silicon

Interconnect Fabric (Si-IF)

A thesis submitted in partial satisfaction

of the requirements for the degree Master of Science

in Electrical Engineering

by

Yandong Luo

© Copyright by

Yandong Luo

2018

#### ABSTRACT OF THE THESIS

# Developing Through-Wafer Via (TWV) and Plasma Dicing Process for Silicon Interconnect Fabric (Si-IF)

by

#### Yandong Luo

Master of Science in Electrical Engineering University of California, Los Angeles, 2018 Professor Subramanian Srikantes Iyer, Chair

In this thesis, the through-wafer via (TWV) technology is developed for signal and power delivery on silicon interconnect fabric (Si-IF). The electrical performance of through-wafer via is simulated by ANSYS HFSS with different design parameters. Low insertion loss is obtained when it is operating at the low-frequency range (<1GHz). The electrical reliability issues such as electromigration are examined and verified. The thermal reliability issues related to TWV during Si-IF fabrication are analyzed by simulation. It is observed that interfacial delamination can be induced at the interface between Cu via and SiO<sub>2</sub> liner due to the CTE mismatch between the materials. The TWV is fabricated in UCLA Nanolab on a 300µm thick wafer. Plasma dicing technology is also developed based on deep silicon etch to obtain smooth die edge after dicing, which enables compact die assembly on Si-IF. The thesis of Yandong Luo is approved.

Chandra J Joshi

Mark S Goorsky

Subramanian Srikantes Iyer, Committee Chair

University of California, Los Angeles

2018

## TABLE OF CONTENTS

| 1. Introduction1                                                    |

|---------------------------------------------------------------------|

| 1.1 The Demand for New Packaging Technology1                        |

| 1.2 Si Interconnect Fabric (Si-IF) Technology2                      |

| 1. 3 Contribution of this Work                                      |

| 1.4 Organization of this Thesis5                                    |

| 2. The Design and Electrical Simulation of Through-Wafer Vias (TWV) |

| 2.1. Transmission Property of TWV                                   |

| 2.2 Transmission Property of a Signal Path13                        |

| 3. Through-Wafer Vias for Power Delivery                            |

| 3.1 Simulation Model16                                              |

| 3.2 Modeling of Current Crowding Effect17                           |

| 3.3 Current Uniformity Analysis                                     |

| 3.4 IR Drops in Power Link                                          |

| 4. Thermo-mechanical Reliability Analysis                           |

| 4.1 Simulation Model                                                |

| 4.2 Results and Discussion                                          |

| 5. Experiment Demonstration of Through-Wafer Vias                   |

| 5.1 Fabrication Process of TWV                                      |

|    | 5.2 Via Etch by Bosch Process                          | 27 |

|----|--------------------------------------------------------|----|

|    | 5.3 Via Profile Characterization                       | 29 |

| 6. | Plasma Dicing for Si-IF                                | 34 |

|    | 6.1 Dicing Technology Requirement for Si-IF            | 34 |

|    | 6.2 Challenges in State-of-the-art Dicing Technologies | 35 |

|    | 6.3 Plasma Dicing Process                              | 36 |

|    | 6.4 Profile Characterization                           | 37 |

|    | 6.5 Throughput Benefits of Plasma Dicing               | 38 |

| 7. | Conclusions and Future Work                            | 40 |

| Re | FERENCES                                               | 41 |

### **List of FIGURES**

| 1.1 The interconnect scheme on PCB (top) and on Si-IF (bottom)4                                            |

|------------------------------------------------------------------------------------------------------------|

| 2.1 The TWVs in silicon interconnect fabric (Si-IF)7                                                       |

| 2.2 The cross-section of the cylindrical TWV (b) the cross-section of the coaxial                          |

| TWV                                                                                                        |

| 2.3 The insertion loss of cylindrical TWV and coaxial TWV10                                                |

| 2.4 Insertion loss S21 vs. TWV pitch                                                                       |

| $2.5 S_{21} vs.$ the thickness of the SiO <sub>2</sub> liner                                               |

| 2.6 S <sub>21</sub> vs. TWV diameter                                                                       |

| 2.7 A data link with TWV (left) Two interconnect scheme between the Cu wires                               |

| and TWV (right)                                                                                            |

| 2.8 The simulation model of a data link with TWV in ANSYS HFSS14                                           |

| 2.9 The insertion loss $S_{21}$ for a data link with TWV15                                                 |

| 3.1 Three interconnect schemes between the power TWV and wiring levels17                                   |

| 3.2 The current density distribution at the via/wire interface                                             |

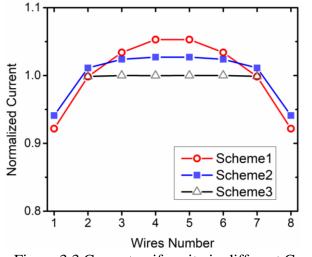

| 3.3 Current uniformity in different Cu wires                                                               |

| 3.4 IR drop vs the length of wires                                                                         |

| 4.1 Thermal load applied to TWVs during the fabrication of Cu wiring levels21                              |

| 4.2 The cross-section view of the simulation model                                                         |

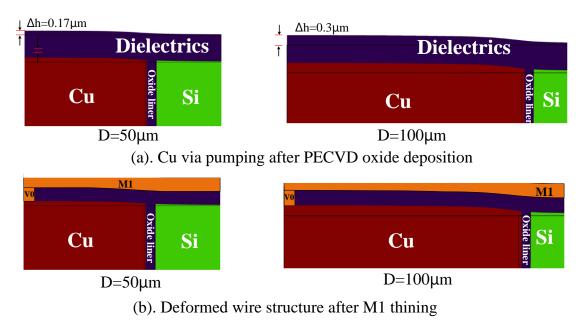

| 4.3 (a). Cu via extrusion after PECVD oxide deposition. (b) The deformed wire                              |

| after planarization by CMP24                                                                               |

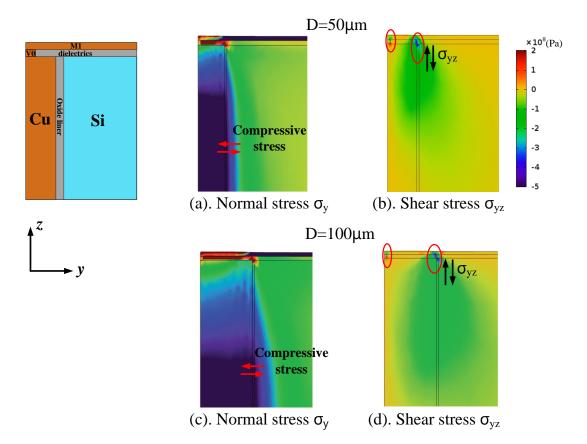

| 4.4(a) The normal stress $\sigma_y$ (b) the shear stress $\sigma_{yz}$ for vias with a 50 $\mu$ m diameter |

| (c) The normal stress $\sigma_y$ (d) the shear stress $\sigma_{yz}$ for vias with a 100 $\mu m$ diameter. |

|-----------------------------------------------------------------------------------------------------------|

| The temperature in the simulation is 300°C25                                                              |

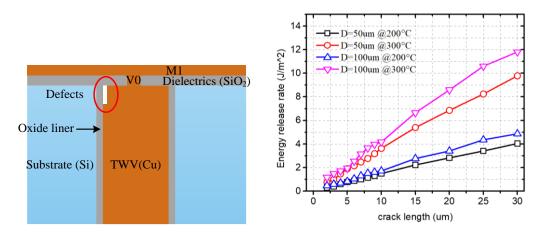

| 4.5 (a) the model to calculate ERR (b) The simulated ERR vs crack length26                                |

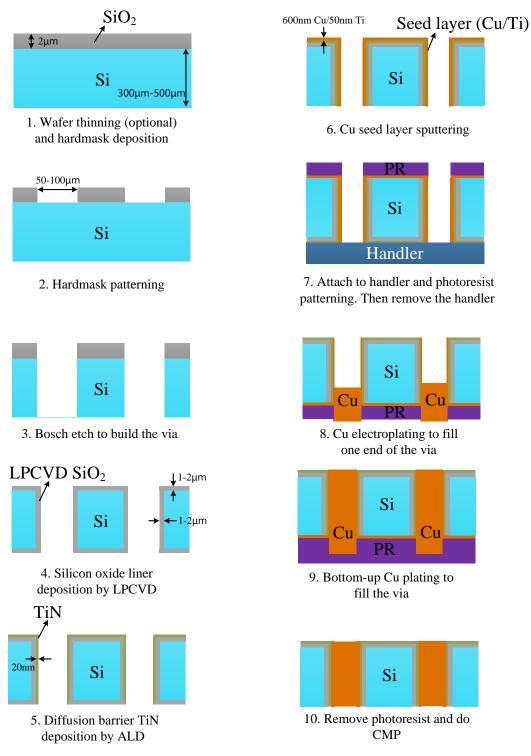

| 5.1 The fabrication process of TWV                                                                        |

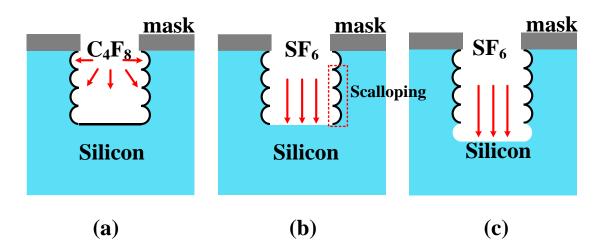

| 5.2 the three phases of a Bosch etch cycle (a) polymerization (b) polymer etch (c)                        |

| silicon etch                                                                                              |

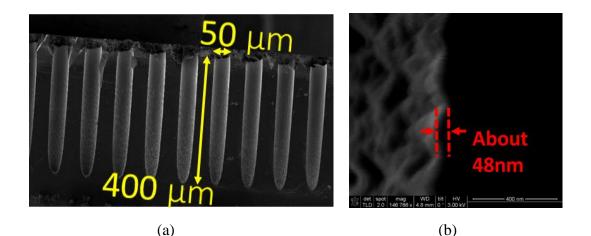

| 5.3 (a) The cross-section view of 50 $\mu$ m diameter TWV under SEM after 100min                          |

| Bosch etch (b) A zoom-in picture of the sidewall                                                          |

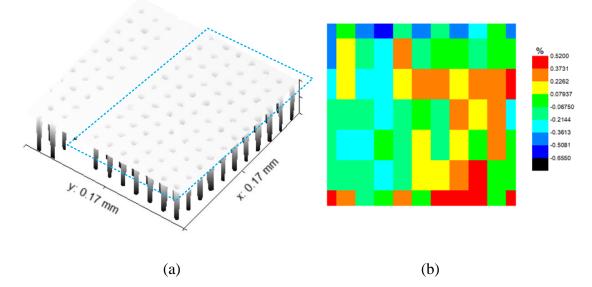

| 5.4 (a) the via profile under an optical profiler. (b) The etch rate of different vias in                 |

| the dash line box in Fig.(a)                                                                              |

| 5.5 (a) top view of the vias after 3h plating. (b). the cross-section image of the vias                   |

| (c) the profile of the sidewall in the blue dash line region in Fig (b)                                   |

| 6.1 The data link between two dies with smooth and rough die edges                                        |

| 6.2 The process flow of plasma dicing (dummy dicing)                                                      |

| 6.3 the dicing street of the die after plasma dicing                                                      |

| 6.4 A comparison of the time consumption for 300mm Si wafer singulation with                              |

| plasma dicing (PD), saw dicing and laser dicing                                                           |

### LIST of TABLES

| 2.1 Parameters for TWV Electrical Simulation              | 9  |

|-----------------------------------------------------------|----|

| 2.2 Parameters for Electrical Simulation                  | 14 |

| 4.1 Materials Parameters in Thermal Mechanical Simulation | 22 |

| 4.2 Hardening Function of Copper                          | 23 |

### Acknowledgments

I would like to thank my advisor Prof. Subramanian Iyer for his guidance and support in this research project. I would like to thank Prof. Chandrashekhar Joshi and Prof. Mark Goorsky for being on my thesis committee. I thank Dr. Zhe Wan, Dr. Amir Hanna, Dr. Arsalan Alam, Dr. Siva Chandra Jangam, Dr. Goutham Ezhilarasu and Dr. Boris Vaisband for their help in fabrication and useful discussions. I thank all my colleagues from CHIPS for their help. I thank UCLA Nanolab for their support in sample fabrication.

At last, I would like to thank my parents for their constant support and help.

# **CHAPTER 1**

# Introduction

#### 1.1 The Demand for New Packaging Technology

Nowadays, device scaling is slowing down due to the high cost of development and manufacturing **[1]**. New approaches to continue system scaling and improve computing performance have become the focus of research.

New packaging technology is a potential candidate for system scaling and performance improvement. First, packaging scaling lags far behind that of device level scaling. In fact, packaging size has only been scaled by 5 times over the past 50 years while the transistor size has been scaled down by over 1000 times [2]. Besides, present packaging technology is limiting the system performance.

In a packaging system, interconnect between packaged dies, laminate and PCB is typically achieved by solder-based interconnect, such as micro bumps, C4 bumps (about 100µm pitch) and BGA (about 400µm pitch) [3]. It is challenging to scale down the pitch of the bumps due to solder protrusions and substrate warpage. Large interconnect pitch limits the number of I/O ports and thus the chip bandwidth. To meet the increasing demand for high chip bandwidth, serial links with high operating frequency are applied for inter-chip communication. It leads to high power consumption and complexity in the design of serialization and deserialization (SerDes) circuit [4]. To accommodate more I/O ports, the chip-level packaging is enlarged.

However, the die space is increased with larger packaging size, which leads to a longer data link and higher communication latency.

System on chip (SoC) technology can shorten the length of the data links by fabricating all functional modules into a single die. However, increasing complexity in design flow and low yield are two issues for large-scale SoC systems. Besides, heterogeneous integration is not applicable in SoC systems.

3D integration technology has been proposed to improve the system performance **[5]**, **[6]**. However, the relatively high cost and the thermal management issues can limit its application.

#### 1.2 Si Interconnect Fabric (Si-IF) Technology

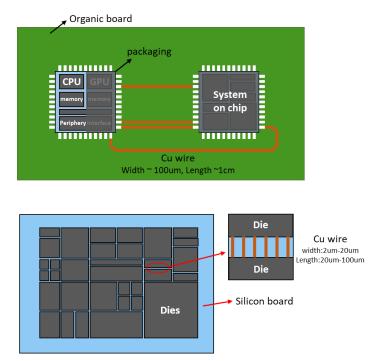

As discussed above, the two significant drawbacks of present packaging technology are the limited number of I/O ports and long data link. To solve these problems, a novel system level packaging scheme—silicon interconnect fabric (Si-IF) technology is proposed **[2],[3], [7],[8]**. Figure 1.1 shows the interconnect scheme on Si-IF and PCB. The basic idea of Si-IF is to build fine-pitch interconnect levels (<10µm pitch) on a silicon board for inter-die communication. The silicon dies are diced by plasma dicing and then bare dies are bonded onto Si-IF by thermal compression bonding (TCB) **[7]**. The key technological features of Si-IF are listed as below.

- Fine-pitch interconnect built on silicon board (<10µm pitch).

- The elimination of die-level packaging and compact die assembly.

- Thermal compression bonding to enable heterogeneous integration scheme.

Through-wafer vias (TWVs) on full thickness Si wafer for signal and power delivery.

These features of Si-IF eliminate the drawbacks of current packaging system and improve the overall system performance. By using fine pitch interconnect, more I/O ports can be placed at the die edge and parallel data transfer is enabled for inter-die communication, which improves the chip bandwidth with less power consumption. By removing die-level packaging, die space is reduced by compact die assembly on the Si-IF, resulting in shorter data link length (50-500µm) compared with that on PCB (typically a few centimeters). The shortened data link leads to lower data latency and the elimination of transceivers and transmitters in data links. As a result, faster interdie communication with less power consumption can be achieved on Si-IF. According to S. Jangam *et.al* [8], the energy consumption for data transfer is significantly reduced to 0.4pJ/bit on the Si-IF, while it is 23pJ/bit on PCB with SerDes circuit. By thermal compression bonding, heterogeneous integration can be realized on Si-IF. It enables better system performance by fabricating each functional module with the manufacturing process that yields its best performance.

Better thermal-mechanical performance is also obtained on Si-IF. For packaging system with an organic substrate, the CTE mismatch between organic materials, the solder bumps, and silicon dies can cause severe reliability issues by CPI. However, on Si-IF, CPI is eliminated because both the dies and the board are made of Si. Si-IF also enables higher heat dissipation efficiency because Si has much higher thermal conductivity (149W/K·m) than organic materials (typically <1W/K·m), which is important for systems with high integration density.

Figure 1.1 The interconnect scheme on PCB (top) and on Si-IF (bottom)

#### 1. 3 Contribution of this Work

The primary objectives of this work are to develop two technological enablers for the

Si-IF: the through-wafer vias (TWVs) and plasma dicing (PD), both of which involves

high aspect ratio Si etch. The contributions of this work are as follows.

(1). Design and verify the electrical performance of TWVs

- (2). Examine the thermal reliability issues related to TWVs during the Si-IF fabrication

- (3). Fabricate TWVs on 300µm thick Si wafer.

- (4). Develop plasma dicing process to enable compact die assembly on Si-IF.

#### **1.4 Organization of this Thesis**

The organization of the thesis is as follows. In Chapter 2, the electrical performance of TWV is simulated in ANSYS HFSS with different design parameters. Chapter 3 presents the interconnect design and electrical reliability analysis for the TWV based power links. The thermal reliability issues related to TWV during the Si-IF process is analyzed in Chapter 4. Chapter 5 demonstrates the fabrication process of TWV in UCLA Nanolab. The process flow of plasma dicing and the characterization results are presented in Chapter 6. The conclusions are drawn in Chapter 7.

# **CHAPTER 2**

# The Design and Electrical Simulation of Through-Wafer Vias (TWV)

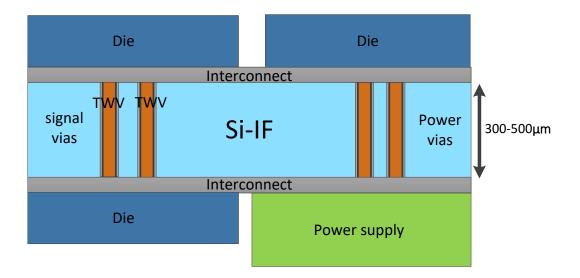

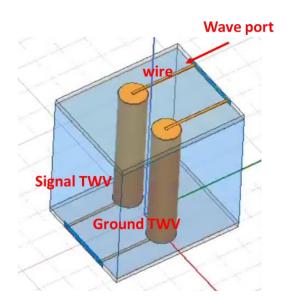

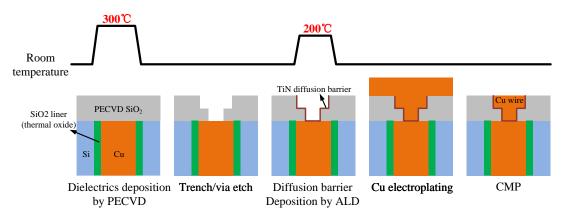

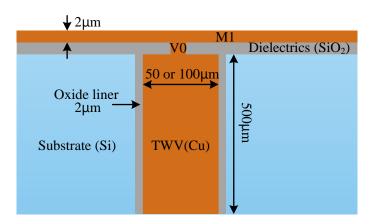

In the silicon interconnect fabric (Si-IF) technology, the communication between dies on the two opposite sides can be achieved by building vias on Si-IF. More importantly, power modules are attached to the backside of Si-IF. Therefore, vias are needed to connect Si-IF and the power modules for power delivery. A similar concept named through silicon via (TSV) has been practiced for 3D integration technology, which provides vertical connect among the stacked Si dies [9], [10]. In the TSV process, the Si dies are usually thinned to about 50µm thick for the ease of making high aspect ratio via. However, the Si-IF is fabricated on a thick Si wafer (300-500µm) to provide enough mechanical support for the dies bonded. Therefore, the vias built on this thick Si-IF are called through-wafer vias (TWV). Two types of TWVs, the signal vias, and power vias are designed for low-frequency signal (<1GHz) transfer and power supply, respectively, as shown in Figure 2.1. In this chapter, we mainly focus on the design and electrical simulation of the signal vias.

Figure 2.1 The TWVs in silicon interconnect fabric (Si-IF)

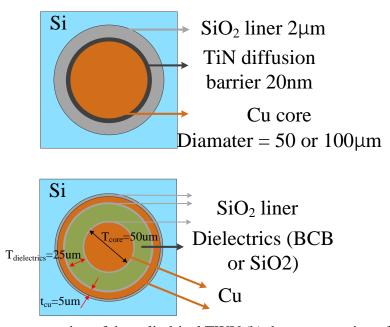

Two types of vias geometry, the cylindrical via and co-axial via are considered [11], [12]. The former is designed for both the signal via and power vias, while the latter is used only for the signal via due to its relatively high resistance. The top view of via cross-section is shown in Figure 2.2. For the cylindrical via, the diameter of the Cu core is 50µm and 100µm for the signal via and power via, respectively. The Cu core is surrounded by 2µm thick SiO<sub>2</sub> dielectrics for electrical insulation. A 20nm TiN diffusion barrier is deposited by ALD to prevent Cu atom diffusion into SiO<sub>2</sub> dielectrics. The depth of a TWV is about 300-500µm, depending on the thickness of the Si-IF. The geometry of a co-axial TWV is shown in Figure 2.2(b). The signal is conducted by the Cu core with 50µm diameter. The 5µm thick copper shell is grounded to prevent coupling noise between the core and the Si substrate. A 25µm-thick dielectric is filled between the Cu core and grounded Cu shell. SiO<sub>2</sub> or benzocyclobutene (BCB) can be used as the filling dielectrics [**12**]. SiO<sub>2</sub> dielectrics are deposited between the Cu shell and Si substrate. The detail information about fabricating co-axial vias can be found in [11].

Figure 2.2 The cross-section of the cylindrical TWV (b) the cross-section of the coaxial TWV  $\,$

#### 2.1. Transmission Property of TWV

To study the transmission property of TWV, the insertion loss of signal TWV is calculated by ANSYS HFSS. For cylindrical via, a signal-ground (S-G) TWV pair is simulated [12], [13]. The diameter of the Cu core is 50µm and the height is 500µm. The thin TiN barrier layer is not considered for the ease of simulation. A 20µm SiO<sub>2</sub> layer is built at the top and bottom surfaces of the Si substrate to consider the effect of redistribution layer dielectrics. The silicon substrate is assumed to be lightly doped with a resistivity of  $10\Omega \cdot cm$ . The lumped ports are applied at the top and bottom surface of the via. For the coaxial TWV, the diameter and height of the Cu core are the same as the cylindrical TWV. The thickness of the filling dielectrics and the Cu shell are 25µm

and 5 $\mu$ m, respectively. Two types of filling dielectrics, SiO<sub>2</sub> and BCB are considered. The insertion loss is characterized by the transmission coefficient S<sub>21</sub> with a frequency sweep from 10MHz to 20GHz. All the materials parameters and geometrical parameters used in the simulation are listed in TABLE 2.1.

| Parameter                                   | Value  | Parameter                                              | Value |

|---------------------------------------------|--------|--------------------------------------------------------|-------|

| The dielectric constant of Silicon          | 11.7   | The thickness of Cu shell (coaxial TWV)                | 5µm   |

| The dielectric constant of SiO <sub>2</sub> | 3.9    | The thickness of the filling dielectrics (coaxial TWV) | 25µm  |

| The dielectric constant of BCB              | 2.6    | TWV height                                             | 500µm |

| Si Substrate resistivity                    | 10Ω·cm | TWV pitch (for the S-G pair)                           | 100µm |

| The diameter of Cu core                     | 50 µm  | The thickness of the SiO <sub>2</sub> liner            | 2µm   |

Table 2.1 Parameters for TWV Electrical Simulation

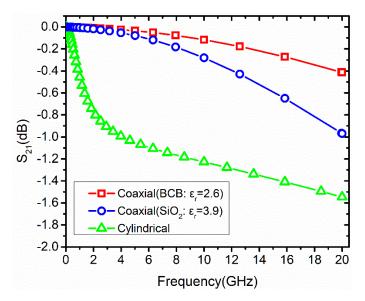

The simulated  $S_{21}$  is plotted in Figure 2.3. The insertion loss rises as the signal frequency is increased due to the leakage from Cu core to Si substrate through the SiO<sub>2</sub> dielectrics [14]. At high-frequency range (>5GHz), insertion loss of the co-axial TWV is 0.6dB~1.3dB smaller than the cylindrical TWV because the Cu shell effectively prevents the signal from coupling into Si substrate. The transmission property of the coaxial TWV also depends on the property of its filling dielectrics. The insertion loss is smaller when filling dielectrics with smaller dielectric constant and less loss tangent is used. Though coaxial TWV shows less insertion loss at a higher frequency, the signal TWV is designed to operate at the frequency <1GHz, where both types of TWV show insertion loss <0.25dB. Therefore, only the cylindrical TWV is studied in this thesis because of its less complicated fabrication process.

Figure 2.3 The insertion loss of cylindrical TWV and coaxial TWV

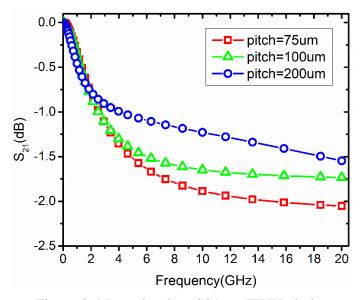

The impact of TWV design parameters on its transmission property is studied by varying one parameter while keeping the other parameters unchanged. First, the TWV pitch is changed from 75µm, 100µm to 200µm. From the results in Figure 2.4, the transmission property with different TWV pitches is similar at the low-frequency range (<1GHz), where the insertion loss is about 0.25dB at 1GHz. For high-frequency range (>5GHz), the insertion loss increases with a smaller TWV pitch. As the TWV pitch decreases, the conductance and capacitance of the Si substrate between the signal via and ground via is increased, which leads to larger insertion loss [14].

Figure 2.4 Insertion loss S21 vs. TWV pitch

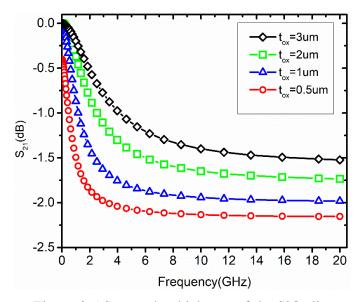

The insertion loss  $S_{21}$  vs the thickness of SiO<sub>2</sub> liner is plotted in Figure 2.5. It is observed that the insertion loss is reduced with thicker SiO<sub>2</sub> dielectrics. It can be explained by the leakage loss between TWV and Si substrate through SiO<sub>2</sub>. Since the capacitance of the SiO<sub>2</sub> liner is inversely proportional to its thickness, thicker oxide liner has a larger impedance ( $Z = 1/j\omega C_{SiO2}$ ), which leads to less leakage and therefore lower insertion loss. To ensure the insertion loss is less than 1dB at 1GHz, the SiO<sub>2</sub> thickness should be larger than 1µm. However, thicker SiO<sub>2</sub> requires longer oxidation time, especially for thermal oxidation where the non-linear deposition rate makes it time-consuming to grow thick SiO<sub>2</sub>. Therefore, the SiO<sub>2</sub> is chosen to be 1µm-2µm for the fabrication process.

Figure 2.5 S<sub>21</sub> vs. the thickness of the SiO<sub>2</sub> liner

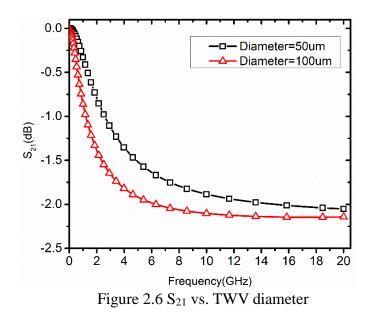

Figure 2.6 shows the relation between TWV diameter and insertion loss. The via space is fixed at 50 $\mu$ m. It is observed that insertion loss is reduced for smaller via diameters, which can be explained by the decreased capacitance of the SiO<sub>2</sub> liner due to a smaller surface area. Therefore, the diameter of the signal via is chosen to be 50 $\mu$ m (aspect ratio = 10 for 500 $\mu$ m thick Si wafer) considering the difficulty in high aspect ratio via etching.

#### 2.2 Transmission Property of a Signal Path

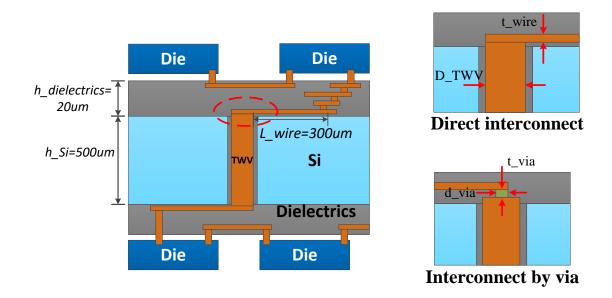

For inter-die communication across the Si-IF, a complete data link consists of 4-layer Cu wiring levels on both sides of the Si-IF, the interconnect between Cu wiring levels and dies, and the TWV, as shown in Figure 2.7.

Figure 2.7 A data link with TWV (left) Two interconnect scheme between the Cu wires and TWV (right).

For the TSVs, the interconnect between via and Cu wiring levels are achieved by building micro bumps above the vias [14]. However, for TWVs, it is difficult to fabricate micro bumps with uniform thickness because of dishing effect in CMP. Therefore, two interconnect schemes without micro bumps are proposed: the direct connect scheme (scheme 1) and via-connect scheme (scheme 2), as shown in Figure 2.7. In scheme 1, Cu wires are fabricated directly on the TWV with a single damascene process. In scheme 2, the Cu wires are connected to TWV by a via. The dual damascene

process is used for this scheme.

Figure 2.8 The simulation model of a data link with TWV in ANSYS HFSS

The transmission property of a data link with TWV is studied in ANSYS HFSS with a signal-ground (S-G) model, as shown in Figure 2.8. The Si-IF is modeled as a Si substrate with 20 $\mu$ m thick SiO<sub>2</sub> dielectrics on its top and bottom surfaces. Although there are four wiring levels on Si-IF, only the bottom wiring level is considered to reduce the complexity of the simulation. The pitch of Cu wire is 10 $\mu$ m and the thickness is 2 $\mu$ m [3]. The wire length is 300 $\mu$ m in the simulation model, which is a reasonable value for compact die assembly with less than 100 $\mu$ m die space. Therefore, the total length of the data link is about 1100 $\mu$ m. The EM wave excitations are applied at the end of the Cu wires. All the parameters in the simulation are listed in TABLE 2.2.

TABLE 2.2 Parameters for Electrical Simulation

| Parameter                                       | Value          | Parameter                               | Value |

|-------------------------------------------------|----------------|-----------------------------------------|-------|

| The dielectric constant of Silicon              | 11.7           | The thickness of SiO <sub>2</sub> liner | 2µm   |

| The dielectric constant of the SiO <sub>2</sub> | 3.9            | Cu wire pitch                           | 10µm  |

| Si Substrate resistivity                        | $10\Omega$ cm. | Cu wire width                           | 5µm   |

| The diameter of Cu core                         | 50 µm          | Cu wire thickness                       | 2µm   |

| TWV height                                      | 500µm          | Cu wire length                          | 300µm |

| TWV pitch                                       | 100µm          |                                         |       |

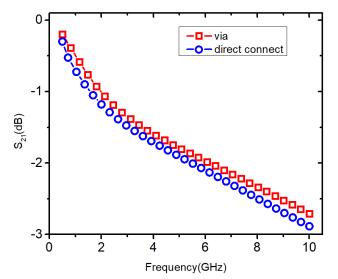

The simulated insertion loss  $S_{21}$  is plotted in Figure 2.9. Low insertion loss is obtained at both low-frequency range (less than 0.6dB at 1GHz) and high-frequency range (less than 3dB at 10GHz). It is also observed that scheme 2 shows 0.2dB lower loss than scheme 1 for signals with 0-10 GHz frequency. It can be attributed to lower insertion loss at the TWV/Cu wire interface.

Figure 2.9 The insertion loss  $S_{21}$  for a data link with TWV

# **CHAPTER 3**

# **Through-Wafer Vias for Power Delivery**

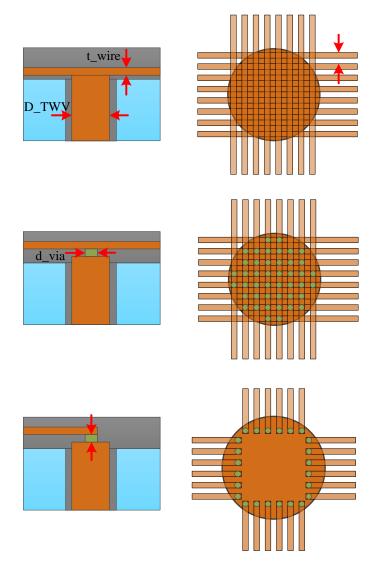

The power delivery on Si-IF is achieved by TWV based power delivery network (PDN), where each TWV carriers 1A current from the power modules to the densely packed Si dies on Si-IF. The geometry of the TWVs for power delivery is similar to the cylindrical signal TWVs except that the diameter is increased to 100µm to reduce the resistance. In this chapter, we mainly focus on designing the interconnect schemes between power TWV and Cu wiring levels for the PDNs. Reliability issues such as current crowding at the interface of via and Cu wires, IR drops in the PDNs and current uniformity in the Cu wires are modeled and analyzed.

#### **3.1 Simulation Model**

Three interconnect schemes are compared in this chapter, as shown in Figure 3.1. In Scheme 1, the Cu wires are directly connected to TWV with a single damascene process. In Scheme 2, the Cu wires are connected to TWV by an array of vias, where  $4\times8=32$  wires are fanned out for each TWV. In Scheme 3, the vias are fabricated at the periphery of TWV only and each Cu wire is then connected to one via, where  $4\times6=24$  wires are fanned out from each TWV. Both Scheme 2 and 3 can be fabricated by the dual damascene process.

Figure 3.1 Three interconnect schemes between the power TWV and wiring levels

### **3.2 Modeling of Current Crowding Effect**

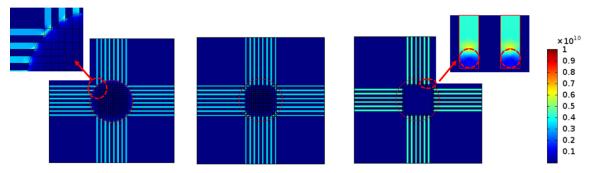

For Cu wiring levels, electro-migration is induced by the "electron wind force", where the electron flux drives Cu atom to a vacancy nearby and leaves behind a new vacancy at the original Cu atom position. The Cu atom flux is in the direction of current while the vacancy flux is in the opposite direction, which leads to void formation near the cathode. The void can increase wire resistance and even lead to interconnect functional failure. More information about the electro-migration can be found in **[15]-[17]**. The locally enhanced current density, termed current crowding, is the primary cause of electromigration [15]. It occurs at the turning point of current flow due to resistance mismatch. The current density distribution in TWV and Cu wiring levels are examined by FEM simulation, where 1A current is carried by each TWV. Figure 3.2 plots the current density at the intersection plane of the via and Cu wire. For Scheme 1, current crowding occurs at the periphery of the TWV. For Scheme 2 and 3, current crowding occurs at the interface of the via and Cu wire. The maximum current density is  $1.1 \times 10^{10}$  A/m<sup>2</sup>,  $8.73 \times 10^9$  A/m<sup>2</sup> and  $7.4 \times 10^9$  A/m<sup>2</sup> for the three interconnect schemes, respectively. These values are below the threshold for electromigration, which is  $5.7 \times 10^{10}$ A/m<sup>2</sup> for Cu [3]. Therefore, it is indicated that interface between TWV and Cu wiring levels are resistant to electromigration due to low current crowding.

Figure 3.2 The current density distribution at the via/wire interface

#### **3.3 Current Uniformity Analysis**

The current enters each Cu wire can be different due to the non-uniform current density distribution at the TWV/Cu wire interface. Figure 3.3 shows the current in each Cu wire, which is normalized by the current in the ideal case. The Current non-uniformity  $\Delta I$  is

defined as the difference between the maximum and minimum current. Scheme 1 shows poor current uniformity where  $\Delta I$  is as high as 20%. In scheme 2, good current uniformity is observed for the Cu wires in the middle. However, for the two wires near the boundary, the current drops rapidly, resulting in  $\Delta I = 8\%$ . Good current uniformity is obtained in scheme 3 with less than 0.2%  $\Delta I$ .

Figure 3.3 Current uniformity in different Cu wires

#### **3.4 IR Drops in Power Link**

The IR drop in a TWV based power link is evaluated with different Cu wire lengths, as plotted in Figure 3.4. It is observed that the IR drop varies linearly with the wire length. Scheme 1 and 2 show similar IR drops while Scheme 3 shows slightly higher IR drop since each wire carries higher current. If the maximum IR drop allowed is 2% V<sub>dd</sub>, then the maximum length of Cu wire is about 200-250µm in this power link. It is also observed that the voltage drop rises if the via diameter is reduced to 50µm (the dashed line) because of higher via resistance.

Figure 3.4 IR drop vs the length of wires

# **CHAPTER 4**

# **Thermo-mechanical Reliability Analysis**

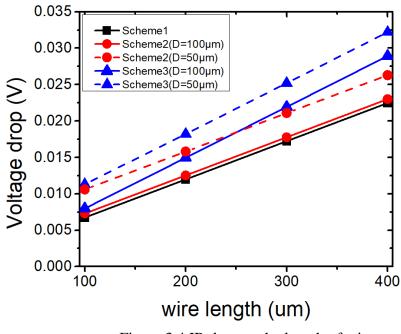

Thermal excursions are applied to TWV when building the four-layer Cu wiring levels above it with the dual damascene process, as shown in Figure 4.1. The maximum temperature occurs during PECVD SiO<sub>2</sub> deposition. Under high thermal load, Cu via extrudes out of surrounding Si due to its higher coefficient of thermal expansion (CTE) [**18**], resulting in non-uniform dielectrics deposition. The Cu wires built above the local extrusion will be thinned down after the CMP process, which leads to higher wire resistance [**19**]. Besides, high thermal stress can induce interfacial delamination at the Cu/SiO<sub>2</sub> interface and cohesive cracks in Si substrate due to the CTE mismatch between Cu, Si and SiO<sub>2</sub> [**20**]-[**23**]. It degrades the reliability and electrical performance of TWV and Si-IF. In this chapter, the thermal-mechanical reliability issues are analyzed to study the impact of process temperature on TWV reliability.

Figure 4.1 Thermal load applied to TWVs during the fabrication of Cu wiring levels

#### **4.1 Simulation Model**

The simulation model is shown in Figure 4.2. The Cu via is surrounded by a 2µm thick SiO<sub>2</sub> liner and the Si substrate. The bottom wiring level with 10µm pitch Cu wires is built above the TWV. The TiN diffusion barrier is neglected in this model because it is only 20nm thick. Anisotropic material property of Si is considered and its stiffness matrix is expressed as Eq. (4.1) [19], which is a symmetrical matrix. Cu is treated as an orthotropic material and its Young's modulus and shear modulus are adopted from Ref. [24]. A non-linear material model is applied here to consider Cu hardening under plastic deformation, as listed in TABLE 4.2 [21]. The yield strength of Cu is 240MPa and its stress-free temperature is set to be 25°C. All the materials parameters used in the simulation are listed in TABLE 4.1. The symmetrical boundary condition is applied at the lateral surfaces to simulate a periodic TWV array on the Si-IF.

Figure 4.2 The cross-section view of the simulation model

| Material | Young's modulus                                                    | Poisson's ratio | CTE (ppm) |

|----------|--------------------------------------------------------------------|-----------------|-----------|

| Si       | See Eq. (4.1)                                                      | 0.21            | 2.6       |

| Cu       | E <sub>1</sub> =156GPa E <sub>2</sub> =68GPa E <sub>3</sub> =68GPa | 0.36            | 17        |

| Cu       | G12=G23=G13=60.96GPa                                               | 0.50            | 17        |

TABLE 4.1 Materials Parameters in Thermal Mechanical Simulation

| SiO <sub>2</sub> | 70GPa | 0.17 | 0.5 |

|------------------|-------|------|-----|

|------------------|-------|------|-----|

| Stress(MPa) | Plastic Strain |

|-------------|----------------|

| 240         | 0              |

| 250         | 0.003          |

| 255         | 0.007          |

| 255         | 0.009          |

| 250         | 0.007          |

TABLE 4.2 Hardening Function of Copper

|            | $C_{11}$ | $C_{12}$ | $C_{33}$                                                                      | 0           | 0        | 0        |

|------------|----------|----------|-------------------------------------------------------------------------------|-------------|----------|----------|

|            | $C_{12}$ | $C_{22}$ | $C_{23}$                                                                      | 0           | 0        | 0        |

| <i>S</i> = | $C_{33}$ | $C_{23}$ | $C_{33} \\ C_{23} \\ C_{33} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | 0           | 0        | 0        |

| 5 –        | 0        | 0        | 0                                                                             | $C_{_{44}}$ | 0        | 0        |

|            | 0        | 0        | 0                                                                             | 0           | $C_{55}$ | 0        |

|            | 0        | 0        | 0                                                                             | 0           | 0        | $C_{66}$ |

| $C_{1} = C_{2} = C_{\overline{2}} C_{\overline{3}} = 165.$ |       |

|------------------------------------------------------------|-------|

| $C_{12} = C_{2\overline{3}} C_{\overline{1}3} 63. $        | (4.1) |

| $C_{44} = C_{55} = C_{56} = 79.6P$                         |       |

#### **4.2 Results and Discussion**

The effect of Cu extrusion is first analyzed. 300°C thermal load is applied to TWV to simulate the situation during PECVD SiO<sub>2</sub> dielectrics deposition. Under this temperature, Cu via extrudes out of the Si substrate and induces non-uniform dielectrics deposition due to plastic deformation. As shown in Figure 4.3(a), the height variation  $\Delta h$  of the dielectrics is 0.17µm and 0.3µm for 50µm and 100µm diameter vias, respectively. The deformation is exaggerated when plotting the figure to make it more visible. The Cu wire on the local extrusion is thinned down after CMP process, which increases the local wire resistance, as shown in Figure 4.3(b). To solve this problem, the TWV is annealed and Cu extrusions are planarized by CMP before fabricating the

Cu wiring levels [18].

Figure 4.3 (a). Cu via extrusion after PECVD oxide deposition. (b) The deformed wire after planarization by CMP.

The thermal stress distribution at 300°C is obtained by FEM simulator. In general, the thermal stress is higher for TWVs with 100 $\mu$ m diameter than 50 $\mu$ m, as shown in Figure 4.4 (a) and (c). High compressive stress is induced in the Cu via and Si substrate because of lateral Cu expansion, which can cause cohesive cracks [22]. High shear stress  $\sigma_{yz}$  is induced at the top of via because of Cu extrusion, as shown in Figure 4.4 (b) and (d). It induces plastic deformation and peels the Cu via off the SiO<sub>2</sub> liner, which is the driven force of interfacial delamination.

Figure 4.4(a) The normal stress  $\sigma_y$  (b) the shear stress  $\sigma_{yz}$  for via with a 50µm diameter (c) The normal stress  $\sigma_y$  (d) the shear stress  $\sigma_{yz}$  for via with a 100µm diameter. The temperature in the simulation is 300°C.

Under thermal stress, interfacial delamination initiates at defects such as micro-cracks or voids, which is introduced during the TWV process. Energy release rate (ERR) based fracture mechanical analysis is conducted to evaluate the potential risk of interfacial delamination under thermal load [20]. A pre-existing defect of length *a* is assumed at the Cu/SiO<sub>2</sub> interface and the total strain energy is *U*, as shown in Figure 4.5(a). When the crack length is increased by *da*, the materials along the crack is freed and the stored strain energy is released to break the atomic bond and extend the crack, resulting in strain energy change *dU* [25]. The energy release rate is calculated as ERR = -dU/dA, where *dA* is the surface area change of the crack. The ERR is calculated under different process temperature for 50µm and 100µm diameter vias, as shown in Figure 4.5(b). Generally, the ERR is increased as the crack extends. If the ERR becomes larger than the fracture energy of the Cu/SiO<sub>2</sub> interface (9J/m<sup>2</sup> [20]), the crack will propagate catastrophically and induces delamination. Under process temperature of 200°C, ERR is smaller than the fracture energy of Cu/SiO<sub>2</sub> interface over a large range of crack length (0-30µm), which indicates that the delamination of Cu/SiO<sub>2</sub> interface can be avoided under 200°C. When the process temperature rises to 300°C, the ERR exceeds the fracture energy if the crack length is longer than 20µm, which indicates that delamination can be initiated by long cracks. Besides, it is also observed that higher ERR is induced by Cu via with larger diameter. The reliability issues can be alleviated by lowering the process temperature and increasing the process reliability in the TWV fabrication to reduce the number of defects.

Figure 4.5 (a) the model to calculate ERR (b) The simulated ERR vs crack length

### **CHAPTER 5**

### Experiment Demonstration of Through-Wafer Vias

#### **5.1 Fabrication Process of TWV**

The fabrication process of TWVs is shown in Figure 5.1. The via is etched by Bosch etch process with 2µm thick Si oxide as hard mask. The photoresist cannot be used as the etch mask because of its high consumption rate during Bosch etch. A 1µm oxide liner layer is grown by wet oxidation for electrical insulation, which provides good film uniformity and step coverage in high aspect ratio via. TEOS based PECVD can also be used for oxide deposition [**26**]. A 20nm TiN diffusion barrier is deposited by ALD to prevent Cu diffusion into SiO<sub>2</sub>. The via is filled by Cu electroplating after sputtering seed layer (600nm Cu/50nm Ti). Three challenges exist in the process because of the high aspect ratio of vias: 1). Obtaining desired via profile with acceptable etch rate. 2). step coverage of the deposition and sputtering steps. 3). void free Cu electroplating with an acceptable rate.

#### 5.2 Via Etch by Bosch Process

The high aspect ratio vias on the Si wafer is created by Bosch etch process, which is featured of high etch rate, high selectivity and controllable profile **[27]**.

The Bosch etch is a multi-cycle plasma etch process that each cycle consists of passivation, polymer etch and silicon etch, as shown in Figure 5.2. The typical reactant

gases are SF<sub>6</sub>, C<sub>4</sub>F<sub>8</sub>, and Ar. The glow charge of Ar helps with plasma formation. The high energy electrons in the plasma dissociate SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub>, which forms fluorine radical, SF<sub>5</sub><sup>+</sup> ions, and CF<sub>2</sub> monomer [**28**].

Figure 5.1 The fabrication process of TWV

In the passivation phase, the  $CF_2$  monomer polymerizes on the sidewall and the bottom of the vias. The polymer passivates the Si surface and prevents it from chemical etch in the later etch phase. In the polymer etch phase, the  $SF_5^+$  ions are accelerated under the high electric field in the plasma sheath and bombard the Si surface vertically, which selectively removes the polymer at the bottom and expose the Si surface. Then, in the Si etch phase, ion bombardment breaks the Si-Si bond at the surface and creates highly active dangling bonds. The fluorine radicals diffuse to Si surface and form volatile  $SiF_4$ . Si is removed when the  $SiF_4$  is desorbed from the surface.

Figure 5.2 the three phases of a Bosch etch cycle (a) polymerization (b) polymer etch (c) silicon etch

#### **5.3 Via Profile Characterization**

Figure 5.3(a) shows the SEM images of the TWV cross-section with 50 $\mu$ m diameter after 100min Bosch etch. The sidewall profile is straight while it gets narrower and stops at about 400 $\mu$ m depth. It can be attributed to the impact of aspect ratio dependent etch, where the limited gas transport and less ion bombardment at the bottom of the via

makes it gets narrow and finally stops at the critical aspect ratio [29]. The impact of aspect ratio dependent etch can be reduced by increasing the bias power, reducing chamber pressure or using a ramped parameter process [27].

The average etch rate is 6µm/min in the first 50min. Higher etch rate can be obtained by reducing polymerization time. However, the etch anisotropy is reduced at the same time and scalloping is increased because of thinner polymer on the sidewall. An optimal point of the etching rate and anisotropy should be achieved by balancing the duration of polymerization and etch steps.

Figure 5.3 (a) The cross-section view of  $50\mu m$  diameter TWV under SEM after 100min Bosch etch (b) A zoom-in picture of the sidewall

Ideally, the etch process is anisotropic because of the sidewall passivation. However, since the passivation and etch steps are alternative, the freshly exposed sidewall is not covered by polymer and lateral etch occurs, which leads to scalloping at the sidewalls [30]-[33]. Figure 5.3(b) shows a zoom-in picture of the via sidewall, where the amplitude of the sidewall is about 48nm. The scalloping on sidewall will impact the

step coverage and conformity of the dielectrics in the subsequent deposition process **[31]**. For vias with thin oxide liner, a large leakage current is also observed due to the poor dielectrics step coverage and cohesive crack induced by stress concentration at the scalloping protrusions **[32]**. Continuous gas flow can help reduce the scalloping. Thick SiO<sub>2</sub> liner (>1µm) also helps smoothen the scalloping.

Optical profiler is used for non-destructive characterization of the 3D via profile, which provides a large field of view, as shown in Figure 5.4(a). Based on this measurement, the etch rate uniformity is calculated to estimate the etch time to etch through each via. Figure 5.4(b) shows the etch rate difference in the region marked by the dashed line in Figure 5.4(a). The etch rate of each via is normalized by the average etch rate. Only 1.2% etch rate difference is observed. The etch uniformity TWV density is also impacted by the local via density through micro-loading effect [27], which should be considered during the layout design to get a uniform etch rate.

Figure 5.4 (a) the via profile under an optical profiler. (b) The etch rate of different vias in the dash line box in Figure (a)

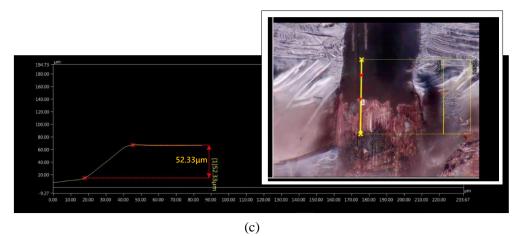

The top view of the vias after 3h Cu plating is shown in Figure 5.5 (a). The wafer is cleaved along the blue dash line to get cross-section image of the via, as shown in Figure 5.5 (b). Due to high via aspect ratio, only part of the via is covered by seed layer. Therefore, Cu is plated near one end of the via. The via sidewall profile in the blue dash line region is characterized by Keyence microscope. The sidewall profile along the yellow line is shown in Figure 5.5(c). The Cu thickness on the sidewall is about  $52\mu m$ , which indicates that one end of the via is filled. With this Cu plug, a bottom-up Cu plating can be used to fill the via. Further improvement of the plating tool and chemicals should be conducted to obtain acceptable plating rate.

(a)

(b)

Figure 5.5 (a) top view of the vias after 3h plating. (b). the cross-section image of the vias (c) the profile of the sidewall in the blue dash line region in Figure (b).

# CHAPTER 6 Plasma Dicing for Si-IF

#### 6.1 Dicing Technology Requirement For Si-IF

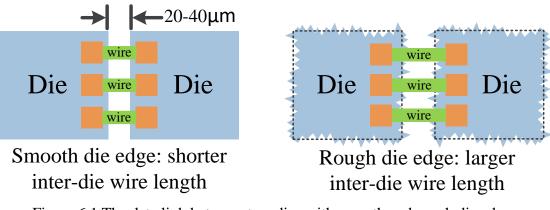

On Si-IF, compact die assembly is conducted to reduce data latency. 20-40µm die space is achieved by advanced bonding tool with precise overlay control. However, with a rough die edge, the minimum die space and the distance from the metal pad to die edge are increased, which leads to longer data links, as shown in Figure 6.1. Therefore, smooth die edge is needed to get short data link. The mechanical strength of silicon die is also important because there is no die-level packaging on Si-IF, which requires less chipping and micro-cracks induced during dicing. Besides, polygonal die shape is preferred to increase the flexibility for die assembly.

Figure 6.1 The data link between two dies with smooth and rough die edges

As discussed above, the requirement for dicing technology is summarized as follows.

• Smooth die edge

- No chipping and micro-cracks after dicing

- Flexible die shapes

#### 6.2 Challenges in State-of-the-art Dicing Technologies

Saw dicing and laser dicing are the two common ways for Si die singulation. But unfortunately, none of them satisfies the above requirements. The drawbacks of saw dicing are listed as follows [33]-[35].

- Rough die edge. Irregular fracture occurs under the high pressure induced by the blade, which is more significant for thinner wafers.

- Large dicing street (typically > 60µm) is needed to accommodate the blade. It reduces the total die area on one wafer, especially for wafers with small dies (1×1mm).

- Micro-cracks and delamination are introduced. Catastrophic die fracture can be induced by the cracks and die malfunction also occurs when the cracks propagate into the fragile low-k dielectrics. Keep out zone (KOZ) and crack stops are usually designed at the die edge to prevent the crack propagation, which further increases the length of the data links.

- Inefficient for thin dies. As the wafer becomes thinner, the blade feed speed needs to slow down to reduce chipping.

Laser dicing creates dicing street by the local high temperature induced by laser. The drawbacks of laser dicing are seen as follows **[36]**.

• Heat affected zones (HAZ) created by high local temperature. Neither active device nor interconnect can be put near the HAZ, which increases the length of the data

links.

- Multilayer delamination. Since multiple different materials are stacked on the wafer surface, multilayer delamination occurs at high temperature due to the CTE mismatch.

- Low throughput because the laser beam is scanned linearly.

#### **6.3 Plasma Dicing Process**

To overcome the drawbacks of current dicing technology, plasma dicing technology is developed. In plasma dicing, dies are diced by plasma assisted chemical etch instead of mechanical dicing. In this work, plasma dicing process for 300µm thick Si wafer is developed with acceptable etch rate.

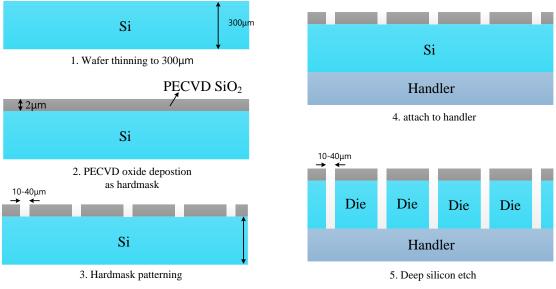

A dummy dicing process is conducted to characterize the etch rate, dicing street profile and die edge roughness, as shown in Figure 6.2. The wafer is first thinned to 300 $\mu$ m by polish and CMP, which is a reasonable value that balances die strength and the etching time. Then 2 $\mu$ m PECVD SiO<sub>2</sub> is deposited as hard mask. Thermal oxidation cannot be used here because the active devices on a real wafer will be damaged by high temperature (>1000 °C ). The dicing street is then patterned on the hard mask by lithography and reactive ion etch. The width of the dicing street are 10 $\mu$ m, 20  $\mu$ m, 30  $\mu$ m and 40 $\mu$ m in this experiment. The wafer is attached to a handler after the photoresist is removed. Finally, the dicing street is etched by Bosch etch process to get the silicon dies.

Figure 6.2 The process flow of plasma dicing (dummy dicing)

#### **6.4 Profile Characterization**

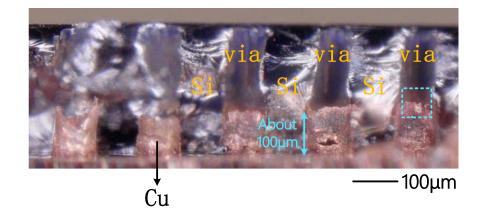

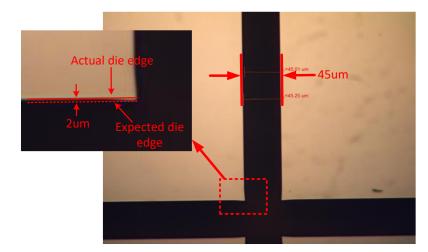

The 40 $\mu$ m width dicing street after Bosch etch is shown in Figure 6.3, where a smooth die edge is obtained. The width at the top of the dicing street is enlarged to 45 $\mu$ m, which can be attributed to the undercut effect during the Bosch process [27].

Figure 6.3 the dicing street of the die after plasma dicing

The etch rate for  $10\mu m$  wide dicing street is about  $6\mu m/m$  in while it is about  $6.5\mu m/m$  in for the other three. It can be attributed to the lower etchant transport rate when the

aspect ratio is increased.

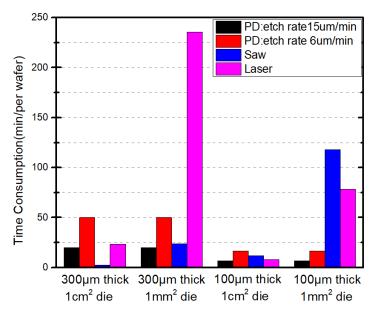

#### 6.5 Throughput Benefits of Plasma Dicing

The time consumption to dice a 300mm wafer is compared with different dicing technology, including plasma dicing, saw dicing and laser dicing. For plasma dicing, the time consumption is calculated by dividing wafer thickness with etch rate. Two typical etch rate, 6µm/min (in UCLA Nanolab) and 15µm/min (state-of-the-art commercial tool) are used here. For saw dicing and laser dicing, the time consumption is calculated by dividing total dicing street length by dicing speed. The dicing speed of saw dicing depends on wafer thickness and the values are adopted from [36]. Figure 6.4 shows the calculated results. To dice  $1 \text{ cm}^2$  square die on a 300µm thick wafer, saw dicing shows significantly higher efficiency than the other methods. However, when the wafer thickness is reduced to 100µm, plasma dicing becomes the most time-efficient method because the speed of saw dicing is slowed down from 120mm/s to 20mm/s to reduce chipping [36]. For smaller dies of 1mm<sup>2</sup>, plasma dicing provides quick wafer singulation while the dicing time of saw dicing and laser dicing is increased linearly as the dicing street length increases. Therefore, plasma dicing is beneficial for the situations where thin and small dies are required.

Figure 6.4 A comparison of the time consumption for 300mm Si wafer singulation with plasma dicing (PD), saw dicing and laser dicing.

# **CHAPTER 7** Conclusions and Future Work

In this thesis, the through-wafer via (TWV) technology is developed for signal and power delivery on silicon interconnect fabric (Si-IF). The electrical performance of through-wafer via is simulated by ANSYS HFSS width different design parameters. Low insertion loss is obtained when it is operating at the low-frequency range (<1GHz). The electrical reliability issues such as electromigration are examined and verified. The thermal reliability issues related to TWV during Si-IF fabrication are analyzed by simulation. It is observed that interfacial delamination can be induced at the interface between Cu via and SiO<sub>2</sub> liner due to the CTE mismatch between the materials. The TWV is fabricated in UCLA nanolab on a 300µm thick wafer. Plasma dicing technology is also developed based on deep silicon etch to obtain smooth die edge after dicing, which enables compact die assembly on Si-IF.

In the future, a novel electroplating method is to be developed for void-free copper plating with an acceptable rate. The electrical test is to be conducted to measure the via resistance and transmission property. Electromigration test is also to be conducted to examine the reliability issues when carrying high current.

#### REFERENCES

- [1]. International Technology Roadmap for Semiconductors (ITRS) 2013

- [2]. S. S. Iyer, "Heterogeneous Integration for Performance and Scaling," in *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 6, no. 7, pp. 973-982, July 2016.

- [3]. S. Jangam, "Simple Universal Parallel Interface (SuperCHIPS) Protocol for High Performance Heterogeneous System Integration.", University of California, Los Angeles, 2017.

- [4]. T. C. Carusone, "Introduction to Digital I/O: Constraining I/O Power Consumption in High-Performance Systems," in IEEE Solid-State Circuits Magazine, vol. 7, no. 4, pp. 14-22, Fall 2015.

- [5]. J. Knickerbocker et al. "3D silicon integration." Electronic Components and Technology Conference, 2008. ECTC 2008. 58th. IEEE, 2008.

- [6]. E. Beyne. "3D system integration technologies." VLSI Technology, Systems, and Applications, 2006 International Symposium on. IEEE, 2006.

- [7]. A. A. Bajwa et al., "Heterogeneous Integration at Fine Pitch (≤ 10 µm) Using Thermal Compression Bonding," 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, 2017, pp. 1276-1284.

- [8]. S. Jangam, S. Pal, A. Bajwa, S. Pamarti, P. Gupta and S. S. Iyer, "Latency, Bandwidth and Power Benefits of the SuperCHIPS Integration Scheme," 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, 2017, pp. 86-94.

- [9]. M. Motoyoshi, "Through-Silicon Via (TSV)," in Proceedings of the IEEE, vol. 97, no. 1, pp. 43-48, Jan. 2009.

- [10]. M. Koyanagi, T. Fukushima and T. Tanaka, "High-Density Through Silicon Vias for 3-D LSIs," in Proceedings of the IEEE, vol. 97, no. 1, pp. 49-59, Jan. 2009.

- [11]. Soon Wee Ho, Seung Wook Yoon, Qiaoer Zhou, K. Pasad, V. Kripesh and J. H. Lau, "High RF performance TSV silicon carrier for high frequency application," 2008 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, 2008, pp. 1946-1952.

- [12]. Z. Xu and J. Q. Lu, "Three-Dimensional Coaxial Through-Silicon-Via (TSV) Design," in IEEE Electron Device Letters, vol. 33, no. 10, pp. 1441-1443, Oct. 2012.

- [13]. L. Liang, M. Miao, Z. Li, S. Xu, Y. Zhang and X. Zhang, "3D modeling and electrical characteristics of through-silicon-via (TSV) in 3D integrated circuits," 2011 12th International Conference on Electronic Packaging Technology and High Density Packaging, Shanghai, 2011, pp. 1-5.

- [14]. J. Kim et al., "High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV)," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 1, no. 2, pp. 181-195, Feb. 2011

- [15]. Tu, K. N., Yingxia Liu, and Menglu Li. "Effect of Joule heating and current crowding on electromigration in mobile technology." Applied Physics Reviews 4.1 (2017): 011101.

- [16]. J. Pak, M. Pathak, S. K. Lim and D. Z. Pan, "Modeling of electromigration in through-silicon-via based 3D IC," 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, 2011, pp. 1420-1427.

- [17]. Frank, T., et al. "Reliability of TSV interconnects: Electromigration, thermal cycling, and impact on above metal level dielectric." Microelectronics Reliability 53.1 (2013): 17-29.

- [18]. D. Zhang, K. Hummler, L. Smith and J. J. Q. Lu, "Backside TSV protrusion induced by thermal shock and thermal cycling," 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, 2013, pp. 1407-1413.

- [19]. W. Guo et al., "Analysis of copper plasticity impact in TSV-middle and backside TSV-last fabrication processes," 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, 2015, pp. 1038-1044.

- [20]. K. H. Lu et al., "Thermal stress induced delamination of through silicon vias in 3-D interconnects," 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 2010, pp. 40-45.

- [21]. C. S. Selvanayagam, J. H. Lau, X. Zhang, S. K. W. Seah, K. Vaidyanathan and T. C. Chai, "Nonlinear Thermal Stress/Strain Analyses of Copper Filled TSV (Through Silicon Via) and Their Flip-Chip Microbumps," in IEEE Transactions on Advanced Packaging, vol. 32, no. 4, pp. 720-728, Nov. 2009.

- [22]. Jung, Moongon, et al. "TSV stress-aware full-chip mechanical reliability analysis and optimization for 3D IC." Communications of the ACM 57.1 (2014): 107-115.

- [23]. W. Feng, N. Watanabe, H. Shimamoto, K. Kikuchi and M. Aoyagi, "Methods to reduce thermal stress for TSV Scaling ~TSV with novel structure: Annular-Trench-Isolated TSV," 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, 2015, pp. 1057-1062.

- [24]. A. P. Karmarkar, X. Xu, K. B. Yeap and E. Zschech, "Copper Anisotropy Effects in Three-Dimensional Integrated Circuits Using Through-Silicon Vias," in IEEE Transactions on Device and Materials Reliability, vol. 12, no. 2, pp. 225-232, June 2012.

- [25]. Wang, Chun Hui. Introduction to fracture mechanics. Melbourne, Australia: DSTO Aeronautical and Maritime Research Laboratory, 1996.

- [26]. D. Archard, K. Giles, A. Price, S. Burgess and K. Buchanan, "Low temperature PECVD of dielectric films for TSV applications," 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 2010, pp. 764-768.

- [27]. Wu, Banqiu, Ajay Kumar, and Sharma Pamarthy. "High aspect ratio silicon etch: A review." Journal of applied physics 108.5 (2010): 9.

- [28]. Manos, Dennis M., and Daniel L. Flamm, eds. Plasma etching: an introduction. Elsevier, 1989.

- [29]. Yeom, Junghoon, et al. "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect." Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 23.6 (2005): 2319-2329.

- [30]. Y. C. Hsin et al., "Effects of etch rate on scallop of through-silicon vias (TSVs) in 200mm and 300mm wafers," 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, 2011, pp. 1130-1135.

- [31]. K. W. Lee, J. C. Bea, T. Fukushima, Y. Ohara, T. Tanaka and M. Koyanagi, "High reliable and fine size of 5-μm diameter backside Cu through-silicon Via(TSV) for high reliability and high-end 3-D LSIs," 2011 IEEE International 3D Systems Integration Conference (3DIC), Osaka, pp. 1-4.

- [32]. T. Nakamura, H. Kitada, Y. Mizushima, N. Maeda, K. Fujimoto and T. Ohba, "Comparative study of side-wall roughness effects on leakage currents in throughsilicon via interconnects," 2011 IEEE International 3D Systems Integration Conference (3DIC), 2011 IEEE International, Osaka, 2012, pp. 1-4.

- [33]. A. P. Singulani, H. Ceric, E. Langer and S. Carniello, "Effects of Bosch scallops on metal layer stress of an open Through Silicon Via technology," 2013 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, 2013, pp. CP.2.1-CP.2.5.

- [34]. N. Matsubara, R. Windemuth, H. Mitsuru and H. Atsushi, "Plasma dicing technology," 2012 4th Electronic System-Integration Technology Conference, Amsterdam, Netherlands, 2012, pp. 1-5.

- [35]. A. Podpod et al., "Investigation of Advanced Dicing Technologies for Ultra Low-k and 3D Integration," 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, 2016, pp. 1247-1258.

- [36]. Lishan, David, et al. "Wafer dicing using dry etching on standard tapes and frames." International Symposium on Microelectronics. Vol. 2014. No. 1. International Microelectronics Assembly and Packaging Society, 2014.