# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

High Efficiency Power Amplifier Design Techniques for Advanced Transmitters

#### **Permalink**

https://escholarship.org/uc/item/9h87m964

#### **Author**

Rabet, Bagher

#### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

# High Efficiency Power Amplifier Design Techniques for Advanced Transmitters

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Bagher Rabet

#### Committee in charge:

Professor Peter Asbeck, Chair Professor Gert Cauwenberghs Professor William Hodgkiss Professor Patrick Mercier Professor Gabriel Rebeiz

| The dissertation of Bagher Rabet is approved, and it is acceptable quality and form for publication on microfilm and electronically: | e in |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                      |      |

|                                                                                                                                      |      |

|                                                                                                                                      |      |

|                                                                                                                                      |      |

|                                                                                                                                      |      |

| C                                                                                                                                    | hair |

University of California San Diego

2019

#### TABLE OF CONTENTS

| Signature Pa  | age                                          |                                                                                                                                                               | iii                              |

|---------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Table of Co   | ntents                                       |                                                                                                                                                               | iv                               |

| List of Abbi  | eviation                                     | S                                                                                                                                                             | vi                               |

| List of Figur | res                                          |                                                                                                                                                               | viii                             |

| List of Table | es                                           |                                                                                                                                                               | xi                               |

| Acknowledg    | gements.                                     |                                                                                                                                                               | xii                              |

| Vita          |                                              |                                                                                                                                                               | xiv                              |

| Abstract of   | the Disse                                    | ertation                                                                                                                                                      | xv                               |

| Chapter 1     | 1.1<br>1.2                                   | luction                                                                                                                                                       | 1<br>3                           |

| Chapter 2     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>Acknowled | nasing with Current-Mode Power Amplifiers Introduction / Background Mathematical Analysis Design and Implementation Test Results Conclusion owledgement ences | 7 9 21 24 29 30                  |

| Chapter 3     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>Ackno     | Vave Outphasing Power Amplifier Design Using the Triaxial Balun Introduction                                                                                  | 32<br>33<br>37<br>40<br>42<br>43 |

| Chapter 4     | 4.1<br>4.2                                   | Introduction                                                                                                                                                  | 45<br>47<br>47                   |

|           | 4.2.3 Operation at High Power Region                           | 50            |

|-----------|----------------------------------------------------------------|---------------|

|           | 4.2.4 Systematic AM-AM and AM-PM Variations                    |               |

|           | 4.3 Implementation                                             | 65            |

|           | 4.4 Measurement Results                                        | 69            |

|           | 4.5 Conclusion                                                 | 72            |

|           | Acknowledgement                                                | 73            |

|           | Appendices                                                     | 73            |

|           | I- The Idealized Transistor Model                              | 73            |

|           | II- Derivation of the Systematic AM-PM Equation                | 75            |

|           | References                                                     | 76            |

| Chapter 5 | Gate Leakage Current Effects on the Linearity of CMOS Power Am | plifiers . 78 |

| •         | 5.1 Introduction                                               | _             |

|           | 5.2 Experimental Circuit                                       | 81            |

|           | 5.3 Gate Leakage and Bias Effects                              | 82            |

|           | 5.4 Linearity Measurements                                     |               |

|           | 5.5 Discussion and Conclusion                                  | 88            |

|           | Acknowledgement                                                | 88            |

|           | References                                                     | 89            |

| Chapter 6 | Summary and Future Work                                        | 90            |

| •         | 6.1 Summary                                                    |               |

|           | 6.2 Future Work                                                |               |

#### LIST OF ABBREVIATIONS

AC Alternating Current

ACLR Adjacent Channel Leakage Ratio

ACPR Adjacent Channel Power Ratio

AM-AM Amplitude-to-Amplitude Modulation

AM-PM Amplitude-to-Phase Modulation

Balun Balanced-to-Unbalanced

BiCMOS Bipolar Complementary Metal-Oxide-Semiconductor

BW Bandwidth

CM Common Mode

CMOS Complementary Metal-Oxide-Semiconductor

CW Continuous Wave

DC Direct Current

DM Differential Mode

DPD Digital Predistortion

DUT Device Under Test

EVM Error Vector Magnitude

FET Field Effect Transistor

GND Ground

HBT Heterojunction Bipolar Transistor

IC Integrated Circuit

IM3 3rd Order Intermodulation

IQ In-phase / Quadrature

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

LDMOS Laterally-Diffused Metal-Oxide-Semiconductor

LINC Linear Amplification with Nonlinear Components

mm-Wave Millimeter Wave

NMSE Normalized Mean Squared Error

OFDM Orthogonal Frequency-Division Multiplexing

OPA Outphasing Power Amplifier

P<sub>1dB</sub> 1-dB Compression Power

PA Power Amplifier

PAE Power-Added Efficiency

PAPR Peak-to-Average Power Ratio

PF Power Factor

pHEMT Pseudomorphic High-Electron-Mobility Transistor

Psat Saturated Output Power PSD Power Spectral Density

Q Quality Factor

QAM Quadrature Amplitude Modulation

RF Radio Frequency

SiGe Silicon-Germanium

SILC Single-Input Linear Chireix

SOI Silicon-on-Insulator

TDDB Time-Dependent Dielectric Breakdown

VCCS Voltage-Controlled Current Source

VSWR Voltage Standing Wave Ratio

#### LIST OF FIGURES

| Figure 2.1:  | Voltage-mode Chireix outphasing                                                                                                                                                                                                                                                                      | 9  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2:  | Admittances seen by the unit PAs in conventional Chireix outphasing designs for $B_{CH}R_L$ of (a) 0.6, and (b) 0.8                                                                                                                                                                                  | 11 |

| Figure 2.3:  | Efficiency vs. output power for classical Chireix outphasing in (a) linear scale and (b) log scale.                                                                                                                                                                                                  | 12 |

| Figure 2.4:  | Current-mode Chireix outphasing.                                                                                                                                                                                                                                                                     | 14 |

| Figure 2.5:  | (a) Magnitude and (b) phase variations of the output voltage and current of a unit PA in conventional Chireix outphasing with $B_{CH}R_L = 0.6$                                                                                                                                                      | 14 |

| Figure 2.6:  | $f(x)$ (the second term in Eq. 2.13b) vs $x$ for $B_{CH}R_L = 0.6$ .                                                                                                                                                                                                                                 | 17 |

| Figure 2.7:  | Comparison of the outphasing method with standard (dashed lines) and optimal (solid line) control functions for $B_{CH}R_L$ of 0.6; (a) impedance variations seen by the unit PAs, (b) normalized efficiency, (c) magnitude and (d) phase variations of the output voltage and current of a unit PA. | 19 |

| Figure 2.8:  | Normalized PSD for a 100MHz 64-QAM OFDM signal with 9dB PAPR and the related input signals required for the standard voltage-mode and the optimally controlled current-mode outphasing methods.                                                                                                      | 20 |

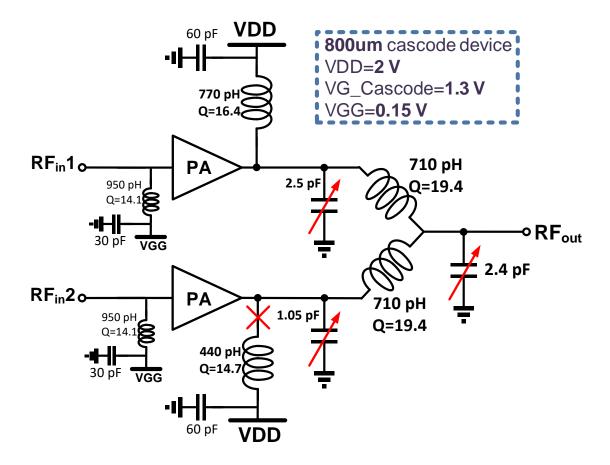

| Figure 2.9:  | Schematic of the 5.5GHz dual-input current-mode outphasing PA implemented in 45nm high-resistivity substrate CMOS-SOI process. The red marks annotate the elements that are laser trimmed after the fabrication to achieve best tuning                                                               | 22 |

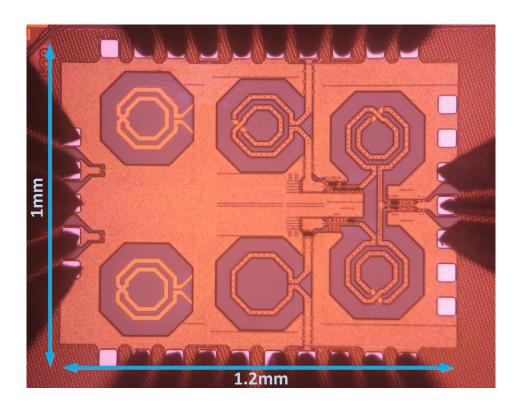

| Figure 2.10: | Die photo of the 5.5GHz dual-input outphasing PA after laser trimming                                                                                                                                                                                                                                | 23 |

| Figure 2.11: | Measurement results of a simultaneous sweep of the input amplitude and outphasing angle $(\theta)$ to find the best control function for the highest efficiency                                                                                                                                      | 24 |

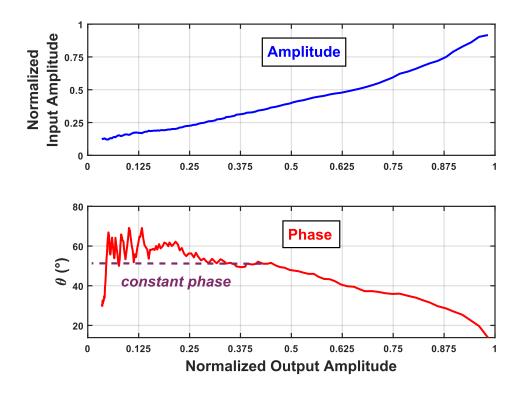

| Figure 2.12: | Optimal control functions for the input amplitude and outphasing angle $(\theta)$ , obtained by the sweep measurement. The noisy part of the phase function at the low power region is replaced by a constant value as shown by the dotted line                                                      | 25 |

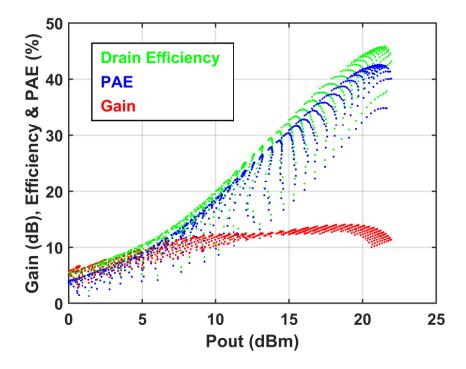

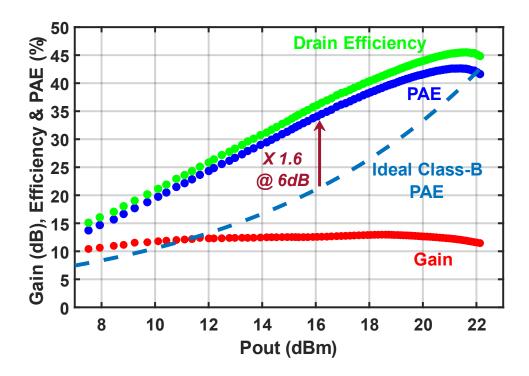

| Figure 2.13: | CW performance measured at 5.5GHz. The gain is defined by $P_{out}/(P_{in1}+P_{in2})$ . At 6-dB power backoff the PAE is improved by 1.6 times compared to an ideal class-B PAE.                                                                                                                     | 26 |

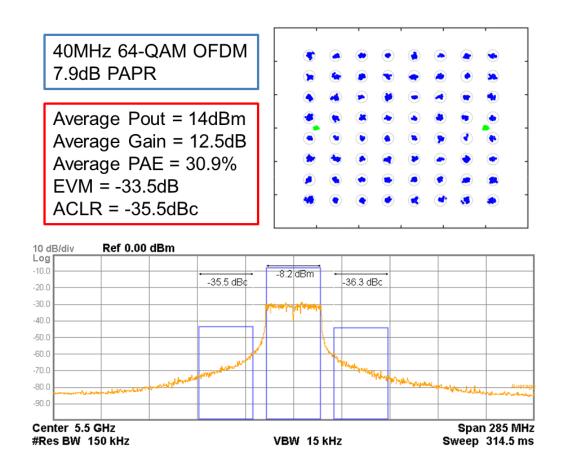

| Figure 2.14: | Modulated signal performance of the PA for a 40MHz 64-QAM OFDM signal with 7.9dB PAPR centered at 5.5GHz                                                                                                                                                                                             | 27 |

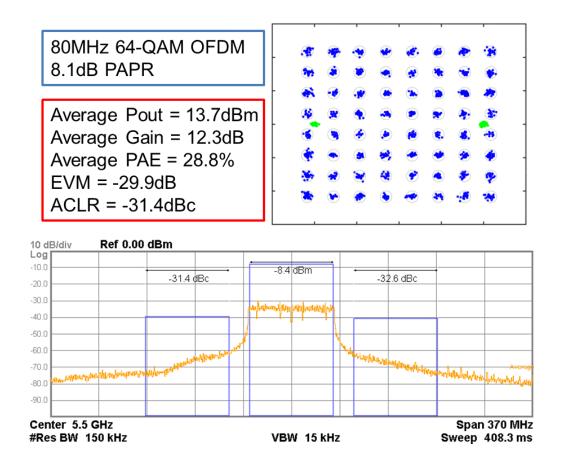

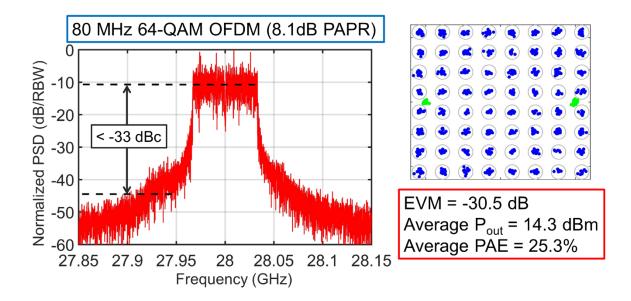

| Figure 2.15: | Modulated signal performance of the PA for an 80MHz 64-QAM OFDM signal with 8.1dB PAPR centered at 5.5GHz                                                                                                                                                                                            | 28 |

| Figure 3.1:  | Triaxial (or coaxial) balun.                                                                                                                                                                                                                                                                                       | 34 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2:  | (a) Equivalent RF model of the triaxial balun, (b) equivalent RF and DC model of the triaxial balun.                                                                                                                                                                                                               | 35 |

| Figure 3.3:  | Proposed triaxial balun outphasing PA                                                                                                                                                                                                                                                                              | 36 |

| Figure 3.4:  | The equivalent model and design criteria for the proposed outphasing PA shown in Fig. 3.3.                                                                                                                                                                                                                         | 36 |

| Figure 3.5:  | (a) Schematic of the HBT PA cell, and (b) post-layout simulation of PAE for $R_L$ sweep.                                                                                                                                                                                                                           | 37 |

| Figure 3.6:  | The implemented triaxial balun in a SiGe IC process.                                                                                                                                                                                                                                                               | 38 |

| Figure 3.7:  | (a) Measured and simulated S-parameters of the fabricated back-to-back balun, and (b) simulation of the resulting load modulation on the PA cells                                                                                                                                                                  | 39 |

| Figure 3.8:  | Die photo.                                                                                                                                                                                                                                                                                                         | 40 |

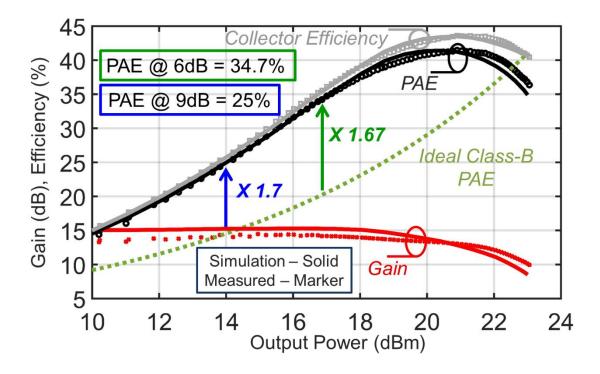

| Figure 3.9:  | CW performance measured at 28GHz. At 6-dB and 9-dB power backoff the PAE is improved by 1.67 and 1.7 times respectively, compared to an ideal class-B PAE.                                                                                                                                                         | 41 |

| Figure 3.10: | Modulated signal performance of the PA for an 80MHz 64-QAM OFDM signal with 8.1dB PAPR centered at 28GHz                                                                                                                                                                                                           | 42 |

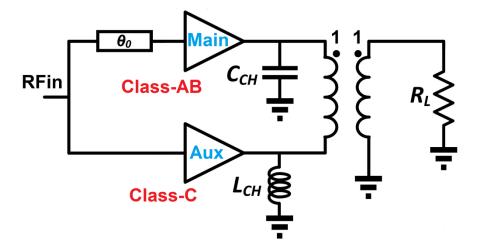

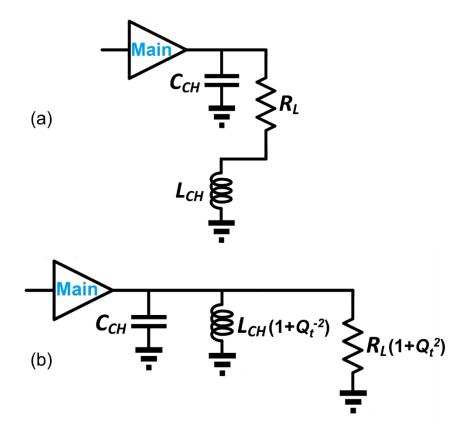

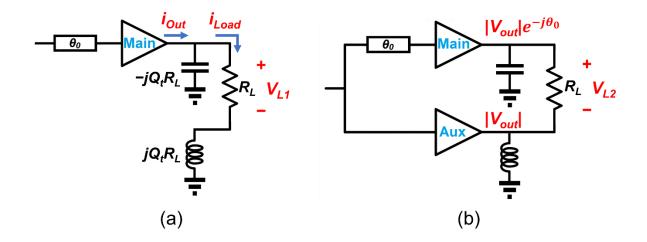

| Figure 4.1:  | Proposed PA architecture with the main and auxiliary PA cells biased in class-AB and Class-C respectively.                                                                                                                                                                                                         | 48 |

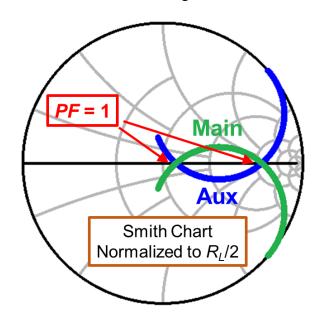

| Figure 4.2:  | Equivalent circuit at low power when the auxiliary amplifier is off: (a) $R_L$ moved to the primary side of the transformer and (b) series to parallel impedance transformation applied.                                                                                                                           | 49 |

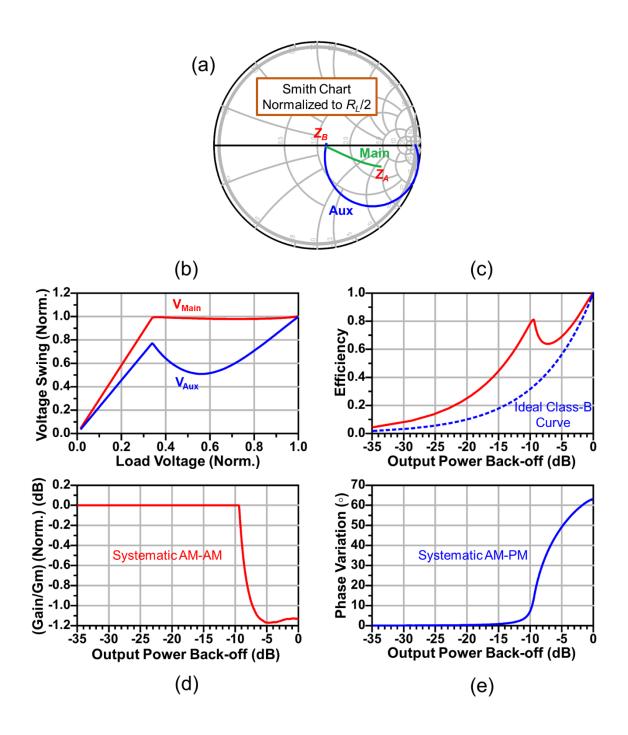

| Figure 4.3:  | Impedance trajectories provided by the Chireix combiner in standard outphasing operation. The high-efficiency points with unity <i>PF</i> are marked                                                                                                                                                               | 51 |

| Figure 4.4:  | Simulation of an example design with a low, purely resistive impedance at peak power, using the idealized transistor model: (a) impedance trajectories seen by the amplifiers, (b) output voltage magnitudes of the amplifiers, (c) normalized overall efficiency, (d) systematic AM-AM, and (e) systematic AM-PM  | 53 |

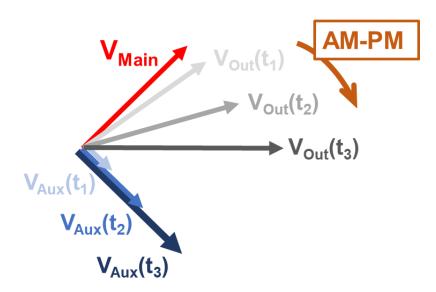

| Figure 4.5:  | Simplified phasor diagram describing the systematic AM-PM of the load voltage in the high power mode of operation.                                                                                                                                                                                                 | 56 |

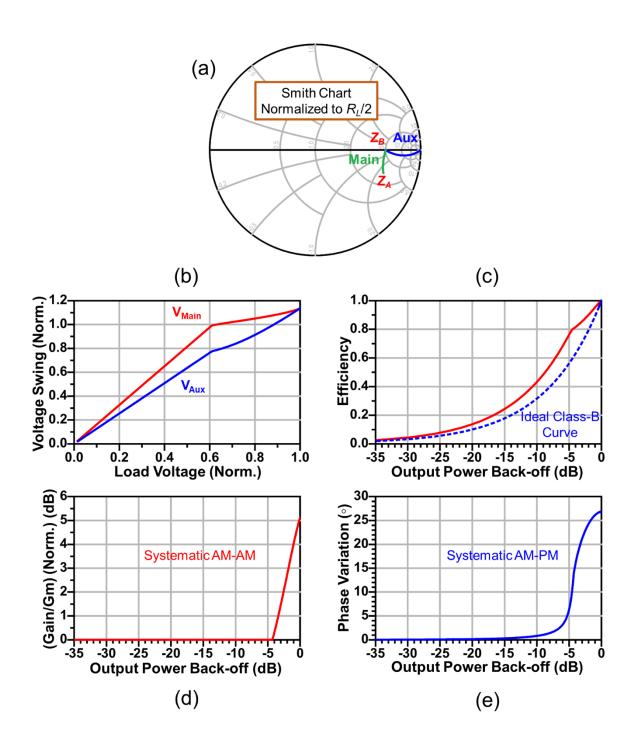

| Figure 4.6:  | Simulation of an example design with a high, purely resistive impedance at peak power, using the idealized transistor model: (a) impedance trajectories seen by the amplifiers, (b) output voltage magnitudes of the amplifiers, (c) normalized overall efficiency, (d) systematic AM-AM, and (e) systematic AM-PM | 59 |

|              |                                                                                                                                                                                                                                                                                                                    |    |

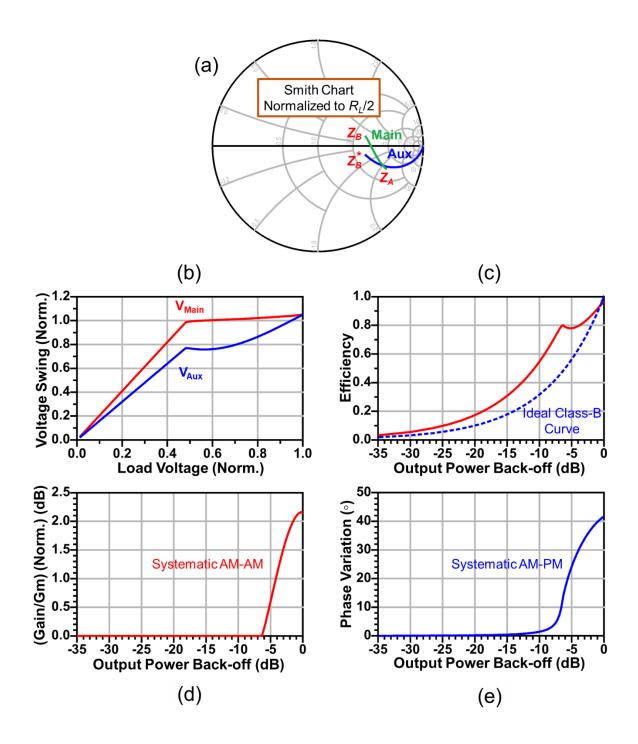

| Figure 4.7:  | Simulation of an example design with 90° phase shift at the input, using the idealized transistor model: (a) impedance trajectories seen by the amplifiers, (b) output voltage magnitudes of the amplifiers, (c) normalized overall efficiency, (d) systematic AM-AM, and (e) systematic AM-PM |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

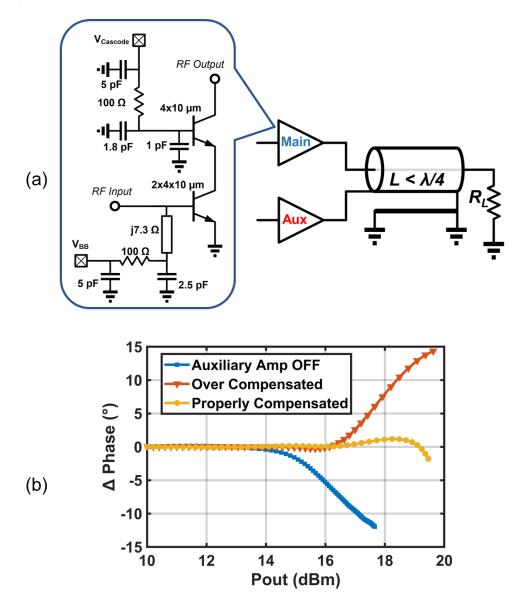

| Figure 4.8:  | (a) Schematic of the core PA (b) Post-layout simulation of the overall AM- PM response at 28GHz65                                                                                                                                                                                              |

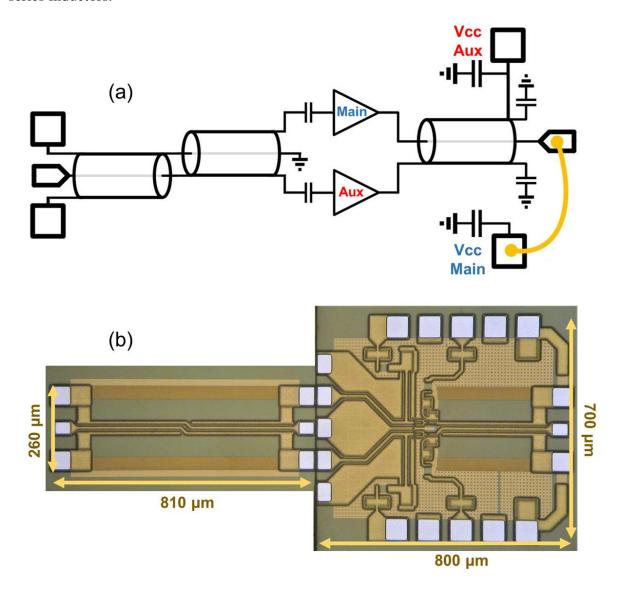

| Figure 4.9:  | (a) Schematic of the overall PA. (b) Die photo (before wirebonding)67                                                                                                                                                                                                                          |

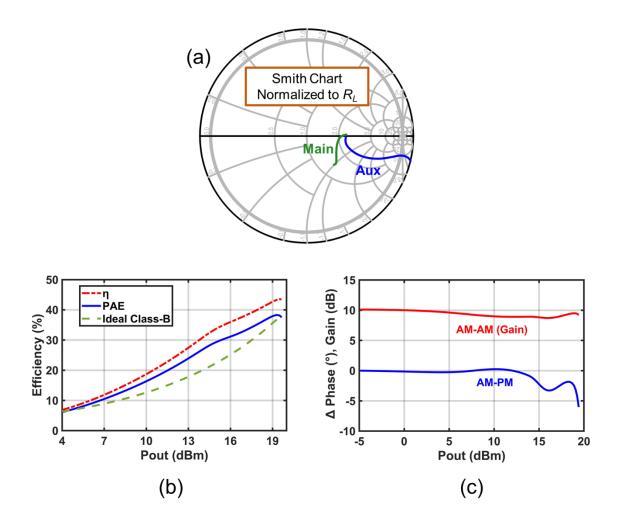

| Figure 4.10: | Full PA post-layout simulation at 28GHz: (a) Trajectories of impedance seen by the internal current sources of the main and auxiliary amplifiers (b) Efficiency, (c) Gain and AM-PM.                                                                                                           |

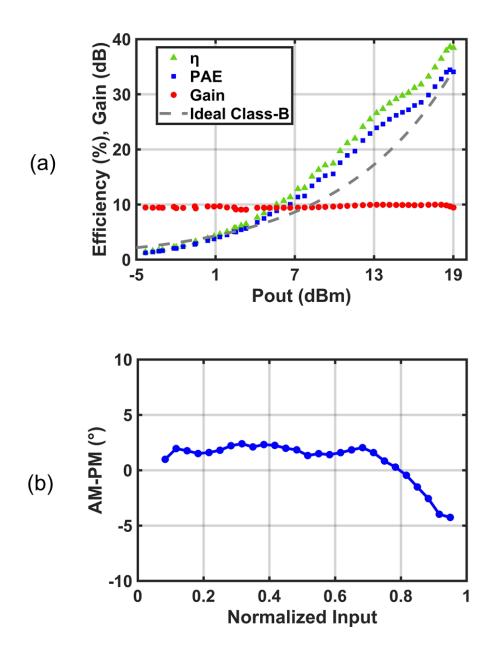

| Figure 4.11: | (a) CW measurement at 27.5GHz showing efficiency and gain (b)AM-PM obtained from the modulated signal measurement under the same bias condition70                                                                                                                                              |

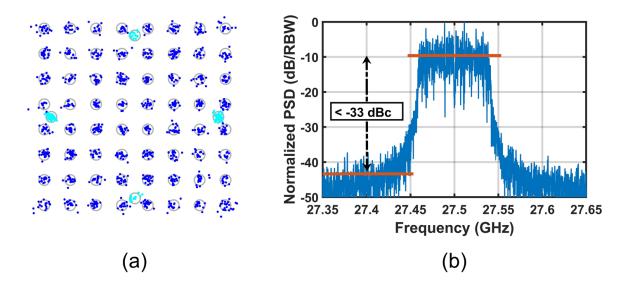

| Figure 4.12: | (a) constellation and (b) spectrum of the PA output for a 100MHz 64-QAM OFDM signal cantered at 27.5GHz with no DPD                                                                                                                                                                            |

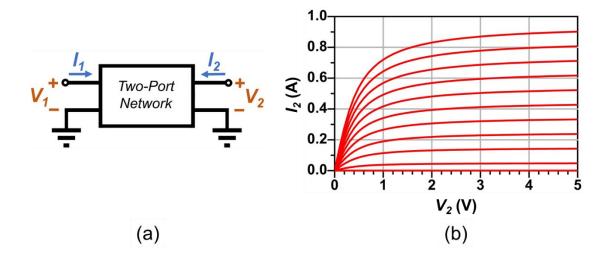

| Figure 4.13: | (a) A generic two port network that is used to create the VCCS transistor model, (b) I-V curves of the model described by (12) with $V_{th}$ =0.5, $gm$ =0.1, and $\alpha$ =2.5 while $V_I$ is swept from 0 to 10V with 1V steps                                                               |

| Figure 4.14: | Equivalent circuits to calculate the phase of the load voltage at (a) low power, and (b) peak power.                                                                                                                                                                                           |

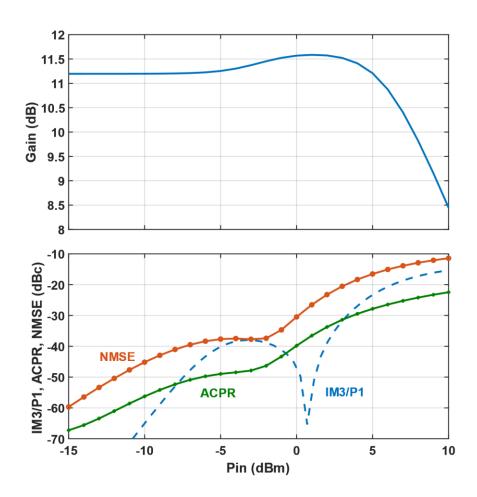

| Figure 5.1:  | Gain vs Pin (CW measurements) and simulated IM3/P1(two-tone), ACPR and NMSE (OFDM) vs Pin average.                                                                                                                                                                                             |

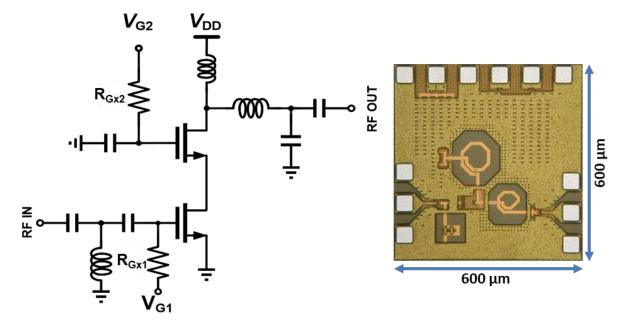

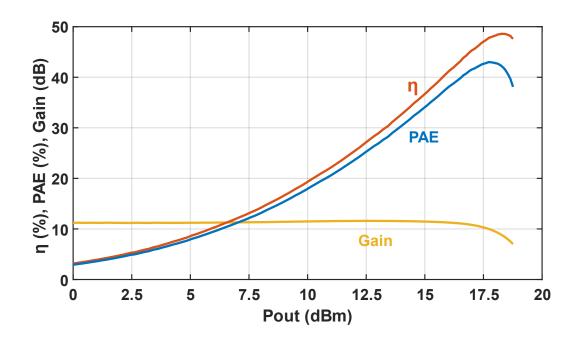

| Figure 5.2:  | Circuit diagram of a 2-stack 28GHz PA, along with chip microphotograph81                                                                                                                                                                                                                       |

| Figure 5.3:  | Measured drain efficiency, PAE and gain vs output power at 28GHz82                                                                                                                                                                                                                             |

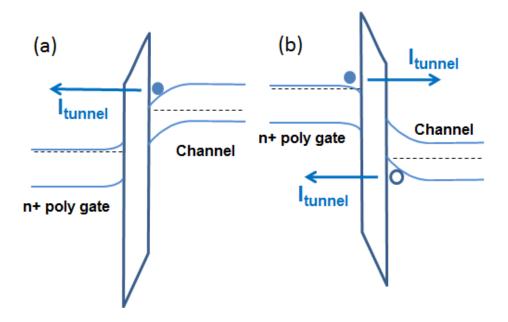

| Figure 5.4:  | Band diagram of FET gate, oxide and channel showing gate leakage paths: (a) near source, for Vgs>0; (b) near drain, for Vgs<0 and Vds>0                                                                                                                                                        |

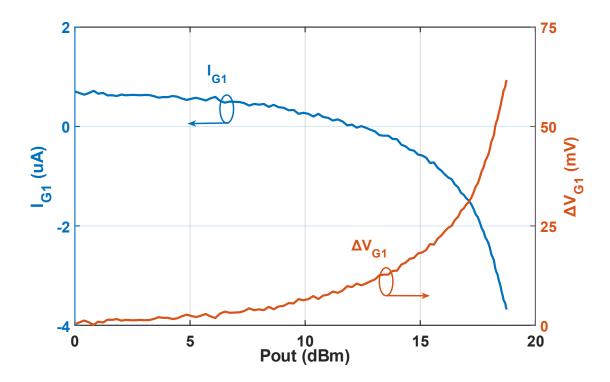

| Figure 5.5:  | Measured gate leakage current $I_{G1}$ vs output power, and calculated $V_{G1}$ bias variation ( $R_{Gx1}$ =14K $\Omega$ ).                                                                                                                                                                    |

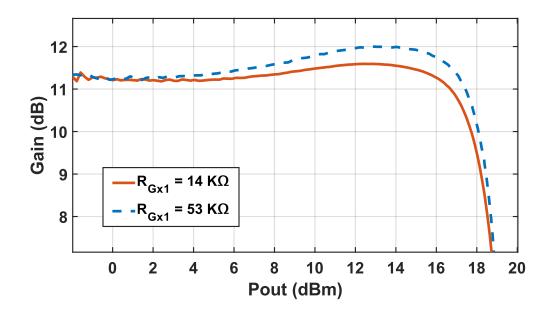

| Figure 5.6:  | Measured gain vs output power using $R_{Gx1}$ =14 (solid line) and 53K $\Omega$ (dashed line)86                                                                                                                                                                                                |

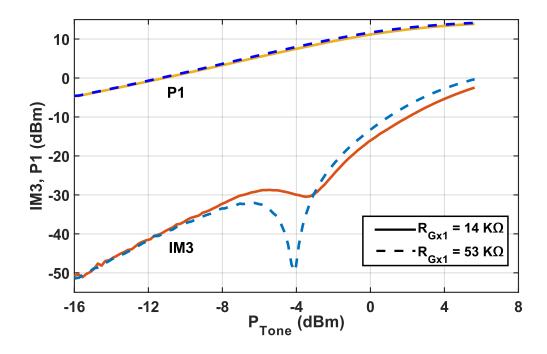

| Figure 5.7:  | Measured IM3 and fundamental output (P1) vs input tone power, using $R_{Gx1}$ =14K $\Omega$ (solid line)86                                                                                                                                                                                     |

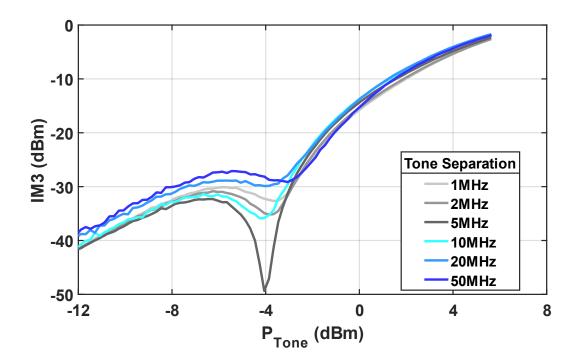

| Figure 5.8:  | IM3 vs input power for tone spacings of 1MHz, 2MHz, 5MHz, 10MHz, 20MHz and 50MHz ( $R_{Gx}=14K\Omega$ )                                                                                                                                                                                        |

#### LIST OF TABLES

| Table 2.1: | Comparison to state of the art. | .29 |

|------------|---------------------------------|-----|

|            | •                               |     |

| Table 3.1: | Comparison to state of the art. | .43 |

|            |                                 |     |

| Table 4.1: | Comparison to state of the art. | .72 |

#### ACKNOWLEDGEMENTS

I would like to first thank the committee members of my dissertation and acknowledge Professor Peter Asbeck for his guidance and support as my PhD advisor. The vast knowledge, intelligence, patience, availability, and willingness of him to help, have made it possible for me to accomplish this work.

I would also like to thank the former High Speed Integrated Circuits and High Speed Device Group members (Mahdi Bagheri, Saeid Daneshgar Asl, Cooper Levy, Po-Han Wang, Kelvin Fang, Wei Wang, Po-Yi Wu, Cheng-Kai Luo, Mohammad Mehrjoo, Tissana Kijsanayotin, Hamed Gheidi, Narek Rostomyan, Jefy Jayamon, Sravya Alluri, Mustafa Özen, Davon Thomas, Hidenori Yamada, ...), our colleagues in the Calit2 circuits labs (Vincent Leung, John Fairbanks, Don Kimball, Mark Stambaugh, ...) and my friends from other groups (Omid Ghadami, Somayeh Imani, and ...), for their mentorship, support, and contributions to my PhD journey.

I'm grateful to the very nice staff members of the UCSD ECE department and Calit2 building, ECE Graduate Student Council, UCSD International Center, Graduate Division, Graduate Housing, Student Health, Transportation Services, Geisel Library, Booksotre, Price Center, Police Department, and many others, for doing their jobs in the best possible way and making it a great experience to be a student here.

Finally, I would like to express special thanks to my family, for their continuous love and encouragement, that due to the circumstances was only possible via long-distance communications.

This dissertation, in part, is based on the following materials.

Chapter 2 is co-authored with H. Gheidi and P. Asbeck. The dissertation author was the primary investigator and author of this chapter.

Chapter 3 is mostly a reprint of the material as it appears in IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2018, Rabet, Bagher; Buckwalter, James. The dissertation author was the primary investigator and author of this paper.

Chapter 4, in full, has been submitted for publication of the material as it may appear in IEEE Journal of Solid-State Circuits, 2019, Rabet, Bagher; Asbeck, Peter. The dissertation author was the primary investigator and author of this paper.

Chapter 5, in full, is a reprint of the material as it appears in the Proceedings of the IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications, 2019, Rabet, Bagher; Rostomyan, Narek; Asbeck, Peter. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2009 | Bachelor of Science, University of Tabriz, Iran          |

|------|----------------------------------------------------------|

| 2012 | Master of Science, University of Tehran, Iran            |

| 2019 | Doctor of Philosophy, University of California San Diego |

#### ABSTRACT OF THE DISSERTATION

# High Efficiency Power Amplifier Design Techniques for Advanced Transmitters

by

#### Bagher Rabet

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2019

Professor Peter M. Asbeck, Chair

The emerging 5G and mm-wave high data rate wireless communication applications have exacerbated the challenges of the PA design, especially for the commercial Si-based ICs. The complex wideband OFDM signals in these applications, with high PAPR, demand stringent PA requirements of linearity, and efficiency at both peak and backoff power levels. This dissertation addresses the design challenges for sub-6GHz and 28GHz CMOS and SiGe integrated PAs, by introducing novel techniques and presenting them with proper

mathematical framework and modeling, alongside the hardware implementations that achieve record results.

Active load modulation, employed in Doherty and Chireix outphasing architectures, is one of the well-known techniques to improve the backoff efficiency of PAs. In theory, outphasing offers a better efficiency profile than Doherty, but it was traditionally believed that it works well only with voltage-mode PAs. However, recently it has been shown that for outphasing with current-mode PAs, if the input drive power reduced at backoff, good results can be achieved. In this dissertation a detailed mathematical analysis for current-mode outphasing is presented, and then the implemented 5.5GHz 45nm CMOS-SOI dual-input outphasing PA is discussed that achieves record average PAE of 30.9% while generating a 40MHz 64-QAM OFDM modulated signal with 7.9dB PAPR and 14dBm average output power.

At 28GHz band, the loss due to the integrated passive elements is one of the bottlenecks to achieve high efficiency. To address this issue a novel Chiriex combiner based on a "triaxial balun" is presented. An equivalent circuit model of the balun is introduced for the first time to make the analysis and design more straight forward. The implemented chip in 130nm SiGe BiCMOS process shows balun loss of only 0.5dB at 28GHz, and the dual-input outphasing PA achieves a record average PAE of 25.3% for an 8.1dB PAPR, 80MHz 64-QAM OFDM signal with average output power of 14.3dBm.

In phased array systems, it is not practical to employ individual digital predistortion (DPD) for each PA unit, and they must be inherently linear. A novel architecture named Single Input Linear Chireix (SILC) PA is introduced that not only has a high backoff efficiency but also has a linear response achieved by correcting the transistor related

distortions using the systematic AM-AM and AM-PM variations. The implemented PA in 130nm SiGe process demonstrates 19dBm saturated output power with 34.4% peak PAE and 6-dB backoff PAE of >23% at 27.5GHz. The modulated signal performance using a 100MHz 64-QAM OFDM signal shows average output power of 11.9dBm with PAE >20%, EVM <5%, and ACLR<-33dBc without using predistortion.

For 28GHz applications that require small footprint, the 2-stack CMOS PAs can offer enough output power with high peak efficiency. In order to improve the linearity, it is desirable to design for a "sweet spot" in the 3rd order intermodulation (IM3) at a critical power, where the distortion is significantly decreased. By adding a large resistor with a proper value at the gate of the transistor, the power dependent leakage current is used to create a dynamic bias that results in a slight amount of gain expansion that counters the gain compression due to the saturation of the PA. Experimental result using a 2-stack 28GHz PA implemented with 45nm CMOS-SOI shows peak output power of 19dBm and 43% PAE, and can attain high linearity without predistortion. Two-tone measurements show the formation of sweet spots at which IM3 decreases on order of 5-10dB at output power levels of order of 5dB backed off from P<sub>1dB</sub>.

# Chapter 1

# Introduction

# 1.1 Background and Motivation

One of the important enablers of our present highly-interconnected society is the broad availability of wireless communication systems that allow the transmission of high data rates using compact devices with low power consumption. To support the further advancement of the wireless system capabilities, including higher data rates and wider signal bandwidths, there is an on-going research effort to move to higher frequencies ranges like the mm-wave regime, and to employ high-order QAM / OFDM signals with high peak-to-average power ratios (PAPR). One of the most significant challenges for the implementation of such systems is the design of the power amplifiers, which are responsible for accurately generating the required high frequency signals to be delivered to the transmitter antennas. The efficiency of power amplifiers typically decreases with increasing frequency, and with backoff from the maximum output power of the amplifier as required for modern complex modulations (whose peak-to-average power ratios are typically in the range of 7 to 10dB). The development of

power amplifier designs which improve efficiency is an important task for the future widespread deployment of 5G wireless systems, both at sub-6GHz frequencies and at mm-wave frequencies (particularly 24, 28 and 39 GHz).

In order to improve efficiency at power backoff, there are a number of architectures that have been exploited in existing 3G and 4G systems. Of these, envelope tracking, outphasing and Doherty amplifiers are the most popular power amplifier designs. Virtually every base-station amplifier in use today employs one of these variants in order to improve the overall transmitter efficiency. One common feature of these techniques, however, is the need for predistortion processing of the input signal in order to obtain a sufficiently accurate output signal (which must linearly replicate the desired signal in order to minimize transmission errors and to avoid producing spurious outputs in neighboring spectral bands). The predistortion in current systems is typically done using digital techniques (Digital Predistortion, DPD). This entails significant costs in power consumption and complexity, which increase as the signal bandwidth increases. For large base-station amplifiers, with output power in the range of 10's of Watts, the cost of the DPD can be absorbed. For future 5G systems, transmitters will be based on antenna arrays, using a multiplicity of power amplifiers (typically 16 to 256), each of which will have correspondingly lower output power than for 4G amplifiers; and each will have wider bandwidths than in use today. As a result, the use of DPD in the future will be significantly constrained, and there is a major effort to develop power amplifiers which do not require external predistortion in order to meet linearity objectives, while at the same time providing high efficiency for signals with high peak-toaverage power backoff.

Another consequence of the fact that the overall power of the transmitter is shared by many power amplifiers, is that the power required of each power amplifier can be relatively modest (often in the range of 10's to 100's of mWs). This allows silicon-based technologies to be potentially used to meet the power amplifier needs. With the dimensional scaling of Si transistors, primarily driven in the past by digital circuit requirements, the speeds of the transistors have increased to the point where they have ample gain in the mm-wave regime. A key remaining concern is the need to improve their output power and efficiency to the point where they can meet 5G transmitter goals.

## 1.2 Dissertation Objective and Contributions

This dissertation addresses the design challenges for sub-6GHz and 28GHz CMOS and SiGe integrated PAs, by introducing novel techniques and presenting them with proper mathematical framework and modeling, alongside hardware implementations that achieve record results.

One of the novel techniques is a derivative of the outphasing amplifier architecture, in which the "voltage-mode" building block amplifiers employed in the conventional outphasing theory are replaced by more realistic current-mode amplifiers. The associated system is analyzed in detail, and an optimal control strategy for the current-mode amplifier inputs is derived, which provides high efficiency and at the same time minimizes input bandwidth requirements. The technique is demonstrated with a 5.5GHz 45nm CMOS-SOI dual-input outphasing PA that achieves record average PAE of 30.9% while generating a 40MHz 64-QAM OFDM modulated signal with 7.9dB PAPR and 14dBm average output power.

Another technique, also a derivative of the outphasing architecture, employs the current-mode outphasing method at mm-wave frequencies, along with a novel Chiriex power combiner based on a triaxial balun, which significantly reduces the losses compared with conventional combiners. The technique is demonstrated with a 28GHz PA in a 130nm SiGe BiCMOS process, which shows a balun loss of only 0.5dB; the dual-input outphasing PA achieves a record average PAE of 25.3% for an 8.1dB PAPR, 80MHz 64-QAM OFDM signal with average output power of 14.3dBm.

In order to avoid the need for DPD, a novel architecture named Single Input Linear Chireix (SILC) PA is introduced that not only has a high backoff efficiency but also has a linear response achieved by correcting the transistor-related distortions using the systematic AM-AM and AM-PM variations from the architecture itself. The implemented PA in 130nm SiGe process demonstrates 19dBm Psat with 34.4% peak PAE and 6-dB backoff PAE of >23% at 27.5GHz. The modulated signal performance using a 100MHz 64-QAM OFDM signal shows average output power of 11.9dBm with PAE >20%, EVM <5%, and ACLR<-33dBc without using predistortion.

An additional technique for linearity improvement is introduced in a 28GHz CMOS PAs using silicon-on-insulator (SOI) technology. It is desirable to design for a "sweet spot" in the 3rd order intermodulation (IM3) at a critical power, where the distortion is significantly decreased. It was shown that by adding a large resistor with a proper value at the gate of the transistor, the power-dependent leakage current can create a dynamic bias that results in a slight amount of gain expansion that counters the gain compression due to the saturation of the PA. With a 2-stack 28GHz PA, peak output power of 19dBm and 43% PAE was obtained; at the same time, two-tone measurements show the formation of sweet spots at

which IM3 decreases on order of 5-10dB at output power levels backed off from  $P_{1dB}$ , as desired for high efficiency high PAPR applications.

### 1.3 Dissertation Organization

This dissertation is organized as follows.

In Chapter 2, after a brief background, a detailed mathematical framework for the outphasing technique is presented. Then the rationale for and analysis of the outphasing architecture using current-mode building block amplifiers and its associated optimal control strategy is presented. The technique is demonstrated with a 5.5GHz 45nm CMOS-SOI dual-input outphasing PA.

Chapter 3 follows the same current-mode outphasing design principle for mm-wave frequencies, where the high insertions loss of the passive networks is a big challenge for achieving high efficiencies. To address this issue, a novel Chireix combiner based on a "triaxial balun" is presented. An equivalent circuit model of the balun is introduced for the first time to make the analysis and design more straight-forward. An implemented chip in 130nm SiGe BiCMOS process is described, which achieves record PAE in backoff.

The linearity aspects of the mm-wave PAs, while maintaining high efficiencies, are addressed in Chapter 4. The Single Input Linear Chireix (SILC) PA architecture is introduced that not only has a high backoff efficiency but also has a linear response achieved by correcting the transistor-related distortions using the systematic AM-AM and AM-PM variations. The technique is demonstrated with a PA implemented in 130nm SiGe technology which demonstrates record PAE for 64-QAM OFDM signals without the use of DPD.

A 2-stack CMOS PA is introduced in Chapter 5 that can offer enough output power with high peak efficiency for the mm-wave applications that require small footprint. In order to improve the linearity, the power-dependent gate leakage current is used to create a dynamic bias that results in a slight amount of gain expansion, forming a "sweet spot" in the 3rd order intermodulation response. Experimental two-tone results using a 28GHz 2-stack PA implemented with 45nm CMOS-SOI demonstrate the formation of sweet spots at which IM3 decreases on order of 5-10dB at output power backoff levels.

# Chapter 2

# Outphasing with Current-Mode Power Amplifiers

## 2.1 Introduction / Background

Outphasing was invented by Henri Chireix around 1935 as an efficiency improvement technique for the AM radio station power amplifiers (PAs) [1], and was employed in RCA's commercially successful *Ampliphase* transmitters from mid-1950s to 1970s [2]. A similar technique was introduced by D. C. Cox in 1974 for a different purpose; Linear Amplification with Nonlinear Components (LINC) [3]. Both methods work based on the same principle; the relative phase between two identical and constant-envelope unit PAs is varied in order to construct the desired signal that is obtained by combining the individual outputs. The difference, however, is in the type of the combiners that are required for each method.

For LINC applications, isolating combiners, like standard Wilkinson, are needed, so that there will be no load-pulling effects between the unit PAs and a highly linear overall response can be obtained. Unfortunately, isolation comes at a cost; all the power that is not sent to the load gets wasted on the isolating resistor, because the unit PAs always generate a constant amount of power. This feature results in a Class-A like efficiency profile, meaning that the efficiency and output power drop with the same rate as the PA goes to backoff. Also, compared to a Class-A (or any other linear mode) PA, the required input signals for a LINC transmitter are subject to a severe bandwidth expansion that is cumbersome. Nevertheless, there are still some advantages in terms of efficiency and linearity to use a LINC architecture instead of a Class-A PA. The first advantage is that LINC makes it possible to modulate signals using highly efficient switching mode PAs (e.g., Class-E, Class-D) that are otherwise hard to backoff. This choice for unit PAs will improve the overall peak efficiency because for instance an ideal Class-D PA is twice as efficient as an ideal Class-A PA. It is also possible to restore some of the power sent to the isolating node, by using a rectifier, in order to further improve the efficiency [4]. The second advantage is more subtle and is related to heating. Class-A PAs get cooler at their peak output power and get hotter at backoff, but in LINC the unit PAs always remain at the same temperature. Therefore, the related memory effects that can degrade the linearity are not present.

For Chireix outphasing, on the other hand, the combiners are non-isolating, and the two unit PAs load-pull each other such that the efficiency improves at backoff. An in-depth analysis of the Chireix outphasing is provided in the next section.

# 2.2 Mathematical Analysis

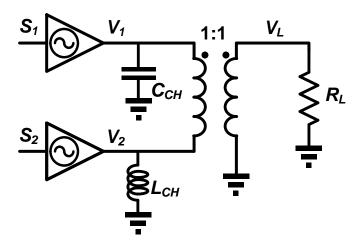

Analysis of the Chireix outphasing scheme is usually done by replacing the unit PA cells with ideal voltage sources [5, 6], as shown in Fig. 2.1.

Figure 2.1: Voltage-mode Chireix outphasing.

The constant-envelope signals generated by these two voltage sources have equal amplitudes and opposite phases  $(V_1 = Ae^{-j\varphi} \text{ and } V_2 = Ae^{+j\varphi})$ , and the load power is controlled by varying  $\varphi$  (outphasing angle) from 90° to 0°, since  $|V_L| = 2A\sin\varphi$ . To find the impedance seen by each PA cell, the "Common Mode (CM) / Differential Mode (DM)" analysis method can be used.

$$V_{CM} = \frac{1}{2}(V_2 + V_1) = A\cos\varphi \tag{2.1a}$$

$$V_{DM} = \frac{1}{2}(V_2 - V_1) = jA \sin \varphi$$

(2.1b)

$$V_1 = V_{CM} - V_{DM} (2.1c)$$

$$V_2 = V_{CM} + V_{DM} (2.1d)$$

For CM excitation, the balun appears as an "open", therefore the CM current flowing into it is zero. For DM excitation, on the other hand, this current is  $2V_{DM}/R_L$ . Thus, the overall impedance at each port, presented by the balun itself (without considering  $L_{CH}$  and  $C_{CH}$ ), can be derived.

$$Z_{1} = \frac{V_{1}}{I_{1}} = \frac{V_{CM} - V_{DM}}{-\frac{2V_{DM}}{R_{L}}} = \frac{R_{L}}{2} \left( 1 - \left( \frac{V_{CM}}{V_{DM}} \right) \right) = \frac{R_{L}}{2} (1 + j \cot \varphi)$$

(2.2a)

$$Z_2 = Z_1^* = \frac{R_L}{2} (1 - j \cot \varphi)$$

(2.2b)

In order to include the effect of Chireix compensating elements, it is easier to first convert the impedances ( $Z_1$  and  $Z_2$ ) to admittances ( $Y_1$  and  $Y_2$ ).

$$Y_1 = \frac{1}{Z_1} = \frac{2}{R_L} \left[ \sin^2 \varphi - j \sin \varphi \cos \varphi \right]$$

(2.3a)

$$Y_2 = Y_1^* = \frac{2}{R_L} [\sin^2 \varphi + j \sin \varphi \cos \varphi]$$

(2.3b)

Then, by adding  $+jB_{CH}$  to  $Y_1$  and  $-jB_{CH}$  to  $Y_2$ ,  $C_{CH}$  and  $L_{CH}$  are taken into account, and the overall admittances seen by the unit PAs  $(Y_1')$  and  $(Y_2')$  are calculated.

$$Y_1' = Y_1 + jB_{CH} = \frac{2}{R_L} \left[ \sin^2 \varphi - j \left( \sin \varphi \cos \varphi - \frac{B_{CH} R_L}{2} \right) \right]$$

(2.4a)

$$Y_2' = {Y_1'}^* = \frac{2}{R_L} \left[ \sin^2 \varphi + j(\sin \varphi \cos \varphi - \frac{B_{CH} R_L}{2}) \right]$$

(2.4b)

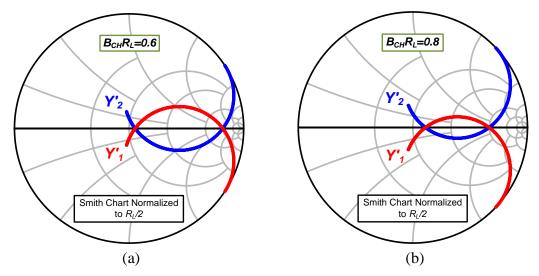

$B_{CH}R_L$  is the design parameter which determines the impedance profile seen by the unit PAs at power backoff. Figure 2.2 shows  $Y_1'$  and  $Y_2'$  on the smith chart for two different  $B_{CH}R_L$  values.

**Figure 2.2**: Admittances seen by the unit PAs in conventional Chireix outphasing designs for  $B_{CH}R_L$  of (a) 0.6, and (b) 0.8.

The two points where the admittance curves on Fig. 2.2 cross each other are associated with the  $\varphi$  values that result in purely resistive load impedances seen by the unit PAs. These values can be found by setting the imaginary part of Eq. 2.4a to zero.

$$\sin \varphi \cos \varphi = \frac{B_{CH}R_L}{2} \implies \sin 2\varphi = B_{CH}R_L$$

(2.5a)

$$\varphi_1 = \frac{1}{2} \sin^{-1} B_{CH} R_L \quad , \quad \varphi_2 = 90^{\circ} - \varphi_1$$

(2.5b)

The real power generated by each unit PA  $(P_{PA})$  can be calculated based on the assumptions made so far. Having a constant voltage amplitude at the outputs of the unit PAs means that  $P_{PA}$  varies only as a function of  $Real\{Y'_{1,2}\}$ .

$$P_{PA} = \frac{1}{2} \times |V_{1,2}|^2 \times Real\{Y'_{1,2}\} = \frac{A^2}{R_L} \sin^2 \varphi = P_{PA,MAX} \sin^2 \varphi$$

(2.6)

Similarly,  $\eta$  for an ideal Class-B PA with constant output amplitude, is only a function of  $Real\{Y'_{1,2}\}$  /  $|Y'_{1,2}|$  which is also known as  $Power\ Factor\ (PF)^1$ .

$$\eta = \eta_{MAX} \frac{Real\{Y'_{1,2}\}}{|Y'_{1,2}|} = \eta_{MAX} \frac{\sin^2 \varphi}{\sqrt{(\sin^2 \varphi)^2 + \left(\sin \varphi \cos \varphi - \frac{B_{CH}R_L}{2}\right)^2}}$$

(2.7)

The relation between  $\eta$  and  $P_{PA}$  is obtained by combining Equations 2.6 and 2.7. As a shorthand notation, we replace " $\sin^2 \varphi$ " with "x".

$$\frac{P_{PA}}{P_{PA,MAX}} = \sin^2 \phi \triangleq x \tag{2.8}$$

$$\eta_{norm} = \frac{\eta}{\eta_{MAX}} = \frac{x}{\sqrt{x^2 + \left(\sqrt{x - x^2} - \frac{B_{CH}R_L}{2}\right)^2}}$$

(2.9)

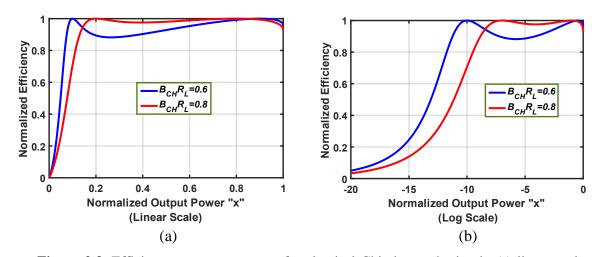

Fig. 2.3 shows  $\eta_{norm}$  plotted vs. x for two different  $B_{CH}R_L$  values.

**Figure 2.3**: Efficiency vs. output power for classical Chireix outphasing in (a) linear scale and (b) log scale.

<sup>1-</sup> With a small approximation, this statement is also correct for an ideal Class-C PA.

The two peak efficiency points on each curve are associated with the two crossing points of  $Y'_1$  and  $Y'_2$  trajectories on the smith chart (Fig. 2.2).

It is important to note that a class-B PA, even a saturated one, does not resemble a voltage source [7], because for a current-mode PA when the load impedance has a varying reactive part (as is the case here), the phase of the output voltage does not follow the input signal. In order to satisfy this condition, voltage-mode PAs (e.g., Class-D) are needed, although they are not available at high frequencies.

The other disadvantages of this approach become apparent at deep backoff power levels where the two full-swing signals at the outputs of the unit PAs need to cancel out each other. Any mismatch between the two paths results in an unwanted signal to leak to the output and cause nonlinearity. Besides, since the input signals ( $S_1$  and  $S_2$  in Fig. 2.1) are also constant envelope, for low output power levels the overall gain is low and the power-added-efficiency (PAE) is degraded.

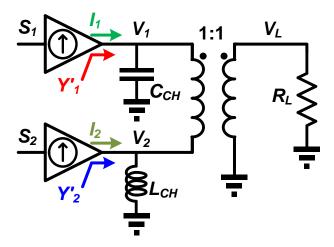

In order to address these issues, "outphasing with current-mode PAs" is proposed. In fact, an ideal Class-B PA can be modeled as a voltage-controlled current source (Gm), and is considered as a current-mode PA. A question arises, however, regarding how the condition of constant voltage envelope should be maintained at the outputs of the unit PA cells such that the outphasing operation is intact. To find the answer, we need to first look at the output currents of the unit PA cells under the ideal outphasing operation condition.  $I_1$  and  $I_2$ , shown in Fig. 2.4, can be calculated by multiplying the required output voltages of the unit PAs  $(V_1$  and  $V_2)$  by the admittances they see  $(Y_1')$  and  $(V_2)$ .

Figure 2.4: Current-mode Chireix outphasing.

$$I_1 = V_1 \times Y_1' = \frac{A}{R_L} [B_{CH} R_L \sin \varphi - j(2 \sin \varphi - B_{CH} R_L \cos \varphi)] = |I_1| e^{-j\theta}$$

(2.10a)

$$I_2 = V_2 \times Y_2' = V_1^* \times Y_1'^* = I_1^* = |I_1|e^{j\theta}$$

(2.10b)

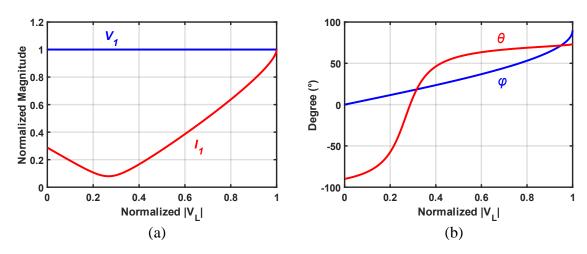

In Fig. 2.5, the normalized magnitudes of  $I_1$  and  $V_1$  and their phases ( $\theta$  and  $\varphi$ ) are plotted vs. normalized  $V_L$ , for a design with  $B_{CH}R_L=0.6$ .

**Figure 2.5**: (a) Magnitude and (b) phase variations of the output voltage and current of a unit PA in conventional Chircix outphasing with  $B_{CH}R_L = 0.6$ .

From these plots it is clear that the magnitude of  $I_1$  (and  $I_2$ ) is not constant, and  $\theta$  is not equal to  $\varphi$  (except at the two crossing points where the impedances seen by the unit PA cells become purely resistive). These details are important because for a Gm cell, it is the output current (not the voltage) that is controlled by the input. Therefore, the PA input signals,  $S_1$  and  $S_2$ , should be chosen based on the required  $I_1$  and  $I_2$ , so that the outphasing condition will be maintained. In an ideal case,  $S_1$  and  $S_2$  would simply be equal to  $I_1$  and  $I_2$  divided by a constant real Gm. In practice however, the nonidealities of the PA cells should be taken into account, meaning that the Gm will no longer be a constant real number.

The relationship between  $\varphi$  and  $\theta$  can be calculated using Eq. 2.10a.

$$-\theta = \tan^{-1}\left(\frac{-2\sin\varphi + B_{CH}R_L\cos\varphi}{B_{CH}R_L\sin\varphi}\right)$$

(2.11a)

$$-\tan\theta = \frac{-2}{B_{CH}R_L} + \cot\varphi \tag{2.11b}$$

$$\tan \theta + \cot \varphi = \frac{2}{B_{CH}R_L} \tag{2.11c}$$

It is interesting to note that, as shown in Fig. 2.5, the required variation for  $\theta$  in order to go from full power down to around 8dB backoff (0.4 normalized  $V_L$ ) is much less than the variation required for  $\varphi$  (27° instead of 67°). This reduction in the required phase variation can be advantageous if analog circuitry is to be used to generate the input signals [8, 9].

Another issue with the canonical outphasing is that  $Y_1'$  and  $Y_2'$ , as depicted in Fig. 2.2, become highly susceptive (reactive) after the second crossing point near the edge of the smith chart, resulting in low PF and thus low efficiency. The fast drop in  $\eta$  at deep power backoff is evident in the plots shown in Fig. 2.3. Also, the unusual increase of  $|I_1|$  (and hence  $I_{DC}$ )

toward low  $V_L$  values (Fig. 2.5) indicates the same fact. Fortunately, this problem can be resolved by employing the current-mode nature of the unit PAs when they are no longer forced to have a constant voltage envelope. To proceed with this idea, it will be useful to include the effect of the output voltage amplitude ( $|V_{1,2}|$ ) in the equations of the efficiency ( $\eta$ ) and power ( $P_{PA}$ ) for the unit PAs.

$$\eta_{norm} = \frac{|V_{1,2}|}{|V_{1,2}|_{max}} \times PF = |V_{1,2}|_{norm} \frac{x}{\sqrt{x^2 + \left(\sqrt{x - x^2} - \frac{B_{CH}R_L}{2}\right)^2}}$$

(2.12)

$$P_{PA,norm} = \frac{P_{PA}}{P_{PA,MAX}} = \left(\frac{|V_{1,2}|}{|V_{1,2}|_{max}}\right)^2 \sin^2 \varphi = |V_{1,2}|_{norm}^2 x$$

(2.13)

Equation 2.13 shows that in addition to outphasing (varying x), reducing the voltage magnitude ( $|V_{1,2}|$ ) can also be used to decrease the output power. Therefore, to avoid the fast drop in PF and  $\eta$  at deep backoff, it is better to stop doing outphasing below a certain power level and instead reduce the voltage magnitude, similar to the way that a standard class-B PA works ("mixed-mode" operation [10-12]). Doing so, the efficiency will drop with a rate proportional to the square root of the output power. To determine the optimal point for switching to "class-B mode", we first re-arrange Eq. 2.13 as  $|V_{1,2}|_{norm} = \sqrt{P_{PA,norm}/x}$ , and accordingly substitute  $|V_{1,2}|_{norm}$  in Eq. 2.12.

$$\eta_{norm} = \sqrt{\frac{P_{PA,norm}}{x}} \times \frac{x}{\sqrt{x^2 + \left(\sqrt{x - x^2} - \frac{B_{CH}R_L}{2}\right)^2}}$$

(2.14a)

$$\eta_{norm} = \sqrt{P_{PA,norm}} \times \sqrt{\frac{x}{x^2 + \left(\sqrt{x - x^2} - \frac{B_{CH}R_L}{2}\right)^2}}$$

(2.14b)

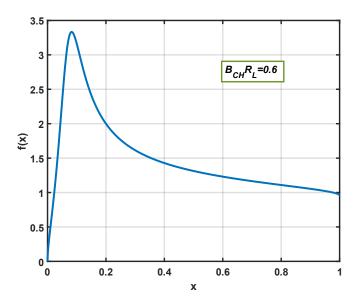

Equation 2.14b shows that, as the output power is reduced from its peak value, no matter by decreasing x (outphasing) or decreasing the voltage magnitude (class-B mode), the  $\sqrt{P_{PA,norm}}$  term pulls down the efficiency with a square root rate. The improvement due to the Chireix outphasing, however, comes from the other term that is a function of x only (f(x)). To have a better understanding, f(x) is plotted in Fig. 2.6, for  $B_{CH}R_L$  of 0.6.

**Figure 2.6**: f(x) (the second term in Eq. 2.13b) vs x for  $B_{CH}R_L = 0.6$ .

It is shown in this plot that as x decreases from 1 toward 0, f(x) increases up to its maximum point, therefore the reduction in  $\eta$  (Eq. 2.14b) due to the first term ( $\sqrt{P_{PA,norm}}$ ) gets compensated and the efficiency remains high. After its maximum point however, f(x) also

starts decreasing in addition to the first term, causing the efficiency to drop fast. Thus, the optimal point to switch to Class-B mode is where f(x) is maximum. This point can be found by setting the derivative of f(x) equal to 0 and solving it for x.

$$\frac{df}{dx} = 0 \implies x_{switch} = \frac{(B_{CH}R_L/2)^2}{1 + (B_{CH}R_L/2)^2}$$

(2.15)

$x_{switch}$  is slightly below the x value associated with the backoff peak efficiency point. For instance, in a case with  $B_{CH}R_L$  of 0.6, the x value of the backoff peak point is equal to  $\sin^2 \varphi_1 = 0.1$  (where  $\varphi_1$  is obtained by Eq. 2.5b), but the  $x_{switch}$  is equal to  $\sim 0.08$ . Also, it is interesting to note that  $x_{switch}$  corresponds to  $\theta = 0^\circ$ , which is obtained by finding  $\cot \varphi_{switch}$  with respect to  $x_{switch}$  and plugging it in Eq. 2.11c.

$$\cot \varphi_{switch} = \sqrt{\frac{1}{\sin^2 \varphi_{switch}} - 1} = \sqrt{\frac{1}{x_{switch}} - 1} = \frac{2}{B_{CH}R_L}$$

(2.16)

$$\tan \theta_{switch} + \cot \varphi_{switch} = \frac{2}{B_{CH}R_L} \Rightarrow \tan \theta_{switch} = 0 \Rightarrow \theta_{switch} = 0^{\circ}$$

(2.17)

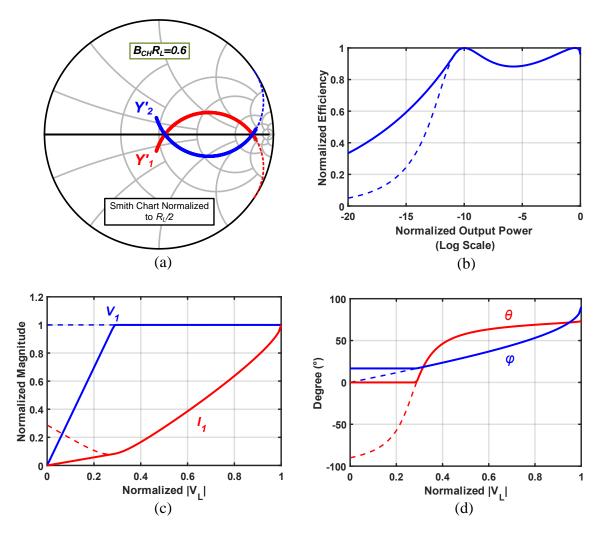

Thus, for optimal control,  $\theta$  needs to be varied from  $\tan^{-1} 2/B_{CH}R_L$ , that is related to the maximum load power ( $\varphi = 90^{\circ}$  in Eq. 2.5b), down to  $0^{\circ}$  which is the switching point to Class-B mode. Figure 2.7 shows the impedance variations, efficiency enhancement and the voltage and current changes under the optimal control condition and compares it to the standard method.

**Figure 2.7**: Comparison of the outphasing method with standard (dashed lines) and optimal (solid line) control functions for  $B_{CH}R_L$  of 0.6; (a) impedance variations seen by the unit PAs, (b) normalized efficiency, (c) magnitude and (d) phase variations of the output voltage and current of a unit PA.

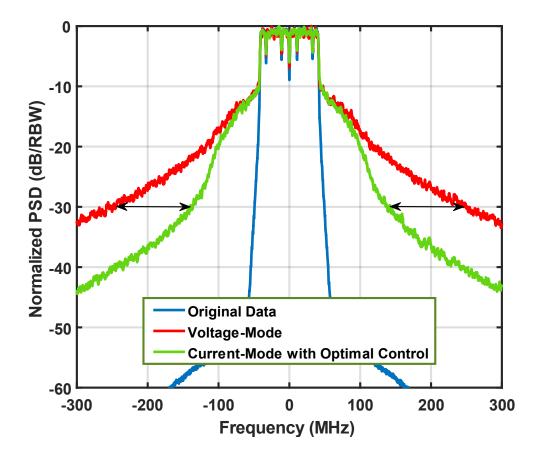

The last and one of the most important issues to discuss about outphasing, is the bandwidth expansion experienced by the input signals due to the required non-linear function of  $\varphi = \sin^{-1}|V_L|_{norm}$ . This problem is usually a major discouragement for the PA designers, preventing them from pursuing outphasing-based designs, especially for the modern applications with wide bandwidth signals. Here, with a simulation-based experiment, we show that for the current-mode outphasing with optimal control the bandwidth expansion is

greatly alleviated compared to the standard method. Figure 2.8 shows the normalized power spectral density (PSD) of a 100MHz 64-QAM OFDM signal with 9dB PAPR and compares it to the spectra of the input signals required in the standard and optimally controlled approaches.

**Figure 2.8**: Normalized PSD for a 100MHz 64-QAM OFDM signal with 9dB PAPR and the related input signals required for the standard voltage-mode and the optimally controlled current-mode outphasing methods.

If we take the -30dB spectrum level as the reference, Fig. 2.8 shows that, compared to the standard outphasing, the bandwidth expansion in the optimally controlled current-mode approach is reduced by more than a factor of 2.

In this section, we reviewed the mathematical framework describing the Chireix outphasing operation for current-mode PAs, and showed that by optimally controlling the input signals, the problems associated with the standard voltage-mode outphasing (e.g., low efficiency, gain, and PAE at deep backoff, sensitivity to path mismatches, operation at high frequencies, and the bandwidth expansion of the input signals) can be resolved. Although similar analyses and conclusions have been published by other authors [11, 12], to the best of our knowledge, the equation describing the relation between the input and output outphasing angles ( $\theta$  and  $\varphi$  in Eq. 2.11c), and the equations showing the optimal point to switch to class-B mode (Eq. 2.15 and 2.17) have been introduced here for the first time. In the next section we will explore a practical implementation of this technique using a CMOS IC process.

### 2.3 Design and Implementation

As a proof of concept, and in order to show the applicability of this technique in IC implementations, we designed a 5.5GHz dual-input current-mode outphasing PA, using a high-resistivity substrate 45nm CMOS-SOI process. Figure 2.9 shows the schematic of this design.

**Figure 2.9**: Schematic of the 5.5GHz dual-input current-mode outphasing PA implemented in 45nm high-resistivity substrate CMOS-SOI process. The red marks annotate the elements that are laser trimmed after the fabrication to achieve best tuning.

Note that we have implemented a common-mode combiner rather than a differential one that was described in the previous section. Two identical cascode cells with gate widths of 800um, Vdd of 2V, top gate bias voltages of 1.3V, and gate bias voltages of 0.15V (class-C) were used as the unit PAs. The high-resistivity substrate option was chosen to achieve a lower insertion loss in the passive elements of the output combiner. It is known that the loss caused by the electric and magnetic couplings from the inductors to the substrate, reduces considerably when it has a high resistivity. However, since this process was new at the time (offered for the first time), and the device models were premature for accurate simulations, we

designed the passive network such that we could tune it post process by laser trimming. This strategy included having segmented capacitive banks that are easy to laser trim, and two inductor options for the DC feed. As shown in Fig. 2.9, eventually the smaller inductor was trimmed out and the Vdd was supplied through the bigger inductor for both unit PAs. Figure 2.10 shows the die photo after the final tunings. The chip measures 1.2mm x 1mm including the RF and DC pads.

Figure 2.10: Die photo of the 5.5GHz dual-input outphasing PA after laser trimming.

#### 2.4 Test Results

The unit PAs were biased in the class-C region, which results in a high efficiency as well as in a nonlinear gain ( $G_m$ ) profile. Thus, the exact theoretical control functions, derived in section 2.2 by assuming a constant gm, are not directly applicable here, although the basics of that analysis hold thoroughly. The best strategy, therefore, is to sweep the two input signals, with equal amplitudes and opposite phases to each other, in order to find the best control function for the highest efficiency. Figure 2.11 shows the results of such a sweep.

**Figure 2.11**: Measurement results of a simultaneous sweep of the input amplitude and outphasing angle  $(\theta)$  to find the best control function for the highest efficiency.

By choosing the highest PAE points for each output power in the plot of Fig. 2.11, the optimal control functions for the input amplitude and phase are obtained. Figure 2.12 shows these functions.

**Figure 2.12**: Optimal control functions for the input amplitude and outphasing angle  $(\theta)$ , obtained by the sweep measurement. The noisy part of the phase function at the low power region is replaced by a constant value as shown by the dotted line.

Note that since we have implemented a common-mode combiner in this design, the curve of  $\theta$  is flipped vertically compared to what was shown in Fig. 2.7. Following the optimal control functions, the static performance of the PA is evaluated be measuring the continuous wave (CW) response, that is shown Fig. 2.13.

**Figure 2.13**: CW performance measured at 5.5GHz. The gain is defined by  $P_{out} / (P_{in1} + P_{in2})$ . At 6-dB power backoff the PAE is improved by 1.6 times compared to an ideal class-B PAE.

At 5.5GHz, the PA achieves 22.1dBm  $P_{sat}$ , 42.6% peak PAE, and 6-dB backoff PAE of 34% that is 1.6 times improvement over the ideal class-B case. The gain for dual input is defined as  $P_{out}/(P_{in1} + P_{in2})$ .

In order to evaluate the dynamic performance of the PA, a 40MHz 64-QAM OFDM signal with 7.9dB PAPR is used. The response was linearized by utilizing a simple memoryless DPD. Also, the whole measurement setup including the PA was equalized. The results are depicted in Fig. 2.14.

**Figure 2.14**: Modulated signal performance of the PA for a 40MHz 64-QAM OFDM signal with 7.9dB PAPR centered at 5.5GHz.

The PA achieves 30.9% average PAE and 14dBm average output power with the EVM better than -33.5dB and ACLR better than -35dBc. Another modulated signal test was run using an 80MHz 64-QAM OFDM signal with 8.1dB PAPR. Similar to the previous test, memoryless DPD and equalization of the setup were utilized. Figure 2.15 shows the results.

**Figure 2.15**: Modulated signal performance of the PA for an 80MHz 64-QAM OFDM signal with 8.1dB PAPR centered at 5.5GHz.

For the 80MHz signal, the PA demonstrates 28.8% average PAE with average  $P_{out}$  of 13.7dBm. The EVM is -29.9dB and the ACLR is better than -31dBc. Table 2.1 summarizes the performance of the PA and compares it to the state of the art.

**Table 2.1**: Comparison to state of the art.

|                        | This work      |         | K | [13] RFIC'16             | [14] ISSCC'15            | [15] JSSC'17    |

|------------------------|----------------|---------|---|--------------------------|--------------------------|-----------------|

| Frequency (GHz)        | 5.5            |         |   | 5.9                      | 3.7                      | 3.5             |

| Technology             | 45nm CMOS      |         |   | 40nm CMOS                | 65nm CMOS                | 45nm CMOS       |

| Architecture           | Outphasing     |         |   | Outphasing               | Class-G / Doh.           | Class-G / Doh.  |

| PA Cell                | Class-C        |         |   | RFDAC / E                | RFDAC / D <sup>-1</sup>  | SC / D          |

| P <sub>SAT</sub> (dBm) | 22.1           |         |   | 22.2                     | 26.7                     | 25.3            |

| Peak PAE (%)           |                | 42.6    |   | 34.9                     | 40.2*                    | 30.4            |

| 6-dB PBO PAE (%)       |                | 34      |   | 19                       | 37*                      | 25.3            |

| Modulation Type        | 64-QAM<br>OFDM |         |   | 64-QAM<br>Single Carrier | 16-QAM<br>Single Carrier | 256-QAM<br>OFDM |

| Signal BW (MHz)        |                | 40 / 80 |   | 20                       | 1                        | 10 / 40         |

| Pre-distortion         | Mem-less DPD   |         |   | Mem-less DPD             | Mem-less Dyn.            | Mem-less DPD    |

| Average Pout (dBm)     | 14 / 13.7      |         |   | 16.4                     | 20.8                     | 17.1 / 15.6     |

| EVM (dB)               | -33.5 / -29.9  |         |   |                          | -24                      | -40.1 / 35.8    |

| Average PAE (%)        | 30.9 / 28.8    |         |   | 16.1                     | 28.8*                    | 21.4 / 19.2     |

<sup>\*</sup> Drain Efficiency

To the best of our knowledge, this work demonstrates the highest reported average efficiency for a CMOS PA in the 5GHz band.

#### 2.5 Conclusion

An in-depth mathematical analysis of the outphasing technique for power amplifier efficiency improvement was presented in this chapter. The short-comings of the standard voltage-mode outphasing were discussed and it was shown that by utilizing current-mode PA cells and optimally controlling them, the backoff gain, efficiency and PAE can be improved, the bandwidth expansion of the input signal can be reduced, and the operating frequency can be extended to the range where voltage-mode PAs cannot be realized. We introduced new

equations describing the relation between the input and output outphasing angles, as well as equations describing the optimal control functions. Next, we demonstrated a CMOS IC implementation of this method for sub-6GHz band with an exceptional performance. The PA achieved 22.1dBm  $P_{sat}$  at 5.5GHz, with 42.6% peak PAE, and 6-dB backoff PAE of 34%. The modulated signal performance showed average efficiencies as high as 30.9% and 28.8% for 64-QAM OFDM signals with 40MHz and 80MHz bandwidth, 7.9dB and 8.1dB PAPR, average output powers of 14dBm and 13.7dBm, and EVMs of -33.5dB and -29.9dB, respectively. To the best of our knowledge, these numbers are record results for a CMOS PA at this frequency band.

#### Acknowledgement

This chapter is co-authored with H. Gheidi and P. Asbeck. The dissertation author was the primary investigator and author of this chapter.

#### References

- [1] H. Chireix, "High power outphasing modulation," *Proc. IRE*, vol. 23, no. 11, pp. 1370–1392, Nov. 1935.

- [2] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, Cambridge, U.K.: Cambridge Univ. Press, 2003.

- [3] D. C. Cox, "Linear amplification with nonlinear components", *IEEE Trans. Commun.*, vol. COM-22, no. 12, pp. 1942-1945, Dec. 1974.

- [4] X. Zhang, L. E. Larson, P. M. Asbeck, R. A. Langridge, "Analysis of power recycling techniques for RF and microwave outphasing power amplifiers", *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 312-320, May 2002.

- [5] S. C. Cripps, *RF Power Amplifiers for Wireless Communications*, Norwood, MA, USA: Artech House, 1999.

- [6] F. Raab, "Efficiency of outphasing RF power-amplifier systems", *IEEE Trans. Commun.*, vol. COM-33, no. 10, pp. 1094-1099, Oct. 1985.

- [7] J. Yao, S. Long, "Power amplifier selection for LINC applications", *IEEE Trans. Circuits Syst. II Exp. Briefs*, vol. 53, no. 8, pp. 763-767, Aug. 2006.

- [8] T. Barton, D. Perreault, "An RF-input outphasing power amplifier with RF signal decomposition network", *Proc. IEEE MTT-S Int. Microw. Symp. (IMS)*, pp. 1-4, 2015–May.

- [9] H. Jang, R. Wilson, T. Canning, D. Seebacher, C. Schuberth, B. Arigong, F. Trang, and S. Ward, "RF-input self-outphasing Doherty-Chireix combined amplifier" *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4518–4534, Dec. 2016.

- [10] W. Gerhard and R. Knoechel, "Improved design of outphasing power amplifier combiners," *in Proc. German Microw. Conf.*, Mar. 2009, pp.1–4.

- [11] Jawad H Qureshi, Marco J Pelk, Mauro Marchetti, WC Edmund Neo, John R Gajadharsing, Mark P van der Heijden, LCN de Vreede, "A 90-W peak power GaN outphasing amplifier with optimum input signal conditioning", *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 8, pp. 1925-1935, Aug. 2009.

- [12] D. Calvillo-Cortes and L. de Vreede, "Analysis of pure- and mixed-mode class-B outphasing amplifiers," in Proc. IEEE Latin American Symp. Circuits and Systems, 2014, pp. 1–4.

- [13] Z. Hu, L. C. N. de Vreede, M. S. Alavi, D. A. Calvillo-Cortes, R. B. Staszewski, S. He, "A 5.9 GHz RFDAC-based outphasing power amplifier in 40-nm CMOS with 49.2% efficiency and 22.2 dBm power", *Proc. IEEE Radio Freq. Integr. Circuits Symp.* (*RFIC*), pp. 206-209, May 2016.

- [14] S. Hu, S. Kousai, H. Wang, "A broadband CMOS digital power amplifier with hybrid Class-G Doherty efficiency enhancement", *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 1-3, Feb. 2015.

- [15] V. Vorapipat, C. S. Levy, P. M. Asbeck, "A class-G voltage-mode Doherty power amplifier", *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3348-3360, Dec. 2017.

## **Chapter 3**

# mm-Wave Outphasing Power Amplifier Design Using the Triaxial Balun

#### 3.1 Introduction

Gigabit-per-second millimeter-wave (mm-wave) access and backhaul networks at 28GHz demand high-order QAM, OFDM, and/or carrier-aggregated waveforms that force the PA to operate under high peak-to-average power ratio (PAPR) [1]. High PAPR requirements aggravate the design of mm-wave Si CMOS and SiGe BiCMOS PAs since a linear response and high efficiency are simultaneously desired. Recent work has demonstrated mm-wave PAs with peak efficiency exceeding 30% at 28GHz for output powers above 20dBm [1-5]. However, high average efficiency associated with high-PAPR waveforms remains elusive. To improve average efficiency, circuit techniques based on Doherty [3] and outphasing [6] have been demonstrated in mm-wave bands. Earlier work using these techniques showed average efficiency with QAM waveforms that is well under 20%.

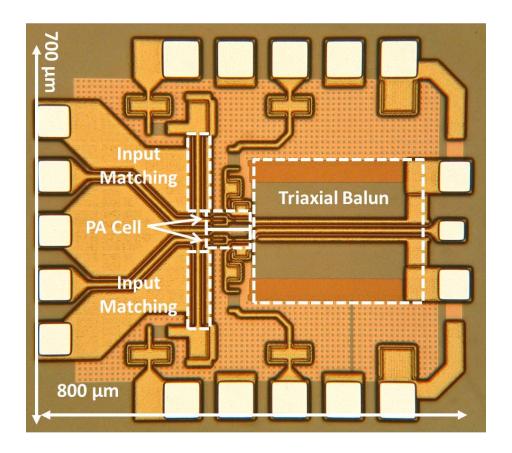

In this chapter, we present a SiGe BiCMOS outphasing power amplifier (OPA) with substantially better performance due to an extremely low-loss power combiner that realizes both excellent peak power-added-efficiency (PAE) of 41% and average PAE of 25.3% for an 8.1dB-PAPR signal at 28GHz. The power combiner is based on a compact triaxial balun structure that simultaneously generates the Chireix compensating reactances at the output ports of the PAs for load modulation and combines the RF power with low loss.

In the conventional Chireix OPA, as discussed in the previous chapter, the PAs drive the combiner with constant-envelope signals separated by an outphasing angle  $(\pm \varphi)$ . The load seen by each PA is modulated through a non-isolating power combiner, along with the opposite-signed Chireix reactances  $(\pm jX_{CH})$  at each of the combiner ports. Previous work investigated the Chireix OPA in mm-wave bands with limited success to realize high average efficiency [6]. Two significant challenges exist for CMOS/BiCMOS PAs in mm-wave bands. First, high losses in the on-chip power combiners significantly reduce the gain, output power, and any theoretical average efficiency improvement. Second, the typical OPA requires a voltage-mode PA that is difficult to realize at mm-wave frequencies due to the relative admittance presented by device parasitics.

#### 3.2 Triaxial Balun as the Chireix Combiner

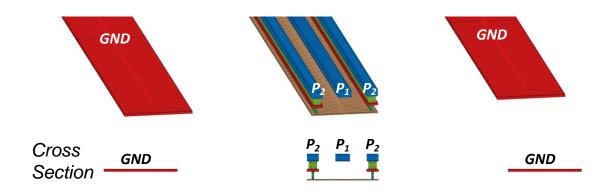

The triaxial balun is conceptually illustrated in Fig. 3.1.

Figure 3.1: Triaxial (or coaxial) balun.

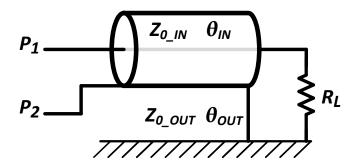

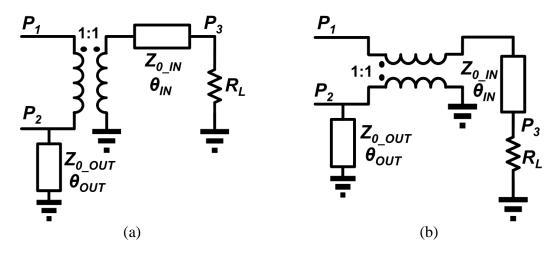

This passive structure, originally known as the coaxial balun, consists of two conductors connected to the input ports ( $P_1$  and  $P_2$ ) and a ground plane that serves as a return path for the load current. In our design, since we explicitly implement the ground plane with a third conductor, we refer to the structure as the triaxial balun. There are two transmission lines in this balun, one formed between the conductors of  $P_1$  and  $P_2$  with the characteristics of  $Z_{0\_IN}$  and  $\theta_{IN}$ , and the other one formed between the conductor of  $P_2$  and the ground plane with the characteristics of  $Z_{0\_OUT}$  and  $\theta_{OUT}$ , although the conductor connected to  $P_1$  is shielded from the ground plane and there is no transmission line formed between them. Figure 3.2a shows the proposed equivalent RF model of the triaxial balun.

**Figure 3.2**: (a) Equivalent RF model of the triaxial balun, (b) equivalent RF and DC model of the triaxial balun.

This model captures the RF behavior precisely, but slight adjustments are needed to capture the DC behavior. Alternately, the model shown in Fig 3.2b captures both the DC and RF behaviors; for simplicity however we continue to use the first model throughout this chapter.

In a standard application [7] the inner transmission line needs to provide matching to the load impedance ( $Z_{0\_IN} = R_L$ ), while the outer transmission line, which appears as a shorted stub on  $P_2$ , needs to provide a high impedance in order to not create imbalance between the ports. Therefore, the length of the balun should be  $\lambda/4$ , so that the outer shorted stub provides an open. In our application the situation is different, we inherently need the imbalance in order to make a Chireix combiner, thus the balun can be shorter than  $\lambda/4$ .

The proposed OPA is shown in Fig. 3.3.

Figure 3.3: Proposed triaxial balun outphasing PA.

It replaces the conventional Chireix combiner with a triaxial balun that combines the outputs of the two PAs while inherently producing the compensating reactances and providing impedance match to the load with low loss. The impedances produced by the triaxial balun can be related to the design of the Chireix outphasing scheme as shown in Fig. 3.4.

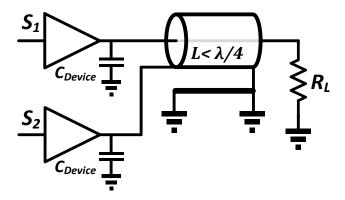

**Figure 3.4**: The equivalent model and design criteria for the proposed outphasing PA shown in Fig. 3.3.

The PA cell's output capacitance ( $C_{Device}$ ) is absorbed into the Chireix network while the length of the balun is chosen to produce the desired shunt inductance on one of the PA

outputs. Thus, a relatively short length, e.g.  $l \approx \lambda/15$ , transmission line is required for the outphasing combiner, resulting in low loss.

### 3.3 Design and Implementation

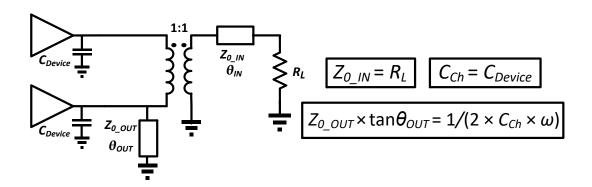

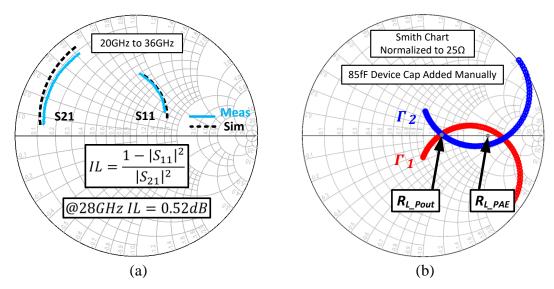

The PA cell is illustrated in Fig. 3.5a based on a  $0.13\mu m$  SiGe HBT cascode where the output capacitance is roughly 85fF.

**Figure 3.5**: (a) Schematic of the HBT PA cell, and (b) post-layout simulation of PAE for  $R_L$  sweep.

The cascode base is biased with low impedance to sweep out the carriers generated from impact ionization, thereby improving the breakdown for increased output power. The transistor emitter lengths are sized to create a loadline impedance that optimizes the efficiency and output power over the range of impedances seen by the triaxial balun (Fig. 3.5b). The PA cell produces 20.5dBm and a maximum PAE of 47% based on post-layout simulation.

In Fig. 3.6, the triaxial balun, as implemented in a planar integrated circuit process, is shown.

Figure 3.6: The implemented triaxial balun in a SiGe IC process.

$P_1$  is the central conductor while  $P_2$  is the shield around  $P_1$  to form a microstrip structure, and the return path is through the ground conductor on either side of  $P_2$ . A fabricated back-to-back test structure indicates that the measured insertion loss of the combiner is 0.52dB and is close to the simulated value of 0.35dB around 28GHz (Fig 3.7a).

**Figure 3.7**: (a) Measured and simulated S-parameters of the fabricated back-to-back balun, and (b) simulation of the resulting load modulation on the PA cells.

Furthermore, Fig. 3.7b shows the impedances seen at  $P_1$  and  $P_2$  as a function of outphasing angle, which matches the canonical outphasing load modulation. The loads corresponding to the PA cell's peak output power and efficiency, denoted  $R_{L\_Pout}$  and  $R_{L\_PAE}$ , are traversed by the outphasing impedance trajectories.