## **UCLA**

### **UCLA Electronic Theses and Dissertations**

### **Title**

'Junction-Level' Heterogeneous Integration of III-V Materials with Si CMOS for Novel Asymmetric Field-Effect Transistors

### **Permalink**

https://escholarship.org/uc/item/9dj779rv

### **Author**

Chang, Yoon Jung

### **Publication Date**

2016

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

'Junction-Level' Heterogeneous Integration of III-V Materials with Si CMOS for Novel Asymmetric Field-Effect Transistors

A dissertation submitted in partial satisfaction of the requirement for the degree Doctor of Philosophy in Electrical Engineering

by

Yoon Jung Chang

© Copyright by

Yoon Jung Chang

#### ABSTRACT OF THE DISSERTATION

'Junction-Level' Heterogeneous Integration of III-V Materials with Si CMOS for Novel Asymmetric Field-Effect Transistors

by

## Yoon Jung Chang

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2016

Professor Jason C.S. Woo, Chair

Driven by Moore's law, semiconductor chips have become faster, denser and cheaper through aggressive dimension scaling. The continued scaling not only led to dramatic performance improvements in digital logic applications but also in mixed-mode and/or communication applications. Moreover, size/weight/power (SWAP) restrictions on all high-performance system components have resulted in multi-functional integration of multiple integrated circuits (ICs)/dies in 3D packages/ICs by various system-level approaches. However, these approaches still possess shortcomings and in order to truly benefit from the most advanced digital technologies, the future high-speed/high power devices for communication applications need to be fully integrated into a single CMOS chip. Due to limitations in Si device performance in high-frequency/power applications as well as expensive III-V compound semiconductor devices with low integration density, heterogeneous integration of compound semiconductor materials/devices with Si CMOS platform has emerged as a viable solution to low-cost high-performance ICs.

In this study, we first discuss on channel and drain engineering approaches in the state-of-the-art multiple-gate field-effect transistor to integrate III-V compound semiconductor materials with Si CMOS for improved device performance in mixed-mode and/or communication applications. Then, growth, characterization and electrical analysis on small-area (diameter < 100nm) complete selective-area epitaxy of GaAs/GaN will be demonstrated for achieving 'dislocation-free' III-V compound semiconductor film on a Si(001) substrate. Based on a success in dislocation-free heterogeneous III-V film growth, we propose a novel ultra-scaled 'junction-level' heterogeneous integration onto mainstream Si CMOS platform. Device architecture and its key features to overcome aforementioned challenges will be given to demonstrate the potential to improve the overall system performance with diverse functionality.

The dissertation of Yoon Jung Chang is approved.

Mark S. Goorsky

Subramanian Srikantes Iyer

Robert N. Candler

Jason C.S. Woo, Committee Chair

University of California, Los Angeles

2016

To God the Father, my dearest parents and my younger brother

## **Contents**

| 1. Introduction                                                            | 1            |

|----------------------------------------------------------------------------|--------------|

| 1.1 Overview                                                               | 1            |

| 1.2 Motivation and Objectives                                              | 2            |

| 1.3 Organization                                                           | 6            |

| 1.4 Bibliography                                                           | 7            |

| 2. Nanoscale MOSFET for Low-Power Analog/RF SoC Applications               | 15           |

| 2.1 Introduction                                                           | 15           |

| 2.2 Three-dimensional Multiple-Gate Si MOSFET                              | 18           |

| 2.2.1 SOI Vertical DG and Planar TG in Analog/RF/mixed-signal Applications | s18          |

| 2.2.2 Impact of Process Variation in Fin Shape on SOI TG Performance       | 25           |

| 2.3 Asymmetric Graded-Channel III-V MOSFET                                 | 34           |

| 2.4 Summary                                                                | 49           |

| 2.5 Bibliography                                                           | 51           |

| 3. Wide Bandgap Drain Heterogeneous MOSFET for High-Power RF SoC App       | plications61 |

| 3.1 Introduction                                                           | 61           |

| 3.2 Device Concept and Structure                                           | 63           |

| 3.3 Simulation Setup                                                       | 64           |

| 3.4 Optimization of Device Parameters                                      | 67           |

| 3.5 Summary                                                                | 84           |

| 3.6 Bibliography                                                           | 85           |

| 4. Selective-Area MBE Growth of GaAs/GaN Nanostubs                         | 86           |

| 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Intro                                   | duction                                                                                                 | 86                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 Back                                  | ground                                                                                                  | 87                                         |

| 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 Aspe                                  | ect-Ratio Trapping (ART)                                                                                | 89                                         |

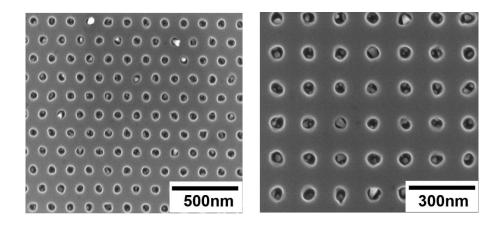

| 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4 Subs                                  | trate Nano-patterning on Bulk Si(001) Substrate                                                         | 91                                         |

| 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 MBE                                   | E Film Growth                                                                                           | 94                                         |

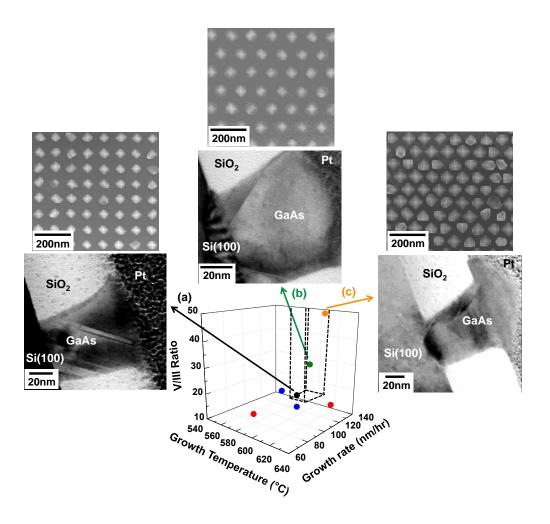

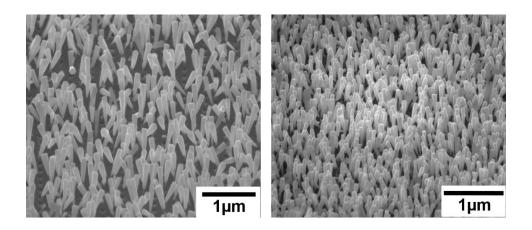

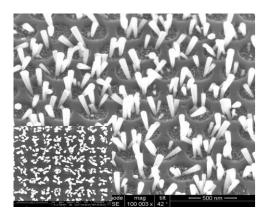

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5.1                                   | Selective-Area <i>n</i> -GaAs Buffer Growth                                                             | 94                                         |

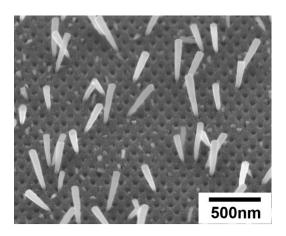

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5.2                                   | Selective-Area <i>n</i> -GaN Growth                                                                     | 101                                        |

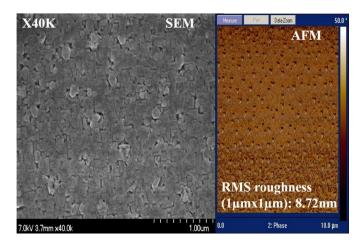

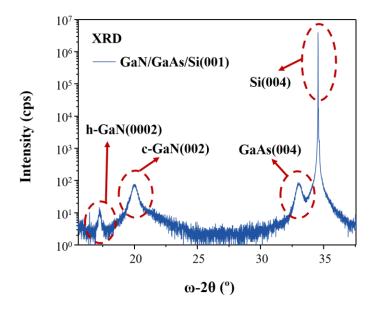

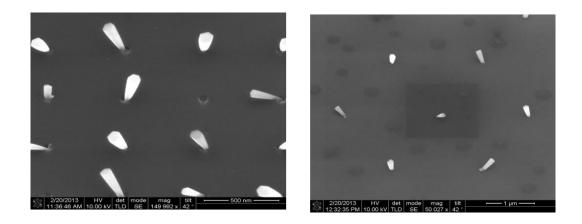

| 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6 MBE                                   | E Film Characterization                                                                                 | 115                                        |

| 4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7 Sum                                   | mary                                                                                                    | .120                                       |

| 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bibli                                   | ography                                                                                                 | 121                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                         |                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fabric                                  | ation of GaAs/Si Heterogeneous PN Diodes                                                                | 135                                        |

| <b>5.</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                         |                                            |

| <b>5. 1</b> 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Intro                                   | ation of GaAs/Si Heterogeneous PN Diodes                                                                | .135                                       |

| 5. 1<br>5.1<br>5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Intro                                   | ation of GaAs/Si Heterogeneous PN Diodesduction                                                         | .135<br>136                                |

| 5.1<br>5.2<br>5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Intro Proces Expe                       | ation of GaAs/Si Heterogeneous PN Diodesductioness Flow                                                 | .135<br>136<br>.137                        |

| 5. 1<br>5.1<br>5.2<br>5.3<br>5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Intro Proces Expe                       | ation of GaAs/Si Heterogeneous PN Diodes                                                                | 135<br>136<br>137                          |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Intro Proces Expe Devi Sum              | ation of GaAs/Si Heterogeneous PN Diodes                                                                | 135<br>136<br>137                          |

| 5.1 5.2 5.2 5.2 5.2 5.2 5.2 5.2 5.2 5.2 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Intro Proces Expe Devi Sum Bibli        | ation of GaAs/Si Heterogeneous PN Diodes                                                                | .135<br>136<br>.137<br>.138<br>.144        |

| 5.1 5.2 5.3 5.4 5.5 6. (Control of the control of t | Intro Proces Expe Devi Sum Bibli Conclu | ation of GaAs/Si Heterogeneous PN Diodes.  duction ess Flow erimental Setup ce Performance mary ography | .135<br>136<br>.137<br>.138<br>.144<br>145 |

# **List of Figures**

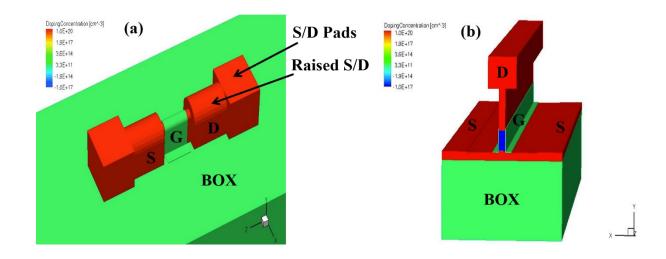

| Fig 2.1 Schematic diagrams of fully-depleted SOI n-channel (a) TG and (b) DG MISFET                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------|

| structures                                                                                                                            |

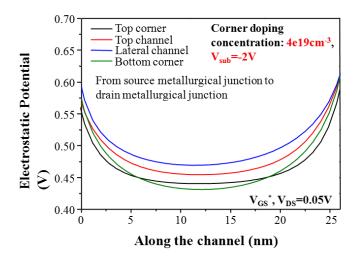

| Fig 2.2 Electrostatic potential distribution along the channel at virtual cathode point in fully-                                     |

| depleted SOI <i>n</i> -channel planar TG MOSFET21                                                                                     |

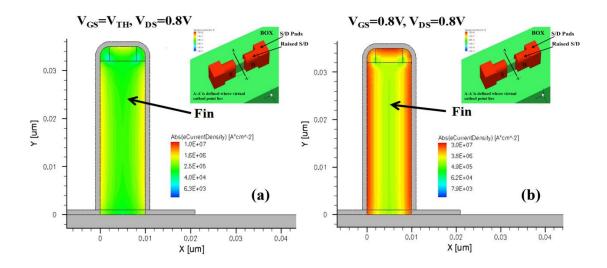

| Fig 2.3 Schematic diagrams of electron current density in fully-depleted SOI <i>n</i> -channel planar TG                              |

| MOSFET cut along fin-width direction (A-A') at (a) $V_{GS}=V_{TH}$ , $V_{DS}=0.8~V$ ; (b) $V_{GS}=V_{DD}$ , $V_{DS}=0.8~V$            |

| V22                                                                                                                                   |

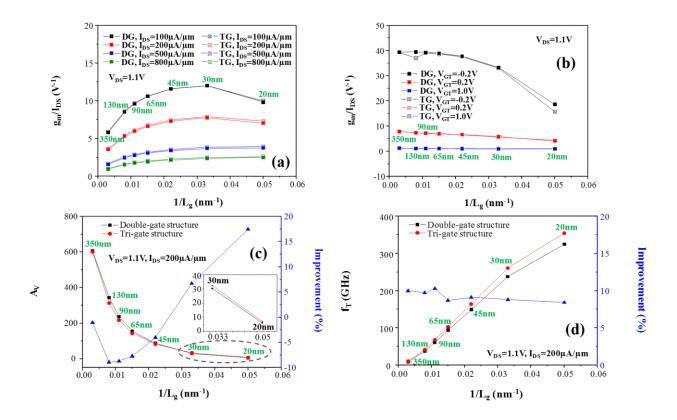

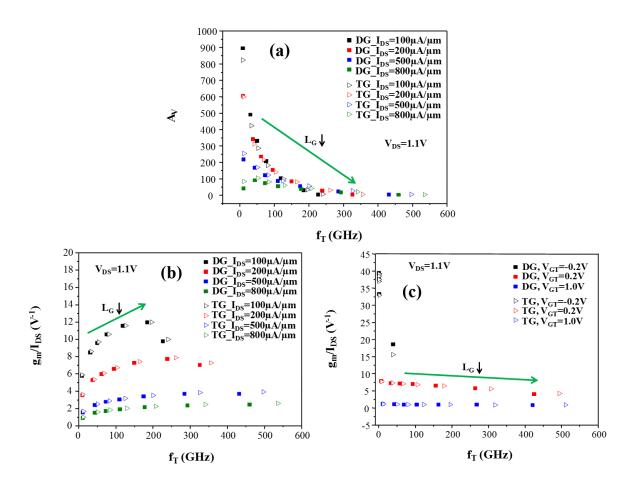

| Fig 2.4 Plots of (a) $g_m/I_{DS}$ ratio at fixed $I_{DS}$ ; (b) $g_m/I_{DS}$ ratio at fixed $V_{GT}$ ; (c) intrinsic gain $(A_V)$ at  |

| fixed $I_{DS}$ ; (d) cutoff frequency ( $f_T$ ) at fixed $I_{DS}$ for vertical DG and planar TG device                                |

| structures                                                                                                                            |

| Fig 2.5 Plots of (a) $A_V$ vs. $f_T$ trade-off at fixed $I_{DS}$ ; (b) $g_m/I_{DS}$ ratio vs. $f_T$ trade-off at fixed $I_{DS}$ ; (c) |

| $g_m/I_{DS}$ ratio vs. $f_T$ trade-off at fixed $V_{GT}$ for vertical DG and planar TG device structures25                            |

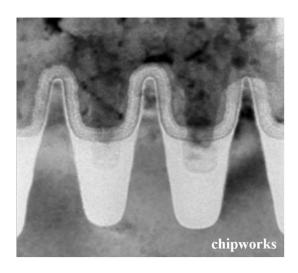

| Fig 2.6 TEM image of Intel's 22 nm-node tri-gate NMOS gate and fin structures showing fin                                             |

| thickness variations taken by chipworks                                                                                               |

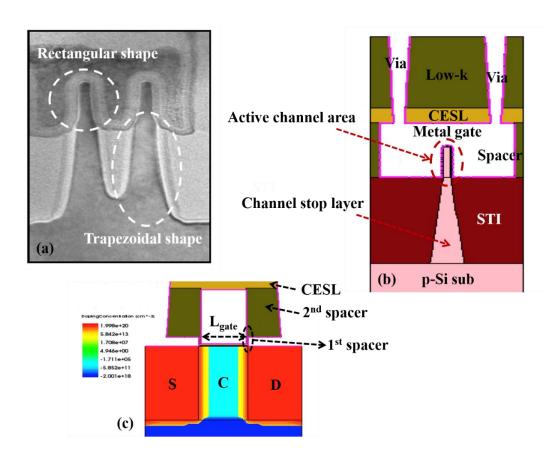

| Fig 2.7 (a) XTEM image of Intel's 14 nm-node tri-gate NMOS device; schematic diagrams of                                              |

| simulated 14 nm-node Si tri-gate MISFET structure cut along (b) fin width direction and (c)                                           |

| channel direction                                                                                                                     |

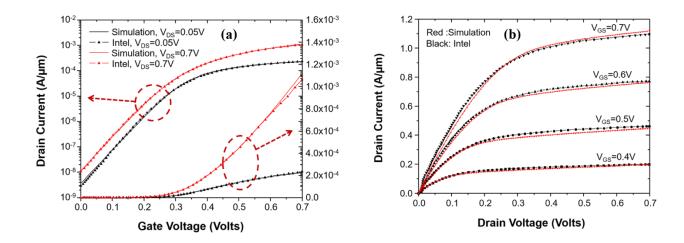

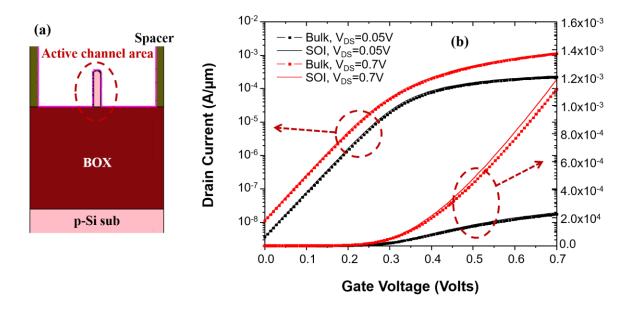

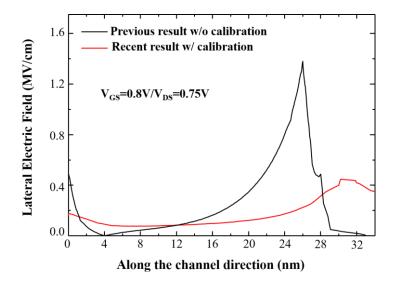

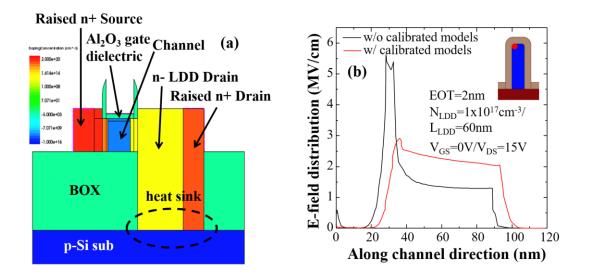

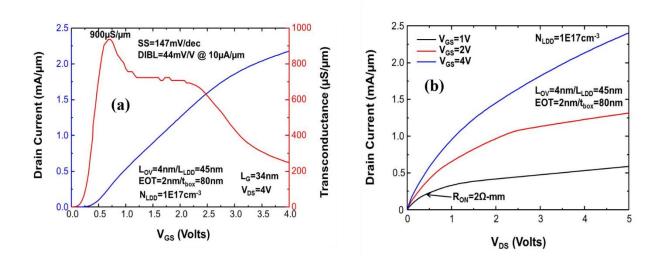

| Fig 2.8 Calibrated results of a fully-depleted narrow-fin <i>n</i> -channel Si bulk tri-gate structure (a)     |

|----------------------------------------------------------------------------------------------------------------|

| transfer characteristics and (b) output characteristics                                                        |

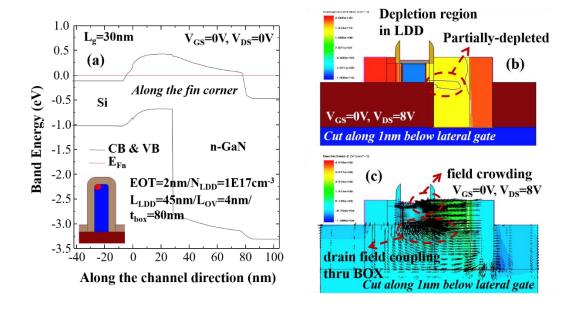

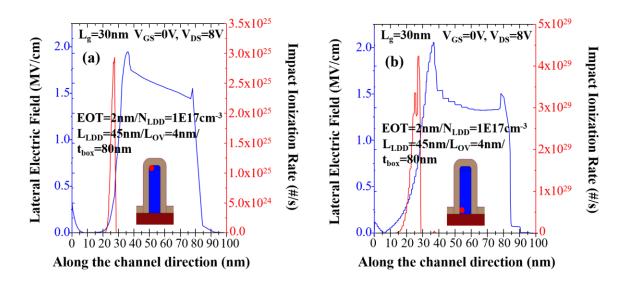

| Fig 2.9 (a) Simulated 14 nm-node SOI tri-gate MISFET structure cut along fin width direction; (b)              |

| calibrated transfer characteristics of a fully-depleted narrow-fin n-channel SOI tri-gate                      |

| structure30                                                                                                    |

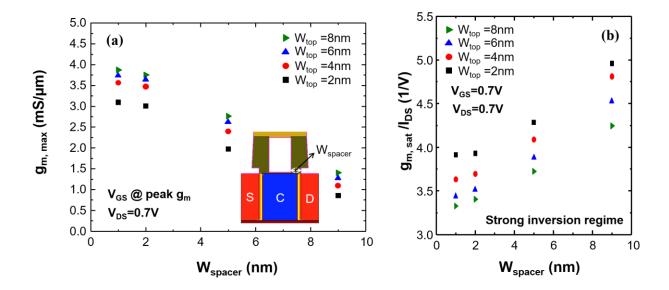

| Fig 2.10 (a) Maximum transconductance $(g_{m,max})$ and (b) drain current efficiency $(g_{m,sat}/I_{DS})$ of a |

| fully-depleted narrow-fin $n$ -channel SOI tri-gate structure with variations in spacer widths for             |

| different top fin widths32                                                                                     |

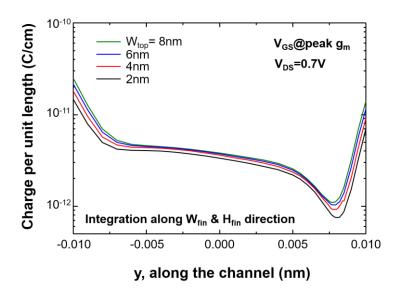

| Fig 2.11 Inversion charge distribution along the channel with different top fin widths at $V_{\rm GS}$ @peak   |

| $g_m$ and $V_{DS}$ =0.7 V, integrated along fin width and height directions                                    |

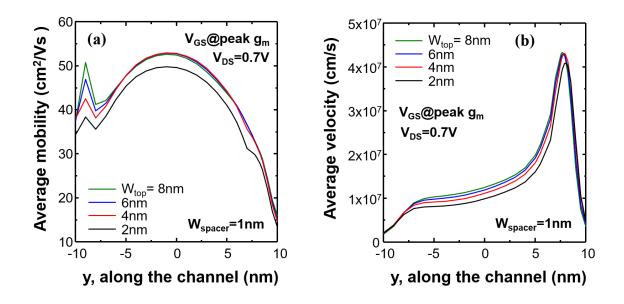

| Fig 2.12 (a) Average electron mobility and (b) average electron velocity along the channel with                |

| different top fin widths at $V_{GS}$ @peak $g_m$ and $V_{DS}$ =0.7 $V$ 33                                      |

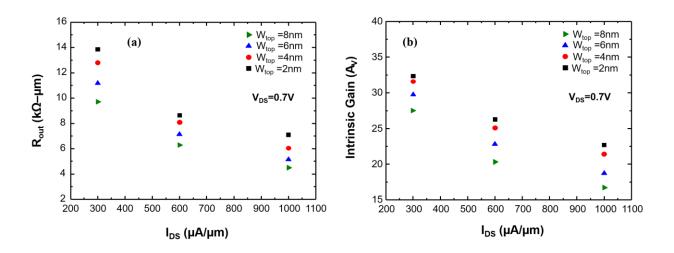

| Fig 2.13 (a) Output resistance and (b) device intrinsic gain at various bias currents for different top        |

| fin widths with spacer width of 1nm at $V_{DS}$ =0.7 V33                                                       |

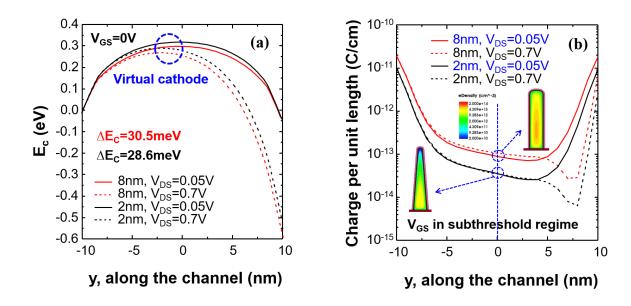

| Fig 2.14 (a) Conduction band profile along the channel at $V_{GS}$ =0 V and $V_{DS}$ =0.05/0.7 V and (b)       |

| electron charge distribution along the channel at $V_{GS}$ in the subthreshold regime and $V_{DS}$ =0.05/0.7   |

| V for W <sub>fin,top</sub> =2 nm and 8 nm34                                                                    |

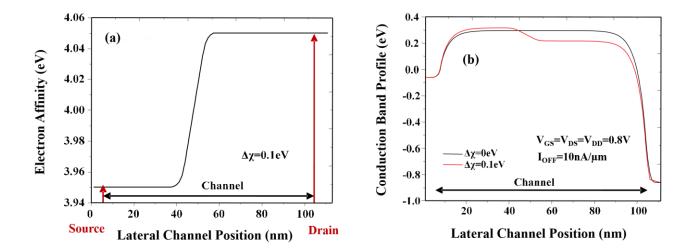

| Fig 2.15 (a) Graded electron affinity profile along the channel (20 nm grading distance inside the             |

| channel region) and (b) conduction band profiles with and without electron affinity grading in the             |

| channel region $(L_0 = 100 \text{ nm})$                                                                        |

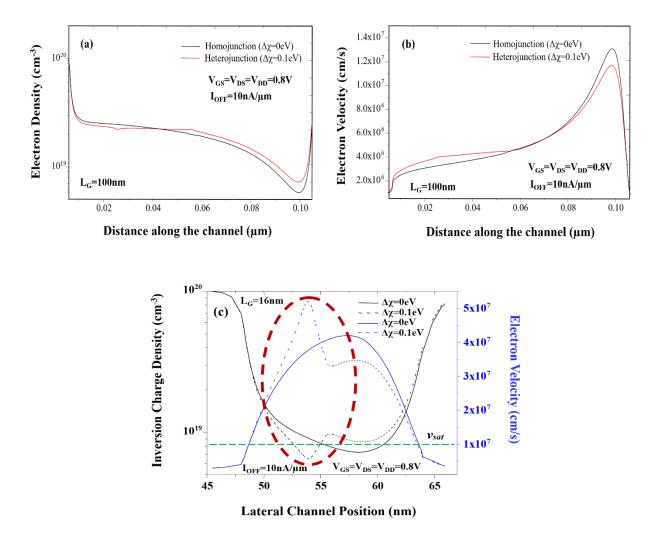

| Fig 2.16 (a) Inversion charge density distribution and (b) electron velocity profile along the                   |

|------------------------------------------------------------------------------------------------------------------|

| channel ( $L_G$ =100 nm); (c) inversion charge density distribution and electron velocity profile along          |

| the channel ( $L_G$ =16 nm) (More uniform inversion charge density along the channel and enhanced                |

| average carrier drift velocity near the source region for a graded heterojunction device)37                      |

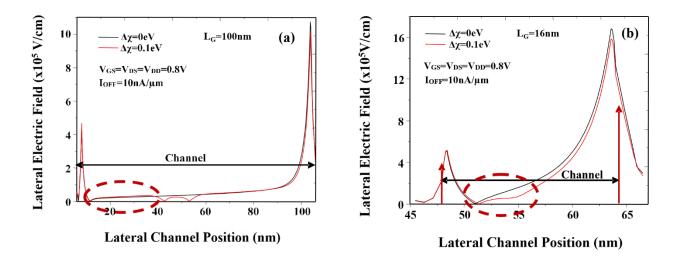

| Fig 2.17 Lateral electric field distribution along the channel at (a) $L_G$ =100 nm and (b) $L_G$ =16 nm         |

| (increased lateral electric field near the source for a graded heterojunction device)                            |

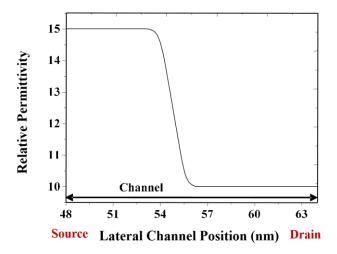

| Fig 2.18 Graded relative permittivity profile along the channel ( $L_G$ =16 nm) (3 nm grading distance           |

| inside the channel region)39                                                                                     |

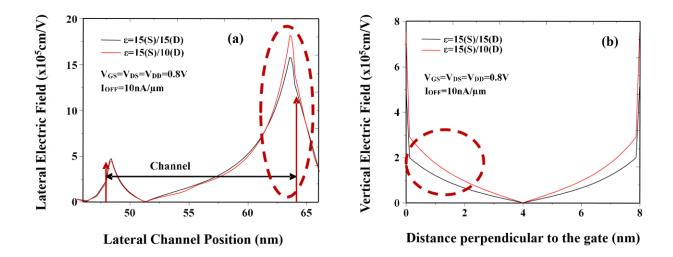

| Fig 2.19 (a) Lateral electric field distribution along the channel (voltage drop that occurs in the              |

| drain region is increased in the case with $\epsilon=15(S)/10(D)$ ; (b) vertical electric field distribution,    |

| cut along 1nm into the channel from the top of the source-to-channel barrier (vertical electric field            |

| is increased in the case with $\epsilon$ =15(S)/10(D), which translates to a better gate control over the        |

| channel) (L <sub>G</sub> =16 nm)40                                                                               |

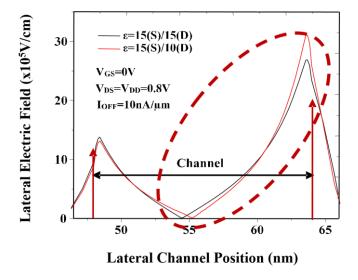

| Fig 2.20 Lateral electric field distribution along the channel when $V_{GS}$ =0 V and $V_{DS}$ = $V_{DD}$ =0.8 V |

| $(L_G=16\ nm)$ (Less drain field penetration into the channel region in the case with                            |

| $\varepsilon = 15(S)/10(D))$ 40                                                                                  |

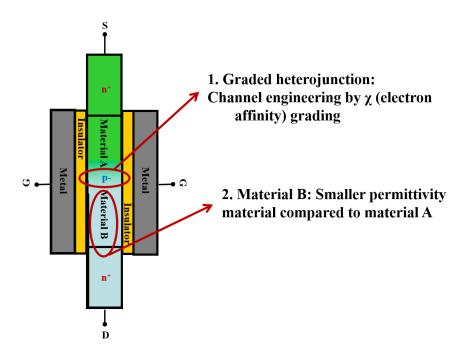

| Fig 2.21 Simulated III-V channel double-gate MOSFET with channel engineering approach42                          |

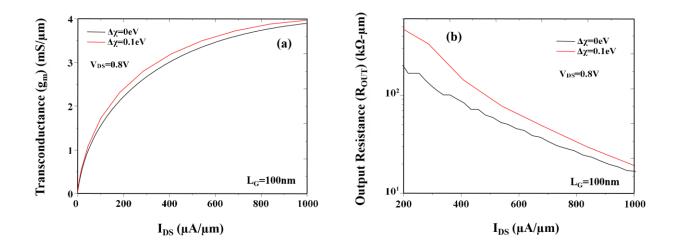

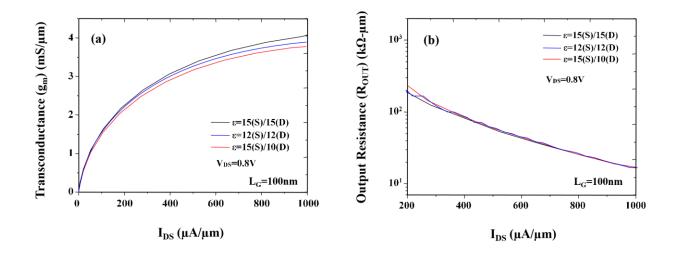

| Fig 2.22 (a) Transconductance and (b) output resistance of the simulated double-gate device with                 |

| electron affinity grading for a gate length of 100 nm at a fixed $V_{DS}$ =0.8                                   |

| V                                                                                                                |

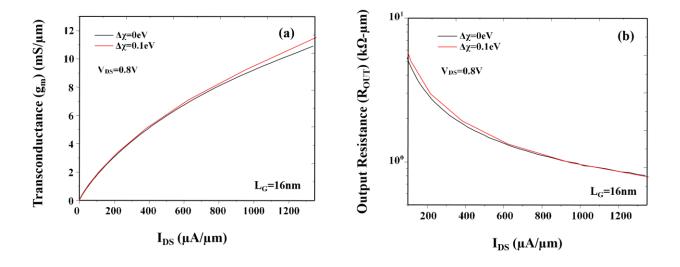

| Fig 2.23 (a) Transconductance and (b) output resistance of the simulated double-gate device with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| electron affinity grading for a gate length of 16 nm at a fixed $V_{DS}$ =0.8 $V_{D$ |

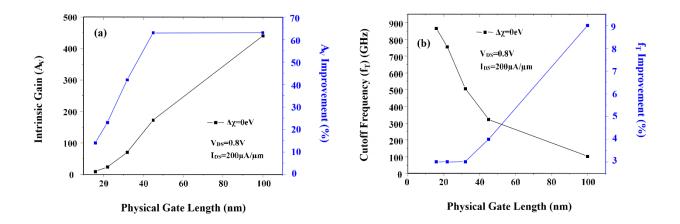

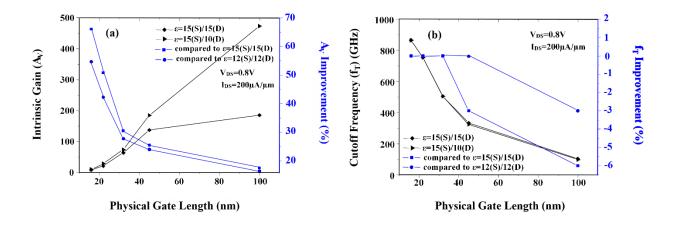

| Fig 2.24 (a) Intrinsic gain with its improvement and (b) cutoff frequency with its improvement of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| the simulated double-gate device with electron affinity grading for various physical gate lengths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| at a fixed $V_{DS}$ =0.8 V and $I_{DS}$ =200 $\mu A/\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

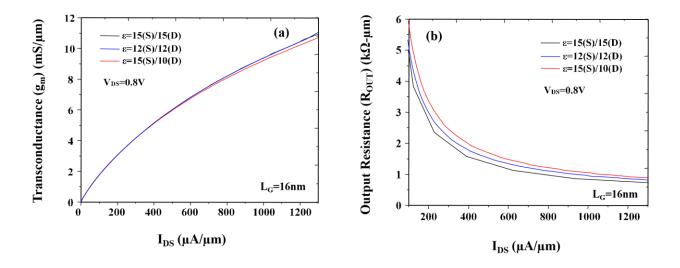

| Fig 2.25 (a) Transconductance and (b) output resistance of the simulated double-gate device with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| permittivity grading for a gate length of 100 nm at a fixed $V_{DS}$ =0.8 V46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig 2.26 (a) Transconductance and (b) output resistance of the simulated double-gate device with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| permittivity grading for a gate length of 16 nm at a fixed $V_{DS}$ =0.8 $V_{DS}$ =0.9 $V_{DS}$ =0 |

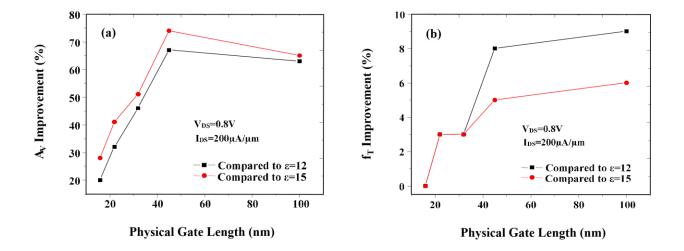

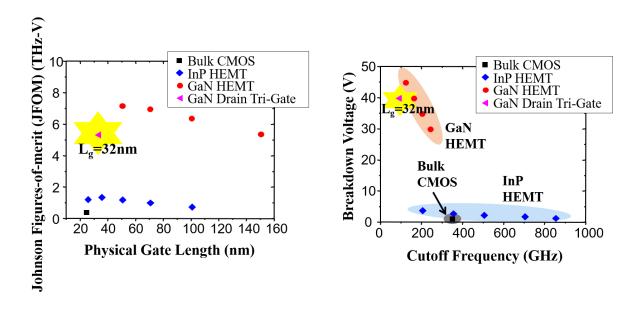

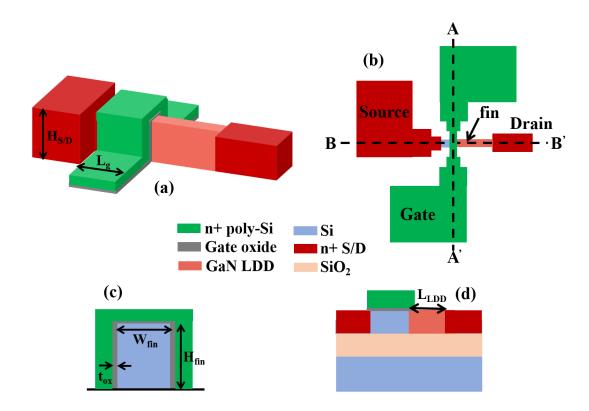

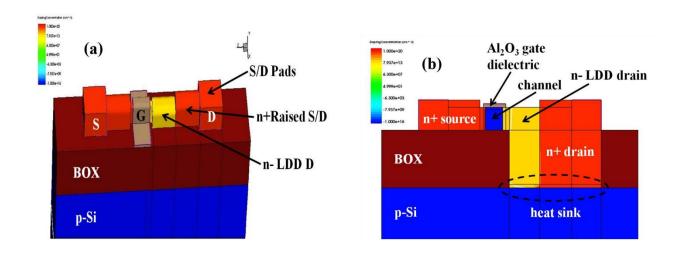

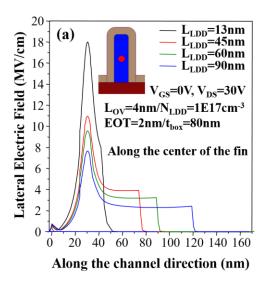

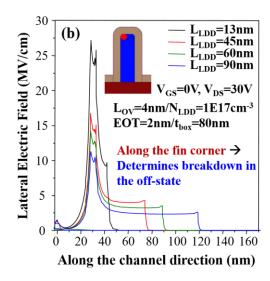

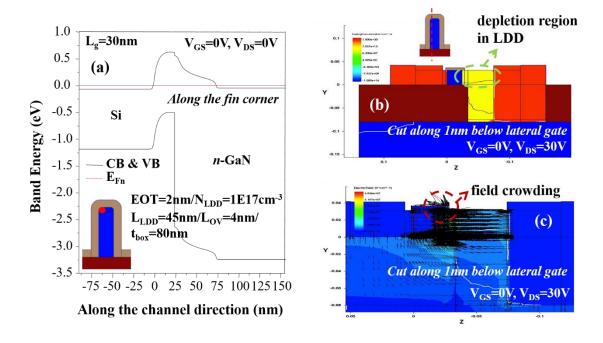

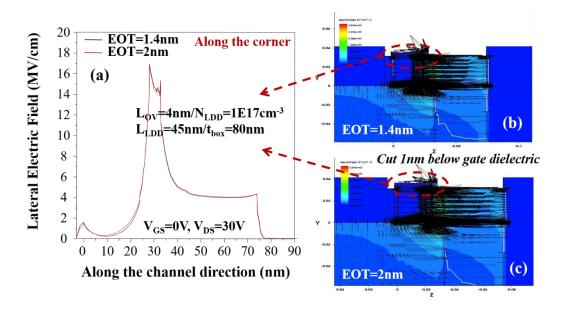

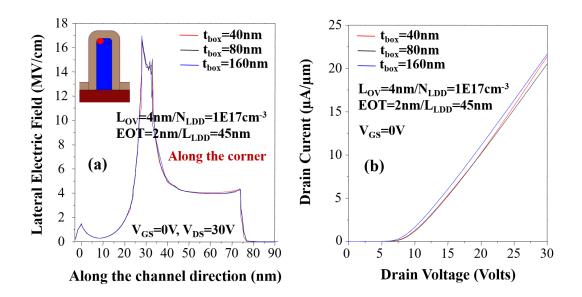

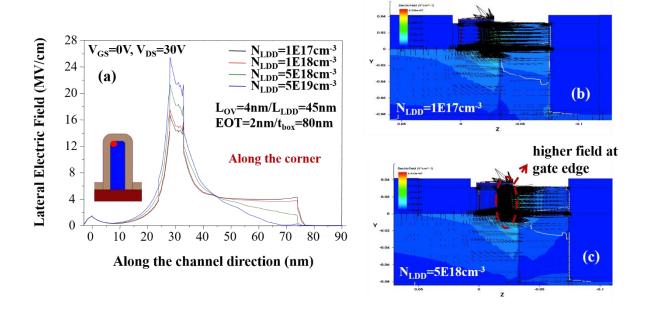

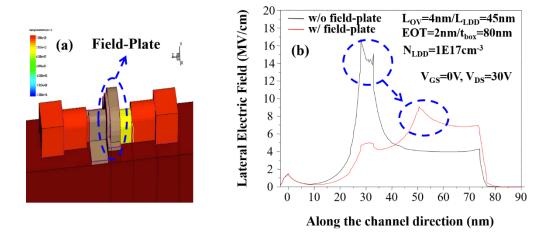

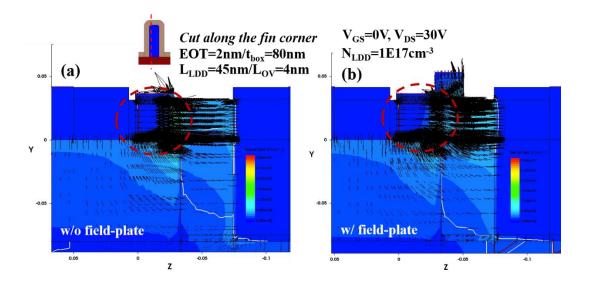

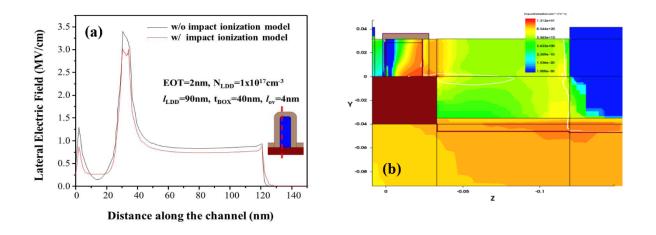

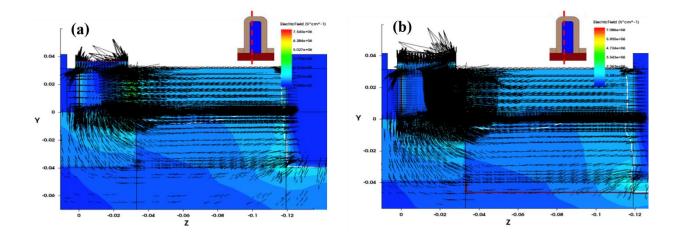

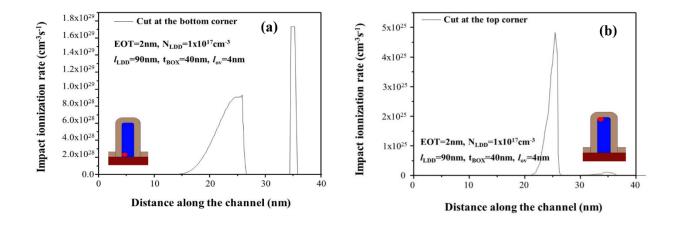

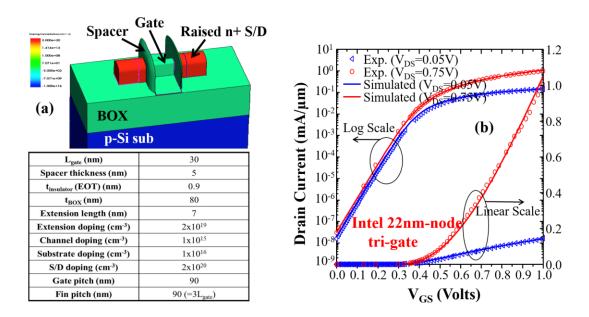

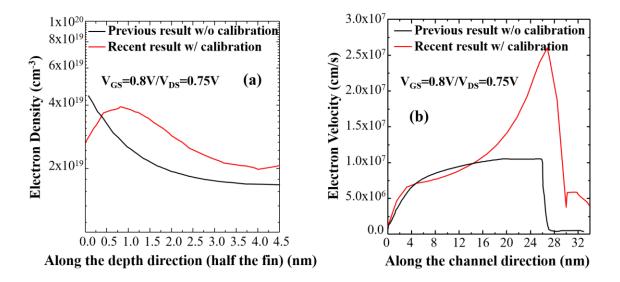

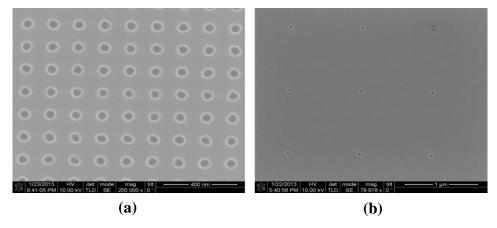

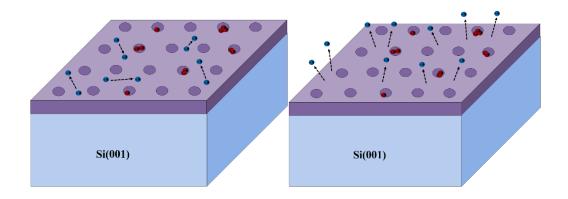

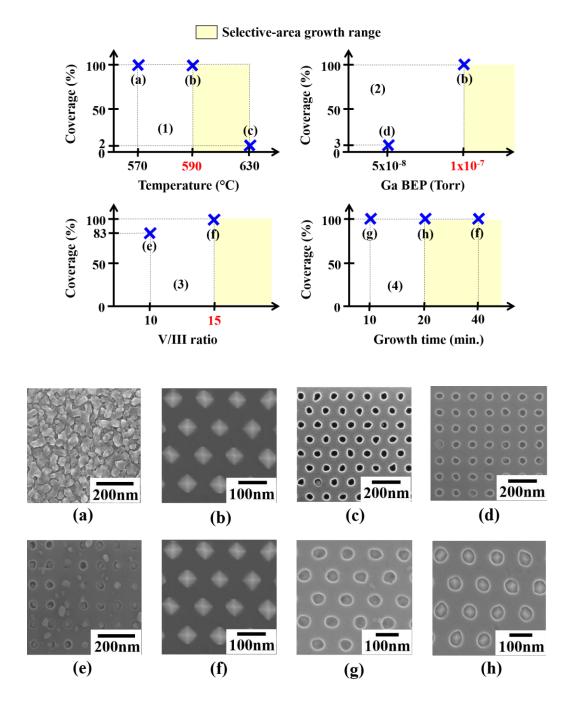

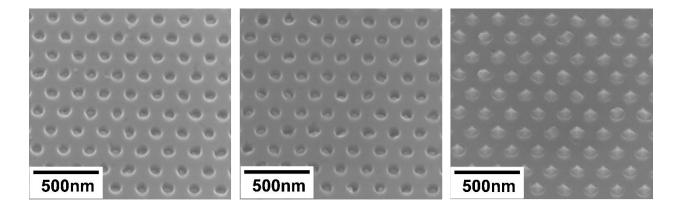

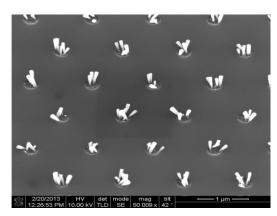

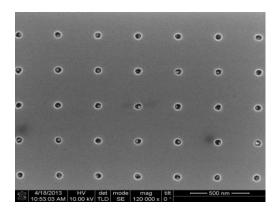

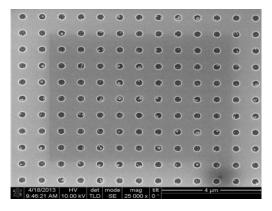

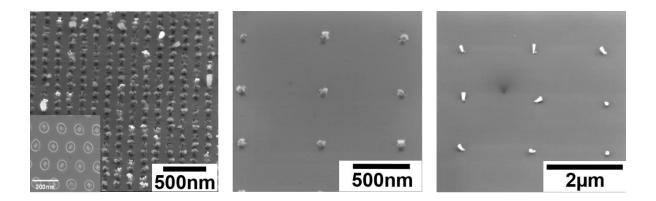

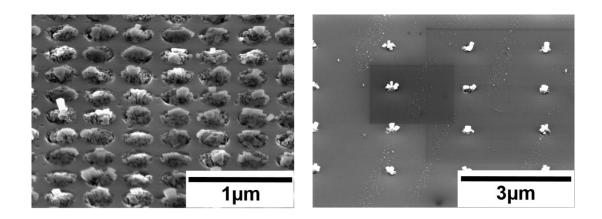

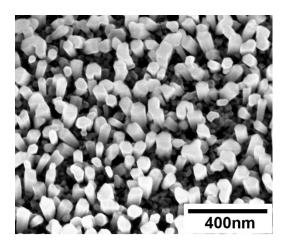

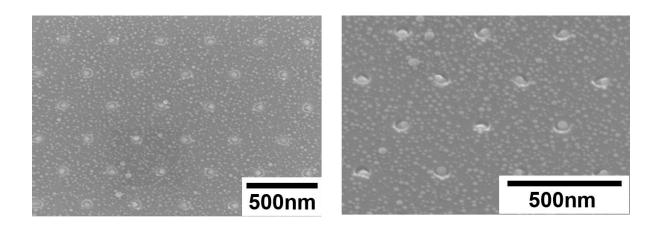

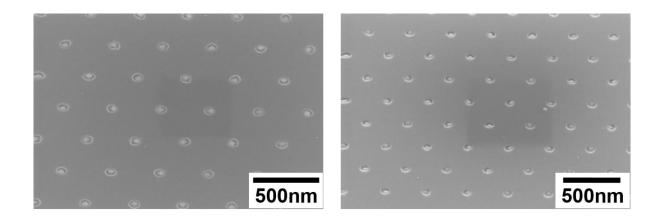

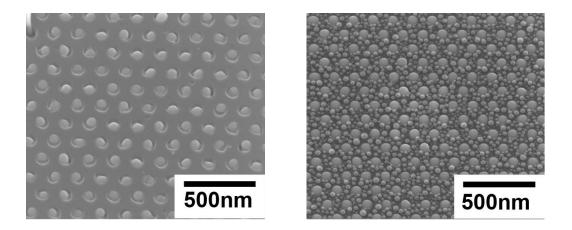

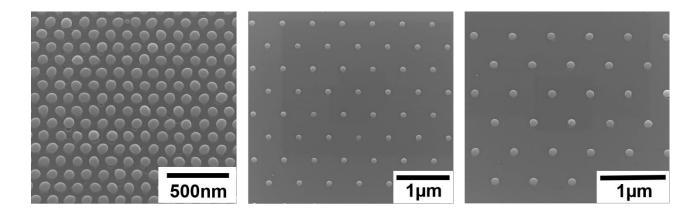

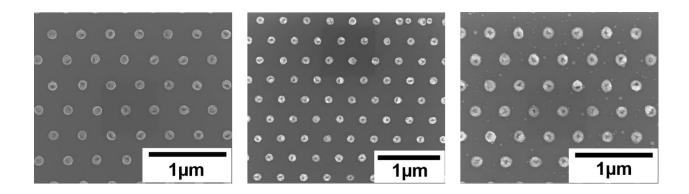

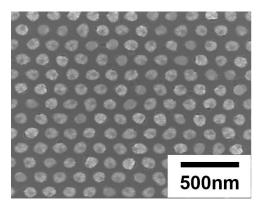

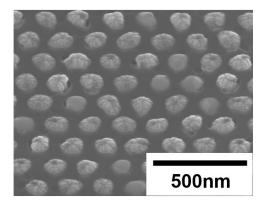

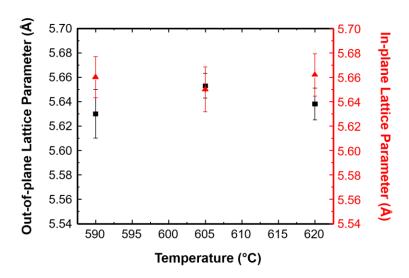

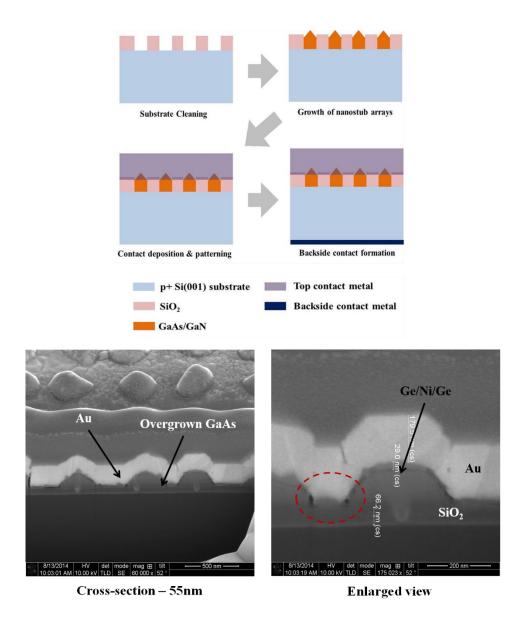

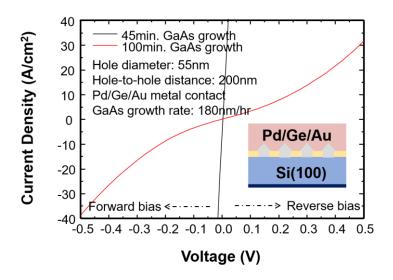

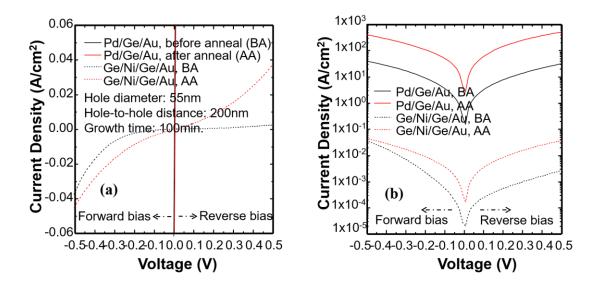

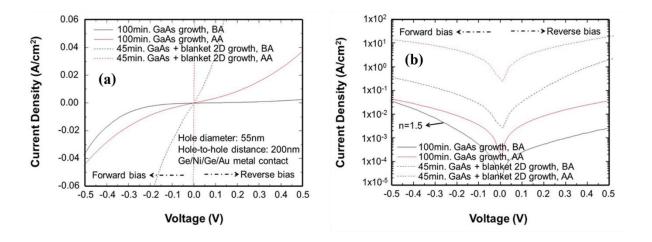

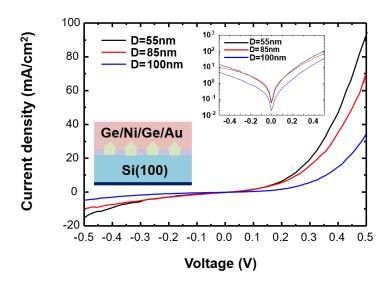

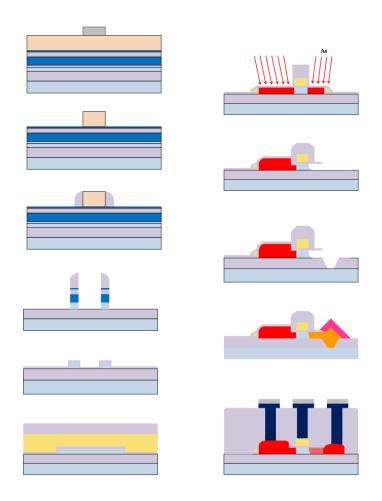

| Fig 2.27 (a) Intrinsic gain with its improvement and (b) cutoff frequency with its improvement of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |