# UCLA UCLA Electronic Theses and Dissertations

# Title

Hardware-Assisted Software Testing and Debugging for Heterogeneous Computing

# Permalink

https://escholarship.org/uc/item/9dh545t9

# Author

Wang, Jiyuan

# Publication Date 2025

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Hardware-Assisted Software Testing and Debugging for Heterogeneous Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Jiyuan Wang

2025

© Copyright by Jiyuan Wang 2025

#### ABSTRACT OF THE DISSERTATION

#### Hardware-Assisted Software Testing and Debugging for Heterogeneous Computing

by

Jiyuan Wang Doctor of Philosophy in Computer Science University of California, Los Angeles, 2025 Professor Miryung Kim, Chair

There is a growing interest in the computer architecture community to incorporate heterogeneity and specialization to improve performance. Developers can write *heterogeneous applications* that consist of *host* code and *kernel* code, where compute-intensive kernels can be offloaded from CPU to GPU, FPGA, or quantum computer. However, the high complexity of these systems can pose challenges to developer productivity, particularly when it comes to understanding performance or ensuring correctness. Testing and debugging such heterogeneous applications and software stacks are also extremely challenging because the characteristics of the hardware in heterogeneous computing can vary from a traditional CPU. For example, the output of a quantum computer is completely different from a CPU.

By leveraging hardware accelerator capability and by accounting for hardware accelerator behavior, this thesis presents efficient debugging and testing techniques for heterogeneous computing. My first work QDIFF is a differential testing framework for quantum software stacks to find *unexpected behavior*, such as crashes or unexpected divergences. By accounting for unique characteristics of quantum circuit execution and measurement, QDIFF automatically finds abnormalities in quantum software stacks by detecting quantum circuit result divergence. QDIFF proposes an input generation approach that applies gate-level equivalent transformation and explores the backends and compiler setting options to generate *semantic equivalent quantum circuits*. We then compare the measurement results of circuits with K-S distance and report unexpected results. For Cirq, Pyquil, and Qiskit, we found four new bugs in their simulators and two possible root causes for hardware execution divergence.

While QDIFF targets the correctness of quantum software stacks, bugs in heterogeneous applications are another concern in this domain. My second work HFUZZ designs a fuzz testing technique for heterogeneous applications. By designing hardware-level probes and offloading input mutations to hardware accelerators, HFUZZ leverages in-kernel probes to retrieve hardware execution feedback, including channel usage and in-kernel variable's value range. HFUZZ also uses FPGA to accelerate input mutations during fuzzing process. We conduct detailed experiments on seven benchmarks and demonstrate that HFUZZ significantly improves the fuzzing efficiency and reveals 25 unique and unexpected behavior symptoms that could not be found by state-of-the-art testing techniques.

QDIFF and HFUZZ together provide automated testing approaches for heterogeneous computing. However, developers must be able to diagnose the detected errors. Compilation for heterogeneous applications is inherently complex. For example, CIRCT, an MLIR-based heterogeneous compiler, requires 13 compilation layers to translate high-level Python code into low-level RTL. Identifying which layers and which parts of the intermediate representation (IR) contribute to bugs is difficult. To tackle this issue, my third work, DUOREDUCE, introduces a novel dual-dimensional error localization approach. DUOREDUCE systematically analyzes errors across both IR code dimension and compilation path dimension within the compilation process. By combining delta debugging techniques with dependency-aware compilation path reduction, DUOREDUCE identifies the minimal subset of IR code and compilation passes responsible for triggering an error. Through evaluation on real-world scenarios, DUOREDUCE demonstrated significant improvements in debugging accuracy and efficiency, accelerating error localization by  $901 \mathrm{x}$  compared to traditional techniques.

The dissertation of Jiyuan Wang is approved.

Harry Guoqing Xu

Jens Palsberg

Anthony John Nowatzki

Miryung Kim, Committee Chair

University of California, Los Angeles

2025

To my family and my passed grandma

### TABLE OF CONTENTS

| 1        | Intr                   | $\mathbf{roduction}$                                                          | 1  |

|----------|------------------------|-------------------------------------------------------------------------------|----|

|          | 1.1                    | Thesis Statement                                                              | 2  |

|          | 1.2                    | Automated test generation by understanding hardware characteristics and       |    |

|          |                        | leveraging hardware                                                           | 3  |

|          | 1.3                    | A bug isolation approach by considering multi-layer, extensible heterogeneous |    |

|          |                        | compilation                                                                   | 6  |

|          | 1.4                    | Outline                                                                       | 8  |

| <b>2</b> | Bac                    | kground                                                                       | 10 |

|          | 2.1                    | Heterogeneous Computing: Context and Challenge                                | 10 |

|          | 2.2                    | Quantum Computing & Quantum Software Stack                                    | 12 |

|          | 2.3                    | MLIR in Heterogeneous Computing                                               | 13 |

|          | 2.4                    | Automated Testing Techniques for Heterogeneous Application                    | 14 |

|          | 2.5                    | Testing and Verification for Quantum                                          | 16 |

|          | 2.6                    | Automated Debugging in Heterogeneous Domains                                  | 19 |

| 3        | $\mathbf{Q}\mathbf{D}$ | iff: Redesign Differential Testing for Quantum Computing                      | 22 |

|          | 3.1                    | Introduction                                                                  | 23 |

|          | 3.2                    | Background                                                                    | 23 |

|          | 3.3                    | Motivation                                                                    | 26 |

|          | 3.4                    | Approachh                                                                     | 28 |

|          |                        | 3.4.1 Program Variant Generation                                              | 29 |

|   |     | 3.4.2  | Quantum Simulation and Hardware Execution        | 31 |

|---|-----|--------|--------------------------------------------------|----|

|   |     | 3.4.3  | Equivalence Checking via Distribution Comparison | 34 |

|   | 3.5 | Evalua | ation                                            | 38 |

|   |     | 3.5.1  | RQ1: Variant Generation via S2S transformation   | 39 |

|   |     | 3.5.2  | RQ2: Speed Up                                    | 39 |

|   |     | 3.5.3  | RQ3: What has QDIFF found?                       | 40 |

|   |     | 3.5.4  | Threats to Validity                              | 46 |

|   | 3.6 | Discus | sion                                             | 46 |

| 4 | ΗFι | ızz: R | edesign Fuzz Testing for Heterogeneous Computing | 48 |

|   | 4.1 | Introd | uction                                           | 49 |

|   | 4.2 | Backg  | round                                            | 51 |

|   |     | 4.2.1  | Heterogeneous Applications with FPGA             | 52 |

|   |     | 4.2.2  | An Illustrating Example: Nbody-simulation        | 53 |

|   | 4.3 | Appro  | ach                                              | 54 |

|   |     | 4.3.1  | Injecting HW Probes in addition to SW Monitors   | 56 |

|   |     | 4.3.2  | Offloading Input Mutations to Kernels            | 59 |

|   |     | 4.3.3  | FPGA Optimizations for Fuzzing                   | 61 |

|   | 4.4 | Evalua | ation                                            | 65 |

|   |     | 4.4.1  | Defect Detection by HW and SW Feedback           | 67 |

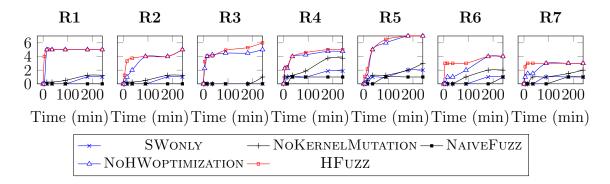

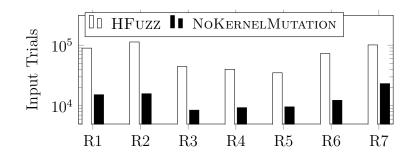

|   |     | 4.4.2  | Speed-up from In-kernel Input Mutations          | 69 |

|   |     | 4.4.3  | Speed-up from FPGA-level Optimizations           | 70 |

|   |     | 4.4.4  | Probe Overhead                                   | 71 |

|   | 4.5 | Conclu | usion                                            | 73 |

| <b>5</b> | Duo  | Reduc  | ce: Redesign Delta Debugging for Multi-layer Heterogeneous        | 3   |

|----------|------|--------|-------------------------------------------------------------------|-----|

| Co       | ompi | ler    |                                                                   | 74  |

|          | 5.1  | Introd | uction                                                            | 74  |

|          | 5.2  | Backgr | round                                                             | 78  |

|          |      | 5.2.1  | Multi-Level Intermediate Representation                           | 78  |

|          |      | 5.2.2  | Motivating Example                                                | 80  |

|          | 5.3  | Appro  | ach                                                               | 82  |

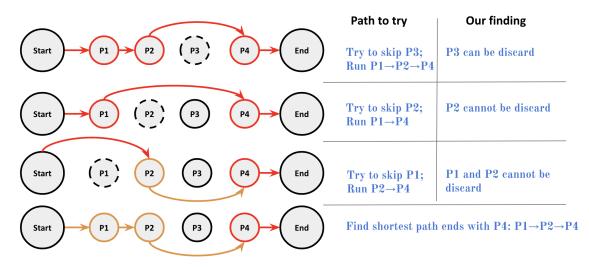

|          |      | 5.3.1  | Dependency-Aware Compilation Path Reduction                       | 84  |

|          |      | 5.3.2  | Transformation-Based Code Reduction                               | 87  |

|          |      | 5.3.3  | IR-Path Dual-Dimensional Reduction                                | 89  |

|          |      | 5.3.4  | Overall Time Complexity                                           | 90  |

|          | 5.4  | Evalua | ation                                                             | 91  |

|          |      | 5.4.1  | Experiment Design                                                 | 91  |

|          |      | 5.4.2  | RQ1: Effectiveness of MLIR Code Transformations                   | 94  |

|          |      | 5.4.3  | RQ2: Effectiveness of Dual-Dimensional Reduction                  | 97  |

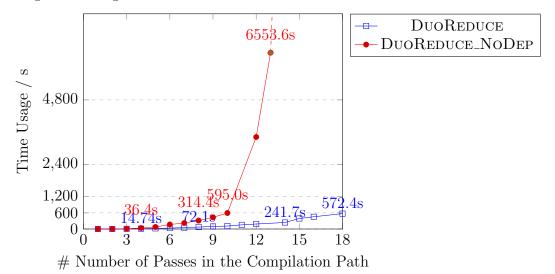

|          |      | 5.4.4  | RQ3: Effectiveness of Compilation Pass Dependence-Aware Reduction | 99  |

|          | 5.5  | Conclu | usion                                                             | 101 |

| 6        | Con  | clusio | n and Future Direction                                            | 102 |

|          | 6.1  | Conclu | asion                                                             | 102 |

|          | 6.2  | Discus | sion $\ldots$                                                     | 103 |

|          | 6.3  | Future | e Direction                                                       | 104 |

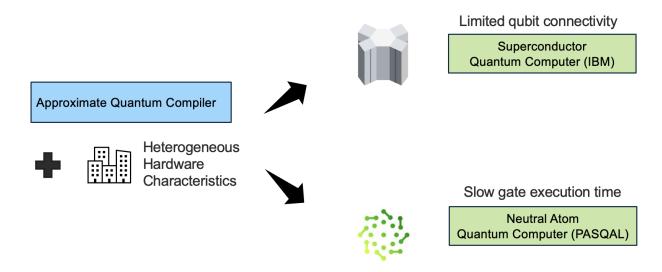

|          |      | 6.3.1  | Challenges in Quantum Computing: Embracing Noise in Compilation   | 105 |

|          |      | 6.3.2  | Challenges in Heterogeneous Application Development: Optimization | 106 |

| References . |  | • | • |  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • |  | • | • | • |  |  |  | • | • | 1 | 80 | 3 |

|--------------|--|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|--|---|---|---|--|--|--|---|---|---|----|---|

|--------------|--|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|--|---|---|---|--|--|--|---|---|---|----|---|

### LIST OF FIGURES

| 3.1 | An example Qiskit program.                                                             | 25 |

|-----|----------------------------------------------------------------------------------------|----|

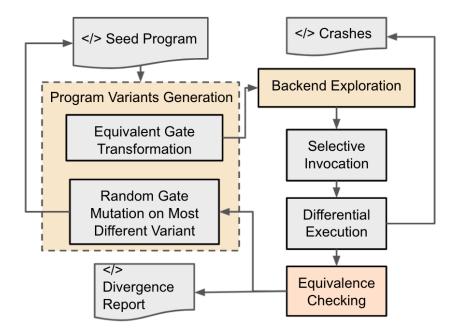

| 3.2 | QDIFF overview                                                                         | 27 |

| 3.3 | A quantum circuit in Qiskit with two backends: quantum simulator and state-            |    |

|     | vector simulator.                                                                      | 36 |

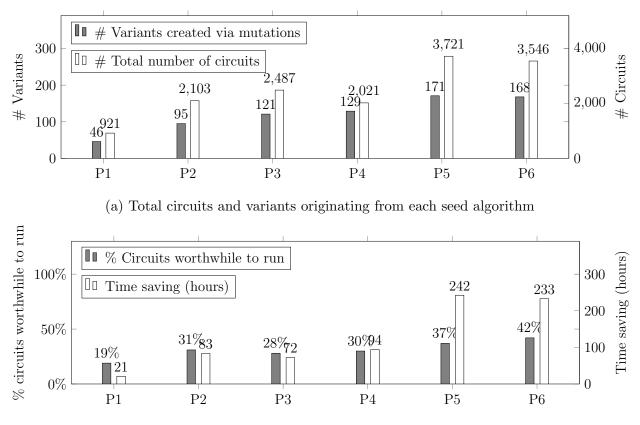

| 3.4 | Statistics of QDIFF-generated circuits.                                                | 40 |

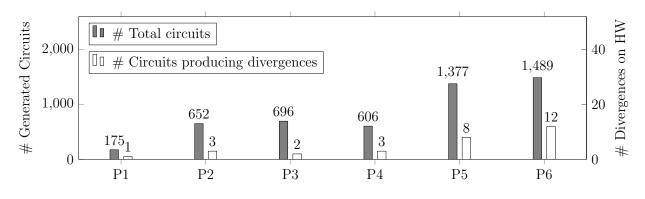

| 3.5 | Circuits producing divergences on IBM hardware                                         | 41 |

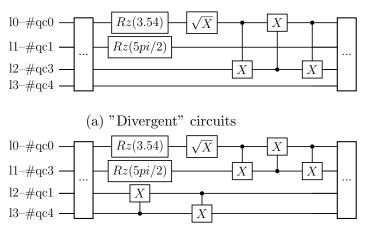

| 3.6 | Bugs in Pyquil found by QDIFF                                                          | 42 |

| 3.7 | Divergence on IBM ibmq_yorktown: no operation on qc4 for a long time                   | 44 |

| 3.8 | Divergence detected on IBM hardware: bad connection between qc_2 and qc_3              | 45 |

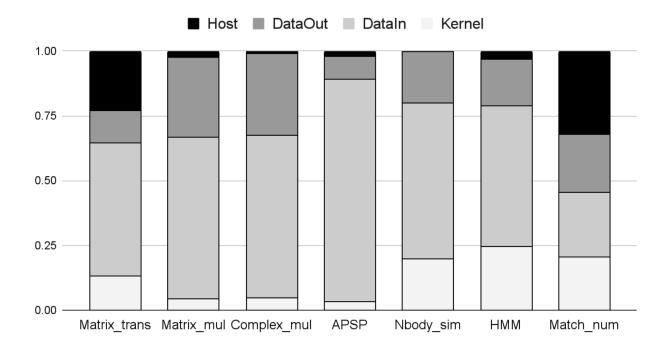

| 4.1 | Latency breakdown of running applications on heterogeneous archi-                      |    |

|     | tectures. On average, data transfer into kernels takes $60\%$ of execution             |    |

|     | time, highlighted in gray.                                                             | 50 |

| 4.2 | Nbody-simulation: a heterogeneous version with DPC++ high-level                        |    |

|     | synthesis.                                                                             | 51 |

| 4.3 | Matrix transform: inserted Value Range Probes are in the green rectangle. In-          |    |

|     | serted<br>Pipe Usage Probes are in the red rectangles. Inserted SW Monitors are in     |    |

|     | the orange rectangle                                                                   | 57 |

| 4.4 | Sparsity mutation: replace the zero elements to non-zero elements from index ${\bf s}$ |    |

|     | to index <b>e</b>                                                                      | 62 |

| 4.5 | Number of Defects                                                                      | 65 |

| 4.6 | Number of Input Trials                                                                 | 69 |

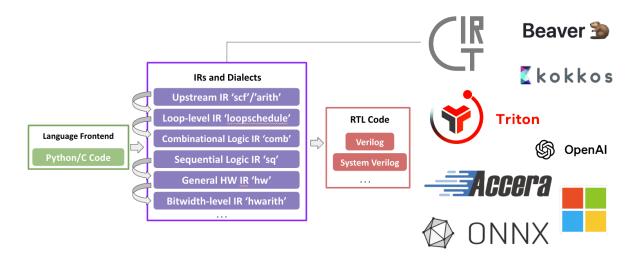

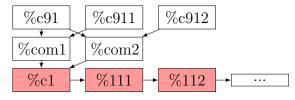

5.1 CIRCT's multi-layer compilation involves 4 core dialects and 26 optimizing dialects such as hwarith and sq. An MLIR input program goes through on average 13 transformation passes and produces the resulting Verilog code. The MLIR community is growing and as of Sep. 2024, there are 30 MLIR-based compiler projects on GitHub.

76

78

- 5.3 MLIR bug #56914 [18]: the original input IR code in Fig 5.3a and 9 compilation passes to reproduce the crash in Fig 5.3c. If she compiles the input IR with all available 9 passes, 4480 lines of compiler code should be inspected. In Fig 5.3b, DUOREDUCE successfully removed the **@matmul** with "constant replacement" transformation in Section 5.3.2. DUOREDUCE removes 6 irrelevant compilation passes out of 9, leaving only 1245 lines of compiler code to inspect. . . . 81

- 5.5 Code example from MLIR GitHub issue 64074 [19]. DUOREDUCE applies program transformation on the 1-minimal IR code and enables a further 75% reduction. 87

| 5.6  | After removing <b>@matmul</b> in Figure 5.3, the pass <b>affine-loop-unroll</b> is no longer |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | relevant. DUOREDUCE removes 4 out of 7 passes, and reduces the inspection                    |     |

|      | scope from 2279 to 1245 lines                                                                | 89  |

| 5.7  | MLIR GitHub issue 64071 [20]. DUOREDUCE achieves 4 more lines of code                        |     |

|      | reduction with the constant replacement compared to Perses+ and Vulcan+,                     |     |

|      | and only takes 617.4 seconds compared to Vulcan+ which takes 2604 seconds,                   |     |

|      | resulting in $3.87 \times$ speedup                                                           | 95  |

| 5.8  | MLIR GitHub issue 82382 [21]. DUOREDUCE finds the buggy pass affine-loop-ti                  | le  |

|      | in the results while the compiler crash message doesn't, which motivates the need            |     |

|      | for DUOREDUCE.                                                                               | 97  |

| 5.9  | MLIR GitHub issue 76579 [22]. With dual-dimensional reduction, DUOREDUCE                     |     |

|      | removes 3 redundant passes and achieves better reduction than $DuOReduce_{-}$                |     |

|      | NO2DIM, which translates to not needing to inspect 2139 lines of MLIR compiler $\mathcal{N}$ |     |

|      | code                                                                                         | 98  |

| 5.10 | Time usage for DUOREDUCE and DUOREDUCE_NODEP. The x-axis represents                          |     |

|      | the number of passes, and the y-axis represents the average time usage. DUORE-               |     |

|      | DUCE achieves higher speedup when more compilation passes are involved. For                  |     |

|      | example, for 13 compilation passes, DUOREDUCE takes 241.7s, while DUORE-                     |     |

|      | DUCE_NODEP takes 6553.6s, resulting in $27 \times$ speedup                                   | 99  |

| 6.1  | A quantum compiler should employ diverse compilation strategies, since different             |     |

|      | quantum computers have different hardware constraints.                                       | 106 |

| 6 9  |                                                                                              |     |

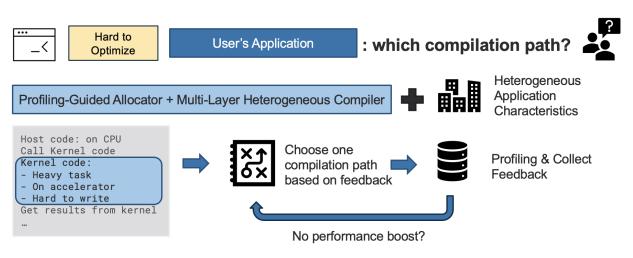

| 6.2  | Overview for a Profiling-Guided Allocator                                                    | 107 |

### LIST OF TABLES

| 3.1 | Different layers that bugs appear                                                                                                                          | 26 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Explored Compiler Configurations                                                                                                                           | 28 |

| 3.3 | QDIFF generates program variants based on EGT rules G1-G7                                                                                                  | 30 |

| 3.4 | IBM quantum hardware's gate-level error rates, gate time, and T1 relaxation                                                                                |    |

|     | $(decoherence) time. \ldots \ldots$ | 31 |

| 3.5 | Explored Backends (Simulators and Hardware)                                                                                                                | 32 |

| 3.6 | Cumulative probability of KS test                                                                                                                          | 34 |

| 3.7 | Seed subject programs                                                                                                                                      | 38 |

| 3.8 | Bugs found by QDIFF when executing generated programs with simulation only                                                                                 | 41 |

| 4.1 | Mutations accelerated by hardware                                                                                                                          | 56 |

| 4.2 | Example execution of input generator $G$                                                                                                                   | 61 |

| 4.3 | Example symptoms of kernel defects in R1.                                                                                                                  | 68 |

| 4.4 | Resource overhead from injecting hardware probes                                                                                                           | 72 |

| 5.1 |                                                                                                                                                            |    |

| 0.1 | The systems used in our evaluation are significant-sized real-world projects (444k,                                                                        |    |

| 0.1 | The systems used in our evaluation are significant-sized real-world projects (444k, 171k, and 96k LOC for MLIR, CIRCT, and ONNX-MLIR, respectively). They  |    |

| 9.1 |                                                                                                                                                            |    |

| 9.1 | 171k, and 96k LOC for MLIR, CIRCT, and ONNX-MLIR, respectively). They                                                                                      |    |

#### ACKNOWLEDGMENTS

The past six years were the best years of my entire life. When I look back, I still remember the first day I met my advisors Miryung Kim and Harry Xu. It was during the Spring Festival, and at that time, I still hadn't received any PhD offers. I was deeply worried and sent emails to potential advisors to request interviews. That's when Miryung, like a superhero, stepped in and saved not only my winter holiday but also the next six years of my life. Though Miryung didn't give any immediate positive signals (I'm still striving to adopt to her style), Harry asked, "If we give you the offer, will you come?"

To be honest, I never felt like I was a "qualified" UCLA PhD student in the beginning. Before leaving for the US, all the students from my home university who had been admitted to UCLA gathered for a farewell dinner. I remember they were all either summa cum laude or cum laude graduates from Tsinghua—except me. My peers who joined the lab the same year, Haoran and Yifan, had exceptionally strong computer science backgrounds, and today they're both incredibly successful researchers. I want to prove I am qualified, both as a student, and a researcher.

I knew I did.

Life was never easy as a PhD student, especially during the covid. After the first quarter, just as I was beginning to learn how to conduct research, the world came to a halt. COVID-19 began, and suddenly everyone—including my advisors, Miryung Kim and Harry Xu, and my mentor, Qian Zhang—shifted to working from home. I found myself locked in a small apartment with my roommate and his girlfriend. Despite the isolation, I didn't feel lonely. My advisors provided me with more support during that difficult time than I could have ever imagined. I am also deeply grateful to Yifan Qiao and Haoran Ma, who often invited me over to their apartment for dinner

After two years in Los Angeles, I decided to visit my parents in China. It was a time of personal hardship; my father nearly lost his job and was in a very low emotional state. Seeing him like that was heartbreaking. However, when I tried to return to the US, the visa approval process took nearly four months, and the delay deeply affected my productivity that summer and into the fall quarter. While everyone else returned to campus, I was still stuck in China. During this difficult period, my advisors showed me immense patience—patience that I couldn't even muster for myself.

If I list all the troubles I met during the PhD, then the acknowledgments will become 100 pages long. I want to express my gratitude to all the wonderful people who gave me support along the journey.

I would like to thank my committee members, Miryung Kim, Harry Xu, Jens Palsberg, and Tony Nowatzki. Thanks for your time and feedback on my research.

Thank you to my advisor, Miryung Kim. You once told me that your daughter is your first priority and your PhD students are your second priority. At the time, I thought it was a joke, but I realized you truly meant it. Your unwavering support has been invaluable. You taught me how to navigate the complexities of research, guided me when I felt lost in the dark, and stood by me during my most challenging times.

Thank you to my co-advisor, Harry Xu. I am deeply grateful for the invaluable insights you have provided for my research, as well as the thoughtful advice you have offered for life beyond academia. Being co-advised by you and Miryung has not only broadened my perspective on research but also enriched my understanding of life from different angles.

Thank you to my mentor and friend, Qian Zhang. I deeply appreciate all the guidance and countless hours you have dedicated to supporting me. I know I wasn't always the easiest collaborator, and I am grateful for your patience, understanding, and advocacy on my behalf. Working with you has been a privilege, and I am confident you will be an exceptional professor.

Thank you, my intern manager and my friend, Antonio Filieri. Amazon might not be the best company, but you are the best employee and best manager. Wish you all the best for your career and family.

Thank you to my collaborators, Yuxin Qiu, Hongbo Rong, and Rohan Padhye. Thanks for the brilliant ideas and valuable comments.

Thank you to my dear lab mates, Yifan Qiao, Haoran Ma, Jason Teoh, Muhammad Ali Gulzar, Yaoxuan Wu, Ben Limpanukorn, Zitong Zhou, and Hong Jin Kang. Thanks for the brainstorming and support as friends.

Thank you to my love, Jiayi. Your unwavering support—emotional, practical, and financial—has been a constant source of strength for me. The joy, compromises, and sacrifices you've made will forever leave an indelible mark on my heart.

Thank you to my cousin, Liang Shang. Having a family member in this foreign land gives me much more strength than I could ever imagine. Your presence means the world to me.

Thank you to my grandma. You raised me up for my childhood and taught me how to recognize the words one by one. I really want to say how much I love you in person, and I regret I did not use my last chance to say it. COVID took too much than I could bear.

Thank you to my parents. My name, "Jiyuan," means "to go far," and I hope I have lived up to the dreams you held for me. I can only wish to return even a fraction of the boundless love you have given me.

Thank you Jiyuan. No one is the arbiter of who does and doesn't have value, and you should always remember this.

#### VITA

- 2019 2025 Graduate Student Researcher/Teaching Assistant University of California, Los Angeles

- 2019 2022 M.S. in Computer Science University of California, Los Angeles

- 2015 2019 B.S. in Physics Tsinghua University

#### PUBLICATIONS

**Jiyuan Wang**, Yuxin Qiu, Ben Limpanukorn, Hong Jin Kang, Qian Zhang, Miryung Kim, DuoReduce: Bug Isolation for Multi-Layer Extensible Compilation, FSE, 2025

Ben Limpanukorn, **Jiyuan Wang**, Hong Jin Kang, Zitong Zhou, Miryung Kim, Fuzzing MLIR Compilers with Custom Mutation Synthesis, ICSE, 2025

**Jiyuan Wang**, Qian Zhang, Hongbo Rong, Guoqing Harry Xu, Miryung Kim, Leveraging Hardware Probes and Optimizations for Accelerating Fuzz Testing of Heterogeneous Applications, ESEC/FSE, 2023

Qian Zhang, **Jiyuan Wang**, Guoqing Harry Xu, Miryung Kim, HeteroGen: Transpiling C to Heterogeneous HLS Code with Automated Test Generation and Program Repair, ASPLOS, 2022 **Jiyuan Wang**, Qian Zhang, Guoqing Harry Xu, Miryung Kim, QDiff: Differential Testing for Quantum Software Stacks, ASE, 2021, **SIGSOFT research highlight**

Qian Zhang, **Jiyuan Wang**, Miryung Kim, HeteroFuzz: Fuzz Testing to Detect Platform Dependent Divergence for Heterogeneous Applications, ESEC/FSE, 2021

Jiyuan Wang, Fuchen Ma, Yu Jiang, Poster: Fuzz Testing of Quantum Program, Poster, ICST, 2021, Best Poster

Qian Zhang, **Jiyuan Wang**, Muhammad Ali Gulzar, Rohan Padhye, Miryung Kim, Efficient Fuzz Testing for Apache Spark Using Framework Abstraction, Demonstrations, ICSE, 2021

Qian Zhang, **Jiyuan Wang**, Muhammad Ali Gulzar, Rohan Padhye, Miryung Kim, BigFuzz: Efficient Fuzz Testing for Data Analytics using Framework Abstraction, ASE, 2020

# CHAPTER 1

# Introduction

Specialized hardware accelerators like GPUs, FPGAs, and quantum computers have become a prominent part of the current computing landscape. As a result, an increasing number of applications and software stacks are constructed to leverage heterogeneous architectures. Developers can write *heterogeneous applications* that consist of *host* code and *kernel* code, where compute-intensive kernels can be offloaded from CPU to GPU, FPGA, or quantum computer. Similar to other software development scenarios, developers often deal with software underlying errors, such as divergent results produced by different hardware accelerators or crashes in compilers for heterogeneous computing. Heterogeneous computing systems provide increased computing ability and expressiveness through pragma and optimizations that specially designed for hardware accelerators. This consequently increases the complexity of testing and debugging heterogeneous applications and underlying software stacks.

Therefore, testing and debugging heterogeneous applications and software stacks can be an expensive and time-consuming process. For example, ensuring the correctness of FPGA programs, even seemingly-simple kernels, could take a substantial amount of time in terms of months [140]. Moreover, most software developers treat hardware accelerators as a black box, and failures in hardware accelerators like FPGAs occur silently without any raised exception. For example, when a divide-by-0 is generated in FPGA, there is no signal but only returned wrong values. In order to test software in the heterogeneous domain, we need to account for hardware execution behavior and leverage hardware accelerators to produce feedback. Traditional software testing and debugging approaches do not work for heterogeneous applications, because they do not consider the hardware accelerators' characteristics. For example, it can takes AFL days and hours to trigger the bugs in heterogeneous applications [182, 13].

### 1.1 Thesis Statement

We synthesize ideas from software engineering and heterogeneous computing and answer the following research questions in the context of heterogeneous computing:

- What kinds of hardware accelerator characteristics can be leveraged to filter out hardware noise and accurately identify software bugs?

- How can we utilize hardware accelerators to generate execution feedback and accelerate test input generation?

- How can we systematically localize compilation layers and code segments responsible for bugs in heterogeneous computing?

Our hypothesis is that by leveraging hardware accelerator capabilities and accounting for execution behavior, we can develop efficient testing and debugging techniques that enhance the accessibility and reliability of heterogeneous computing.

To address the first research question, we introduce QDIFF, a differential testing framework for quantum software stacks. QDIFF enhances testing efficiency by filtering out noise circuits and leveraging quantum-specific properties such as qubit decay time (T1) and twoqubit error rates to optimize test case selection. Additionally, QDIFF employs a Kolmogorov-Smirnov (K-S) based statistical comparison to detect quantum software bugs by analyzing deviations in measurement results.

For the second question, we design HFUZZ, an automated fuzz testing framework for heterogeneous applications. HFUZZ enhances test case generation by monitoring execution behavior across both software host code and hardware kernel code. Additionally, HFUZZ offloads input mutation tasks directly to FPGAs, and accelerates mutation with FPGA-specific optimization, including loop unrolling, shannonization, and data preloading.

To further advance debugging for heterogeneous compilation, we focus on MLIR (Multi-Level Intermediate Representation), a flexible compiler infrastructure designed to unify and optimize compilation across diverse hardware backends. MLIR introduces a structured, extensible IR that enables progressive lowering from high-level domain-specific abstractions to hardware-specific representations. It serves as the foundation for several heterogeneous and ML compilation frameworks, including CIRCT, which provides specialized dialects for FPGA design. We introduce DUOREDUCE, a debugging methodology for heterogeneous compilation. Our third hypothesis is that by analyzing relationships between IR-level debugging and compilation-layer debugging, we can systematically identify which compilation layers contribute to a given bug. This approach enables more precise error localization within complex compilation pipelines, improving debugging efficiency and reliability.

# 1.2 Automated test generation by understanding hardware characteristics and leveraging hardware

The existing testing approach, including fuzz testing and differential testing, has been proved successful for traditional software. Google's OSS-Fuzz project alone has detected over 10,000 security vulnerabilities and 36,000 functional bugs across open-source projects since its inception [1]. Most fuzzing techniques, such as AFL [13], start from a seed input, generate new inputs by mutating the previous input, and add new inputs to the queue if they improve a given guidance metric, such as branch coverage.

However, applying these traditional testing approaches to specialized domains presents unique challenges, necessitating tailored solutions [185, 182, 28, 119]. Traditional software testing methods, including symbolic execution, fuzz testing, and differential testing, rely on assumptions that do not hold in heterogeneous computing. Symbolic execution, for example, struggles with the complexity of hardware-accelerated code due to its reliance on constrained symbolic reasoning, making it infeasible for analyzing optimized code running on GPUs, FPGAs, or quantum processors. Fuzz testing, which typically relies on random input mutation and branch coverage as a feedback metric, also faces fundamental limitations in heterogeneous environments. In traditional software, branch coverage is an effective measure of code exploration, but in hardware-accelerated computation, it often becomes meaningless. For example, in quantum computing, quantum circuits do not follow conventional branching logic—every operation in a quantum circuit executes simultaneously due to the inherent parallelism of quantum gates. This means that traditional branch coverage cannot provide useful feedback on test effectiveness, rendering conventional fuzzing techniques ineffective for exploring diverse execution behaviors in quantum and other heterogeneous systems.

Differential testing, which compares the outputs of multiple implementations to detect discrepancies, faces fundamental challenges in hardware-accelerated systems. Unlike traditional software, where execution is deterministic, heterogeneous computing involves nondeterministic factors such as hardware noise (e.g., quantum gate errors) and precision loss (e.g., floating-point rounding differences across CPUs and FPGAs). These factors introduce noise into differential outputs, making it difficult to distinguish true bugs from hardwareinduced variations.

To address the above challenges, we investigate the following hypothesis:

Sub-hypothesis 1: By understanding the quantum hardware characteristics, we can build efficient differential testing for quantum software stacks. We redesign *differential testing* approach for quantum software stacks (QSSes) with three major innovations: (1) We generate input programs to be tested via semantics-preserving transformation to explore program variants. (2) We speed up differential testing by filtering out quantum circuits that are unnecessary to execute on quantum hardware by analyzing static charac-

teristics such as the circuit depth, gate error rates, and T1 relaxation time. (3) We design an extensible equivalence-checking mechanism via distribution comparison functions such as Kolmogorov–Smirnov test.

We evaluate QDIFF with three widely-used open-source QSSes: Qiskit from IBM, Cirq from Google, and Pyquil from Rigetti. Our hypothesis is that by accounting for unique characteristics of quantum circuit execution and measurement, QDIFF can improve the efficiency of automated test input generation and the effectiveness of differential testing. By running QDIFF on both real hardware and quantum simulators, we found several critical bugs revealing potential instabilities in these platforms. QDIFF's source transformation is effective in producing semantically equivalent yet not-identical circuits (i.e., 34% of trials), and its filtering mechanism can speed up differential testing by 66%.

Understanding hardware accelerators is the first step toward enhancing the effectiveness of traditional testing approaches. Our work on QDIFF demonstrated that leveraging domainspecific hardware characteristics—such as quantum noise, circuit depth, and measurement fidelity—can significantly improve the efficiency of test input generation and bug detection in quantum software stacks. However, the challenges posed by hardware-accelerated computing extend beyond quantum processors to other specialized architectures, including FPGAs, GPUs, and TPUs.

Similar to quantum circuits, FPGA-based computations follow a fundamentally different execution model from traditional CPUs. FPGA kernels operate as dataflow-driven accelerators, where execution is dictated by hardware-encoded pipelines rather than sequential software instructions. This hardware specialization introduces two major challenges for traditional software testing methods. First, limited observability: unlike conventional programs, FPGA kernels lack internal execution visibility, making it difficult to detect silent failures, hangs, or incorrect outputs. Second, inefficient test generation: fuzzing for FPGA applications is constrained by slow host-device communication and the highly inefficient mutation that modifies input data at the bit level. We extended our focus to FPGA-based heterogeneous application testing, investigating the following hypothesis:

Sub-hypothesis 2: By understanding and leveraging the FPGA accelerators, we can build efficient fuzz testing for heterogeneous applications. Testing heterogeneous applications is extremely challenging: FPGA kernels are black boxes, revealing no information about the kernels' internal execution to help diagnose when the kernels silently hang or produce unexpected results. We propose HFUZZ to leverage hardware probes and acceleration for testing heterogeneous applications. The essence of HFUZZ is to introduce observability to FPGA kernels by combining host-side software monitors and device-side in-kernel hardware probes. Furthermore, HFUZZ speeds up iterative test generation with hardware acceleration by offloading input mutation from the host-side to the kernel-side.

Our hypothesis is that by designing hardware-level probes and offloading input mutations to hardware accelerators, HFUZZ can improve the efficiency and effectiveness of fuzz testing. We evaluate HFUZZ on seven real-world heterogeneous applications. HFUZZ speeds up fuzz testing by  $4.7 \times$  times with HW accelerated mutations. By incorporating HW probes in tandem with SW monitors, HFUZZ finds 33 kernel defects on the seven benchmarks within 24 hours and reveals 25 unique and unexpected behavior symptoms that could not be found by SW-based monitoring.

# 1.3 A bug isolation approach by considering multi-layer, extensible heterogeneous compilation

Exposing a bug is not the last step. Our collaboration with Intel partners revealed that merely triggering a bug is not enough—developers need more context to debug effectively. Heterogeneous compilers are specialized compilers designed to support diverse hardware architectures, such as CPUs, GPUs, FPGAs, and quantum accelerators. Unlike traditional compilers, which follow a linear pipeline to generate machine code for a single instruction set, heterogeneous compilers perform multiple layers of transformation and optimization, progressively lowering high-level abstractions to hardware-specific representations [88, 63].

MLIR (Multi-Level Intermediate Representation) [23] plays a crucial role in enabling this complexity by providing a flexible and extensible framework for heterogeneous compilation. MLIR structures compilation as a progressive lowering process, where code is transformed across multiple abstraction levels, from high-level domain-specific dialects to low-level hardware-specific IRs. This approach allows heterogeneous compilers to modularize transformations and optimizations, making it easier to support new hardware architectures. Such examples include Triton [155], CIRCT [63], and ONNX-MLIR [96]. Take CIRCT as an example; it offers domain-specific dialects for FPGA development, enabling high-performance hardware synthesis through structured transformations.

However, while MLIR improves the modularity and scalability of heterogeneous compilers, it also introduces new debugging challenges. The layered compilation flow makes it difficult to trace how a high-level operation is transformed through various IR stages, leading to bugs that are hard to localize. When a failure occurs in the low-level code, developers often lack visibility into which transformation, optimization pass, or lowering step introduced the issue. Manually inspecting the entire compiler stack—spanning multiple dialects, transformations, and hardware-specific optimizations—is impractical and time-consuming. A systematic approach is needed to localize the root cause at both the code dimension and the compilation dimension.

While existing delta debugging techniques can be used to identify a minimum subset of IR code that reproduces a given bug symptom, their naive application to MLIR is timeconsuming, because real-world MLIR compilers usually involve a large number of compilation passes and compiler developers must also identify a minimized set of relevant compilation passes simultaneously, in order to reduce the footprint of MLIR compiler code to be inspected for a bug fix. To address this challenge, we investigate the following hypothesis:

Sub-hypothesis 3: By understanding the relation between the IR code and multilayer heterogeneous compilers, we can build efficient debugging tool. We propose DUOREDUCE, a dual-dimensional reduction approach for MLIR bug localization. DUORE-DUCE leverages three key ideas in tandem to design an efficient MLIR debugger. First, DUOREDUCE reduces the bug-irrelevant compilation passes by identifying ordering dependencies among different compilation passes. Second, DUOREDUCE uses MLIR-semantics aware transformations to expedite IR code reduction. Finally, DUOREDUCE leverages crossdependence between the IR code dimension and the compilation passes to reduce the unused passes.

Experiments with three large-scale MLIR compiler projects find that DUOREDUCE outperforms syntax-aware reducers such as Perses and Vulcan in terms of IR code reduction by 31.6% and 21.5%, respectively. If one uses these reducers by enumerating all possible compilation passes (on average 18 passes), it could take up to 145 hours. By identifying ordering dependencies among compilation passes, DUOREDUCE reduces this time to 9.5 minutes. By identifying which compilation passes are unused for compiling reduced IR code, DUORE-DUCE reduces the number of passes by 14.6%. This translates to not needing to examine 281 lines of MLIR compiler code on average to fix the bugs. DUOREDUCE has the potential to significantly reduce debugging effort in multi-layer extensible compilers, which serves as an important basis for the current landscape of machine learning and hardware accelerators.

#### 1.4 Outline

The structure of this dissertation is outlined as follows. Chapter 2 introduces several related basic concepts. In Chapters 3 and 4, we delve into two testing methods for heterogeneous

computing: QDIFF for quantum software stacks, and HFUZZ for heterogeneous applications, Chapter 5 presents DUOREDUCE, the dual-dimensional bug isolation method for multi-layer compilers. Finally, we conclude and discuss future directions in Chapter 6.

# CHAPTER 2

## Background

There has been a growing interest in developing specializable hardware accelerators for domain-specific workloads for various performance and energy benefits [55, 59, 62]. As an example, FPGA can be easily customized to accelerate applications across a wide variety of domains [48, 60] at lower power and higher performance than general-purpose CPUs [49, 136, 79]. Major hardware vendors are offering or plan to offer packages that include both CPUs and FPGAs [67, 30]. Such hardware packages have also been made into all major clouds to accelerate various analytic and learning tasks.

FPGAs, for instance, can be easily customized to accelerate applications across diverse domains [48, 60], delivering higher performance and lower power consumption compared to general-purpose CPUs [49, 136, 79]. Recognizing these advantages, major hardware vendors have begun integrating CPUs and FPGAs into unified packages [67, 30]. These hybrid architectures are now widely available in all major cloud platforms to accelerate analytics and machine learning tasks.

In this section, I will introduce the traditional testing and debugging approach, and illustrate why they cannot work for heterogeneous domains.

### 2.1 Heterogeneous Computing: Context and Challenge

With the slowdown of Moore's Law—the observation that transistor density doubles approximately every two years—traditional CPU performance scaling has become increasingly difficult [129, 71]. There has been a growing interest in developing specializable hardware accelerators for domain-specific workloads for various performance and energy benefits [55, 59, 62]. As an example, FPGA can be easily customized to accelerate applications across a wide variety of domains [48, 60] at lower power and higher performance than general-purpose CPUs [49, 136, 79, 67, 30]

Heterogeneous architectures are now widely adopted across various computing domains:

- Machine Learning and AI: GPUs accelerate deep learning training and inference [97, 53].

- Scientific Computing: Supercomputers leverage GPUs and FPGAs for high-performance simulations, molecular dynamics, and climate modeling [70].

- Embedded & Edge Computing: FPGAs and custom ASICs (Application-Specific Integrated Circuits) are used in low-power, high-throughput applications such as autonomous vehicles, IoT devices, and robotics [122, 157].

- Quantum Computing: Quantum accelerators, such as IBM's Q System and Google's Sycamore, are emerging as promising alternatives for problems involving cryptography, optimization, and quantum chemistry [34, 135].

Despite their advantages, heterogeneous architectures pose several challenges, particularly in software testing and debugging. Traditional testing and debugging techniques struggle to handle the complexity of heterogeneous computing because hardware characteristics are not considered. For example, Symbolic testing, a widely used program analysis technique that systematically explores all possible execution paths by treating inputs as symbolic variables instead of concrete values [99, 37] cannot work because it struggles to model parallel, event-driven, and hardware-level execution effectively.

### 2.2 Quantum Computing & Quantum Software Stack

Quantum Computing. Quantum computing emerges as a promising technology for many domains where quantum computers have been demonstrated to outperform classical computers by a large margin. For example, Grover's algorithm [77] can find a given item in an unsorted database with a  $\sqrt{N}$ -times speedup when running on a quantum computer, compared to a classical computer. Similar to programs executed on heterogeneous devices such as FPGAs, a quantum application is comprised of *host code* that runs on CPU and *quantum code* that runs on quantum hardware. Generally, quantum computers work as accelerators to execute the compute-intensive parts of the original application. For example, the Shor algorithm [145] can achieve an exponential speedup by decomposing integer factorization into a reduction to be executed on a classical computer and an order finding problem to be executed on quantum hardware.

**Quantum Software Stack.** A quantum software stack (QSS) includes (1) APIs and language constructs to express quantum algorithms, (2) a compiler that transforms and optimizes a given input quantum algorithm at the circuit level, and (3) a backend executor that either simulates the resulting gates on classical devices or executes directly on quantum hardware. Currently, three most widely used QSSes are Qiskit, Cirq, and Pyquil [104].

- Qiskit [31] is an open-source framework developed by IBM. Qiskit provides a software stack that is easy to use quantum computers and facilitates quantum computing research. Qiskit consists of Qiskit Terra (compiler), Qiskit Aer (several quantum simulators), Qiskit Ignis (which supports error correction and noise characterization), and Qiskit Aqua (APIs to help developers write applications).

- Cirq [6] is an open-source Python framework from Google. It enables a developer to create and simulate Noisy Intermediate-Scale Quantum (NISQ) circuits. Cirq consists of an optimization component to compile and transform circuits, a simulator compo-

nent for emulating quantum computation on classical devices, and other development libraries for application development.

• **Pyquil** [58] is an open-source Python framework developed by Rigetti. It builds on Quil, an open quantum instruction language for near-term quantum computers, and uses a combined classical/quantum memory model. PyQuil is the main component of Forest, the overarching platform for Rigetti's quantum software. Pyquil consists of: quilc (compiler), qvm (quantum virtual machine with several kinds of simulators), and pyquil (a library to help users write and run quantum applications).

All three QSSes are similar to one another in that each includes a quantum programming language, an optimizing compiler that outputs quantum gate instructions, a quantum simulator that emulates these instructions on a classical device, and a software controller that executes gate instructions on quantum hardware.

As with any compiler framework, a QSS could be error-prone. Developers and users often report bugs on popular QSSes [7, 8, 31], and a simple search on StackOverflow with the keyword "quantum error" would bring up over 500 posts on various QSS components, ranging from compiler settings, simulation, and the actual hardware [14]. These posts often reveal deeper confusion that developers face due to the inherent probabilistic nature of quantum measurements—*if a program produces a result that looks different from what is expected, is it due to a bug or the non-determinism inherent in quantum programs? Is there divergence beyond expected noise coming from an input program, a compiler, a simulator, and/or hardware?*

#### 2.3 MLIR in Heterogeneous Computing

LLVM [74] and the Multi-Level Intermediate Representation (MLIR) [64] framework are gaining significant traction across a wide array of compilers for machine learning and heterogeneous computing. They have revolutionized modern compiler architectures with layered and extensible compiler development, by enabling custom extension of IRs. For example, Triton [155], a cutting-edge language and compiler for machine learning developed by OpenAI, leverages the MLIR framework to translate Python kernels into Triton's IR representation. This IR is then optimized through various transformation passes before being lowered to PTX assembly, which is then fed to the CUDA compiler. The increasing adoption of MLIR compiler projects such as Triton underscores the importance of *extensible* compiler design, particularly in the domain of machine learning and hardware accelerators, where the underlying IRs and key optimization strategies are rapidly evolving.

The CIRCT project [63] is an effort to apply MLIR and the LLVM development methodology to the domain of hardware design tools. They aim to have reusable infrastructure that is modular, uses library-based design techniques, is more consistent, and builds on the best practices in compiler infrastructure and compiler design techniques.

The multi-layer nature of MLIR-based compilers, where high-level representations are progressively lowered through multiple IR transformations, brings significant challenges to testing and debugging. Existing fuzzing techniques such as MLIRSmith [160], HirGen [121], CLSmith [113], NNSmith [116], Neuri [117], and Tzer [118] have made strides in compiler testing and validation.

# 2.4 Automated Testing Techniques for Heterogeneous Application

In software engineering, symbolic execution is a program analysis technique that systematically explores program paths by treating inputs as symbolic variables [37]. For example, KLEE [46] is an open-source symbolic execution engine designed for automatically generating test cases and detecting bugs in programs written in C and C++. GKLEE [109] extends symbolic execution to CUDA programs, enabling the analysis of GPU kernels for correctness and performance issues. SmarTest leverages symbolic execution for smart contract testing [147]. However, symbolic execution's applicability to heterogeneous computing is limited due to differences in execution models, memory architectures, and programming paradigms. Alternative approaches, such as fuzz testing, have gained more traction for validating software on GPUs, FPGAs, and quantum processors.

Traditional fuzzing starts from a seed input, runs the program on the selected input, generates new inputs by mutating the previous input, and adds new inputs to the queue if they improve a given guidance metric such as branch coverage. Instead of using coverage as guidance, several techniques use custom guidance mechanisms. UAFL [161] incorporates typestate properties and information flow analysis to detect the use-after-free vulnerabilities. BigFuzz [181] monitors dataflow operator coverage in tandem with branch coverage for dataflow-based analytics. For example, MemLock [166] employs both coverage and memory consumption metrics. AFLgo [41] extends AFL to direct fuzzing toward user-specified target sites. SiliFuzz [142] finds CPU defects by fuzzing software proxies, like CPU simulators or disassemblers, and then executing the accumulated test inputs (known as the corpus) on actual CPUs on a large scale. PerfFuzz [107] uses the execution counts of exercised instructions together with branch coverage to identify inputs revealing pathological performance. HeteroFuzz [182] generates concrete test inputs for heterogeneous applications to perform differential testing between CPU vs. CPU+FPGA. However, Although these techniques work effectively in their domains, none of them leverage hardware to speed up their approach with parallelism. In other words, they overlook the opportunities for hardware optimizations, as the mutations often consist of independent tasks that can be parallelized efficiently when offloaded to the hardware accelerator.

A fuzzing loop consists of multiple invocations of a target program with different inputs in an independent manner; thus, it provides a natural opportunity for parallelism. AFL++ [73] injects a fork server, which tells the target to fork itself to run, and thus realizes parallel fuzzing across multiple CPU cores or across a fleet of systems. For example, P-Fuzz [148] distributes unique seeds to run fuzzing in parallel, and PAFL [112] maintains global and local guiding information for synchronizing parallel fuzzing jobs. While these techniques accelerate fuzz testing through distributed computation on CPUs, their underlying principles can be adapted to hardware accelerators like FPGAs to design a more efficient and scalable fuzzing approach.

Coverage-guided greybox fuzzing adds test cases into the set of seeds if they exercise the new path or new behavior. However, most seeds exercise the same "high-frequency" paths. To explore more paths with the same number of tests, researchers develop strategies to select seeds wisely. AFLFast [42] models coverage-based greybox fuzzing as a Markov chain, and assigns different selection probabilities for different seeds. EcoFuzz [174] improves AFLFast's Markov chain model and presents a variant of the Adversarial Multi-Armed Bandit model. EcoFuzz sets three states of the seeds set and develops a unique adaptive scheduling algorithm. However, these traditional coverage-feedback techniques do not translate well to heterogeneous computing. Unlike conventional software, heterogeneous kernels execute at the hardware level, where all branches are typically exercised, providing no meaningful code coverage signal. Furthermore, kernel code running on accelerators (e.g., GPUs, FPGAs) is often treated as a black box, offering no direct execution feedback that fuzzers can use for guidance. To enable effective fuzzing for heterogeneous computing, a new approach is required—one that extracts meaningful execution feedback from kernel code and provides guidance for exploring diverse execution behaviors beyond simple control-flow coverage.

## 2.5 Testing and Verification for Quantum

Zhao [184] introduces a quantum software life cycle and lists the challenges and opportunities we face. Long et al. [120] introduce quantum-specific testing principles and criteria for quantum program testing. Ying et al. [173] formally reason about quantum circuits by representing qubits and gates using matrix-valued Boolean expressions, and verify them using a combination of classical logical reasoning and complex matrix operations. Huang et al. [86] introduce quantum program assertions, allowing programmers to decide if a quantum state matches its expected value. They define a logic to provides  $\epsilon$ -robustness to characterize the possible distance between an ideal program and an erroneous one. Proq [111] is a runtime assertion framework for testing and debugging quantum programs. It transforms hardware constraints to executable versions for measurement-restricted quantum computers. QPMC [72] applies classical model checking on quantum programs based on Quantum Markov Chain. Ali et al. [32] propose a new testing metric called quantum input-output coverage, a test generation strategy, and two new test oracles for testing quantum programs. Two test oracles include *wrong output oracle*, which checks whether a wrong output has been returned, and *output probability oracle* which checks whether the quantum program returns an expected output with its corresponding expected probability. However, their work targets at quantum program testing, and the measurement they used might not be sufficient.

Verified quantum compilers guarantee gate transformation and circuit optimization is correct by construction. CertiQ [144] is a verified Qiskit compiler by introducing a calculus of quantum circuit equivalence to check the correctness of compiler transformation. VOQC [82] provides a verified optimizer for quantum circuits by adapting CompCert [108] to the quantum setting. Smith and Thornton [146] present a compiler with built-in translation validation via QMDD equivalence checking. However, verifying large-scale quantum circuits remains a major challenge. However, verifying large-scale quantum compilers remains a major challenge. As quantum circuits grow in size, their unitary representations expand exponentially, making equivalence checking computationally infeasible [186]. Without scalable verification techniques, ensuring correctness for real-world, large-scale quantum compilers and applications remains an open problem.

Given the scalability limitations of traditional verification techniques for quantum compilers, differential testing emerges as a superior alternative due to its ability to validate compiler correctness without requiring full formal verification or exponential equivalence checking [124, 151]. It has been used to test large software systems and to find bugs in various domains such as SSL/TLS [45, 134], machine learning applications [78], JVM [54], and clones [183], etc. Equivalence modulo inputs (EMI) [105] is such an example that tests compilers by generating equivalent variants. Many random program generators are used for compiler testing [52]. Csmith [172] randomly generates C programs and checks for inconsistent behaviors via differential testing. Quest [115] focuses on argument passing and value returning, while testing with randomly generated programs. Different from Csimth-like tools, refactoring-based testing systematically modifies input programs with refactorings, as opposed to random program generation. Orion [105] adapts EMI to test GCC and LLVM compilers. Christopher et al. [113] combine random differential testing and EMI-based testing to test OpenCL compilers. Orison [106] uses a guided mutation strategy for the same purpose. Mucerts [51] applies differential testing to check the correctness of certificate validation in SSL/TLS. It uses a stochastic sampling algorithm to drive its input generation while tracking the program coverage. DLFuzz [78] does fuzz testing of Deep Learning systems to expose incorrect behaviors. Chen et al. [54] perform differential testing of JVM with input generated from Markov Chain Monte Carlo sampling with domain-specific mutations with the knowledge of Java class file formats.

Such classical compiler testing is not directly applicable to quantum software stacks due to the three challenges: (1) how to generate variants, (2) how to test simulators and hardware together with compilers, and (3) how to interpret quantum measurements for differential testing.

Based on my work QDiff [164], MorphQ [133] leverages equivalent quantum gate transformations to detect bugs in quantum compilers such as Qiskit [29], demonstrating the effectiveness of differential testing in identifying miscompilations in quantum software stacks.

## 2.6 Automated Debugging in Heterogeneous Domains

To ease the development of heterogeneous applications, HLS tools automatically generate RTL descriptions from C/C++ programs. To help debugging HLS-generated circuits, *Inspect* [47] introduces software debugger-like capabilities, including gdb-like breakpoints, step, and data inspection. It tracks file names and line numbers in HLS code, so that HW probes at the level of wires and registers could be linked to specific lines in the HLS code. A user can monitor each variable for its data width and the number of elements in an array. Monson and Hutchings [128] design a debugger for HLS-generated FPGA-based circuits via source instrumentation by connecting C expressions to top-level ports that serve as debug signals. HLScope [56] is a performance debugger that traces the cause of stalls for HLS-generated circuits. Curreri et al. realize in-circuit assertions for timing analysis and stall-relate bugs [66].

In traditional software engineering, taint analysis and program slicing are widely used in automated debugging [130, 156, 40, 168]. For example, Wang et al. [165] used taint analysis to localize bugs in configuration options. Soremekun et al. [149] did an empirical study on how program slicing can be applied on locating real-world faults. Badihi et al. [36] developed a program slicing based debugger for java. While program slicing and taint analysis are effective in traditional debugging, they fail in multi-layer heterogeneous compilation debugging, whereas delta debugging succeeds. Taint tracking assumes a direct mapping between input and output variables, but heterogeneous compiler optimizations break this assumption. Constant propagation, register allocation, and strengthening reduction may directly rewrite expressions with hardware resource specification. Program slicing works best when explicit control-flow dependencies exist. However, many compiler passes eliminate, reorder, or replace control structures, making it impossible to extract an accurate slice. Delta debugging, however, instead of following control/data dependencies, simply removes pieces of the input program until the bug disappears.

Delta debugging is a seminal work for input reduction to identify the minimal failure-

inducing changes between two program versions [178, 176]. Based on *ddmin*, Ghassan et al. developed Hierarchical Delta Debugging (HDD) [127]. It applies delta debugging at each level of a program's input, working from the coarsest to the finest levels. Recent work proposed several enhancements on HDD [83, 84, 100]. ProbDD [159] is a probabilistic DD algorithm that learns from testing history to select elements based on probabilities. RCC [153] uses ZIP and SHA to compress the generated variants to speed up program reduction. Perses [150] ensures that each reduction step considers only syntactically valid variants to avoid futile effort on syntactically invalid variants and was later extended to specific domains [180, 154]. None of these reducers can handle bug isolation across two dimensions: code and compilation pass. Existing DD is inefficient for today's extensible multi-layer compilation and can take up to 145 hours to isolate culprit compilation passes along with the minimized IR program.

Many delta debugging tools consider the underlying language feature and apply various program transformations to decompose an input program into fine-granular units [69]. Vulcan [171] applies general code program transformations including identifier and subtree replacement. LPR [179] combines LLMs and language-generic reduction tools to refine the results of program reduction. C-Reduce [137] tackles this problem by leveraging domain-specific program transformations to reduce C/C++ programs. J-Reduce [98] and ddSMT [132] serve as the domain-specific reducers for Java and SMT-LIBv2. CHISEL [81] uses reinforcement learning in the C programming to select steps in *ddmin* that are more likely to satisfy the target oracle.

MLIR is widely adopted in heterogeneous compilation because it provides a modular IR infrastructure that spans multiple abstraction levels, from high-level computational graphs to low-level hardware instructions. However, debugging MLIR-based compilers poses unique challenges.

• Multi-Layer Transformations: MLIR enables a layered compilation flow where highlevel representations progressively transform into low-level IRs, making it difficult to trace how errors propagate across different passes. • Interaction Between Passes: Compiler bugs often emerge due to unintended interactions between optimization passes, making it essential to consider dependencies between transformations rather than debugging individual passes in isolation.

The MLIR and CIRCT projects also develop their own debugger utilities [63, 64]. They provide useful mechanisms for isolating faults but lack dependency-aware debugging approaches that account for the interactions between compilation passes and their effect on program correctness.

Given these challenges, a new debugging approach is needed—one that explicitly considers the dependency relationships between compilation passes and between compiled code and its transformations.

## CHAPTER 3

# QDiff: Redesign Differential Testing for Quantum Computing

As a first step toward building software support for heterogeneous systems, we focus on providing compiler testing support for quantum software stacks. A quantum software stack (QSS) includes (1) APIs and language constructs to express quantum algorithms, (2) a compiler that transforms and optimizes a given input quantum algorithm at the circuit level, and (3) a backend executor that either simulates the resulting gates on classical devices or executes directly on quantum hardware. Quantum computing, as an emerging field, currently lacks robust compiler and system testing frameworks. However, testing quantum software stacks poses significant challenges. The probabilistic nature of quantum computing results makes it difficult to determine whether unexpected outputs are due to the inherent quantum randomness or actual bugs in the software stack. Furthermore, the noisy nature of contemporary quantum hardware complicates the detection of software bugs from hardwareinduced errors.

In this chapter, we address the following research question: What kinds of hardware accelerator characteristics can be leveraged to filter out hardware noise and accurately identify software bugs? To address this problem, we investigate the sub-hypothesis: By understanding the quantum hardware characteristics, we can build efficient differential testing for quantum software stacks. Building on the insights discussed in Section 3.4, we redesign differential testing frameworks to account for T1 time and 2-qubit gate number, which are the main sources of the quantum hardware noise, enabling more effective identification of software

bugs while mitigating the impact of hardware noise.

## 3.1 Introduction

As with any heterogeneous compiler framework, a Quantum Software Stack could be errorprone. Developers and users often report bugs on popular QSSes [7, 8, 31]. A bug in a QSS can be just as severe as a miscompilation in a traditional compiler, potentially leading to incorrect quantum computations or silent failures. For example, In Qiskit, the transpile function is used to transform quantum circuits into a form that is compatible with a specific quantum backend. However, a bug was identified where the transpilation process fails when handling parameterized delay instructions [16].

We evaluated QDIFF with the latest versions of three widely-used QSSes: Qiskit, Cirq, and Pyquil. With six seed quantum algorithms, QDIFF generates 730 variant algorithms through semantics-modifying mutations. Starting from the generated algorithms, it generates a total of 14799 program variants using semantics-preserving source transformations. This generation process took QDIFF 14 hours. With the filtering mechanism, QDIFF reduces its testing time by 66%. Using QDIFF, we determined total 6 sources of instabilities. These include 4 software crash bugs in Pyquil and Cirq simulation, and 2 potential root causes that may explain 25 out of 29 cases of divergence beyond expected noise on IBM hardware.

### 3.2 Background

**Quantum Bit.** A quantum bit, or qubit for short, is the basic unit of quantum computation. Unlike a classical bit that is either 0 or 1, a qubit's state is a probabilistic function of  $|0\rangle$  and  $|1\rangle$ , represented as:

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle$$

, where  $|\alpha|^2 + |\beta|^2 = 1$  (3.1)

The state of a qubit is unknown until a *measurement* is completed, resulting in  $|\alpha|^2$  to be 0 and  $|\beta|^2$  to be 1. Naturally, the sum of the probabilities (i.e., the modulus squared of amplitudes) is 1:  $|\alpha|^2 + |\beta|^2 = 1$ .

**Quantum Gate.** Classical computers use logic gates to transform signals from input wires. For example, a *NOT* gate, also known as an inverter, takes a single signal as input and outputs the opposite value. The quantum gate analogous to *NOT* is an X gate, which transforms a qubit  $\alpha |0\rangle + \beta |1\rangle$  to  $\beta |0\rangle + \alpha |1\rangle$ .

An X gate has the following matrix-based representation:

$$X = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$$

(3.2)

Using a vector to represent the quantum state  $\alpha |0\rangle + \beta |1\rangle$ , applying an X gate has the following effect:

$$X\begin{bmatrix}\alpha\\\beta\end{bmatrix} = \begin{bmatrix}\beta\\\alpha\end{bmatrix} = \begin{bmatrix}\alpha'\\\beta'\end{bmatrix}$$

(3.3)

Other commonly-used quantum gates include H, T, CNOT, Z, CZ, S, U1, and U3; a full explanation of these gates is elsewhere [131].

Since all quantum gates can be represented as *matrices*, we can transform a sequence of gates to another logically equivalent sequence without altering its outcome, as long as *the multiplication of the matrices for gates in each sequence* produces the same result. As an example, a SWAP gate, a two-qubit gate that swaps the two qubits' states, is semantically equivalent to a sequence of three CNOT gates.

$$SWAP(q_1, q_2) = CNOT(q_1, q_2)CNOT(q_2, q_1)CNOT(q_1, q_2)$$

(3.4)

This observation forms the foundation of QDIFF's program variant generation procedure, detailed in Section 3.4.

```

1 def make_circuit() -> QuantumCircuit:

```

- 2 qubit = QuantumRegister(2,"qc")

- 3 bit = ClassicalRegister(2, "qm")

- 4 prog = QuantumCircuit(qubit, bit)

- 5 prog.h(qubit[0])

- 6 prog.x(qubit[1])

```

7 for i in range(2):

```

```

8 prog.measure(qubit[i], bit[i])

```

```

9 return prog

```

(a) A quantum circuit with an H gate and an X gate.

```

1 prog = make_circuit()

2 backend = BasicAer.get_backend('qasm_simulator')

3 info = execute(prog, backend=backend, shots=1000).result().get_counts()

```

(b) The host code using the circuit in (a).

Figure 3.1: An example Qiskit program.

**Quantum Circuit.** A quantum circuit consists of a set of connected quantum gates. Since quantum gates can be represented as unitary matrices, a quantum circuit is essentially the multiplication of the matrices.

Figure 3.1a shows a program in IBM's Qiskit [31]. It first registers two qubits and initializes them to  $|0\rangle$ . Next, an H gate sets the first qubit into state  $\frac{1}{\sqrt{2}}|0\rangle + \frac{1}{\sqrt{2}}|1\rangle$  and an X gate flips the second qubit from  $|0\rangle$  to  $|1\rangle$ . Finally, a measurement is performed and stored in a classical array. The function returns this circuit as a function-type value.

Figure 3.1b shows host code that calls this quantum circuit. Users can execute this circuit on different backends such as real quantum hardware or simulators. The circuit is executed on *qasm\_simulator* for a thousand times (shots=1000). Since the first qubit state is  $\frac{1}{\sqrt{2}}|0\rangle + \frac{1}{\sqrt{2}}|1\rangle$  and the second qubit state is  $|1\rangle$ , each run produces a result of either  $|01\rangle$  or  $|11\rangle$  with the equal probability of  $0.5 = (\frac{1}{\sqrt{2}})^2$ .

| Layers                  | Percentage | Example                                  |

|-------------------------|------------|------------------------------------------|

| Compiler (optimizations | 53.9%      | MergeInteractions() returns different    |

| & settings)             |            | results for the same circuit [9].        |

| Backend (simulators     | 19.7%      | Simulators change a global random        |

| & hardware)             |            | state on Cirq [2].                       |

| API and quantum gate    | 11.8%      | PhasedXPowGate raised to a symbol power  |

|                         |            | fails the is_parameterized protocol [3]. |

Table 3.1: Different layers that bugs appear

**T1 relaxation time.** In quantum computing, a qubit can retain data for only a limited amount of time, referred to as *relaxation Time* because a qubit in a high-energy state (state  $|1\rangle$ ) naturally decays to a low-energy state (state  $|0\rangle$ ). The time span for this decay is referred to as *T1 Relaxation Time*. For a physical circuit, its measurement results are unreliable if its execution time is longer than *T1*.

## 3.3 Motivation

To understand real-world QSS bugs, we collected 76 latest issues reported on Github Pyquil, Cirq, and Qiskit. After excluding 11 issues related to installation and other tools, we categorized the remaining 65 issues by the layer where each issue appears: compilers, backends, and APIs.

Table 3.1 summarizes the percentage of the corresponding layer and a representative example. Most bugs appear at the compiler level—compiler optimizations and settings. For example, Cirq produces incorrect circuits when using MergeInteractions() [9]. The second most common bugs appear at the backend level—simulators and hardware execution, *e.g.*, the initial state is unexpectedly modified by the Cirq simulator in [2]. The other issues are with respect to the API implementation of high-level gates. For example, in

Figure 3.2: QDIFF overview

Cirq, when cirq.PhasedXPowGate is invoked with an input argument exponent, invoking is\_parameterized on the resulting gate should return true but returns false due to a bug in cirq.PhasedXPowGate.

The aforementioned bugs are hard to find due to quantum indeterminacy. The following excerpt illustrates a concrete example of how one google tutorial user is confused whether a problem is a bug or due to inherent non-determinism. Cirq's VQE (Variational-Quantum-Eigensolver) tutorial had a mistake—the orders of mix layer and cost layer were described in a wrong order. The tutorial user D (shortened) posted a question on StackExchange [4] with the embedded code from Cirq's VQE tutorial. A Cirq developer C (shortened) noticed that "The strange thing is the example output shows the output probabilities varying with gamma (the CZ parameter)", where gamma should not have any effect on the measurement results." D actually believed the disagreement is due to quantum indeterminacy, until C explicitly labeled it as a compiler bug.

| Framework                        | Options                               | Description                                   |

|----------------------------------|---------------------------------------|-----------------------------------------------|