### UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Design and Analysis of Digitally Modulated Transmitters for Efficiency Enhancement

### Permalink

https://escholarship.org/uc/item/98s794p9

### Author

YE, LU

## Publication Date 2013

Peer reviewed|Thesis/dissertation

### Design and Analysis of Digitally Modulated Transmitters for Efficiency Enhancement

by

Lu Ye

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

$\mathrm{in}$

#### Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor Paul Wright

Spring 2013

### Design and Analysis of Digitally Modulated Transmitters for Efficiency Enhancement

Copyright 2013 by Lu Ye

#### Abstract

Design and Analysis of Digitally Modulated Transmitters for Efficiency Enhancement

by

Lu Ye

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Ali M. Niknejad, Chair

The last decade has witnessed a tremendous growth in wireless communications. Consumer demands for battery-operated mobile devices with versatile, high data-rate communication capabilities that are of low cost, small form-factor and long operating cycle have motivated the research on fully-integrated, back-off-efficient and coexistence-friendly wireless transceivers in CMOS VLSI technology. However, the full integration of an efficient CMOS power amplifier (PA) into such a transceiver is still among the most difficult challenges towards a true System-On-Chip (SOC) solution. This thesis investigates the PA efficiency enhancement techniques for a complete power transmitter system that is fully-integrated and coexistable. Direct digitally modulated transmitter architecture has been identified as one of the most promising solutions to the above challenges. Within such a transmitter, the PA efficiency is able to back off from a high peak efficiency at least with class-B characteristic; meanwhile, the transmit linearity can be more easily improved by digital predistortion due to the direct digital modulation scheme. To validate such a promising architecture, we have built a fully-integrated CMOS digital power transmitter for the IEEE 802.11g 54Mbps application. System-level considerations and design choices are presented with an aim for low out-of-band noise and good transmit linearity. As the core of the transmitter, the RF switching PA is designed for high efficiency with minimum number of on-chip passives that only exercise an accurate control over fundamental and second-harmonic terminations. The class-B efficiency back-off characteristic is further improved by a dynamic impedance modulator which boosts the PA drain impedance at a low instantaneous envelope level. Open-loop phase interpolator based topology is used for the polar phase modulator, which achieves wideband phase modulation with competitive power consumption. Digital baseband filtering is fully optimized at both the algorithm and the hardware level, which offers larger than 60dB attenuation on the close-in spectral images with reduced filter complexity. The prototype has been implemented in a 65nm bulk CMOS technology and has demonstrated a combination of good output power, overall efficiency and spectral purity with a very high level of system integration.

To the loving memory of my maternal grandfather (2000), grandmother (2013), and my mother-in-law (2008). To the memory of the good, old days.

## Contents

| C  | ontents                                                                                                                                                                                           | ii                                            |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Li | ist of Figures                                                                                                                                                                                    | v                                             |

| Li | ist of Tables                                                                                                                                                                                     | ix                                            |

| Ι  | Introduction and Background Studies                                                                                                                                                               | 1                                             |

| 1  | Introduction         1.1 Thesis Organization                                                                                                                                                      | <b>2</b><br>6                                 |

| 2  | Overview of Efficiency Enhancement Techniques at Back-off Output Powers2.1Efficiency Back-off of Class-A, Class-B and Class-AB PAs                                                                | 7<br>9<br>15<br>22<br>25<br>30<br>35          |

| II | Design of Digitally Modulated TX for Efficiency Enhance-<br>ment                                                                                                                                  | 37                                            |

| 3  | TX System Level Considerations3.1 Target Application: IEEE 802.11g3.2 Spectral Purity for Coexistence3.3 TX System Overview3.4 Crest Factor Reduction3.5 Amplitude Resolution3.6 Phase Resolution | <b>38</b><br>38<br>39<br>41<br>43<br>46<br>48 |

|          | $3.11 \\ 3.12$ | Bandwidth Expansion due to Transmit Predistortion       5         Baseband Output Sample Rate       5         Filter-First and Filter-Last Architecture       5         Baseband Input Sample Rate       5         AM/PM Delay Alignment       5 | 49<br>52<br>53<br>55<br>57<br>58<br>52 |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4        |                | 5                                                                                                                                                                                                                                                | 63                                     |

|          | 4.1            | 0 1                                                                                                                                                                                                                                              | 64                                     |

|          |                | 4.1.1 Transistor as Voltage Switch or Current Switch?                                                                                                                                                                                            | 54                                     |

|          |                | 0 0                                                                                                                                                                                                                                              | 64                                     |

|          |                | 4.1.3 Zero Voltage Slope Switching?                                                                                                                                                                                                              | 35                                     |

|          |                | 4.1.4 Half-Wave Rectified Sinusoidal Drain Voltage                                                                                                                                                                                               | 35                                     |

|          |                | 4.1.5 Ideal Inverse-Class-D/F with Finite Switch On-Resistance 6                                                                                                                                                                                 | 56                                     |

|          | 4.2            |                                                                                                                                                                                                                                                  | 58                                     |

|          |                | 4.2.1 Number of Harmonics To Be Controlled                                                                                                                                                                                                       | 58                                     |

|          |                | 4.2.2 Choice of Device Width for Efficiency                                                                                                                                                                                                      | 71                                     |

|          |                |                                                                                                                                                                                                                                                  | 71                                     |

|          | 4.3            | A Simplified Design Methodology for An RF Switching PA with Limited Con-                                                                                                                                                                         |                                        |

|          |                | trollability Over Harmonic Terminations                                                                                                                                                                                                          | 72                                     |

|          |                | 4.3.1 Impedance level and Device Size                                                                                                                                                                                                            | 72                                     |

|          |                | 4.3.2 Insensitivity of Efficiency and Output Power with Fixed Harmonic                                                                                                                                                                           |                                        |

|          |                | Tuning Frequencies                                                                                                                                                                                                                               | 73                                     |

|          |                | 4.3.3 Sensitivity of Efficiency and Output Power to Harmonic Tuning Fre-                                                                                                                                                                         |                                        |

|          |                |                                                                                                                                                                                                                                                  | 75                                     |

|          | 4.4            | Effect of PA Input Drive Characteristics                                                                                                                                                                                                         | 77                                     |

|          | 4.5            | Capacitive Feedforward for Cascode Parasitics                                                                                                                                                                                                    | 78                                     |

|          | 4.6            | -                                                                                                                                                                                                                                                | 30                                     |

|          | 4.7            | Conclusion                                                                                                                                                                                                                                       | 30                                     |

|          |                |                                                                                                                                                                                                                                                  |                                        |

| <b>5</b> | Trar           | 1                                                                                                                                                                                                                                                | 32                                     |

|          | 5.1            |                                                                                                                                                                                                                                                  | 32                                     |

|          |                | 1                                                                                                                                                                                                                                                | 33                                     |

|          | 5.2            | 1 0                                                                                                                                                                                                                                              | 37                                     |

|          |                | 8                                                                                                                                                                                                                                                | 37                                     |

|          |                | 5.2.2 Efficiency Loss in Backoff Mode                                                                                                                                                                                                            | 38                                     |

|          | 5.3            | 0.0                                                                                                                                                                                                                                              | 90                                     |

|          | 5.4            | Conclusion                                                                                                                                                                                                                                       | 90                                     |

| 6        | One            | n-Loop Phase Modulator 9                                                                                                                                                                                                                         | 92                                     |

| U        | 6.1            | -                                                                                                                                                                                                                                                | )2                                     |

|          | 0.1            |                                                                                                                                                                                                                                                  | 14                                     |

|    | $     \begin{array}{r}       6.2 \\       6.3 \\       6.4 \\       6.5 \\       6.6 \\     \end{array} $ | Phase Resolution and Current-DAC Mismatch                         | 92<br>93<br>95<br>96<br>97                |

|----|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------|

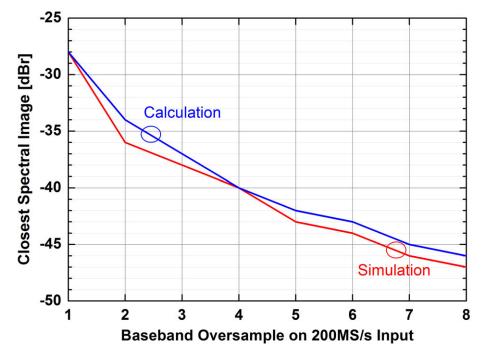

| 7  | Bas                                                                                                       | eband Digital Filtering                                           | 98                                        |

|    | 7.1                                                                                                       | Choice of Nyquist Filter Type                                     | 98                                        |

|    | 7.2                                                                                                       | Nyquist Filter Specification                                      | 98                                        |

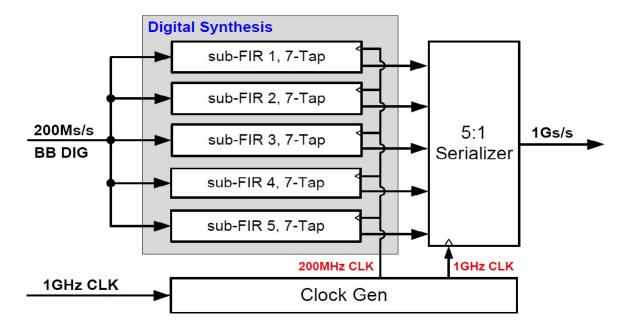

|    | 7.3                                                                                                       | Poly-Phase Decomposition                                          | 99                                        |

|    |                                                                                                           | 7.3.1 Poly-Phase Decomposition for Up-Sampling by Zero Insertion  | 100                                       |

|    |                                                                                                           | 7.3.2 Poly-Phase Decomposition for Up-Sampling by Zero-Order-Hold | 103                                       |

|    | 7.4                                                                                                       | Measure of Filter Complexity                                      | 104                                       |

|    | $7.5 \\ 7.6$                                                                                              | Filter Synthesis with A Minimum Number of SPT Terms               | $\begin{array}{c} 105 \\ 105 \end{array}$ |

|    | 7.0 $7.7$                                                                                                 | Pipelining for Synthesis Timing Closure                           | $\frac{105}{106}$                         |

|    | 7.8                                                                                                       | Amplitude Filter with Waveform Smoother                           | $100 \\ 107$                              |

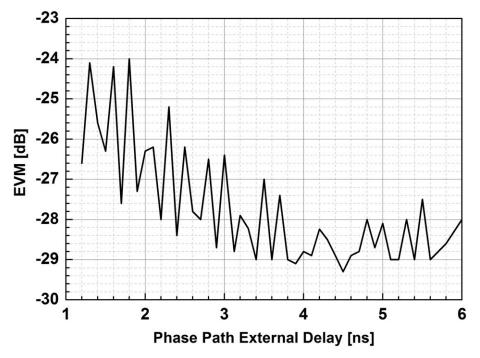

|    | 7.9                                                                                                       | Filtering on the Phase Path                                       | 101                                       |

|    | 7.10                                                                                                      | Conclusion                                                        | 108                                       |

| 8  | Mea                                                                                                       | surement Results                                                  | 110                                       |

|    | 8.1                                                                                                       | Measurement Setup                                                 | 110                                       |

|    | 8.2                                                                                                       | Continuous-Wave Test                                              | 110                                       |

|    | 8.3                                                                                                       | Modulated Signal Test                                             | 113                                       |

|    | 8.4                                                                                                       | Comparison with State-of-Art                                      | 114                                       |

|    | 8.5                                                                                                       | Conclusion                                                        | 116                                       |

| 9  | Con                                                                                                       | clusion                                                           | 119                                       |

|    | 9.1                                                                                                       | Thesis Summary                                                    | 119                                       |

|    | 9.2                                                                                                       | Future Directions                                                 | 120                                       |

| Bi | bliog                                                                                                     | raphy                                                             | 122                                       |

## List of Figures

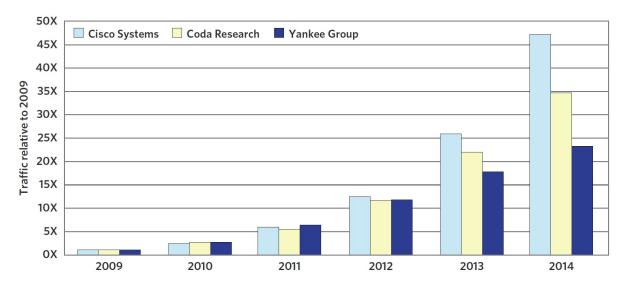

| 1.1  | Industry forecast of mobile data traffic from 2009 to 2014 $([1])$                  | 2  |

|------|-------------------------------------------------------------------------------------|----|

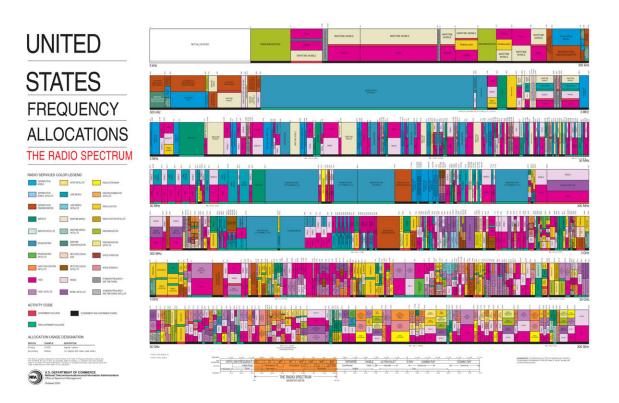

| 1.2  | United States frequency allocations                                                 | 3  |

| 1.3  | Theoretical throughputs of a single spatial stream for IEEE 802.11ac                | 4  |

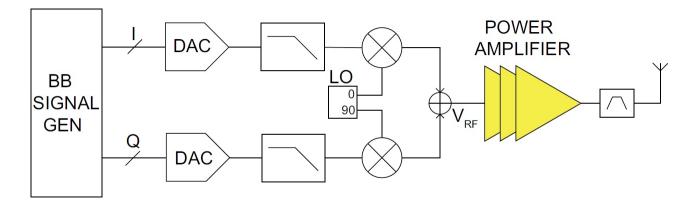

| 1.4  | A generic Cartesian transmitter [2]                                                 | 4  |

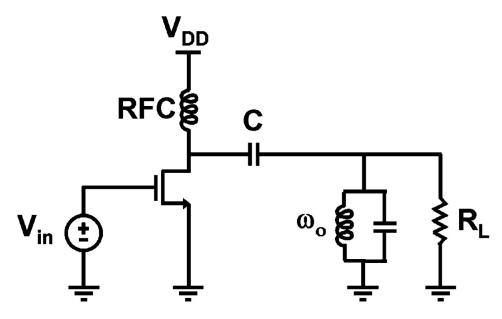

| 2.1  | A generic class-A power amplifier with RF-choke (RFC) [3]                           | 8  |

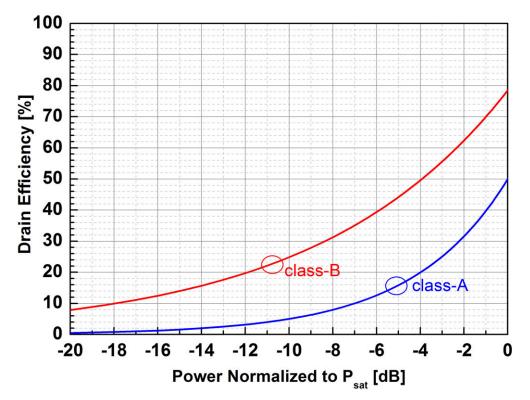

| 2.2  | The drain efficiency of an ideal class-A and class-B power amplifier                | 10 |

| 2.3  | An adaptive current biasing scheme for the class-AB PA [4]                          | 11 |

| 2.4  | Adaptive current bias control implemented with a feedback loop [4]                  | 12 |

| 2.5  | Dynamic current bias control implemented with a feedforward path [5]                | 12 |

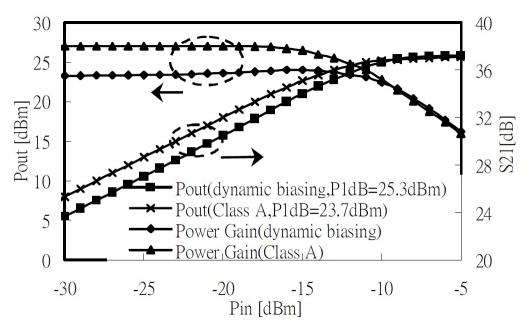

| 2.6  | The measured large-signal gain flatness is improved by dynamic current biasing [5]. | 13 |

| 2.7  | The measured EVM and PAE are improved by dynamic current biasing [5]                | 13 |

| 2.8  | Dynamic current biasing implemented by an aux-PA biased differently [6]             | 14 |

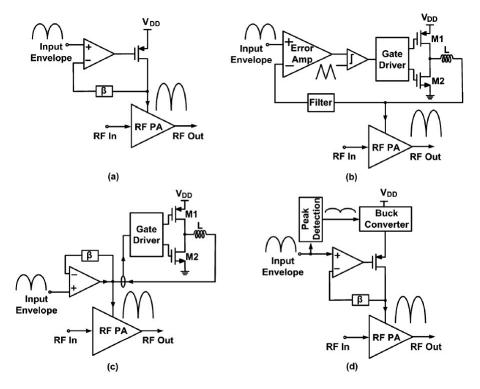

| 2.9  | An Envelope Elimination and Restoration (EER) TX [7]                                | 16 |

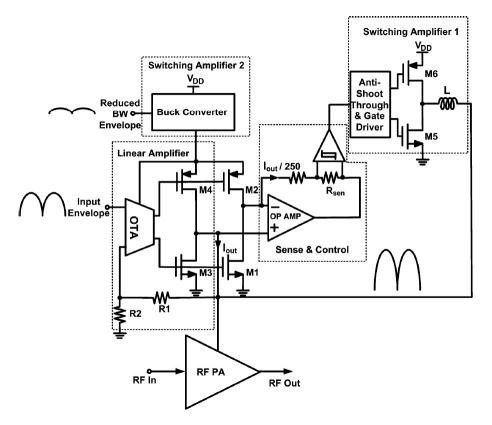

| 2.10 | Supply regulators constructed from linear and switching amplifiers [8]              | 17 |

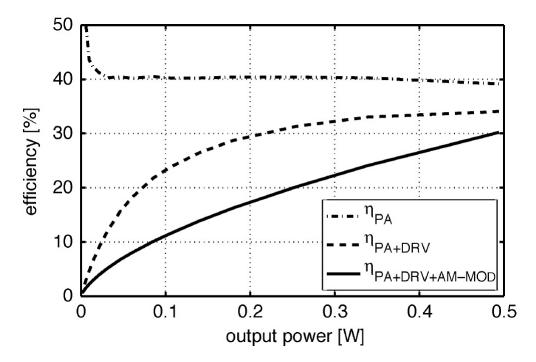

| 2.11 | The efficiency of PA-only and PA with linear regulator in an EER system [9].        | 18 |

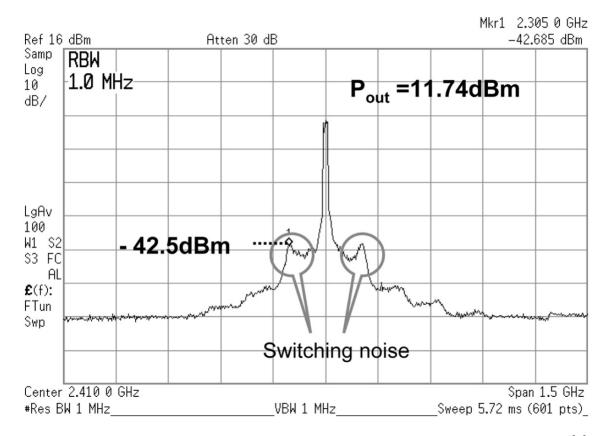

| 2.12 | Noise humps in the transmit spectrum due to switching regulator [7]                 | 19 |

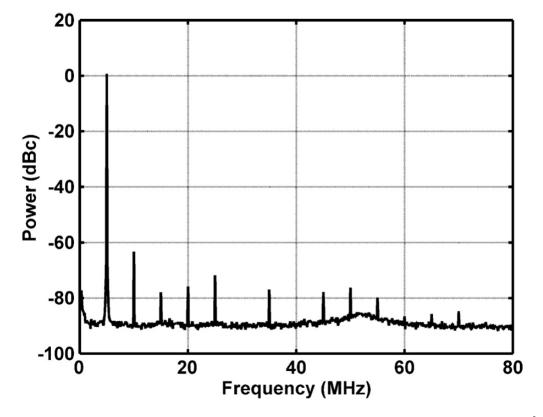

| 2.13 | Noise spurs in the transmit spectrum due to switching regulator [8]                 | 20 |

| 2.14 | A combined series-parallel hybrid supply regulator [8]                              | 21 |

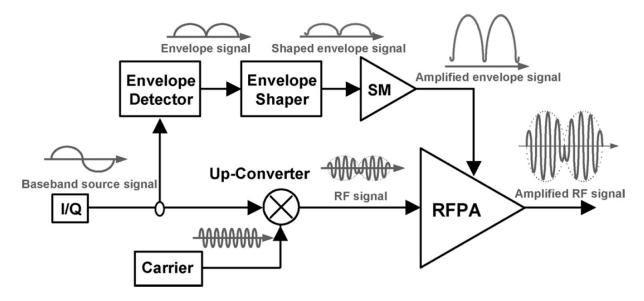

| 2.15 | An Envelope Tracking (ET) TX [10]. $\ldots$                                         | 22 |

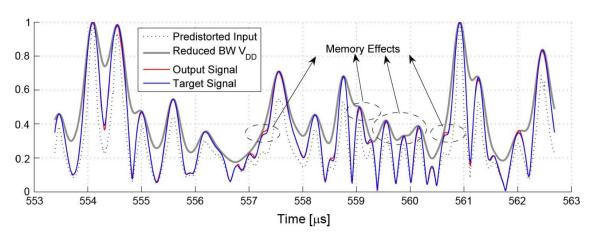

| 2.16 | Time domain waveforms of the target, output, reduced bandwidth supply, and          |    |

|      | predistorted RF input envelope in an ET system [11]                                 | 23 |

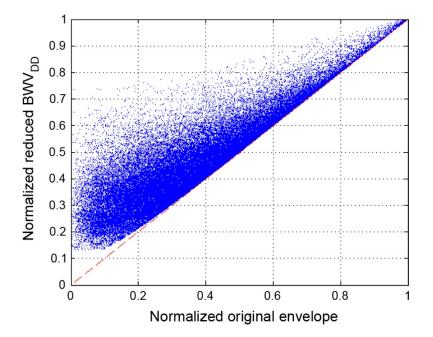

| 2.17 | The supply voltage corresponding to a particular envelope level has a wide spread   |    |

|      | in an ET system $[11]$                                                              | 24 |

|      | Digital predistortion for an envelope tracking PA [11]                              | 25 |

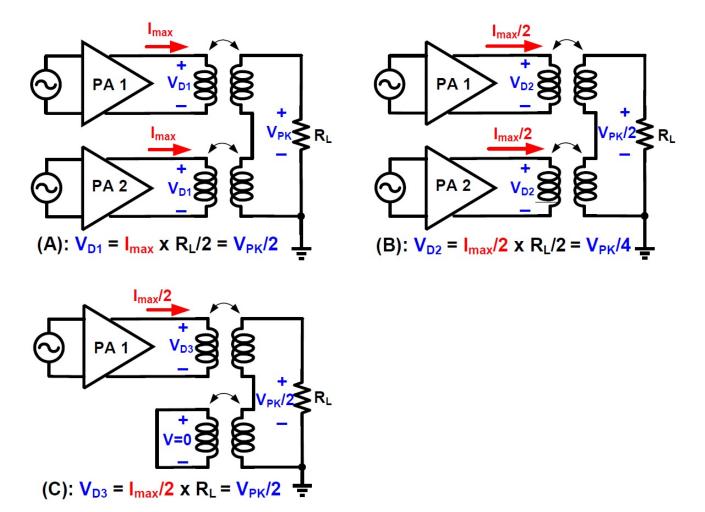

| 2.19 | Efficiency enhancement through boosted drain impedance                              | 26 |

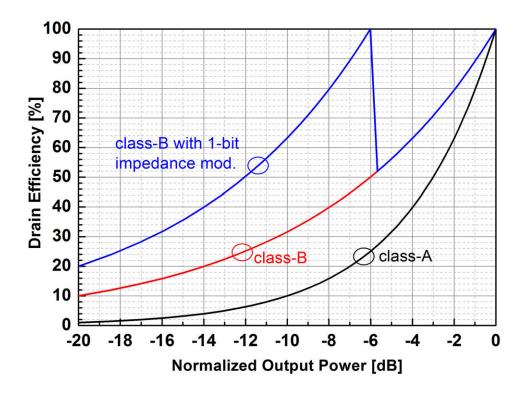

| 2.20 | Efficiency back-off characteristics for an ideal class-A, class-B and class-B PA    |    |

|      | with 1-bit drain impedance modulation                                               | 30 |

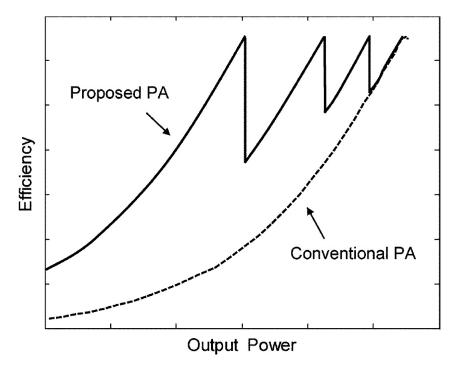

|      | Efficiency enhancement through multi-level drain impedance modulation [12].         | 31 |

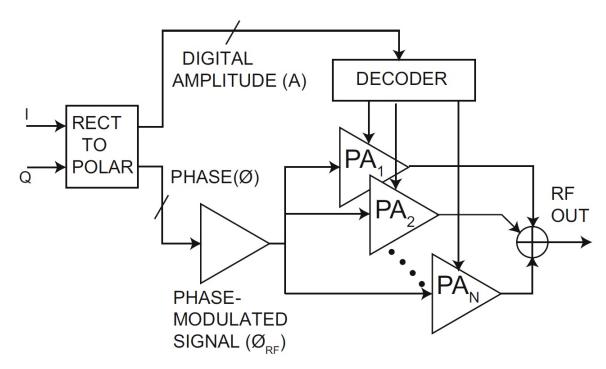

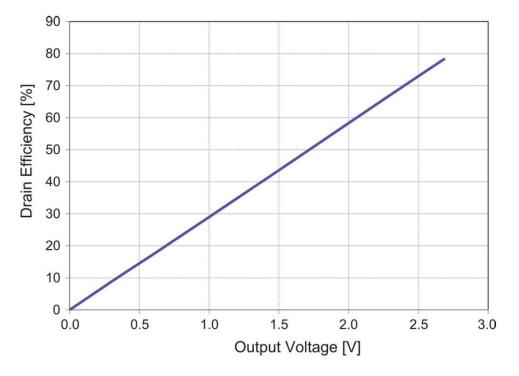

|      | A polar TX with direct digital amplitude modulation [3]                             | 32 |

| 2.23 | Linear back-off of drain efficiency with output amplitude in a polar TX with        |    |

|      | direct digital amplitude modulation $[13]$                                          | 33 |

|      |                                                                                     |    |

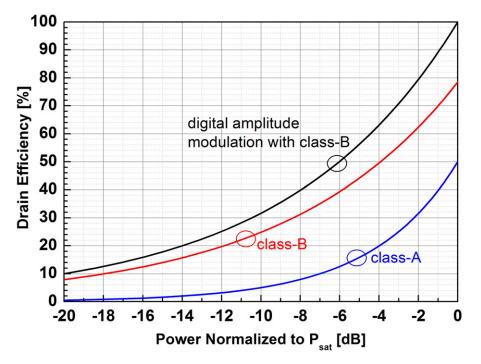

| 2.24         | Drain efficiency of an ideal class-A, class-B and digitally-modulated PA with class-B backoff.              | 34       |

|--------------|-------------------------------------------------------------------------------------------------------------|----------|

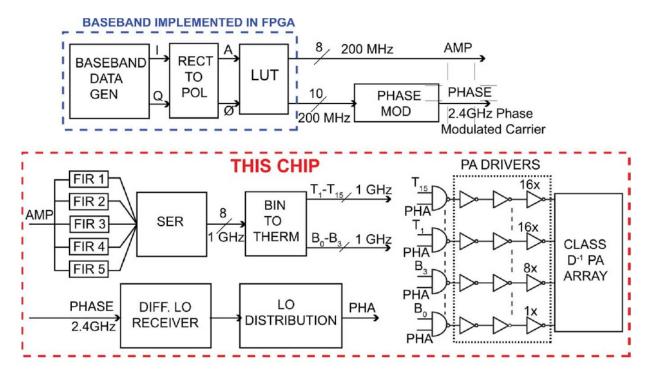

| 2.25         | A direct digitally modulated polar TX system [13]                                                           | 35       |

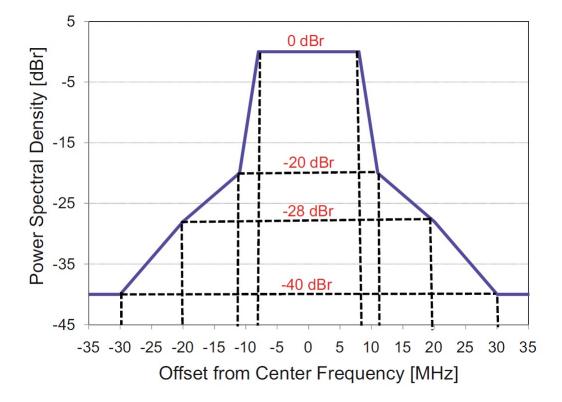

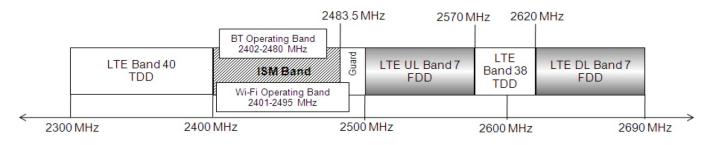

| $3.1 \\ 3.2$ | The transmit spectral mask of 802.11g [2]                                                                   | 40<br>41 |

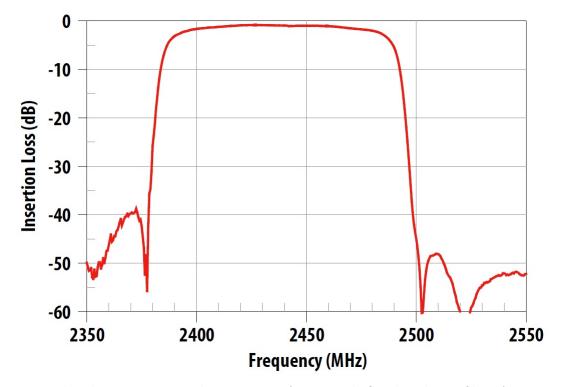

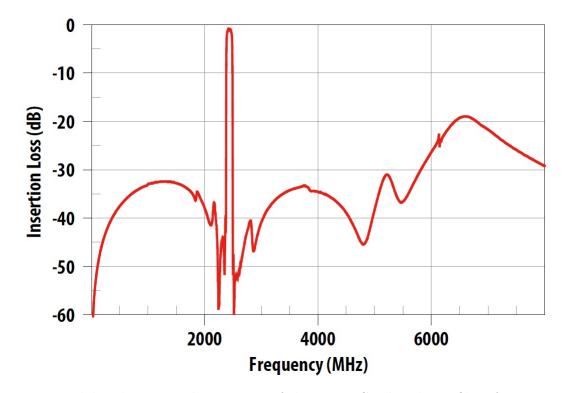

| 3.3          | The close-in magnitude response of a typical ISM bandpass filter for LTE coex-<br>istence [15]              | 42       |

| 3.4          | Wideband magnitude response of the same ISM bandpass filter for LTE coexis-<br>tence [15]                   | 43       |

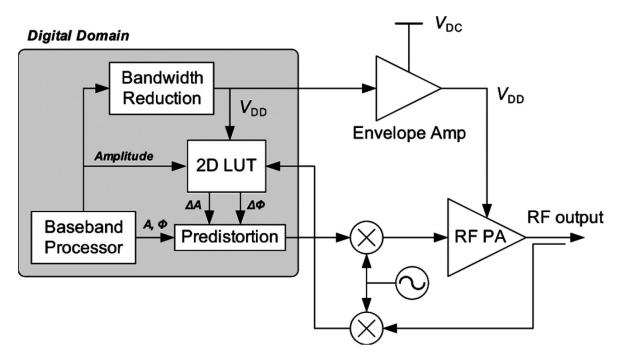

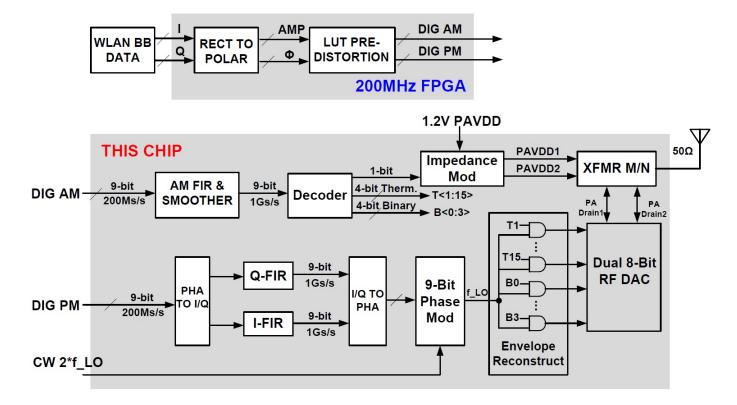

| 3.5          | Block diagram of a digitally-modulated WLAN polar TX.                                                       | 44       |

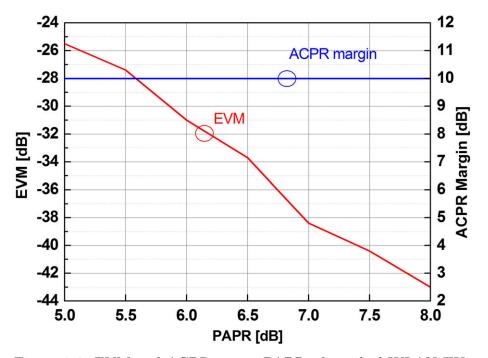

| 3.6          | EVM and ACPR versus PAPR of an ideal WLAN TX                                                                | 45       |

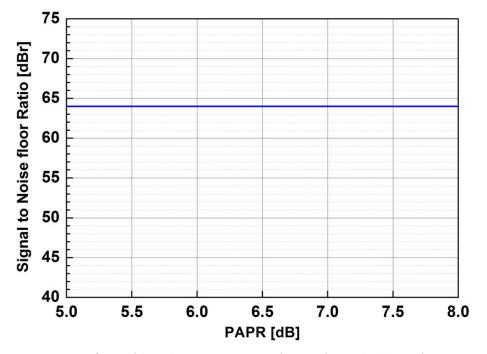

| 3.7          | Out-of-band noise versus PAPR of an ideal WLAN TX                                                           | 46       |

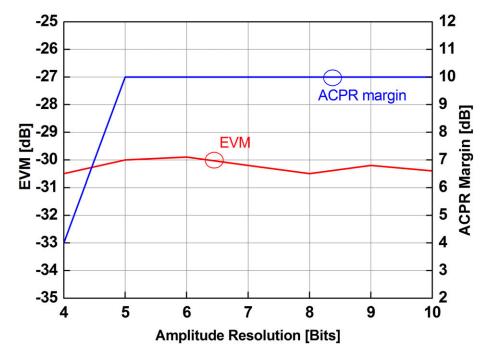

| 3.8          | EVM and ACPR versus amplitude resolution of an ideal WLAN TX                                                | 47       |

| 3.9          | The transmit spectrum of an ideal polar TX with 4-bit amplitude resolution                                  | 47       |

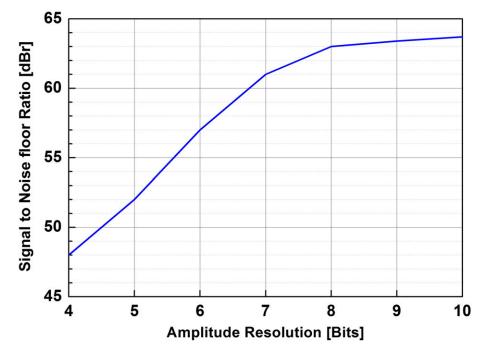

| 3.10         | The out-of-band noise versus amplitude resolution of an ideal WLAN TX                                       | 48       |

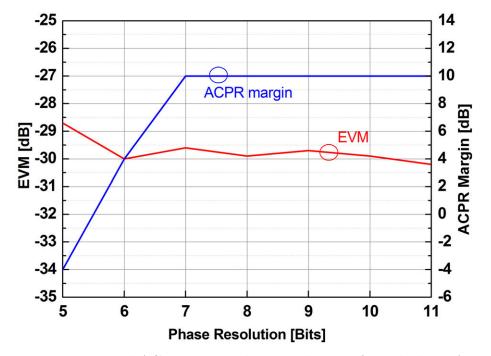

| 3.11         | EVM and ACPR versus phase resolution of an ideal WLAN TX                                                    | 49       |

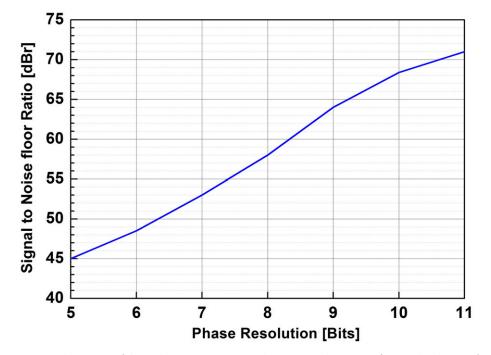

| 3.12         | The out-of-band noise versus phase resolution of an ideal WLAN TX                                           | 50       |

| 3.13         | Bandwidth extension of the amplitude signal due to Cartesian-to-polar conversion.                           | 51       |

|              | Bandwidth extension of the phase signal due to Cartesian-to-polar conversion.                               | 51       |

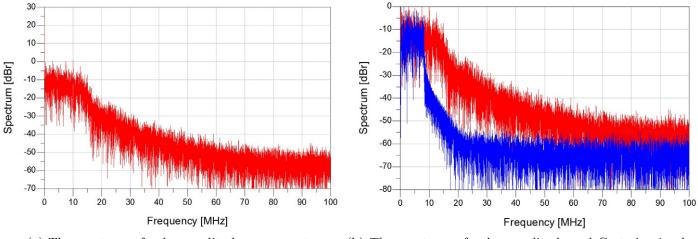

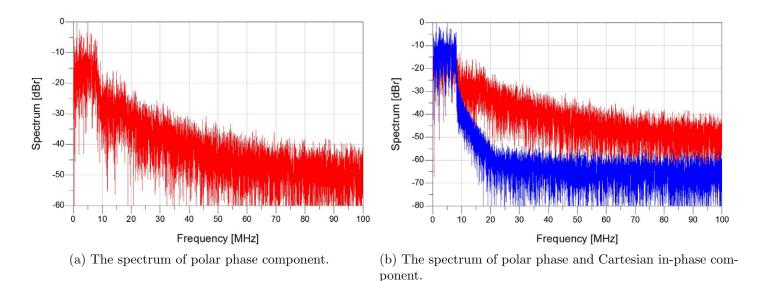

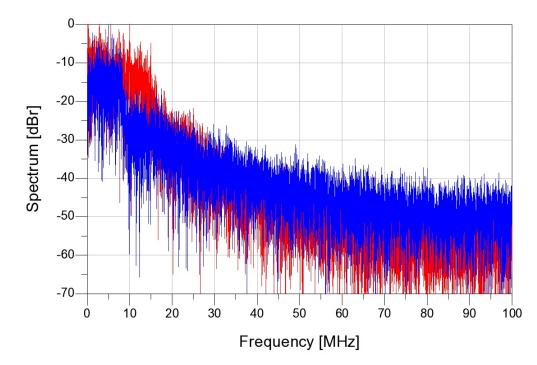

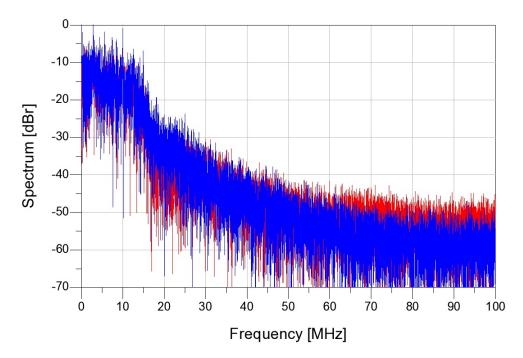

| 3.15         | The spectrum of the amplitude (red) and phase (blue) component of an ideal                                  |          |

| 3.16         | polar WLAN TX                                                                                               | 52       |

|              | tortion in a WLAN TX.                                                                                       | 53       |

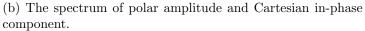

| 3.17         | The spectrum of the phase component before (blue) and after (red) predistortion<br>in a WLAN TX.            | 54       |

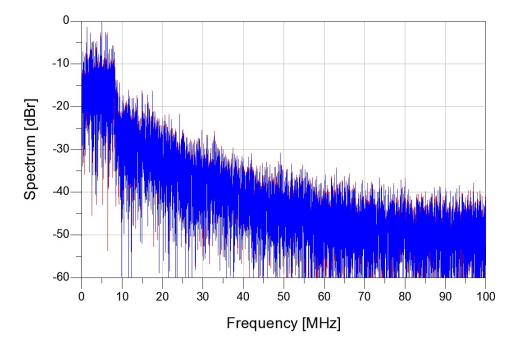

| 3.18         | The sample-and-hold (S/H) spectral images of an ideal polar TX with a baseband output sample rate of 1GS/s. | 55       |

| 3.19         |                                                                                                             | 56       |

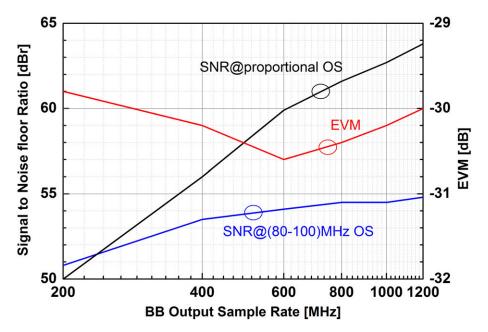

| 3.20         | The out-of-band noise and EVM versus baseband output sample rate of an ideal                                | 50       |

|              | WLAN TX.                                                                                                    | 56       |

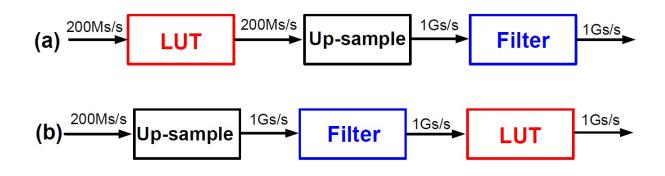

| 3.21         | The filter-last (a) and filter-first (b) baseband architecture                                              | 57       |

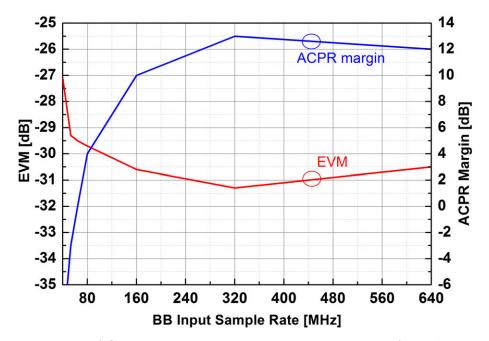

| 3.22         | EVM and ACPR versus baseband input sample rate of an ideal WLAN polar TX.                                   | 58       |

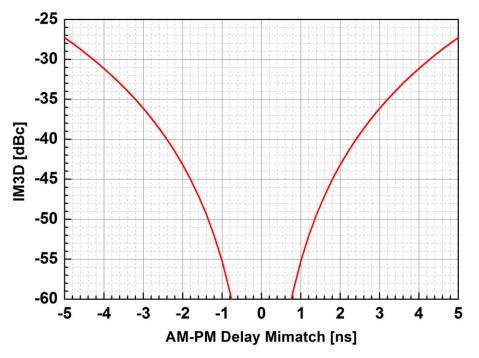

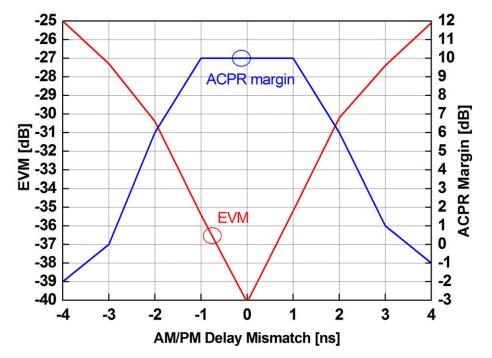

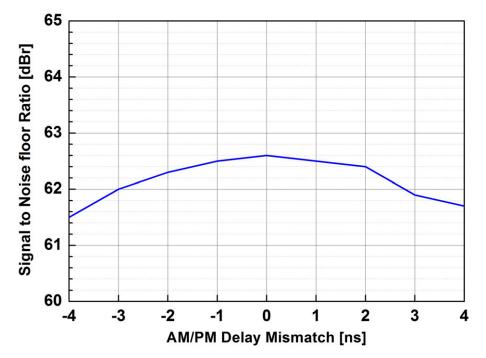

| 3.23         | The calculated third-order intermodulation distortion due to AM/PM delay mis-<br>match                      | 59       |

| 3.24         | EVM and ACPR versus AM/PM delay mismatch of an ideal WLAN TX                                                | 60       |

|              | The out-of-band noise versus AM/PM delay mismatch of an ideal WLAN TX.                                      | 60       |

|              | The measured EVM versus $AM/PM$ delay mismatch for a WLAN polar TX [13].                                    | 61       |

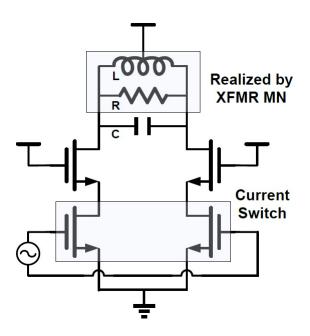

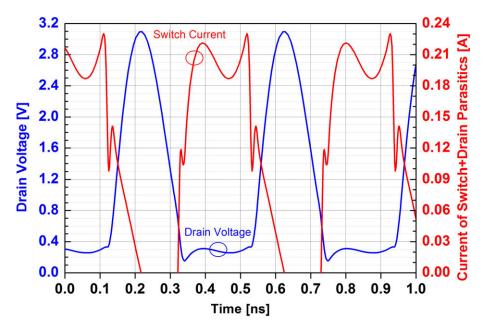

| 4.1          | The differential cascode switching PA with XFMR matching network as the core RF-DAC.                        | 63       |

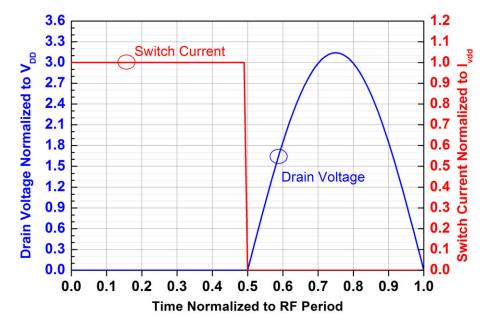

| 4.2                 | The ideal waveforms of the drain voltage and the switch current in a class- $D^{-1}$<br>and class- $F^{-1}$ PA                                                                                    | 66       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

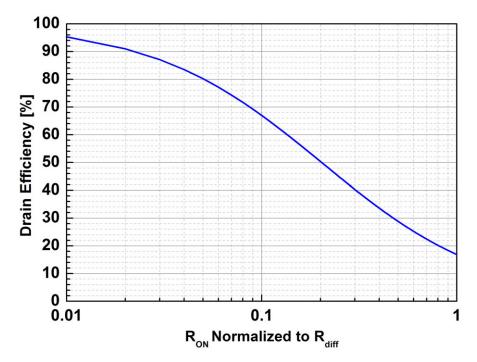

| 4.3                 | Efficiency degradation due to the switch finite on-resistance for a class- $D^{-1}$ and class- $F^{-1}$ PA.                                                                                       | 69       |

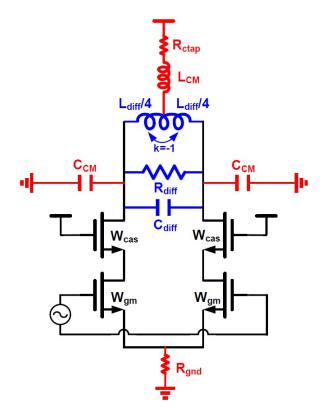

| 4.4                 | A differential cascode PA with separate differential (blue) and common-mode (red) tuning network.                                                                                                 | 70       |

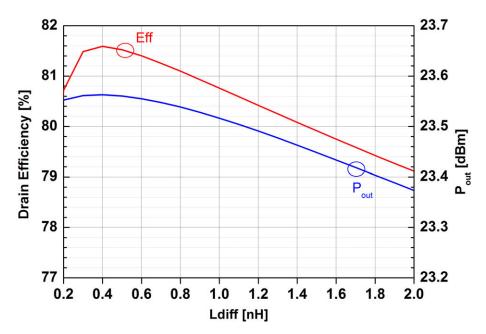

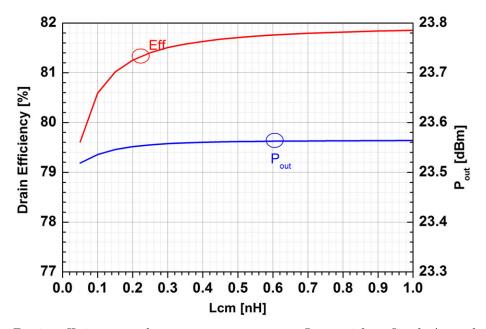

| 4.5                 | Drain efficiency and output power versus $L_{\text{diff}}$ with a fixed $A_1$ and $A_2$ defined by                                                                                                |          |

| 4.6                 | Eq (4.14) and Eq (4.15)                                                                                                                                                                           | 74       |

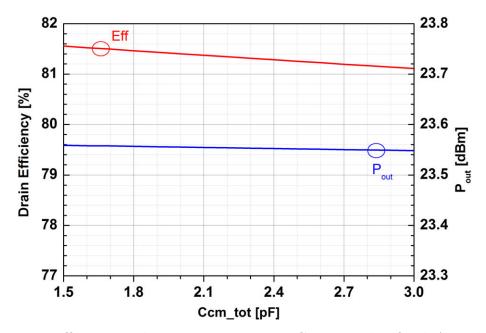

| 4.7                 | Eq (4.14) and Eq (4.15)                                                                                                                                                                           | 74       |

| 10                  | by Eq (4.14) and Eq (4.15). $\ldots$ with a fixed A defined by Eq (4.15).                                                                                                                         | 75<br>76 |

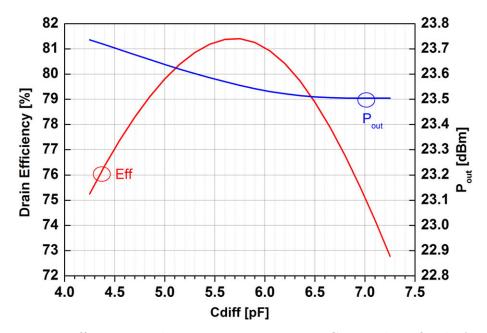

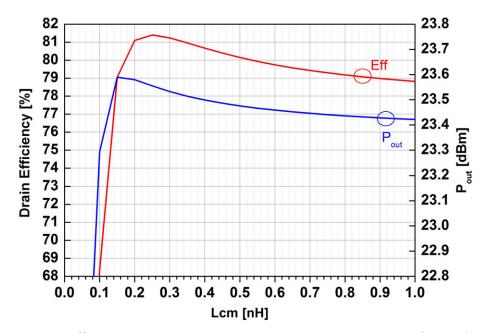

| 4.8<br>4.9          | Drain efficiency and output power versus $C_{\text{diff}}$ with a fixed $A_2$ defined by Eq (4.15).<br>Drain efficiency and output power versus $L_{CM}$ with a fixed $A_1$ defined by Eq (4.14). | 70<br>76 |

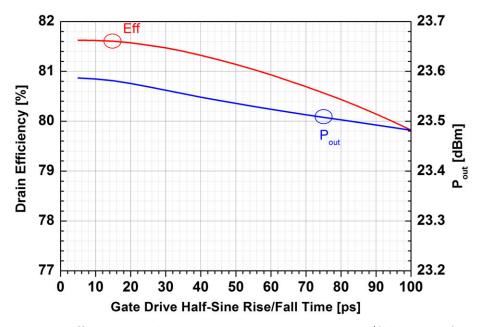

| 4.10                | Drain efficiency and output power versus the rise/fall time of the PA input drive                                                                                                                 | 10       |

|                     | with a half-sine edge.                                                                                                                                                                            | 78       |

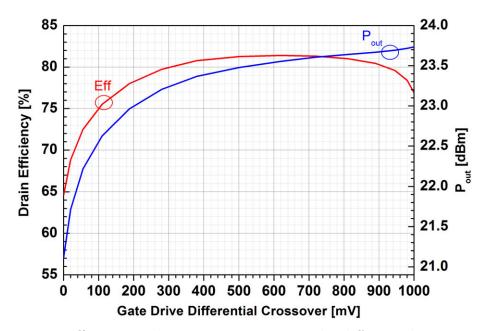

| 4.11                | Drain efficiency and output power versus the differential crossover of the PA input                                                                                                               |          |

| 4 10                | drive.                                                                                                                                                                                            | 79<br>70 |

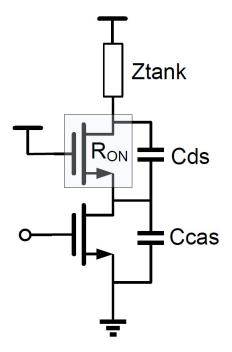

| 4.12<br>4.13        | Capacitive feedforward through $C_{ds}$ of the cascode device                                                                                                                                     | 79       |

| 4.10                | the transformer DC IR drop taken into account                                                                                                                                                     | 81       |

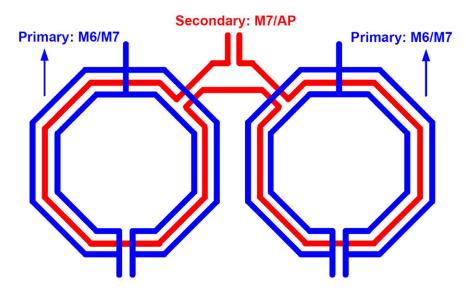

| 5.1                 | Dual-section transformer power combiner with parallel primary windings                                                                                                                            | 82       |

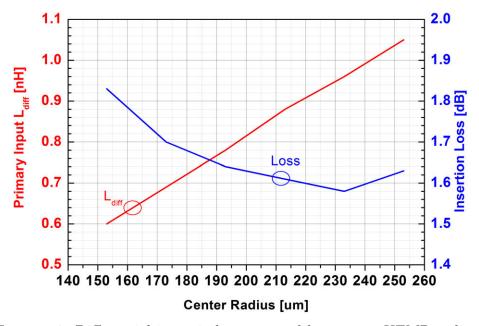

| 5.2                 | Differential input inductance and loss versus XFMR radius                                                                                                                                         | 83       |

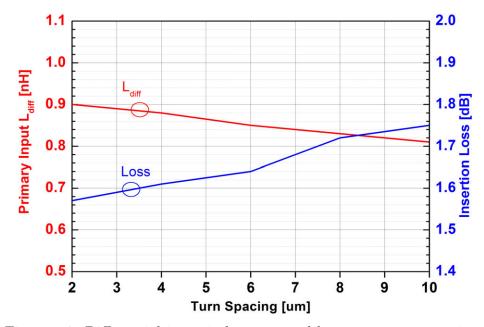

| 5.3                 | Differential input inductance and loss versus turn spacing.                                                                                                                                       | 84       |

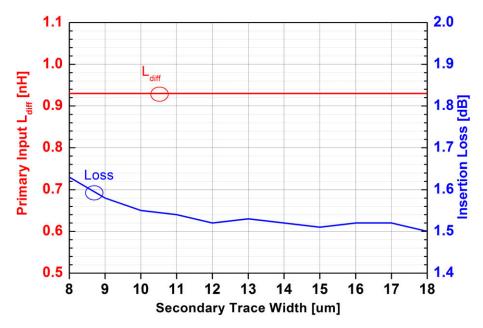

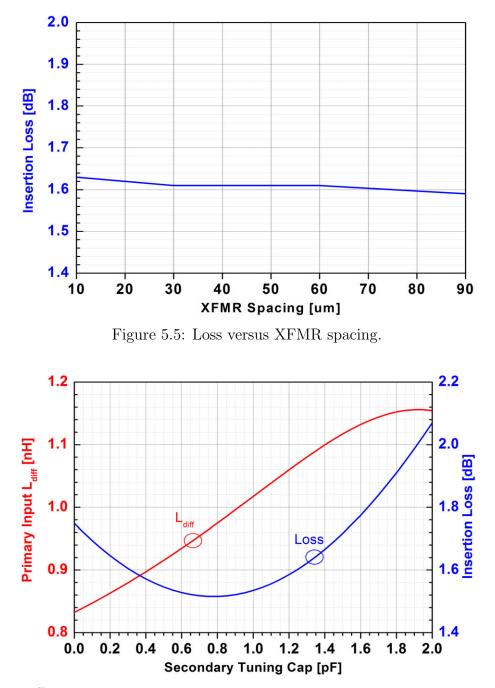

| $5.4 \\ 5.5$        | Differential input inductance and loss versus secondary trace width Loss versus XFMR spacing                                                                                                      | 85<br>86 |

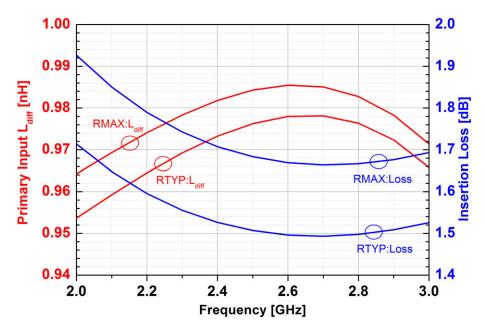

| $5.0 \\ 5.6 \\ 5.7$ |                                                                                                                                                                                                   | 80<br>86 |

| 0.1                 | resistance corners.                                                                                                                                                                               | 87       |

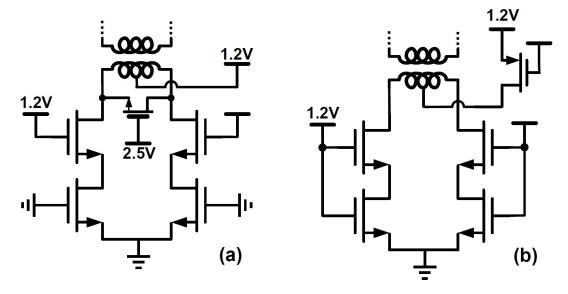

| 5.8                 | Shorting the XFMR primary with a) additional thick-oxide device and b) PA-                                                                                                                        |          |

|                     | device itself                                                                                                                                                                                     | 88       |

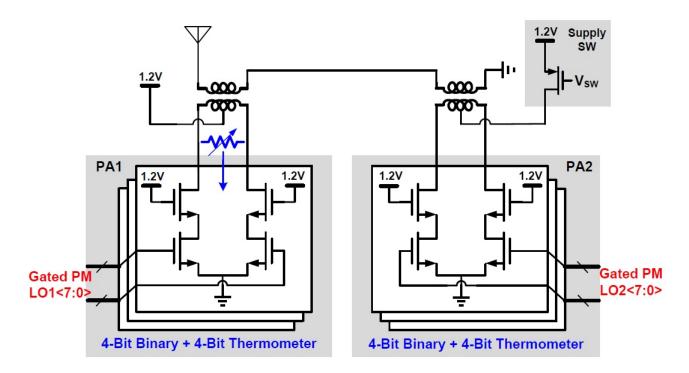

| 5.9                 | Two 8-bit RF-DACs with XFMR-based impedance modulator.                                                                                                                                            | 89       |

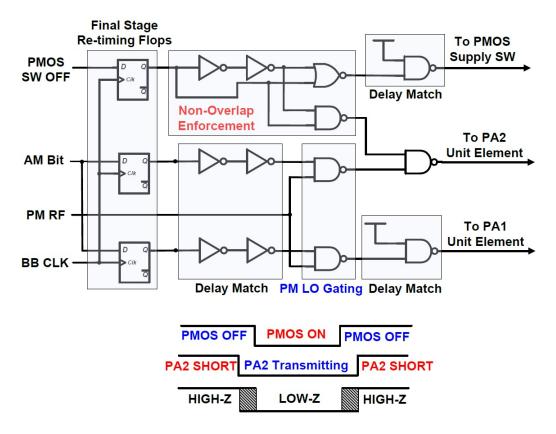

| 5.10                | Digital logic to combine AM bits and PMOS supply switch control with PM-LO.                                                                                                                       | 91       |

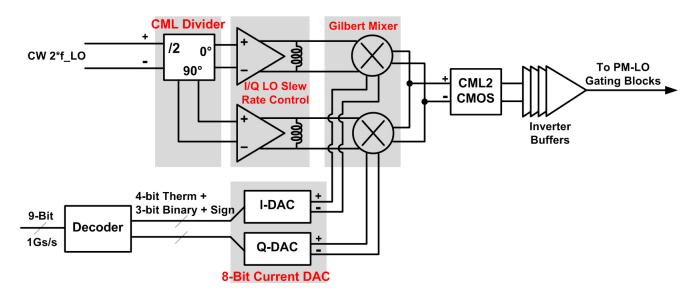

| 6.1                 | The open-loop phase modulator architecture.                                                                                                                                                       | 93       |

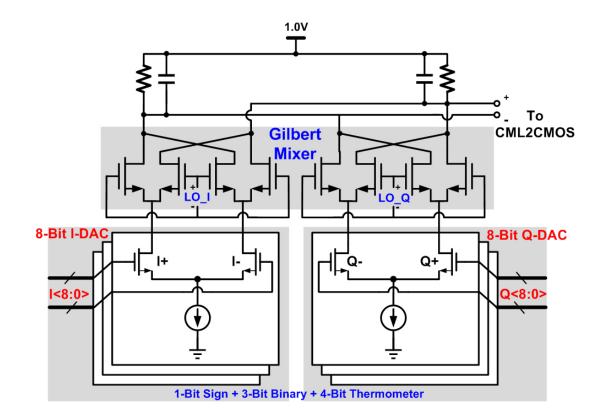

| 6.2                 | The phase interpolator circuitry                                                                                                                                                                  | 94       |

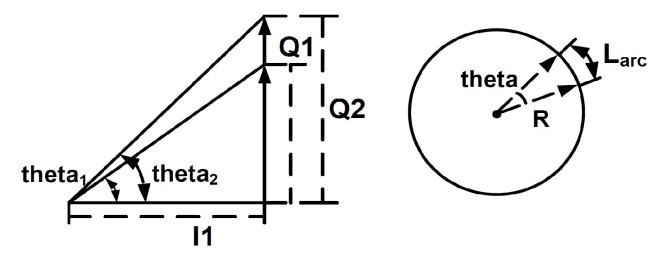

| 6.3                 | Phase approximation and phase representation in a polar coordinate                                                                                                                                | 94       |

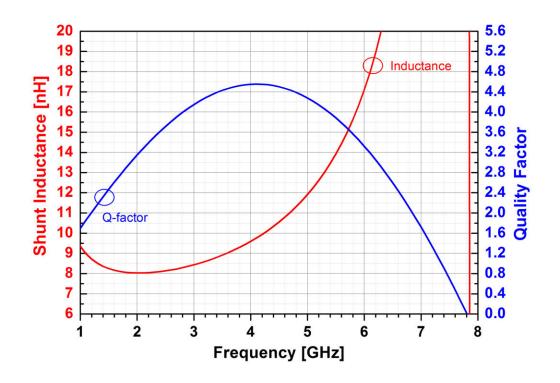

| 6.4                 | The simulated shunt inductance and qualify factor of the multi-layer differential inductor                                                                                                        | 95       |

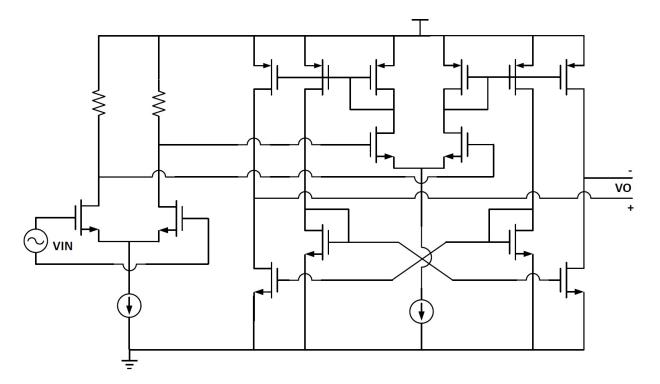

| 6.5                 | The two-stage OTA as CML-to-CMOS PM-LO receiver.                                                                                                                                                  | 95<br>96 |

| -                   | <b>o</b>                                                                                                                                                                                          |          |

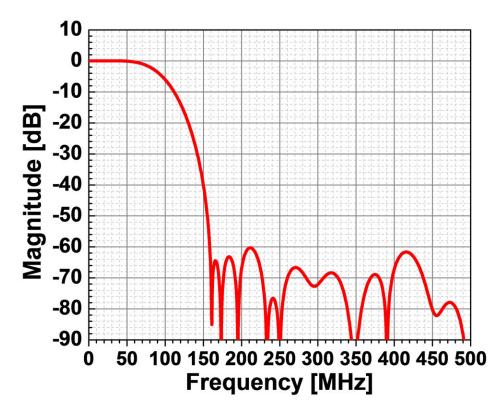

| 7.1 | The magnitude response of the interpolation filter after coefficient quantization. | 99  |

|-----|------------------------------------------------------------------------------------|-----|

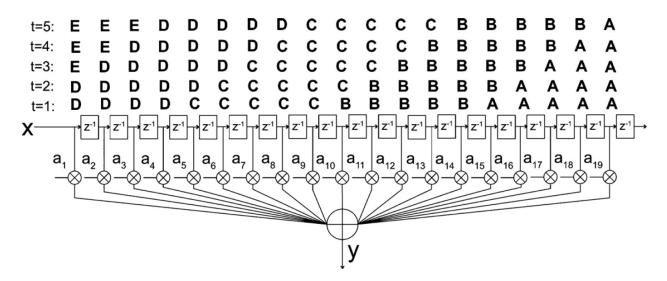

| 7.2 | The poly-phase FIR architecture.                                                   | 102 |

| 7.3 | The concept of coefficient grouping in a parallelized FIR filter with zero-order-  |     |

|     | hold up-sampling                                                                   | 102 |

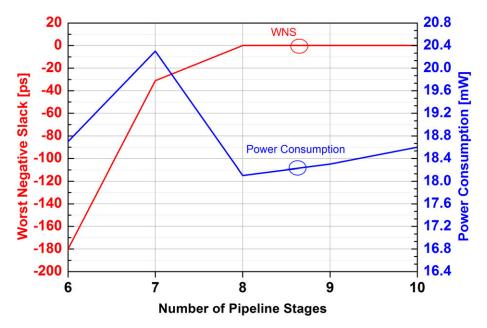

| 7.4 | Worst-Negative-Slack and power consumption of a 1.8GHz filter ([16]) in a Design   |     |

|     | Compiler synthesis.                                                                | 107 |

| 7.5 | The amplitude discontinuity with and without pre-scaling                           | 108 |

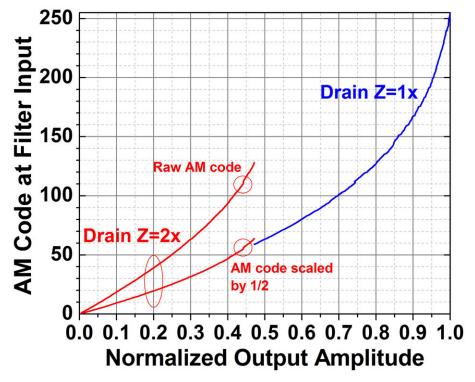

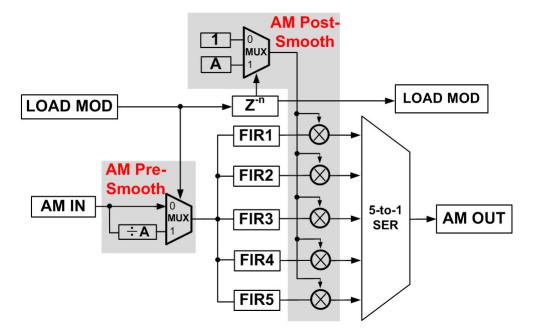

| 7.6 | The amplitude filter with waveform smoother.                                       | 109 |

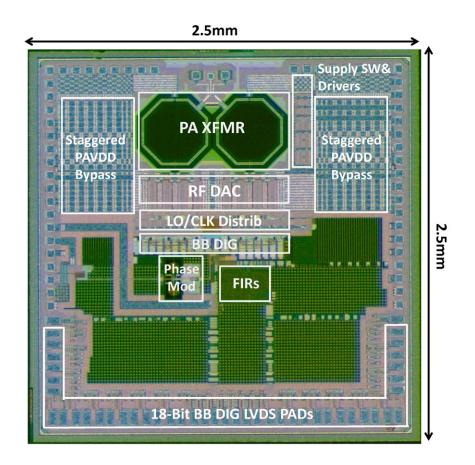

| 8.1 | Die photograph of the prototype WLAN polar TX in 65nm CMOS                         | 111 |

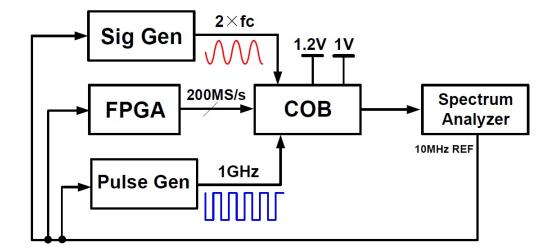

| 8.2 | Measurement setup.                                                                 | 112 |

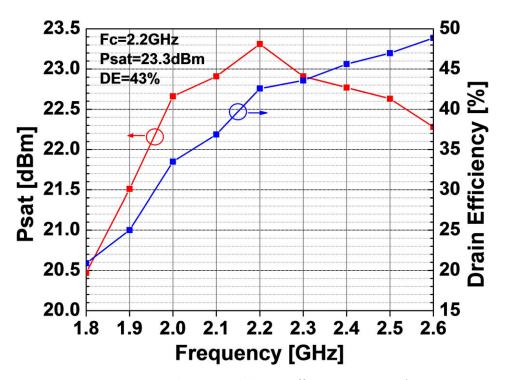

| 8.3 | Measured $P_{sat}$ and drain efficiency versus frequency                           | 112 |

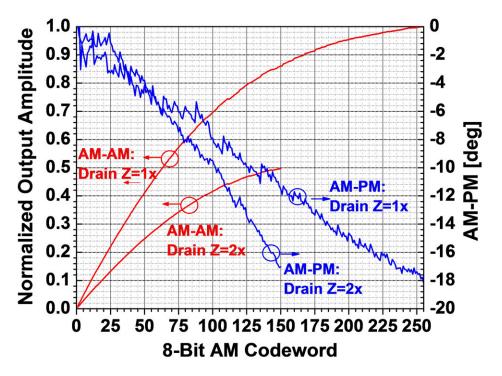

| 8.4 | Measured AM-AM and AM-PM                                                           | 113 |

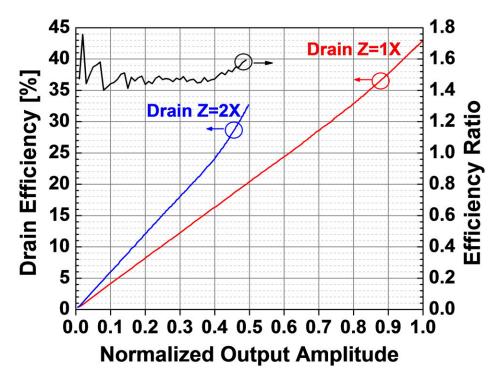

| 8.5 | Measured efficient improvements with drain impedance modulation                    | 114 |

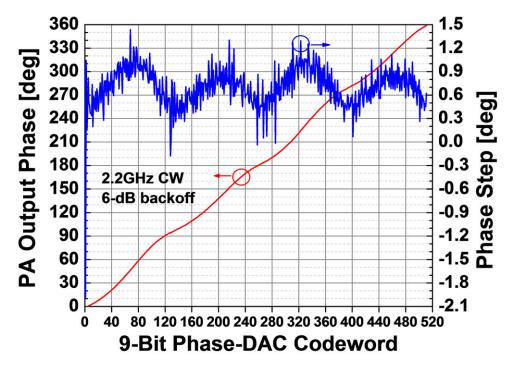

| 8.6 | Measured phase path response (PM-PM)                                               | 115 |

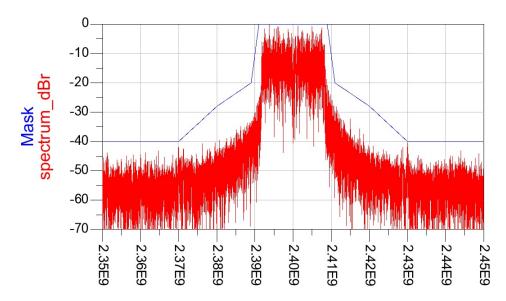

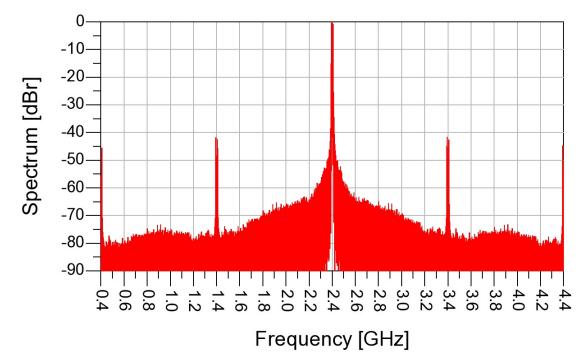

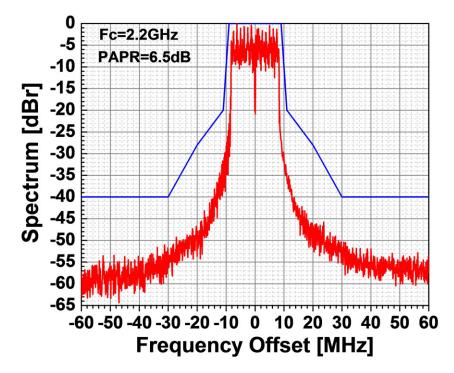

| 8.7 | WLAN 802.11g 54Mbps: measured close-in spectrum                                    | 116 |

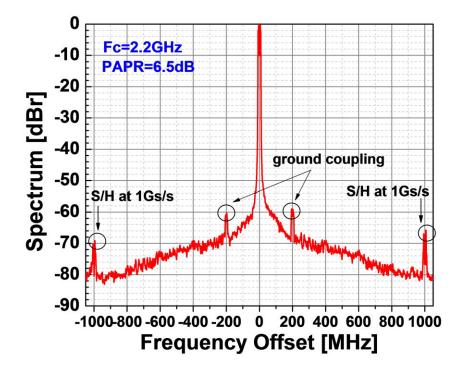

| 8.8 | WLAN 802.11g 54Mbps: measured far-out spectrum                                     | 117 |

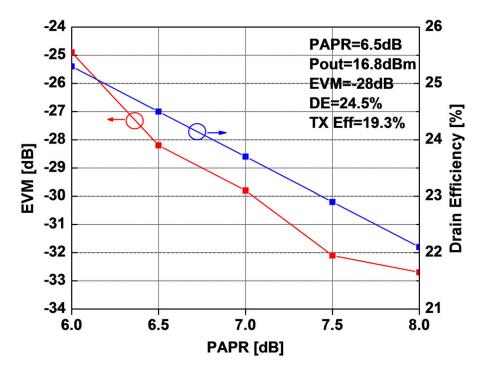

| 8.9 | WLAN 802.11g 54Mbps: measured EVM and efficiency versus PAPR                       | 117 |

## List of Tables

| 1.1                                      | Power breakdown of an 802.11n TX at $P_{out}$ =-8.3dBm [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6$ | Efficiency back-off characteristics with dynamic current biasing Performance comparison for state-of-the-art supply modulators Efficiency backoff characteristic with envelope tracking TXs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15<br>21<br>24<br>29<br>30<br>34 |

| $3.1 \\ 3.2$                             | 802.11g Modulation-dependent parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39<br>40                         |

| $4.1 \\ 4.2 \\ 4.3$                      | Impedance termination requirements for a class- $D^{-1}$ and class- $F^{-1}$ PA Maximum achievable efficiency with half-wave rectified sinusoidal voltage Simulated performances of the harmonic-tuned switching PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67<br>70<br>80                   |

| $5.1 \\ 5.2 \\ 5.3$                      | Dynamic impedance configurations.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 88<br>89<br>90                   |

| 6.1                                      | Phase modulator power breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97                               |

| 8.1<br>8.2                               | TX power breakdown for WLAN 802.11g 54Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 115<br>118                       |

#### Acknowledgments

Although it took me six years to get help and support from various sources to complete my PhD, it only takes me more than one page to acknowledge those who have made this happen. Therefore this acknowledgment is never going to be complete; nor is it enough to fully express my gratitude.

First of all, my faculty advisor, Prof. Ali M. Niknejad. He is knowledgeable and has a logical and rigorous way of technical thinking. I appreciate the opportunity of being part of his research group and working with him on interesting topics. A true gentleman, Ali is always calm, patient and considerate. In fact, he has almost all the characteristics I would picture out of a "good person" in a well-cultivated society. I am as impressed by his nice personality as by his academic vision. Being treated nicely, I have gradually learned to "be nicer" to others.

I want to thank Prof. Elad Alon, who has also taken the time and the pains to improve my work which was sometimes not solid, my oral presentation which was always awkward, and my paper draft which was often poorly organized. Advising on the digital transmitter project, Elad has made millions of challenges to my technical statements, which urged me to re-examine my understandings and make my work more compelling. For some of my drafts for paper submissions, Elad almost edited every single sentence (if he was not completely rephrasing it); the fact that he (as well as Ali) is not giving up the effort of helping me out is one of the reasons I myself did not give up during difficult times.

Prof. Paul Wright has kindly agreed to serve on my dissertation committee and I really appreciate his valuable time and feedback. Upon his first read, he shared with me some harsh criticisms, which, in addition to making me feel really bad, helped to improve the readability and organization of this dissertation.

I have been very fortunate to work with a group of brilliant and fun students at Berkeley Wireless Research Center (BWRC). We have gone through tough tapeouts together and also enjoyed lots of fun all through. Especially I want to thank Debo Chowdhury for setting an excellent example in research and technical communication which I can only approach over my entire career. A complete enumeration would not be practical here; but once again I want to thank the BWRC folks and wish you all the best. I truly hope our paths will cross sometime in the future.

Many thanks to my friends from Peking University as well my "Cedar 2008" housemates. I cherish the enjoyable times with you.

This dissertation has been completed in a rush within two weeks (dear committee members, please do not disapprove it simply because this short length of time!). Also on my plate is another hard cutoff at the company, perhaps even harder than 60dB per decade. My supervisor, Julian Tham, has generously allowed me to interleave work with dissertation writing. Without Julian's support, I can easily screw up either one. I also want to acknowledge the supervision from Ali Afsahi in the same company; working with him during my internship has exposed me to the various real-world transmitter issues that are sometimes not easily encountered in academia. I dedicate this dissertation to the whole of my family, without whose unconditional love and enduring support this work would have never been possible. My passed maternal grandfather (2000), my grandmother (2013) and my mother-in-law (2008), I miss you from the bottom of my heart and I am sure you will be proud of my achievement. Last, but never the least, my wife; please continue to "be my co-driver", whenever and wherever.

## Part I

**Introduction and Background Studies**

# Chapter 1 Introduction

The last decade has seen a spectacular surge in the wireless industry, and wireless connectivity has now become an indispensable ingredient of everyday life. The trend has been partially fueled by the recent explosive growth in the popularity of mobile devices featuring personal computing as well as versatile, high data rate communication capabilities such as Long Term Evolution (LTE) and Wireless Local Area Network (WLAN). As seen in Fig. 1.1, the mobile data traffic is forecast to expand by 35x from 2009 to 2014. Meanwhile, a vast plethora of other applications such as gaming, multimedia streaming and home networking have also motivated the development of low-cost and high data-rate radios.

Figure 1.1: Industry forecast of mobile data traffic from 2009 to 2014 ([1]).

Driven by the need for high data-rates in spite of a highly crowded spectrum (Fig. 1.2), the modulation schemes for various wireless standards have evolved towards spectrally-efficient (e.g. Orthogonal Frequency Division Multiplexing (OFDM)) and higher-order (e.g. 256-

QAM as opposed to BPSK) ones. For example, IEEE 802.11ac, an amendment to the 802.11-2007 standard (including 802.11a/b/g/n), offers a peak throughput of 200Mbps within 40MHz channel bandwidth; if BPSK modulation is used on the per-sub-carrier basis as opposed to 256-QAM, it can only support 15Mbps over the same bandwidth (Fig. 1.3). The improved spectral efficiency in the frequency domain comes at the expense of an increased Peak-to-Average-Power-Ratio (PAPR) in the time domain. For 802.11ac OFDM signals of 40MHz bandwidth, for example, the theoretical PAPR (as calculated by Eq.(1.1), where  $N_{sub,tr}$  is the number of carriers transmitting data) is 20.6dB.

$$PAPR = 10 \times \log_{10}(N_{sub,tr}) \qquad [dB] \tag{1.1}$$

Figure 1.2: United States frequency allocations.

In contrast to constant envelope modulation, such as Quadrature Phase Shift Keying (QPSK), high-PAPR modulations typically require a highly linear power amplifier (PA) (Fig. 1.4). This is typically achieved by employing a class-A PA with a large back-off from its saturated output power ( $P_{sat}$ ). Due to the efficiency loss associated with the large back-off, the average power efficiency is severely compromised. With the fast-growing data rates, this issue has become increasingly problematic for battery-operated mobile devices, because the PA is often times the most power hungry within a wireless transmitter (TX). To extend

|       | Theoretical throughput for single Spatial Stream (in Mb/s) |        |                 |           |                 |           |                 |           |                  |           |

|-------|------------------------------------------------------------|--------|-----------------|-----------|-----------------|-----------|-----------------|-----------|------------------|-----------|

| MCS   | Modulation                                                 | Coding | 20 MHz channels |           | 40 MHz channels |           | 80 MHz channels |           | 160 MHz channels |           |

| index | type                                                       | rate   | 800 ns GI       | 400 ns Gl | 800 ns GI       | 400 ns Gl | 800 ns GI       | 400 ns GI | 800 ns GI        | 400 ns GI |

| 0     | BPSK                                                       | 1/2    | 6.5             | 7.2       | 13.5            | 15        | 29.3            | 32.5      | 58.5             | 65        |

| 1     | QPSK                                                       | 1/2    | 13              | 14.4      | 27              | 30        | 58.5            | 65        | 117              | 130       |

| 2     | QPSK                                                       | 3/4    | 19.5            | 21.7      | 40.5            | 45        | 87.8            | 97.5      | 175.5            | 195       |

| 3     | 16-QAM                                                     | 1/2    | 26              | 28.9      | 54              | 60        | 117             | 130       | 234              | 260       |

| 4     | 16-QAM                                                     | 3/4    | 39              | 43.3      | 81              | 90        | 175.5           | 195       | 351              | 390       |

| 5     | 64-QAM                                                     | 2/3    | 52              | 57.8      | 108             | 120       | 234             | 260       | 468              | 520       |

| 6     | 64-QAM                                                     | 3/4    | 58.5            | 65        | 121.5           | 135       | 263.3           | 292.5     | 526.5            | 585       |

| 7     | 64-QAM                                                     | 5/6    | 65              | 72.2      | 135             | 150       | 292.5           | 325       | 585              | 650       |

| 8     | 256-QAM                                                    | 3/4    | 78              | 86.7      | 162             | 180       | 351             | 390       | 702              | 780       |

| 9     | 256-QAM                                                    | 5/6    | N/A             | N/A       | 180             | 200       | 390             | 433.3     | 780              | 866.7     |

Figure 1.3: Theoretical throughputs of a single spatial stream for IEEE 802.11ac.

battery life, the TX must be efficient not only at peak power but also at backoff. TX efficiency enhancement at back-off powers has therefore become one of the key research focuses in recent years.

Figure 1.4: A generic Cartesian transmitter [2].

On the other hand, portable devices generally require small form-factor radios to reduce the overall size and packaging costs for high volume productions. Therefore, a high level of integration of merging as many components into a single die in an inexpensive technology is one of the long term visions for wireless transceivers. Over the last decade, most of the transceiver building blocks have been successfully integrated into CMOS technology as possible and co-exist with Digital Signal Processing (DSP) modules on the same die. Although several advances have been made recently, the full integration of CMOS PAs is still among the most difficult challenges towards achieving a true System-On-Chip (SOC) solution. This is further exacerbated by supply voltage reduction due to device geometry and gate dielectric scaling, which poses significant challenges in terms of power handling capabilities to integrated CMOS PAs. Meanwhile, increased losses of on-chip passives due to the semi-conducting silicon substrate as well as the closer proximity of the metal stack to such a lossy substrate also tends to degrade the overall efficiency of a fully integrated CMOS PA [18].

The primary goal of this dissertation is hence to investigate fully-integrated, powerefficient RF transmitter designs with a special emphasis on the direct digitally modulated TX architecture. The key design trade-off is the TX linearity and efficiency for high output power levels. Although the full TX power consumption is dominated by the PA output stage, we still provide a complete treatment at the system level to investigate various efficiency enhancement techniques. That is because the baseband (BB) stage (comprising of DSP modules, Digital-to-Analog Converter (DAC) and filters) and the up-conversion and driver stages all contribute a significant portion to the total power consumption of a TX, especially at back-off power levels where the PA power consumption is usually scaled down accordingly while the overhead from the BB and the up-conversion stages are usually fixed (Table 1.1). Linear and efficient preceding stages are therefore equally important as the PA output stage.

| TX block           | Power dissipation [mW] | Percentage [%] |  |  |

|--------------------|------------------------|----------------|--|--|

| LO Dividers+Buffer | 124                    | 33             |  |  |

| Up-conversion      | 39.3                   | 10             |  |  |

| RF filter          | 40.7                   | 11             |  |  |

| VGA                | 110                    | 29             |  |  |

| Output driver      | 61.4                   | 16             |  |  |

Table 1.1: Power breakdown of an 802.11n TX at  $P_{out}$ =-8.3dBm [17].

Furthermore, we will also investigate the out-of-band (OOB) spectral purity and its tradeoff with various efficiency enhancement techniques. Contemporary mobile solutions are most likely to integrate multiple radios together to offer a complete and versatile user experience. It is not uncommon today to have the simultaneous availability of cellular, WLAN, Bluetooth, GPS and FM functionality all from a single mobile terminal. Co-existence among multiple radios is therefore an important consideration. The key requirement for the TX in this regard would be the OOB transmit noise be low enough not to de-sensitize the receiver (RX) of another radio in that band. Ideally, the far-out noise should be below the thermal noise floor defined by Eq.(1.2)

$$P_n = 10 \times \log_{10}(k_B T) \qquad [\text{dBm/Hz}] \tag{1.2}$$

where  $k_B$  is the Boltzmann constant and T is temperature. At room temperature (T = 300K), the thermal noise floor is about -174dBm/Hz. With a modest isolation of 40dB from antenna-to-antenna and/or diplexers, the OOB transmit noise floor should be below -134dBm/Hz. Compared with state-of-the-art analog Cartesian WLAN TXs, this specification is still challenging to achieve across a wide bandwidth at >15dBm OFDM power levels. On the other hand, the direct digitally modulated TX inherently has spectral images at offsets equal to multiples of the BB sample rate due to its zero-order-hold operation at the digital/RF-DAC interface. Furthermore, the OOB noise floor is also contributed by digital quantization, besides the Adjacent Channel Power Regrowth (ACPR) due to TX non-linearities purely in the analog domain. Due to these two additional noise contributing factors that are absent in an analog Cartesian TX, the spectral purity of a digitally modulated TX tends to be worse at similar output power levels, jeopardizing its co-existence with other radios. It is for this reason that the OOB spectrum is also an important consideration in our research on digitally-modulated TXs.

### 1.1 Thesis Organization

To rephrase, this thesis is focused on the design and analysis of a fully-integrated, powerefficient and co-existable digitally-modulated CMOS power transmitter system. Part I of this thesis serves as the background studies for our research work: we review the various techniques to enhance PA efficiencies at back-off power levels in Chapter 2; digitally modulated TX architecture is introduced with its advantages as well as fundamental limitations. We then proceed with the design and analysis of fully-integrated digitally modulated polar TX system for efficiency enhancement in Part II. We first outline TX system-level considerations in Chapter 3, cover the design of the core switching PA in Chapter 4, and then the transformer-based impedance modulator in Chapter 5. The design considerations of the power-efficient, open-loop phase modulator are explained in Chapter 6, while Chapter 7 is dedicated to the design and synthesis of baseband digital filters to knock down the close-in spectral images. Measurement results are presented in Chapter 8, and concluding remarks in Chapter 9.

### Chapter 2

## Overview of Efficiency Enhancement Techniques at Back-off Output Powers

### 2.1 Efficiency Back-off of Class-A, Class-B and Class-AB PAs

The PA drain efficiency is defined as the output power delivered the load normalized by the total power drawn from the supply

$$\eta_{de} = \frac{P_{out}}{P_{supply}} = \frac{I_{out} \times V_{out}}{I_{vdd} \times V_{dd}} = \frac{I_{out}}{I_{vdd}} \times \frac{V_{out}}{V_{dd}}$$

(2.1)

where  $P_{out}$  is the output power delivered to the load,  $P_{supply}$  is the total power drawn from the supply,  $I_{out}$  is the room-mean-square (RMS) output current,  $V_{out}$  is the RMS output voltage,  $V_{dd}$  is the supply voltage, and  $I_{vdd}$  is the supply current. As shown above, the drain efficiency can be calculated as the normalized output current,  $\frac{I_{out}}{I_{vdd}}$ , times the normalized output voltage,  $\frac{V_{out}}{V_{dd}}$ . Drain efficiencies of an ideal class-A, class-B and switching PA are analyzed below at both peak and back-off power levels.

In an ideal class-A PA (Fig. 2.1) where the drain voltage is allowed to swing up to  $2 \times V_{dd}$ , the RMS output voltage at peak power is

$$V_{out} = \frac{V_{dd}}{\sqrt{2}} \tag{2.2}$$

because the amplitude of  $V_{out}$  is  $V_{dd}$ . In a proper design, the drain current has an amplitude equal to its quiescent level such that the drain current transiently reaches zero at peak power. In other words,

$$I_{out} = \frac{I_{vdd}}{\sqrt{2}} \tag{2.3}$$

Figure 2.1: A generic class-A power amplifier with RF-choke (RFC) [3].

Substituting Eq.(2.2) and Eq.(2.3) into Eq.(2.1), the peak drain efficiency of a class-A PA, which occurs at peak power, is

$$\eta_{class-A,pk} = \frac{I_{out} \times V_{out}}{I_{vdd} \times V_{dd}} = 50\%$$

(2.4)

To derive the efficiency back-off characteristics for a class-A PA, assume the load for power delivery is a real impedance,  $Z_L$

$$Z_L = \frac{V_{out}}{I_{out}} \tag{2.5}$$

The drain efficiency for a class-A PA is therefore

$$\eta_{class-A} = \frac{I_{out} \times V_{out}}{I_{vdd} \times V_{dd}} = \frac{I_{out}^2 \times Z_L}{P_{const}} = \frac{V_{out}^2}{Z_L \times P_{const}}$$

(2.6)

where  $P_{const}$  is the constant power drawn by the class-A PA from the supply

$$P_{const} = V_{dd} \times I_{vdd} \tag{2.7}$$

The drain efficiency of a class-A PA therefore reduces quadratically with output amplitude. At 6-dB power backoff, the drain efficiency is only 25% of its peak value.

In class-B operation, the transistor drain current is a half-wave rectified sine-wave, whose time-average is the current drawn from the supply

$$I_{vdd} = \frac{\sqrt{2} \times I_{out}}{\pi} \times 2 \tag{2.8}$$

where the factor of 2 accounts for the dual power transistors in a push-pull fashion. The class-B operation inherently scales its quiescent current in proportion to signal amplitude, which is much more efficient than class-A where the quiescent current is a constant regardless of signal level. The drain efficiency of a class-B PA is therefore

$$\eta_{class-B} = \frac{I_{out} \times V_{out}}{I_{vdd} \times V_{dd}} = \frac{V_{out} \times I_{out}}{V_{dd} \times \frac{2\sqrt{2}}{\pi} I_{out}} = \frac{\pi}{2\sqrt{2}} \frac{V_{out}}{V_{dd}}$$

(2.9)

Therefore, the class-B efficiency backs-off linearly with output amplitude, due to the linear scaling of quiescent current with signal amplitude. Similar to a class-A PA, the drain voltage can swing up to  $2 \times V_{dd}$  for a class-B PA at peak power, yielding

$$V_{out} = \frac{V_{dd}}{\sqrt{2}} \tag{2.10}$$

and giving a peak efficiency of

$$\eta_{class-B,pk} = \frac{I_{out} \times V_{out}}{I_{vdd} \times V_{dd}} = \frac{\pi}{4} = 78.5\%$$

$$(2.11)$$

The class-B PA can achieve better efficiency at peak power (78.5% vs. 50%) and back-off power levels (linear vs. quadratic), as shown in Fig. 2.2. Despite of the efficiency advantage, a class-B PA suffers from degraded linearity as opposed to class-A, because the transistor is only conducting for half the RF period. To get a descent efficiency back-off characteristic without much linearity hit, a transconductance-based PA is usually biased in the hybrid of class-A and class-B mode (hence the name class-AB). The efficiency and linearity of a class-AB PA are between those of an ideal class-A and class-B.

In this chapter, various techniques to improve the PA efficiency at back-off power levels are briefly reviewed [19]. Note that some of these techniques only achieve the class-B back-off characteristic. However, those are still significant improvements over a conventional class-B/class-AB PA if they have linearity as good as class-A. In other words, the goal of the various techniques is to improve the trade-off between efficiency and linearity inherent in the class-A/B/AB PA; this can be accomplished by either achieving an ideal class-B back-off with better linearity, or achieving a better-than-class-B back-off with similar linearity.

### 2.2 Dynamic Current Biasing

For a transconductance  $(g_m)$ -based PA, a significant portion of non-linearity comes from the current domain, where the gate/base voltage non-linearly trans-conducts the drain current. To reduce this  $g_m$  non-linearity, the RF current swing normalized by quiescent current should be low enough. Partially due to a constant quiescent current regardless of signal

Figure 2.2: The drain efficiency of an ideal class-A and class-B power amplifier.

level and the resultant low normalized signal current, a  $g_m$ -based PA that is biased deep into class-A region exhibits superior current linearity. At very low signal levels, however, the normalized current swing is unnecessarily low, wasting power and degrading efficiency. The dynamic current biasing technique (Fig. 2.3) therefore attempts to scale the bias current according to the average transmit power across a short period of time (on the order of several RF cycles and above) and hence maintain a roughly constant normalized current swing. Much the same way as class-B (Eq.(2.8)), the quiescent current as regulated by this technique is able to linearly track signal amplitude and therefore achieve class-B back-off in the best case. At the same time, the normalized current swing is still maintained at a low enough level that linearity is not significantly degraded with respect to class-A.

The potential linearity improvement from this technique can be derived in the following way. Since the  $g_m$ -based PA provides higher small-signal gain with higher bias current, this technique essentially increases the small-signal gain with increased signal level. This just compensates the compressive AM-AM characteristic where the apparent gain (i.e. the largesignal gain) is reduced with increased input power. Essentially a "pre-distortion" technique, it therefore helps to maintain a constant large signal gain across a wider range of input power levels. It should be noted that although this technique compensates the compressive AM-AM non-linearity of the PA and hence improves the linearity, it does not improve the

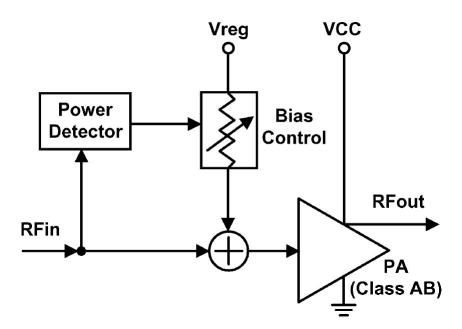

Figure 2.3: An adaptive current biasing scheme for the class-AB PA [4].

AM-PM distortion which is another important non-linearity source.

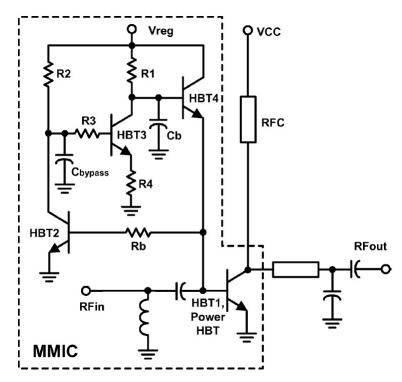

The implementation of this technique requires input power (envelope) sensing, filtering (to determine the time-average of a varying envelope) as well as a bias control to convey the detected average envelope to the biasing voltage. It can be implemented in a closed-loop fashion ([4]) as shown in Fig. 2.4. In the circuits,  $C_{bypass}$  is used as the envelope filter. By adjusting the base resistor  $R_b$  and the emitter area of HBT2, the slope of the biasing current with respect to input signal level can be adjusted and high efficiency at low output powers and high linearity at high output powers can be achieved simultaneously. With Wideband Code-Division Multiple Access (WCDMA) modulated signal and for a fixed -33dBc of Adjacent Channel Leakage Ratio (ACLR) target, this technique increases the PA output power from 27.5dBm to 28.3dBm, although with a Power Added Efficiency (PAE) degradation from 54%to 52.4% ([4]). With the PA Probability Distribution Function (PDF) based on an IS-95 CDMA urban environment, the dynamic current biasing technique achieves an average power efficiency of 11.8% at 5dB output power.

Dynamic current bias control can also be implemented with a separate feedforward path ([5]), as shown in Fig. 2.5. Fig. 2.6 shows the measured gain flatness improvement with this technique, where the gain is intentionally lowered at low power levels to extend the output 1-dB compression point  $(P_{1dB})$  by 1.6dB. The linearity improvement is also readily verified by the measured EVM (Fig. 2.7), which is improved from -25.3dB to -28.5dB at 17dBm WLAN OFDM (64-QAM, 54Mbps) power; the low quiescent current in low power regions also improves the PAE in the same condition from 3.3% to 8.9%.

Figure 2.4: Adaptive current bias control implemented with a feedback loop [4].

Figure 2.5: Dynamic current bias control implemented with a feedforward path [5].

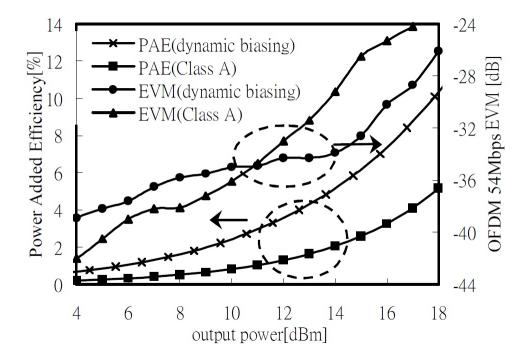

Dynamic current biasing can also be implemented by current-combining various PA branches that are biased differently ([6]), as illustrated in Fig. 2.8. The auxiliary PA (aux-PA) is biased deep into class-B and it only conducts enough quiescent current to deliver signal power when the input power is higher than some threshold. The idea can be further

Figure 2.6: The measured large-signal gain flatness is improved by dynamic current biasing [5].

Figure 2.7: The measured EVM and PAE are improved by dynamic current biasing [5].

extended to the case where multiple aux-PAs are current-combined and therefore multiple levels of biasing currents would respond to multiple input power levels. In [6], the biasing for the main- and aux-PA can be designed differently, allowing one more degree of design freedom for the tradeoff between linearity and efficiency. The linearized PA delivers a  $P_{sat}$  of 28.3dBm with 35.3% drain efficiency; the WLAN OFDM power at -28dB EVM is 21.2dBm with 19% drain efficiency. This implementation is inherently more amenable to static predistortion, because it gets rid of an explicit envelope filter for time-averaging, which would otherwise be realized with memory elements (i.e. capacitors) ([4][5]). The employment of the envelope filter makes the present biasing also strongly dependent on previous history of input power levels, posing challenges to static predistortion.

Figure 2.8: Dynamic current biasing implemented by an aux-PA biased differently [6].

The dynamic current biasing technique, which attempts to have the biasing level track the signal amplitude, can only achieve class-B efficiency back-off characteristic at best (Table 2.1). As summarized in Table 2.1, efficiencies at the same  $P_{out}$  with class-B backoff characteristic are calculated by Eq.(2.12) and shown in the third column.

$$\eta_{class-B,P_{out}} = \eta_{P_{sat}} \times 10^{-\frac{P_{backoff}}{20}} \tag{2.12}$$

where  $P_{backoff}$  is the power backoff from  $P_{sat}$  in dB. With two exceptions ([6] and [20]), the class-B extrapolated efficiencies are all better than the measured results. For [6], it has been confirmed that the measured efficiency at  $P_{sat}$  is degraded by the elevated temperature due to the increased heat dissipation under this high power condition; as the  $P_{out}$  backs off by more than 7dB from  $P_{sat}$ , the temperature goes down and the efficiency increases. Therefore the exact  $\eta_{P_{sat}}$  for [6] in Eq.(2.12) is higher than the measured value that is actually used in the equation. In [20], the measured PAE remains roughly the same over a  $P_{out}$  range from 25.0 to 27.5dBm, indicating some other mechanisms that are also affecting the PAE.

| Ref  | $P_{sat}/\eta ~[dBm/\%]$ | Linear $P_{out}/\eta ~[dBm/\%]$ | $\eta$ with class-B backoff [%] |

|------|--------------------------|---------------------------------|---------------------------------|

| [4]  | 28.3 / 52.4              | $17.3 \ ^{1}/ \ 11.8$           | 14.8                            |

| [5]  | 25.3 / N.A.              | 17.0 / 8.9                      | N.A.                            |

| [6]  | 28.3 / 35.3              | 21.2 / 19.0                     | 15.6                            |

| [20] | 27.5 / 15.0              | 20.0 / 7.2                      | 6.3                             |

| [21] | 26.0 / 27.0              | $15.0 \ ^{1}/ \ 5.0$            | 7.6                             |

Table 2.1: Efficiency back-off characteristics with dynamic current biasing.

<sup>1</sup> PAPR of 11dB is assumed for WCDMA downlink carrier.

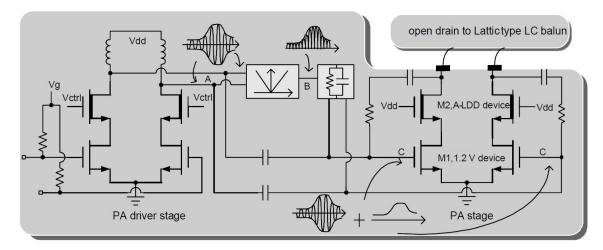

As shown in Eq.(2.1), the drain efficiency is the normalized output current times the normalized output voltage. Dynamic current biasing tries to make the supply current track the signal amplitude to improve the efficiency of transconductance-based PAs. The efficiency can also be enhanced by making the supply voltage to track signal levels. This can be achieved by either the supply modulation with fixed drain impedances seen by the PA or by the drain impedance modulation with a fixed supply voltage. If the modulation scheme can convey a non-linear envelope without relying on the transistor  $g_m$ , a switching-mode PA can be used and a constant peak efficiency can be theoretically achieved regardless of output power levels, as discussed below.

### 2.3 Envelope Elimination and Restoration (Polar Modulation)

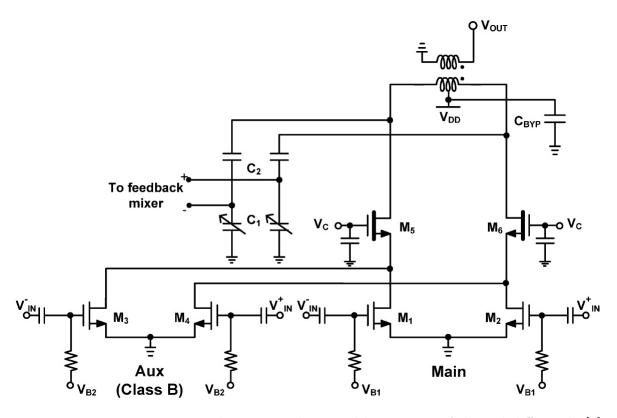

In an Envelope Elimination and Restoration system ([22]), a phase modulated signal with constant envelope is amplified by an efficient, non-linear switching PA while the amplitude information is restored through the PA supply modulation (Fig. 2.9). Because the non-linear envelope is conveyed by supply modulation, a non-linear switching PA (class-D, class-E, class-F and etc) can be employed to amplify the constant-envelope and phase-modulated signal at its input, offering higher efficiency compared to its linear counterpart (e.g., class-A and class-AB PA). With an ideal supply modulator, this architecture can achieve 100% theoretical

efficiency regardless of power levels. In fact, an EER system is a polar transmitter where the modulated signal is decomposed into a phase-modulated RF component and a baseband envelope component.

Figure 2.9: An Envelope Elimination and Restoration (EER) TX [7].

The implementation of the supply modulator for an EER system, however, typically suffers from a serious trade-off among efficiency, bandwidth and linearity. It has to support a supply current to the order of several hundred milli-amperes (mAs) and above, with a high Peak-to-Average-Ratio (PAR) and a large bandwidth. The bandwidth requirement for the supply modulator may be much more (3-10x) than the corresponding BB signal bandwidth due to bandwidth expansion from Cartesian to polar conversion ([23]). In this section, our review will focus on the design of the supply modulator, which is usually the efficiency bottleneck in an EER system.