# **UC Irvine**

# **ICS Technical Reports**

#### **Title**

A design representation model for high-level synthesis

#### **Permalink**

https://escholarship.org/uc/item/96500274

#### **Authors**

Rundensteiner, Elke A. Gajski, Daniel D.

#### **Publication Date**

1990

Peer reviewed

# A Design Representation Model For High-Level Synthesis

Elke A. Rundensteiner and Daniel D. Gajski

Department of Information and Computer Science University of California, Irvine September, 1990

Technical Report 90-27

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

# A DESIGN REPRESENTATION MODEL FOR HIGH-LEVEL SYNTHESIS

Elke A. Rundensteiner and Daniel D. Gajski

Department of Information and Computer Science

University of California, Irvine

Irvine, CA 92717

September, 1990

#### ABSTRACT

Design tools share and exchange various types of information pertaining to the design. The identification of a uniform design representation to capture this information is essential for the development of a successful design environment. We have done an extensive study on the representation needs of existing database tools in the UCI CADLAB; examples of which are graph compilers for high-level hardware specifications, state schedulers, hardware allocators, and micro-architecture optimizers. The result of this study is the development of a design representation model that will serve as a common internal representation (DDM) for all system and behavioral synthesis tools. DDM thus builds the foundation for a CAD Framework in which design tools can communicate via operating on this common representation. The design information is composed of three separate graph models: the conceptual model, the behavioral model and the structural model. The conceptual model (represented by a Design Entity Graph) captures the overall organization of the design information, such as, versions and configurations. The behavioral model (represented by an Augmented Control/Data Flow Graph) describes the design behavior. The structural model (represented by an Annotated Component Graph) captures the hierarchical data path structure and its geometric information. In this paper, we define the last two graph models. They both capture the actual design data of the application domain. Since VHDL has gained increasing popularity as hardware description language for synthesis, we give numerous examples throughout this report that show how the proposed design representation model can be used to represent VHDL specifications.

Key Words: Design Data Model, Design Representation for Computer-Aided Design, Hierarchical Control/Data Flow Graph, State Transition Graph, Annotated Component Graph.

CONTENTS

# Contents

| 1 INTRODUCTION                      |     | UCTION                             | 1                                                           |    |

|-------------------------------------|-----|------------------------------------|-------------------------------------------------------------|----|

| 2 THE DESIGN DATA MODEL: BASIC CONC |     |                                    | SIGN DATA MODEL: BASIC CONCEPTS                             | 3  |

|                                     | 2.1 | Gene                               | ral Goals                                                   | 3  |

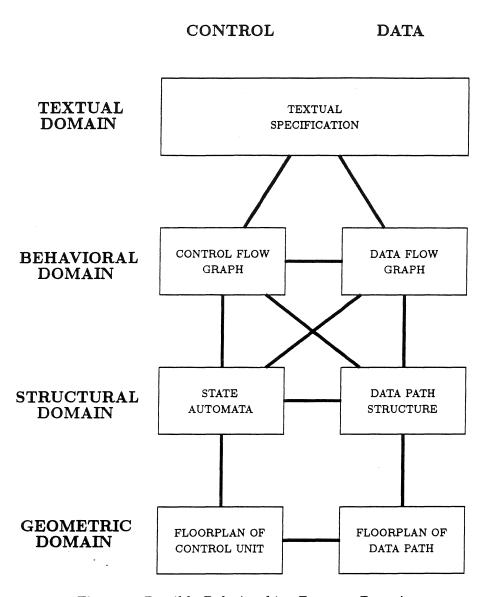

|                                     | 2.2 | Multi                              | ple Domains                                                 | 4  |

|                                     | 2.3 | The (                              | CDFG Model                                                  | 2  |

|                                     | 2.4 | The I                              | Design Representation Continuum Problem                     | 6  |

|                                     | 2.5 | Found                              | dation of DDM                                               | 9  |

| 3                                   | тн  | E DA                               | TA FLOW GRAPH                                               | 11 |

|                                     | 3.1 | The I                              | Oata Flow Graph Definition                                  | 11 |

|                                     | 3.2 | Repre                              | esentation of the Data Flow Vertices                        | 12 |

|                                     | 3.3 | Repre                              | esentation of the Data Flow Arcs                            | 18 |

|                                     | 3.4 | Modeling with Data Flow Constructs |                                                             | 20 |

|                                     |     | 3.4.1                              | Separate Data Flow Nodes for Accesses to the Same Variable. | 20 |

|                                     |     | 3.4.2                              | Data Types                                                  | 20 |

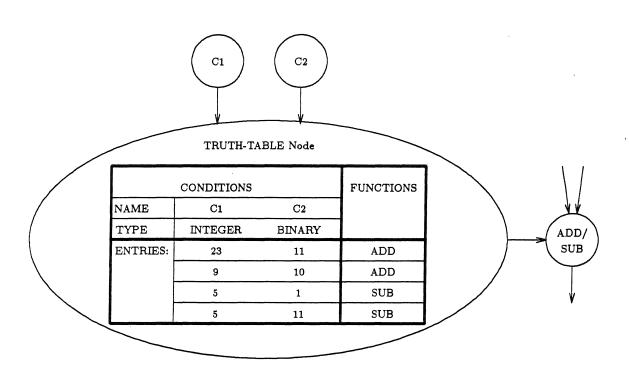

|                                     |     | 3.4.3                              | Operator Nodes Revisited                                    | 20 |

|                                     |     | 3.4.4                              | Access to Registers                                         | 22 |

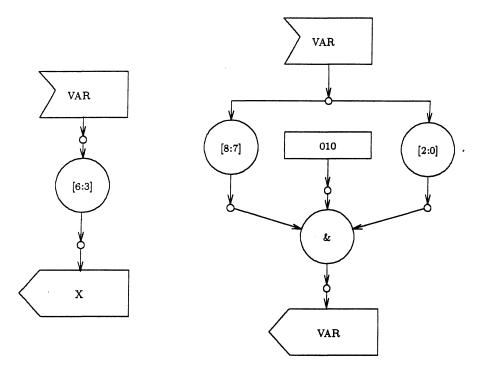

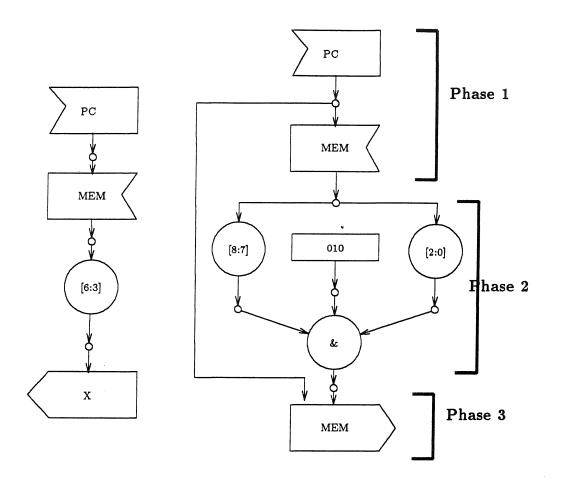

|                                     |     | 3.4.5                              | Access to Memory                                            | 22 |

|                                     |     | 3.4.6                              | Variable References and Dependencies                        | 25 |

|                                     |     | 3.4.7                              | Array References and Dependencies                           | 26 |

|                                     |     | 3.4.8                              | Formal Procedure Parameters and Dependencies                | 26 |

|                                     |     | 3.4.9                              | Design Entity Ports and Dependencies                        | 29 |

|                                     |     | 3.4.10                             | Modeling a Condition in the Data Flow Graph                 | 30 |

|                                     |     | 3.4.11                             | Selected Signal Assigment Statements                        | 31 |

|                                     |     | 3.4.12                             | Conditional Signal Assignment Statements                    | 33 |

|                                     |     | 3,4.13                             | Loops in the Data Flow Graph                                | 34 |

|                                     |     | 3.4.14                             | Events in the Data Flow Graph                               | 35 |

|                                     |     | 9 1 15                             | Path Related Timing Constraints                             | 38 |

|   |         | 3.4.16   | Event-Related Timing Constraints              | 46 |

|---|---------|----------|-----------------------------------------------|----|

| 4 | TH      | IE CO    | NTROL FLOW GRAPH                              | 52 |

|   | 4.1     | The C    | Control Flow Graph Definition                 | 52 |

|   | 4.2     | Repre    | esentation of the Control Flow Vertices       | 53 |

|   | 4.3     | Repre    | esentation of the Control Flow Arcs           | 59 |

|   | 4.4     | Mode     | ling with Control Flow Constructs             | 60 |

|   |         | 4.4.1    | Process Statement                             | 60 |

|   |         | 4.4.2    | Subprogram Specification                      | 61 |

|   |         | 4.4.3    | Concurrent Block Statement                    | 63 |

|   |         | 4.4.4    | Concurrency versus Parallelism                | 65 |

|   |         | 4.4.5    | Procedure Call                                | 65 |

|   |         | 4.4.6    | The If-Statement                              | 67 |

|   |         | 4.4.7    | The Case Statement                            | 70 |

|   |         | 4.4.8    | The For Loop                                  | 70 |

|   |         | 4.4.9    | The While Loop                                | 73 |

|   |         | 4.4.10   | The Infinite Loop                             | 73 |

|   |         | 4.4.11   | The Generalized Condition Node                | 75 |

|   |         | 4.4.12   | Timing Constraints                            | 79 |

|   |         | 4.4.13   | Asynchronous Events                           | 82 |

|   |         | 4.4.14   | Process Sensitivity List                      | 85 |

| _ | <b></b> | D 000 10 |                                               |    |

| 5 |         |          | TE TRANSITION GRAPH                           | 86 |

|   | 5.1     | •        | ating State Information into the CDFG Model   | 86 |

|   | 5.2     |          | Transition Graph Definition                   | 88 |

|   | 5.3     | Repres   | sentation of the State Transition Graph Nodes | 89 |

|   | 5.4     | Repres   | entation of the State Transition Graph Arcs   | 91 |

|   | 5.5     | Discuss  | sion                                          | 92 |

|   | 5.6     | State I  | Information Extension to the CDFG             | 92 |

*CONTENTS*

| 6                                                            | The | ANN                                                      | OTATED COMPONENT GRAPH                                       | 95   |

|--------------------------------------------------------------|-----|----------------------------------------------------------|--------------------------------------------------------------|------|

|                                                              | 6.1 | Defini                                                   | tion of the Annotated Component Graph                        | 95   |

| 6.3 Representation of the Arcs in the Annotated Component Gr |     | sentation of the Nodes in the Annotated Component Graph  | 95                                                           |      |

|                                                              |     | sentation of the Arcs in the Annotated Component Graph   | 98                                                           |      |

|                                                              |     | re Detailed Description of the Annotated Component Graph | 99                                                           |      |

|                                                              |     | 6.4.1                                                    | Timing Constraints                                           | 99   |

|                                                              |     | 6.4.2                                                    | Structural Attributes of Component and Interconnection Nodes | 101  |

|                                                              |     | 6.4.3                                                    | Geometric Attributes of Component and Interconnection Nodes  | 102  |

|                                                              |     | 6.4.4                                                    | Timing Attributes of the Component and Interconnection Nodes | s103 |

|                                                              | 6.5 | An Ex                                                    | ample of an Annotated Component Graph                        | 104  |

| 7                                                            | OU! | R APF                                                    | PROACH TOWARDS THE LINKAGE PROBLEM                           | 108  |

|                                                              | 7.1 | Linkag                                                   | e between the Behavioral and the Structural Domain           | 108  |

|                                                              | 7.2 | A Com                                                    | aplete Example: The Programmable Counter                     | 109  |

|                                                              | 7.3 | Summ                                                     | ary of our Linkage Approach                                  | 113  |

| 8                                                            | CO  | NCLUS                                                    | SION                                                         | 116  |

| 8                                                            | BIB | LIOGI                                                    | RAPHY                                                        | 117  |

# List of Figures

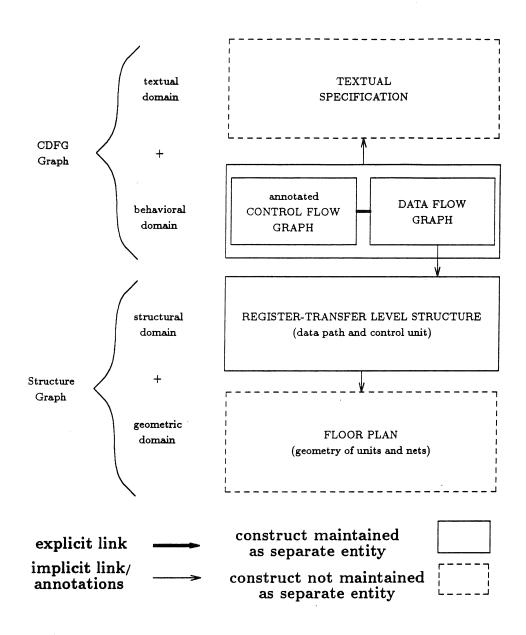

| 1  | Possible Relationships Between Domains                                              | 8  |

|----|-------------------------------------------------------------------------------------|----|

| 2  | Grapical Representation of Nodes in the Data Flow Graph                             | 13 |

| 3  | Grapical Representation of Arcs in the Data Flow Graph                              | 14 |

| 4  | The TRUTH-TABLE Node Type                                                           | 21 |

| 5  | Variable Access Representation                                                      | 23 |

| 6  | Subscript Access Representation                                                     | 24 |

| 7  | Formal Procedure Parameters and Dependencies                                        | 28 |

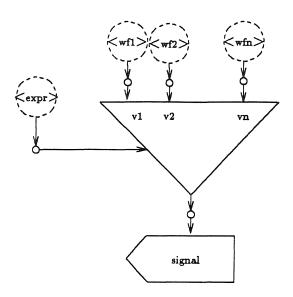

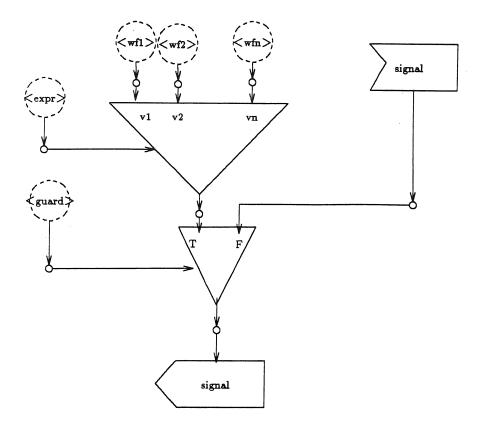

| 8  | The Choose Value Node Type                                                          | 30 |

| 9  | VHDL Selected Signal Assignment                                                     | 31 |

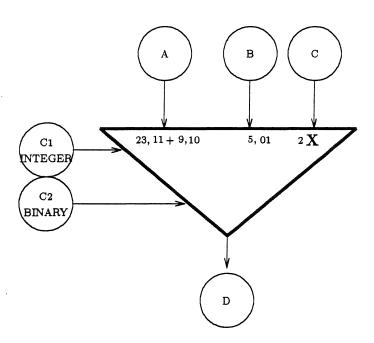

| 10 | CDFG Choose-Value Node                                                              | 32 |

| 11 | VHDL Selected Signal Assignment with Guard                                          | 33 |

| 12 | CDFG Choose-Value Node with Guard                                                   | 34 |

| 13 | VHDL Conditional Signal Assignment with Guard                                       | 35 |

| 14 | CDFG Representation for a Conditional Signal Assignment                             | 36 |

| 15 | Signal-Related Attributes in a Conditional-Signal Assignment Statement              | 37 |

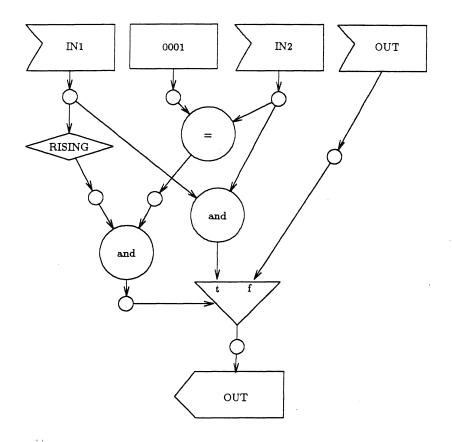

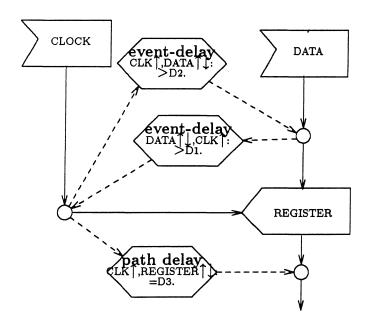

| 16 | Events in the Data Flow Graph                                                       | 37 |

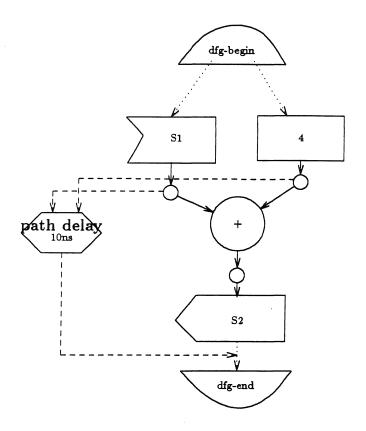

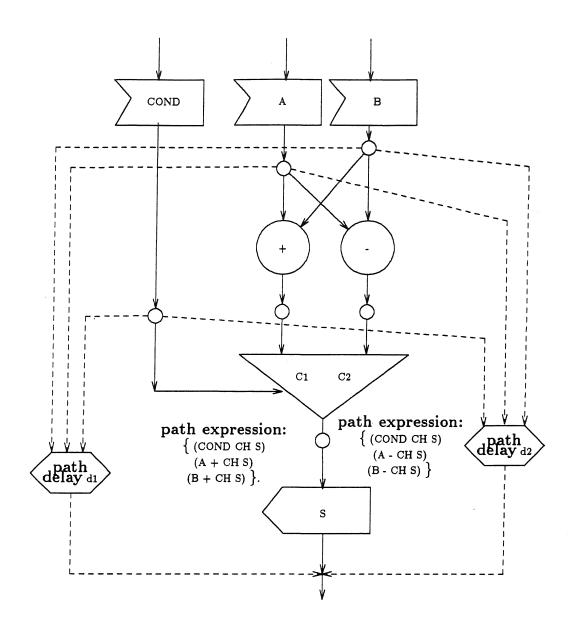

| 17 | A Simple Path Delay                                                                 | 40 |

| 18 | VHDL Specification of a Path-Delay.                                                 | 41 |

| 19 | VHDL Specification of Path Delays. (Selected Signal Assignment with After-Clauses.) | 42 |

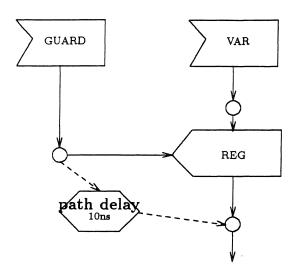

| 20 | Modeling the Delay of a Register                                                    | 45 |

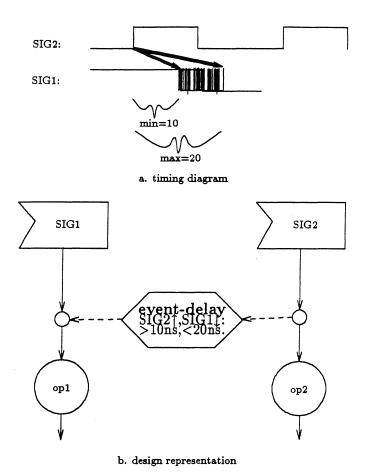

| 21 | The Representation of Event-related Timing Constraints                              | 47 |

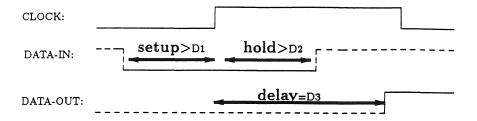

| 22 | Timing Diagram for Set-up, Hold and Register Delays                                 | 49 |

| 23 | CDFG Representation of Set-up and Hold Times                                        | 49 |

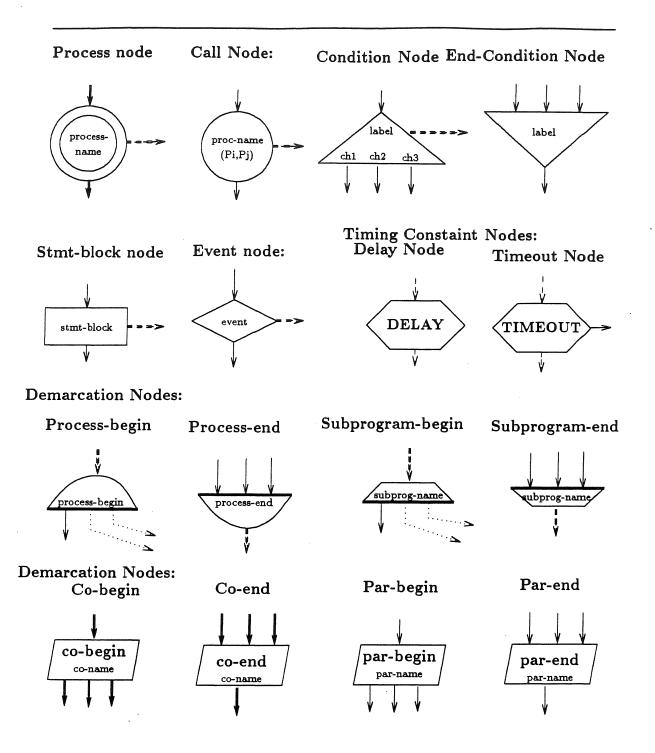

| 24 | Graphical Representation of Nodes in the Control Flow Graph                         | 54 |

| 25 | Graphical Representation of Arcs in the Control Flow Graph                          | 55 |

| 26 | A VHDI Process Specification                                                        | 60 |

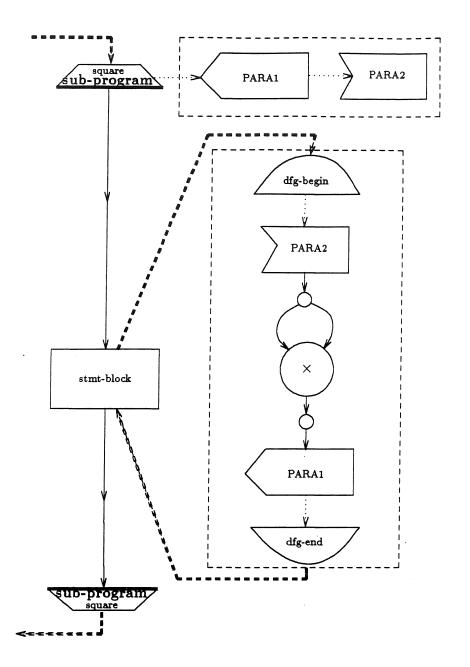

| 27 | A VHDL Procedure Specification                                                      | 61 |

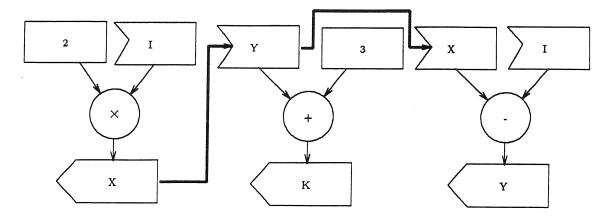

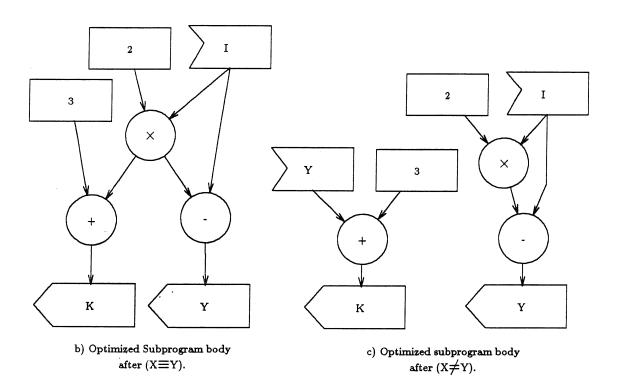

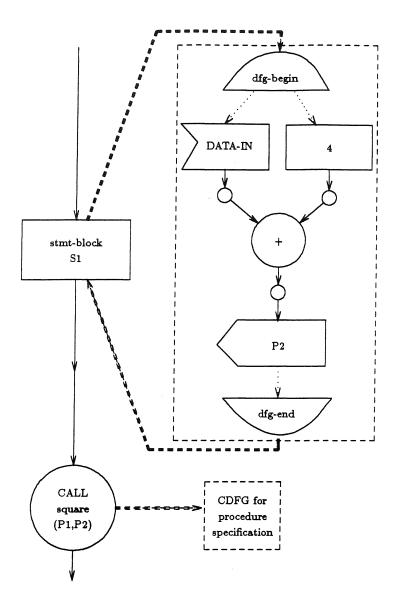

| 28 | CDFG Representation of the Procedure Specification Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62 . |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

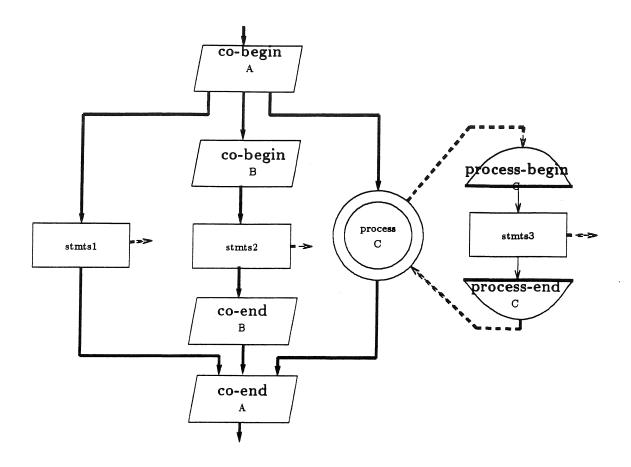

| 29 | A VHDL Block Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63   |

| 30 | A VHDL Block Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64   |

| 31 | CDFG Representation of the Procedure Call Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66   |

| 32 | VHDL If-Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68   |

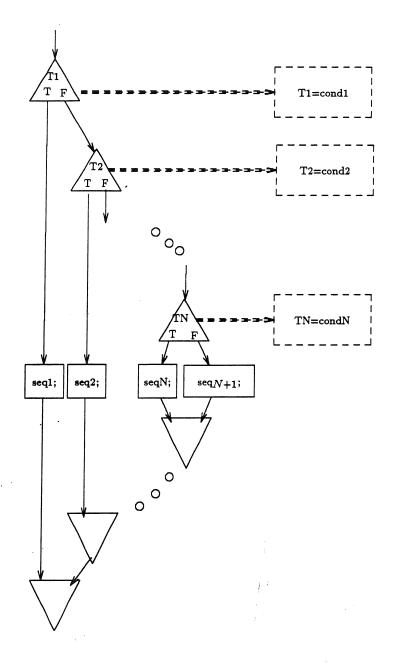

| 33 | CDFG Representation of the If-Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68   |

| 34 | VHDL Case Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71   |

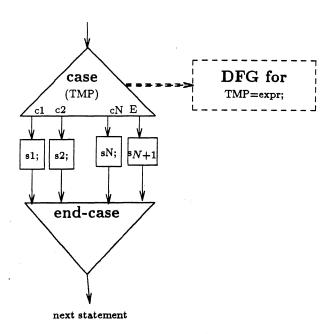

| 35 | CDFG Representation of the Case Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71   |

| 36 | VHDL For-Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72   |

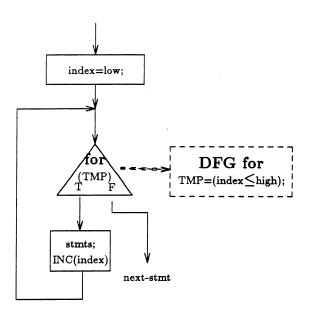

| 37 | CDFG Representation of the For-Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72   |

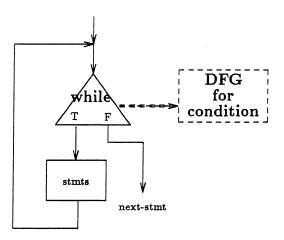

| 38 | VHDL While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74   |

| 39 | CDFG Representation of the While-Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74   |

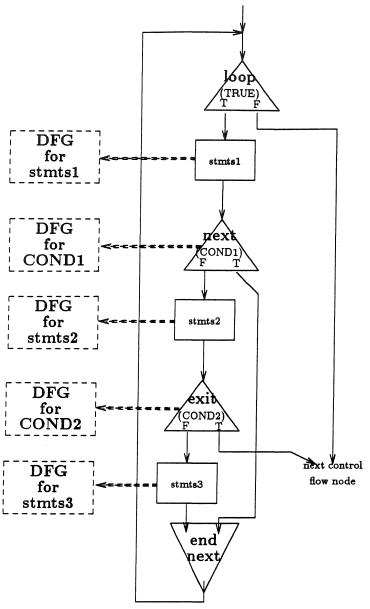

| 40 | CDFG Representation of the Infinite Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76   |

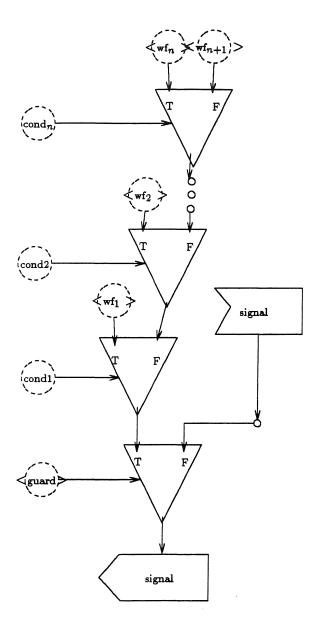

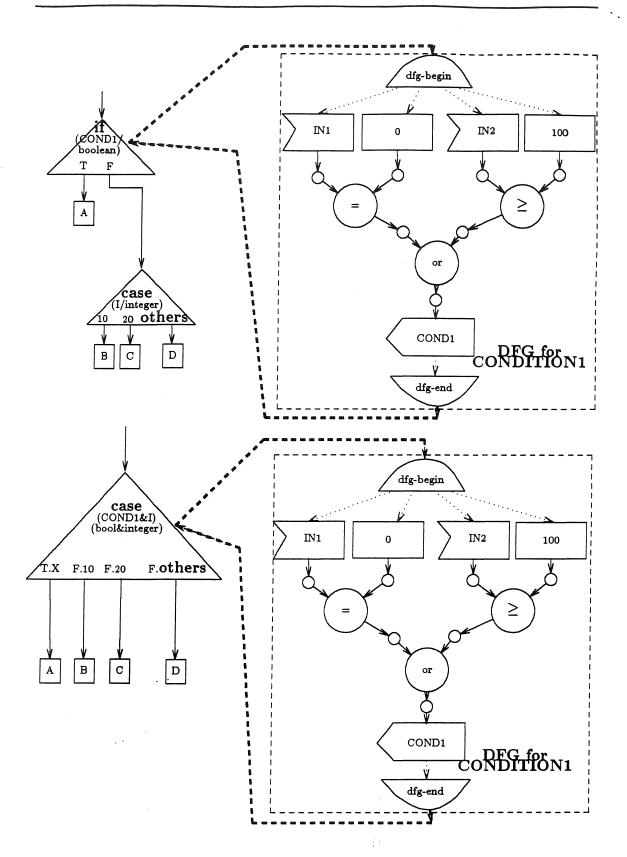

| 41 | VHDL Specification of Nested Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 77   |

| 42 | CDFG Representation of the Extended Condition Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78   |

| 43 | VHDL Wait Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79   |

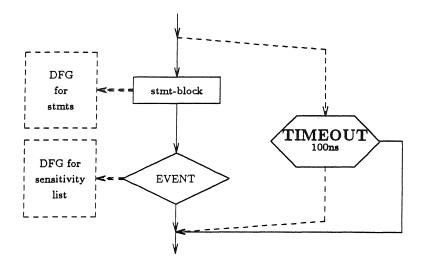

| 44 | CDFG Representation of the Wait-For Construct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80   |

| 45 | CDFG Representation of the Wait-On-For Construct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81   |

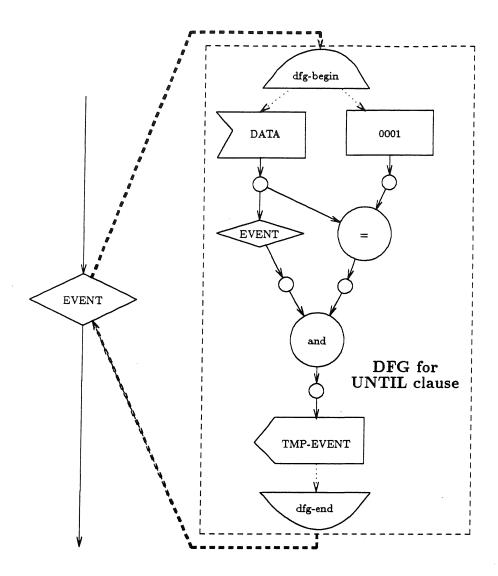

| 46 | CDFG Representation of the Wait-Until Construct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83   |

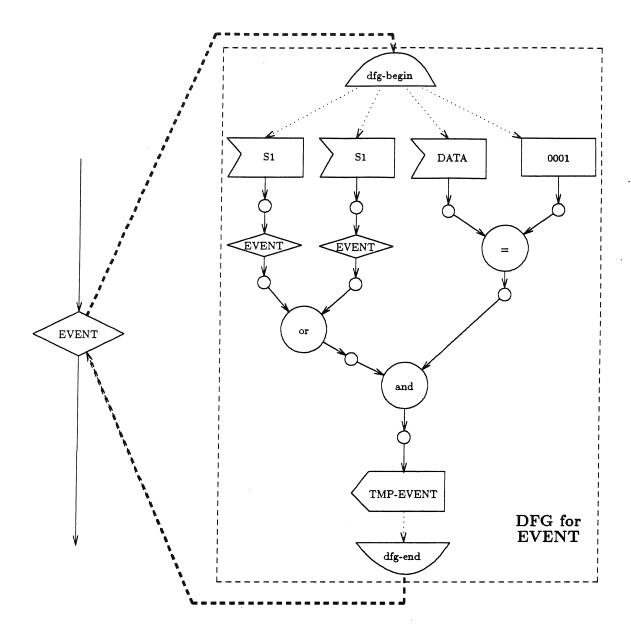

| 47 | CDFG Representation of the Wait-On-Until Construct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84   |

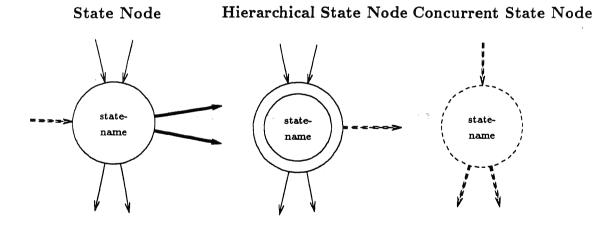

| 48 | Graphical Representation of Nodes in the State Transition Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89   |

| 49 | Graphical Representation of Arcs in the State Transition Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90   |

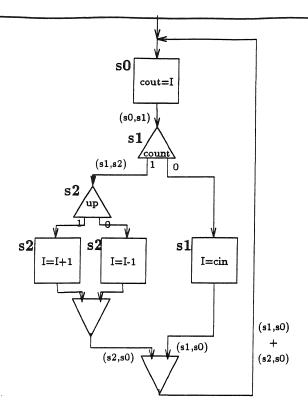

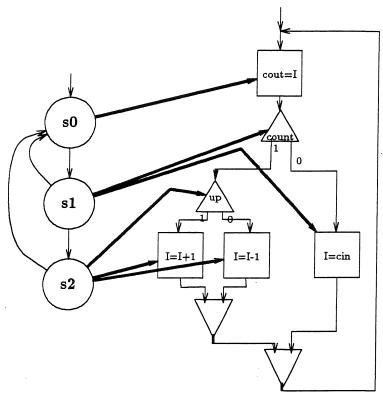

| 50 | CDFG of Counter Example with State Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93   |

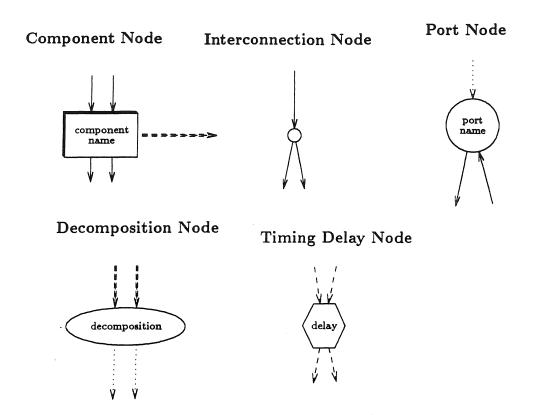

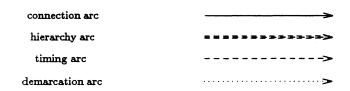

| 51 | Graphical Representation of Nodes in the Annotated Component Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96   |

| 52 | Graphical Representation of Arcs in the Annotated Component Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96   |

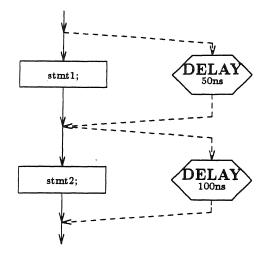

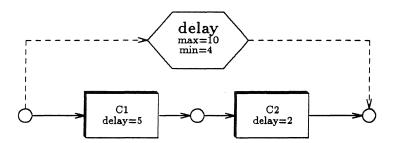

| 53 | Timing Constraints in the Annotated Component Graph 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00   |

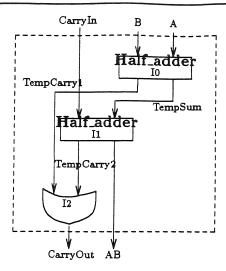

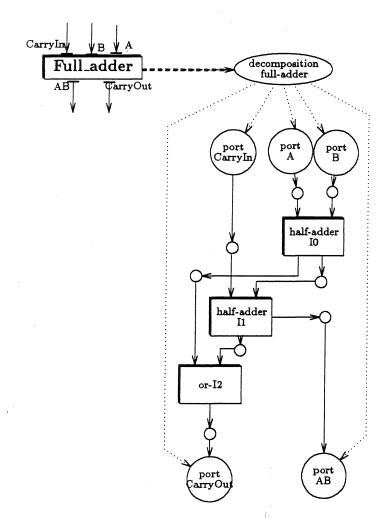

| 54 | Entity Declaration and Architecture Body of a Full-Adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 05   |

| 55 | Block Diagram of the Full-Adder Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 66 | Annotated Component Graph for the Full-Adder Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 06   |

|    | in the second of | 1    |

LIST OF FIGURES vi

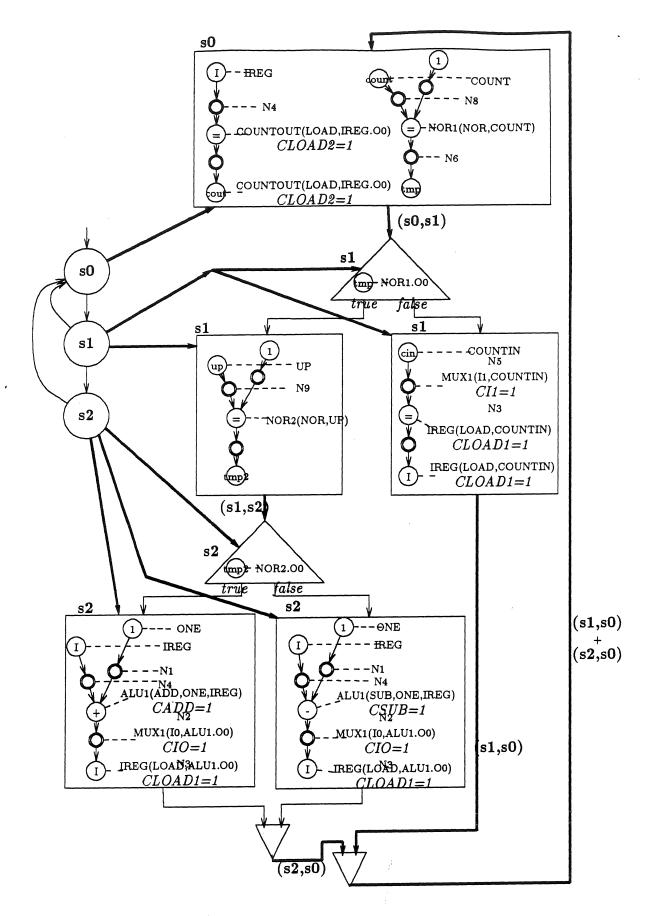

| 57 | VHDL Specification of a 4 bit programmable up and down counter . | 109 |

|----|------------------------------------------------------------------|-----|

| 58 | The State Table                                                  | 110 |

| 59 | Complete Flow Graph Representation of the Counter                | 111 |

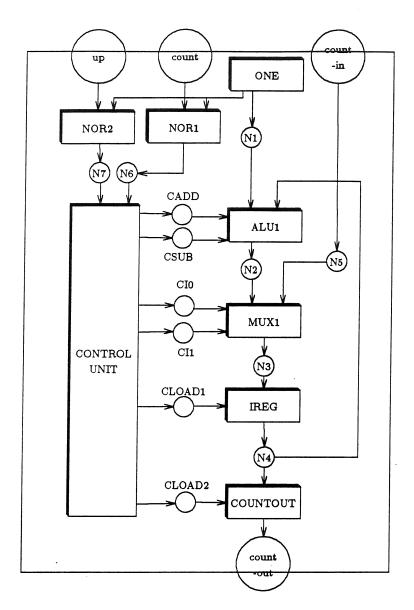

| 60 | Data Path of the Counter Example                                 | 112 |

| 61 | DDM's Approach towards the Linkage Problem                       | 114 |

## 1 INTRODUCTION

Design tools, such as system and behavioral synthesis tools, have to share and exchange diverse types of information during the course of the design exploration process. For the integration of this variety of design information into one unified representation we define the design data model (DDM). The identification and definition of such a uniform design representation is essential as the synthesis tools interact via operating on this common representation. This design representation is to be maintained by a design database. In this report, we describe the design model, while a description of the design data base architecture and its functionality will be given in a later report.