## UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Processing in Memory using Emerging Memory Technologies

### Permalink

https://escholarship.org/uc/item/95z3z84c

### **Author** Gupta, Saransh

## Publication Date 2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

Processing in Memory using Emerging Memory Technologies

A Thesis submitted in partial satisfaction of the requirements for the degree of Master of Science

in

### Electrical and Computer Engineering (Electronic Circuits and Systems)

by

### Saransh Gupta

Committee in charge:

Professor Tajana Šimunić Rosing, Chair Professor Chung-Kuan Cheng Professor Farinaz Koushanfar

Copyright Saransh Gupta, 2018 All rights reserved. The Thesis of Saransh Gupta is approved and is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2018

#### ACKNOWLEDGEMENTS

I thank my advisor, Professor Tajana S. Rosing for her support throughout the course of my degree. I thank her for her guidance which helped me in solving numerous problems and made this thesis possible. Her enthusiasm and willingness to explore new domains have always encouraged me to look at a problem from different perspectives. I am grateful to her for giving me the opportunity to do research with her. I would also like to thank my thesis committee members, Professors Chung-Kuan Cheng and Farinaz Koushanfar, for their time to review my research and their insightful comments. Finally, I would like to thank my current and former labmates (Mohsen Imani, Yeseong Kim, Joonseop Sim, Michael Ostertag, Daniel Peroni, Minxuan Zhao, Sahand Salamat, Yunhui Guo, Ricardo Garcia, Samuel Bosch, Harveen Kaur, Sahil Sharma, Christine Chan) for their continuous support.

The material in this thesis is based on the following publications.

Chapter 3, in part, is a reprint of the material as it appears in M. Imani, S. Gupta, T. Rosing, "Ultra-Efficient Processing In-Memory for Data Intensive Applications," *Proc. IEEE/ACM Design Automation Conference*, 2017, pp. 1-6.

Chapter 4, in part, is a reprint of the material as it appears in M. Imani, S. Gupta, T. Rosing, "GenPIM: Generalized Processing In-Memory to Accelerate Data Intensive Applications," *Proc. IEEE/ACM Design Automation and Test in Europe Conference*, 2018, pp. 1155-1158.

Chapter 5, in part, has been submitted for publication of the material as it may appear in S. Gupta, M. Imani, H. Kaur, T. Rosing, "NNPIM: A Processing In-Memory Architecture for Neural Network Acceleration," *IEEE Transactions on Computers*, 2019.

Chapter 6, in part, is a reprint of the material as it appears in M. Imani, S. Gupta, A. Arredondo, T. Rosing, "Efficient Query Processing in Crossbar Memory," *Proc. IEEE/ACM International Symposium on Low Power Electronics and Design*, 2017, pp. 1-6 and M. Imani, S. Gupta, S. Sharma, T. Rosing, "NVQuery: Efficient Query Processing in Non-Volatile Memory," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2018.

My co-authors (Atl Arredondo, Mohsen Imani, Harveen Kaur, Prof. Tajana S. Rosing,

and Sahil Sharma, listed in alphabetical order) have all kindly approved the inclusion of the aforementioned publications in my thesis.

| Signatur                            | e Page .                                                              |                                                                                                                                                                                                                  | iii                                                      |

|-------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Acknow                              | ledgeme                                                               | ents                                                                                                                                                                                                             | iv                                                       |

| Table of                            | Conten                                                                | ts                                                                                                                                                                                                               | vi                                                       |

| List of F                           | igures .                                                              |                                                                                                                                                                                                                  | viii                                                     |

| List of T                           | ables                                                                 |                                                                                                                                                                                                                  | X                                                        |

| Vita                                |                                                                       |                                                                                                                                                                                                                  | xi                                                       |

| Abstract                            | of the T                                                              | Thesis                                                                                                                                                                                                           | xii                                                      |

| Chapter                             | 1 Intr                                                                | oduction                                                                                                                                                                                                         | 1                                                        |

| Chapter<br>2.1<br>2.2<br>2.3<br>2.4 | Memri<br>Near-D<br>Process<br>2.3.1<br>2.3.2<br>2.3.3                 | Skground and Related Work         Stive Memory         Data Computing         Sing in-Memory         SRAM PIM         DRAM PIM         NVM PIM         pplication Examples                                       | 5<br>5<br>7<br>7<br>7<br>7<br>8<br>9<br>10               |

| Chapter                             | 3 PIN                                                                 | I for Data Intensive Applications                                                                                                                                                                                | 15                                                       |

| 3.1<br>3.2<br>3.3                   | 3.1.1<br>3.1.2<br>APIM<br>Results<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | Architecture         Fast Addition in APIM         Multiplication in APIM         Approximation         Experimental Setup         APIM vs state-of-the-art         Approximate APIM         APIM & Dataset Size | 15<br>16<br>18<br>22<br>24<br>24<br>24<br>25<br>26<br>27 |

| Chapter 4.1 4.2 4.3                 | GenPII<br>4.1.1<br>4.1.2                                              | a Management in a PIM Supported Heterogeneous System         M: A Generalized PIM         GenPIM Architecture Overview         Functions Supported by GenPIM         M Data Management                           | 29<br>29<br>31<br>31<br>32<br>34                         |

|                                     | 4.3.1                                                                 | Experimental Setup                                                                                                                                                                                               | 34                                                       |

### TABLE OF CONTENTS

|          | 4.3.2  | Data size                                                      | 36 |

|----------|--------|----------------------------------------------------------------|----|

| Chapter  | 5 Pro  | cessing In-Memory Architecture for Neural Network Acceleration | 38 |

| 5.1      |        | Networks                                                       | 38 |

| 5.2      |        | r Neural Networks                                              | 39 |

| 5.3      |        | / Design                                                       | 41 |

|          | 5.3.1  | NNPIM Overview                                                 | 41 |

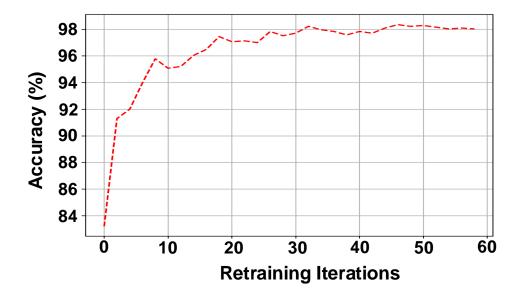

|          | 5.3.2  | Weight Clustering in NNPIM                                     | 42 |

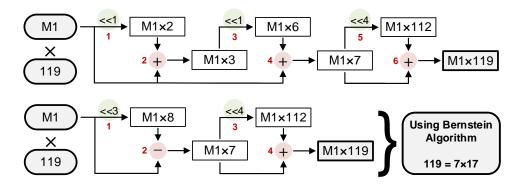

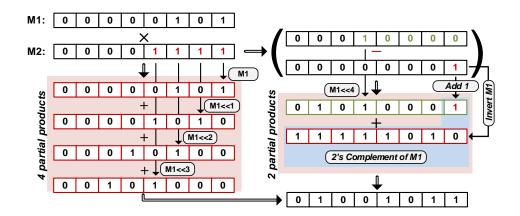

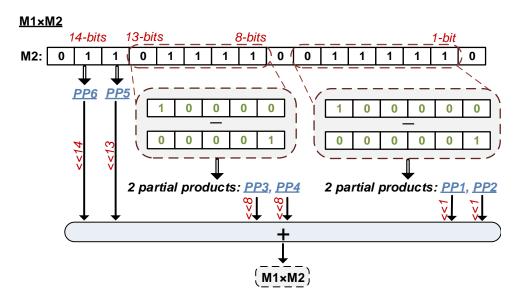

|          | 5.3.3  | NNPIM Multiplication                                           | 43 |

|          | 5.3.4  | NNPIM Architecture                                             | 47 |

|          | 5.3.5  | In-Memory Parallelism                                          | 50 |

| 5.4      | Experi | mental Results                                                 | 52 |

|          | 5.4.1  | Experimental Setup                                             | 52 |

|          | 5.4.2  | NNPIM & Weight Sharing                                         | 53 |

|          | 5.4.3  | Energy-performance Efficiency                                  | 55 |

|          | 5.4.4  | Area Overhead                                                  | 56 |

| Chapter  | 6 Eff  | cient Query Processing in NVM                                  | 58 |

| 6.1      |        | ery Accelerator                                                | 58 |

| 0.1      | 6.1.1  | Exact Search                                                   | 60 |

|          | 6.1.2  | Nearest Distance Search                                        | 61 |

|          | 6.1.3  | Join                                                           | 62 |

|          | 6.1.4  | Bit-wise Operations and Addition                               | 63 |

| 6.2      | Hardw  | are Support                                                    | 64 |

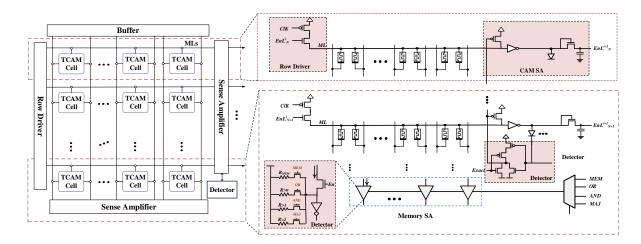

|          | 6.2.1  | Exact Search                                                   | 65 |

|          | 6.2.2  | Nearest Distance Search                                        | 66 |

|          | 6.2.3  | Bit-wise Operation and Addition                                | 69 |

| 6.3      | Approx | kimation in NVQuery                                            | 70 |

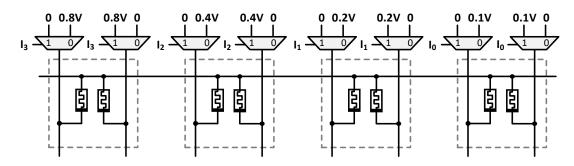

|          | 6.3.1  | Bit Trimming                                                   | 71 |

|          | 6.3.2  | Voltage Scaling                                                | 72 |

| 6.4      | Experi | mental Results                                                 | 73 |

|          | 6.4.1  | Experimental setup                                             | 73 |

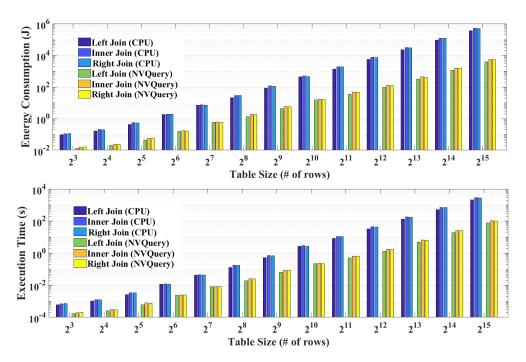

|          | 6.4.2  | NVQuery Efficiency                                             | 74 |

|          | 6.4.3  | NVQuery & Dataset Size                                         | 75 |

|          | 6.4.4  | NVQuery Approximation                                          | 76 |

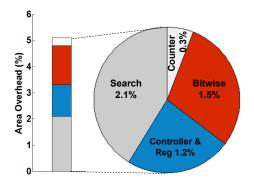

|          | 6.4.5  | Area Overhead                                                  | 78 |

| Chapter  | 7 Cor  | nclusion                                                       | 79 |

| Bibliogr | aphy   |                                                                | 80 |

### LIST OF FIGURES

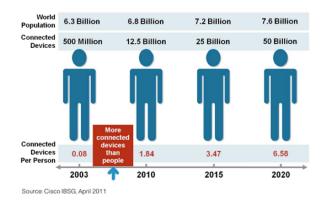

| Figure 1.1. | Increase in number of connected devices over the years                                                                                                                                                                                                                                      | 1  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

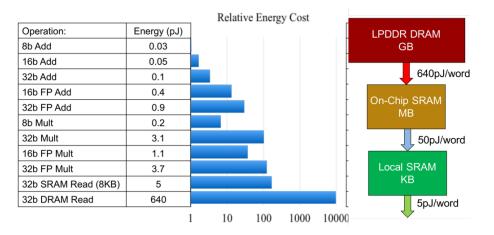

| Figure 1.2. | The cost of various operations in a typical computer organization. Reading data from DRAM is the most energy consuming operation.                                                                                                                                                           | 2  |

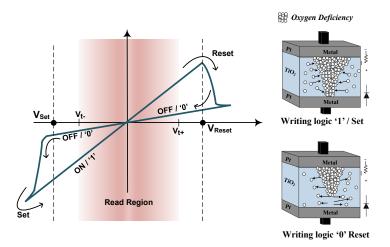

| Figure 2.1. | Working mechanism of memristor device when reading and writing                                                                                                                                                                                                                              | 6  |

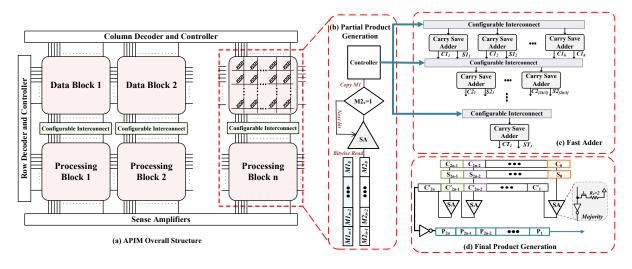

| Figure 3.1. | <ul><li>(a) The overall structure of APIM consisting of several data and processing blocks, (b) APIM controller and parallel product generator, (c) Fast adder tree structure consisting of carry save adder and configurable interconnects.</li><li>(d) Final product generator.</li></ul> | 17 |

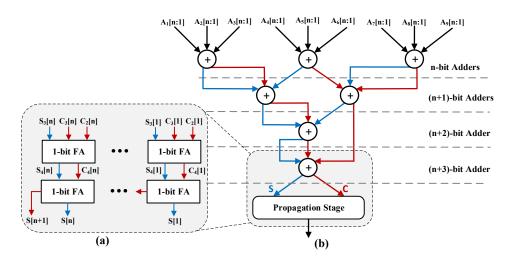

| Figure 3.2. | (a) Carry save addition (b) Tree structured addition of 9 n-bit numbers                                                                                                                                                                                                                     | 18 |

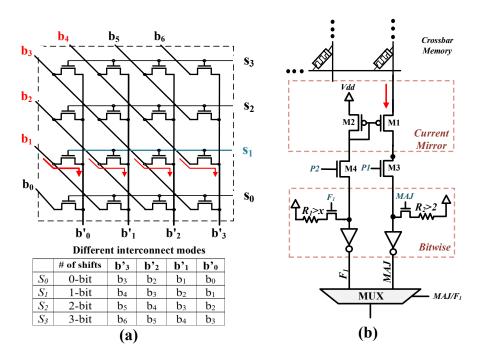

| Figure 3.3. | The circuit of (a) an interconnect (b) a sense amplifier                                                                                                                                                                                                                                    | 21 |

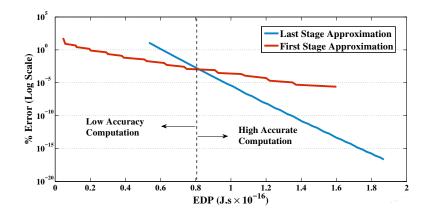

| Figure 3.4. | Error and EDP comparison of the two approximation approaches                                                                                                                                                                                                                                | 23 |

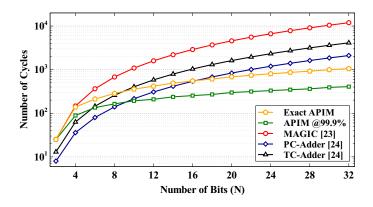

| Figure 3.5. | Performance comparison of the proposed design with previous work for addition of N operands, each sized N bits                                                                                                                                                                              | 25 |

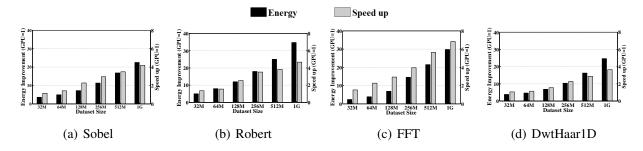

| Figure 3.6. | Energy consumption and speedup of exact APIM normalized to GPU vs different dataset sizes.                                                                                                                                                                                                  | 27 |

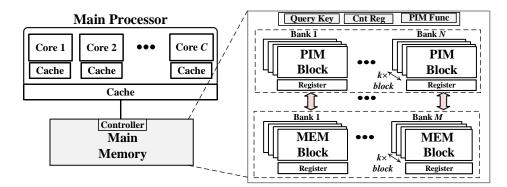

| Figure 4.1. | Architecture overview of the proposed GenPIM.                                                                                                                                                                                                                                               | 30 |

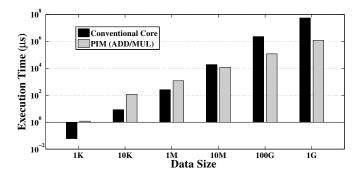

| Figure 4.2. | Execution time of conventional core and PIM addition/multiplication in different data sizes.                                                                                                                                                                                                | 33 |

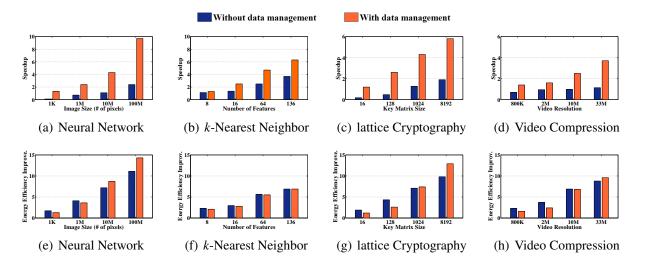

| Figure 4.3. | Speedup and energy efficiency improvement of proposed GenPIM as com-<br>pared to traditional cores.                                                                                                                                                                                         | 36 |

| Figure 5.1. | An example of MNIST classification accuracy during different retraining iterations when the NN weights are represented as eight cluster centers                                                                                                                                             | 44 |

| Figure 5.2. | Example of Bernstein's Algorithm                                                                                                                                                                                                                                                            | 45 |

| Figure 5.3. | Generating the partial products in latency-optimized NNPIM                                                                                                                                                                                                                                  | 46 |

| Figure 5.4. | Optimizing NNPIM by reducing the complexity of weights                                                                                                                                                                                                                                      | 48 |

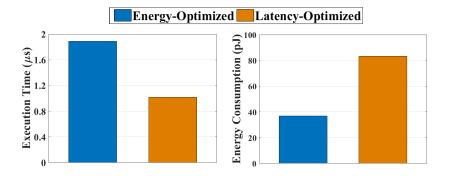

| Figure 5.5. | Execution time and energy consumption of 32-bit NNPIM multiplication in energy and latency-optimized.                                                                                                                                                                                       | 48 |

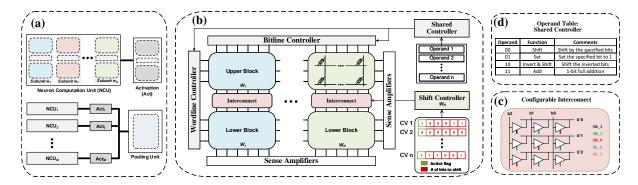

| Figure 5.6. | Architecture overview of the proposed NNPIM. (a) Overall view of neural network implementation in-memory; (b) in-memory implementation of neuron; (c) circuit for configurable interconnect; (d) functions used in NNPIM. | 49 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.7. | Operands and control vectors for two parallel NNPIM multiplications                                                                                                                                                       | 51 |

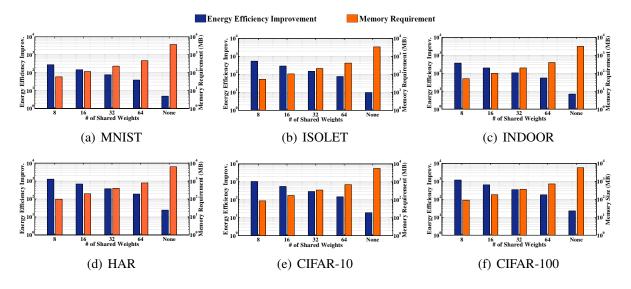

| Figure 5.8. | Energy consumption and memory size requirement of NNPIM with and without weight sharing.                                                                                                                                  | 55 |

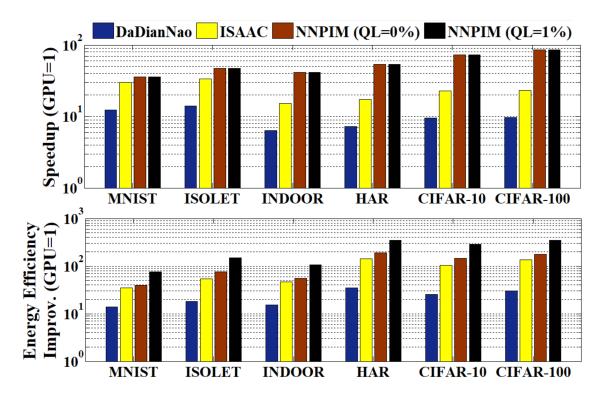

| Figure 5.9. | Comparing the energy consumption and execution time of NNPIM with state-of-the-art NN accelerators.                                                                                                                       | 56 |

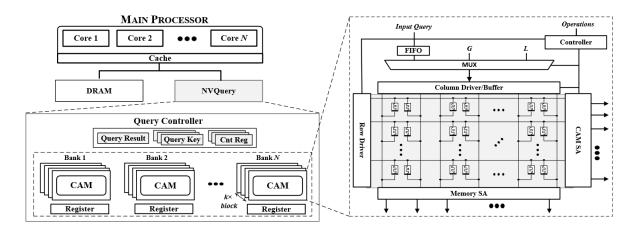

| Figure 6.1. | Proposed architecture with $N$ banks and $k \times N$ blocks. The right part details the crossbar implementation of memory banks along with the supporting control logic.                                                 | 59 |

| Figure 6.2. | Circuit level implementation of CAM SA, Memory SA, and Row Driver                                                                                                                                                         | 64 |

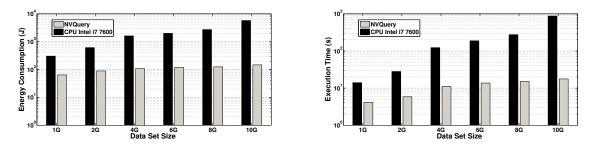

| Figure 6.3. | Energy consumption and performance of running join operations with different table sizes on traditional cores and the proposed NVQuery                                                                                    | 66 |

| Figure 6.4. | NVQuery in nearest distance search configuration.                                                                                                                                                                         | 67 |

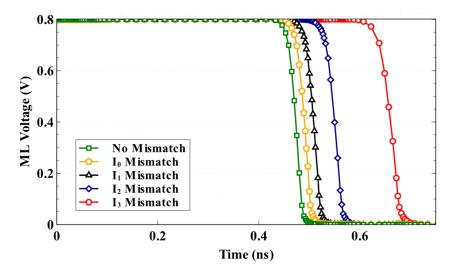

| Figure 6.5. | Timing characteristic of CAM block in nearest distance search configura-<br>tions.                                                                                                                                        | 67 |

| Figure 6.6. | Energy consumption and performance of query processing running on traditional core and the proposed NVQuery                                                                                                               | 74 |

| Figure 6.7. | Energy consumption and performance of the NVQuery at different approx-<br>imation levels.                                                                                                                                 | 76 |

| Figure 6.8. | Area overhead as compared to conventional crossbar memory                                                                                                                                                                 | 78 |

### LIST OF TABLES

| Table 3.1. | Quality of loss and EDP improvement of the proposed APIM compared to GPU in different level of approximation.                                                    | 26 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1. | Execution time of arithmetic functions using CMOS-based logic and differ-<br>ent PIM architectures.                                                              | 32 |

| Table 4.2. | Neural network configuration over CIFAR-10 dataset.                                                                                                              | 35 |

| Table 5.1. | NN models and baseline error rates for 6 applications (Input layer - $IN$ , Fully connected layer - $FC$ , Convolution layer - $C$ , and Pooling layer - $PL$ .) | 53 |

| Table 5.2. | Quality loss of different NN applications due to weight sharing                                                                                                  | 54 |

| Table 6.1. | NVQuery supported configurations                                                                                                                                 | 60 |

| Table 6.2. | NVQuery supported functionality                                                                                                                                  | 60 |

| Table 6.3. | Approximation in 16-Bit Addition                                                                                                                                 | 70 |

| Table 6.4. | NVQuery Approximation at Different Supply Voltages                                                                                                               | 72 |

| Table 6.5. | Energy Consumption and Performance Speedup of Queries in NVQuery<br>Normalized to Digital Design over 1k Data                                                    | 75 |

| Table 6.6. | Energy-Delay Product Improvement of SAQ, DAQ and Proposed NVQuery                                                                                                | 75 |

VITA

| 2016 | B.E.(Hons), Electrical and Electronics Engineering, Birla Institute of Technology |

|------|-----------------------------------------------------------------------------------|

|      | and Science Pilani, Goa Campus, India                                             |

- 2016-2018 Graduate Student Researcher, University of California, San Diego

- 2018 M.S. in Electrical and Computer Engineering, University of California, San Diego

### PUBLICATIONS

**S. Gupta**, M. Imani, T. Rosing, "FELIX: Fast and Energy-Efficient Logic in Memory," *Proc. IEEE/ACM International Conference on Computer Aided Design*, 2018.

M. Imani, R. Garcia, S. Gupta, T. Rosing, "RMAC: Runtime Configurable Floating Point Multiplier for Approximate Computing," *Proc. IEEE/ACM International Symposium on Low Power Electronics and Design*, 2018.

M. Zhou, M. Imani, **S. Gupta**, T. Rosing, "GAS: A Heterogeneous Memory Acceleration for Graph Processing," *Proc. IEEE/ACM International Symposium on Low Power Electronics and Design*, 2018.

M. Imani, S. Gupta, S. Sharma, T. Rosing, "NVQuery: Efficient Query Processing in Non-Volatile Memory," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2018.

M. Imani, **S. Gupta**, T. Rosing, "GenPIM: Generalized Processing In-Memory to Accelerate Data Intensive Applications," *Proc. IEEE/ACM Design Automation and Test in Europe Conference*, 2018, pp. 1155-1158.

M. Imani, S. Gupta, A. Arredondo, T. Rosing, "Efficient Query Processing in Crossbar Memory," *Proc. IEEE/ACM International Symposium on Low Power Electronics and Design*, 2017, pp. 1-6.

M. Imani, **S. Gupta**, T. Rosing, "Ultra-Efficient Processing In-Memory for Data Intensive Applications," *Proc. IEEE/ACM Design Automation Conference*, 2017, pp. 1-6.

### ABSTRACT OF THE THESIS

Processing in Memory using Emerging Memory Technologies

by

Saransh Gupta

#### Master of Science in Electrical and Computer Engineering (Electronic Circuits and Systems)

University of California San Diego, 2018

Professor Tajana Šimunić Rosing, Chair

Recent years have witnessed a rapid growth in the amount of generated data, owing to the emergence of Internet of Things (IoT). Processing such huge data on traditional computing systems is highly inefficient, mainly due to the limited cache capacity and memory bandwidth. Processing in-memory (PIM) is an emerging paradigm which tries to address this issue. It uses memories as computing units, hence reducing the data transfers between memory and processing cores. However, the application of present PIM techniques is restricted by their limited functionality and inability to process large amounts of data efficiently. In this thesis, we propose novel techniques which exploit the analog properties of emerging memory technologies. Not only do these support more complex functions such as addition, multiplication, and search but also manage and process large data more efficiently. We present a new blocked PIM architecture which uses inter-block interconnects to accelerate data intensive processing. We also introduce a heterogeneous architecture having general purpose cores and PIM-enabled memory and a data-dependent task allocation scheme for it. We apply application specific optimizations and approximation techniques to further design accelerators for neural networks and database query systems. While we design a multiplication-by-constant hardware for neural networks, query processing is accelerated by a novel in-memory nearest search technique. Our neural network accelerator achieves  $113.9 \times$  higher energy efficiency and  $56.3 \times$  speedup as compared to AMD GPU. The query accelerator provides  $49.3 \times$  performance speedup and  $32.9 \times$  energy savings as compared to recent Intel CPU.

## Chapter 1 Introduction

The Internet of Things is expected to have billions of connected devices that will generate huge amount of raw data. This data amounted to 16.1 zettabytes (ZB) in 2016 and is expected to increase  $10 \times$  till 2025 [1]. In recent years, the number of smart electronic devices has surpassed the number of humans in the world [2], as shown in Figure 1.1.

Several algorithms try to pre-process and compress big data [3]. These algorithms are traditionally run on conventional general purpose processors. However, conventional processing architectures have poor performance when processing big data. This inefficiency comes from large amount of data movement between the main memory and processing cores [4]. Figure 1.2 shows that DRAM read operation is the costliest operation in a system with a 32-bit read consuming  $170 \times$  more energy than a 32-bit floating point multiplication [5]. The limited on-chip

Figure 1.1. Increase in number of connected devices over the years.

**Figure 1.2.** The cost of various operations in a typical computer organization. Reading data from DRAM is the most energy consuming operation.

cache memories in traditional cores along with limited memory bandwidth of main memory, contribute to inefficiency. For example, running k-nearest neighbors algorithm (classification) requires calculating the distance of each data point with all existing points in the dataset [6]. To process 1 billion candidate points, one query needs 150 GFLOPs of computation and 500G of data communication [7]. This results in significant performance overhead when the data cannot fit in memory.

Near data computing (NDC) and processing in-memory (PIM) are two efficient techniques which aim to reduce the cost of data movement [8, 9, 10, 11, 12, 13]. NDC puts the computing units close to the main memory, in order to avoid data movement cost in computation [14]. On the other hand, PIM exploits the analog characteristics of emerging memory technologies to enable in-place computations. The goal of both these techniques is to perform computations on data near/where it is stored. Since they do not send the all data from memory all the way up to the processing cores, they can reduce the amount of data communication and the related high costs. These techniques have challenges of their own. While the application of NDC may be restricted by the difficult integration of memory and logic and the costs of large computing cores, PIM may be limited by the slow device latencies, low endurance, and limited computing capabilities. However, the emerging memory technologies have made it possible to overcome the challenges faced by PIM and present feasible PIM implementations [15, 16, 17, 18, 19, 20, 21]. Resistive RAM (ReRAM) is one such memory, which enjoys the benefit of low energy, high switching speeds, high density, and scalability. Many solutions have been proposed which utilize ReRAM to realize efficient PIM architectures [8, 10, 22]. Some have proposed general purpose PIM implementations with limited capabilities, while others propose application-specific PIM accelerators with more advanced functionality. For example, the work in [23] only supports NOR directly in crossbar memory, while [24, 25] implements implication in memory and [26] implements majority operation. All other functions are implemented by repeated multiple cycles of the base operation. There is no exploration about how these can be used at application level and the related design constraints. On the other hand, some works propose accelerators targeted towards specific applications like neural networks [10, 27], query processing [28], graph processing [29], etc which cannot be generalized for other applications.

The goal of this thesis is to take steps to bridge the gap between these two extremes, i.e. the limited functionality of general PIM techniques and application-specific processors. We first propose a new PIM architecture which accelerates processing of data intensive workloads. It makes multi-input in-memory additions and multiplications faster. We introduce configurable interconnects to reduce the latency of in-memory shift operations and exploit the inherent parallelism in PIM operations. We observe that in-memory acceleration of applications is suitable only when these applications are data intensive. This is due to the slower switching of memory cells as compared to conventional CMOS devices.Hence, we design a heterogeneous architecture which combines a PIM accelerator with a general purpose processor. It includes a data management unit which controls the allocation of data intensive tasks to PIM, while others are executed by the general purpose cores. This allocation prevents PIM operations from becoming a bottleneck for small applications. We also propose two application specific accelerators. The neural network accelerator uses PIM techniques along with operation level optimizations to improve the performance and efficiency of inference tasks. We design a new in-memory multiplication technique customized for inference task in neural networks. It achieves

$113.9 \times$  higher energy efficiency and  $56.3 \times$  speedup as compared to AMD GPU. We also design a PIM accelerator for database queries. It uses a novel search technique to enable nearest distance search in-memory. We combine it with traditional content addressable memory (CAM) and PIM functionality to execute a wide range of query operations in memory. The query accelerator provides  $49.3 \times$  performance speedup and  $32.9 \times$  energy savings as compared to recent Intel CPU.

The thesis is organized as follows. Chapter 2 presents a background on memristors and near/in-memory processing. Chapter 3 introduces a new PIM architecture for data intensive applications. Chapter 4 proposes a heterogeneous architecture and a data management scheme for such systems. Chapter 5 & 6 present accelerators for neural networks and database queries respectively. The thesis is then concluded in Chapter 7.

# Chapter 2 Background and Related Work

### 2.1 Memristive Memory

Recent years have witnessed the development of emerging non-volatile memory technologies, such as Conductive Bridging RAM (CBRAM), Resistive Random Access Memory (ReRAM or RRAM), Phase Change Memory (PCM), and Spin-Transfer Torque Magnetoresistive RAM (STT-RAM).Several industry leaders have demonstrated large capacity NVM products, including 16 Gb CBRAM [30], 32 Gb RRAM [31], 8 Gb PCM [32], 1 Gb STT-RAM [33], and 128 Gb 3D-Xpoint memory. These memories have been shown capable of both storing and processing data. This versatile nature of these technologies have increased interest in non von-Neumann architectures.

Memristive technologies are non-volatile and compatible with CMOS fabrication process [34]. Memristive devices are expected to have low switching energy and fast switching speed. The read and write times can be as fast as 120 *ps* [35, 36]. The switching energy is as low as 1 *pJ* [36]. The endurance limit of memristors is measured approximately as  $10^{10}$  allowed write operations per cell [37] (except STT-RAM, where  $10^{15}$  is achieved). This limit is likely to increase to  $10^{15}$  [38]. Memristive devices are fabricated between two metals, which act as the top and bottom electrodes of a dielectric material [39]. Hence, memristors can be fabricated in the metal layers as part of a standard CMOS Back End of Line (BEOL) process. Memristive memories generally utilize a crossbar structure, with  $4F^2$  density, where *F* is the feature size.

Figure 2.1. Working mechanism of memristor device when reading and writing.

Such a memory achieves significantly lower energy and higher scalability, while occupying negligible area unlike traditional memory technologies like SRAM and DRAM [40, 41]. Digital data is represented in terms of its resistance, where LRS (low resistance state,  $R_{ON}$ ) is logical '1' and HRS (high resistance state,  $R_{OFF}$ ) is logical '0.'

General structure of memristor is based on metal/oxide/metal. Two metal layers (e.g. Pt) sandwich an oxide layer which is based on Ta, Ti and Hf [40]. The metal/diode connection usually shows the Ohmic behavior (shown in Figure 2.1). The data is pre-stored based on the memristor resistance state. Figure 2.1 shows the functionality of the memristor device in low and high resistance states. The value is stored on a memristor device based on its hysteresis mechanism. By applying a large positive voltage across the device (>  $V_{t+}$ ), the device changes its state from an LRS state to HRS, which is called *reset*. When the device is in the HRS, by applying a large negative voltage (>  $|V_{t-}|$ ), it changes to the LRS. In order to read the memristor values, we apply a voltage that is less than a write threshold voltage across the device and sense the current passing through the device. In this way, we can identify the state of the device, without changing the memristor value [42].

## 2.2 Near-Data Computing

Near data computing (NDC) aims to address the issue of data movement by physically placing computing units closer to the memory chip [43, 44, 45, 46, 14, 47]. It leverages the high local data bandwidth to accelerate applications. These computing units may range from small ASICs, FPGAs all the way to GPUs and multi-core systems. These "cores" are put close to memory to minimize the overhead of data transfers. Several works have proposed adding cores at different levels in the memory hierarchy. While many researchers propose to add computing capability to commodity DRAMs [48, 49, 50, 51], some also use SSDs [52, 53] and other emerging memory technologies [54, 55, 56, 57] to enable NDC.

Recent advances in die-stacking technology have been exploited by researchers to reduce the cost of NDC, improving its practicality [58, 59]. Moreover, introduction of new memory architectures like High Bandwidth Memory (HBM) [60] and Hybrid Memory Cube (HMC) [61] have resulted in an increased interest in using 3D-DRAMs for NDC. The through-silicon-vias (TSVs) optimized for 3D architectures enable stacking of multiple DRAM dies on top of a CMOS logic layer, customized to the requirements of targeted applications. The high memory-level parallelism in memories like HMC provides better random access performance than traditional DRAM [62]. In addition, the logic layer in HMC also allows memory operations like readmodify-write, locking, etc., paving way for accelerating operations in memory [49, 51, 63].

## 2.3 Processing in-Memory

Processing in-memory (PIM) accelerates computation by reducing the overhead of data movement and providing high parallelism in some cases [64, 65].

### **2.3.1 SRAM PIM**

Some researches present PIM like techniques for SRAMs. The work in [66] proposes the concept of compute memory, where computation is deeply embedded into SRAM. It enables multi-row read access and analog signal processing. Based on this compute memory, the authors in [67] proposes energy-efficient and high throughput implementation of sparse distributed memory which is used as an associative processor. The work in [68] introduces a new content addressable memory (CAM) based on the conventional 6T SRAM cells. They design a configurable SRAM with both CAM and logic functions. Further, the design in [69] presents approaches to improve the performance and energy efficiency of this configurable SRAM, called compute cache. Such caches are able to execute only simple bitwise functions on the data stored in SRAM cells using sense amplifiers. The work in [70] accelerates machine learning by doing computations in SRAM cell. However, it uses large DACs to implement it, introducing significant power and area overhead.

### 2.3.2 DRAM PIM

The work in [71] exploits the concept of 3D stacking to separate the logic and memory circuits into different DRAM dies, overcoming the cost challenges involved in integrating memory and logic. There have been other proposals to enable computing capabilities inside DRAM [72, 73, 74, 75, 76]. DRAM is inherently destructive in read operations, that is, the stored bits are invalidated after read operations. Thus, the original data should be backed up to another cell before any computations, causing undesired overhead in PIM operations [74]. The work in [76, 73, 72] enable processing by modifying the sense amplifiers (SAs) as well as the 1-transistor-1-capacitor (1T1C) cell structures. These approaches result in additional area overhead to the conventional design. The In-Memory Intelligence (IMI) architecture proposed in [75] is a standard DRAM in form and function with the ability for massive SIMD parallelism and a standard and familiar programming model. It attaches simple bit-serial computing elements to DRAM array's sense amplifiers. These elements are based on standard DRAM structures, for example, slow, dense transistors, and a drastically limited number of metal layers.

### 2.3.3 NVM PIM

High density, low-power consumption, and CMOS-compatibility of emerging nonvolatile memories (NVMs), in particular memristor devices, make them appropriate candidates for both storage and computing purposes [54, 77, 78]. A class of PIM techniques in memristors utilize the inherent dot-product capability of the crossbar structure to implement logic [79, 80, 81, 82]. The architectures employing such techniques use various peripheral circuits to implement different functions. The other class of PIM techniques use the analog properties of memristive devices to realize logic in-memory. Many logic families have been proposed for computation inside memristive crossbar. Some of these logic implementations such as stateful implication logic [24, 25] and Memristor Aided loGIC (MAGIC) [23] are purely realized within memory. The work in [83] extends the bitwise operations in [23] to present schemes for addition in memristive crossbar memory. They also introduce PIM in transpose crossbar memory, allowing more flexibility in logic execution. On the other hand, Pinatubo [84] and MPIM [85] modified sensing circuits to implement fundamental bitwise operations, such as AND and OR. However, they can not support arithmetic operations, e.g. addition and multiplication, which are the key functions involved in many applications such as deep learning algorithms and image processing. The direct application of these schemes in data intensive applications such as DNNs is highly limited due to the linear dependency of execution latency on the size of the data. The work in [86] presents a very fast adder based on complementary resistive switches (CRS). However, CRS-based logic involves reading and sensing the intermediate data during execution, which makes execution dependent on inputs. Moreover, the area overhead involved in arrayed addition grows significantly for data intensive workloads.

Of the proposed memristor-based PIM techniques, MAGIC NOR [23] is the simplest to implement, with its execution being independent from data in memory. An execution voltage,  $V_0$ , is applied to the bitlines of the inputs (in case of NOR in a row) or wordlines of the outputs (in case of NOR in a column) in order to evaluate NOR, while the bitlines of the outputs (NOR in a row)

or wordlines of the inputs (NOR in a column) are grounded. The work in [83] extends this idea to implement adder in a crossbar. It executes a pattern of voltages in order to evaluate sum and carry bits of 1-bit full addition (inputs being A, B, C) given by,

$$C_{out} = ((A+B)' + (B+C)' + (C+A)')'.$$

(2.1a)

$$S = (((A' + B' + C')' + ((A + B + C)' + C_{out})')')'.$$

(2.1b)

Here, *S* and  $C_{out}$  have been related to the inputs (*A*, *B*, and *C*) in terms of NOR operations. Here,  $C_{out}$  is realized as a series of 4 NOR operations while *S* is obtained by 3 NOT operations (evaluation of A', B', and C') followed by 5 NOR operations. A NOT operation is implemented as a NOR operation with 1 input. From this point onwards, a NOR operation by default implies a MAGIC NOR operation. This design takes 12N + 1 cycles to add two *N*-bit numbers.

### **2.4 PIM Application Examples**

**Neural Networks (NNs):** Deep neural networks (NNs) demonstrate superior effectiveness for diverse classification problems, image processing, video segmentation, speech recognition, computer vision and gaming [87, 88, 89, 90]. Although many NN models are implemented on high-performance computing architectures, such as parallelizable GPGPUs, running neural networks on the general purpose processors is still slow, energy hungry, and prohibitively expensive. Attempts have been made to improve NNs' computation cost but the data movement between memory and processing cores remains the main bottleneck for NNs' energy consumption and execution time. Several recent research works reduce this bottleneck by in-memory acceleration.

The work in [91] presents an SRAM-embedded convolution architecture, which does not require reading the weights explicitly from the memory. They implement voltage averaging using ADCs and add local multiply-and-average circuits for computation. The authors in [92] accelerated on-chip training of always-on machine learning classifiers using analog computations in the periphery of the SRAM bitcell array. The CIM-SRAM in [93] presents a cost-aware solution for DNN AI edge processors which is designed by co-optimizing the previously proposed SRAM PIM circuits and the system.

The authors in [94] present a novel process-in-memory architecture to process emerging binary CNN tests in 3D DRAMs. It conducts XNORs inside DRAM arrays, transfers XNOR results by through-silicon-vias (TSVs), and completes popcounts on the logic die. The work in [95] introduces a programmable and scalable digital architecture platform for computing neuro-inspired algorithms. It integrates a parallel compute layer within 3D HMC.

The authors in [10, 27, 96, 97, 98] proposed PIM architectures for implementing NNs in ReRAM. They utilize the dot-product computation inherently supported by ReRAM crossbars to implement matrix vector multiplication in memory. These designs utilize multi-level memristor cells to store data and perform NN computations.

The work in [27] divided a ReRAM bank into three types of subarrays: memory (Mem), buffer, and full function (FF). Mem subarrays only store data whereas FF subarrays can either store data or perform NN computations. They reused write drivers and SAs, with some modifications, to perform the function of DAC and ADC, respectively. Although the sharing of periphery between computation and memory lowers the area overhead, yet the overhead is significantly high. The work in [98] extends the work in [27] to provide support for back-propagation and weight-update, while leveraging peripheral circuitry for inference operation. The sense amplifier implements ReLU and max functions and precision control apart from analog-to-digital conversion.

A ReRAM-based tiled architecture for accelerating NNs was presented in [97]. Each tile in [97] has an MCA-based PE (processing engine) array, an eDRAM buffer, a register buffer and multiple DACs. The input feature maps of CNN are stored in the eDRAM buffer, which is cached by the register buffer for different convolution steps. Every PE has also an ADC, some logic elements and SH units. While the ADC works similar to the other works, this work requires less number of DACs since it uses DACs in only one column, reducing the area and power overheads.

The CNN accelerator presented in [10] uses ReRAM dot-product computations for convolution and classifier layers. The system has multiple tiles each designed with ReRAM crossbars which store synaptic weights and computations on them. Since a crossbar cannot be efficiently reprogrammed at runtime, it assigns one crossbar for processing a group of neurons in any CNN layer. The strength of their design lies in pipelined architecture where different CNN layers are pipelined, reducing the buffering requirement and increasing the throughput.

The authors in [96] accelerated both training and testing of CNNs using ReRAM crossbar. They divide MCAs into two types: memory and morphable. The morphable MCAs perform both computation and data-storage and memory MCAs only store data. The design exploits both intra-layer and inter-layer parallelism. To exploit intra-layer parallelism, they map the kernels to multiple MCAs and, then, collect and add their outputs. The number of duplicate copies of MCAs storing the same weight presents a trade-off between hardware overhead and throughput. They also propose a pipelined training architecture where inputs inside a batch can be processed in pipelined manner. They eliminated the use of both DACs and ADCs by integrating the weighted spike-codes in a counter.

**Query Processing:** Data management systems (DMS) are the standard tools for collecting and serving large amounts of information for web applications and end users. Over the past decade, data generation has grown exponentially due the diversity of collection sources [99, 100, 101]. In addition, organizations collect large amounts of information for decision making and business analytics [102, 103, 104]. In the majority of scenarios, the execution time of DMS queries tends to increase linearly and sometimes exponentially as more records are stored in a single server instance. This has been one of the main challenges of DMS and its caused by the the hardware and software co-design limitations [105].

To increase the performance of query processing, the work in [28] presented a ReRAMbased PIM architecture for SQL queries. Their technique utilizes the dot-product computation scheme of ReRAM crossbar to process cells storing identical attribute in different tuples and different attributes in the same tuple. They mapped data to ReRAM such that a tuple is stored in a ReRAM row and attributes of a tuple are stored in columns of a row. Their technique supports three query operations: restriction (selecting rows that fulfill a criterion), projection (selecting specific columns in a row) and aggregation (summarizing specific properties of multiple columns in a group of rows, e.g., adding the values). The multiplication of attributes happens in CPU, for which data is transferred from memory to CPU. An analog comparator is used for comparison operations whereas to process the output by equality or Boolean functions, an ADC is used at row-output for converting the result to digital domain. In a projection operation, '1' is applied at the column to be read and the remaining columns are supplied with '0' signal. Only sum is supported in aggregation, which is implemented using column-wise dot-product computation.

The design proposed in [106] further proposed a query optimization method to make the optimizer fully utilize the performance of the PIM structure and generate an execution plan specific to the SQL query unit hybrid database system proposed in [28]. They propose some heuristic rules and a cost-based optimizer for such systems. The heuristic rules are based on the PIM characteristics of the RRAM-based SQL unit. These rules are required since the RRAM-based SQL unit supports a subset of typical operations of a database. Hence, the rules try to utilize the RRAM-based SQL unit whenever possible during query processing to reduce system cost. The cost-based optimizer helps the system determine if it should choose an index or PIM to implement a restriction operation.

**Graph Processing:** Graph processing plays an important role in data processing because most of data collected from the real world can be represented as graphs like social network [107], road network [108], and human brain [109]. Since the current trends suggest an explosive growth of data in near future [110, 111, 112, 113, 114], processing large graphs in an efficient way, therefore, has become significantly important.

Inspired by this, the work in [4] designed a new programmable accelerator for in-memory graph processing that can effectively utilize PIM using 3D-stacked DRAM and provided the programming interface for the same. They introduced novel communication mechanism and

hardware prefetchers to fully utilize the available memory bandwidth. The work in [63] proposes a PIM architecture for graph processing on Hybrid Memory Cube (HMC) array. They integrate SRAM-based on-chip vertex buffers to eliminate local bandwidth degradation. They also introduce reconfigurable double-mesh connection to provide high global bandwidth.

The work in [29] investigates the use of PIM based ReRAM crossbar for graph processing. GraphR [29] is a ReRAM based accelerator which processes graph applications using matrix multiplication capability of ReRAM crossbar memory. It treats ReRAM crossbar as a replacement for conventional processing unit and dynamically transfers data from the memory to a multi-level memory cell based crossbar to finish computations for sub-graphs. Furthermore, GraphR utilizes ReRAM for matrix-vector multiplication, using ADC and DAC devices for conversions at the memory periphery.

**Hyperdimensional Computing:** Although deep learning algorithms work well for many applications, they are facing scalability and power issues when running on todays computers. This motivate designing brain-inspired hyperdimensional (HD) computing algorithms which have significantly lower power consumption, while providing excellent accuracy. Brain-inspired HD computing explores this idea by looking at computing with ultra-wide words high-dimensional vectors, or hypervectors [115, 116, 117]. Hyperdimensional computing has been shown to support a wide range of applications. For example, the design proposed in [118] enables general speech recognition in high dimensional spaces and then combines them to generate a unique vector for each output class. The work in [119] introduces a language recognition algorithm working with high dimensional vectors. Similarly, [120] uses hyperdimensional computing for DNA sequencing. Researchers have proposed new architectures for hyperdimensional associative memory that can facilitate energy-efficient, fast, and scalable implementation of HD in-memory [121]. These analog HD designs use ReRAM based memory to store vectors and perform HD operations. These designs linearly scale with the number of dimensions in the hypervectors, while providing orders of magnitude higher efficiency.

## Chapter 3 PIM for Data Intensive Applications

A number of logic families have been proposed for computation inside memristive crossbar. They focus on logical and arithmetic operations between limited inputs and extend them linearly for large number of inputs. The direct application of these schemes in data intensive processing is limited largely due to the dependency of latency of execution on the size of data. In this thesis, we propose a configurable approximate processing in-memory architecture, called APIM, which supports addition and multiplication operations inside the non-volatile RRAM-based memory. APIM exploits the analog characteristic of the memristor devices to enable basic bitwise computation and then, extend it to fast and configurable addition and multiplication within memory. We propose a blocked crossbar memory which introduces flexibility in executing operations and facilitates shift operations in memory. Then, we introduce a novel approach for fast addition in memory. Finally, we design an in-memory multiplier using the proposed memory unit and fast adder. For each application, APIM can also dynamically tune the level of approximation in order to trade the accuracy of computation while improving energy and performance.

## 3.1 APIM Architecture

A typical crossbar memory is an array of unit memory cells. In case of RRAM, these cells are made of resistive switching elements such as memristors. Each cell in the memory is accessed by activating the corresponding wordline and bitline. MAGIC makes execution of operations in a crossbar memory simple. It also allows easy copying of data provided the source and destination are in the same column/row. While being acceptable in many cases, this memory structure limits the performance of instructions which involve a lot of shifting and asymmetric movement of data. One such instruction is multiplication where the multiplicand is shifted and added. Multiple copy operations can emulate a shift operation. However, such an approach is impractical when the number to be shifted is large since it requires shifting each and every bit individually. The problem is aggravated when multiple such numbers are to be shifted.

We hence propose the use of a blocked memory structure as shown in Figure 3.1(a). The crossbar is divided into blocks. Any new data which is loaded into the memory is stored in the data block. Whenever there is a request to process data, it is copied to the processing block and computation is done. The two blocks are structurally the same and can be used interchangeably. These blocks are connected by configurable interconnects. The interconnects support shift operations inherently such that  $i^{th}$  bitline of one block can be connected to  $(i + j)^{th}$  bitline of another block. The availability of interconnects allows the memory to shift data while copying it from one block to another without introducing any latency overhead. This makes shifting an efficient operation since the entire string of data can be shifted at once, unlike shifting each bit individually.

### **3.1.1 Fast Addition in APIM**

The design in [83] is good for small numbers but as the length of numbers increases, time taken increases linearly. A  $N \times M$  multiplication requires addition of M partial products, each of size N bits, to generate a (N+M)-bit product. This takes  $(M-1) \cdot (12(N-1)+1)$  cycles to obtain the final product.

In order to optimize latency of addition, we propose a fast adder for memristive memories. Our design is based on the idea of carry save addition (CSA) and adapts it for in-memory computation. Figure 3.2(a) shows carry save addition. Here, S1[n] and C1[n] are the sum and

**Figure 3.1.** (a) The overall structure of APIM consisting of several data and processing blocks, (b) APIM controller and parallel product generator, (c) Fast adder tree structure consisting of carry save adder and configurable interconnects. (d) Final product generator.

carry-out bits, respectively of 1-bit addition of A1[n], A2[n], and A3[n]. The 1-bit adders do not propagate the carry bit and generate two outputs. This makes the *n* additions independent of each other. The proposed adder exploits this property of CSA. Since, MAGIC execution scheme doesn't depend upon the operands of addition, multiple addition operations can execute in parallel if the inputs are mapped correctly. The design utilises the proposed memory unit, which supports shifting operations, to implement CSA like behaviour. The latency of this 3:2 reduction, 3 inputs to 2 outputs, is same as that of a 1-bit addition (*i.e.*, 13 cycles) irrespective of the size of operands. The two numbers can then be added serially, consuming 12N + 1 cycles. This totals to 12N + 14cycles while the previous adder would take 24N - 22 cycles. The difference increases linearly with the size of inputs.

We use a Wallace-tree inspired structure leveraging the fast 3:2 reduction of our new adder design, as shown in Figure 3.2(b), to add multiple numbers (9 *n*-bit numbers in this case). At every stage of execution, the available addends are divided in groups of three. The addends are then added using a separate adder (as described above) for each group, generating two outputs per group. The additions in the same stage of execution are independent and can occur in parallel

Figure 3.2. (a) Carry save addition (b) Tree structured addition of 9 n-bit numbers

to each other. Our configurable interconnect arranges the outputs of this stage in groups of three for addition in the next stage. This structure takes a total of four stages for 9:2 reduction, having the same delay as that of four 1-bit additions. At the end of the tree structure we are left with two (N+3)-bit numbers which can then be added serially. The tree-structured addition reduces the delay substantially as carry propagation happens only in the last stage, unlike the conventional approach where carry is propagated at every step of addition. Although this speed up comes at the cost of increased energy consumption and number of writes in memory, it is acceptable because the latency is reduced by large margins as shown in Section 3.3.

### **3.1.2** Multiplication in APIM

The process of multiplication can be divided into three stages, partial product generation, fast addition, and final product generation as shown in Figure 3.1. The partial product generation stage creates partial products of a  $N \times N$  multiplication. These partial products can then be added serially (inefficient) or by the fast adder introduced in Section 3.1.1. The fast addition reduces N numbers to 2. The final product generation stage adds two numbers generated by the previous stage and outputs the product of  $N \times N$  multiplication.

A partial product is the result of ANDing the multiplicand  $(M_1)$  with a bit of the multiplier

$(M_2)$ . Hence,  $N \times N$  multiplication generates N (size of  $M_2$ ) partial products of size N-bits (size of  $M_1$ ). AND operation can be implemented as a series of three NOR operations as given by,

$$F = AND (A, B) = NOR (NOR(A), NOR(B))$$

(3.1)

This requires three cycles given that the inputs A & B and output F are in the same row or column. In the case of in-memory computation, even if we assume that the numbers to be multiplied are located adjacent to each other, we would require an empty crossbar row/column of length  $N^N$  which is quite large even for N = 16. This would be expensive not only in terms of area but also in latency, requiring  $3N^N$  cycles.

We propose the use of sense amplifiers to develop a faster partial product generator as shown in Figure 3.1(b). In order to avoid the time and area overhead involved in transposing and creating multiple copies of multiplier, we read-out the multiplier. The design exploits the fact that the partial product is the multiplicand itself if multiplier bit is '1' and 0 otherwise.  $M_2$  is read bit-wise using the sense amplifier. If the read bit is '1',  $M_1$  is copied, while nothing is done when the bit is '0'. We achieve this by modifying the multiplexer in the controller, incorporating the sensed bit in the select signals. In this way, we avoid writing data when the bit is zero, thus saving energy. A copy operation is equivalent to two successive *NOT* operations. This result is used for all successive copy operations, limiting the worst case delay of copying to N + 1 cycles. The actual delay would vary depending upon the number of '1s' in  $M_2$ .

Although this is a huge improvement in latency from the initial design, we have not yet considered the cost of shifting the partial products for add operation. Shift operation in a normal memory crossbar can only be done bitwise, which would be quite large given the number and size of operands to be shifted. The blocked memory architecture introduced in Section 3.1 proves advantageous in this scenario. If the above operations are performed in a blocked memory crossbar, the latency of shifting would actually reduce to zero. Shift operation can be clubbed with copy operation and hence, shifted partial products can be obtained in the processing block

at no extra delay.

The fast adder discussed in Section 3.1.1 reduces the generated partial products to 2, owing to its N:2 reduction. Since a step in the fast adder involves parallel additions, it requires that the three addends of a 3 : 2 adder are present in the same columns (rows) and all such groups in a step are present in the same rows (columns). Interestingly, arranging the partial products in this manner involves no added latency as this arrangement can be done while shifting and copying the data in the partial product generation stage. Instead of writing the partial products one below the other, the interconnects are set such that the partial products are arranged in the required way. After the first step of 3 : 2 reduction, we again need to arrange the intermediate results into groups of three. This can be done by moving these results to the data block, performing the next 3 : 2 reduction there (blocks being functionally the same), and coming back to the current block for the following reduction. In this way, N : 2 reduction can be efficiently executed by utilizing only 2 blocks of the memory, toggling between them at every step. However, if the data block is specifically reserved for storing data and bars logic execution, a 3-level memory (with 2 processing blocks per data block) can be used. The reduction is done until only 2 addends remain.

The major advantage of reduction addition is that the time taken by this adder is independent of the size of the operands *i.e.*,  $N \times 32$  multiplication takes the same time in this stage for any value of N. It varies only by the number of operands to be added. Moreover, since we only generate a partial product when the multiplier bits are 1, the actual number of operands to be added is quite small. For instance, with a random input data, there would be only 16 additions on average for  $32 \times 32$  multiplication. The final product generation stage adds the two outputs of the previous stage to generate the required product.

Figure 3.3(a) shows the configurable interconnect used in our design. It can be visualized as a collection of switches, similar to a barrel shifter, which connects the bitlines of the two blocks.  $b_n$  and  $b'_n$  are bitlines coming into and going out of the interconnect respectively. The select signals,  $s_n$  control the amount of shift. These interconnects can connect cells with different

Figure 3.3. The circuit of (a) an interconnect (b) a sense amplifier.

bitlines together. For example, they can connect  $b_n, b_{n+1}, b_{n+2}, ...$  incoming bitlines to, say,  $b'_{n+4}, b'_{n+5}, b'_{n+6}, ...$  outgoing bitlines, respectively, hence enabling the flow of current between the cells on different bitlines of blocks. This kind of a structure makes shifting operations energy efficient and fast, having the latency same as that of a normal copy operation. It also allows for inter-column MAGIC NOR operations between the two blocks. If inputs are stored on  $n^{th}$  bitline of one block, the output of NOR operation can be stored on, say,  $(n+4)^{th}$  bitline of another block. This can be extended to multiple NOR operations in parallel. The shift select signals,  $s_n$ , are controlled by the memory controller present at the periphery of memory unit. It is important to note that all of these blocks still share the same row and column controllers and decoders. So, the area and logic overhead introduced by the proposed memory unit is restricted to the interconnect circuit and its control logic.

## **3.2 APIM Approximation**

The individual additions in the final stage cannot occur in parallel since they require the propagation of carry in order to generate the final answer. The two addends in the final stage of APIM multiplication are of size 2N each. The conventional approach requires  $13 \cdot 2N$  cycles to compute the result. This latency is dominant as compared to the previous stages of multiplication, making the last stage a bottleneck of the entire process.

However, we can dramatically speed it up if a fully accurate result is not desired. This is the case with many highly data intensive applications which tolerate some inaccuracy as long as it is within the prescribed limits. One approach is to mask some of the LSBs of  $M_2$ , reducing the number of computations. The other approach approximates the sum bits in the last stage from the accurately generated carry bits and saves the delay involved in calculation of the bit. We use the second approach in the evaluation of our design.

In the first approach, the number of masked bits depends upon the amount of accuracy desired. Masking the bits of the multiplier effectively reduces the number of partial products to be added because we don't generate partial products when the multiplier bit is 0. For example, masking 8 LSBs of  $M_2$  in the first stage reduces a  $32 \times 32$  multiplication to  $32 \times 24$ . Hence, this method of approximation results in a direct reduction in delay and energy consumption of multiplication. It comes majorly due to the reduction in computation in the fast adder stage. However, since this approach masks the bits in the initial stage itself, the error propagates through the entire process, resulting in huge errors in some cases. This makes it unsuitable for an application demanding very high accuracy.

In the second approach, our design exploits the fact that the sum bit (*S*) of an 1-bit addition is the complement of the generated carry bit ( $C_{out}$ ) except for two combinations of inputs (*i.e.*,(A, B, C) = (0, 0, 0) and (1, 1, 1)) [122]. It evaluates  $C_{out}$  accurately (hence, preventing the propagation of error) and then approximates *S*. Our design uses a modified sense amplifier (SA). It supports basic memory operation along with MAJ (majority) function as shown in

Figure 3.4. Error and EDP comparison of the two approximation approaches.

Figure 3.3(b). The carry generated ( $C_{out}$ ) as a result of addition of three input bits ( $A, B, C_{in}$ ) is MAJ(A, B, C) *i.e.*, AB + BC + CA. Our circuit level evaluation shows that just reading the inputs from memory takes about 0.3*ns*, while our design needs 0.6*ns* to calculate majority and compute  $C_{out}$  resulting in an effective delay of less than 1 cycle. One additional cycle is needed to write the computed  $C_{out}$  to the memory. It acts as an input to the next 1-bit addition, the output of SA is written such that it is in the same column as that of the next two inputs, saving the trouble and cost of copying it. Since the carry bit is propagated, these 1-bit additions cannot occur in parallel to each other. The computation of  $C_{out}$  takes  $2 \cdot 2N$  cycles. All *S* bits can then be approximated by just inverting the  $C_{out}$  bits, which costs only 1 cycle and can all be done at the same time. This technique reduces the latency from  $13 \cdot 2N$  (time taken to add two 2*N*-bit numbers) cycles to  $2 \cdot 2N + 1$  cycles. This improvement comes with a significant cost of 25% error (2 out of 8 cases) for a random input data.

The accuracy can be improved substantially by approximating just a part of the final product while accurately calculating the rest of the product. The design improves accuracy by dividing the product into two groups of size k and m bits such that k + m = 2N. The k bits are calculated using the conventional approach which consumes 13k cycles and produces k accurate bits in the product. On the other hand, m bits are approximated using the technique described above, which takes a total of 2m + 1 cycles. This increases the accuracy since the k accurate bits

are generally the most significant bits and any error in the *m* least significant bits has less effect on the result, as shown in Section 3.3.3. The proposed technique implements the final stage with a latency of 13k + 2m + 1 cycles. The appropriate values of *k* and *m* depend upon the application in hand. Section 3.3.3 talks about different applications and selecting these values in order to obtain acceptable results.

While approximation in the last stage reduces the latency, it is still slower that the first approach in which approximation is done in the first stage. The first approach is more energy efficient too since it reduces the size of multiplication and uses less resources. However, unlike the first approach, second approach introduces error only in the final stage of the process. This approach can thus achieve very low error rates making it suitable for applications requiring precise results. Figure 3.4 presents a comparison between the two approaches for  $32 \times 32$  multiplication. While, approximation in the first stage is convenient for error tolerant applications, approximation in the last stage can guarantee very high accuracies for similar EDPs. For example, for  $32 \times 32$  multiplication and an EDP of  $1.4 \times 10^{-16}$ , the error rate for the second approach is less by 5 orders of magnitude as compared to the first approach.

# 3.3 Results

#### **3.3.1** Experimental Setup

We compare the efficiency of the proposed APIM design with state-of-the-art processor AMD Radeon R9 390 GPU with 8GB memory. In order to avoid the disk communication in the comparison, all the data used in the experiments is preloaded into 64GB, 2.1GHz DDR4 DIMMs. We used Hioki 3334 power meter to measure the power consumption of GPU. We implement the APIM functionality by changing the multi2sim [123], cycle-accurate CPU-GPU processor. Performance and energy consumption of proposed hardware are obtained from circuit level simulations for a 45nm CMOS process technology using Cadence Virtuoso. We use VTEAM memristor model [124] for our memory design simulation with  $R_{ON}$  and  $R_{OFF}$  of 10k $\Omega$  and

**Figure 3.5.** Performance comparison of the proposed design with previous work for addition of N operands, each sized N bits

$10M\Omega$  respectively.

We compare the efficiency of APIM and GPU by running six general OpenCL applications including: *Sobel, Robert, Fast Fourier transform (FFT), DwHaar1D, Sharpen* and *Quasi Random.* For image processing we use random images from *Caltech 101* [125] library, while for non-image processing applications inputs are generated randomly. Majority of these applications consists of additions and multiplications. The other common operations such as square root has been approximated by these two functions in OpenCL code. To evaluate the computation accuracy in approximate mode, our framework compares the approximate output file of each application with the golden output from calculating exactly. For image processing applications, we accept 30*dB* peak signal-to-noise ratio as an accuracy metric. For other applications, the acceptable accuracy is defined by having less than 10% average relative error. To find a proper level of accuracy, our framework computes APIM at the maximum level of approximation (32 relax bits). In case of large inaccuracy, it increases the level of accuracy in 4-bit steps until ensuring the acceptable quality of service.

#### **3.3.2 APIM** vs state-of-the-art

Figure 3.5 compares the performance efficiency of the proposed design with the stateof-the-art prior work [83, 86]. The work in [83] computes addition in-memory using MAGIC

**Table 3.1.** Quality of loss and EDP improvement of the proposed APIM compared to GPU in different level of approximation.

| Applications | 0 bit        |     | 4 bits   |      | 8 bits   |      | 16 bits  |      | 24 bits  |       | 32 bits      |       |

|--------------|--------------|-----|----------|------|----------|------|----------|------|----------|-------|--------------|-------|

|              | EDP Imp.     | QoL | EDP Imp. | QoL  | EDP Imp. | QoL  | EDP Imp. | QoL  | EDP Imp. | QoL   | EDP Imp.     | QoL   |

| Sobel        | 94×          | 0%  | 164×     | 1.3% | 235×     | 3.1% | 305×     | 6.9% | 376×     | 11.4% | 446×         | 15.6% |

| Robert       | 177×         | 0%  | 311×     | 1.2% | 444×     | 2.9% | 577×     | 4.8% | 711×     | 6.8%  | $844 \times$ | 9.1%  |

| FFT          | $203 \times$ | 0%  | 356×     | 2.2% | 509×     | 3.7% | 662×     | 5.8% | 815×     | 8.6%  | 968×         | 13.5% |

| DwHaar1D     | $90 \times$  | 0%  | 157×     | 0.9% | 225×     | 2.6% | 293×     | 5.7% | 361×     | 7.9%  | $428 \times$ | 10.6% |

| Sharpen      | $104 \times$ | 0%  | 149×     | 3.4% | 206×     | 5.1% | 273×     | 8.1% | 340×     | 12.5% | $410 \times$ | 18.4% |

| QuasiR       | $69 \times$  | 0%  | 127×     | 2.1% | 198×     | 3.5% | 258×     | 5.8% | 310×     | 9.3%  | 386×         | 15.7% |

logic family, while the work in [86] uses the complementary resistive switching to perform addition inside the crossbar memory. Our evaluation comparing the energy and performance of addition of N operands of length N bits each shows that the APIM can achieve at least  $2\times$  speed up compared to previous designs in exact mode. APIM can be at least  $6\times$  faster with 99.9% accuracy. The proposed design is even better since the calculations for previous work do not include the latency involved in shift operations. This improvement comes at the expense of the overhead of interconnect circuitry and its control logic. However, the next best adder, *i.e.*, the PC-Adder [86] uses multiple arrays each having different wordline and bitline controllers, introducing a lot of area overhead. This overhead is not present in our design since all the blocks share the same controllers.

#### **3.3.3** Approximate APIM

Table 3.1 shows the energy consumption and performance of the applications running on APIM in different approximation level. As we explained in Section 3.2, APIM approximates m least significant bits of the product in the final product generation stage. The value of m has an important impact on the computation accuracy and performance of multiplication in APIM design. As Table 3.1 shows, large number of approximate LSBs (m) significantly improve energy-delay product of APIM, at the expense of increased computation inaccuracy. Similarly, small m makes the computation more accurate with small benefit. We observed that different applications satisfy the required accuracy for different values of m. Therefore, our design detects the application at runtime and then sets the pre-calculated value of m that is obtained offline to ensure the acceptable quality of computation. Using this adaptive design, our design can achieve

**Figure 3.6.** Energy consumption and speedup of exact APIM normalized to GPU vs different dataset sizes.

$480 \times$  energy-delay product improvement as compared to APIM in the exact mode.

## 3.3.4 APIM & Dataset Size