# UC Irvine UC Irvine Electronic Theses and Dissertations

### Title

Tackling the Effects of Elevated Temperature and Aging Phenomena in 3D Integrated Circuits

Permalink https://escholarship.org/uc/item/95x5m06f

Author Alqahtani, Ayed Saad A

**Publication Date** 2019

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

# Tackling the Effects of Elevated Temperature and Aging Phenomena in 3D Integrated Circuits

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Ayed Saad A Alqahtani

Dissertation Committee: Professor Nader Bagherzadeh, Chair Professor Rainer Dömer Professor Alexander Veidenbaum

$\begin{array}{c} {\rm Chapter \ 2 \ \bigodot \ 2018 \ ACM} \\ {\rm All \ other \ materials \ \bigodot \ 2019 \ Ayed \ Saad \ A \ Alqahtani} \end{array}$

### DEDICATION

This dissertation is dedicated to:  $my \ family$ for their love and support

> وَمَنْ يَتَهَيَّب صُعُودَ الحِبَـالِ يَعِشْ أَبَدَ الدَهرِ بَيْنَ الحُفَر

"Those who do not like climbing the mountains will live forever among the hollows", from "The will of life" poem, by Abi Alqasim Alshabbi (1909-1934).

A person who is afraid of trying, will not be able to achieve any success throughout his life. If you are afraid to climb mountains, you will not be able to get out of your holes. One who wants to survive and get up from these holes should not be afraid. One who wants to advance must learn that climbing mountains is the way to success.

# TABLE OF CONTENTS

|               |                                  |                                                                                                                                                                                                                                                       | Page                                                |

|---------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| $\mathbf{LI}$ | ST C                             | OF FIGURES                                                                                                                                                                                                                                            | $\mathbf{vi}$                                       |

| LI            | ST C                             | OF TABLES                                                                                                                                                                                                                                             | ix                                                  |

| $\mathbf{LI}$ | ST C                             | OF ALGORITHMS                                                                                                                                                                                                                                         | $\mathbf{x}$                                        |

| A             | CKN                              | OWLEDGMENTS                                                                                                                                                                                                                                           | xi                                                  |

| C             | URR                              | ICULUM VITAE                                                                                                                                                                                                                                          | xii                                                 |

| A]            | BSTI                             | RACT OF THE DISSERTATION                                                                                                                                                                                                                              | xiv                                                 |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3 | oductionElevated Temperature and Aging Phenomena in 3D ICs and NoCs1.1.1Elevated Temperature Challenge in 3D ICs1.1.2Delay Degradation Problem in NoCsDissertation Objectives and ContributionsDissertation Organization                              | <b>1</b><br>2<br>4<br>5<br>9                        |

| 2             | Syst<br>2.1<br>2.2<br>2.3        | tem Level Analysis of 3D Integrated Circuits with Thermal TSVsIntroductionRelated Work2.2.1Thermal TSV Placement in 3D ICs.Composition of Thermal Models of 3D ICs2.3.1Through Silicon Vias (TSVs)2.3.2BEOL Wiring layers2.3.3Die-to-Die (D2D) Layers | <b>12</b><br>13<br>16<br>17<br>20<br>20<br>21<br>22 |

|               | 2.4                              | <ul> <li>Hotspot Validation and Thermal Analysis on a Case Study Processor- ev6</li> <li>Floorplan of 2D and 3D ev6</li> <li>HotSpot Tool Validation Using Ansys and the Thermal Analysis</li> </ul>                                                  | $22 \\ 22 \\ 23 \\ 25$                              |

|               | 2.5                              | Problem Formulation and Our Framework                                                                                                                                                                                                                 | $25 \\ 26 \\ 28$                                    |

|               | 2.6                              | Results and Discussion                                                                                                                                                                                                                                | 29<br>30                                            |

|          |     | 2.6.2  | Simulation, result and discussion of 2D and 3D Nehalem                | 31 |

|----------|-----|--------|-----------------------------------------------------------------------|----|

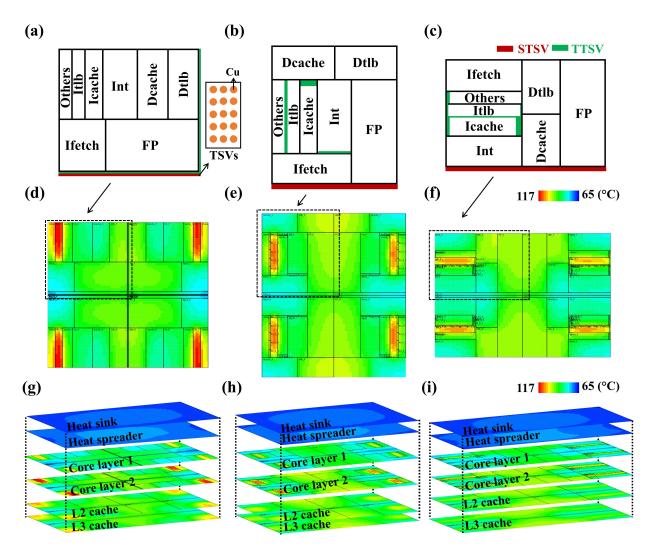

|          |     | 2.6.3  | Thermal management of 3D Nehalem processor using TTSVs                | 34 |

|          | 2.7 | Conclu | asion                                                                 | 38 |

| 3        | The |        | <b>TSV</b> Optimization and Hierarchical Floorplanning                | 39 |

|          | 3.1 |        | uction                                                                | 40 |

|          | 3.2 | System | n-Level Simulation and Power Consumption of the 3D Nehalem $\ldots$ . | 43 |

|          |     | 3.2.1  | System-Level Simulation Using gem5                                    | 43 |

|          |     | 3.2.2  | Power Consumption Estimation Using McPAT                              | 43 |

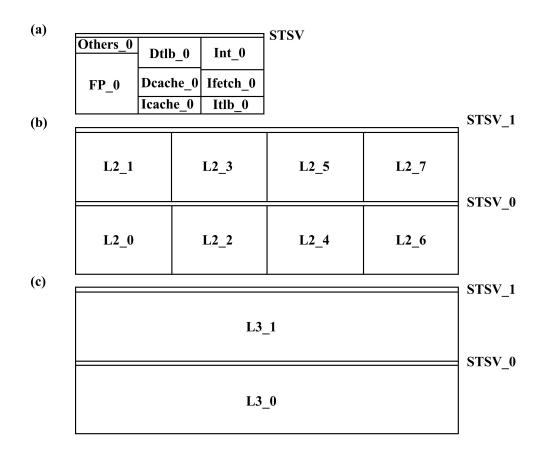

|          |     | 3.2.3  | The Architecture of the 3D Nehalem                                    | 44 |

|          |     | 3.2.4  | The Floorplan of 3D Nehalem                                           | 44 |

|          | 3.3 | Therm  | hal Characterization and Modeling of 3d Nehalem and Tsvs              | 45 |

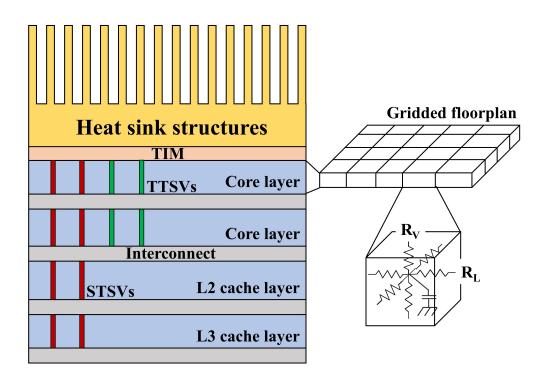

|          |     | 3.3.1  | Thermal Modeling of the 3D Nehalem                                    | 45 |

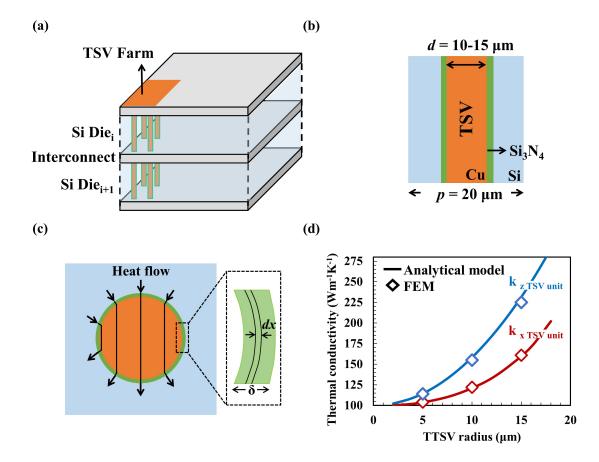

|          |     | 3.3.2  | Analytical Models of TSV Unit Cell                                    | 47 |

|          | 3.4 | TTSV   | Placement Optimization and Hierarchical Floorplanning Method          | 49 |

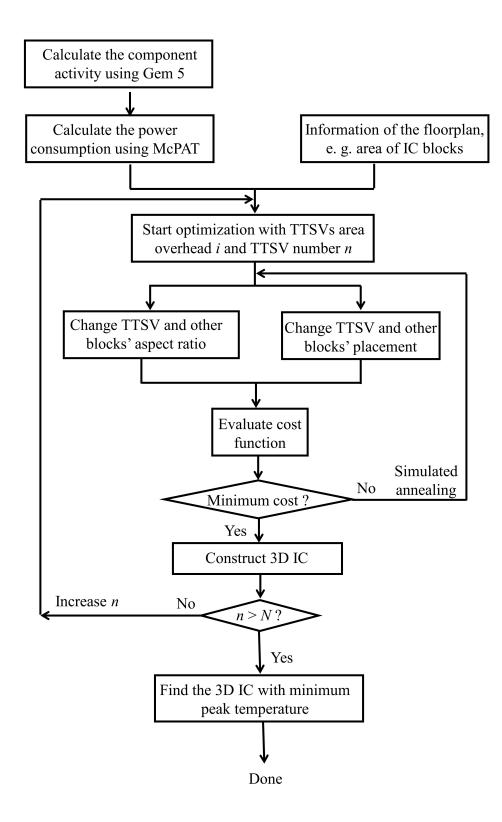

|          |     | 3.4.1  | Optimization Flow                                                     | 49 |

|          |     | 3.4.2  | Problem Formulation for Floorplan Optimization                        | 52 |

|          |     | 3.4.3  | Simulated Annealing Based Optimization Algorithm                      | 54 |

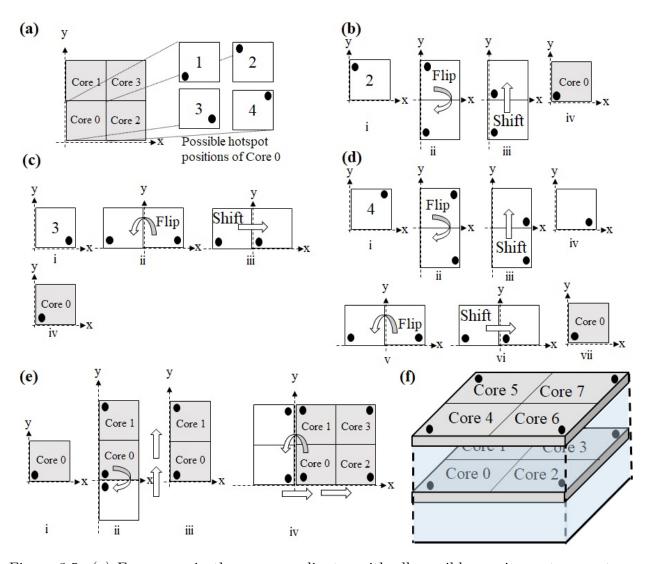

|          |     | 3.4.4  | Hierarchical Floorplanning of the 3D Nehalem                          | 55 |

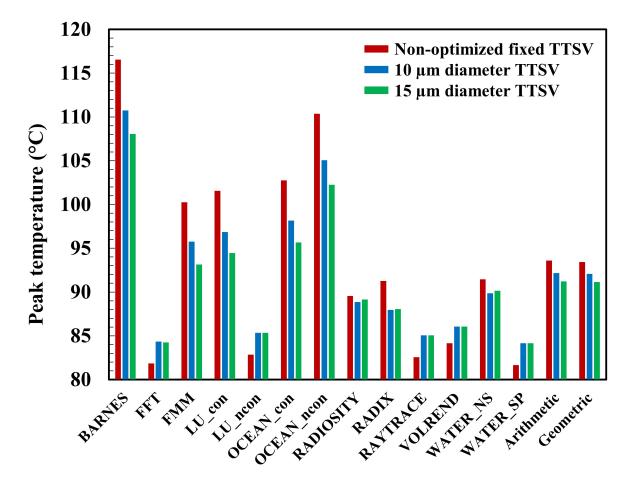

|          | 3.5 | Result | s and Discussion                                                      | 58 |

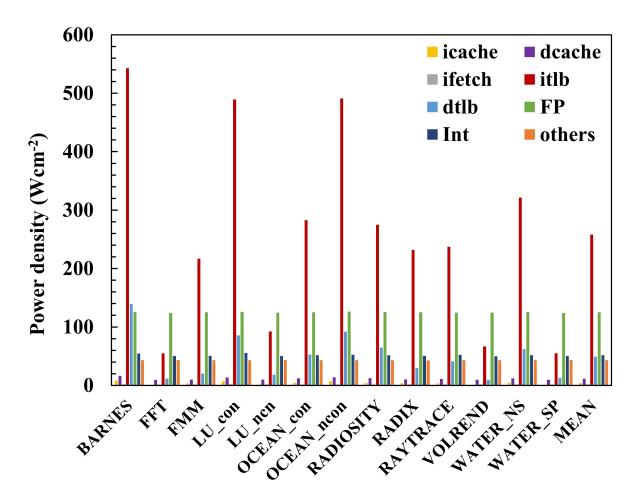

|          |     | 3.5.1  | Power Density of the 3D Nehalem Running Splash-2 Benchmarks           | 59 |

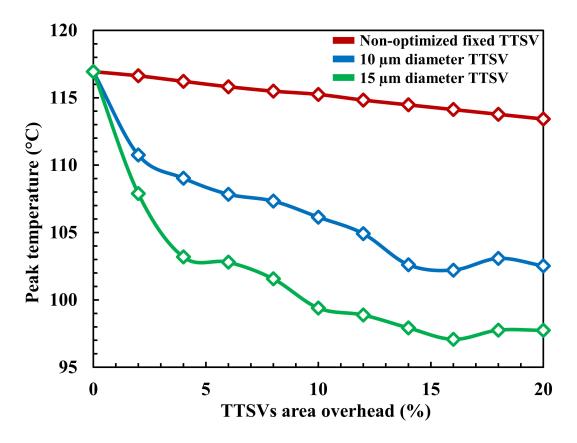

|          |     | 3.5.2  | Impacts of TTSVs on the Core Layer Peak Temperature of the 3D         |    |

|          |     |        | Nehalem                                                               | 59 |

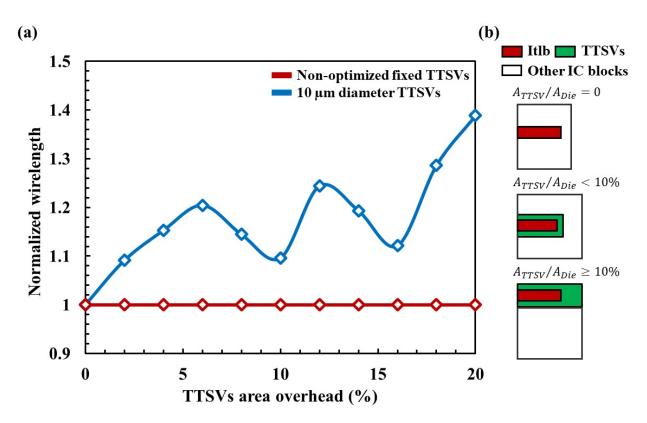

|          |     | 3.5.3  | Impacts of TTSVs on Area and Wirelength of 3D Nehalem                 | 64 |

|          | 3.6 | Conclu | sions                                                                 | 67 |

| 4        | Onl | ine Mo | onitoring and Adaptive Routing for Aging Mitigation in NoCs           | 69 |

|          | 4.1 | Introd | uction                                                                | 70 |

|          | 4.2 | Relate | d Work                                                                | 72 |

|          | 4.3 | Aging  | in NoC                                                                | 73 |

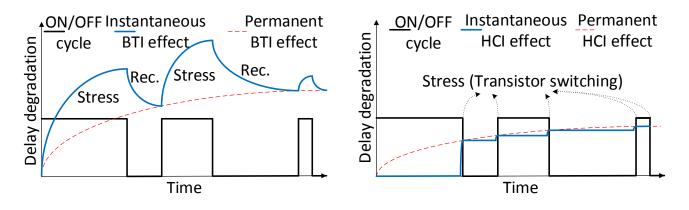

|          |     |        | BTI Aging Effect                                                      | 74 |

|          |     | 4.3.2  | HCI Aging Effect                                                      | 74 |

|          | 4.4 |        | e Aging Monitoring in NoC                                             | 75 |

|          | 4.5 | Aging- | Aware Routing Algorithm                                               | 79 |

|          | 4.6 | Experi | imental Setup and Results                                             | 81 |

|          |     | 4.6.1  | Setup                                                                 | 81 |

|          |     | 4.6.2  | Results                                                               | 82 |

|          |     | 4.6.3  | Overhead analysis                                                     | 83 |

|          | 4.7 | Conclu | usion                                                                 | 87 |

| <b>5</b> | Agi | ng-Aw  | are Deadlock-Free Adaptive Routing in 3D NoCs                         | 88 |

|          | 5.1 | Introd | uction                                                                | 89 |

|          | 5.2 | Relate | d work                                                                | 94 |

|          |     | 5.2.1  | Congestion aware adaptive routings                                    | 95 |

|          |     | 5.2.2  | Fault tolerant adaptive routings                                      | 96 |

|    |       | 5.2.3  | Aging-aware adaptive routings and motivation                 | 97  |

|----|-------|--------|--------------------------------------------------------------|-----|

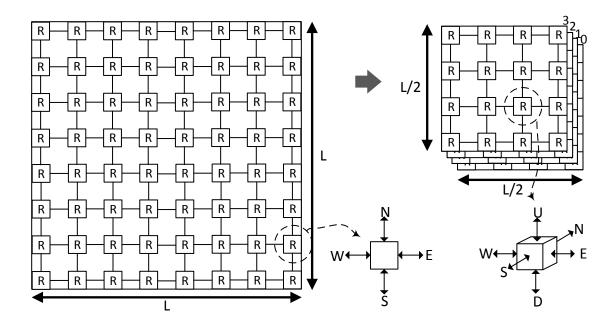

|    | 5.3   | 3D No  | C Background                                                 | 99  |

|    | 5.4   | Aging- | -induced Delay Degradation Background                        | 100 |

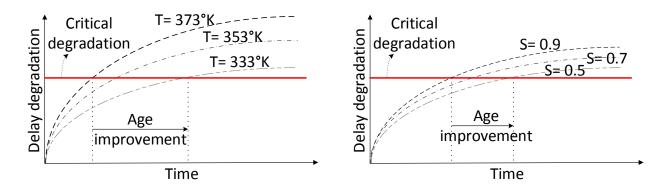

|    |       | 5.4.1  | BTI aging impact                                             | 101 |

|    |       | 5.4.2  | HCI aging impact                                             | 103 |

|    |       | 5.4.3  | Joint impact of BTI and HCI                                  | 103 |

|    | 5.5   | Proble | m Formulation                                                | 106 |

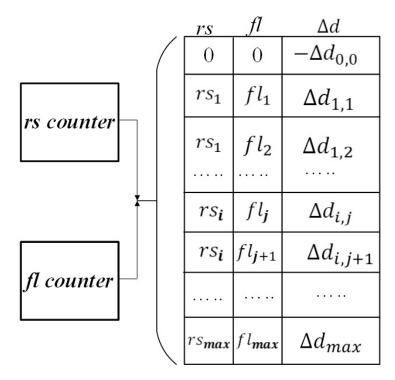

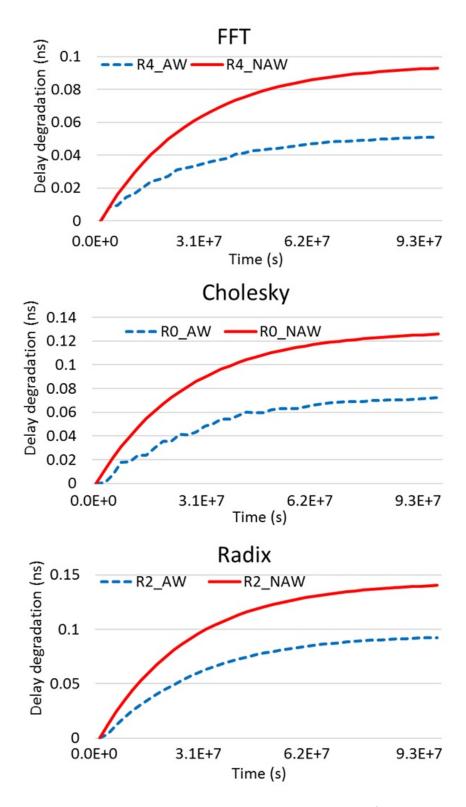

|    | 5.6   | Online | e Aging Monitoring in 3D NoC                                 | 107 |

|    |       | 5.6.1  | D-CAT construction algorithm                                 | 114 |

|    | 5.7   | Adapt  | ive Aging-aware Routing                                      |     |

|    |       | 5.7.1  | Adaptive aging-aware routing algorithm in AROMa              | 117 |

|    | 5.8   | Experi | imental Evaluation                                           | 125 |

|    |       | 5.8.1  | Setup                                                        | 126 |

|    |       | 5.8.2  | Results                                                      | 129 |

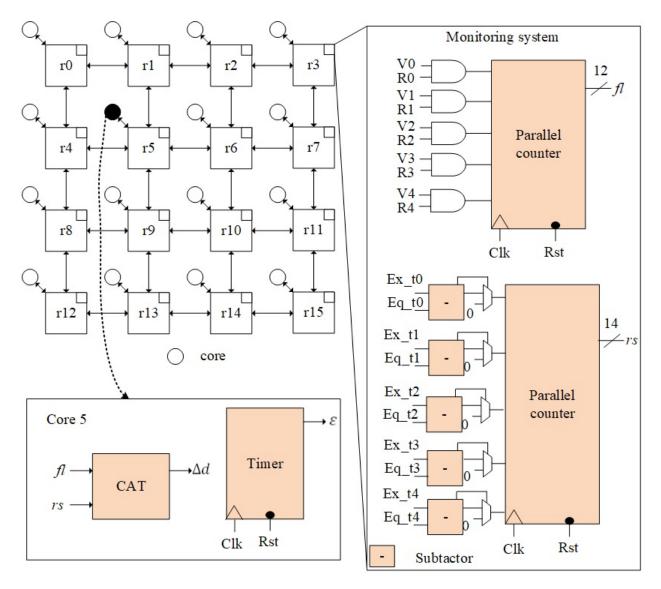

|    |       | 5.8.3  | Analysis and Discussions                                     | 135 |

|    |       | 5.8.4  | Overhead                                                     | 138 |

|    | 5.9   | Conclu | nsion                                                        | 143 |

| 6  | Con   | clusio | n and Future Work                                            | 144 |

|    | 6.1   | Conclu | ısion Remarks                                                | 144 |

|    | 6.2   | Future | e Directions                                                 | 146 |

|    |       | 6.2.1  | Machine Learning method for THermal Aware Floorplanning (ML- |     |

|    |       |        | THAF)                                                        | 146 |

|    |       | 6.2.2  | Utilizing PID Controller                                     | 148 |

|    |       | 6.2.3  | AROMA Improvement                                            |     |

| Bi | bliog | raphy  |                                                              | 150 |

# Bibliography

# LIST OF FIGURES

### Page

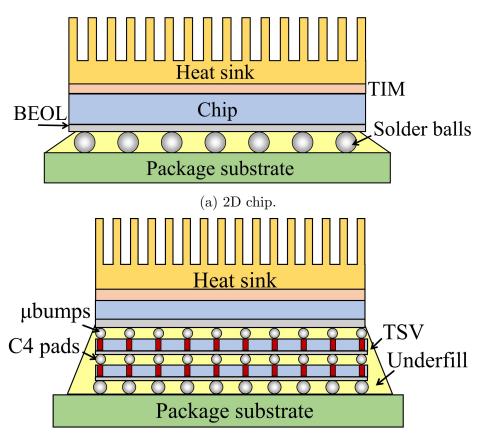

| 2.1  | Schematic diagram of liquid-less chip package                                   | 15 |

|------|---------------------------------------------------------------------------------|----|

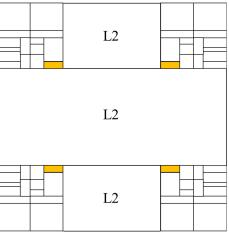

| 2.2  | Flooorplan of ev6. The hot spot block IntRegs, STSVs and TTSVs are high-        |    |

|      | lighted in yellow, red and green, respectively                                  | 24 |

| 2.3  | The temperature profile of ev6 running $gcc.$                                   | 26 |

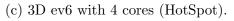

| 2.4  | Simulation flow of gem5                                                         | 27 |

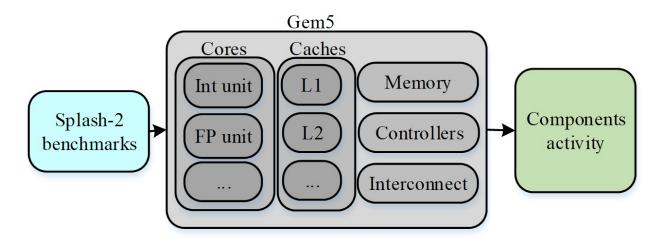

| 2.5  | Framework of our simulation, from gem5 to HotSpot                               | 28 |

| 2.6  | Nehalem floorplan in 2D and 3D cases                                            | 30 |

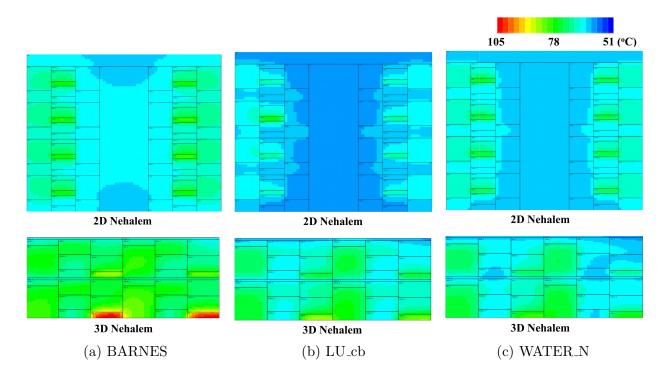

| 2.7  | Temperature profiles of 2D and 3D Nehalem running applications                  | 32 |

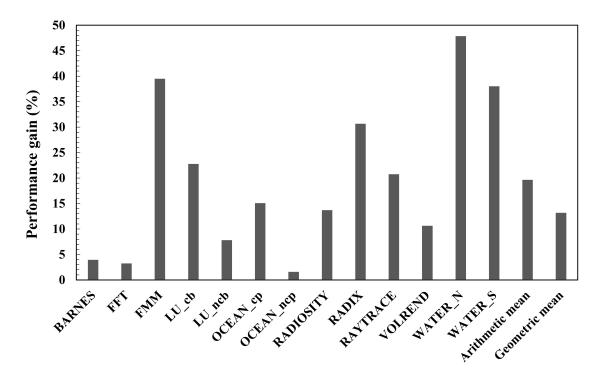

| 2.8  | Performance of 3D Nehalem                                                       | 33 |

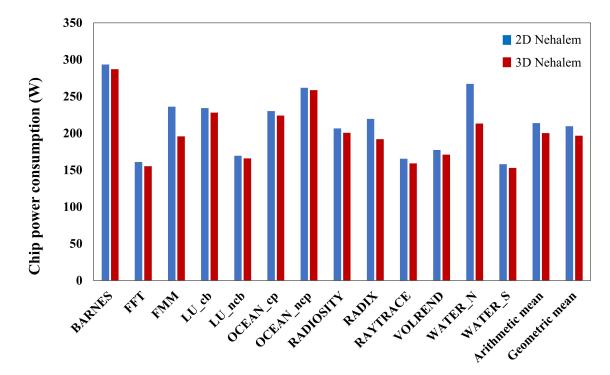

| 2.9  | Power consumption of 2D and 3D Nehalem.                                         | 34 |

| 2.10 | Floorplan of 3D Nehalem with TTSVs, the <i>itlb</i> block, STSVs, and TTSVs are |    |

|      | highlighted in yellow, red and green, respectively                              | 35 |

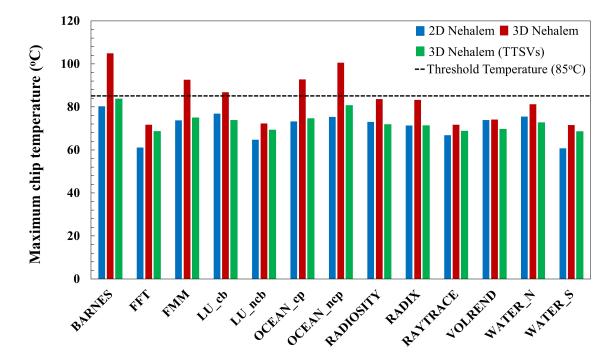

| 2.11 | Maximum chip temperature of 2D Nehalem, 3D Nehalem and 3D Nehalem               |    |

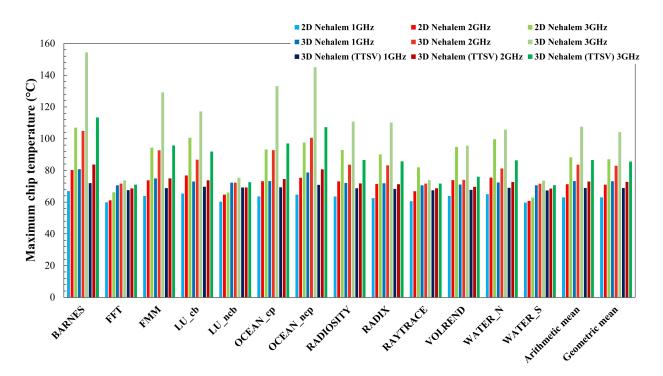

|      | with TTSVs                                                                      | 36 |

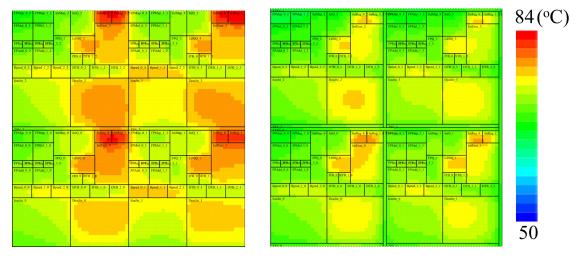

| 2.12 | Temperature profiles of 3D Nehalem without/with TTSVs running BARNES            |    |

|      | benchmark. The BEOL layer and D2D layer are hidden for clarity                  | 36 |

| 2.13 | The maximum chip temperature of 2D Nehalem, 3D Nehalem and 3D Nehalem           |    |

|      | with TTSVs running Splash-2 benchmarks with 1 GHz, 2 GHz, and 3 GHz             |    |

|      | frequencies.                                                                    | 37 |

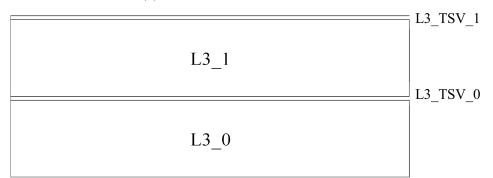

| 3.1  | 3D Nehlaem floorplan discription.                                               | 46 |

| 3.2  | Package model of 3D Nehalem.                                                    | 47 |

| 3.3  | Scematic of TSV and TSV farm with its lateral and vertical thermal conduc-      |    |

|      | tivity                                                                          | 50 |

| 3.4  | The floorplan optimization flow for 3D Nehalem                                  | 51 |

| 3.5  | Generating 3D Nehalem core layers.                                              | 58 |

| 3.6  | The power densities for Splash-2 benchmarks for all the IC blocks in one core   |    |

|      | of the 3D Nehalem.                                                              | 60 |

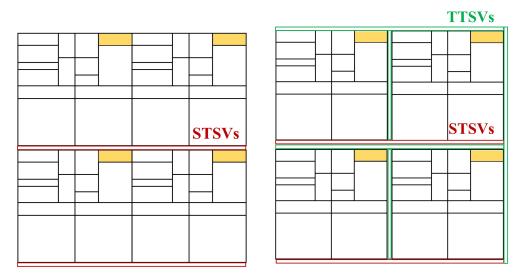

| 3.7  | Single core floorplans of non-optimized, optimized TTSVs arrangement for        |    |

|      | 3D Nehalem along with the most heated core layer and the entire 3D structure.   | 62 |

| 3.8  | Peak temperature change for the 3D Nehalem with/without the TTSV place-         |    |

|      | ment optimization.                                                              | 63 |

| 3.9  | Peak temperatures for the 3D Nehalem with/without the TTSVs placement           |    |

|      | optimization running Splash-2 benchmark.                                        | 64 |

| 3.10                                                                  | The normalized wirelength change with different TTSV area overheads                                                                                                                                                                          | 66                                        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$ | Age imbalance of different routers in FFT $\dots \dots \dots$                                                                                | 72<br>76<br>77<br>78<br>85<br>86          |

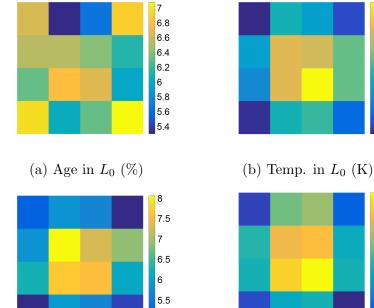

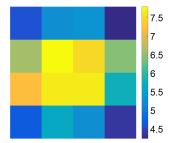

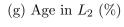

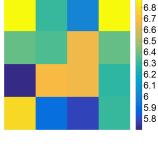

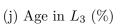

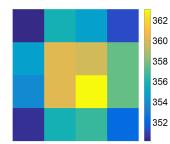

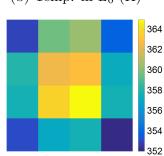

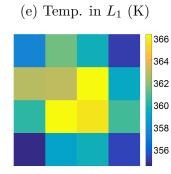

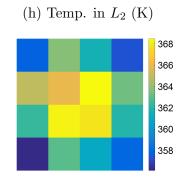

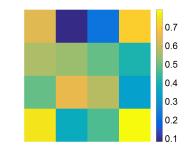

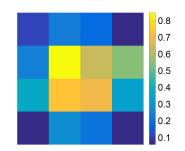

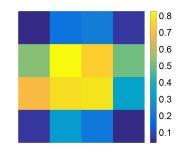

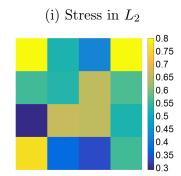

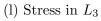

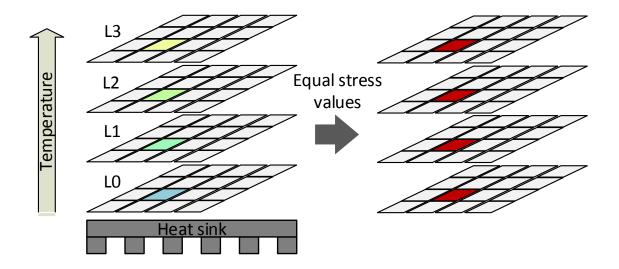

| 5.1                                                                   | Age, temperature (Temp.) and stress maps in each layer $L_i$ of 3D NoC (4 $\times$                                                                                                                                                           |                                           |

| 5.2                                                                   | $4 \times 4$ ) for uniform random distribution                                                                                                                                                                                               | 91<br>98                                  |

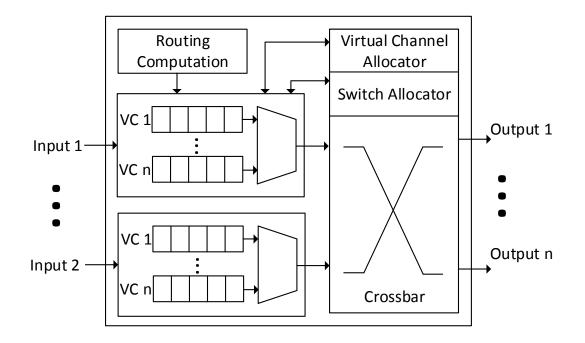

| $5.3 \\ 5.4$                                                          | Router components and architecture                                                                                                                                                                                                           | $\begin{array}{c} 100 \\ 102 \end{array}$ |

| $5.4 \\ 5.5 \\ 5.6$                                                   | Temperature and stress impacts on delay degradation.                                                                                                                                                                                         | 102                                       |

| 5.7                                                                   | utive time periods                                                                                                                                                                                                                           | 105                                       |

| 0                                                                     | different temperatures                                                                                                                                                                                                                       | 108                                       |

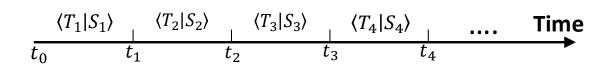

| 5.8                                                                   | Age monitoring at each period of $P$ at each layer $L_i$                                                                                                                                                                                     | 110                                       |

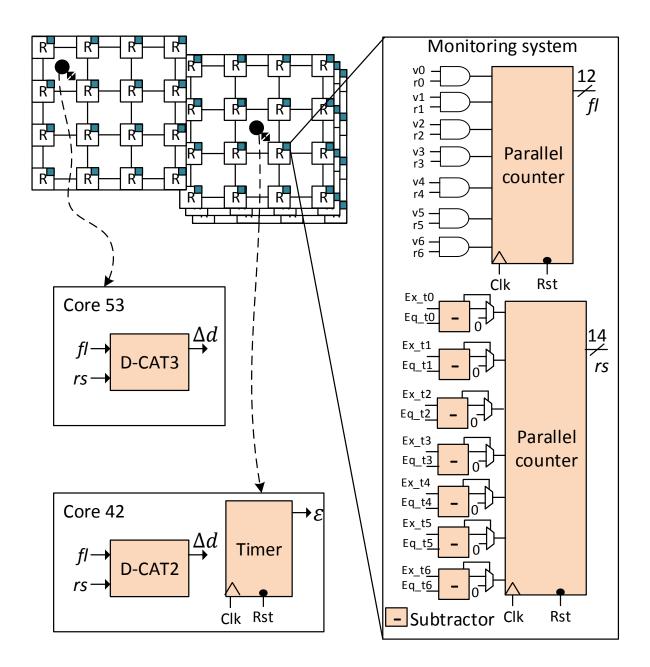

| 5.9                                                                   | AROMa online aging monitoring architecture. Other cores (black circles) and                                                                                                                                                                  |                                           |

| F 10                                                                  | two D-CATs are not shown for clarity)                                                                                                                                                                                                        | 112                                       |

| 5.10                                                                  | D-CATs for layer $L_0$ and layer $L_k$                                                                                                                                                                                                       | 113                                       |

|                                                                       | Swapping between different shortest paths that have different routers' ages<br>Updating routers' routing tables' entries for the new shortest path from S to D considering high aging in routers number 48 and 52. Routing table is detailed | 115                                       |

|                                                                       | for router number 47                                                                                                                                                                                                                         | 116                                       |

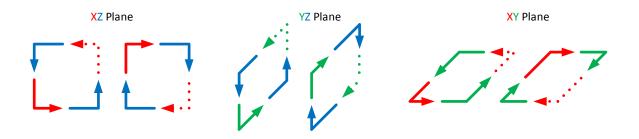

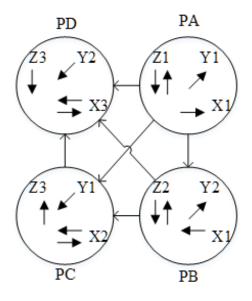

|                                                                       | The possible abstract cycles in different planes of 3D NoCs                                                                                                                                                                                  | 119                                       |

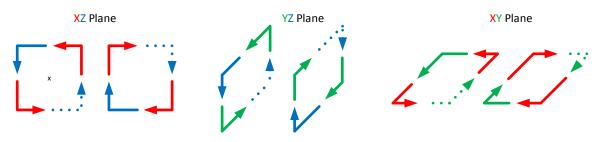

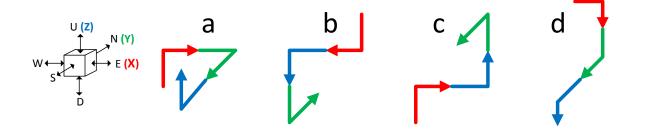

| 5.14                                                                  | Four various combinations of allowed turns (solid lines) to have deadlock-free                                                                                                                                                               | 100                                       |

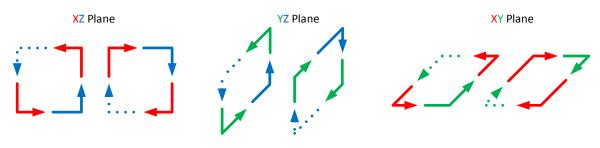

| 5 15                                                                  | algorithms in 3D NoCs                                                                                                                                                                                                                        | 120                                       |

| 0.10                                                                  | of the deadlock-free turn models (a, b, c, and d) in Section 5.7.1                                                                                                                                                                           | 122                                       |

| 5.16                                                                  | EbDa allowable transitions for 3D NoC based on the derivation from table 5.1                                                                                                                                                                 |                                           |

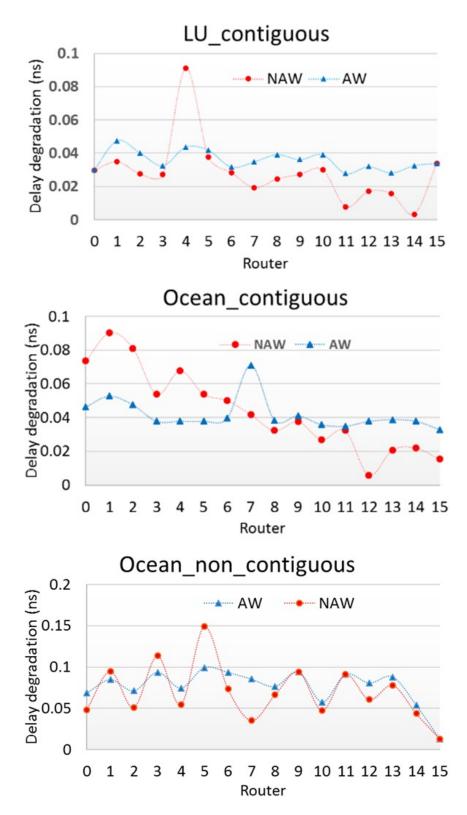

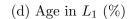

|                                                                       | Age imbalance in 3 years for different routers in the network                                                                                                                                                                                | 132                                       |

|                                                                       | Age imbalance in 3 years for different routers in the network (continued)                                                                                                                                                                    | 133                                       |

| 5.19                                                                  | Age imbalance between different routers in X264.                                                                                                                                                                                             | 134                                       |

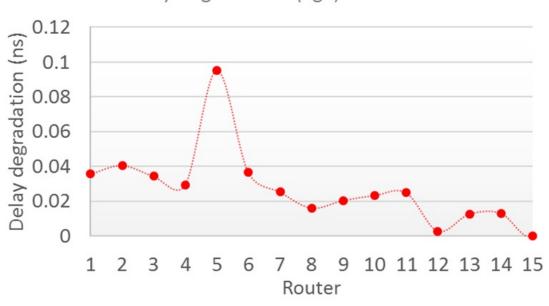

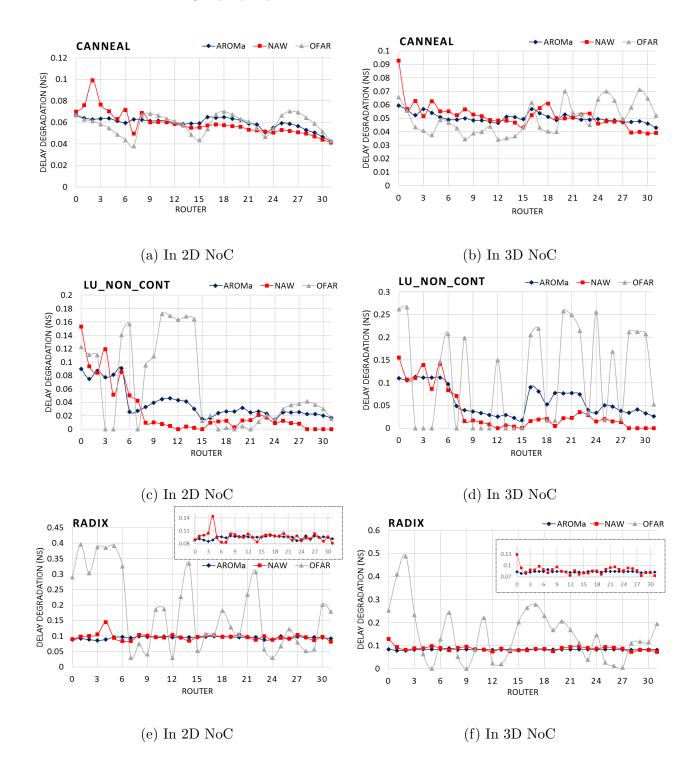

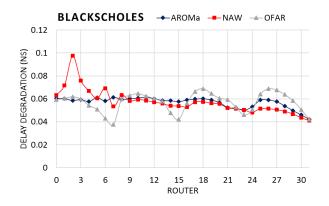

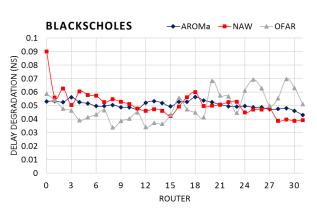

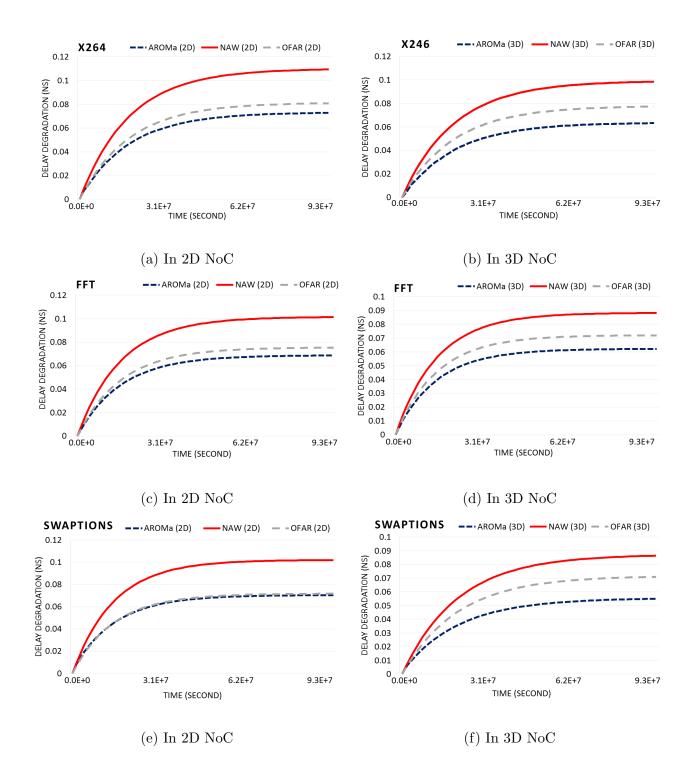

| 5.20                                                                  | Delay degradation for 3 years (9.3E+7 seconds) for maximum aged routers in                                                                                                                                                                   |                                           |

|                                                                       | the network                                                                                                                                                                                                                                  | 137                                       |

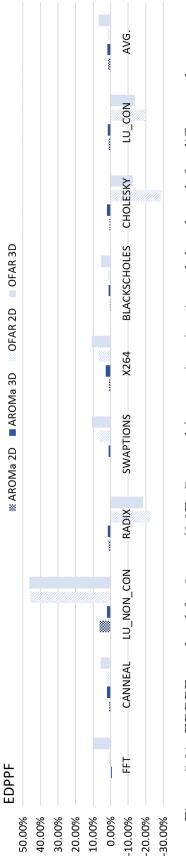

| 5.21                                                                  | EDPPF overhead for 3-year (9.3E+7 seconds) execution time in each bench-                                                                                                                                                                     |                                           |

| - 00                                                                  | mark for different schemes                                                                                                                                                                                                                   | 139                                       |

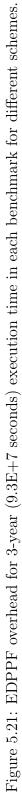

|                                                                       | Latency in different injection rates. $\dots \dots \dots$                                                                                    | 141                                       |

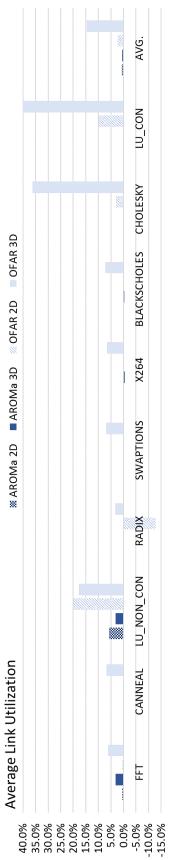

| 5.23                                                                  | Link utilization overhead for 3-year (9.3E+7 seconds) execution time in each benchmark for different schemes.                                                                                                                                | 142                                       |

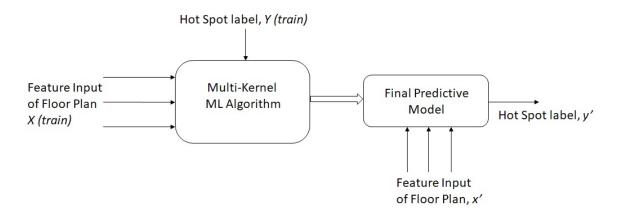

| 6.1                                                                   | ML-THAF predictive model                                                                                                                                                                                                                     | 147                                       |

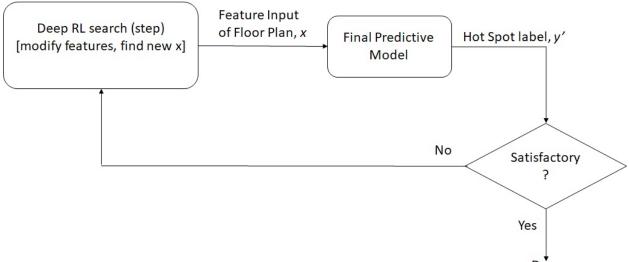

| 6.2 | ML-THAF deep reinforcement learning | 148 |

|-----|-------------------------------------|-----|

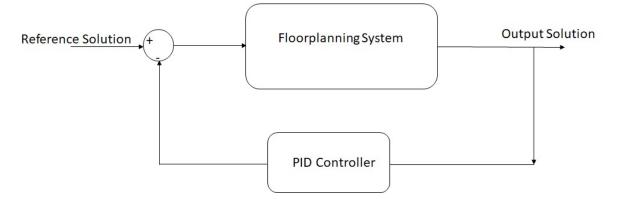

| 6.3 | Control system with PID controller  | 148 |

# LIST OF TABLES

### Page

| $2.1 \\ 2.2 \\ 2.3$ | System level core simulators                                                                                                                                                                                                     | 19<br>22<br>31                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 3.1<br>3.2<br>3.3   | x86 Nehalem-based processor parameter                                                                                                                                                                                            | 44<br>47<br>55                        |

| 3.4<br>3.5          | The maximum, minimum, and average temperature of splash-2 benchmarks for the second layer of 3D Nehalem in ( $^{\circ}C$ )                                                                                                       | $\begin{array}{c} 65\\ 67\end{array}$ |

| $4.1 \\ 4.2$        | Simulation setup $\ldots$ Aging degradation for maximum aged router, average, and its imbalance ( $\Delta$ )                                                                                                                     | 82                                    |

| 4.3                 | in NoC                                                                                                                                                                                                                           | 84<br>84                              |

| $5.1 \\ 5.2$        | Generating partitions using EbDa                                                                                                                                                                                                 | 124                                   |

| 5.3                 | freedom using EbDa                                                                                                                                                                                                               | 126<br>127                            |

| 5.4<br>5.5          | Aging-induced delay degradation for maximum aged router and network age<br>imbalance ( $\Delta$ ) in 2D NoC for 3 years of execution (9.3E+7 seconds)<br>Aging-induced delay degradation for maximum aged router and network age | 128                                   |

| 0.0                 | imbalance ( $\Delta$ ) in 3D NoC for 3 years of execution (9.3E+7 seconds)                                                                                                                                                       | 130                                   |

# LIST OF ALGORITHMS

|   |                                                                    | Page  |

|---|--------------------------------------------------------------------|-------|

| 1 | <i>Optimal_flp</i> : SA-based floorplan optimization algorithm     | . 56  |

| 2 | Create_3D_structure: hierarchical floorplanning for the 3D Nehalem | . 57  |

| 3 | CAT construction                                                   | . 79  |

| 4 | Aging aware routing algorithm                                      | . 80  |

| 5 | D-CAT construction                                                 | . 113 |

| 6 | Aging aware adaptive routing algorithm                             | . 117 |

# ACKNOWLEDGMENTS

I am extremely grateful to God Almighty who bestowed upon me the understanding, perseverance and critical thinking to make this accomplishment possible.

I would like to express my appreciation and thanks to my dissertation chairman and adviser, Professor Nader Bagherzadeh, for his incessant guidance through out dissertation completion process. He has been available whenever I needed his assistance. I really appreciate his help in developing ideas as well as his positive comments for improving and bringing out the utmost optimum consequences out of my endeavors. Without his guidance and support, I would have never been able to organize and complete the dissertation tasks as optimal and within time constraints.

I would like to extend my deep appreciation to *King Saud University* (KSU) and the *Saudi Arabian Cultural Mission* (SACM) for their support, funds, and assistance. Also, I would like to express my thanks and appreciation to the dissertation committee members Professor Rainer Dömer and Professor Alexander Veidenbaum for their creative comments and guidance through out the dissertation completion.

In addition, I express my greatest regards to my friends and colleagues for their support throughout my stay at UCI. They have been a steady source for help and encouragement.

Last but not least, I am highly indebted to all my family members for their love and patience. Without their support I would have never been able to finish the dissertation.

Ayed

April 2019

## CURRICULUM VITAE

### Ayed Saad A Alqahtani

#### EDUCATION

| <b>Doctor of Philosophy in Electrical and Computer Engineering</b> | <b>2019</b>           |

|--------------------------------------------------------------------|-----------------------|

| Univercity of California, Irvine (UCI)                             | Irvine, California    |

| Master of Science in Computer & Information Sciences               | <b>2010</b>           |

| King Fahad University for Petroleum & Minerals (KFUPM)             | Dhahran, Saudi Arabia |

| Bachelor of Science in Computer & Information Sciences             | <b>2007</b>           |

| King Saud University (KSU)                                         | Riyadh, Saudi Arabia  |

#### WORK EXPERIENCE

Consultant Al-ELM Information Security Company

**R&D Engineer** Advanced Electronic Company (AEC)

Smart Card Developer Al-ELM Information Security Company

**Testing Engineer** Advanced Electronic Company (AEC)

#### TEACHING EXPERIENCE

Lecturer VLSI Design and Testing,

Control Systems, Computer Networks, Computer Security King Saud University (KSU) **Teaching Assistant** VLSI Design and Testing,

Control Systems King Saud University (KSU)

#### **REFEREED JOURNAL PUBLICATIONS**

Sep 2006–Jan 2008 Riyadh, Saudi Arabia

Jun 2007–Oct 2007 Riyadh, Saudi Arabia

Jun 2006–Sep 2006 Riyadh, Saudi Arabia

Summer 2005 Riyadh, Saudi Arabia

#### 2010 - 2014

Riyadh, Saudi Arabia 2006–2010

Riyadh, Saudi Arabia

| System Level Analysis of 3D ICs with Thermal TSVs<br>ACM Journal on Emerging Technologies in Computing (JETC)                                                                 | 2018        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| AROMa: Aging-Aware Deadlock-Free Adaptive Rout-<br>ing Algorithm and Online Monitoring in 3D NoCs<br>IEEE Transactions on Parallel & Distributed Systems (TPDS)               | 2017        |

| A Finite State Machine Based Fault Tolerance Tech-<br>nique for Sequential Circuits<br>Microelectronics Reliability                                                           | 2013        |

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                              |             |

| Thermal Analysis of 3D ICs with TSVs Using System<br>Level Simulations<br>Semiconductor Research Corporation (SRC) TECHCON 2018                                               | 2018        |

| Online monitoring and adaptive routing for aging miti-<br>gation in NoCs<br>Design, Automation & Test in Europe Conference & Exhibition (DATE)                                | 2017        |

| Serial vs. parallel elliptic curve crypto processor designs<br>IADIS International Conference: Applied Computing                                                              | 2013        |

| <b>Triple-A: Secure RGB Image Steganography Based on</b><br><b>Randomization</b><br>The 7th ACS/IEEE International Conference on Computer Systems and Application<br>(AICCSA) | <b>2009</b> |

| Asymptotic Behavior of Networked Control System<br>(NCS)<br>18th National Computer Conference (NCC18)                                                                         | 2007        |

### ABSTRACT OF THE DISSERTATION

# Tackling the Effects of Elevated Temperature and Aging Phenomena in 3D Integrated Circuits

By

Ayed Saad A Alqahtani

Doctor of Philosophy in Electrical and Computer Engineering University of California, Irvine, 2019

Professor Nader Bagherzadeh, Chair

With technology advancement to the nanoscale level, 3D stacking of *Integrated Circuits* (ICs) provides significant advantages in saving device footprints, improving power management, and continuing performance enhancement which aim to increase energy efficiency and scalability particularly for many-core and NoCs systems. However, the benefits of these systems can be jeopardized because they became more subjected to elevated temperature induced by thermal management challenges as well as delay degradation (i.e. aging) caused by load imbalance.

On one hand, the elevated temperature in 3D systems can be solved by *Thermal Through Silicon Vias* (TTSVs). However, past research has either overestimated or underestimated the effects of TTSVs as a consequence of the lack of detailed 3D IC models or system-level simulations. In this dissertation, we propose a simulation flow to accurately simulate TTSV effects on 3D ICs. Furthermore, we present a hierarchical approach to optimize the floorplan of a 3D Nehalem-based multicore processor via *Simulated Annealing* (SA) with respect to the area, temperature, and wirelength. By using detailed 3D thermal model along with full system and validated thermal simulators, our results show accurate thermal analysis of 3D ICs. In addition, we found that the peak temperature of 3D IC such as 3D Nehalem is reduced with a minimal area overhead.

On the other hand, previous mitigation techniques to reduce aging phenomena effects on NoC system either ignore the runtime operating conditions or impose significant overheads to the system. Hence, this dissertation also presents an online monitoring method through a *Centralized Aging Table* (CAT) for routers in NoCs. Our methodology populates CAT by values that represent aging degradation for each different pairs of stress and temperature ranges during a given period of time. Moreover, utilizing CAT, we propose an online adaptive aging-aware routing algorithm in order to avoid highly aged routers in 2D NoC which eventually leads to age and load balancing between routers. We also extend this idea to 3D NoC by proposing AROMa, which is an aging-aware deadlock-free adaptive routing algorithm integrated with a novel online aging monitoring system for 3D NoCs. The monitoring system in AROMa exploits *Distributed-Centralized-Aqing-Table* (D-CAT) to obtain routers' aging rates for each layer of 3D NoCs. Consequently, AROMa swaps between different k-best source-destination shortest paths periodically to avoid highly aged routers, force them in the recovery phase, and accordingly balance aging in the network. Our results demonstrate that our online routing algorithm and monitoring methodology improves delay degradation of maximum aged router and aging imbalance while ensuring that the impact of our proposed methodology on network latency, *Energy-Delay-Product* (EDP) and link utilization is negligible.

**Keywords:** Multicore, Manycore, 3D ICs, Thermal Issues, Thermal Management, Through Silicon Via (TSV), Thermal Through Silicon Via (TTSV), Floorplanning, Network on Chips (NoCs), 3D NoCs, Aging, Delay Degradation; Online Monitoring; Adaptive Routing, Deadlock Freedom.

# Chapter 1

# Introduction

In this chapter, we describe the importance of overcoming the effects of elevated temperature and aging phenomena in 3D Integrated Circuits (ICs), and briefly characterize delay degradation and Thermal Through Silicon Vias (TTSVs) in 3D stacked structures. Methodologies and techniques to reduce the issues associated with stacking integrated circuits especially temperature and delay degradation(i.e. aging) is emphasized as the topic of research for this dissertation. We specify the problem to be solved and list the dissertation objectives in the following subsections, the details of which is going to be demonstrated in their respective chapters. Before discussing several aspects related to the dissertation topic, we give an overview of the previous work in this field. In the following chapters, the background material are reinstated whenever relevant to the subject. Finally, we summarize the organization of this dissertation.

# 1.1 Elevated Temperature and Aging Phenomena in 3D ICs and NoCs

With technology advancement to the nanoscale level, 3D stacking of integrated circuits (ICs) provides significant advantages in saving device footprints, improving power management, and continuing performance enhancement which aim to increase energy efficiency and scalability particularly for many-core and NoCs systems [24, 85, 81, 50]. However, the benefits of these systems can be jeopardized because they became more subjected to elevated temperature induced by thermal management challenges as well as delay degradation (i.e. aging) caused by load imbalance [129].

#### 1.1.1 Elevated Temperature Challenge in 3D ICs

The continual cramming of more silicon transistors onto chips, known as Moore's Law, has been the building block of exuberant innovation in computing. Now it is approaching its physical limitations, where transistors' density increase on a microprocessor is becoming intractable. To extend Moore's law life expectancy, 3D ICs offer one of the most practical solutions by expanding the architecture in the third dimension to reduce chip area and shorten the metal wires [24, 85, 81]. Die-to-Die (D2D) connections along with Through Silicon Vias (TSVs) made stacking of chips feasible. The D2D layers are made of microbumps (or  $\mu$ bumps) and underfill, which exist between dies for physical connections. TSVs run across the bulk silicon die, which serve as electrical connections between active layers [27]. Hence, the move from 2D to 3D stacking for System-on-Chip (SoC) and Network-on-Chip (NoC) introduces a methodology for integrating a very high number of logic in a single die. The achievable performance benefits arising out of adopting 3D stacking in these systems include performance gain, functionality, packaging density, and heterogeneous integration, especially in terms of throughput, latency, energy dissipation, and wiring area overhead reduction [52, 33, 110].

3D ICs attribute clear performance improvement as compared to 2D ICs, however, the thermal issues have become a severe problem as a direct result of the high power density and stacked structures. The power consumption of a 3D IC is expected to decrease because of the shorter interconnects, but, the power density increases induced by the high number of active devices per unit volume [33]. The stacked dies in 3D ICs are also detrimental to thermal management. For 2D ICs, the heat generated by the active circuits can be easily accessed and dissipated through the bulk silicon substrate and *Thermal Interface Material* (TIM) to the heat sink structures, which undergoes convection heat transfer to 25°C ambient air. Only a small fraction of the heat flows downwards through the *Back-End-Of-Line* (BEOL) wiring layers and the solider balls into the package substrate because of this path's high thermal resistance. On the other hand, for 3D ICs, there is no direct access to the stacked chips nor a method of dissipating heat laterally from the stacked dies, both the BEOL wiring layers and the  $\mu$  bump layer between the stacked chips are now in the thermal path [36]. The increased power density and the various low thermal conductivity interlayer materials have made it significantly more difficult to maintain all the dies at an acceptable junction temperature. The challenges in thermal management can be even higher because of the nonuniform power dissipation, which leads to the formation of local hot spots that cannot be easily eliminated by conventional heat sink structures [15, 112]. 3D ICs encounter inevitable thermal management problems [72, 128, 109, 16]. The major reasons for the thermal issues include high power density generated by a large number of active layers per unit area as well as high thermal resistance between active dies and heat sinks in a stacked structure. Moreover, the aggressive wafer thinning process makes the thermal management of 3D ICs more challenging [112].

#### 1.1.2 Delay Degradation Problem in NoCs

The elevated temperature in 3D structures has a direct impact in delay degradation, i.e. aging, on the 3D chip. Delay degradation caused by aging mechanisms becomes a reliability challenge in advanced semiconductor technology [2]. It imposes a large design margin to the critical paths which results in design complexity and overhead [92, 75]. Bias Temperature Instability (BTI) and Hot Carrier Injection (HCI) are the dominant aging mechanisms that gradually increase the threshold voltage  $(V_{th})$  of transistors [2, 43, 55, 58]. The shifted  $V_{th}$ leads to undesired increase in system critical path delay which ultimately exacerbates performance loss and timing failure within the system components in the long run. This impacts the lifetime of the chip in the long term and its performance in the short term. Consequently, designers have to allocate considerable guardband to the critical path for avoiding timing failure. This imposes power, area, and performance overheads to the system [35, 127, 97] and threaten the performance and scalability for many-core designs and NoCs which motivates careful aging investigation. Furthermore, critical path's age is affected by operating conditions such as stress (i.e. usage of transistors along it) and temperature, which change with time because of variation in running all applications on a system. In other words, higher temperature and stress leads to higher aging rate. Since flits are the only router's stimuli inside the router and their residence time affect the temperature and stress of the router, by monitoring them one can predict temperature and stress, which impact the aging rate. Additionally, the number of flits and their associated resident time are stimulated by the routing algorithm. Router's age and reliability have direct relations with routing algorithm. By changing the routing algorithm and controlling source-destination shortest paths selection, the aging impact on NoCs can be mitigated.

### **1.2** Dissertation Objectives and Contributions

The elevated temperature in 3D systems can be solved by *Thermal Through Silicon Vias* (TTSVs) which provide a promising potential solution to thermal management in 3D ICs by lowering the thermal resistance of their dies and facilitating heat transfer across them. Past research has either overestimated or underestimated the effects of TTSVs as a consequence of the lack of detailed 3D IC models or system-level simulations. In this dissertation, we propose a simulation flow to accurately simulate TTSV effects on 3D ICs. The temperature profiles of 2D and 3D modified Nehalem x86 processor are investigated, then TTSVs are later placed close to hot spot regions to facilitate heat dissipation. First, we adopt benchmarks from Splash-2 running on a full system mode of gem5 simulator while McPAT is employed to generate the corresponding power consumption. Then, the power traces are fed to HotSpot for thermal simulation and temperature profiling. By using detailed 3D thermal model along with full system and validated thermal simulators, our results show accurate thermal analysis of 3D ICs. In addition, we found that the peak temperature of 3D Nehalem is reduced with a small area overhead. Furthermore, we present a hierarchical approach to optimize the floorplan of a 3D Nehalem-based multicore processor via Simulated Annealing (SA) with respect to the area, temperature, and wirelength. Our findings show that an increase in the TTSV area generally accompanies a decrease in peak temperature, but the wirelength depends on the TTSV arrangement, which is uniquely optimized for each case of the allowed TTSV area.

On the other hand, aging is an emerging reliability concern, which degrades the performance of systems and causes timing failure eventually. *Bias-Temperature-Instability* (BTI) and *Hot-Carrier-Injection* (HCI) are the dominant aging mechanisms, which escalate in higher temperature and stress (i.e. usage). Previous mitigation techniques to reduce aging phenomena effects on NoC system are either offline, while aging is strictly influenced by runtime operating conditions, or impose significant overheads to the system. For this purpose, this dissertation also presents an online monitoring method through a *Centralized Aging Ta*ble (CAT) for routers in NoCs. Router's capacity in flits, which are the main stimuli in routers, is predictable and limited for a given period of time. Consequently, stress rate and temperature will be in the predictable ranges, as well. Our methodology uses CAT which is populated by values that represent aging degradation for each different pairs of stress and temperature ranges during a given period of time. Furthermore, utilizing CAT, we propose an online adaptive aging-aware routing algorithm in order to avoid highly aged routers which eventually leads to age balancing between routers. Additionally, our proposed routing algorithm reduces the maximum age of routers by changing the shortest paths between source-destination pairs adaptively, considering routers' ages across them in each given period of time. We also extend this idea to 3D by proposing AROMa, which is an aging-aware deadlock-free adaptive routing algorithm integrated with a novel online aging monitoring system for 3D NoCs. The monitoring system in AROMa exploits Distributed-Centralized-Aqing-Table (D-CAT) to obtain routers' aging rates for each layer of 3D NoCs periodically. Consequently, AROMa swaps between different k-best source-destination shortest paths periodically to avoid highly aged routers, force them in the recovery phase of BTI, and accordingly balance aging in the network. Our results demonstrate that online routing algorithm and monitoring methodology, CAT, improves delay degradation of maximum aged router and aging imbalance while ensuring that the impact of our proposed methodology on network latency, *Energy-Delay-Product* (EDP) and link utilization is negligible. Moreover, our analysis using gem5 full system mode for PARSEC and SPLASH-2 benchmark suites concludes that AROMa outperforms state-of-the-art works while improving age imbalance and router maximum age with negligible overheads.

In Chapter 2, we propose a simulation flow which combines the system-level modeling and detailed thermal simulation to provide an accurate description of the performance enhancement and thermal issues in 2D and 3D ICs. Chapter 2 contributions can be summarized as follows:

- We conduct a full system level simulation of 3D ICs using gem5 [22] for Splash-2 [134] benchmarks to extract and evaluate all the defined component activities. The components' activities output along with the system configuration are fed to McPAT [88] to obtain power consumptions for all components and units.

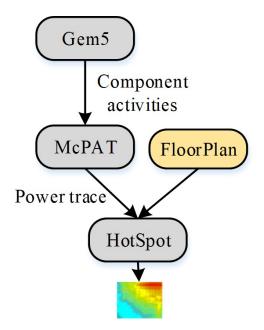

- Accurate temperature distributions of a 2D and 3D x86 processor with Nehalem floorplan [84] are simulated using the HotSpot tool [70]. The temperature profiles of 3D Alpha 21264 ev6 chip obtained from HotSpot tool and Ansys simulator are compared as a case study. To our knowledge, this is the first time that a comparison of thermal results of 3D ICs between the HotSpot tool and finite element simulator has been reported.

- A detailed thermal model of 3D ICs including TIM, TSVs, BEOL layers, and D2D layers are presented, both primary heat path upwards through the heat sink and secondary heat path downwards through package substrate are considered. A simple but effective TTSVs placement method that assigns TTSVs close to the hot spot regions is proposed and tested. The simulation result shows that putting TTSVs close to the hot spot area can cool the 3D IC significantly with a small chip area overhead.

In Chapter 3, multithreaded application benchmarks are applied to the system-level simulator and the TTSV arrangement optimization occurs early in the design phase. To be more accurate with thermal modeling, we apply the *Effective Medium Theory* (EMT) to capture direction-dependent effective thermal conductivities of TSV units. This chapter presents a hierarchical floorplanning method with a TTSV arrangement optimization algorithm for 3D multicore processors. The contributions of Chapter 3 are summarized as follows:

We conduct full system-level simulations using gem5 [22] to extract the component activities of Splash-2 benchmarks [135, 134] and calculate the power density of each IC block of a 3D Nehalem-based multicore processor (referred to as 3D Nehalem in the rest of the chapter) [84] using McPAT (Multicore, Power, Area, and Timing) [88]. We demonstrate that a critical benchmark (BARNES) can be selected to guide the floorplan optimization process.

- 2. We develop analytical models based on the EMT to capture lateral and vertical effective thermal conductivities of TSV unit cell. The impact of the liner layer is also considered and the results are validated by the *Finite-Element Method* (FEM).

- 3. We provide a TTSV placement algorithm based on SA, which optimizes the temperature, wirelength, and area of the floorplan. TTSV blocks with the direction-dependent thermal conductivities are considered during the optimization process.

- 4. We present a hierarchical approach to generate the floorplan of multicore 3D ICs, which utilizes an optimized single-core to complete the core layer floorplan of the multicore 3D IC based on a symmetric operation. The impacts of TTSV dimensions and area overheads on the peak temperature and wirelength of 3D ICs are discussed in detail.

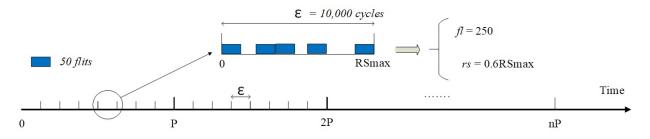

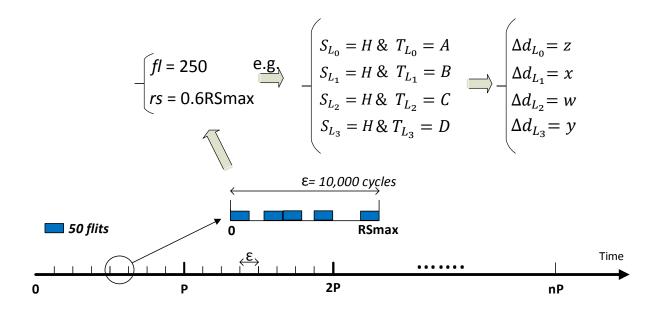

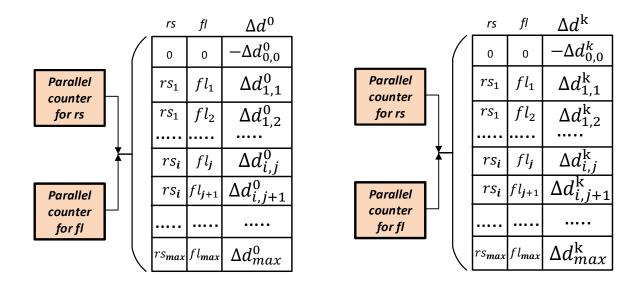

In Chapter 4, we propose a methodology based on a *Centralized Aging Table* (CAT). CAT is populated by the amount of aging degradation for different ranges of fl and rs in a router from zero up to the router capacity. This makes CAT independent from the running application. CAT, which is stored in one of the cores, can be accessed by all routers through the NoC in order to accumulate their current age to the pre-evaluated respective aging degradation. To compute fl and rs, a counter and a timer is embedded into each router. Our routing algorithm finds k-best shortest paths and selects between them periodically based on the impact of aging on routers (using CAT) to reduce maximum aged router and balance the age between routers. Since aging mechanisms impacts critical path's delay gradually, we update the routing tables in periodic time (P) (e.g. each week).

In Chapter 5, the work in Chapter 4 is extended to 3D NoCs and its main contributions are summarized as follows:

- We formulate aging effects cause by HCI and BTI for 3D NoCs using our proposed online monitoring distributed centralized aging table (D-CAT) in AROMa. D-CAT is able to quantify the gap imposed by temperature change in different perpendicular distances of layers from the heat sink and system's conditions expressed by stress in 3D NoC. Using D-CAT, routers are able to keep track of their ages at each determined time *ε*.

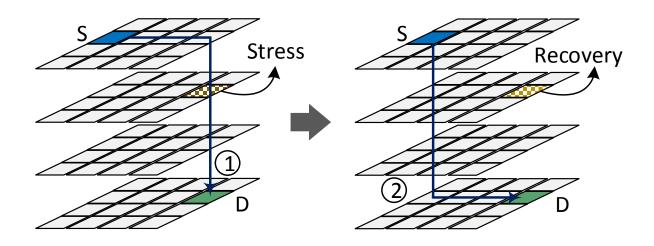

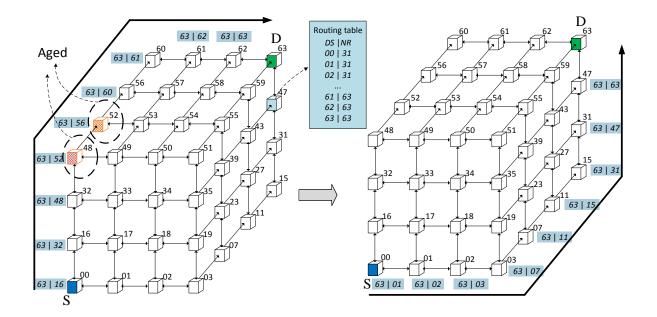

- We propose Aging-aware Routing algorithm and Online Monitoring (AROMa), an online adaptive aging-aware, deadlock free routing algorithm, and online monitoring system for 3D NoCs. AROMa chooses one of k-best shortest paths between each source-destination pairs, which has least aged routers by avoiding the maximum aged ones. This adaptivity happens at each period of time  $P = n \times \epsilon$ .

- We proved AROMa is a deadlock-free technique.

- We implemented AROMa using gem5 full system mode and compare it to OFfline budgeting for adaptive Aging-aware Routing (OFAR) and Non-Aging aWare routing (NAW) for both 2D and 3D NoCs.

### **1.3** Dissertation Organization

In Chapter 2, we analyze 3D Integrated Circuits (ICs) with and without the inclusion of TTSVs. A system level approach is detailed that demonstrates the benefit of adding TTSV to the 3D structure in term of heat dissipation. First, we introduce our approach and investigate its current related research. Then the composition of thermal models that have been employed in our analysis is discussed including TTSVs placement in 3D ICs, BEOL and D2D Layers. Next, Hotspot, which is the tool that we used in our thermal analysis and temperature profiling, is validated against the state of the art tools as well as theoretical thermal

models. To this end, Hotspot's thermal analysis on a case study processor, namely ev6, is conducted. In addition, we show the simulation model and describe our Nehalem multicore floorplan components which is used in our experimentation. After that, we demonstrate the effect of adding TTSVs on heat dissipation which leads to significant reduction of the elevated temperature of the entire 3D IC stack. Finally, we discuss our finding regarding the thermal management of 3D Nehalem processor using TTSVs then conclude the chapter.

In Chapter 3, thermal TSV optimization and hierarchical floorplanning for 3D ICs is investigated. It is different from Chapter 2 because the addition of the TTSVs to the 3D IC is optimized using *Simulated Annealing* (SA). After introducing the idea and discussing its associated related work, thermal characterization and modeling of 3D Nehalem is explained in order to optimize its floorplan with the presence of TTSV in term of area, wirelength and temperature. For this purpose, we first give a formal representation of the analytical models of a TSV unit cell. Then, we explain our framework and formulate the problem of TTSVs placement. Next, our method of TTSVs optimization and hierarchical floorplanning is outlined. Finally, the impacts of TTSVs on the peak temperature reduction of the 3D Nehalem and its associated area and wirelength overhead is thoroughly explained with conclusive remarks.

In Chapter 4, online monitoring and adaptive routing for aging mitigation in 2D NoCs are illustrated. First, we introduce the delay degradation effect on NoCs and review the works that have been performed in this subject. Next, we explain our online method for observing the aging problem in NoC routers using *Centralized Aging Tables* (CAT), which directly affect their associated cores themselves. After that, our aging aware routing algorithm is demonstrated in details. Eventually, the experimental setup and our findings are discussed with overhead analysis, then the chapter is concluded.

In Chapter 5, we present our Aging-aware deadlock-free Adaptive Routing algorithm and Online Monitoring (AROMA) in 3D NoCs. First, we specifically discuss the most recent studies related to 3D NoC aging including congestion aware, fault tolerant and aging aware adaptive routings. Then, 3D NoCs brief background is provided. Next, aging-induced delay degradation background with its associated BTI and HCI aging impact as well as the joint impact of them. After that, our problem formulation is outlined and its solution by online aging monitoring in 3D NoC using Distributed, Centralized Aging Tables, or D-CAT. We develop and implement an algorithm for adaptive aging-aware routing algorithm based on online monitoring, and we show the simulation result of this algorithm. Also the notion of delay degradation effect reduction analysis and the results are discussed. Finally, the chapter is concluded with our overall findings.

In Chapter 6, we present the conclusion of the entire dissertation and an outlook for the potential improvements and future research in this field.

# Chapter 2

# System Level Analysis of 3D Integrated Circuits with Thermal TSVs

3D stacking of ICs provides significant advantages in saving device footprints, improving power management, and continuing performance enhancement, particularly for many-core systems. However, the stacked structure makes the heat dissipation a challenging issue. While TTSV is a promising way of lowering the thermal resistance of dies, past research has either overestimated or underestimated the effects of TTSVs as a consequence of the lack of detailed 3D IC models or system-level simulations. Here, we propose a simulation flow to accurately simulate TTSV effects on 3D ICs. We adopt benchmarks from Splash-2 running on a full system mode of the gem5 simulator, which generates all the system component activities. McPAT is used to generate the corresponding power consumption and the power traces are fed to HotSpot for thermal simulation. The temperature profiles of 2D and 3D Nehalem like x86 processor are compared. TTSVs are later placed close to hot spot regions to facilitate heat dissipation, the peak temperature of 3D Nehalem is reduced by 5-25% with a small area overhead of 6%. By using a detailed 3D thermal model, full system simulation, and a validated thermal simulator, our results show accurate thermal analysis of 3D ICs.

The rest of this chapter is organized as follows: an overview is given in the introducing Section 2.1. In Section 2.2, we discuss related work of 3D ICs in terms of TTSV cooling solution and simulation tools. In Section 2.3, we propose a detailed thermal model of 3D ICs. In Section 2.4, we present a case study showing the overall chip temperature changes of 2D to 3D ev6. The case study also shows a comparison between two major thermal simulation tools and the cooling effect of TTSVs on 3D ev6. Section 2.5 discusses the simulation framework and 2D and 3D Nehalem floorplan. Then, the simulation setup and results are discussed in Section 2.6. Finally, we conclude the chapter in Section 2.7.

### 2.1 Introduction

It is well known that Moore's law is approaching its physical limitations, where the continuous shrinking of transistor size and increasing of its density on a microprocessor is becoming intractable. 3D ICs may offer one of the most practical solutions to extend Moore's law by expanding the architecture in the third dimension to reduce the footprint and short the metal wires [24, 85, 81]. Stacking of the chips is made possible by the D2D connections and TSVs. The D2D layers are made of microbumps (or  $\mu$ bumps) and underfill, which exist between dies for physical connections. TSVs run across the bulk silicon die, which serve as electrical connections between active layers [27]. The move from 2D to 3D stacking for SoC and NoC introduces a methodology for integrating a very high number of logic in a single die. The achievable performance benefits arising out of adopting 3D stacking in these systems include performance gain, functionality, and packaging density, especially in terms of throughput, latency, energy dissipation, and wiring area overhead [52]. The work in [110] also showed that 3D NoCs achieve better average performance than 2D NoCs through both analysis and simulation. 3D ICs attribute clear performance improvement as compared to 2D ICs, however, the thermal issues have become a severe problem as a direct result of the high power density and stacked structures. The power consumption of a 3D IC is expected to decrease because of the shorter interconnects, but the power density increases caused by the high number of active devices per unit volume [33]. The stacked dies in 3D ICs are also detrimental to thermal management. As shown in Figure 2.1, for 2D ICs, the heat generated by the active circuits can be easily accessed and dissipated through the bulk silicon substrate and TIM to the heat sink structures, which undergoes convection heat transfer to 25 °C ambient air. Only a small fraction of the heat flows downwards through the BEOL wiring layers and the solider balls into the package substrate because of this path's high thermal resistance. For 3D ICs, there is no direct access to the stacked chips nor a method of dissipating heat laterally from the stacked dies, both the BEOL wiring layers and the  $\mu$  bump layer between the stacked chips are now in the thermal path [36]. The increased power density and the various low thermal conductivity interlayer materials have made it significantly difficult to maintain all the dies at an acceptable junction temperature. The challenges in thermal management can be even higher due to the non-uniform power dissipation, which leads to the formation of local hot spots that cannot be easily eliminated by conventional heat sink structures [15, 112].

High chip temperature increases the risk of damaging devices and interconnects. Current cooling schemes of 3D ICs can be classified into two categories: heat sink optimization methods and internal heat distribution optimization methods [62]. Heat sink optimization methods including air cooling by electrical fans or micro-channel cooling at heat sinks, however, these methods cannot provide effective cooling for 3D ICs because the high thermal resistance D2D layers impede the heat dissipation from active circuits to heat sink structures [128]. The internal heat distribution optimization methods are to insert micro-channels or TTSVs inside the silicon chips to facilitate heat transfer from the stacked structures to heat spreaders. Micro-channel cooling scheme is costly in fabrication and dielectric liquids,

(b) 3D ICs.

Figure 2.1: Schematic diagram of liquid-less chip package

it also creates large obstacles for TSVs [74]. TTSVs, on the other hand, offer clear favorable attributes including solid-state operation and electronic process compatibility [86]. Previous studies have focused on the performance improvement from 2D ICs to 3D ICs and investigated the possible cooling solutions, however, most of the work has failed in accurately describing the temperature profiles of 3D ICs, where either a full system level simulation or detailed thermal models are missing. In this work, we propose a simulation flow which combines the system-level modeling and detailed thermal simulation to provide an accurate description of the performance enhancement and thermal issues in 2D and 3D ICs. A simple but effective TTSVs placement method is presented, the peak temperature of 3D Nehalem can be reduced by 5-25% for different Splash-2 benchmarks with a TTSVs block

area overhead of 6%. Following is a summary of the contributions of this work:

- We conduct a full system level simulation of 3D ICs using gem5 [22] for Splash-2 [134] benchmarks to extract and evaluate all the defined component activities. The components' activities output along with the system configuration are fed to McPAT [88] to obtain power consumptions for all components and units.

- Accurate temperature distributions of a 2D and 3D x86 processor with Nehalem floorplan [84] are simulated using the HotSpot tool [70]. The temperature profiles of 3D Alpha 21264 ev6 chip obtained from HotSpot tool and Ansys simulator are compared as a case study. To our knowledge, this is the first time that a comparison of thermal results of 3D ICs between the HotSpot tool and finite element simulator has been reported.

- A detailed thermal model of 3D ICs including TIM, TSVs, BEOL layers and D2D layers are presented, both primary heat path upwards through the heat sink and secondary heat path downwards through package substrate are considered. A simple but effective TTSVs placement method that assigns TTSVs close to the hot spot regions is proposed and tested. The simulation result shows that putting TTSVs close to the hot spot area can cool the 3D IC significantly with a small chip area overhead.

### 2.2 Related Work

This section presents two categories of TTSVs placement methods and covers the widely used system-level and thermal simulation tools including the consequences and the advantages of adding them.

#### 2.2.1 Thermal TSV Placement in 3D ICs.

TTSVs cooling solution is at the heart of thermal management of 3D ICs, the density and placement of TTSVs have a substantial impact on the performance, reliability, and temperature of 3D ICs [86]. The placement methods of TTSVs in 3D ICs can be classified into two categories.

#### **TTSV** Placement Using Optimization Algorithms

One category of thermal aware TSV placement techniques relies on specific algorithms and weight functions. Budhathoki et al. [26] demonstrated a localized TSV placement algorithm that used a greedy approach to place TTSV in the passive substrate and bonding layer until the maximum temperature of each grid cell is below the target temperature. This method reduced the maximum chip temperature at a reasonable TTSV density, but they did not account the secondary heat path through solder bumps and the package substrate. Chen et al. [29] described a finite element code coupled with a sequential quadratic programming algorithm to determine the optimal thermal design of TTSVs, but they lacked full-system simulation and the topology optimization of TTSVs for different benchmarks. As the circuits and power consumption increase, efficient algorithms are required to accurately determine the distribution of TTSVs to cool 3D ICs, but an efficient, systematic and automated thermal design tool that facilitates the combined thermal design including detailed thermal models and full system simulations is currently unavailable.

#### Thermal TSV Placement to Specific Locations and Areas

Goplen and Sapatnekar [62] reported that by assigning the TTSVs to specific areas of a 3D IC and adjusting their effective thermal conductivity, the same temperature reduction can be

achieved with less than 50% TSV area compared to a uniform TTSVs placement. Agrawal et al. [4] showed that by aligning and shorting dummy D2D  $\mu$ bumps with TTSVs, it enabled an average increase in processor frequency of 720 MHz with an area overhead of 0.81% without exceeding acceptable temperatures. Adding TTSVs to specific locations is easy to apply through all the silicon layers without breaking the logics in core layers and cache layers, and where to add the TTSVs can reduce the temperature more efficiently becomes an important question. The peak temperature of 3D ICs is usually determined by the blocks that have the highest power density, in this study, we first run Splash-2 benchmarks to find the regions that have the maximum temperature, after that, we assign TTSVs blocks close to the hot spot regions through all the layers in 3D ICs to facilitate heat dissipation from the stacked chips to the heat sink structures.

#### System Level Simulation Tools for Die Temperature Estimation

The following subsections overview the state-of-the-art system level simulators in architecture research as well as thermal simulators.

#### System Level Simulator

There are several system level simulators that generate cores activities. They differ in many aspects such as their scope, execution accuracy, synchronization techniques for running concurrent simulations, support for full system simulation, and whether they are trace or execution-driven simulation. Table 2.1 summarizes six of the most popular simulators and their properties. The scope of the simulator can be either user level with operating system functionality emulation or system level with the full support of a functioning operating system such as Linux Ubuntu. The accuracy of the simulator can be, cycle by cycle accurate, adopt an emulation technique that reduces the complexity of a rigorous cycle-based simulation, or a hybrid approach. The experimentation parallelism when more than one core is tested in a simulator can be sequential, or parallel with synchronization ways that are either cycle by cycle or intermittently synchronized. In our research, we adopt gem5 which is an event-driven system simulator with a modular platform for computer system architecture research, including system-level architecture as well as processor microarchitecture. Gem5 main advantages are its support for full system mode and its high accuracy.

Table 2.1: System level core simulators

| Name           | Scope            | Accuracy                   | Parallelism              |

|----------------|------------------|----------------------------|--------------------------|

| Gem5 [22]      | User/Full system | Cycle accurate             | Sequential               |

| Marss $[104]$  | Full system      | Hybrid (cycle/emulation)   | Sequential               |

| Sniper [28]    | Full system      | $DBT^{a}$ emulation        | $Loose^{b}$              |

| Zsim [116]     | User             | $DBT^{a}$ emulation        | $Loose^{b}$              |

| Manifold [130] | Full system      | Cycle/hybrid/DBT emulation | $Conservative^{c}/loose$ |

| Hornet [111]   | User             | Cycle accurate             | $Conservative^{c}/loose$ |

<sup>a</sup>DBT stand for dynamic binary translator

<sup>b</sup>loose parallelism is synchronized intermittently (not every cycle)

$^c \mathrm{conservative}$  parallelism reduce the synchronization frequency

#### **Thermal Simulators**

Several tools have been used to study the temperature profiles of 3D ICs, Lau and Yue [86] observed the thermal performance of the 3D system in package (SiP) with copper filled TSV based on CFD analysis. Chien et al. [34] used Icepack as the simulation tool to solve the heat conduction problems of 3D SiP by finite volume method. Besides these, HotSpot is a temperature modeling tool that has been widely used in computer architectural studies [4, 26, 95]. In our research, we use the HotSpot's extension as suggested by Meng et al. [95] to account the thermal properties of different layers for modeling the thermal effects of 3D ICs, we further validate the thermal results of HotSpot tool using a finite element simulator

Ansys in the case study.

# 2.3 Composition of Thermal Models of 3D ICs

In this study, we model a Nehalem like x86 processor. As shown in Figure 2.1b, the package of 3D ICs is composed of many distinct layers, such as heat exchangers, silicon chip, metal layers, and D2D layers. Metallic TSVs are presented in the silicon chip layers and connected to each other by the  $\mu$ bump. The chip stacking can be classified into three configurations: the active layer of the die faces the bulk layer of another (F2B), the active layer of dies facing each other (F2F) and the bulk layer of dies facing each other (B2B) [4]. We assume the F2B configuration in our simulation because its stacking unit process can be repeated multiple times and is favorable for stacking multiple dies.

### 2.3.1 Through Silicon Vias (TSVs)

TSVs are mainly metallic pillars that completely pass through a silicon die, whose main purpose is to establish electrical connections between stacked dies [77]. There are several fabrication processes for TSVs, such as via-first, via-last and via-middle [32]. A typical diameter of via-first TSVs ranges from 1  $\mu m$  to 5  $\mu m$ , whereas that of via-last TSVs ranges from 5  $\mu m$  to 20  $\mu m$  [18]. The presence of the TSVs also increases the thermal conductivity of silicon substrate, researchers have proposed to use dummy TSVs which do not transfer any purposeful signals and simply dissipate heat, as opposed to signal conduction, these TSVs are called thermal TSVs [18, 26, 34, 38, 62]. Non-metallic materials like diamond or Boron Arsenide may attribute higher thermal conductivity and provide better cooling performance, but, metallic materials like Cu or W have been widely used for their wellestablished fabrication process [85]. For metallic TTSVs fabrication, there is a tradeoff between the TSVs density and die thickness. To facilitate the heat transfer, a high TTSVs density is preferred, which needs a thinner die ascribable to the manufacturing constraints. However, a small die thickness reduces the thermal spreading effect and impairs the hot spot heat dissipation [49]. In our simulation, we assume a via-last technique with a TSVs diameter of 20  $\mu m$  and a pitch size of 40  $\mu m$ . The main heat transfer path in 3D ICs is in the cross-plane direction, as shown in Figure 2.1, the thermal conductivity of silicon chip with copper TSVs can be obtained using the effective medium theory [100]:

$$k_{eff} = k_{Cu}(\varphi) + k_{Si}(1-\varphi) \tag{2.1}$$

where  $k_{eff}$  is the effective thermal conductivity,  $k_{si}$  and  $k_{cu}$  is the thermal conductivity of silicon and copper, respectively.  $\varphi$  is the fractional area occupancy of copper TSV in silicon chips. Using the effective thermal conductivity, the temperature profiles of 3D ICs can be obtained with less compactional recourses [34].

#### 2.3.2 BEOL Wiring layers

The BEOL of current high-performance processors contains ten or more wiring levels and up to 10  $\mu m$  thick with a variety of dielectric materials [47]. It is necessary to accurately characterize the additional thermal resistance from the BEOL. Colgan et al. [37] measured that the unit thermal resistances of thirty-nine different BEOL test sites consisting of four line levels and three via levels were in the range of 0.5 - 5.5  $mm^2KW^{-1}$ , in our simulation, we assume the thickness of BEOL is 2  $\mu m$  and the equivalent thermal conductivity is 1  $Wm^{-1}K^{-1}$ .

#### 2.3.3 Die-to-Die (D2D) Layers

The D2D layers include underfill/air,  $SiO_2, SiN$  and  $\mu$ bumps.  $\mu$ bumps provide the interconnection between stacked dies and can be classified as electrical or dummy  $\mu$ bumps. Electrical  $\mu$ bumps provide signal connections between the active layers while dummy  $\mu$ bumps are used for mechanical and thermal transport [36]. Previous research underestimated the thermal resistance of D2D layers by assuming a high conductivity or a small thickness [62, 91]. Recent experimental data [36] showed that for 25  $\mu m$  diameter Pb-free solder  $\mu$ bumps with pitch sizes of 50 - 100  $\mu m$ , the average thermal resistance with underfill was ranged 8 - 20  $mm^2KW^{-1}$ , making it the true thermal bottleneck in the 3D ICs. The complexity of D2D composition makes it hard to simulate using a detailed model. In our simulation, we assume the thickness of the D2D layer is 20  $\mu m$  and use an equivalent thermal conductivity of 2.5  $Wm^{-1}K^{-1}$ . Table 2.2 shows a summary of the dimensions and thermal conductivities of each layer in the stacked chips.

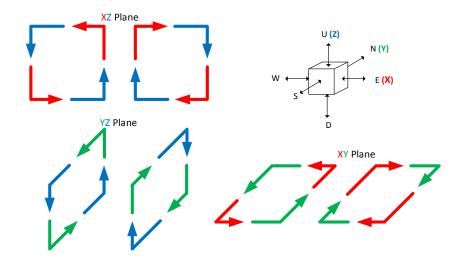

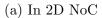

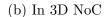

Table 2.2: Dimensions and thermal parameters