## UC San Diego Technical Reports

Title

Deterministic Replay using Processor Support and Its Applications

Permalink https://escholarship.org/uc/item/9490c7h1

**Author** Narayanasamy, Satish

Publication Date 2007-09-30

Peer reviewed

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Deterministic Replay using Processor Support and Its Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Satish Narayanasamy

Committee in charge:

Brad Calder, Chair Fred Chong Paul Chou Dean Tullsen Geoff Voelker

2007

© Satish Narayanasamy, 2007 All rights reserved. The dissertation of Satish Narayanasamy is approved, and it is acceptable in quality and form for publication on microfilm:

Chair

University of California, San Diego

2007

DEDICATION

For My Parents

## EPIGRAPH

Debugging is twice as hard as writing the program, so if you write the program as cleverly as you can, by definition, you won't be clever enough to debug it.

- Kernighan's Law

## TABLE OF CONTENTS

|   | Signature Page                                 | iii                                                                                                                           |

|---|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|   | Dedication Page                                | iv                                                                                                                            |

|   | Epigraph                                       | v                                                                                                                             |

|   | Table of Contents                              | vi                                                                                                                            |

|   | List of Figures                                | х                                                                                                                             |

|   | List of Tables                                 | xii                                                                                                                           |

|   | Acknowledgments                                | xiii                                                                                                                          |

|   | Vita and Publications                          | xvi                                                                                                                           |

|   | Abstract                                       | xviii                                                                                                                         |

| Ι | Introduction                                   | $     \begin{array}{c}       1 \\       2 \\       3 \\       4 \\       6 \\       7 \\       8 \\       9     \end{array} $ |

| Π | <ul> <li>Background and Related Work</li></ul> | 10<br>11<br>13<br>13<br>17<br>18<br>18<br>21<br>21<br>22<br>27<br>29<br>31                                                    |

|     | 6. Discussion $\ldots \ldots 32$                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

|     | E. Processor Support for Debugging and Software Correctness 33                                                                             |

|     | 1. Support in the Modern Processors for Breakpoints and Watch-                                                                             |

|     | points $\ldots \ldots 34$                                                   |

|     | 2. Processor Support for Software Correctness                                                                                              |

|     |                                                                                                                                            |

| III | BugNet: Deterministic Replay of a Uni-Processor System                                                                                     |

|     | A. Flight Data Recorder                                                                                                                    |

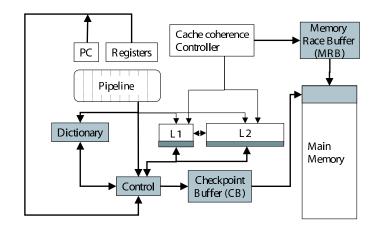

|     | B. BugNet Architecture 41                                                                                                                  |

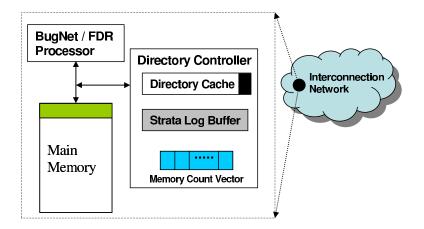

|     | 1. BugNet Architecture Overview                                                                                                            |

|     | 2. Checkpoint Scheme                                                                                                                       |

|     | 3. Tracking Load Values                                                                                                                    |

|     | 4. Handling Interrupts and Context Switches                                                                                                |

|     | 5. Handling External Input                                                                                                                 |

|     | 6. Support for Multi-threaded Applications                                                                                                 |

|     | 7. Memory Backing $\ldots \ldots 54$                   |

|     | 8. On Detecting a Fault                                                                                                                    |

|     | C. Results                                                                                                                                 |

|     | 1. Methodology $\ldots \ldots 56$ |

|     | 2. Replay Window Length                                                                                                                    |

|     | 3. Sensitivity Analysis                                                                                                                    |

|     | 4. Complexity of FDR Vs BugNet                                                                                                             |

|     | D. BugNet Extensions for Handling Self-Modifying Code and Frequent                                                                         |

|     | Interrupts $\ldots \ldots 71$            |

|     | 1. Extending BugNet to Record Code Regions 71                                                                                              |

|     | 2. Efficient Logging Across Interrupts                                                                                                     |

|     | 3. Extending BugNet for Enabling Deterministic Replay of Oper-                                                                             |

|     | ating System Code                                                                                                                          |

|     | E. Using BugNet for Deterministic Replay Debugging 79                                                                                      |

|     | 1. Collecting BugNet Logs                                                                                                                  |

|     | 2. BugNet Replayer $\ldots \ldots $ 80          |

|     | 3. Using BugNet Replayer for Debugging                                                                                                     |

|     | F. Summary                                                                                                                                 |

|     |                                                                                                                                            |

| IV  | Strata: Deterministic Replay of a Multi-Processor System                                                                                   |

|     | A. Baseline: The Point to Point Approach to Log Shared Memory                                                                              |

|     | Dependences                                                                                                                                |

|     | 1. Point-to-Point Logging and Netzer Optimization 91                                                                                       |

|     | 2. Hardware support for Point-to-Point Logging                                                                                             |

|     | B. Using Strata to Determine Shared Memory Dependencies 95                                                                                 |

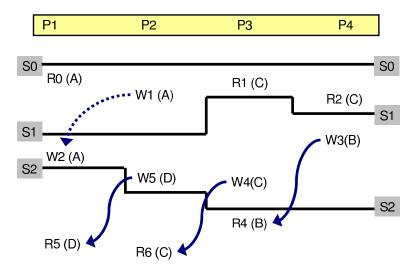

|     | 1. Capturing Shared Memory Dependencies using Strata 95                                                                                    |

|   | 2. Optimizing Strata Log Size                                      | 98           |

|---|--------------------------------------------------------------------|--------------|

|   | 3. Advantages of Strata                                            | 99           |

|   | 4. Off-line Analysis to Determine a Total Order                    | 101          |

|   | 5. Correlating Strata Logs to BugNet/FDR Checkpoint Logs for       |              |

|   | Replay Debugging                                                   | 106          |

|   | 6. Processor Effects on the Logging                                | 108          |

|   | C. Hardware Implementation for Snoop-based Systems                 | 109          |

|   | 1. Detecting Cross-Node RAW and WAW for Cached Blocks              | 109          |

|   | 2. Detecting Cross-Thread RAW and WAW for Evicted Blocks           | 110          |

|   | 3. Implementing Transitive Optimization for Cached Blocks $\ldots$ | 112          |

|   | 4. Complexity Advantage of not Logging WAR                         | 113          |

|   | 5. Hardware Comparison to Point-To-Point Logging                   | 113          |

|   | D. Hardware Implementation for Directory Based Systems             | 114          |

|   | 1. Capturing RAW/WAW using the Strata Log                          | 114          |

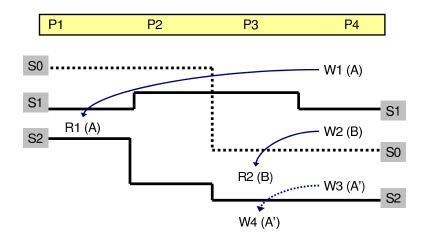

|   | 2. Determining RAW and WAW Dependencies in the Directory .         | 117          |

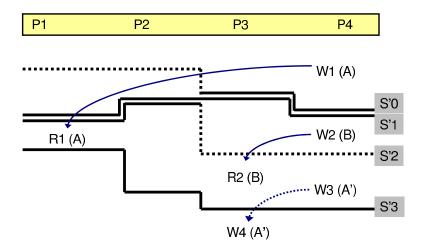

|   | 3. Strata for a Distributed Directory                              | 121          |

|   | 4. Complexity Advantage of Not Logging WAR                         |              |

|   | 5. Hardware Requirements                                           |              |

|   | E. Results                                                         |              |

|   | 1. Logging Performance Overhead                                    | 124          |

|   | 2. Strata Logging Results                                          | 124          |

|   | 3. Bandwidth Overhead                                              | 128          |

|   | 4. Scalability                                                     | 129          |

|   | F. Conclusion                                                      | 130          |

| V | Replay-based Automatic Data Race Detection                         | 132          |

| v | A. Introduction                                                    | $132 \\ 133$ |

|   | B. Finding Happens-before Replay Data Races                        |              |

|   | 1. iDNA Recorder                                                   |              |

|   | 2. Sequencers for Multi-Threaded Programs                          |              |

|   | 3. iDNA Replayer                                                   |              |

|   | 4. Finding Happens-Before Data Races                               | 143          |

|   | C. Classifying Data Races by Replaying Both Orderings              | 143          |

|   | 1. Overview                                                        | 144          |

|   | 2. Mechanism for Alternative Replay                                | 146          |

|   | 3. Classifying Data Races                                          | 147          |

|   | 4. Advantages                                                      | 149          |

|   | 5. Future $Work$                                                   | 149          |

|   | D. Results                                                         | 150          |

|   | 1. Methodology                                                     | 151          |

|   | 2. Data Race Classification Results                                | 152          |

|    | 3. Results for Each Dynamic Data Race Instance                                                                                                            | 6 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 4. Reasons for Benign Data Races                                                                                                                          | 9 |

|    | E. Prior Work                                                                                                                                             | 2 |

|    | 1. Static Analysis $\ldots \ldots \ldots$ | 2 |

|    | 2. Dynamic Analysis                                                                                                                                       | 3 |

|    | 3. Atomicity Violation Detection                                                                                                                          | 6 |

|    | F. Conclusion                                                                                                                                             | 7 |

| VI | Conclusion and Future Work                                                                                                                                | 0 |

|    | A. Summary                                                                                                                                                | _ |

|    | 1. BugNet for Replaying Non-deterministic System Interactions . 17                                                                                        | 1 |

|    | 2. Strata for Replaying Non-deterministic Shared-Memory Multi-                                                                                            |   |

|    | threaded Interactions $\dots \dots \dots$                 | 2 |

|    | 3. Applications of Deterministic Replayer for Automated Debugging 173                                                                                     |   |

|    | B. Future Work $\ldots \ldots 17^{4}$            | 4 |

|    | 1. Compressing BugNet's Logs                                                                                                                              | 4 |

|    | 2. Reducing the Complexity of Strata and Supporting Relaxed                                                                                               |   |

|    | Memory Models                                                                                                                                             |   |

|    | 3. Using Virtual Machine Support with Strata                                                                                                              | 6 |

|    | 4. Open Problems in Supporting Deterministic Replay 176                                                                                                   | 6 |

|    | 5. More Applications of Deterministic Replay 179                                                                                                          | 9 |

|    | Bibliography                                                                                                                                              | 0 |

## LIST OF FIGURES

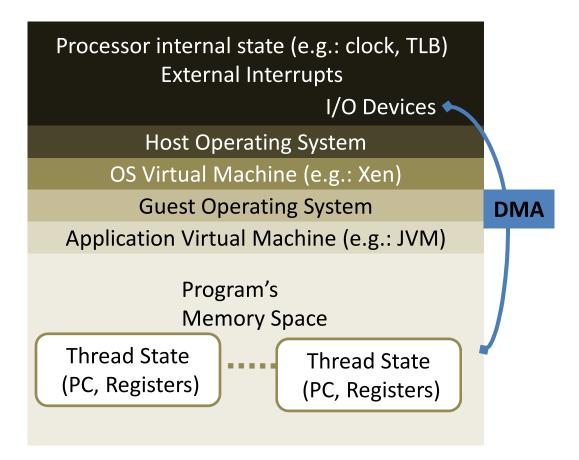

| Figure II.1                    | Layers of abstraction in a typical computer system 1                                                                  | 12 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Figure III.1<br>Figure III.2   | BugNet Architecture                                                                                                   | 42 |

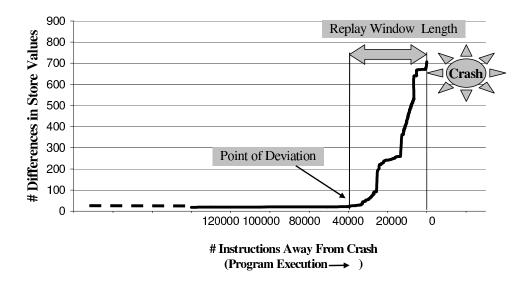

| Figure III.3                   | cution for gzip                                                                                                       | 58 |

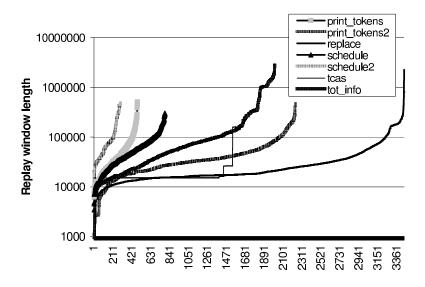

| Figure III.4                   | the Siemen benchmark suite                                                                                            | 60 |

| 0                              |                                                                                                                       | 62 |

| Figure III.5                   | -                                                                                                                     | 62 |

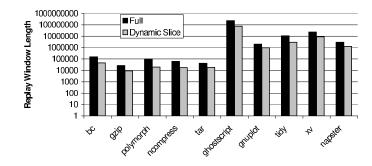

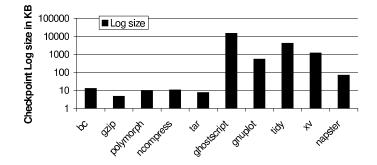

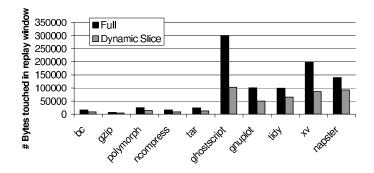

| Figure III.6                   | Memory footprint touched within the replay window (                                                                   | 62 |

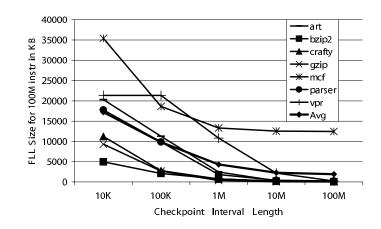

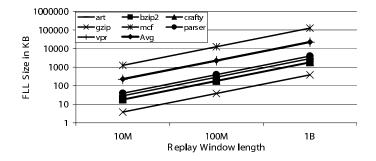

| Figure III.7                   | FLL sizes for different checkpoint interval lengths 6                                                                 | 65 |

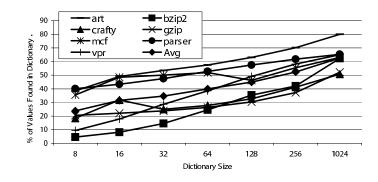

| Figure III.8<br>Figure III.9   | FLL sizes for different replay window lengths 6<br>Percentage of load values found in the dictionary table            | 65 |

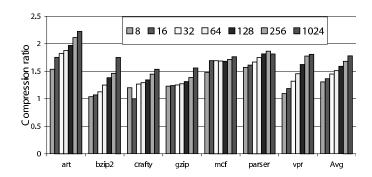

| 0                              |                                                                                                                       | 67 |

| Figure III.10                  |                                                                                                                       | 67 |

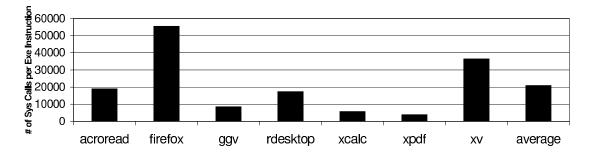

| Figure III.11                  | Number of instructions executed between two system                                                                    | 75 |

| Figure III.12                  | ,                                                                                                                     | 77 |

| Figure III.12<br>Figure III.13 |                                                                                                                       | 78 |

|                                | Too and combarger for montabe moust to brootand.                                                                      |    |

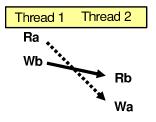

| Figure IV.1                    | ± L J                                                                                                                 | 91 |

| Figure IV.2                    | 0 0                                                                                                                   | 97 |

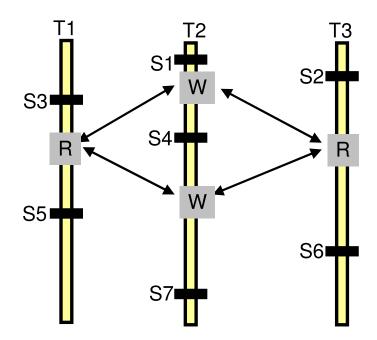

| Figure IV.3                    |                                                                                                                       | 15 |

| Figure IV.4                    | 1 0 0 0                                                                                                               | 17 |

| Figure IV.5<br>Figure IV.6     | Strata log collected in a system with two directories 11<br>Combined strata log created from the strata logs of two   | 18 |

| 0 -                            |                                                                                                                       | 18 |

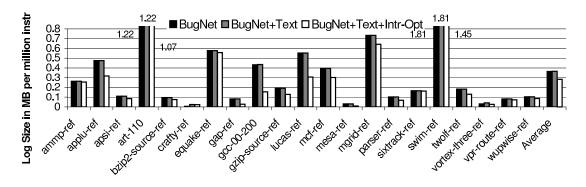

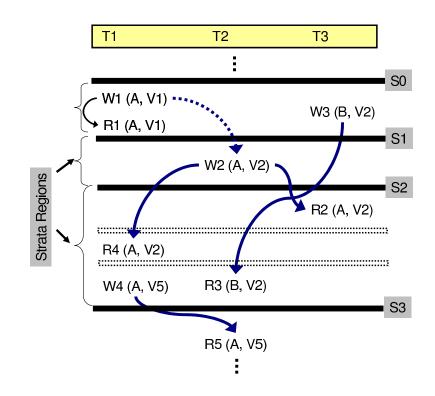

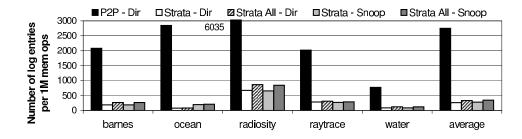

| Figure IV.7                    |                                                                                                                       | 25 |

| Figure IV.8                    |                                                                                                                       | 25 |

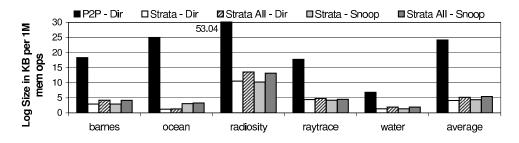

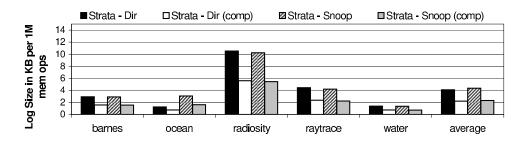

| Figure IV.9                    | Compressed Log sizes for Recording Memory Depen-                                                                      |    |

|                                | dencies $\ldots \ldots 12$ | 25 |

| Figure V.1                     | Happens-before based race detection during replay us-                                                                 |    |

|                                | ing sequencers in the replay log. $\ldots \ldots \ldots \ldots \ldots 14$                                             |    |

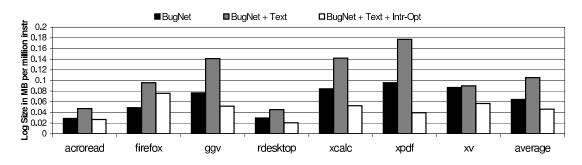

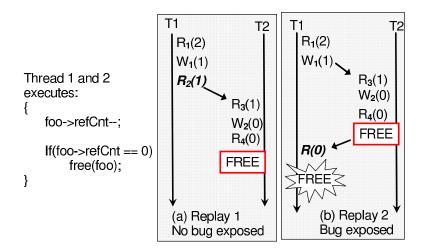

| Figure V.2                     | Race Detection Example                                                                                                | 45 |

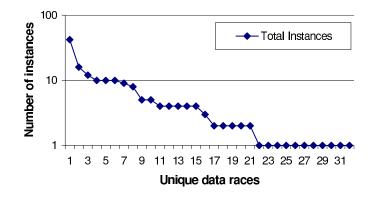

| Figure V.3                     | Statistics for the unique data races classified as Potentially-                                                       |    |

|                                | Benign15                                                                                                              | 57 |

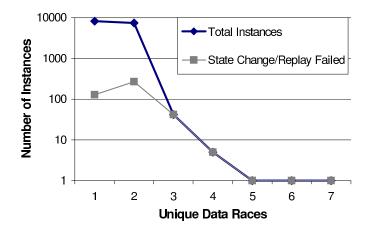

| Figure V.4 | Statistics for the unique data races that were classified |     |

|------------|-----------------------------------------------------------|-----|

|            | as Potentially-Harmful and they were found to be Real-    |     |

|            | Harmful                                                   | 157 |

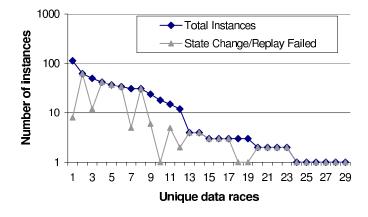

| Figure V.5 | Statistics for the unique data races that were classified |     |

|            | as Potentially-Harmful, but they were actually Real-      |     |

|            | Benign                                                    | 158 |

## LIST OF TABLES

| Table III.1 | Open source programs with known bugs. The first 5       |

|-------------|---------------------------------------------------------|

|             | programs are from the AccMon study $[110]$ , and the    |

|             | rest of the programs are from sourceforge.net 60        |

| Table III.2 | Comparison of log sizes in FDR and BugNet 69            |

| Table III.3 | Comparison of hardware complexity in FDR and BugNet. 69 |

| Table V.1   | Data Race Classification                                |

| Table V.2   | Benign Data Races                                       |

#### ACKNOWLEDGMENTS

I owe this thesis to my advisor Brad Calder. Right from picking me up at the airport when I first landed in this foreign country till my defense talk, he has guided me, inspired me, goaded me and has seen me grow as a researcher. Thank you!

I must thank Dean Tullsen, Geoff Voelker and George Varghese for their help and advise at various times during my graduate life. Thanks to Steve Swanson and Michael Taylor for their help during my interview process. Thanks to Paul Chau and Fred Chong for serving on my thesis committee and for providing useful feedback. I must also thank my undergraduate advisor Ranjani Parthasarathy for introducing me to computer architecture and encouraging me to take on open-ended projects in her courses. Without her influence I doubt if I would have pursued a PhD.

Cristiano and Gilles contributed a lot to this thesis. I would also like to thank all of my labmates for attending my practice talks, discussions, administering the clusters, dinners, movies, foosball, tennis, ping-pong, jokes, perpectives, yo-yo, and more.

Thanks to all my friends and family for all their support and tolerating my insane work schedule. I thank Ritu for her love, companionship and being there to share the ups and downs. Finally, I could not have reached this point in life without the continuing support and selfless love of my parents. I dedicate this thesis to them.

BugNet presented in Chapter III was the result of collaboration with Gilles Pokam at Intel and Brad Calder at the University of California San Diego. I thank my co-authors for allowing me to present the results of our collaboration in my dissertation.

Strata presented in Chapter IV and software implementation of BugNet

presented in Chapter III was the result of collaboration with Cristiano Pereira and Brad Calder at the University of California San Diego. I thank my co-authors for allowing me to present the results of our collaboration in my dissertation.

Replay-based automatic data race classification presented in Chapter V was the result of collaboration with Zhenghao Wang, Jordan Tigani, Andrew Edwards at Microsoft and Brad Calder at the University of California San Diego.

Chapter III contains material that appears in "BugNet: Continuously Recording Program Execution for Deterministic Replay Debugging", in 32nd Annual International Symposium on Computer Architecture, Satish Narayanasamy, Gilles Pokam, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Chapter III are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Chapter III contains material that appears in "Software Profiling for Deterministic Replay Debugging of User Code", in 5th International Conference on Software Methodologies, Tools and Techniques (SoMET), Satish Narayanasamy, Cristiano Pereira, Brad Calder. The dissertation author was the primary investigator and author of this paper.

Chapter IV contains material that appears in "Recording shared memory dependencies using strata", in *Proceedings of the 12th international confer-* ence on Architectural support for programming languages and operating systems (ASPLOS), Satish Narayanasamy, Cristiano Pereira, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Chapter IV are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Chapter V contains material that appears in "Automatically Classifying Benign and Harmful Data Races Using Replay Analysis", in *ACM SIGPLAN* 2007 Conference on Programming Language Design and Implementation (PLDI), Satish Narayanasamy, Zhenghao Wang, Jordan Tigani, Andrew Edwards, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Chapter V are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org. VITA

| 2001 | Bachelor of Engineering in Computer Science and<br>Engineering<br>College of Engineering, Anna University, India. |

|------|-------------------------------------------------------------------------------------------------------------------|

| 2005 | Master of Science in Computer Science<br>University of California, San Diego                                      |

| 2007 | Doctor of Philosophy in Computer Science<br>University of California, San Diego                                   |

#### PUBLICATIONS

Weihaw Chuang, Satish Narayanasamy, and Brad Calder. "Accelerating Meta Data Checks for Software Correctness and Security". *The Journal of Instruction-Level Parallelism*, Volume 9, June 2007.

Smruthi Sarangi, Satish Narayanasamy, Bruce Carneal, Abhishek Tiwari, Brad Calder and Josep Torrellas. "Patching Processor Design Errors Using Programmable Hardware". *IEEE Micro Special Issue: Top Picks from Computer Architecture Conferences*, January 2007.

Satish Narayanasamy, Zhenghao Wang, Jordan Tigani, Andrew Edwards and Brad Calder. "Automatically Classifying Benign and Harmful Data Races Using Replay Analysis". *International Conference on Programming Language Design and Implementation (PLDI)*, June 2007.

Satish Narayanasamy, Ayse Coskun and Brad Calder. "Predicting Faults Based on Anomalies in Speculative Execution". *Design, Automation, and Test in Europe (DATE)*, April 2007.

Weihaw Chuang, Satish Narayanasamy, Brad Calder and Ranjit Jhala. "Bounds Checking with Taint-Based Analysis". *International Conference on High Performance Embedded Architectures & Compilers (HiPEAC)*, January 2007.

Satish Narayanasamy, Bruce Carneal and Brad Calder. "Patching Processor Design Errors". *IEEE International Conference on Computer Design (ICCD)*, October 2006.

Satish Narayanasamy, Cristiano Pereira and Brad Calder. "Software Profiling for Deterministic Replay Debugging of User Code". 5th International Conference on Software Methodologies, Tools and Techniques (SoMET), October 2006.

Satish Narayanasamy, Cristiano Pereira and Brad Calder. "Recording Shared Memory Dependencies Using Strata". 12th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), October 2006.

Weihaw Chuang, Satish Narayanasamy, Ganesh Venkatesh, Jack Sampson, Michael Van Biesbrouck, Gilles Pokam, Osvaldo Colavin and Brad Calder. "Unbounded Page-Based Transactional Memory". 12th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), October 2006.

Satish Narayanasamy, Cristiano Pereira, Harish Patil, Robert Cohn and Brad Calder. "Automatic Logging of Operating System Effects to Guide Application-Level Architecture Simulation". *International Conference on Measurements and Modeling of Computer Systems (SIGMETRICS)*, June 2006.

Satish Narayanasamy, Gilles Pokam and Brad Calder. "BugNet: Recording Application Level Execution for Deterministic Replay Debugging". *IEEE Micro Special Issue: Top Picks from Computer Architecture Conferences*, December 2005.

Satish Narayanasamy, Gilles Pokam and Brad Calder. "BugNet: Continuously Recording Program Execution for Deterministic Replay Debugging". 32nd International Symposium on Computer Architecture (ISCA), June 2005.

Satish Narayanasamy, Hong Wang, Perry Wang, John Shen and Brad Calder. "A Dependency Chain Clustered Microarchitecture". 19th IEEE International Parallel and Distributed Processing Symposium (IPDPS), April 2005.

Satish Narayanasamy, Yuanfang Hu, Suleyman Sair and Brad Calder. "Creating Converged Trace Schedules Using String Matching". 10th International Symposium on High Performance Computer Architecture (HPCA), February 2004.

Satish Narayanasamy, Timothy Sherwood, Suleyman Sair, Brad Calder and George Varghese. "Catching Accurate Profiles in Hardware". 9th International Symposium on High Performance Computer Architecture (HPCA), February 2003.

#### ABSTRACT OF THE DISSERTATION

Deterministic Replay using Processor Support and Its Applications

by

Satish Narayanasamy Doctor of Philosophy in Computer Science University of California, San Diego, 2007 Professor Brad Calder, Chair

The processor industry is at an inflection point. In the past, performance was the driving force behind the processor industry. But in the coming manycore era, improving programmability and reliability of the system will be at least as important as improving raw performance. To meet this vision, this thesis presents a processor feature that assists programmers in understanding software failures.

Reproducing software failures is a significant challenge. The problem is severe especially for multi-threaded programs because the causes of failure can be non-deterministic in nature. The proposed processor feature continuously logs a program's execution while sacrificing very little performance (1%). If the program crashes, the developer can use the log to debug the failure by deterministically replaying every single instruction executed as part of the failed program's execution. Two key mechanisms enable this deterministic replay feature. One is BugNet, a checkpointing technique, which logs all of the non-deterministic input to a thread by logging the values of load instructions. The other is Strata, a logging primitive for recording shared-memory dependencies in a snoop-based or a directory-based shared-memory multi-processor. The former is sufficient for uni-processor systems and the later is required for multi-processor systems. As a proof-of-concept, this thesis presents a software implementation of BugNet replayer built using the Pin instrumentation tool.

To understand the space requirements of the BugNet recorder for debugging, this thesis empirically quantifies how much of a program's execution need to be logged and replayed in order to understand the root cause of a majority of bugs. Finally, to demonstrate the utility of the deterministic replay feature, this thesis presents a software tool built using a deterministic replayer that finds data race bugs in shared-memory multi-threaded programs and automatically prioritizes them. The data race detection tool was built in collaboration with Microsoft. It has been used to find and fix data race bugs in production code, including Windows Vista and Internet Explorer.

## Ι

# Introduction

Debugging software is becoming increasingly challenging due to the increasing complexity in the software and hardware systems. Leveraging the exponential growth in processor's performance over the last few decades, sophisticated software systems have been built. If we consider the latest operating systems for instance, Windows Vista's code base contains about 40-50 million lines of source code and Debian 3.1 contains over 200 million lines [101]. These mammoth software systems purportedly contains thousands of bugs [52] and the number of man-years required to develop a software system will keep increasing as the size of these software systems continues to increase. The advent of many-cores (multiple cores on the same processor chip) will further exacerbate the problem associated with growing complexity of software systems [3], because future applications will have to be parallelized to take advantage of a many-core processor. Traditionally, developing and debugging a parallel system has been an onerous task, because of the difficulty in understanding the non-deterministic interactions between the parallel threads in a multi-threaded system. Ensuring correctness in the face of growing system complexity, at both the hardware and software levels, is critical to the evolution of computing systems.

Significant effort has already gone into developing tools and method-

ologies for improving software engineering practices. To date, however, processors have offered very little support for developing robust software. This thesis presents a processor feature that enables deterministic replay of a program's execution, which significantly enhances a programmer's ability to understand and debug software bugs.

## I.A Deterministic Replay and its Uses

When a software system crashes, the programmer needs a mechanism to determine the causes of the failure. Unfortunately, current systems provide just the final state of the system (core dumps) [53, 63], and it is very challenging to understand the causes of the crash by looking only at the final system state.

A solution to this problem is to provide system support for continuously recording information during a program's execution, which can be used by the programmer to deterministically replay the last few seconds of the failed program's execution. A deterministic replayer is one that is capable of executing exactly the same sequence of instructions with exactly same input and output operands like in the original execution.

Providing system support for deterministic replay will improve the debugging process in several ways. First, if the bug is non-deterministic in nature, a deterministic replayer ensures that a programmer can reproduce the bug. This property is especially important for the multi-threaded programs, which are prone to non-deterministic bugs like data races. Second, a deterministic replayer can be combined with an interactive debugger like gdb or Microsoft's Visual Studio to build a time travel debugger [42]. A time travel debugger will significantly improve a programmer's productivity. Third, any dynamic analysis can be performed over the recorded program's execution, offline during deterministic replay. An offline dynamic analysis has an important advantage in that it is not limited by its performance overhead as it does not affect the behavior of a program's execution. Examples for such dynamic analysis are intrusion detection [26], memory leak detection [88], finding uninitialized variables etc. Chapter V presents a dynamic analysis based on a deterministic replayer, which automatically finds data races in the multi-threaded programs. Fourth, if the recorder is efficient, software vendors can use them to capture a remote site failure and debug it by deterministically replaying the failed execution.

Apart from debugging, system support for deterministic replay can also be useful for providing fault tolerance [48] and developing architectural simulators [59].

### I.B Need for Processor Support for Deterministic Replay

Proving the correctness of even a small scale software system has remained a holy grail for computer scientists. Even after extensive Quality Assurance process, complex software built today still contain significant number of bugs. Commercial pressure to reduce the time-to-market and the ability to distribute patches over the Internet has only aggravated today's software systems' reliability. Tracking down and fixing bugs in production software can be a nightmare, costing a significant amount of time and money. Bugs in production software account for nearly 40% of computer system failures [51], and according to NIST [97], they cost the U.S. economy an estimated \$59.5 billion annually!

Reproducing and debugging a bug at a customer site is difficult due to diversity in the hardware devices and the operating systems used by the customers. Also, non-deterministic bugs such as the data race bugs are difficult to reproduce and debug. To capture a bug at a customer site, we need an execution recorder that incurs very little performance overhead but still supports deterministic replay. Even during the testing process, a recorder with a prohibitive performance overhead will significantly affect the behavior of a program's execution, which will significantly limit its use.

Existing software based replayers either do not support deterministic replay of multi-processor systems [26, 42, 12, 81, 91] and/or incur a high performance overhead [6] (on the order 15 times slowdown when compared to the native execution). Processor support is absolutely essential to provide almost zero overhead deterministic replay debugging solution, so that even the production runs can be continuously logged. If the program crashes, the developer can use the log to debug the failure by deterministically replaying the last second of the program's execution that preceded the crash.

This thesis has three main parts to it. First is BugNet [60, 61], a checkpointing and logging solution for recording sufficient information to deterministically replay a program's execution in a uni-processor system. Second is Strata [57], a logging primitive for recording shared-memory dependencies. Shared-memory dependencies are necessary for deterministically replaying a multi-threaded program on a multi-processor system. The final part of this thesis demonstrates an application of deterministic replay in enabling offline analysis to find data races in multi-threaded programs [58, 62]. The rest of this section introduces each of these three parts.

## I.C BugNet for Deterministic Replay of a Uni-Processor Systems

To enable deterministic replay of a program's execution in a uniprocessor system, we need an ability to record the initial execution state of the program and all the non-deterministic inputs read by the program. Non-deterministic input include input from the external system such as I/O, DMA, processor clock, etc.

Prior deterministic replay solutions [104, 26, 91] employ a copy-on-write

based checkpointing solution to capture the initial execution state (memory and register state) of the program. In addition, they require additional support to explicitly identify every source of non-deterministic input and to log the values read from those sources. As there can be so many different sources of nondeterministic input, it is tedious to implement a recorder and replayer using this approach. Also, the recorder and replayer will be dependent on a particular operating system or a system configuration, which makes it difficult to maintain and port them. System independence is a necessary property for a processorbased deterministic replay solution for it to be useful across diverse systems used at the customer sites.

The key contribution in BugNet is the system-independent checkpointing and logging mechanism that supports deterministic replay of a program's execution on a uniprocessor system. BugNet logs the architectural register state at the beginning of a checkpoint, and then logs a memory value when it is first accessed by a load instruction. The same memory value is logged again only if it has been modified by an external event. Thus, unlike traditional checkpointing mechanisms, BugNet avoids the complexity of capturing information about system calls, I/O, interrupts, DMA, etc. As a result, BugNet can support deterministic replay of only the application's execution and the libraries it uses, but not the full system. However, BugNet does support deterministic replay of user code across *all* non-deterministic system events, including context switches and interrupts. In addition, BugNet does not require a final core dump of the system state for replaying, which significantly reduces the amount of data that must be sent back to the developer.

## I.D Strata for Deterministic Replay of a Multi-processor System

For debugging multi-threaded programs executing on a multi-processor system, in addition to recording non-deterministic input from the external system, we also need to record the non-deterministic interactions between the concurrent threads. That is, for a shared-memory multi-threaded program, we need to capture the dependencies between the memory operations executed across concurrent threads.

To accomplish this, the state-of-the-art deterministic replay solution for a multi-processor system called the Flight Data Recorder (FDR) [104] determines the shared memory dependencies by monitoring the coherence messages. To record a shared memory dependency, FDR records the memory counts of the dependent threads (point-to-point log). FDR implements the Netzer transitive optimization [64] using processor support to reduce the number of shared-memory dependencies that need to be recorded.

Instead of using a point-to-point log, this thesis proposes using a *Stratum* log [57] to record the shared memory dependencies. A stratum consists of the memory counts of all the threads at the time when it is logged. A stratum separates all the memory operations that were executed in all the threads before the time when it is recorded, from those that will be executed after it is recorded. Using this property of Strata, we can implement a transitive optimization that is 12 times more effective than a point-to-point logging solution in terms of log size. Also, unlike the earlier mechanisms, Strata can be used to capture multi-threaded dependencies in a snoop-based multi-processor system. Further, Strata can be recorded using 1/16th the hardware required for implementing a point-to-point logging solution.

#### I.E Deterministic Replay for Debugging

This thesis explores the use of deterministic replay for debugging. The process of debugging with the help of a deterministic replayer is referred to as Deterministic Replay Debugging (DRD). This thesis empirically quantifies certain variables relevant to the DRD process. This includes an empirical analysis [58], which quantifies how much of a program execution has to be logged and replayed, in order to understand the root cause of a majority of bugs in the production code. The result of this analysis shows that we can understand the root cause of a majority of bugs in the open source programs if we have the ability to replay about 10 million instructions that precedes the crash. Further, we examine the potential benefit of using dynamic slicing along with a deterministic replay debugger.

To illustrate the benefits of deterministic replay debugging, this thesis describes an offline dynamic analysis tool based on a replayer, which automatically finds harmful data races. This dynamic data race detection tool was built in collaboration with the Microsoft Corporation. It is based on the replayer that was independently developed at Microsoft [6].

Many concurrency bugs in multi-threaded programs are due to data races. There have been many efforts to develop static [8, 32, 56] and dynamic mechanisms [85, 25, 108, 66, 71, 1, 77] to automatically find the data races. However, most of the prior work has focused on finding the data races and eliminating the false positives. Even if we manage to eliminate all the false positives, not all of the remaining true data races are harmful. In fact, in the production code, we found that only 10% of the true data races are actually harmful. The remaining 90% were all *benign* data races. They were benign in the sense that the programmer was convinced that they do not affect the program's correctness and so the programmer intentionally chose to avoid the overhead of synchronization. Thus, reporting all the true data races places a huge burden on the developers as they have to manually triage and eliminate a large number of benign data races. Triaging data races is a time consuming and tedious exercise.

The replay-based dynamic analysis presented in this thesis [62] automatically classifies the data races into two categories – the data races that are potentially benign and the data races that are potentially harmful. We discuss our experiences in using our dynamic race classification approach on an extensively stress-tested build of Microsoft's Windows Vista and Internet Explorer. The proposed technique was able to automatically filter out over half of the real benign data races, classifying them as potentially benign, which can be ignored by the developers. In addition, all of the harmful data races were correctly classified as potentially harmful. They were reported to the developers, and they all have been fixed in the production code.

## I.F Contributions

This thesis makes the following contributions:

- Motivates the need for providing processor support for deterministic replay, presents a comprehensive solution for supporting deterministic replay with and without using processor support, and explores an application of deterministic replay for debugging.

- Presents the BugNet checkpointing and logging solution that captures all the non-deterministic input read by a thread of program's execution by logging the values of the load instructions. BugNet-based recorder and replayer are easy to implement and maintain. Evaluation of the processor-based BugNet recorder design is also presented.

- Presents Strata logging solution for recording the shared-memory multithreaded dependencies, which are necessary for replaying the execution of a

multi-processor system. Strata logs are 12 times smaller, and requires 1/16th the hardware when compared to the prior solution. Unlike earlier schemes, Strata logs can be recorded in a snoop-based multi-processor system as well.

- Presents an analysis of the bugs in the open source programs to determine the resource requirements of a recorder. This analysis introduces a notion of *replay window length* for a bug, which is the number of instructions that need to be replayed to understand the root cause of the bug.

- Makes an observation that not all the data races are harmful bugs. Presents a unique replay-based dynamic analysis tool that automatically classifies the benign and harmful data races. This tool has been used to find and fix several bugs in Windows Vista and Internet Explorer, and continues to be widely used at Microsoft. These applications demonstrate the need for providing processor support for deterministic replay.

## I.G Organization

Chapter II discusses in detail about deterministic replay, its applications and existing software and processor based solutions. Chapter III presents the BugNet checkpointing and logging technique. It also discusses the usage models for BugNet and characterizes the replay window length for various open source bugs. Chapter IV describes Strata and discusses how it can be recorded in both snoop-based and directory-based multi-processor systems. Chapter V presents a replay-based dynamic analysis tool that automatically classifies benign and harmful data races. Chapter VI concludes with a discussion on the opportunities for future work.

## Π

# **Background and Related Work**

Computer system trends have increased the importance of providing efficient solutions to find and prevent software bugs. Lowering hardware costs have significantly reduced hardware's importance in terms of total computer cost [34, 69]. Lower hardware costs and increasing software complexity has increased the software's component in the total cost of ownership of a system. In addition, with the wide spread use of the Internet and how easy it is to release patches, software is released with more potential bugs than in the past. The need for multi-threaded programs for even desktop applications has never been as compelling as it is today, as we step into the multi-core era. Multi-threaded programs conventionally have been difficult to develop, debug, and maintain. Given these trends it is just as important to examine efficient hardware support for software correctness, security, and debugging as it is to increase the performance of the next generation of processors.

This thesis proposes a processor feature that provides support for deterministically replaying a program and demonstrates the utility of this feature for debugging. In this section, we first define what deterministic replay is, motivate its uses, and then discuss various challenges in implementing such a feature. This is followed by a detailed discussion on prior software-based and hardware-based solutions for providing replay support. Finally, we discuss prior work on providing support for various other software-reliability oriented processor features, including the debugging features that got implemented in real processors.

### **II.A** Deterministic Replay

When a computer system crashes, the programmer needs a mechanism to determine the causes of the failure. Unfortunately, current systems provide just the final state of the system (core dumps) [53, 63], and it is very challenging to understand the causes of the crash by looking only at the final system state. However, if we can deterministically replay exactly what happened, then it will help us understand the system crash.

Various layers of abstraction for a computer system executing a multithreaded program is shown in Figure II.1. A full system deterministic replay should be able to replay all of the hardware and software components in a computer system.

Deterministically replaying a hardware component in a system (eg: a processor or a video card, which are shows as the outermost abstraction layer in Figure II.1) would involve recording the hardware component's internal state (by reading from the JTAG ports) and replaying the electrical signals in these devices. There have been works that focus on providing support for deterministically replaying a hardware component of a computer system [83]. This is useful for debugging bugs in hardware device.

However, to debug a software program, it is sufficient to deterministically replay just the software. We say that we can deterministically replay a software program, if we can replay exactly the same sequence of instructions with exactly the same input and output values like in the original execution. To support deterministic replay of a software program, however, we need to record and

Figure II.1: Layers of abstraction in a typical computer system.

replay the values that are read from any external hardware device (that is, we need to emulate the hardware device), which is one of the challenges in supporting deterministic replay of a program's execution.

This thesis focuses on providing support for debugging software. Hence, the rest of the discussion in this section will focus on supporting deterministic replay of just the software systems.

## **II.B** Deterministic Replay Uses

This section discusses several applications of providing support for deterministic replay.

#### **II.B.1** Deterministic Replay for Debugging

Providing system support for deterministic replay will improve the debugging process in several ways.

#### **Reproduce Non-Deterministic Bugs**

Non-deterministic bugs or Heisenbugs are hard to reproduce. The reason is that they are dependent not just on the input to the program but also on the environment (operating system, run-time libraries, debugging environment, processor speed etc.) in which the program is running. For example, a memory allocator might randomly choose a location in the program's address space to allocate memory for a buffer. This can lead to non-deterministic buffer overflow bugs. In a C program, a bug due to an un-initialized variable can be nondeterministic. Another class of non-deterministic bugs are the data race bugs in multi-threaded programs, which are dependent on the order in which threads are executed. A non-deterministic bug encountered in a program's execution is hard to debug, because when a programmer executes the program in a debugger with exactly the same input the bug might not appear again. With deterministic replay support, however, conventional debuggers like gdb or Microsoft's Visual Studio can reproduce a bug encountered during a program's execution any number of times.

#### **Reproduce Remote Site Failures**

If the recorder is efficient, software vendors can use them to capture a remote site failure and debug it by deterministically replaying the failed execution any number of times. Customers and beta-testers will find such a mechanism useful to report the software failures to the developers.

#### Time Travel Debugging

With deterministic replay support, an interactive debugger like gdb or Microsoft's Visual Studio can be enhanced to support a time travel debugger [42, 6, 78]. A time travel debugger provides functionalities such as step backward, reverse breakpoints and reverse watchpoints [7]. These features are complementary to step forward, breakpoints and watchpoints found in commonly used debuggers like gdb.

Using a breakpoint, a programmer can fast forward a program's execution to a particular line in the source code. Reverse breakpoint on the other hand allows a programmer to go back in program's execution time till the execution reaches a desired line in the source code. Watchpoints and reverse watchpoints are similar to breakpoints and reverse breakpoints, except that watchpoints are not set on a particular function or a source line, but on a variable.

The reverse debugging functionalities discussed above can be supported

using the following approach based on deterministic replay support [42, 6]. A recorder would create checkpoints at regular intervals. A program's execution can be replayed from the beginning from any of these intermediate checkpoints. Let us say that the programmer wants to step back by one instruction. To reach a desired point in the program's execution, the debugger would start the replay from the beginning of the checkpoint that contains the target instruction till the replay reaches the target instruction. If the checkpoint interval lengths are small enough, then stepping back would appear instantaneous to the programmer. The recorder can use relatively longer checkpoint interval lengths for efficiency, and more checkpoints can be created during replay to shorten the checkpoint interval length. Reverse breakpoints and reverse watchpoints can be supported similar to step backwards functionality. More details can be found here [7, 42, 6].

These reverse functionalities are very useful during cyclic debugging when a programmer wants to examine a portion of a program's execution over and over again. With a conventional debugger like gdb, however, a programmer has to restart the program's execution from the beginning, which is not a productive way of using a programmer's time. Thus, a time traveling debugger significantly improves a programmer's productivity. To build such a debugger we need deterministic replay support.

#### Offline Dynamic Analysis

Dynamic analysis techniques can automatically find bugs in a program's execution. Valgrind [88] and Purify [35] are examples of dynamic analysis tools. Such tools can automatically find memory access violations such as memory leaks, uninitialized variables, data races [85], detection intrusions [26] etc. in a program's execution. However, dynamic analysis tools like Valgrind slows down a program's execution by a factor of 20 to even 100 times. As a result, they cannot

analyze an execution behavior of a program on a real machine. If we can record a program's execution without intruding the program's behavior, then we can perform the time consuming dynamic analysis during replay. Chapter V presents a unique dynamic analysis based on a deterministic replayer, which automatically finds data races in the multi-threaded programs.

#### Experience with Using Deterministic Replay Debugging

Microsoft has developed a software record and replay tool called iDNA [6] in parallel with our BugNet work (BugNet is discussed later in Chapter III). It is based on a load-based checkpointing mechanism like that of BugNet to enable deterministic replay. Experiences of this dissertation author in using iDNA is discussed in this section.

iDNA has been used to trace thousands of executions of Microsoft's applications and these traces are stored in a centralized repository. At a developer's site, a developer can afford to allocate large disk spaces for replay logs, and so even full execution of a program is recorded. In addition to iDNA, Microsoft has also built dynamic tools that analyze these recorded program executions by replaying them using the traces. Thousands of bugs (including very many nondeterministic bugs like data races) in Microsoft's applications like Windows Vista and Internet Explorer have been automatically found using these tools. Also, the testers and the users within the organization find it easier to report a bug in a program's execution to the developer through the logs that can replay that execution, instead of having to write a detailed bug report. The author of this dissertation built a dynamic analysis tool based on iDNA that automatically finds data races bugs. The details of this tool are discussed in Chapter V.

However, iDNA is about 15x slower for computationally intensive programs and about 5x slower for interactive programs, when compared to their native executions. This is because it is a purely software-based implementation. Because of the high performance overhead of iDNA, it cannot be used to capture a natural behavior of a program's execution (especially interactive applications like Internet Explorer) on a real system. The processor-based BugNet support presented in this thesis, however, incurs negligible performance overhead. Therefore, developers can use BugNet for recording programs without altering their behavior on a real system and debug them. Also, the customers can use BugNet to capture the bugs even in the production runs and report them to the developers, which is not feasible with iDNA.

#### **II.B.2** Deterministic Architectural Simulators

Simulators used for studying a processor architecture [9, 29] have to correctly execute a program to analyze the architectural characteristics for that particular program's execution. Typically, architectural simulators use a functional system emulator to correctly execute the system calls and interrupts invoked by the program. These functional system emulators are complex to develop and maintain. To emulate a system call, an emulator would invoke an equivalent system call in the host system on which they are running. The values returned by an emulator for a system call are dependent on the host system's environment, which can lead to non-deterministic behavior in the program being simulated. Also, the simulation of a multi-threaded program on a multi-processor system can be non-deterministic because of the synchronization and data races in the multi-threaded program. Non-determinism in architectural simulations is an issue, because it is hard to compare two architecture designs when a program's execution is not the same across the two simulations.

To avoid the complexity of developing and maintaining a functional emulator, and to ensure deterministic simulation of a program's execution, one can use a deterministic replayer instead of a functional emulator [59].

#### II.B.3 Fault Tolerance

System support for deterministic replay can also be useful for providing fault tolerance. ExtraVirt [48] keeps a replicated copy of a virtual machine and ensures deterministic replay in that replicated copy. The output from the original execution and the replicated copy is compared to ensure fault tolerance against transient faults.

#### **II.C** Overview of Prior Record and Replay Solutions

Figure II.1 shows the various layers in a typical computing stack. The recorder and the replayer can be implemented at any of these layers - in the virtual machine monitor [26], or the guest operating system [91], or the application's virtual machine such as the Java Virtual Machine [13], or by compiling or instrumenting the application itself.

Recording a software system's execution essentially involves two parts - checkpointing and logging all the non-deterministic input read by the system being recorded.

Checkpointing is necessary to retrieve the initial execution state of the system from where we would like to replay. A checkpoint mainly constitutes the memory state and the architecturally visible register states of the software system. Most of the record and replay systems [42] create a new checkpoint at regular intervals called checkpoint intervals, instead of just one checkpoint at the beginning of a program's execution. This is useful in two ways. One, if we run out of space to hold the logs, we can discard the logs from the oldest checkpoint and still be able to replay some parts of the program's execution. Two, during debugging, the programmer can fast forward to any intermediate instant in the

program's execution without having to replay from the beginning of the program's execution.

Checkpointing [28] is relatively an easy problem to solve. Some systems [26] just take a complete checkpoint of the software system's memory and register state at the beginning of the execution. However, this solution is inefficient and not useful for taking checkpoints at regular intervals. The most common solution is to employ some form of a copy-on-write checkpointing mechanism [42, 7, 31, 91] to reduce the amount of information recorded and also to reduce the performance overhead. It works as follows. Instead of logging the values in all the memory locations at the beginning of a checkpoint interval, a memory location's value is logged only when it gets modified for the first time within the checkpoint interval. The memory state of the process at the beginning of a checkpoint interval can be rebuilt, during replay, by starting with the process's complete memory state at the end of the program's execution and progressively restoring the values from the latest checkpoint log. This thesis presents a checkpointing solution that is different from the copy-on-write mechanism. It involves checkpointing just the register state. The memory state is captured by logging the values of the load instructions, which also captures all the nondeterministic input to the program. This means that the final complete memory state (core dump) is not required for replay, which is necessary in a copy-on-write based checkpointing mechanism to rebuild the memory state at the beginning of a checkpoint. This solution will be discussed in detail in Chapter III.

The second part of a recorder involves logging all the non-deterministic events that can influence the execution of the software system. Logging all the non-determinism is the most difficult part of recording a software system's execution. Any value read from the system external to the recorded system is considered to be non-deterministic. If the recorder is implemented in the application's space, then any value read from the layers above the application state shown in Figure II.1 is considered to be non-deterministic. This includes all the system interactions such as the values read from the system calls, interrupts, instructions that read processor's state such as processor's clock (e.g.: rdtsc), all the I/O including the memory-mapped I/O and DMA. Apart from these nondeterministic system interactions, if the application is multi-threaded, then there could be non-deterministic interactions between the threads reading and writing from the shared memory locations.

If the recorder is implemented in the higher layer of abstraction such a virtual machine monitor, then the only non-deterministic input in a uniprocessor system can be from the external host operating system and the underlying hardware. Though the decisions of the guest operating system and hence its thread scheduling will be deterministic, to ensure deterministic execution of the virtual monitor and its processes, we still need to take care of the system calls to the host operating system, all the I/O including memory-mapped I/O, DMA and all the non-deterministic instructions.

Capturing all these sources of non-deterministic interactions is what makes it challenging in providing record and replay support. Providing this support in a way that the recorded execution can be replayed across different platforms and processor architectures is even more challenging. Apart from being accurate in capturing all the non-determinism, a recorder should also be efficient in terms of both performance and space overhead. A recorder with a high performance overhead can interfere with the program's execution, making it difficult to record and understand a program's execution on a real system.

#### **II.D** Prior Record and Replay Systems

In this section, we discuss various prior proposals for recording and replaying a program's execution. We start with a description of a simple recorder for a deterministic system. Then we discuss various solutions that provides support for recording non-deterministic system interactions such as system calls, I/O and DMA. Then we discuss solutions for taking care of non-determinism in multi-threaded programs executing on a uniprocessor system. This is followed by a description of the software solutions for recording a multi-threaded program running on a multi-processor system. Finally, we discuss how hardware support can solve some of the limitations of the software-based solutions in replaying multi-processor systems. We conclude with a discussion on the contribution of this thesis and compare them with the prior solutions.

#### **II.D.1** Replaying a Program's Execution on a Deterministic System

**IGOR:** IGOR [31] is one of the earliest recorders that supported replay of a program's execution (IGOR does not support operating system replay). IGOR assumes that a program's execution is completely deterministic. That is, it does not handle non-determinism due to system interactions and races in the multi-threaded programs. Therefore, it provides support for just taking a checkpoint of the program's memory and register state. IGOR's checkpoint mechanism is a form of *copy-on-write* checkpointing. IGOR is based on operating system support. The OS supports a system call that would determine the program's virtual pages that were modified after the last checkpoint. To create a checkpoint at a particular instance in a program's execution, the data in all the modified pages are logged as part of the checkpoint. To replay from a particular dynamic instruction in a recorded program's execution, IGOR first determines the most recent checkpoint that precedes the starting point of replay. Then, the complete memory state is reconstructed for that particular checkpoint. This is done by scanning the recorded log file backwards looking for the most recent log for each virtual memory page. The program is replayed from the reconstructed memory image using an emulator up-to the instruction specified by the user. The performance overhead of the recording phase is between 50% to 400%, while the replay overhead is on the order of 140 times when compared to the native execution.

#### **II.D.2** Recording Non-Deterministic System Interactions

A program gets its input values from the external system through system calls (asynchronous interrupts), asynchronous interrupts and also memorymapped I/O. Some of the I/O activity can also get delegated by the operating system to a DMA (Direct Memory Access) processor, which can modify the program's memory state concurrently with the program's execution. Also, a program can execute instructions that return non-deterministic values. For example, the instruction RDTSC (ReaD TimeStamp Counter) in x86 reads the processor's clock and writes it to an architectural register that is part of the program's register state. All these are sources of non-deterministic input to a program. To ensure deterministic replay of a program's execution, all of these non-deterministic input need to be recorded and replayed. In this sub-section, we discuss how prior proposals addressed this problem. None of the tools described in this section can record and replay a multi-threaded program's execution on a multi-processor system.

Boothe [7] developed a debugging tool to record and replay a program's execution. The tool supports reverse debugging features such as backward stepping and reverse breakpoint. It is based on compile-time instrumentation. The tool creates checkpoints at regular intervals and also captures the non-deterministic input through the system calls. To create a checkpoint, the tool leverages the operating system's copy-on-write based forking mechanism. The tool instruments all the system calls in the program to record the return values from the system calls. However, the semantics of of each system call could vary in terms of how they return their values. That is, the specifications about the memory and register state side-effects of a system call varies across the system calls. Therefore, the tool has to explicitly take care of each of type of system call. Boothe in his paper [7] acknowledges the complexity of this solution. The tool supported only 35 out of 262 system calls in the UNIX system. It cannot handle asynchronous interrupts, memory-mapped I/O and DMA. The performance overhead is less than a factor of two when compared to the native execution. Chapter III presents a system-independent BugNet solution. It automatically captures the input values through all of the system calls, interrupts and DMA without having to explicitly take care of each of these sources of non-determinism.

**jRapture:** In jRapture [94], Java API classes that interact with the JVM and the underlying system through JNI calls are modified to record the non-deterministic input from the external system. But jRapture only records the values returned by the system call (both return by value and reference). It does not capture the side-effects to the application's memory state. Also, it does not record the interrupts, memory-mapped I/O and the values read through DMA.

**Tornado:** Tornado [19] requires modifications to the Linux operating system's kernels to trace the values written to the user space in the kernel mode. In Linux, the operating system can write to the user memory space only through a few write primitives defined in the code. Tornado instrumented these write primitives to keep track of the user memory locations that are modified by the system call. At the end of the system call, the tracer operating in the user space invokes **ptrace()** system call to obtain all the user memory locations. The performance

overhead of Tornado is less than a factor of two. Tornado, however, does not handle asynchronous interrupts, memory-mapped I/O and DMA.

Flashback: Flashback [91] provides operating system support for rolling back a program's execution and replaying it. It does not record a program's execution permanently. To rollback a program's execution, Flashback implements the following checkpoint mechanism. To create a checkpoint of a process, Flashback forks the process similar to Boothe's checkpoint implementation [7]. One of the two process is called the shadow process. The program's execution can be rolled back by restoring the state from the shadow process at any later point. To replay from a checkpoint, Flashback needs to record the nondeterministic input values from the system. Similar to Boothe's implementation, Flashback provides special attention to every type of system call to capture their return values. Interrupts are also recorded and replayed. However, it does not handle read and write to the memory-mapped locations that are shared between multiple processes. A simple copy-on-write checkpoint for the shared-memory locations wouldn't be sufficient, because it would require that we replay all the processes sharing the memory. Flashback, however, provides support for rolling back and replaying only the application program being debugged, and not the full system. While Flashback provides support for rolling back all the threads of a multi-threaded program, it does not support deterministic replay of all the threads after rollback even on a uniprocessor system. This is because it does not record and replay the thread scheduling order.

**ReVirt:** Unlike the other systems we have described so far, ReVirt [26, 42] takes care of all forms of non-determinism in a uniprocessor system. The recorder and the replayer are built inside the virtual machine monitor (UM-Linux). Unlike the previous systems we described, it supports complete deterministic replay of the entire virtual process and all the guest operating systems

and applications that are running inside the virtual process. To achieve this, ReVirt takes a checkpoint consisting of the entire virtual disk and the state of the virtual process (this checkpoint mechanism was later improved using a copyon-write policy in TTVM [42]). After taking a checkpoint, ReVirt records all the non-deterministic events and input read from the host system on which the virtual process is running. (The reader can refer to Figure II.1, which shows the computing stack where the virtual machine monitor lies below the host processor, hardware devices and the host operating system). ReVirt assumes that there cannot be any inter-process communication between the virtual process and the other processes running in the host system. Therefore, ReVirt does not record all the non-deterministic events in the host system, but only those that affect the virtual process and the applications running inside the virtual process.

When an interrupt is delivered to the virtual process, ReVirt records it using a timestamp. ReVirt uses the number of branches executed after since the last interrupt as the timestamp, which is calculated from the performance counters of the host processor. In addition to recording the timestamp, architectural register contents of the virtual process are also logged.

In addition to recording the asynchronous interrupts, ReVirt records the input read from the host system. This is done by intercepting all the host system calls that could potentially read values from the host system. Apart from the host system calls, instructions such as rdtsc (read timestamp counter) and rdpmc (read performance counter) can return non-deterministic values and need to be logged. ReVirt configures the process control register (CR4) to generate a trap to the virtual process when any of these non-deterministic instructions are executed. On receiving a trap, the return values of the non-deterministic instruction is logged.

During replay, ReVirt ensures that the interrupts are delivered to the