### **Lawrence Berkeley National Laboratory**

### **Recent Work**

### **Title**

Analog-to-Digital Conversion Using Custom CMOS Analog Memory for the EOS Time Projection Chamber

### **Permalink**

https://escholarship.org/uc/item/92s7f8zg

### **Authors**

Lee, K.L. Arthur, A.A. Jones, R.W. et al.

### **Publication Date**

1990-10-01

# Lawrence Berkeley Laboratory UNIVERSITY OF CALIFORNIA

### Engineering Division

Presented at the IEEE Nuclear Science Symposium, Arlington, Virginia, October 23–26, 1990, and to be published in the Proceedings

**Analog-to-Digital Conversion Using Custom CMOS Analog Memory for the EOS Time Projection Chamber**

K.L. Lee, A.A. Arthur, R.W. Jones, H.S. Matis, M. Nakamura, S.A. Kleinfelder, H.G. Ritter, and H.H. Wieman

October 1990

### **DISCLAIMER**

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

### Analog-to-Digital Conversion Using Custom CMOS Analog Memory for the EOS Time Projection Chamber

K.L. Lee, A.A. Arthur, R.W. Jones, H.S. Matis,

M. Nakamura, S.A. Kleinfelder, H.G. Ritter, and H.H. Wieman

Lawrence Berkeley Laboratory

University of California

Berkeley, CA 94720

October 1990

This work was supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Nuclear Physics Division, of the U.S. Department of Energy under Contract No. DE-AC03-76SF00098.

## ANALOG-TO-DIGITAL CONVERSION USING CUSTOM CMOS ANALOG MEMORY FOR THE EOS TIME PROJECTION CHAMBER.

K.L. Lee, A.A. Arthur, R.W. Jones, H.S. Matis, M. Nakamura, S.A. Kleinfelder, H.G. Ritter and H.H. Wieman

Lawrence Berkeley Laboratory University of California Berkeley, CA 94720

Abstract

The multiplexing scheme of custom CMOS analog memory integrated circuits, 16 channels x 256 cells, into analog to digital converters (ADC's) to handle 15,360 signal channels of a time projection chamber detector system is described. Primary requirements of this system are high density, low power and large dynamic range. The analog memory device multiplexing scheme was designed to digitize the information stored in the memory cells. The digitization time of the ADC's and the settling times for the memory unit were carefully interleaved to optimize the performance and timing during the multiplexing operation. This kept the total number of ADC's, a costly and power dissipative component, to an acceptable minimum.

### I. INTRODUCTION

There are 15,360 signal channels in the Equation of State (EOS) time projection chamber (TPC) detector [1]. To minimize the sheer number of cables which might otherwise be required, multiplexing and digitization is performed directly on the detector before sending information elsewhere for further processing. Low power, high density front end electronics were designed to meet the cooling and space requirements. The switched capacitor array (SCA) analog memory integrated circuit helped meet these objectives. The SCA is described in reference 2. This paper describes the SCA operation and multiplexing scheme employed to meet our design goals.

### II. SCA TIMING OPERATION

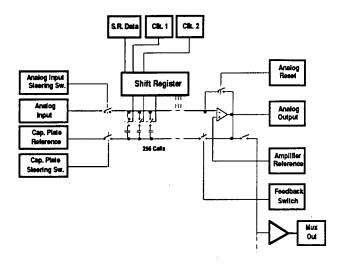

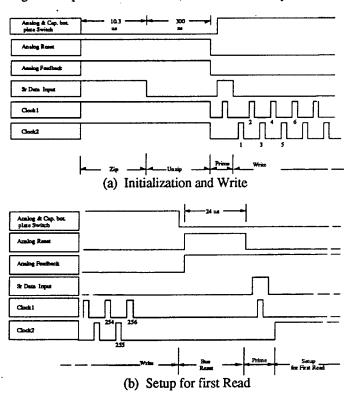

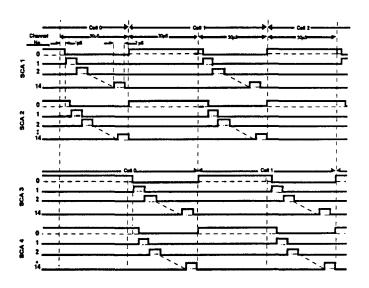

A simplified block diagram Fig. 1 shows 1 of 16 memory banks driven by common internal logic circuits. There are three phases of operation for each data acquisition cycle: 1) initialization, 2) write, and 3) read. Figs. 2(a) and (b) shows a simplified timing diagram for one acquisition cycle.

### A. Initialization

Dynamic shift registers are used as pointers to select individual memory cells in the SCA, but they do not retain their pointing capabilities except for a short time. Due to the nature of dynamic shift registers, keeping the capacitor memories in the shift register in a known state while waiting for an event trigger requires "zipping", a 300 ns operation which turns on all switches to all memory cells. Zipping is accomplished by holding both Clk-1 and Clk-2 high while holding the shift register data input high. All memory cell

Fig. 1 Simpilfied SCA Circuit, one of 16 memory banks.

Figs. 2 (a,b) Simplified SCA timing diagram (waveform timebase not drawn to scale)

capacitors are then reset to zero by having turned on the analog reset and feedback switches. This requires an additional 10  $\mu s$  for all capacitors to fully discharge. Thus, a 10.3  $\mu s$  minimum holdoff time is required after an abort or a write cycle followed by a readout cycle. All during the above operation, the SCA analog input and capacitor bottom plate switches are opened.

### B. Write

Upon the arrival of an event trigger, an "unzipping" period of 300 ns is required before the analog reset and analog feedback switches are opened prior to a write cycle. Unzipping restores all bits to "zero" state at all locations in the shift register. This is accomplished by holding both Clk-1 and Clk-2 high while holding the shift register data input low.

The analog input and capacitor bottom plate switches are then closed. A "prime" bit which brackets the Clk-1 pulse loads the dynamic shift register with a "one" in the first bit in the shift register. Set-up and hold requirements must be observed. The first cell is written into on the following Clk-2 pulse.

An additional 128 pulses for both Clk-1 and Clk-2 are required during write to run the prime bit off the end of the shift register after the prime bit is introduced. Clk-1 and Clk-2 are interleaved to produce a total of 256 additional clock pulses. This procedure is necessary to guarantee that no "ones" are left in the shift register or else two cells could be addressed simultaneously during readout which will give erroneous results.

### C. Read

After writing in data, the analog input and capacitor bottom plate switches are opened. The analog reset switch on the SCA output op-amp of each individual channel is closed for a 24  $\mu s$  period in order to insure that the op-amp output is driven to a known voltage, i.e. Vref. This minimizes the possibility of a negatively charged capacitor from being driven into the substrate. The feedback switch can now be closed and the analog reset switch opened to start the readout cycle. A "prime" bit which brackets the Clk-1 pulse is loaded into the shift register to initiate a pointer to commutate each memory cell to the output amplifier.

After each cell is read, the analog reset switch is turned on to discharge the capacitor and restore the common analog input line to the reference voltage. Clk-1 and Clk-2 continue to toggle until all memory is read.

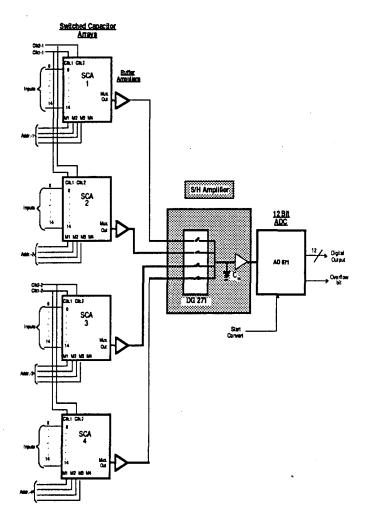

### III. 60 CHANNEL MULTIPLEX MODULE

The simplified block diagram in Fig. 3 shows a basic 60 channel multiplex module consisting of four SCAs each buffered by an output amplifier, a sample and hold circuit, and a 12 bit ADC, an AD671. Only 15 of the 16 available analog channels are used from each SCA, making a total of 60 channels per module.

There are 256 identical modules in the system all logically driven in parallel. Simplified timing diagram of a 60 channel multiplex module is shown in Fig. 4.

A general description of the multiplexing sequence as used in the EOS TPC system is as follows.

Fig. 3 Simplified block diagram of a 60 channel SCA multiplex module.

Fig. 4 Simplified timing diagram of a 60 channel SCA multiplex module.

SCA1 and SCA2 are alternately sampled in 1  $\mu$ s periods until all 15 channels of each SCA have been digitized. This operation takes 30  $\mu$ s. Multiplexing is then performed on SCA3 and SCA4 in the same manner. In the same time frame that SCA3 and SCA4 are sampled and digitized, SCA1 and SCA2 shift new analog data to their respective outputs. This overlapping process allows 30  $\mu$ s for the individual SCA output amplifiers to settle before their next sampling. Toggling between pairs of SCAs continues until all of the memory cells have been processed.

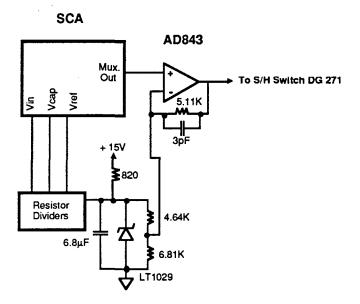

Figure 5 shows in detail the circuit of an SCA output buffer amplifier. The AD843 op-amp provides a voltage gain of 2.8 for full scale drive to the ADC, low impedance drive to the sample and hold switch, and compensation for SCA output offset. LT1029 provides a high stability voltage reference source to the input buffer amplifier and the associated SCA.

Fig. 5 SCA output buffer amplifier.

### IV. PERFORMANCE RESULTS

An SCA test stand was constructed incorporating the multiplex ADC circuit design, and checked out successfully. Test measurements can be made accurately at the full 12 bit resolution of the ADC.

Digital data from the test stand is transmitted to a Macintosh computer via CAMAC interface. There, the raw data is stored in a permanent file and then processed for display or print out.

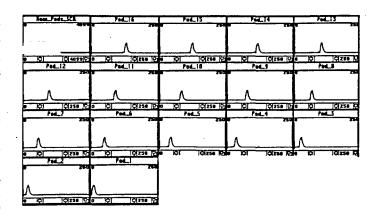

The test stand was used to test production SCAs to select the approximately 1150 devices needed for the system. Critical parameters of each SCA are tested and resultant data stored for analysis at a later time. Sample printouts from SCA tests are shown in the following figures.

Figure 6 shows in a single window all 16 channel outputs of an SCA labeled Pad\_1 through Pad\_16. Input test pulses are shown staggered in time in each SCA channel to measure the amount of crosstalk. The Raw\_Pads window shows the interleaved data just as it is serially transmitted by the test stand.

Fig. 6 SCA crosstalk test

Figure 7 shows a single window display of Pad\_16. Under progam control, any portion of the waveform may be selected and expanded for finer analysis.

Fig. 7 Pad\_16 expanded view.

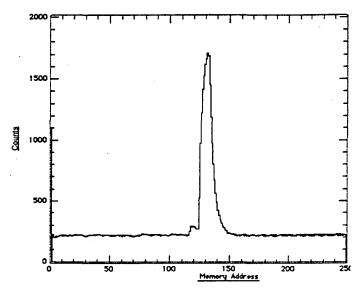

Figure. 8 shows a typical SCA baseline odd-even amplitude of approximately 15 counts peak to peak. Anomalies in cells can be quickly seen and studied.

Fig. 8 SCA baseline odd-even cell amplitude

Operating at a signal sampling frequency of 10 MHz, performance results of the SCA multiplex ADC circuit met design objectives. The circuit does not introduce significant noise or signal distortion. The multiplex scheme achieved a conversion rate of 1 MHz per ADC for a total of 256 MHz system conversion rate.

#### VI. ACKNOWLEDGEMENTS

Technical assistance of H.K. Chen, J.B. Hunter, G.D. Snyder and A. Rudge of U.C. Davis is gratefully acknowledged

This work was supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Division of Nuclear Physics of the U.S. Department of Energy under Contract DE-AC03-76SF00098. Reference to a company or product name does not imply approval or recommendation of the product by the University or the U.S. Department of Energy to the exclusion of others that may be suitable.

#### VII. REFERENCES

- [1] G. Rai, et al, "A TPC Detector for the Study of High Multiplicity Heavy Ion Collisions", IEEE Trans. Nucl. Sci., NS-37, No. 2, pp 56-64, April 1990.

- [2] S.A. Kleinfelder, "A 4096 Cell Switched Capacitor Analog Waveform Storage Integrated Circuit", IEEE Trans. Nucl. Sci., NS-37, No. 3, pp 1230-1236, June 1990.

LAWRENCE BERKELEY LABORATORY

TECHNICAL INFORMATION DEPARTMENT

1 CYCLOTRON ROAD

BERKELEY, CALIFORNIA 94720