### **UC Santa Barbara**

#### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

High Speed Integrated Circuits for High Speed Coherent Optical Communications

#### **Permalink**

https://escholarship.org/uc/item/9269m6g9

#### **Author**

Park, Hyun-chul

#### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY of CALIFORNIA Santa Barbara

### High Speed Integrated Circuits for High Speed Coherent Optical Communications

A Dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Hyun-chul Park

#### Committee in Charge:

Professor Mark J. W. Rodwell, Chair Professor Larry A. Coldren Professor John E. Bowers Professor Luke Theogarajan

September 2014

| The Dissertation of Hyun-chul Park is approved. |

|-------------------------------------------------|

|                                                 |

|                                                 |

|                                                 |

| Professor Larry A. Coldren                      |

|                                                 |

|                                                 |

| Professor John E. Bowers                        |

|                                                 |

|                                                 |

| Professor Luke Theogarajan                      |

|                                                 |

|                                                 |

| Professor Mark J. W. Rodwell, Committee Chair   |

# High Speed Integrated Circuits for High Speed Coherent Optical Communications

Copyright © 2014

by

Hyun-chul Park

This dissertation is dedicated to my parents for their love and support.

#### Acknowledgements

First of all, I would like to thank my advisor, Prof. Mark Rodwell for bringing me into your group and for allowing me to do research in various IC designs and optical communication systems. Four years of research under his guidance were very rewarding and I have learned many essential lessons from him, including a huge amount of passion toward research, how to properly approach research problems, the importance of hard- work, and his warm heart for students. Also I have been very grateful for his patience with my English skills. I would also like to thank Prof. Larry Coldren. He was like my co-advisor. It has been really great to see and meet him in PICO meetings every week and to have gotten so much encouragement and advice for PICO related work. I would like to thank Prof. John Bowers for giving me much encouragement for our OPLL and WDM work and for support for the WDM receiver work with Molly. Additionally, I am grateful for being allowed to use the facilities from his group for many tests. I would like to thank Prof. Luke Theogarajan. It was always pleasure when I met him in his office and outside from time to time. I still cannot forget his comment "I believe that you are doing so well." It was very motivating for me.

I would like to thank our PICO team members. Without the PICO team and our collaborations, none of the system demonstrations in this dissertation could be achieved. Mingzhi, Eli and I were one team for optical phase locked loop (OPLL) designs, and Mingzhi's PIC and Eli's EIC were key blocks for the OPLL working. It was a pleasure to work with Mingzhi all night and even weekends to make OPLLs and their experiments. I will never forget the first time the OPLL worked. In spite of the long distance to Israel, Eli's guidance for the EIC

was essential for our OPLL experiments. Without Molly's guidance and help for WDM system demonstrations, including the Matlab code, none of WDM receiver demonstrations could be achieved. I have learned a lot about digital coherent communications from her. I was very happy to support Abi's laser linewidth narrowing and John's OPLLs to a comb. Especially, Abi, I appreciate for the many English corrections in my thesis. I would like to give a special thanks to Leif for his help and suggestions for the PICO work. He was a mentor for us, and he always provides many solutions when we had issues and problems in our works.

For four years, it was a pleasure to do research and study with the Rodwell group members. For the circuit members, Thomas, Saeid, Seongkyun, Munkyo and Eli, it was always great to discuss and talk of many circuit designs whenever I needed to breakthrough many issues. For the device members, Johann, Han-Wei, Sanghoon, Prateek, Cheng-Ying, Rob (will be one of the circuit members), Andy, Jeremy, Doron, Zach and Miguel, you always gave me answers for my curiosity and questions. I would like to especially thank Johann for his volunteer work on our Linux servers for our IC designs. I would like to thank all UCSB colleagues in the Coldren, Bowers, Theogarajan, Blumenthal, Dagil and Mishra groups. All of my photonics knowledge, components, systems and experiments were from their help, discussions and chats. I would like to thank all Korean student associations (KSA). We had a lot of fun together and also motivated each other.

I would like to thank Professor Youngoo Yang, who was my M.S. advisor, for his strong encouragement and support for my studying in US. I also would like to thank Professor Byung-sung Kim, who was my B.S. advisor, for his circuits and microwave lectures, and strong recommendation to UCSB. I would like to thank my SKKU MCS group members, SKKU-02 friends and Fireballs members as close colleagues and friends. I would like to thank Kwang-ho, Kijin, and Taeho (KETI members) for their big support, encouragement and tears while I was in deep depression. I also would like to thank our visiting scholar Jeong-hoon and In-young from South Korea.

Finally, I would like to thank my family, parents Munsoo Park and Youngsuk Shim, and grand-father Sunchul Park, for raising me and supporting me until this moment. Without their big love and support, I would not have been able to study my Ph.D. in US and finish it successfully. Dearest Kyuhee Kim, thanks for her love and patience.

But He knows the way that I take; when He has tested me, I will come forth as gold. -Jobs 23:10

#### Curriculum Vitæ Hyun-chul Park

#### Personal

Oct. 26, 1980 Born in Seoul, Republic of Korea.

#### Education

2014 Ph.D. in Electrical and Computer Engineering, University of California, Santa Barbara.

2008 M.S. in Electrical and Computer Engineering, Sungkyunkwan University.

University.

2008 B.S. in Information and Communication Engineering, Sungkyunkwan

University.

#### Awards

2014 2nd Place Award, Student Paper Competition

2014 IEEE MTT-S Int. Microwave Symp., Tampa Bay, FL, Jun.

1-6, 2014.

2011 Marquis Who's and Who

in the World 28th Edition, 2011.

2009 The Best Enthusiastic New Employee Award

LG Electronic Inc. Aug. 2009.

2008 Outstanding Paper Award

School of Information and Communication Engineering, Sungkyun-

wan University, Jan. 2008.

2007 The Best Research Award

School of Information and Communication Engineering, Sungkyun-

wan University, Feb. 2007.

2006 Outstanding Achievement Award, 2nd and 3rd Ranked, Student

Design Competition

2006 IEEE MTT-S Int. Microwave Symp., San Francisco, CA,

Jun. 11-16, 2006.

#### **Publications**

[1] **H. Park**, S. Daneshgar, Z. Griffith, M. Urteaga, B. Kim, and M. Rodwell, "Millimeter-Wave Series Power Combining Using Sub-quarter-wavelength Baluns," Solid-State Circuits, IEEE Journal of, vol., no.99, pp.1, 2014.

- [2] **H. Park**, S. Daneshgar, J. C. Rode, Z. Griffith, M. Urteaga, B. Kim, and M. Rodwell, "An 81 GHz, 470 mW, 1.1 mm2 InP HBT Power Amplifier with 4:1 Series Power Combining using Sub-quarter-wavelength Baluns," Microwave Symposium (IMS), 2014 IEEE MTT-S International, pp.1-4, 2014.

- [3] **H. Park**, M. Piels, M. Lu, E. Bloch, A. Sivanathan, Z. Griffith, L. Johansson, J. Bowers, L. Coldren, and M. Rodwell, "Flexible, compact WDM receivers using cascaded optical and electrical," Optics Express, Vol. 22, Issue 1, pp. 102-109 2014.

- [4] **H. Park**, S. Daneshgar, J. C. Rode, Z. Griffith, M. Urteagar, B. Kim, and M. Rodwell, "30% PAE W-band InP Power Amplifiers using Sub-quarter-wavelength Baluns for Series-connected Power-combining," CSICS, 2013 IEEE breaking news, pp. 1-4, Monterey, CA, 2013.

- [5] (Invited) H. Park, S. Daneshgar, J. C. Rode, Z. Griffith, M. Urteagar, B. Kim, and M. Rodwell, "Power Amplifiers using Sub-quarter-wavelength Baluns for Series-connected Power-combining," 013 Topical Symposium on Power Amplifiers for Wireless Communications (PAWC), San Diego, CA, 2013.

- [6] H. Park, M. Piels, E. Bloch, M. Lu, A. Sivanathan, Z. Griffith, L. Johansson, J. Bowers, L. Coldren, and M. Rodwell, "Integrated Circuits for Wavelength Division De-multiplexing in the Electrical Domain," ECOC 2013, London, UK, 2013.

- [7] **H. Park**, M. Lu, E. Block, T. Reed, Z. Griffith, L. Johansson, L. Coldren, and M. Rodwell, "40Gbit/s Coherent Optical Receiver Using a Costas Loop," Optics Express Vol. 20, Issue 26, pp. B197-203, Dec., 2012.

- [8] **H. Park**, M. Lu, E. Bloch, T. Reed, Z. Griffith, L. Johansson, L. Coldren, and M. Rodwell, "40Gbit/s Coherent Optical Receiver Using a Costas Loop," ECOC2012 conference, post-deadline, 2012.

- [9] H. Park, S. Jung, K. Lim, M. Kim, H. Kim, C. Park, and Y. Yang, "Analysis and Design of Compact Third-Order Intermodulation Generation Circuits," Microwave and Optical Technology Letters, vol. 51, no. 9, pp. 2137-2140, Sep. 2009.

- [10] H. Park, J. Van, S. Jung, M. Kim, H. Cho, S. Kwon, J. Jeong, K. Lim, C. Park, and Y. Yang, "A new compact load network for Doherty amplifiers using an imperfect quarter-wave line," IEEE Trans. Microwave Theory Tech., vol. 55, no. 11, pp. 2313-2319, Nov. 2007.

- [11] **H. Park**, G. Ahn, S. Jung, C. Park, W. Nah, B. Kim, and Y. Yang, "High-Efficiency Class-F Amplifier Design in the Presence of Internal Parasitic

- Components of Transistors," 36th European Microwave Conference Dig., vol. 1, pp. 184-187, Sep. 2006.

- [12] (Invited) M. Rodwell, H. Park, M. Piels, D. M. Lu, Elias, A, A. Sivinathan, E. bloch, Z. Griffith, L. Johansson, J. E. Bowers, and L. A. Coldren, "Phase-Locked Coherent Optical Interconnects for Data Links," IEEE Optical Interconnects Conference, May, 4-7, 2014

- [13] S. Daneshgar, **H. Park**, Z. Griffith, M. Urteaga, B. Kim, and M. Rodwell, "High Efficiency W-band Power Amplifiers using Ring-Shaped Sub-Quarter-Wavelength Power Combining Technique," Microwave Symposium (IMS), 2014 IEEE MTT-S International, pp.1-4, 2014.

- [14] E. Bloch, H. Park, Z. Griffith, M. Urteaga, D. Ritter, and M. Rodwell, "A 107 GHz 55 dB-Ohm InP Broadband Transimpedance Amplifier IC for High-Speed Optical Communication Links," CSICS, 2013 IEEE, pp. 1-4, Monterey, CA, 2013.

- [15] (Invited) L. Coldren, M. Lu, H. Park, E. Bloch, J. Parker, Z. Griffith, L. Johansson, and M. Rodwell, "New opportunities for optical phase-locked loops in coherent photonics," OSA OFC 2013, OTh3H.5, 2013.

- [16] M. Lu, H. Park, E. Bloch, A. Sivanathan, J. Parker, Z. Griffith, L. Johansson, M. Rodwell, and L. Coldren, "An Integrated 40 Gbit/s Optical Costas Receiver," Lightwave Technology, Journal of , vol.31, no.13, pp.2244,2253, July, 2013.

- [17] M. Lu, H. Park, J. Parker, A. Sivanathan, E. Bloch, L. Johansson, M. Rodwell, and L. Coldren, "Monoloithic Integration of a high speed widely tunable optical coherent receiver," Photonic Technology Letter, vol.25, no.11, pp.1077,1080, June, 2013.

- [18] A. Sivananthan, H. Park, M. Lu, J. Parker, E. Bloch, L. Johansson, M. Rodwell, and L. Coldren, "Integrated Linewidth Reduction of a Tunable SG-DBR Laser," OSA CLEO2013, CTu1L.2. 2013.

- [19] A. Sivananthan, H. Park, M. Lu, J. Parker, E. Bloch, L. Johansson, M. Rodwell, and L. Coldren, "Monolithic linewidth narrowing of a tunable SG-DBR laser," OSA OFC2013, OTh3l.3, 2013.

- [20] M. Lu, H. Park, E. Bloch, A. Sivananthan, J. Parker, Z. Griffith, L. Johansson, M. Rodwell, and L. Coldren, "A Photonic Integrated Circuit for a 40 Gbaud/s Homodyne Receiver Using an Optical Costas Loop," IPC2012 conference, post-deadline, 2012.

- [21] E. Bloch, **H. Park**, M. Lu, T. Reed, Z. Griffith, L. Johansson, L. Coldren, D. Ritter, and M. Rodwell, "A 1-20GHz All-Digital InP HBT Optical Wavelength

- Synthesis IC," IEEE Trans. Microwave Theory and Tech., to be published, 2012.

- [22] M. Lu, **H. Park**, E. Bloch, A. Sivanathan, A. Bhardwaj, Z. Griffith, L. Johansson, M. Rodwell, and L. Coldren, "A Highly Integrated Optical Heterodyne Phase-locked Loop with Phase/frequency Detection," OPTICS EXPRESS, vol. 20, no. 9, Apr. 2012.

- [23] E. Bloch, H. Park, M. Lu, T. Reed, Z. Griffith, L. Johansson, L. Coldren, D. Ritter, and M. Rodwell, "A 1-20 GHz InP HBT Phase-Lock-Loop IC for Optical Wavelength Synthesis," Microwave Symposium (IMS), 2012 IEEE MTT-S International, pp.1-4, 2012.

- [24] J. Parker, M. Lu, H. Park, A. Sivanathan, E. Bloch, Z. Griffith, L. Johansson, M. Rodwell, and L. Coldren, "Highly-Stable Integrated InGaAsP/InP Mode-Locked Laser and Optical Phase-Locked Loop," Photonics Technology Letters, IEEE, vol.25, no.18, pp.1851,1854, Sept.15, 2013.

- [25] M. Lu, A. Bhardwj, A. Sivananthan, L. Johansson, H. Park, E. Bloch, M. Rodwell, and L. Coldren, "A Widely-tunable Integrated Coherent Optical Receiver Using a Phase-Locked Loop," Photonics Conference (PHO), 2011 IEEEE, pp. 769-770, Oct. 2011.

- [26] S. Jung, H. Park, M. Kim, G. Ahn, J. Van, H. Hwangbo, C. Park, S. Park, and Y. Yang, "A New Envelope Predistorter with Envelope Delay Taps for Memory Effect Compensation," IEEE Trans. Microwave Theory Tech., vol. 55, no. 1, pp. Jan. 2007.

- [27] S. Jung, K. Lim, **H. Park**, R. Negra, M. Kim, F. Ghannouchi, and Y. Yang, "A Load Network for Doherty Amplifiers Using an Optimized Impedance Transformer," Microwave and Optical Technology Letters, vol. 51, no. 10, pp. 2502-2504, Oct. 2009.

- [28] K. Lim, G. Ahn, S. Jung, H. Park, M. Kim, J. Van, H. Cho, J. Jeong, C. Park, and Y. Yang, "A 60-W Multicarrier WCDMA Power Amplifier Using an RF Predistorter," IEEE Trans. Circuits and Systems-II., vol. 56, no. 4, pp. 265-269, APRIL. 2009.

- [29] K. Kim, T. Lim, **H. Park**, and K. Ahn, "mm-wave CMOS Colpitts VCO & frequency divider for the 60GHz WPAN," proceedings of the 2009 IEEE 9th Malaysia International Conference on Communications, 15-17pp Dec. 2009.

- [30] S. Jung, Y. Xi, H. Park, S. Kwon, J. Van, K. Lim, M. Kim, H. Cho, J. Jeong, and Y. Yang, "An optimized Doherty power amplifier using an unequal quadrature input splitter," Microwave and Optical Technology Letters, vol. 50, no. 6, pp. 1536-1539, Jun. 2008.

- [31] H. Cho, M. Kim, J. Jeong, J. Van, S. Jung, H. Park, K. Lim, S. Kwon, J. Y. Kim, S. C. Song, C. Park, and Y. Yang, "A high-power Cartesian feedback transmitter including a compact inverted Doherty amplifier," Microwave and Optical Technology Letters, vol. 50, no. 4, pp. 944-946, Apr. 2008.

- [32] J. Van, S. Jung, **H. Park**, M. Kim, H. Cho, J. Jeong, S. Kwon, K. Lim, and Y. Yang, "Efficiency enhancement for power amplifiers using a dynamic bias switching technique," IEE Electronics Letters, vol. 44, no. 5, pp. 356-357, Feb. 2008.

- [33] S. Jung, K. Lim, H. Park, M. Kim, J. Van, J. Jeong, S. Kwon, Y. Xi, H. Cho, R. Negra, F. M. Ghannouchi, and Y. Yang, "Doherty power amplifier with an optimized load network for improved linearity and efficiency," in 2008 First International Symposium on Foundation of Emerging Information Technology Dig., Suwon, Korea, Jan. 31, 2008, pp. 24-28.

- [34] G. Ahn, M. Kim, H. Park, S. Jung, J. Van, H. Cho, S. Kwon, J. Jeong, K. Lim, J. Kim, S. Song, C. Park, and Y. Yang, "Design of a High-Efficiency and High-Power Inverted Doherty Amplifier," IEEE Trans. Microwave Theory Tech., vol. 55, no. 6, pp. 1105-1111, Jun. 2007.

- [35] H. Cho, M. Kim, J. Jeong, J. Van, S. Jung, H. Park, K. Lim, S. Kwon, J. Y. Kim, S. C. Song, C. Park, and Y. Yang, "A 30 W Cartesian feedback transmitter with 40 % efficiency incorporating an inverted Doherty amplifier," in 2007 Asia-Pacific Microwave Conference Proceedings, Bangkok, Thailand, Dec. 2007, pp. 587-590.

- [36] M. Kim, H. Cho, G. Ahn, H. Park, S. Jung, J. Van, J. Jeong, K. Lim, S. Kwon, J. Y. Kim, S. C. Song, C. Park, and Y. Yang, "The efficiency improvement of a compact inverted Doherty amplifier using bias line adjustment," in 2007 Asia-Pacific Microwave Conference Proceedings, Bangkok, Thailand, Dec. 2007, pp. 583-586.

- [37] G. Ahn, S. Jung, S. Kwon, K. Lim, J. Jeong, J. Van, M. Kim, H. Park, C. Park, S. Park, J. Kim, and Y. Yang, "A RF Predistorter Using a Delay Mismatch for an Additional IM3 Path," 37th European Microwave Conference Dig., vol. 1, pp. 52-55, Oct. 2007.

- [38] M. Rodwell, H. Park, M. Piels, L. Johannson, "A Single-chip Multi-channel WDM Receiver," invention disclosure, 2013.

- [39] Y. Yang, **H. Park**, and S. Jung, "Doherty Amplifier," US patent, published, 7663434.

- [40] Y. Yang, Y. Xi, H. Park, and S. Kwon, "Harmonic Turned Doherty Amplifier," US patent, published, 7646248

#### Abstract

High Speed Integrated Circuits for High Speed Coherent Optical

Communications

by

#### Hyun-chul Park

With the development of (sub) THz transistor technologies, high speed integrated circuits up to sub-THz frequencies are now feasible. These high speed and wide bandwidth ICs can improve the performance of optical components, coherent optical fiber communication, and imaging systems. In current optical systems, electrical ICs are used primarily as driving amplifiers for optical modulators, and in receiver chains including TIAs, AGCs, LPFs, ADCs and DSPs. However, there are numerous potential applications in optics using high speed ICs, and different approaches may be required for more efficient, compact and flexible optical systems.

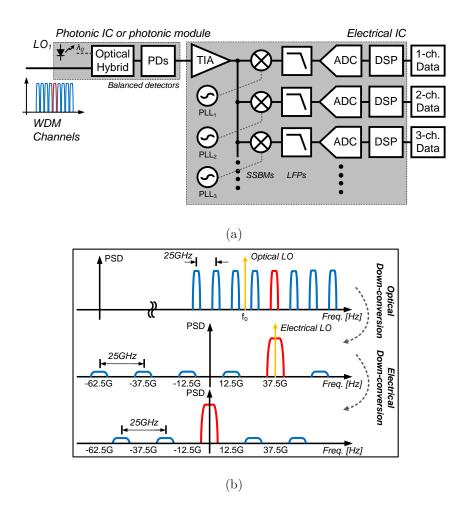

This dissertation will discuss three different approaches for optical components and communication systems using high speed ICs: a homodyne optical phase locked loop (OPLL), a heterodyne OPLL, and a new WDM receiver architecture.

The homodyne OPLL receiver is designed for short-link optical communication systems using coherent modulation for high spectral efficiency. The phase-locked coherent receiver can recover the transmitted data without requiring complex back-end digital signal processing to recover the phase of the received optical carrier. The main components of the homodyne OPLL are a photonic IC (PIC), an

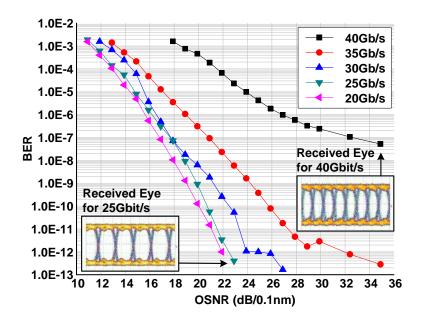

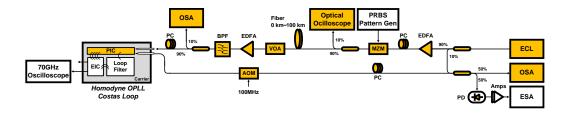

electrical IC (EIC), and a loop filter. One major challenge in OPLL development is loop bandwidth; this must be of order 1 GHz in order for the loop to adequately track and suppress the phase fluctuations of the locked laser, yet a 1 GHz loop bandwidth demands small (<100 ps) propagation delays if the loop is to be stable. Monolithic integration of the high-speed loop components into one electrical and one photonic IC decreases the total loop delay. We have designed and demonstrated an OPLL with a compact size of  $10 \times 10 \ mm^2$ , stably operating with a loop bandwidth of 1.1 GHz, a loop delay of 120 ps, a pull-in time of 0.55  $\mu$ s and lock time of <10 ns. The coherent receiver can receive 40 Gb/s BPSK data with a bit error rate (BER) of <  $10^{-7}$ , and operates up to 35 Gb/s with BER <  $10^{-12}$ .

The thesis also describes heterodyne OPLLs. These can be used to synthesize optical wavelengths of a broad bandwidth (optical wavelength synthesis) with narrow linewidth and with fast frequency switching. There are many applications of such narrow linewidth optical signal sources, including low phase noise mm-wave and THz-signal sources, wavelength-division-multiplexed optical transmitters, and coherent imaging and sensor systems. The heterodyne OPLL also has the same stability issues (loop delay and sensitivity) as the homodyne OPLL. In the EIC, a single sideband mixer operating using digital design principles (DSSBM) enables precisely controlled sweeping of the frequency of the locked laser, with control of the sign of the frequency offset. The loop's phase and frequency difference detector (PFD) uses digital design techniques to make the OPLL loop parameters only weakly sensitive to optical signal levels or optical or electrical component gains. The heterodyne OPLL operates stably with a loop bandwidth of 550 MHz and loop delay of <200 ps. An initial OPLL design exhibited optical frequency

(wavelength) synthesis from -6 GHz to -2 GHz and from 2 GHz to 9 GHz. An improved OPLL reached frequency tuning up to 25 GHz. The homodyne OPLL exhibits -110 dBc/Hz phase noise at 10MHz offset and -80 dBc/Hz at 5 kHz offset.

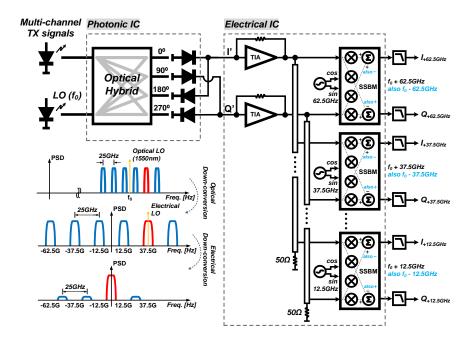

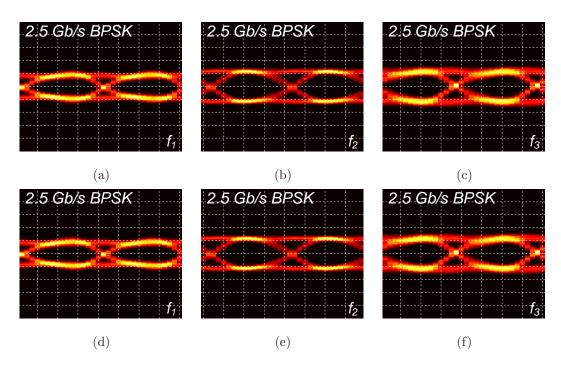

Finally, the thesis describes a new WDM receiver architecture using broadband electrical ICs. In the proposed WDM receiver, a set of received signals at different optical wavelengths are mixed against a single optical local oscillator. This mixing converts the WDM channels to electrical signals in the receiver photocurrent, with each WDM signal being converted to an RF sub-carrier of different frequency. An electrical IC then separately converts each sub-carrier signal to baseband using single-sideband mixers and quadrature local oscillators. The proposed receiver needs less complex hardware than the arrays of wavelength-sensitive receivers now used for WDM, and can readily adjust to changes in the WDM channel frequencies. The proposed WDM receiver concept was demonstrated through several system experiments. Image rejection of greater than 25 dB, adjacent channel suppression of greater than 20 dB, operation with gridless channels, and six-channel data reception at a total 15 Gb/s (2.5 Gb/s BPSK × 6-channels) were demonstrated.

# Contents

| A            | cknov | wledge | ements                                                      | v    |

|--------------|-------|--------|-------------------------------------------------------------|------|

| $\mathbf{C}$ | urric | ulum ' | Vitæ                                                        | viii |

|              |       |        |                                                             | viii |

| A            | bstra | .ct    |                                                             | xiii |

| Li           | st of | Table  | ${f s}$                                                     | xix  |

| Li           | st of | Figur  | es                                                          | xx   |

| 1            | Intr  | oduct  | ion                                                         | 1    |

|              | 1.1   | Backg  | round and motivation                                        | 2    |

|              | 1.2   | Challe | enges and Previous Work                                     | 5    |

|              | 1.3   | Previe | ew of Dissertation                                          | 9    |

|              | Refe  | rences |                                                             | 13   |

| <b>2</b>     | Hig   | h Spe  | ed ICs and Designs                                          | 23   |

|              | 2.1   | Trans  | istor Devices and IC Metal Layers                           | 24   |

|              | 2.2   | Trans  | mission-lines and Broadband Interconnections                | 27   |

|              | 2.3   | High-s | speed Amplifier ICs                                         | 34   |

|              |       | 2.3.1  | Simple $g_m$ -block Amplifier                               | 34   |

|              |       | 2.3.2  | Resistive Feedback Amplifier; In/Output Matching and Band   | _    |

|              |       |        | width Enhancement                                           | 36   |

|              |       | 2.3.3  | Cherry-Hooper $g_m - Z_T$ Amplifier; Broadband Limiting Am- |      |

|              |       |        | plifiers                                                    | 37   |

|              |       | 2.3.4  | Darlington-type Amplifiers                                  | 39   |

|              |       | 2.3.5  | High Frequency ECL-type Circuits                            | 40   |

|              | 2.4   | High-  | Speed ICs for Coherent Optical Communications               | 42   |

|   |      | 2.4.1   | Trans-impedance Amplifiers (TIAs)                             | 43         |

|---|------|---------|---------------------------------------------------------------|------------|

|   |      | 2.4.2   | High-Gain Broadband Limiting Amplifiers                       | 46         |

|   |      | 2.4.3   | Cherry-Hooper Amplifiers                                      | 49         |

|   |      | 2.4.4   | Analog Single-Sideband Mixers                                 | 52         |

|   |      | 2.4.5   | Poly-Phase Filter                                             | 57         |

|   | Refe | erences |                                                               | 60         |

| 3 | Hor  | nodvn   | e OPLLs for Short-Link Optical Communications                 | 65         |

|   | 3.1  |         | ation and Background                                          | 66         |

|   | 3.2  |         | Coherent Receivers Based on Costas Loops                      | 70         |

|   | 3.3  |         | e Characteristics and OPLL Designs                            | 73         |

|   |      | 3.3.1   | Photonic Integrated Circuit                                   | 74         |

|   |      | 3.3.2   | Electrical Integrated Circuit                                 | 82         |

|   |      | 3.3.3   | Hybrid Loop Filter                                            | 91         |

|   | 3.4  | Imple   | mentation and Experimental Results                            | 100        |

|   |      | 3.4.1   | OPLL Integration                                              | 100        |

|   |      | 3.4.2   | Homodyne OPLL Experiments                                     | 102        |

|   |      | 3.4.3   | BPSK Receiver Experiments                                     | 111        |

|   | 3.5  | Conclu  | asion                                                         | 114        |

|   | Refe | erences |                                                               | 116        |

| 4 | Het  | erodyı  | ne OPLLs for Wavelength Synthesis                             | <b>121</b> |

|   | 4.1  |         | ation and Background                                          | 123        |

|   | 4.2  |         | Heterodyne OPLLs and Design Challenges                        | 125        |

|   | 4.3  |         | odyne OPLL Architecture                                       | 128        |

|   |      | 4.3.1   | The Photonic IC                                               | 129        |

|   |      | 4.3.2   | EIC: Digital-Single Sideband Mixers (D-SSBM) and Phase        |            |

|   |      |         | Frequency Detector (PFD) operation                            | 132        |

|   |      | 4.3.3   | Hybrid Loop Filter: Dual-Path (Feed-Forward) Loop Filter      | 144        |

|   | 4.4  | OPLL    | Implementation                                                | 151        |

|   | 4.5  |         | Experiments and Measurement Results                           | 153        |

|   | 4.6  | Conclu  | asion                                                         | 161        |

|   | 4.7  |         | ional Analysis-I: Phase Noise Analysis                        | 162        |

|   | 4.8  | Additi  | ional Analysis-II: Dual-path (Feed-forward) Loop Filter Anal- |            |

|   |      |         |                                                               | 164        |

|   | Refe | erences |                                                               | 168        |

| 5 | Flex | xible C | Compact WDM Receiver                                          | 172        |

|   | 5.1  | Motiva  | ation and Background                                          | 173        |

|   | 5.2  |         | rle-Chin Multi-Channel WDM Receiver Concept                   | 178        |

|   | 5.3  | IC Designs for the Single-Chip 6-Channel WDM Receiver Systems      | 180        |

|---|------|--------------------------------------------------------------------|------------|

|   |      | 5.3.1 Two-channel Receiver IC Designs                              | 180        |

|   |      | 5.3.2 Six-Channel Receiver IC Designs                              | 184        |

|   | 5.4  | System Demonstrations and Experimental Results                     | 188        |

|   |      | 5.4.1 Image Rejection Experiment                                   | 189        |

|   |      | 5.4.2 Adjacent Channel Interference Experiment                     | 193        |

|   |      | 5.4.3 6-Channel Data Reception Experiment                          | 196        |

|   | 5.5  | Conclusion                                                         | 202        |

|   | 5.6  | Additional Analysis-I: RF Sub-Carrier Generations for Circuit Sim- |            |

|   |      | ulations                                                           | 203        |

|   | 5.7  | Additional Analysis-II: Local Oscillator (LO) Laser Power          | 206        |

|   | Refe | erences                                                            | 210        |

| 6 | Sun  | nmary and Future Work                                              | <b>214</b> |

|   | 6.1  | Summary                                                            | 214        |

|   | 6.2  | Future Works                                                       | 216        |

|   |      | 6.2.1 Modified Optical Costas Loop for Higher Bits per Symbol      | 216        |

|   |      | 6.2.2 Polarization Insensitive OPLLs                               | 218        |

|   |      | 6.2.3 Silicon Based Low Power, Compact High Speed IC Designs       | 222        |

|   |      | 6.2.4 Advanced WDM Receiver Concepts                               | 225        |

|   | Refe | rences                                                             | 228        |

# List of Tables

| 3.1 | Summary of the PIC device parameters for the homodyne OPLL                               |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | $\operatorname{design}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 81  |

| 3.2 | Summary of the EIC device parameters for the homodyne OPLL                               |     |

|     | design                                                                                   | 90  |

| 3.3 | Summary of the loop filter parameters for the homodyne OPLL                              |     |

|     | design                                                                                   | 99  |

|     |                                                                                          |     |

| 4.1 | Summary of the PIC device parameters for the heterodyne OPLL                             |     |

|     | design                                                                                   | 132 |

| 4.2 | Summary of the EIC device parameters for the heterodyne OPLL                             |     |

|     | design                                                                                   | 143 |

| 4.3 | Summary of the loop filter parameters for the heterodyne OPLL                            |     |

|     | design                                                                                   | 150 |

# List of Figures

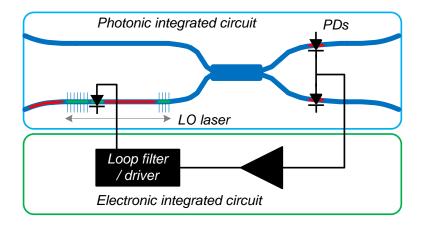

| 1.1<br>1.2 | Conceptual integrated optical phase locked loop (OPLL) schematic.<br>Conceptual WDM receiver schematics for conventional architecture                                                                                                                                                                                                                          | 2   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

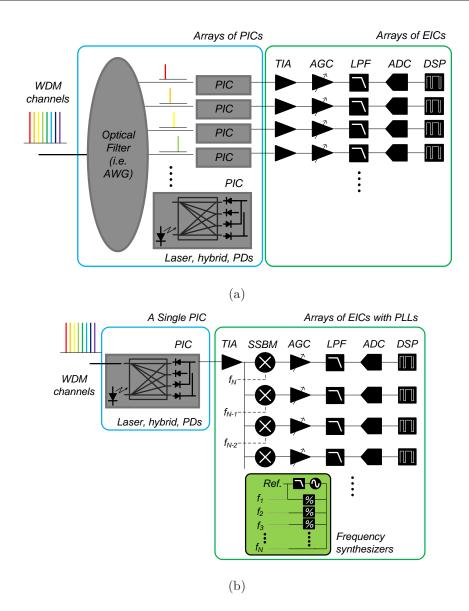

|            | (a) and new proposed WDM receiver architecture (b)                                                                                                                                                                                                                                                                                                             | 4   |

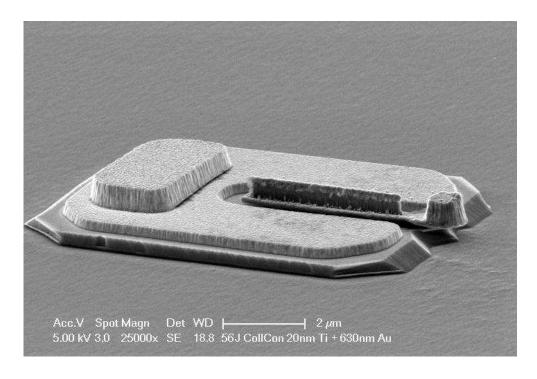

| 2.1        | An SEM image for a THz HBT device from UCSB's facilities ( $L_e = 4 \ \mu m, W_e = 150 \ nm$ , and $W_b = 450 \ nm$ ), image courtesy J. C. Rode.                                                                                                                                                                                                              | 24  |

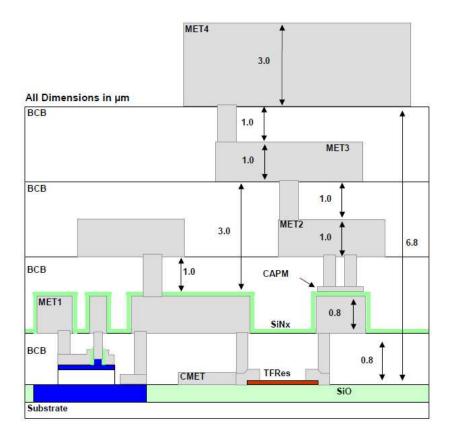

| 2.2        | Metal layer information provided by TSC's 500 nm InP HBT process. Top metal (MET4) of 3 $\mu$ m, MET2-MET3 of 1 $\mu$ m, and bottom metal (MET1) of 0.8 $\mu$ m thickness and a dielectric BCB ( $\epsilon_r = 2.7$ ) separation of 1 $\mu$ m between each metal. Metal-insulator-metal (MiM) capacitors have been supported for high dense capacitance.       |     |

|            | Courtesy of Teledyne Science Company                                                                                                                                                                                                                                                                                                                           | 26  |

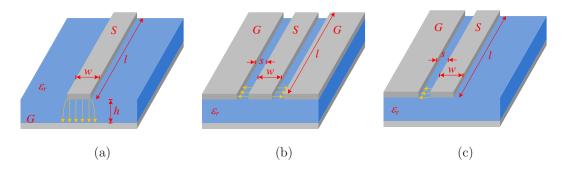

| 2.3        | Three different types of transmission lines in IC designs. Microstrip transmission lines (a), co-planar waveguide (CPW) transmission                                                                                                                                                                                                                           |     |

| 2.4        | lines (b), and slot-type transmission lines (c)                                                                                                                                                                                                                                                                                                                | 27  |

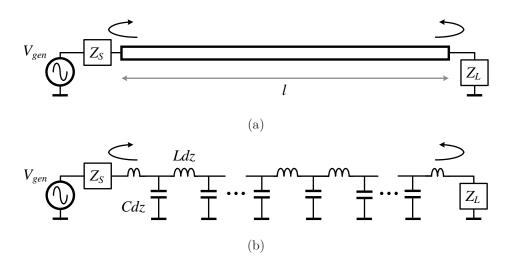

|            | and load impedance, and (b) distributed circuit model using lumped $Ldz$ and $Cdz$ (lossless)                                                                                                                                                                                                                                                                  | 29  |

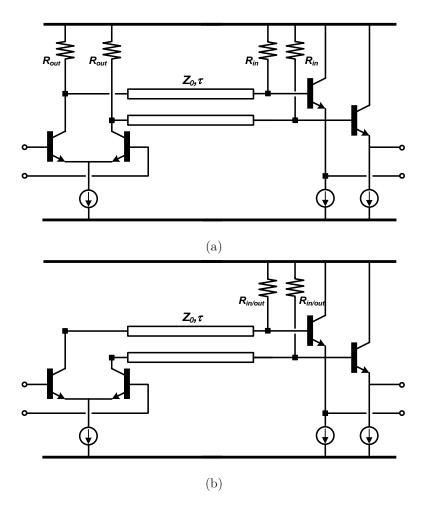

| 2.5        | Circuit-to-circuit interconnection using transmission lines. (a) Double 50 $\Omega$ terminations on the output of the first stage and input of the second stage to minimize reflections and keep high speed interfaces (power consumption is greater than for a single termination), and (b) a single 50 $\Omega$ termination on the input of the second stage | 23  |

|            | only. The reflection occurs in the output of the first stage                                                                                                                                                                                                                                                                                                   | 31  |

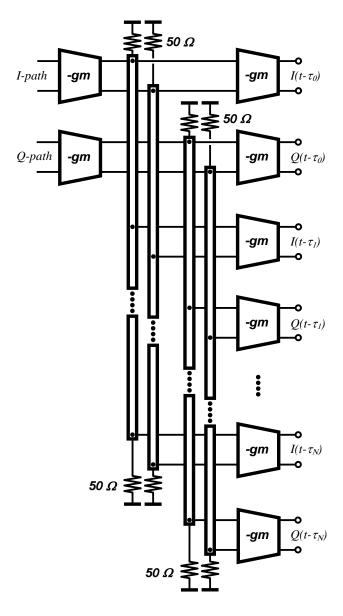

| 2.6        | Bus-type broadband signal distributions using transmission lines.                                                                                                                                                                                                                                                                                              |     |

|            | Two $g_m$ -block outputs are double-terminated at the input of the                                                                                                                                                                                                                                                                                             |     |

|            | first $g_m$ -block and the input of the last $g_m$ -block. The voltage sig-                                                                                                                                                                                                                                                                                    | 0.0 |

|            | nals with different delay are transmitted to each $g_m$ -block                                                                                                                                                                                                                                                                                                 | 33  |

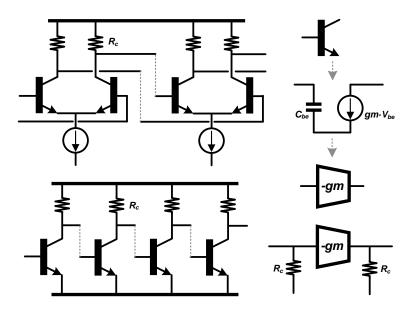

| 2.7  | $g_m$ -block amplifiers: differential-type on the top and single-ended     |    |

|------|----------------------------------------------------------------------------|----|

|      | type on the bottom. In the right section, a bipolar junction transis-      |    |

|      | tor (BJT) has been modelled as a simple trans-conductance $(g_m)$ ,        |    |

|      | a circuit block as a simple block, which are terminated by shunt           |    |

|      | resistors at both the input and output                                     | 34 |

| 2.8  | Resistive feedback amplifiers for broadband input and output ter-          |    |

|      | mination condition and higher $f_{3-dB}$ performance                       | 36 |

| 2.9  | Cherry-Hooper amplifiers for broadband limiting amplifications. It         |    |

|      | consists of a $g_m$ -block at the first stage and a resistive feedback     |    |

|      | block for the second stage                                                 | 37 |

| 2.10 | Darington Amplifiers for $f_{\tau}$ Doublers or voltage level shifters. It |    |

|      | consists of an emitter follower and a $g_m$ -block                         | 39 |

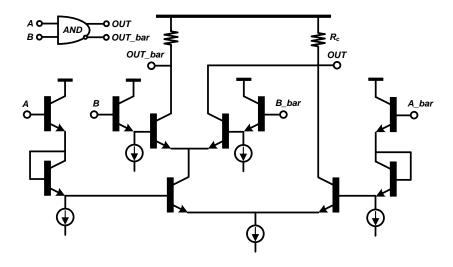

|      | ECL-type AND and NAND gate schematic                                       | 41 |

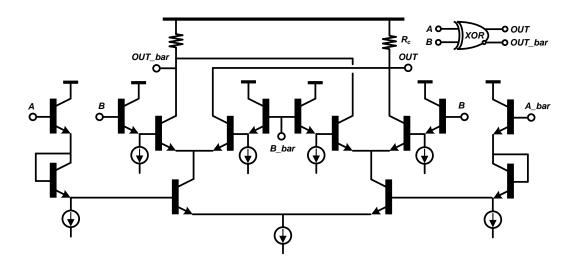

|      | ECL-type XOR gate schematic                                                | 41 |

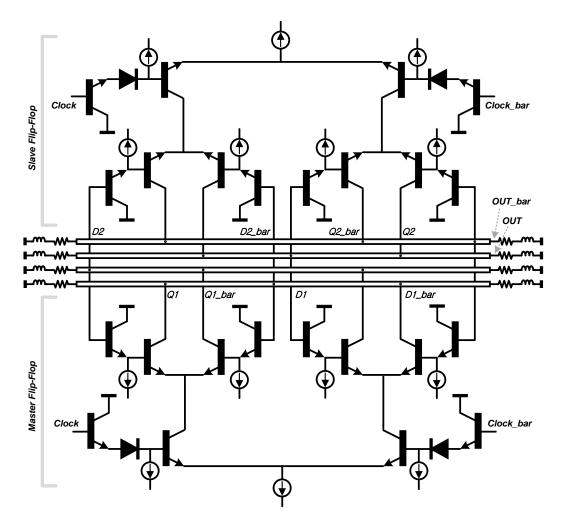

| 2.13 | ECL-type static frequency divider schematic using two flip-flops of        |    |

|      | master and slave and distributed microstrip lines. Courtesy of Z.          |    |

|      | Griffith [27]                                                              | 42 |

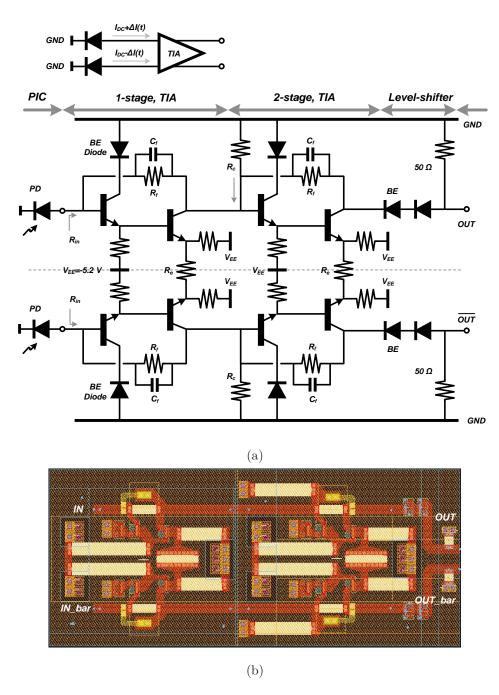

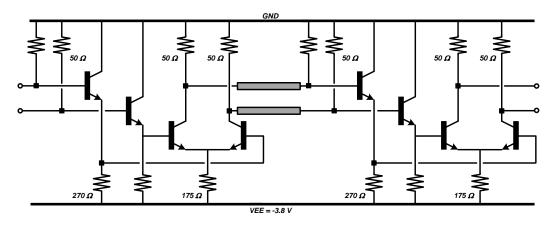

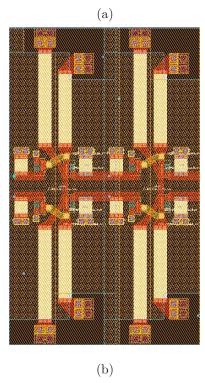

| 2.14 | Designed two-stage differential trans-impedance amplifiers. (a) De-        |    |

|      | tail TIA schematic, and (b) the layouts as a part of the WDM               |    |

|      | receiver IC. Courtesy of E. Bloch [25]                                     | 44 |

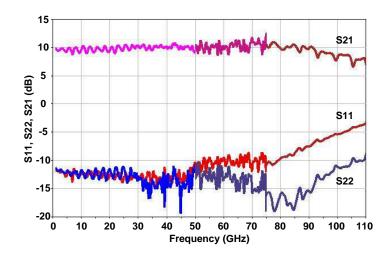

|      | Measured TIA s-parameter results DC-to 110 GHz [25]                        | 45 |

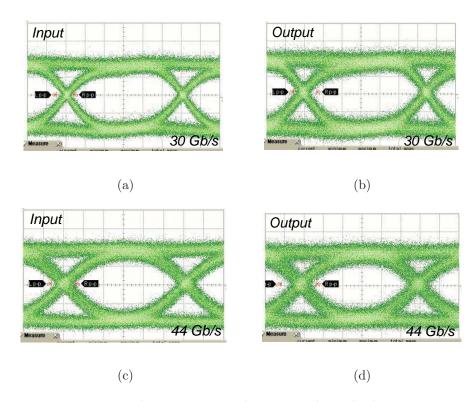

| 2.16 | Measured eye inputs and outputs through the two stage TIA. Data            |    |

|      | PRBS $(2^{31}1)$ modulated signals of 30 Gb/s and 44 Gb/s have been        |    |

|      | used for the measurements [25]                                             | 46 |

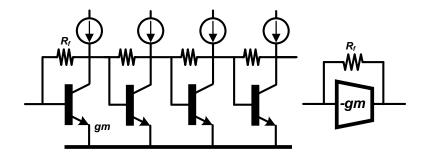

| 2.17 | Two-stage limiting amplifier chains using $g_m$ -blocks and Darlington-    |    |

|      | transistors. (a) Two-stage schematic with double terminated circuit-       |    |

|      | to-circuit interconnections, and (b) its layouts as a part of the ho-      |    |

|      | modyne OPLL IC, heterodyne OPLL IC, and WDM receiver IC.                   | 48 |

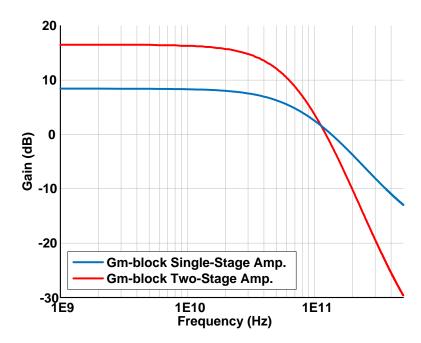

| 2.18 | Simulation results for a single-stage and two-stage $g_m$ -block limiting  |    |

|      | amplifiers. The simulation results show $\sim 8.6$ dB gain with 75 GHz     |    |

|      | $f_{3-dB}$ bandwidth                                                       | 49 |

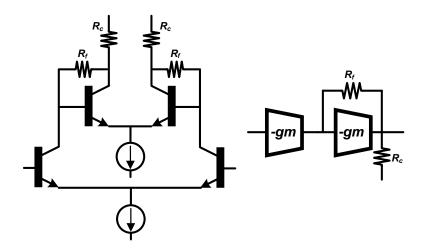

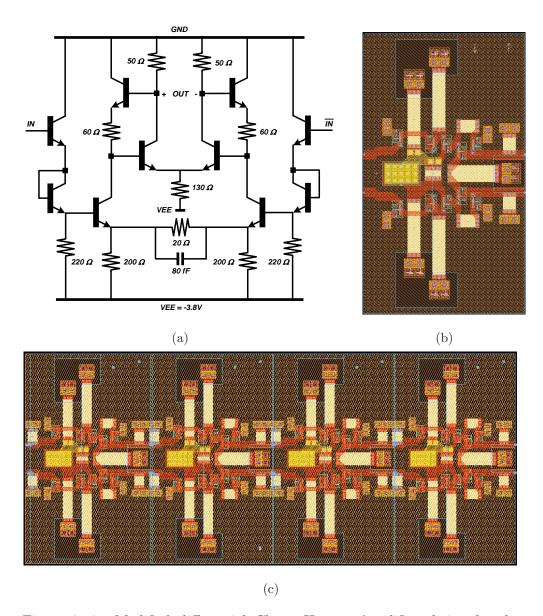

| 2.19 | Modified differential Cherry-Hooper Amplifier chains for the WDM           |    |

|      | receiver LO limiting amplifier paths. (a) A single-stage schematic         |    |

|      | with the degeneration resistor of 20 $\Omega$ with high frequency peaking  |    |

|      | capacitor of 80 fF, (b) a single stage layout, and (C) the layout for      |    |

|      | the four-stage Cherry-Hooper amplifier chains                              | 51 |

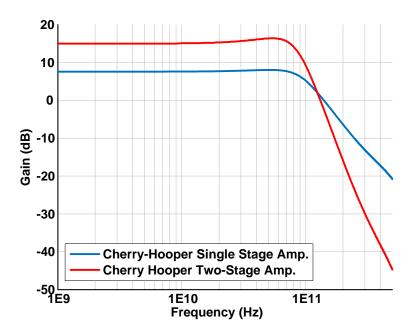

| 2.20 | Simulation results for a single-stage and two-stage Cherry-Hooper          |    |

|      | amplifiers. Bandwidth has been extended because of high frequency          |    |

|      | peaking using the degeneration resistor 20 $\Omega$ with 80 fF capacitor.  | 52 |

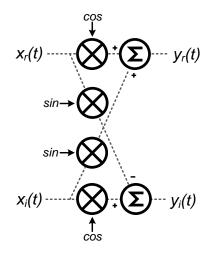

| 2.21 | Weaver-type broadband analog single sideband mixer. Block-level single-sideband mixer architecture using four mixers with sin and                                                                                                                |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | cosin LO signals.                                                                                                                                                                                                                                | 53         |

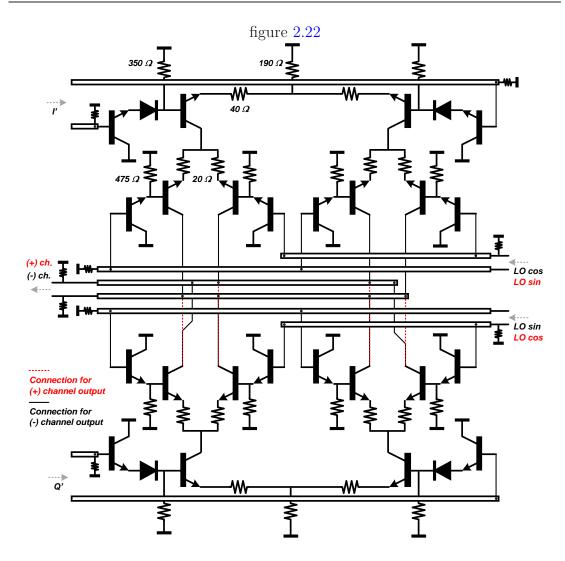

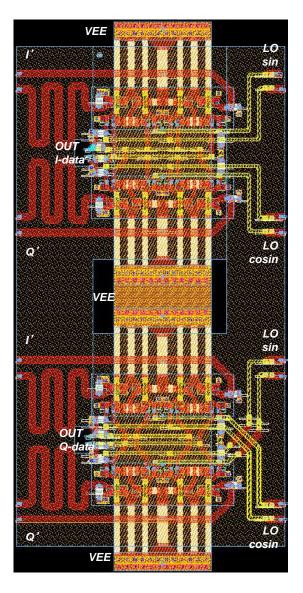

| 2.22 | A schematic for the Weaver-type broadband analog single sideband mixers                                                                                                                                                                          | 55         |

| 2.23 | A layout for the Weaver-type broadband analog single sideband mixers. The upper section is for I-data outputs and the lower section is for Q-data outputs                                                                                        | 56         |

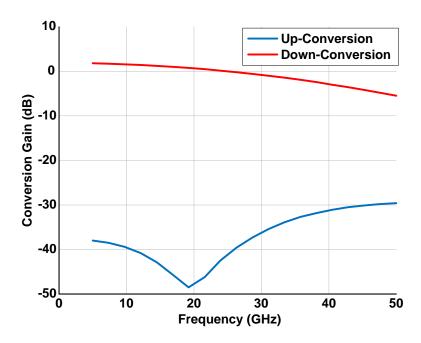

| 2.24 | Simulation of the single sideband suppression ratio. Weaver single sideband mixer as a function of LO frequency. The simulations use EM models for all interconnects                                                                             | 57         |

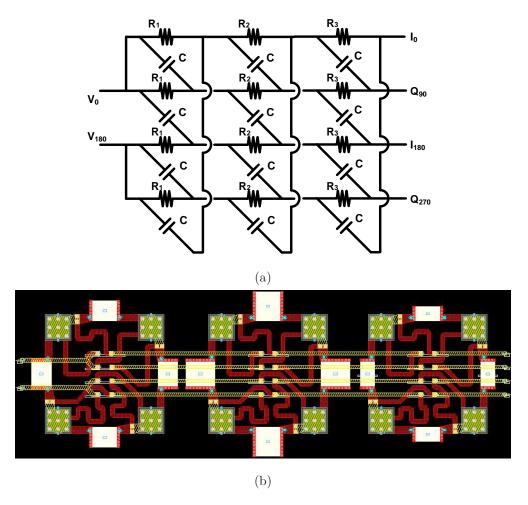

| 2.25 | A three-stage poly-phase filter schematic (a) and layout (b) for quadrature LO signals                                                                                                                                                           | 58         |

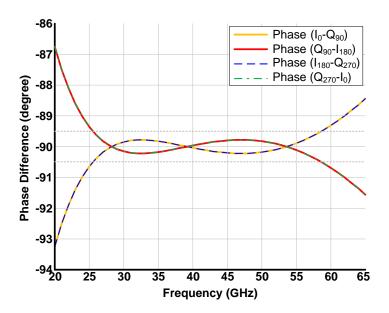

| 2.26 |                                                                                                                                                                                                                                                  | 59         |

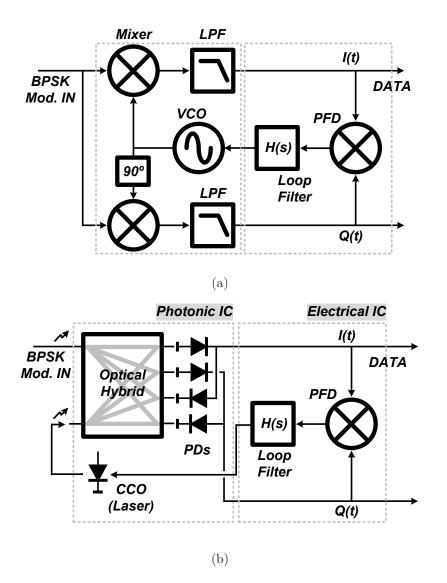

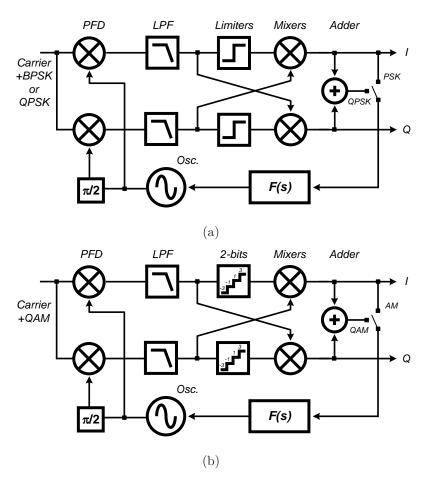

| 3.1  | Costas loop receivers for BPSK modulated signals. The Costas loop using electrical components only (a) and the Costas loop using optical components (hybrid, PDs and laser) and electrical components (mixer as a PFD and loop filter)(b)        | 70         |

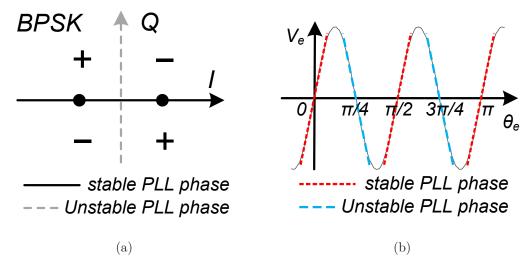

| 3.2  | Stable phase locked loop conditions. The stable conditions of 0 and 180 degrees in the $I-Q$ constellations (a), and the same results with (a) in the sinusoidal plot $sin(2\theta_e)$ of the voltage error $V_e$ vs. phase error $\theta_e$ (b) | 71         |

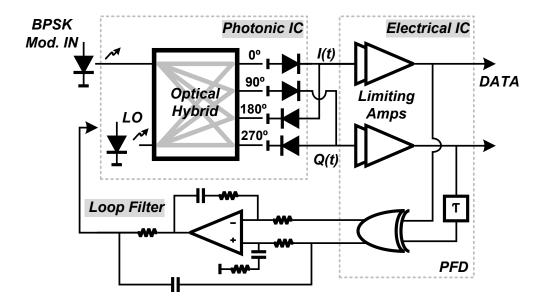

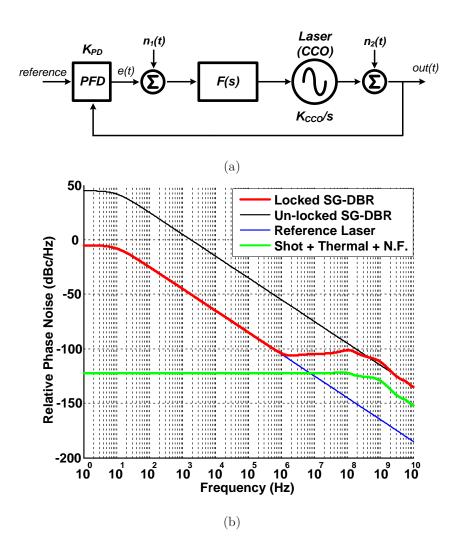

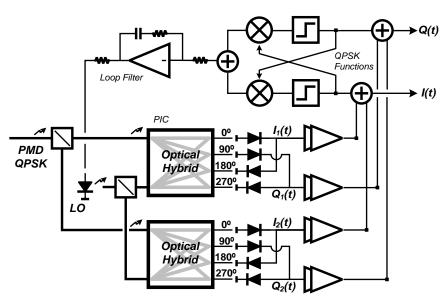

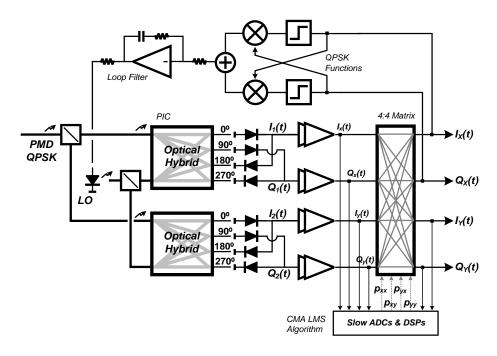

| 3.3  | A concept schematic for a homodyne OPLL structure using a Costas loop which consists of three main parts of the PIC, EIC and loop filter                                                                                                         | 74         |

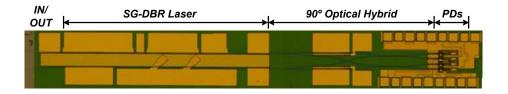

| 3.4  | Photo image for the fabricated PIC in the UCSB facility, courtesy of M. Lu [4, 20]                                                                                                                                                               | 74         |

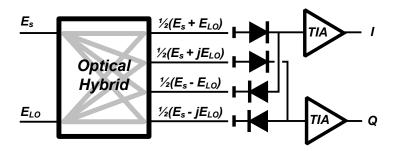

| 3.5  | Balanced detection using the 90 degree optical hybrid, four photo-<br>diodes and electrical trans-impedance amplifiers (TIAs)                                                                                                                    | <b>7</b> 5 |

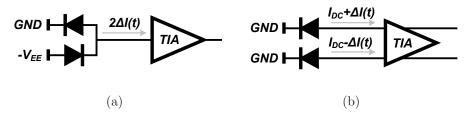

| 3.6  | Two different balanced-types of the photodiode connections with TIAs: (a) balanced PDs and single-ended TIA and (b) single-ended                                                                                                                 |            |

| 3.7  | PDs and differential TIA                                                                                                                                                                                                                         | <b>7</b> 6 |

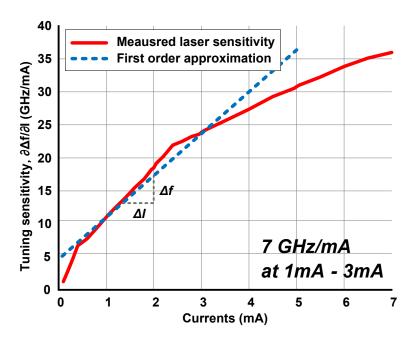

|      | provingation between 1-3 m A bigs ranges courtesy of M Lu                                                                                                                                                                                        | 77         |

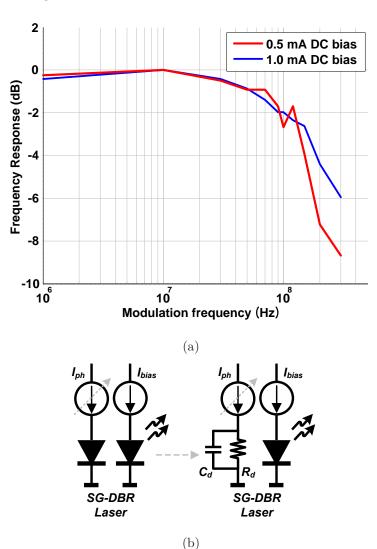

| 3.8  | The frequency response for laser tuning section diode. The mea-                           |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | sured frequency response has a single pole at approximately 100                           |     |

|      | MHz (a). Simple diode $R_d$ and $C_d$ model for the frequency re-                         |     |

|      | sponse $(R_d \sim 10 \Omega \text{ and } C_d \sim 160 \text{ pF})$ (b), courtesy of M. Lu | 78  |

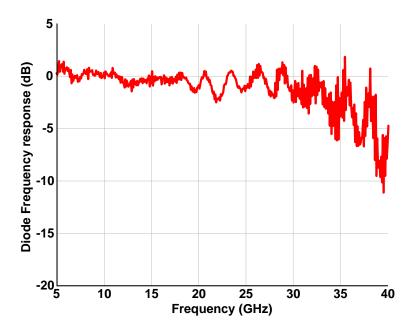

| 3.9  | Measured PD 3-dB bandwidth. More than 30 GHz bandwidth has                                |     |

|      | been achieved. Courtesy of M. Lu [4, 20]                                                  | 79  |

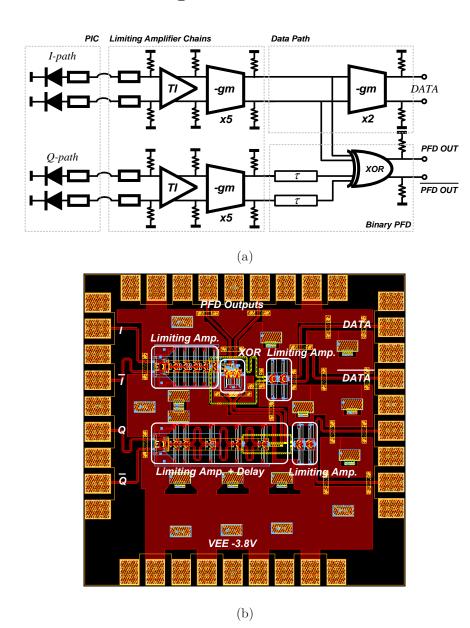

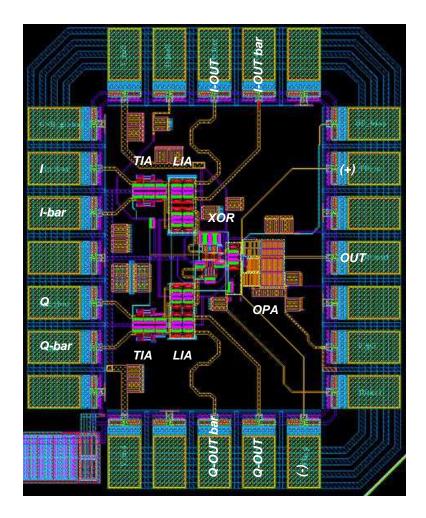

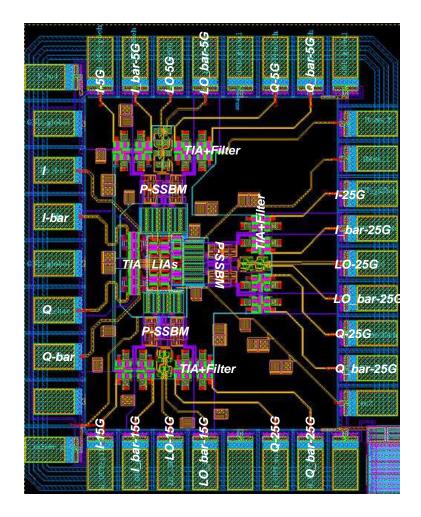

| 3.10 | The EIC schematic (a) and layout (b) for the binary phase and                             |     |

|      | frequency detection with BPSK data outputs. TI: trans-impedance                           |     |

|      | (current to voltage conversion), $g_m$ -blocks as limiting amplifiers,                    |     |

|      | and XOR gate with a delay line for PFD functions, courtesy of E.                          |     |

|      | Bloch and T. Reed [7]                                                                     | 82  |

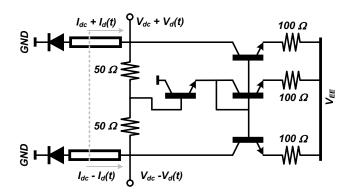

| 3.11 | The biasing circuit to supply $-2 V$ to the single-ended PDs [7].                         | 83  |

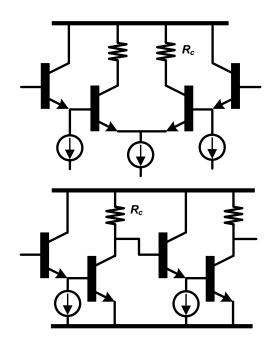

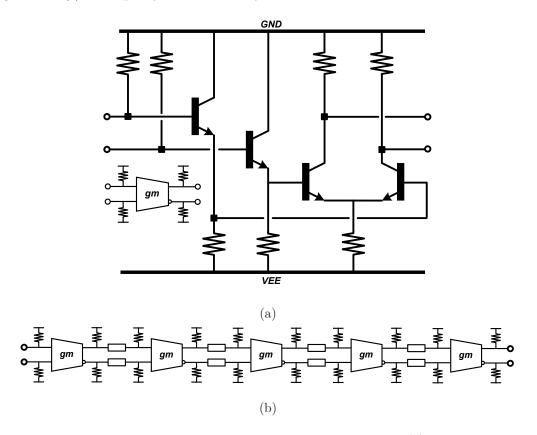

| 3.12 | $g_m$ -block amplifiers for limiting amplifier chains (a) and five-stage                  |     |

|      | limiting amplifier chains (b) [7]                                                         | 84  |

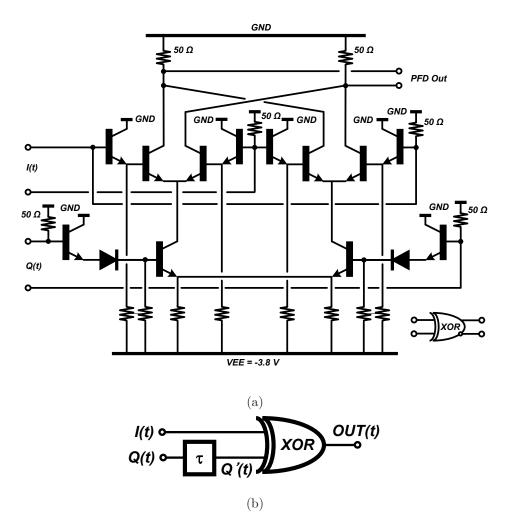

| 3.13 | ECL-XOR gate schematic for the PFD design (a) and Quadri-                                 |     |

|      | correlator PFD structure including the XOR and delay-line (b) [7].                        | 86  |

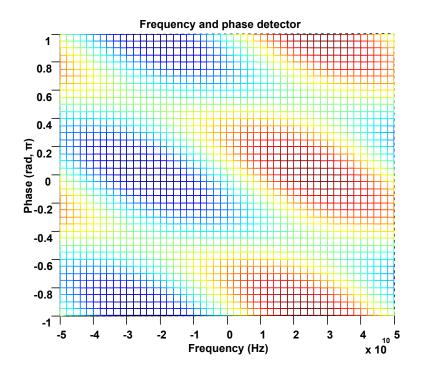

| 3.14 | 3-D frequency and phase detection plot: voltage error vs. frequency                       |     |

|      | (-50 GHz to 50 GHz) and phase (- $\pi$ to $\pi$ ). Dark red corresponds                   |     |

|      | to a 0.5 $V$ output and dark blue to -0.5 $V$ output. Phase detection                     |     |

|      | and frequency detection slopes must have the same sign for negative                       |     |

|      | feedback loop operation                                                                   | 88  |

|      | Measured frequency detection results through the PIC and EIC                              | 89  |

| 3.16 | Dual-path loop filter schematic with low frequency path and high                          |     |

|      | frequency path (a), and the conceptual bode gain plot open loop                           |     |

|      | transfer function $T(s)$ . The feed-forward loop significantly en-                        |     |

|      | hances the loop bandwidth $\omega_{n,FF}$ compared with the conventional                  |     |

|      | loop $\omega_{n,c}$ (b)                                                                   | 94  |

|      | A Bode diagram for the OPLL open loop response $T(s)$                                     | 96  |

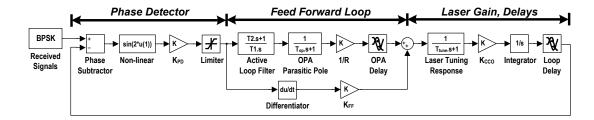

| 3.18 | Matlab Simulink simulation including the binary PFD, laser device                         |     |

|      | characteristics, feed-forward loop filter and the total effective loop                    |     |

|      | delay                                                                                     | 97  |

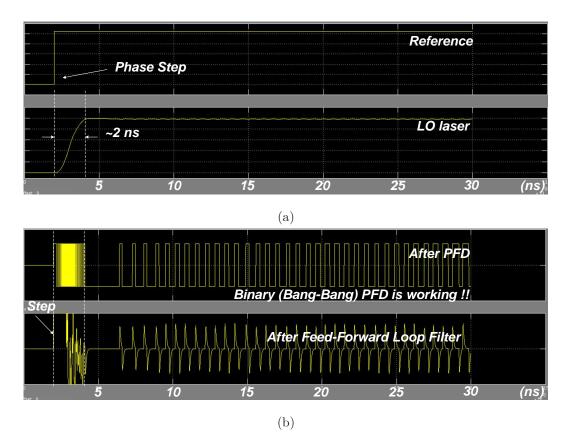

| 3.19 | Matlab Simulink simulation results for the phase step jump. (a)                           |     |

|      | The phase step jump in the reference and the LO laser's phase                             |     |

|      | acquisition through the designed feedback loop, and (b) Binary                            |     |

|      | (bang-bang) PFD output and the modified loop filter output                                | 98  |

| 3.20 | The OPLL hybrid integrations including the PIC, EIC, and hybrid                           |     |

|      | loop filter. Red: short feed-forward path through the single ca-                          |     |

|      | pacitor $C_{FF}$ , yellow: long integrator-path through the commercial                    |     |

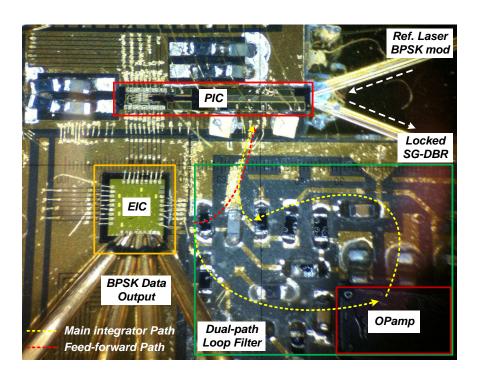

|      | on-amplifier                                                                              | 100 |

| 3.21 | The mask layout, discrete component soldering and wire-bonding locations.                                                                                                                                                                                                                                                                                                                                       | 101 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

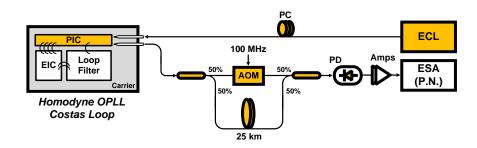

| 3.22 | The test setup for the first homodyne OPLL experiment to measure<br>the beating spectrum between the reference laser and the locked<br>SG-DBR laser. ECL: external cavity laser, PC: phase controller,<br>OSA: optical spectrum analyzer, and AOM: acousto-optical mod-                                                                                                                                         |     |

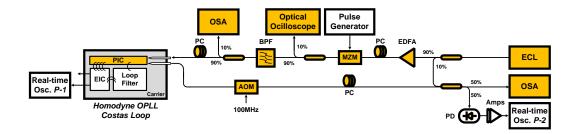

|      | ulator                                                                                                                                                                                                                                                                                                                                                                                                          | 102 |

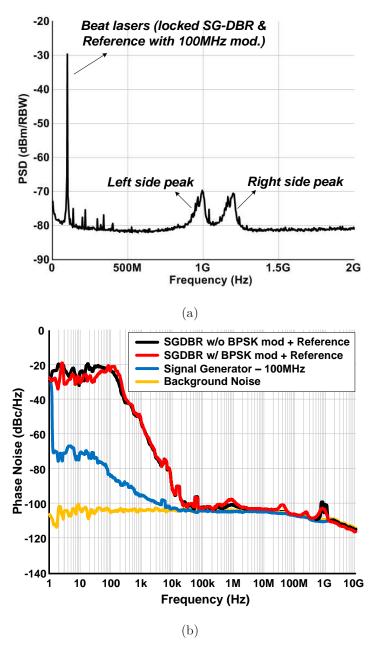

| 3.23 | The homodyne OPLL performance. Beating lasers through the external photodiode to the electrical spectrum analyzer (ESA). Peak tone at 100 MHz and side tones at 1.0 and 1.2 GHz (a). Phase noise performance for the beating lasers and compared with the self-beating reference laser, RF signal phase nosie, and background noise through the amplifiers for the external PD thermal noise and shot noise (b) | 104 |

| 3.24 |                                                                                                                                                                                                                                                                                                                                                                                                                 | 104 |

| 0.24 | periments (self-heterodyne linewidth measurement technique) [46,                                                                                                                                                                                                                                                                                                                                                |     |

|      | 47]                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

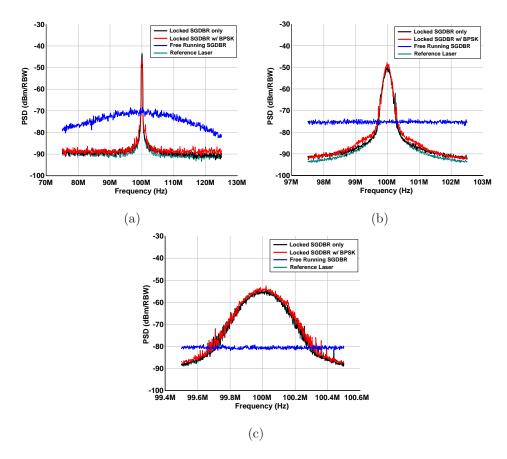

| 3.25 | The homodyne OPLL linewidth measurement experiments. Self heterodyne linewidth measurements for the locked SG=DBR laser (black), locked SG-DBR laser with BPSK modulated input signals (red), free-running SG-DBR laser (blue), and reference laser (green):(a) RBW 20 kHz and span 50 MHz, (b) RBW 10 kHz and                                                                                                  |     |

| 3.26 | span 5 MHz, and (c) RBW 3 kHz and span 1MHz The test setup for the homodyne OPLL closed loop bandwidth                                                                                                                                                                                                                                                                                                          | 105 |

| 0.20 | measurement experiment using the phase modulation                                                                                                                                                                                                                                                                                                                                                               | 106 |

| 3.27 | The homodyne OPLL closed loop bandwidth measurement experiment. Simulated and measured loop bandwidth results are shown                                                                                                                                                                                                                                                                                         |     |

|      | and the results show $\sim 1$ GHz closed loop bandwidth                                                                                                                                                                                                                                                                                                                                                         | 107 |

|      | The test setup for the homodyne OPLL lock time experiments                                                                                                                                                                                                                                                                                                                                                      | 108 |

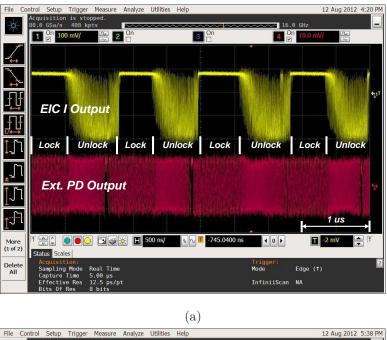

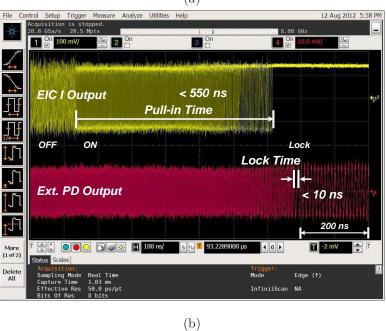

| 3.29 | The homodyne OPLL lock time experiments. (a) Automatic phase lock acquisition monitoring through the real time oscilloscope for the on-off-keying reference input, and (b) pull-in time and lock-time                                                                                                                                                                                                           |     |

|      | monitoring for the worst measurement result                                                                                                                                                                                                                                                                                                                                                                     | 109 |

| 3.30 |                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

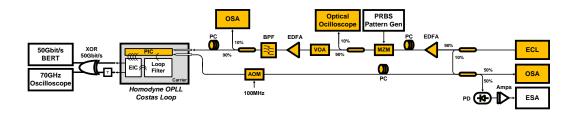

| 3.31 | experiments                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

|      | phase shifters for the differential de-coding                                                                                                                                                                                                                                                                                                                                                                   | 111 |

| 3.32<br>3.33 | The test setup for the homodyne OPLL long-haul data reception experiments for the fiber lengths of 0 km to 100 km and the data rate of 10 Gb/s to 40 Gb/s                                                                                                              | 113          |

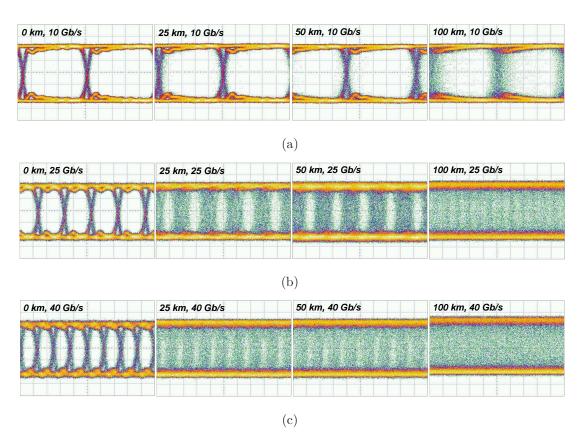

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|              | experiments for the fiber lengths of 0 km - 100 km. (a) 10 Gb/s eye diagrams, (b) 25 Gb/s eye diagrams, and (c) 40 Gb/s eye diagrams.                                                                                                                                  | 113          |

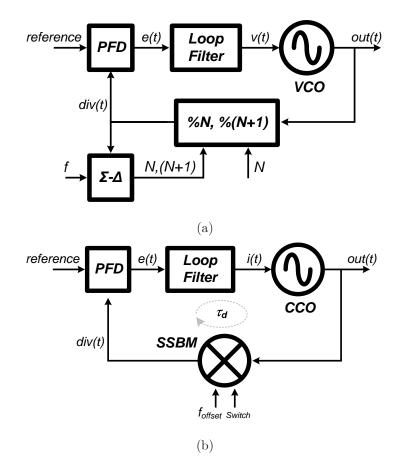

| 4.1          | Block diagrams for frequency synthesizers. An electrical PLL using the fractional-N divider using a sigma-delta modulator (a), and a direction selectable heterodyne optical PLL (OPLL) using a single sideband mixer (SSBM) and an external RF signal (b)             | 123          |

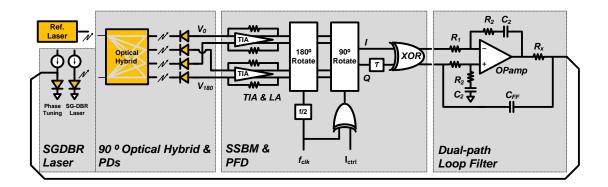

| 4.2          | A full heterodyne OPLL architecture including three main blocks of the PIC, EIC and loop filter. (SG-DBR: sampled grating-distributed Bragg reflector, TIA: trans-impedance amplifiers, LA: limiting amplifiers, SSBM: single side band mixer, and PFD: phase and fre- | 120          |

|              | quency detector)                                                                                                                                                                                                                                                       | 128          |

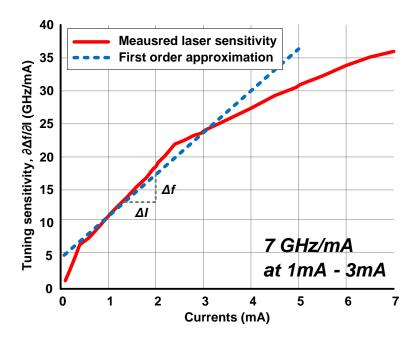

| 4.3          | Measured SG-DBR laser tuning sensitivity of 7 GHz/ $mA$ ( $2\pi \times 7 \times 10^{12}$ [ $rad/sec/A$ ]). The first order approximated laser tuning gain                                                                                                              | - <b>-</b> 0 |

| 4.4          | has been obtained the DC bias ranges 1-3 $mA$                                                                                                                                                                                                                          | 131          |

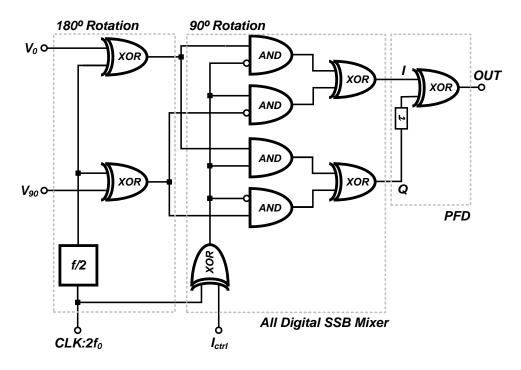

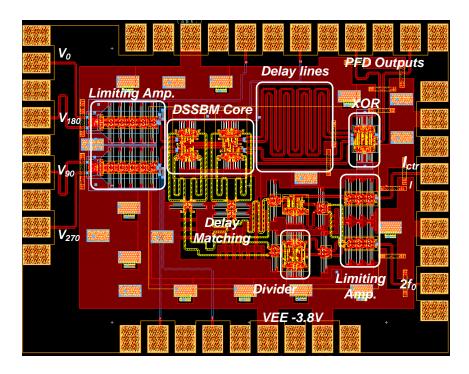

| 4.4          | mixer (D-SSBM) and Quadri-correlator PFD. Courtesy of E. Bloch                                                                                                                                                                                                         |              |

| 4 =          | [1,2]                                                                                                                                                                                                                                                                  | 134          |

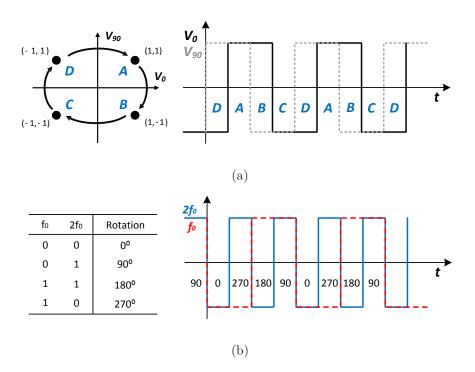

| 4.5          | The logic status for the DSSB operations: (a) The limiting amplifier outputs of $V_0$ and $V_{90}$ . The 90 degree out-of-phase output signals have four different status. (b) The PE effect frequency inputs (f                                                       |              |

|              | have four different status. (b) The RF offset frequency inputs ( $f_0$ and $2f_0$ ) have the DSBBM rotation status. Courtesy of E. Bloch.                                                                                                                              | 135          |

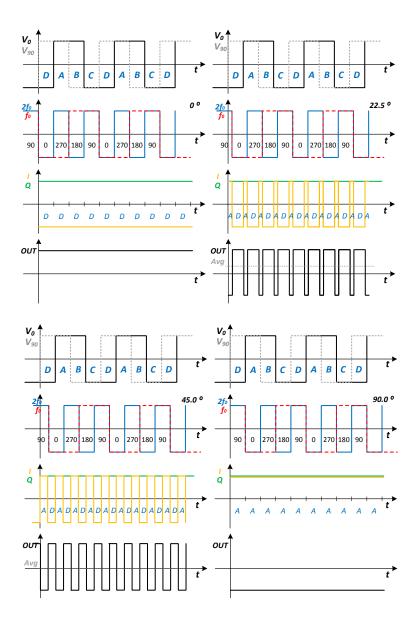

| 4.6          | The time domain phase detection mode analysis with the D-SSBM                                                                                                                                                                                                          | 100          |

|              | and PFD rotation status.                                                                                                                                                                                                                                               | 136          |

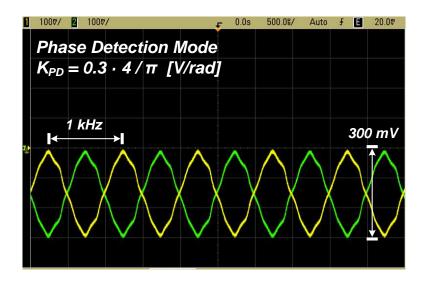

| 4.7          | The measurement results for the phase detection mode. The results                                                                                                                                                                                                      |              |

|              | show a 0.3 $V_{pp}$ periodic triangular waveform with a cycle of $\pi$ .                                                                                                                                                                                               |              |

|              | Courtesy of E. Bloch                                                                                                                                                                                                                                                   | 138          |

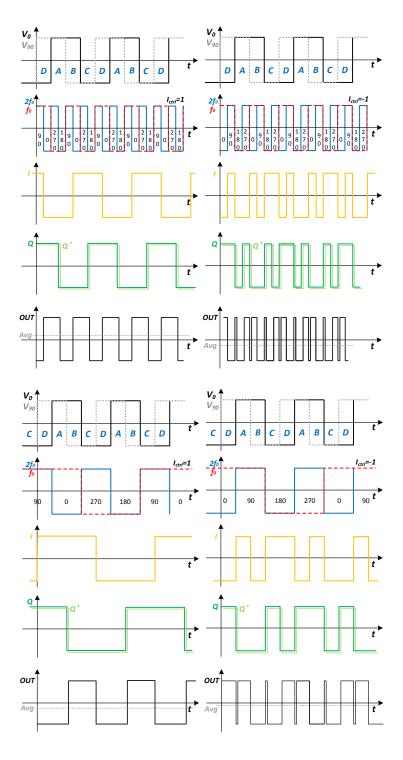

| 4.8          | The time domain frequency detection mode analysis with the DSSBM                                                                                                                                                                                                       |              |

|              | and PFD rotation status.)                                                                                                                                                                                                                                              | 139          |

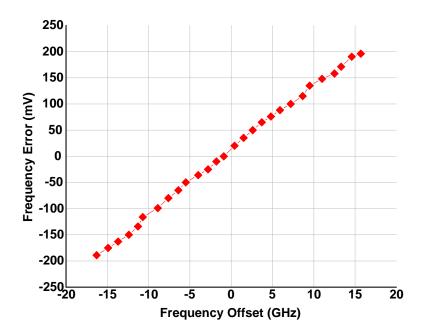

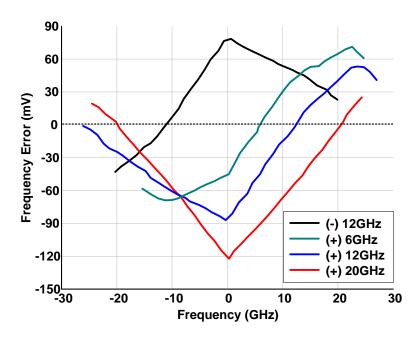

| 4.9          | The measurement results for the frequency detection mode. The results show a 0.3 $V_{pp}$ periodic triangular waveform with a cycle of                                                                                                                                 |              |

|              | $\sim$ 50 GHz                                                                                                                                                                                                                                                          | 141          |

| 4.10         | The EIC layout designed using Teledyne 500 nm HBTs with the                                                                                                                                                                                                            |              |

|              | IC size of $1.55 \times 1.15 \ mm^2$ . Courtesv of Eli Bloch [1,2]                                                                                                                                                                                                     | 142          |

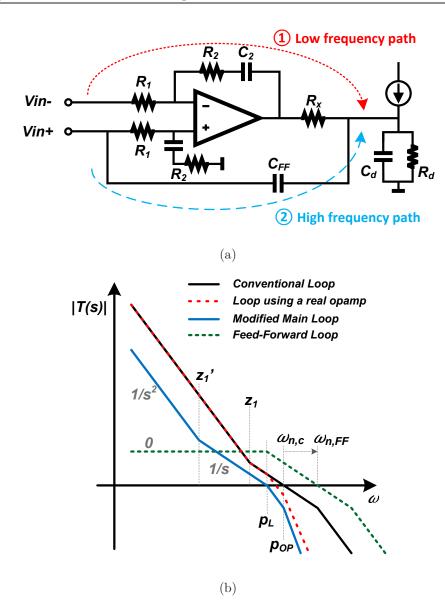

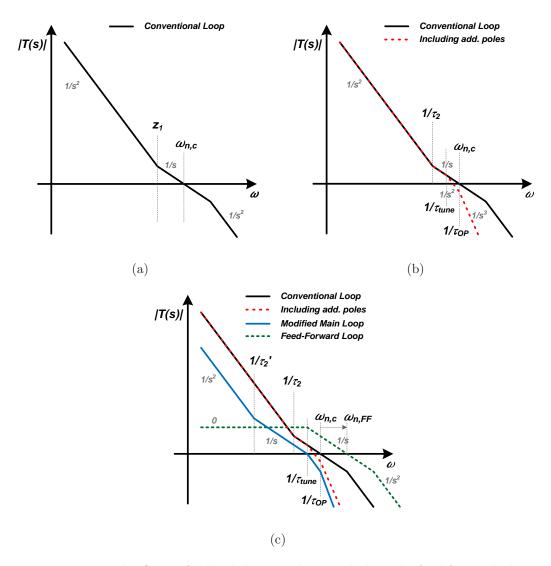

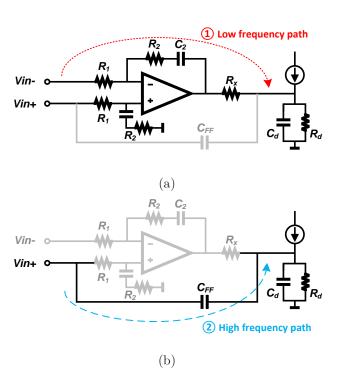

| 4.11 | The OPLL feedback loop analysis including the feed-forward idea<br>to extend the loop bandwidth. (a) The conventional second-order |     |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | type-II loop, (b) the conventional loop with the parasitic poles                                                                   |     |

|      | which make the OPLL unstable or may decrease the loop band-                                                                        |     |

|      | width, and (c) the modified loop with additional novel feed-forward                                                                |     |

|      | path to minimize the effective loop delay and extend the loop band-                                                                |     |

|      | width.                                                                                                                             | 144 |

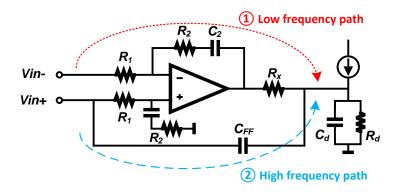

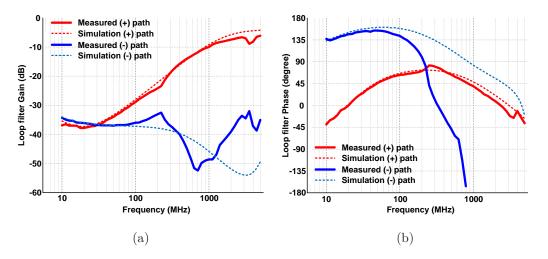

| 4.12 | The dual-path loop filter schematic including the feed-forward path:                                                               |     |

|      | 1) the low frequency path with an integrator, and 2) the high fre-                                                                 |     |

|      | quency path with the passive capacitor $C_{FF}$                                                                                    | 146 |

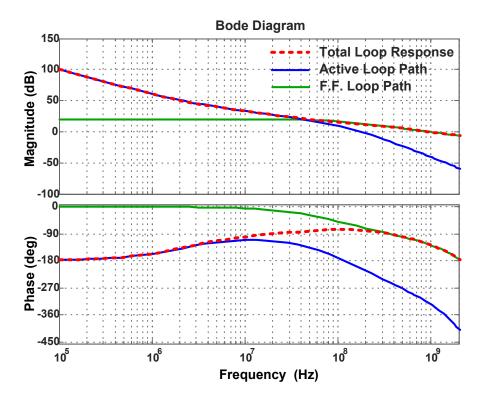

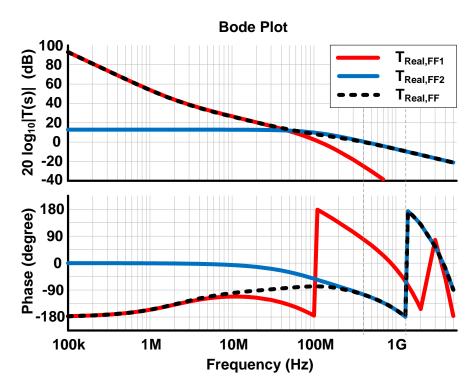

| 4.13 | The OPLL bode-plot including the feed-forward loop: The open                                                                       |     |

|      | loop bandwidth $\omega_n \sim 400$ MHz, the phase margin of more than 60                                                           |     |

|      | degree, and the gain margin of more than 7 dB                                                                                      | 149 |

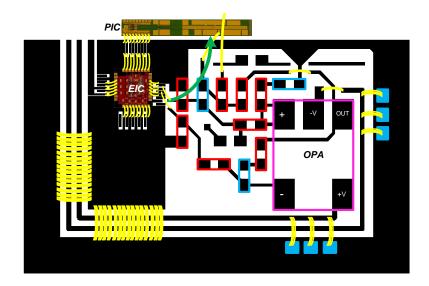

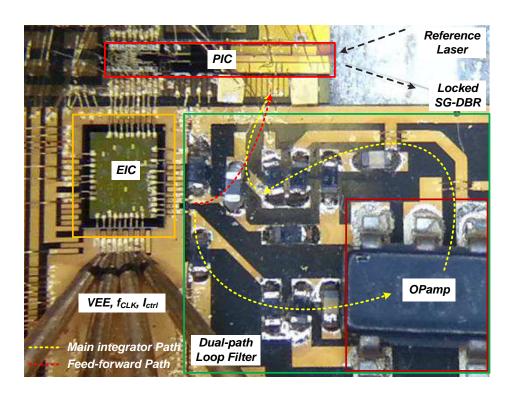

| 4.14 | The photograph of the heterodyne OPLL: The PIC, EIC and loop                                                                       |     |

|      | filter are highly integrated in a single carrier board within $10 \times 8$                                                        |     |

|      | $mm^2$                                                                                                                             | 151 |

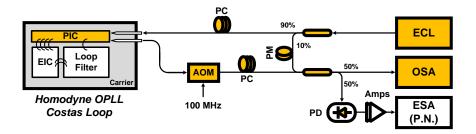

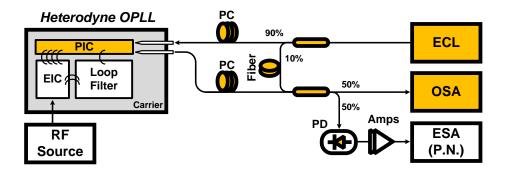

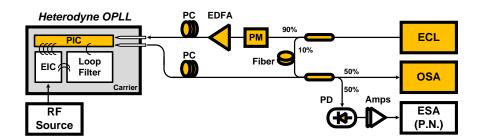

| 4.15 | A test setup for the heterodyne OPLL for the performance of the                                                                    |     |

|      | locked SG-DBR laser (frequency synthesis and phase noise mea-                                                                      |     |

|      | surements). EDFA: Erbium doped fiber amplifier, PC: polariza-                                                                      |     |

|      | tion controller, OSA: optical spectrum analyzer, and ESA: electri-                                                                 |     |

|      | cal spectrum analyzer                                                                                                              | 153 |

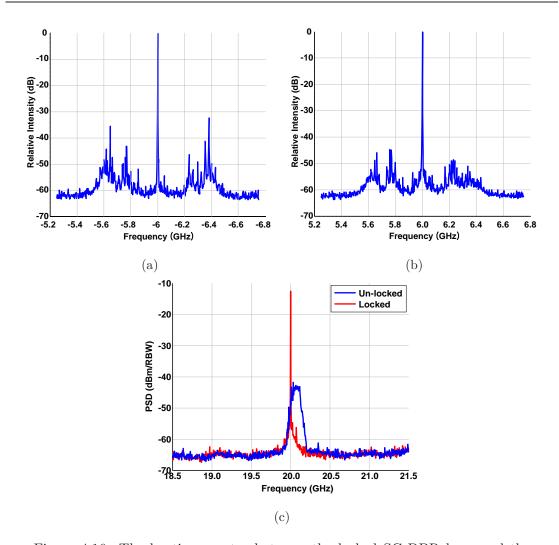

| 4.16 | The beating spectra between the locked SG-DBR laser and the                                                                        |     |

|      | reference laser. (a) An offset frequency lock at (+) 6 GHz, (b)                                                                    |     |

|      | offset frequency lock at (-) 6 GHz, and (c) offset frequency offset                                                                |     |

|      | lock at 20 GHz and unlock (free-running) near 20 GHz frequency                                                                     |     |

|      | offset.                                                                                                                            | 154 |

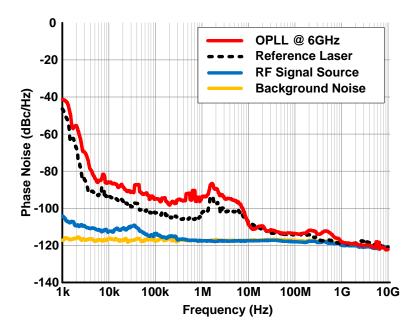

| 4.17 | The phase noise measurement results for the beating spectrum in                                                                    |     |

|      | figure 4.16 (a), and the compared phase noise results of the reference                                                             | 4   |

| 4.10 | laser, RF signal source, and background noise                                                                                      | 155 |

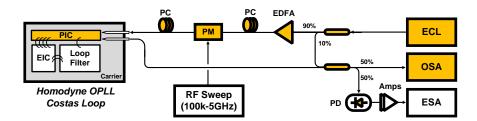

| 4.18 | A test setup for the heterodyne OPLL for the closed loop frequency                                                                 | 150 |

| 1 10 | response measurements (figure 4.19 and figure 4.20 (b))                                                                            | 156 |

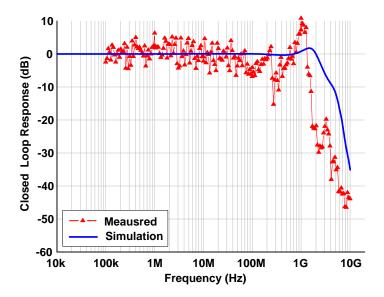

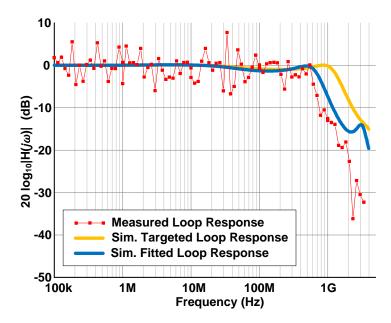

| 4.19 | The closed loop frequency response for the heterodyne OPLL (red                                                                    |     |

|      | line-dot), and comparison results of simulated closed loop frequency                                                               |     |

|      | response for the open-loop response $T_{OPLL}$ (yellow) and fitted frequency response for the measured result (blue)               | 157 |

| 4.20 | quency response for the measured result (blue)                                                                                     | 157 |

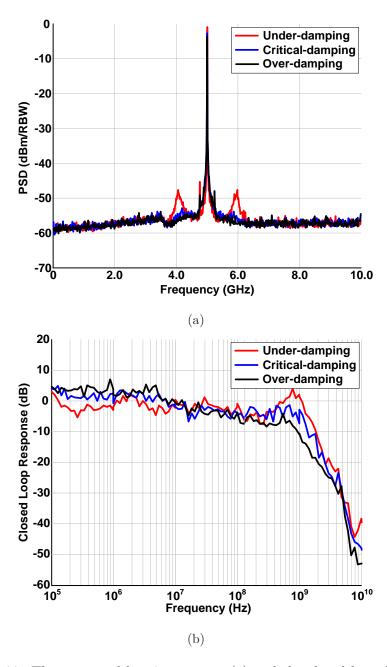

| 4.20 | The measured beating spectra (a) and the closed loop frequency responses (b) at the frequency offset of 5 GHz. The values of the   |     |

|      | feed-forward capacitor are varied with 0.5, 1.0 and 1.5 pF, and the                                                                |     |

|      | different loop responses are measured                                                                                              | 158 |

|      |                                                                                                                                    |     |

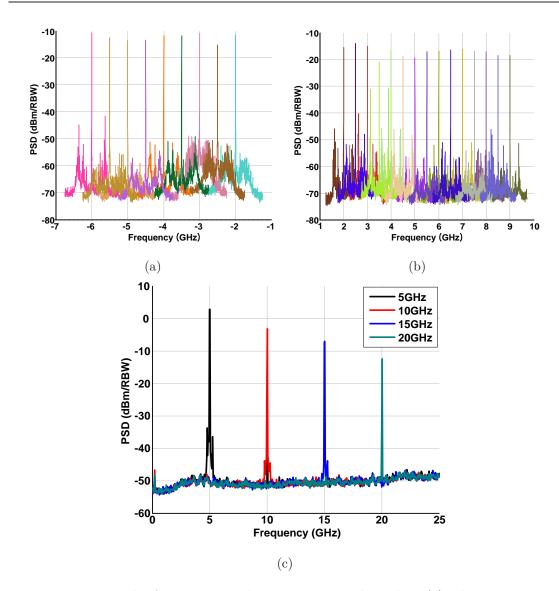

| 4.21 | The frequency synthesis experimental results. (a) The negative frequency sweeps from -6 to -2 GHz with $I_{ctrl} = (-)1$ in the EIC, (b) The positive frequency sweeps from 2 to 9 GHz with $I_{ctrl} = (+)1$ in the EIC, and (c) The wide frequency sweep range up to 20 GHz using the improved OPLL | 160                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 4.22 | Laser phase noise analysis. Optical PLL system diagram including the noise sources of input reference, $n_1(t)$ of shot and white noise including an amplifier noise figure, and $n_2(t)$ of laser (oscillator) noise (a), and phase noise (dBc/Hz) vs. frequency from 1 Hz to 10 GHz                 | 162                               |

| 4.23 | Dual-path (feed-forward) loop filter analysis. The circuit schematic for low frequency path including an integrator and pole and zero (a), and the circuit schematic for high frequency path through the                                                                                              |                                   |

| 4.24 | feed-forward capacitor $C_{FF}$ as a zero (b)                                                                                                                                                                                                                                                         | <ul><li>164</li><li>166</li></ul> |

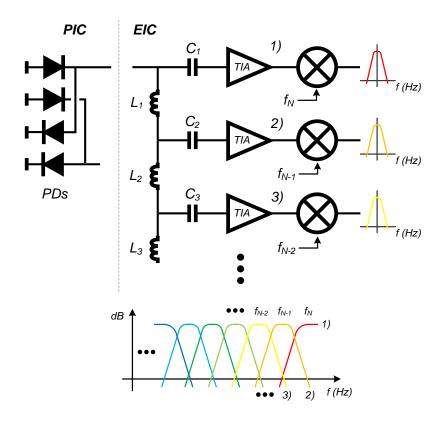

| 5.1  | The conventional WDM coherent receiver concept, (a) block diagrams: optical filters (AWG) for wavelength channel de-multiplexing (b) optical to electrical de-multiplexing flows                                                                                                                      | 175                               |

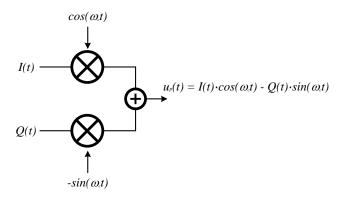

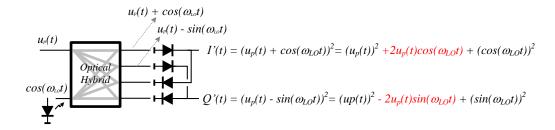

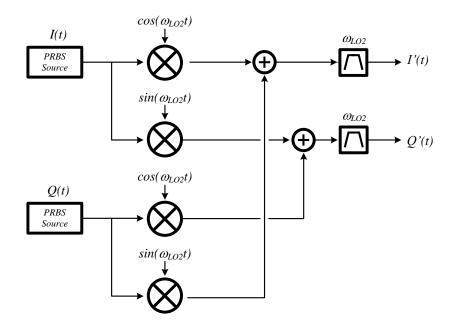

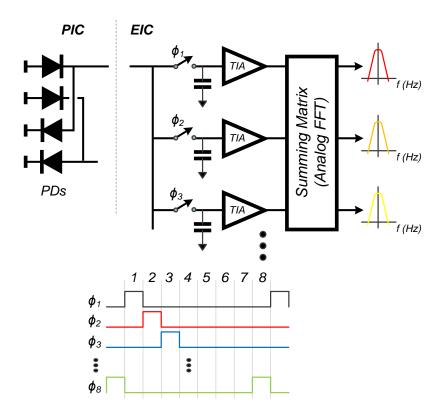

| 5.2  | The new proposed WDM receiver concept, (a) block diagrams: a single photonic IC and channel de-multiplexing in the electrical domain (b) optical and electrical two-step de-multiplexing flows.                                                                                                       | 177                               |

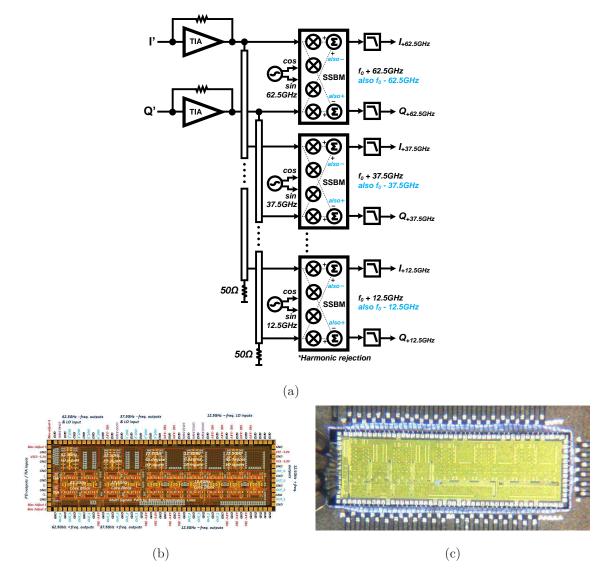

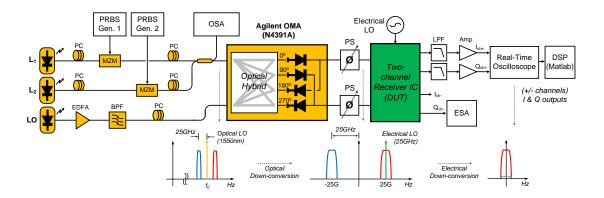

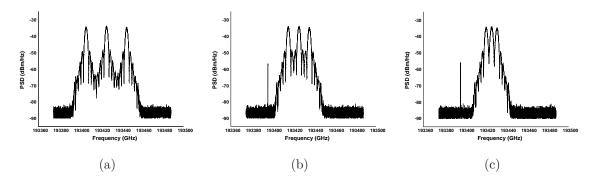

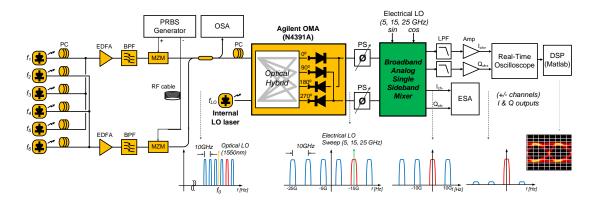

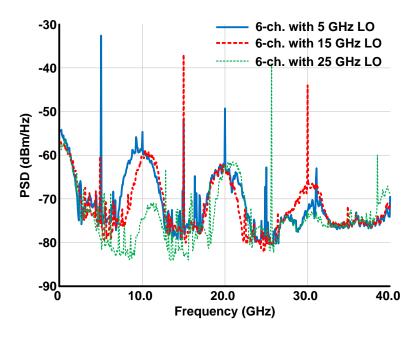

| 5.3  | A concept schematic diagram for a coherent single-chip multi-channel WDM receiver and its de-multiplexing flows for six modulated channels                                                                                                                                                            | 178                               |

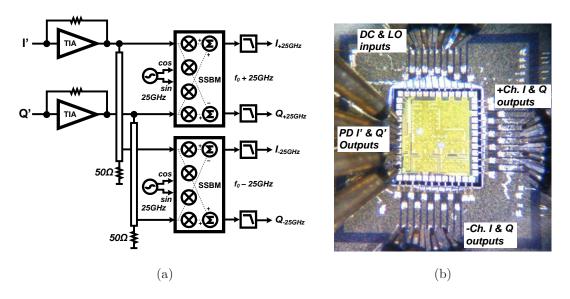

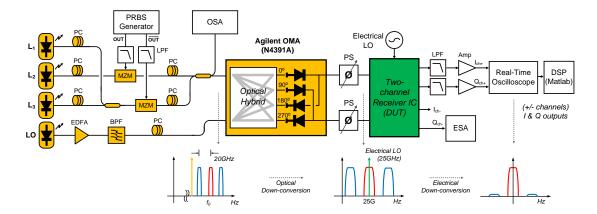

| 5.4  | (a) Two-channel WDM receiver circuit schematic for $\pm$ 37.5 GHz and $\pm$ 62.5 GHz channels, (b) Photo image for the two-channel IC and its probing. PD $I$ ' and $Q$ ' outputs are connected with the                                                                                              |                                   |

| 5.5  | direct probing and others are wire-bonded                                                                                                                                                                                                                                                             | 180                               |

|      | (b)                                                                                                                                                                                                                                                                                                   | 181                               |

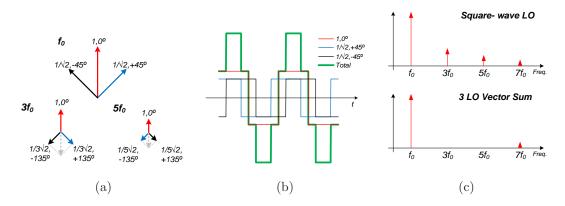

| 5.6  | Harmonic rejection mixer scheme. (a) The vector sums for the fundamental frequency $f_0$ , the third order harmonic frequency $3f_0$ , and the fifth order harmonic frequency $5f_0$ , (b) Time domain signal sum for the three vectors, 1 amplitude with 0 degree, $1\sqrt{2}$ amplitude with +45 degree, and $1\sqrt{2}$ amplitude with -45 degree, and (c) |            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | Therefore, the 3 LO vector sum shows no harmonic components at $3f_0$ and $5f_0$ . [27]                                                                                                                                                                                                                                                                       | 182        |

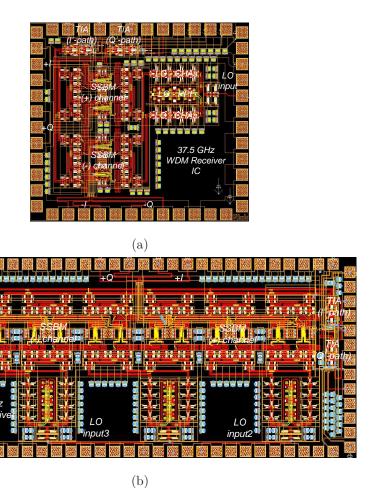

| 5.7  | A proposed six-channel WDM receiver IC schematic (a), a layout for the six-channel receiver IC and its port assignments (b), and a photo image of a 6-channel WDM receier IC with wire-bonding on                                                                                                                                                             |            |

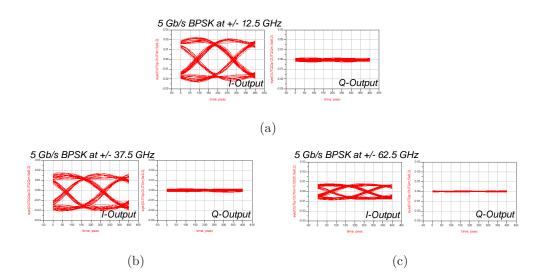

| 5.8  | carrier board (c)                                                                                                                                                                                                                                                                                                                                             | 184        |

|      | and $Q$ -outputs (b), and 5 Gb/s BPSK eye diagrams on both $\pm 62.5$ GHz $I$ - and $Q$ -outputs (c). The eye heights are getting smaller because of the bandwidth EIC bandwidth (limited by the multiple                                                                                                                                                     | 105        |

| 5.9  | buffer stages)                                                                                                                                                                                                                                                                                                                                                | 185        |

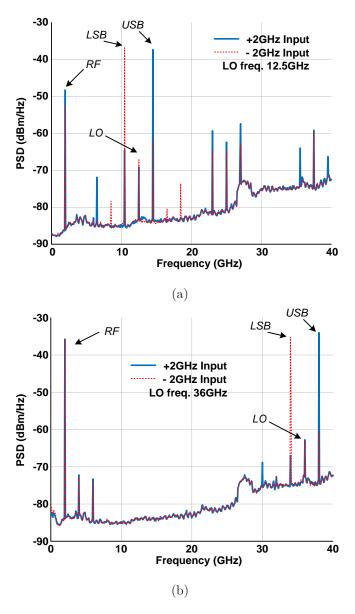

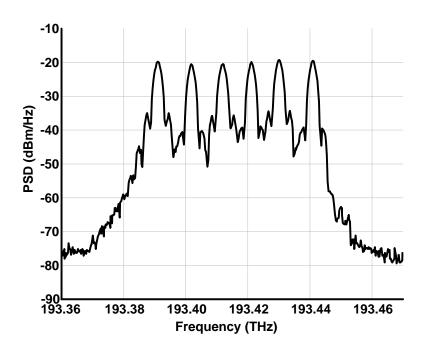

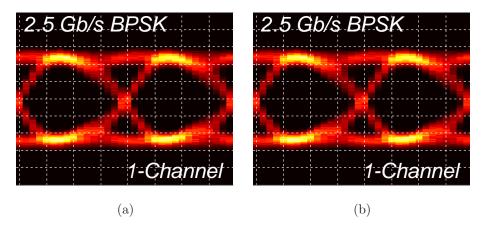

|      | measurement equipments' bandwidth limits (ESA, signal source, and RF probes                                                                                                                                                                                                                                                                                   | 187<br>189 |

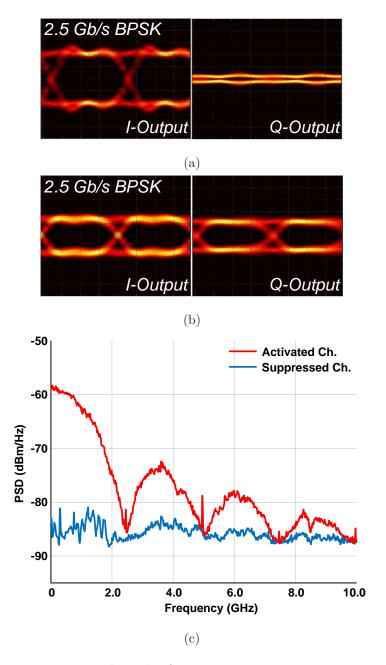

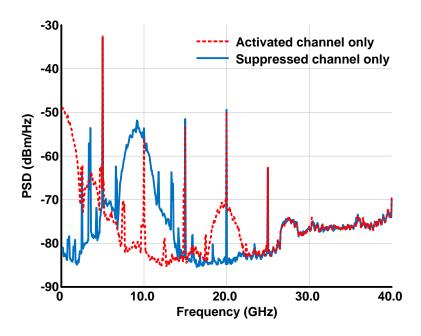

|      | agrams for the activated (+) channel and the suppressed (-) channel with a single modulated carrier (a), the eye diagrams for the (+) and (-) channels with two modulated carriers (b), and the measured output spectra when the signal and the adjacent (crosstalk)                                                                                          | 101        |

| 5.12 | channels are active. Crosstalk suppression is $\sim 25 dB$ (c) Test setup for adjacent channel interference measurements using                                                                                                                                                                                                                                | 191        |