# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

W-band phased array systems using silicon integrated circuits

# Permalink

https://escholarship.org/uc/item/8zz9v532

# **Author** Kim, Sang Young

# Publication Date 2012

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### W-band Phased Array Systems using Silicon Integrated Circuits

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Sang Young Kim

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor James Buckwalter Professor Gert Cauwenberghs Professor William S. Hodgkiss Professor Lawrence E. Larson

2012

Copyright Sang Young Kim, 2012 All rights reserved. The dissertation of Sang Young Kim is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2012

# DEDICATION

To my parents, Jin Heung Kim and Jin Hwan Choi, and my brother and sister-in-law, Jae Young Kim and YoonMi Lee.

# TABLE OF CONTENTS

| Signature Page  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                 | iii                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Dedication      |                                                                                                                                                                                                                       |                                                 |

| Table of Conte  | nts                                                                                                                                                                                                                   | v                                               |

| List of Figures | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                 | /ii                                             |

| List of Tables  |                                                                                                                                                                                                                       | xi                                              |

| Acknowledger    | nents                                                                                                                                                                                                                 | cii                                             |

| Vita            |                                                                                                                                                                                                                       | κv                                              |

| Abstract of the | Dissertation                                                                                                                                                                                                          | vi                                              |

| Chapter 1       | Introduction                                                                                                                                                                                                          | 1<br>1<br>3<br>3<br>6                           |

| Chapter 2       | 2.2.3       R-C-based and L-C Resonator Quadrature Generators       1         2.2.4       Wideband 60–80 GHz Phase Shifter Design       1         2.3       Measurements       1         2.4       Conclusion       1 | 8<br>9<br>9<br>10<br>10<br>16<br>20<br>24<br>24 |

| Chapter 3       | <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                                                   | 26<br>26<br>26<br>27<br>29<br>29<br>34          |

| Chapter 4    | A Low Power 4-Element Phased Array Receiver with Single-Ended Pas-     |

|--------------|------------------------------------------------------------------------|

|              | sive Phase Shifter for 76-84 GHz Radar and Communication Systems 35    |

|              | 4.1 Introduction                                                       |

|              | 4.2 Design                                                             |

|              | 4.2.1 Architecture                                                     |

|              | 4.2.2 Amplifiers                                                       |

|              | 4.2.3 Phase Shifter Design                                             |

|              | 4.2.4 2-stage Wilkinson Combiner                                       |

|              | 4.2.5 Phased Array Simulations                                         |

|              | 4.3 Measurements                                                       |

|              | 4.4 Conclusion                                                         |

|              | 4.5 Acknowledgements                                                   |

| Chapter 5    | A 16-Element 76–84 GHz Differential Phased Array Receiver 59           |

| -            | 5.1 Introduction                                                       |

|              | 5.2 Design                                                             |

|              | 5.2.1 Architecture                                                     |

|              | 5.2.2 Amplifiers                                                       |

|              | 5.2.3 Phase Shifter                                                    |

|              | 5.2.4 Balun and Differential Wilkinson Combiner/Divider 66             |

|              | 5.2.5 Doubler                                                          |

|              | 5.2.6 LO Path Design                                                   |

|              | 5.2.7 I/Q Mixer                                                        |

|              | 5.2.8 IF amplifier                                                     |

|              | 5.2.9 Built-In-Self-Test System Design                                 |

|              | 5.3 Measurements                                                       |

|              | 5.3.1 Single-Element                                                   |

|              | 5.3.2 16-Element Phased Array                                          |

|              | 5.4 Conclusion                                                         |

|              | 5.5 Acknowledgements                                                   |

| Chapter 6    | Conclusion                                                             |

| A            |                                                                        |

| Appendix A   | An 18-20 GHz Subharmonic Satellite Down-Converter in 0.18 $\mu$ m SiGe |

|              | Technology                                                             |

|              | A.1 Introduction                                                       |

|              | A.2 Design                                                             |

|              | A.3 Measurements                                                       |

|              | A.4 Conclusion                                                         |

|              | A.5 Acknowledgements                                                   |

| Bibliography |                                                                        |

# LIST OF FIGURES

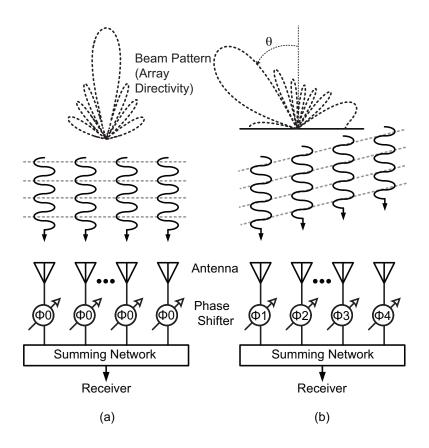

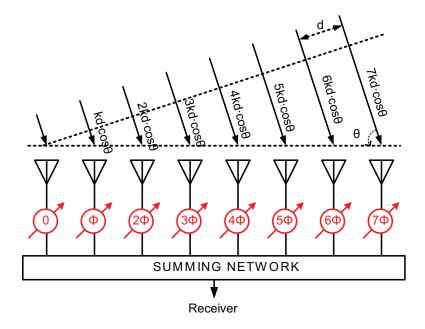

| Figure 1.1:<br>Figure 1.2: | (a) Beam forming and (b) Beam steering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2<br>2   |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

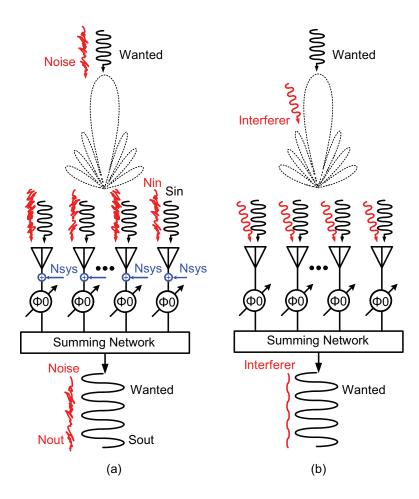

| Figure 1.3:                | (a) SNR improvement and (b) interference rejection, in an All-RF phased array architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4        |

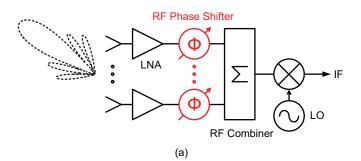

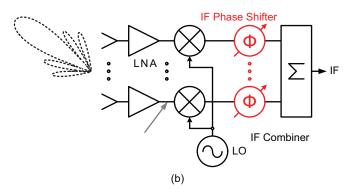

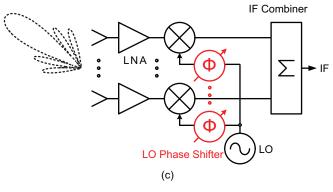

| Figure 1.4:                | Block diagram of the phased array architecture (a) RF phase-shifting, (b) IF phase-shifting, (c) LO phase-shifting and (d) digital beam-forming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5        |

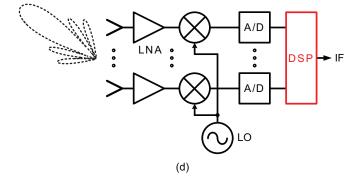

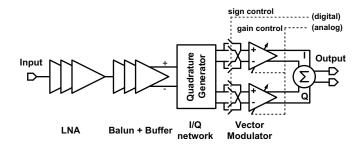

| Figure 2.1:                | The active phase shifter architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9        |

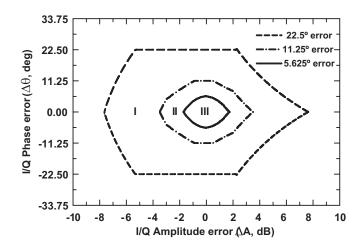

| Figure 2.2:                | The contour plot of I/Q errors (quadrature phase error, $\Delta\theta$ , and amplitude mismatch, $\Delta A$ ) in a quadrature network for 3-bit (region I, $\theta_{error} < 360^{\circ}/2^{4}$ = 22.5°), 4-bit (region II, $\theta_{error} < 360^{\circ}/2^{5} = 11.25^{\circ}$ ) and 5-bit (region III,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Figure 2.3:                | $\theta_{error} < 360^{\circ}/2^4 = 5.625^{\circ}$ ) operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10       |

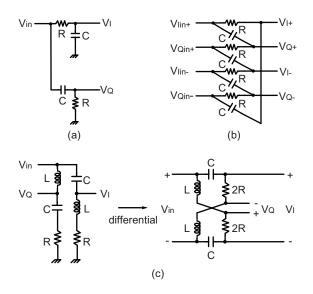

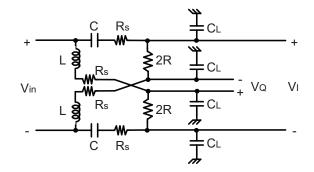

|                            | quadrature networks. The differential version is called as quadrature all-<br>pass (QAF) filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11       |

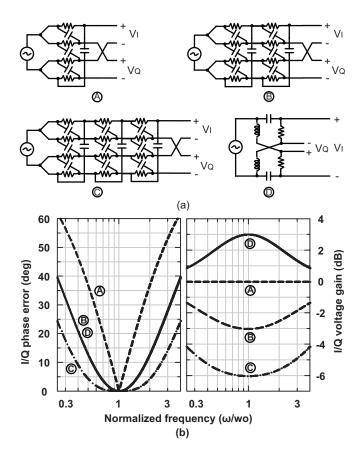

| Figure 2.4:                | Performance comparisons between quadrature networks: (a) R-C one-, two-<br>and three-stage polyphase filters (A, B and C) and QAF (D), (b) quadra-<br>ture phase error and gain characteristics versus normalized angular frequency<br>for the QAF and polyphase filters. $R = 20 \Omega$ , $C = 113.68$ fF, $L = 45.47$ pH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| <b>D</b> : 0.5             | and $f_o = 70 \text{ GHz}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13       |

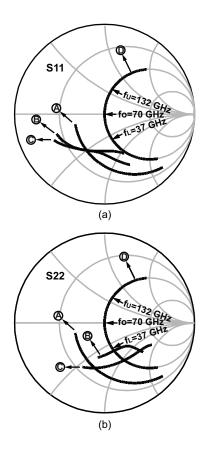

| Figure 2.5:                | Input and output impedance of the I/Q networks shown in Fig. 2.4: (a) input differential impedance, (b) output differential impedance for one of the I/Q outputs. For QAF, $S_{11} < -10$ dB and $S_{22} < -10$ dB at 37 GHz (0.53 $f_o$ ) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14       |

| Eigung 26.                 | 132 GHz (1.88 $f_o$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14<br>14 |

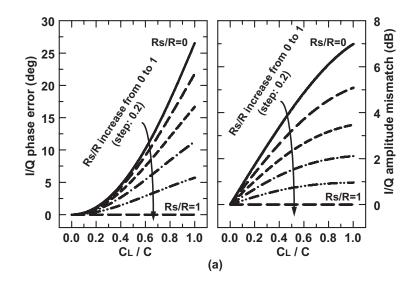

| Figure 2.6:<br>Figure 2.7: | I/Q errors (phase errors and amplitude mismatches) in the QAF under ca-<br>pacitive loading, $C_L$ , with several values of $R_s$ in Fig. 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14       |

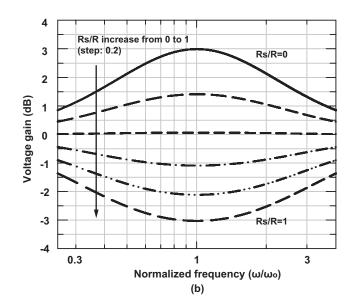

| Figure 2.8:                | Amplitude response of the improved QAF vs. $R_s$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15       |

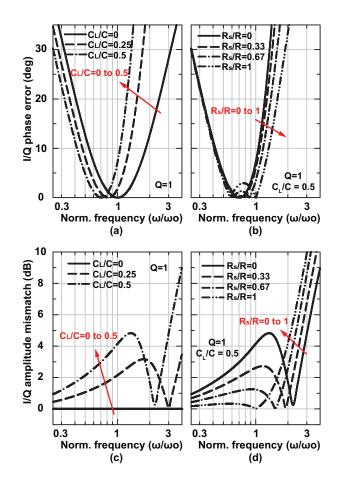

| Figure 2.9:                | (a) I/Q phase error when $C_L/C$ increases ( $R_s = 0$ ), (b) I/Q phase error when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $C_L/C$ increases ( $R_s = 0$ ), (d) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $C_L/C = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mismatch when $R_s/R$ increases ( $R_s = 0.5$ ), (c) I/Q amplitude mi |          |

|                            | 0.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17       |

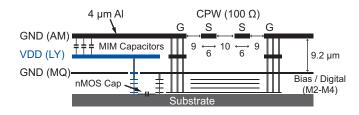

| -                          | IBM 8HP metal stack-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18       |

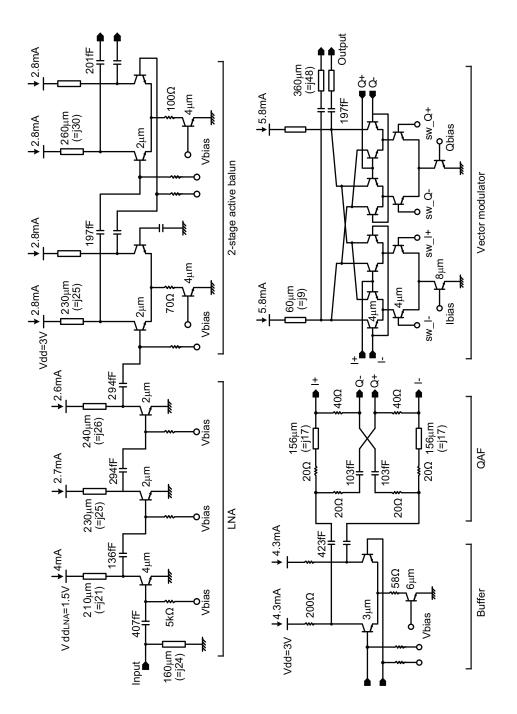

| Figure 2.11:               | Circuit schematics of the wideband millimeter-wave phase shifter front-end.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19       |

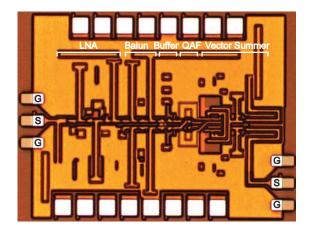

| Figure $2.12$ :            | Microphotograph of the wideband 60-80 GHz phase shifter front-end $(1.15 \times 0.9 \text{ mm}^2 \text{ including pads})$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92<br>21 |

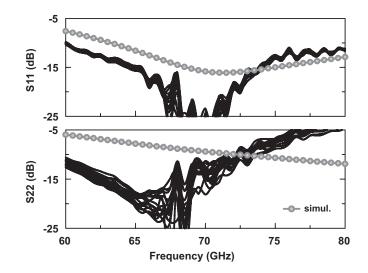

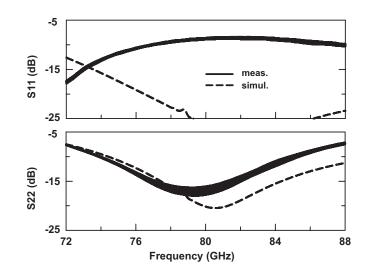

| Figure 2.13:               | Measured and simulated $S_{11}$ and $S_{22}$ for 16 phase states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21       |

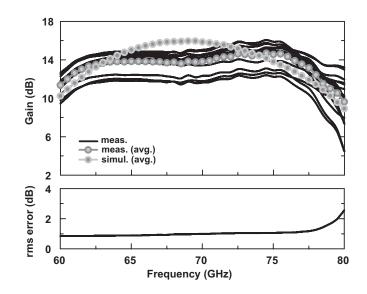

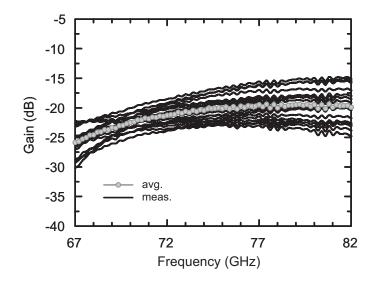

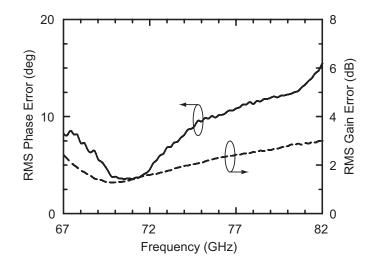

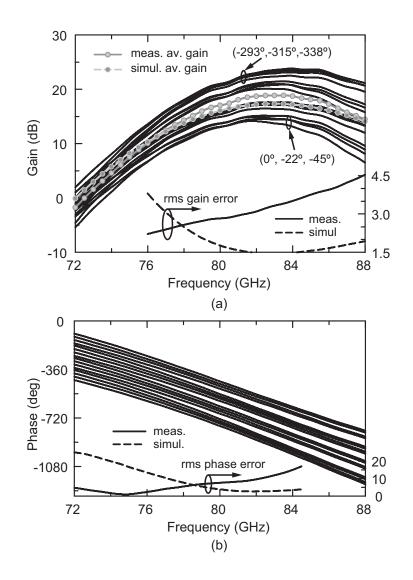

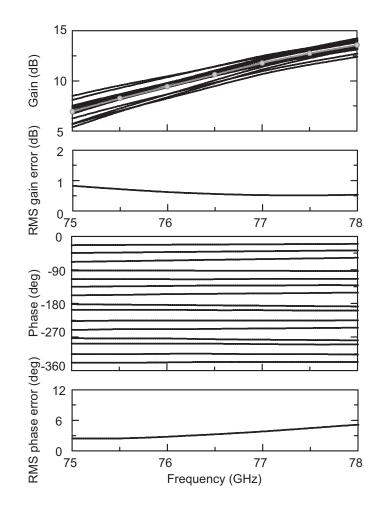

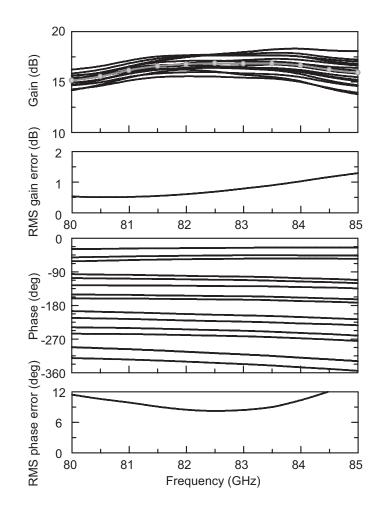

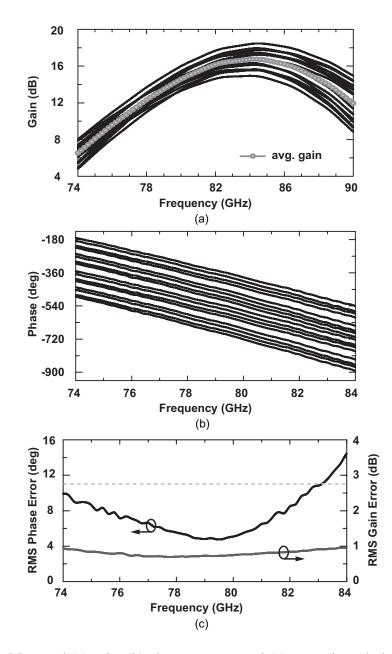

| Figure 2.14:               | Measured and simulated gain response for 16 phase states and rms gain error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22       |

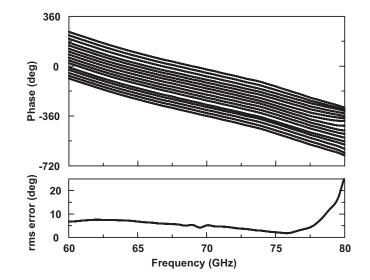

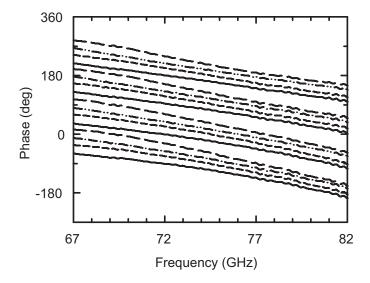

| U                          | Measured phase response and rms phase error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22       |

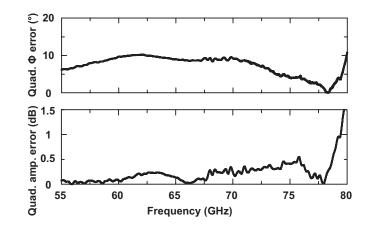

| -                          | Measured quadrature phase error and amplitude error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23       |

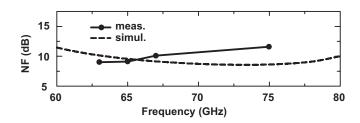

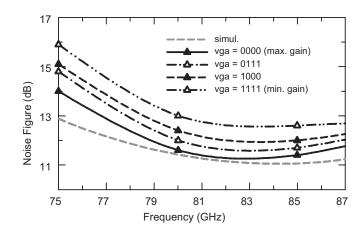

| Figure 2.17:               | Measured and simulated noise figure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23       |

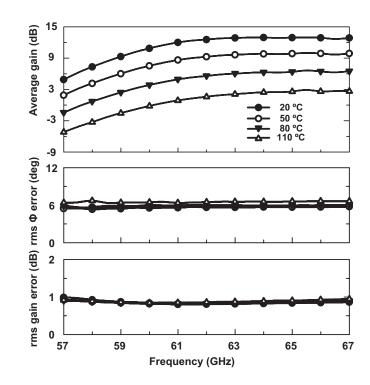

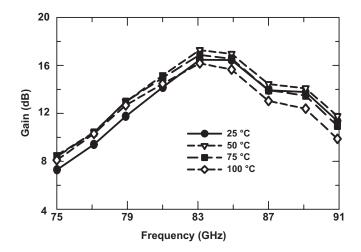

| U                          | Measured gain and rms errors at different temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24       |

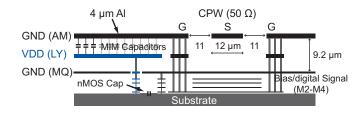

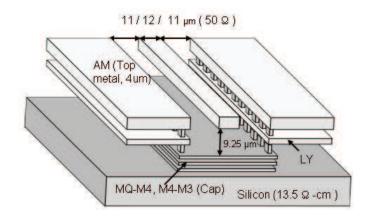

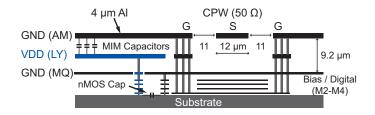

| Figure 3.1:  | The grounded-CPW transmission line and Metal-Oxide-Metal capacitor.                       | 28  |

|--------------|-------------------------------------------------------------------------------------------|-----|

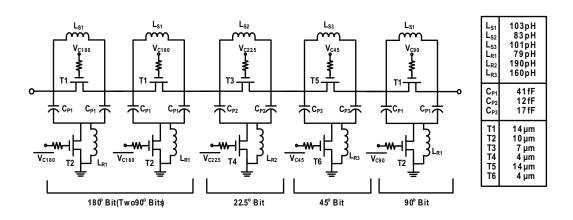

| Figure 3.2:  | Schematic of the 4-bit digital phase shifter.                                             | 28  |

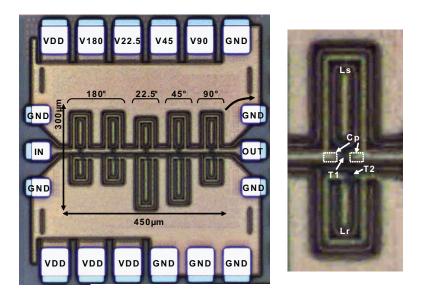

| Figure 3.3:  | Chip photograph of (a) 4-bit digital phase shifter and (b) 90° phase shifter              | • • |

|              | cell                                                                                      | 30  |

| Figure 3.4:  | Measured phase response of 16 different phase states.                                     | 30  |

| Figure 3.5:  | Measured gain response of 16 different phase states and average gain                      | 31  |

| Figure 3.6:  | RMS phase error and RMS gain error of 4-bit phase shifter                                 | 31  |

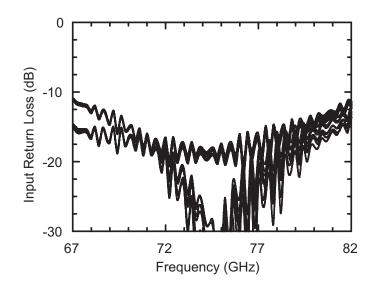

| Figure 3.7:  | Measured input return loss of 16 different phase states                                   | 32  |

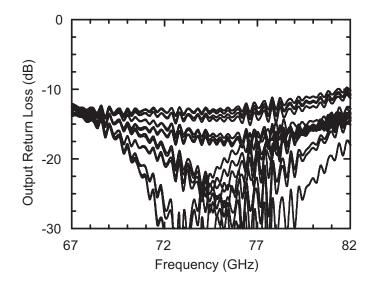

| Figure 3.8:  | Measured output return loss of 16 different phase states                                  | 32  |

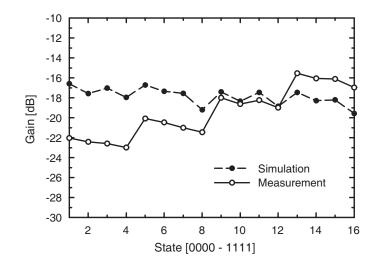

| Figure 3.9:  | Measured and simulated gain vs. phase states.                                             | 33  |

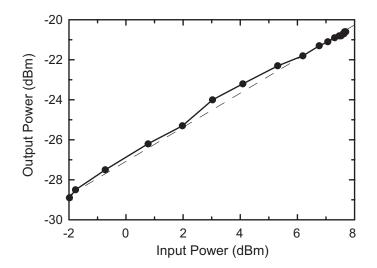

| Figure 3.10: | Measured output power vs. input power.                                                    | 33  |

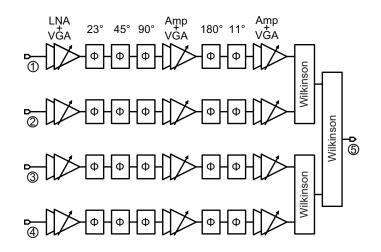

| Figure 4.1:  | W-band 4-element phased-array architecture                                                | 37  |

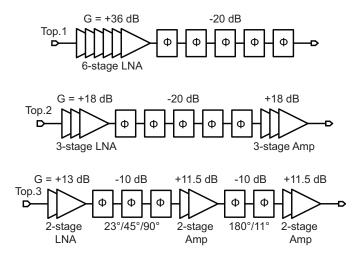

| Figure 4.2:  | Comparison of three different architectures, at 80 GHz                                    | 38  |

| Figure 4.3:  | IBM 8HP metal stack-up with a presentative 50 $\Omega$ CPW line                           | 39  |

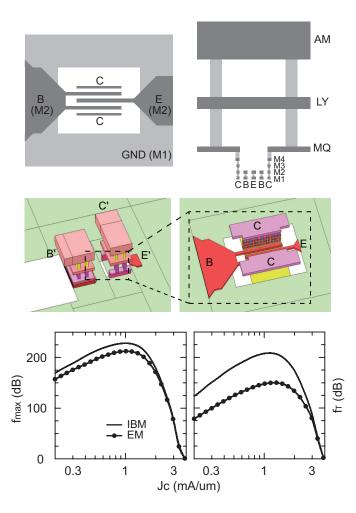

| Figure 4.4:  | Simulated $f_{max}$ and $f_T$ without and with EM simulation (transistor size = 5         |     |

|              | $\mu$ m x 0.12 $\mu$ m.)                                                                  | 40  |

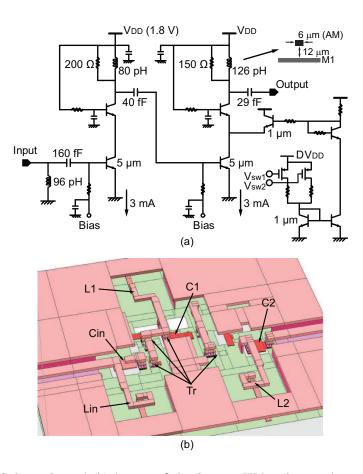

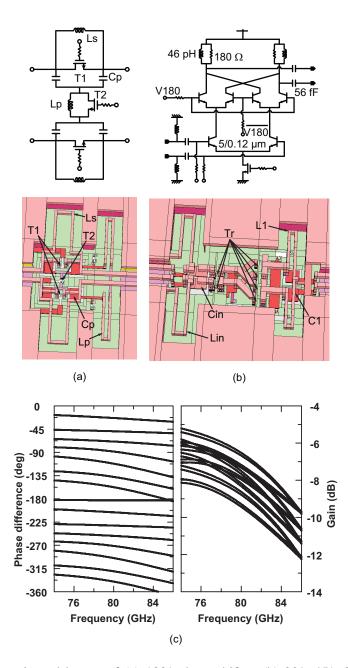

| Figure 4.5:  | (a) Schematic and (b) layout of the 2-stage W-band cascode amplifier with                 |     |

| -            | gain control.                                                                             | 41  |

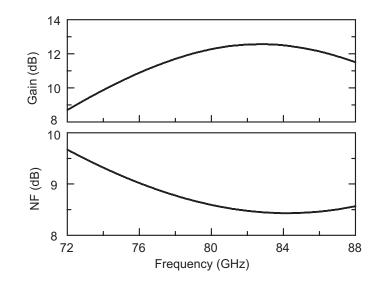

| Figure 4.6:  | Gain and noise figure of the 2-stage W-band cascode amplifier.                            | 41  |

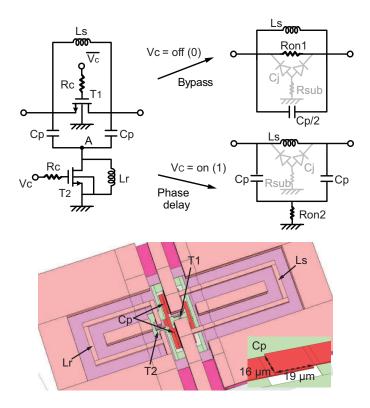

| Figure 4.7:  | Design of switched-delay CMOS phase shifters.                                             | 43  |

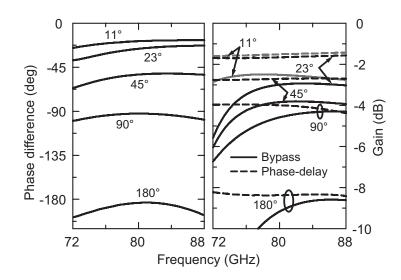

| Figure 4.8:  | Simulated switched-delay CMOS phase shifter cells                                         | 44  |

| Figure 4.9:  | Simulated phase difference and gain of the total phase shifters                           | 44  |

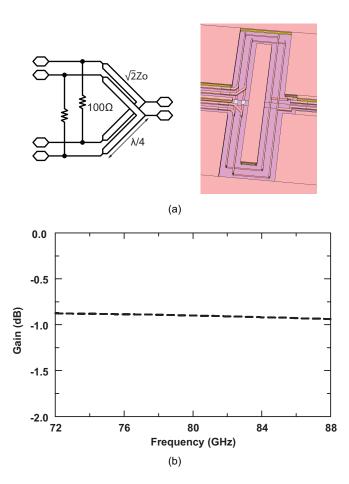

| Figure 4.10: | Simulated S-parameters of a single-stage Wilkinson coupler                                | 45  |

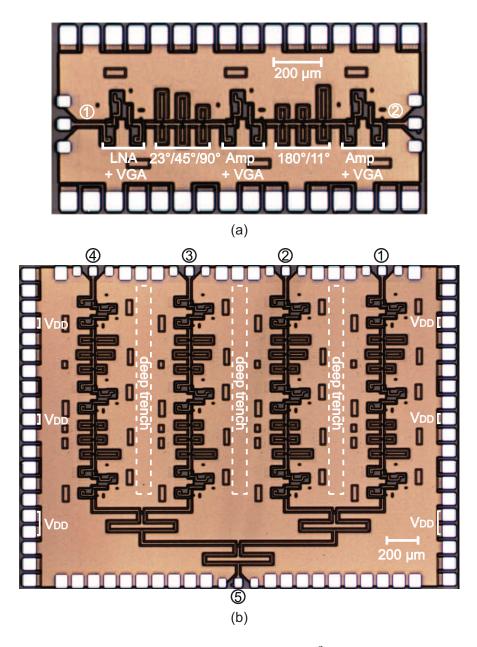

| Figure 4.11: | Photograph of (a) single channel $(1.6 \times 0.8 \text{ mm}^2)$ and (b) 4-element phased |     |

|              | arrays $(2.0 \times 2.7 \text{ mm}^2)$ .                                                  | 47  |

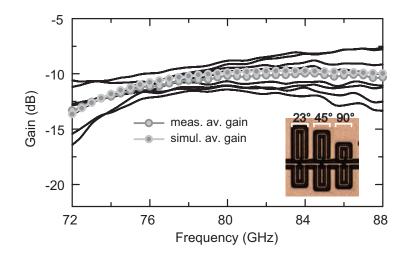

| Figure 4.12: | Measured and simulated gain of the $23^{\circ}/45^{\circ}/90^{\circ}$ phase shifter cell  | 48  |

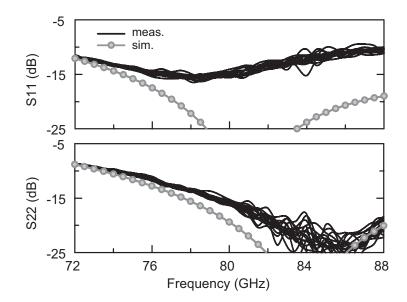

| Figure 4.13: | Measured $S_{11}$ and $S_{22}$ for 16 phase states                                        | 48  |

| Figure 4.14: | Measured (a) gain and (b) phase response vs. 16 phase states                              | 49  |

| Figure 4.15: | Measured VGA operation at the $(1,1,1,1)$ state                                           | 50  |

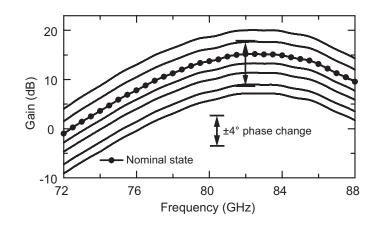

| Figure 4.16: |                                                                                           |     |

|              | the nominal state (see text).                                                             | 51  |

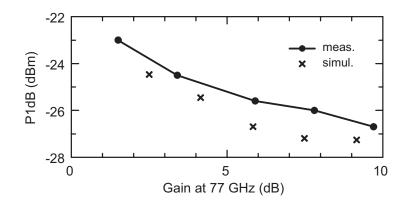

|              | Measured input $P_{1dB}$ vs. gain setting at 77 GHz                                       | 51  |

|              | Gain, phase, and RMS error after calibration at 76.5 GHz                                  | 52  |

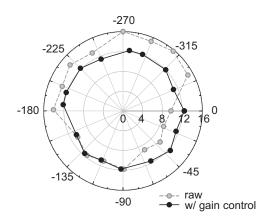

| Figure 4.19: | Gain and phase correction on a vector chart at 76.5 GHz                                   | 52  |

| Figure 4.20: | Gain, phase, and RMS error after calibration at 80 GHz                                    | 53  |

| -            | Gain and phase correction on a vector chart at 80 GHz                                     | 53  |

| -            | Gain, phase, and RMS error after calibration at 82.5 GHz                                  | 54  |

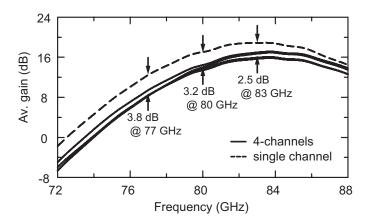

| Figure 4.23: | Measured average gain of 4-channel phased array chip and single channel                   |     |

|              | chip                                                                                      | 54  |

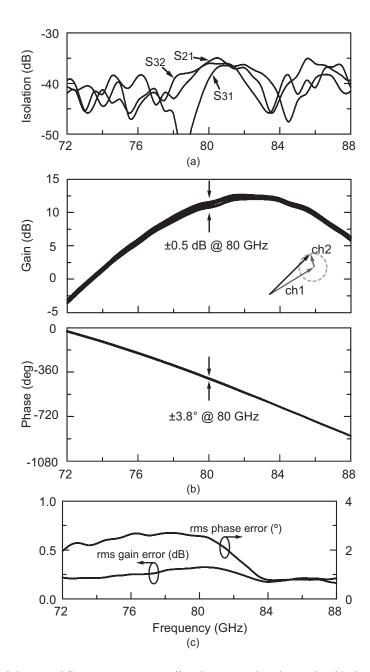

| Figure 4.24: | (a) Measured S-parameters coupling between the channels, (b) the effect of                |     |

|              | channel 2 phase change on channel 1, and (c) rms gain and phase error in                  |     |

|              | channel 1 due to the phase change in channel 2                                            | 55  |

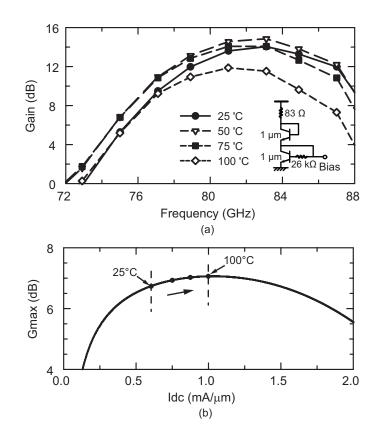

| Figure 4.25: | (a) Measured gain of a single channel at different temperatures, (b) channel              |     |

|              | current consumption and bias condition vs. temperature                                    | 57  |

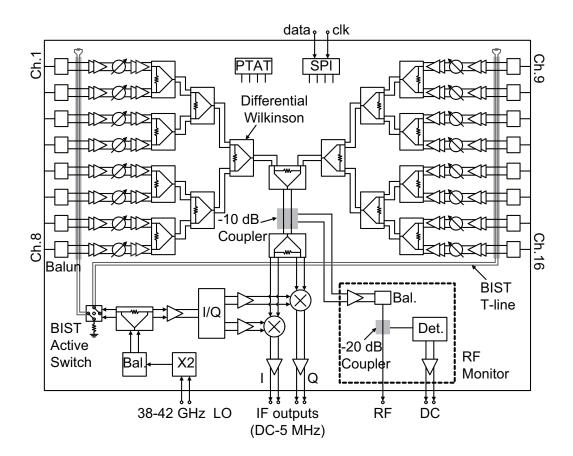

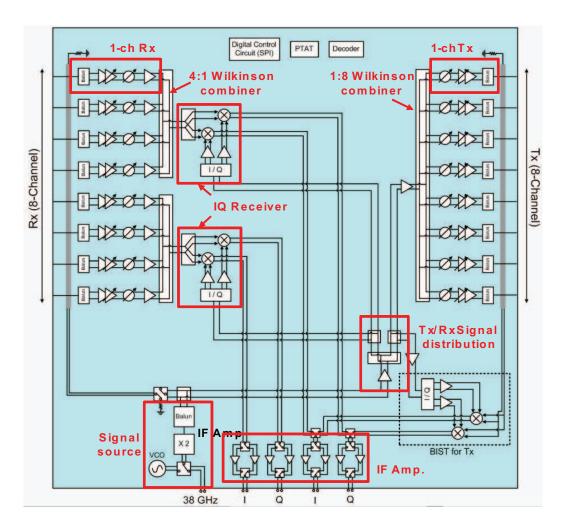

| Figure 5.1:                 | Block diagram of the 76-84 GHz 16-element phased array receiver with a chip-level built-in-self-test (BIST) system.                                                                               | 61       |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

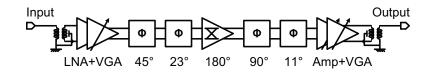

| Figure 5.2:                 |                                                                                                                                                                                                   | 62       |

| Figure 5.3:                 | 6 6                                                                                                                                                                                               | 63       |

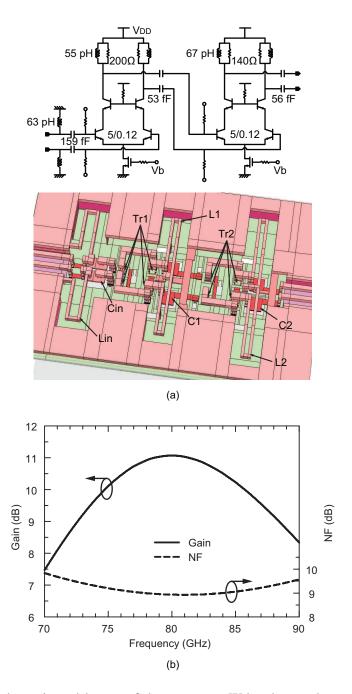

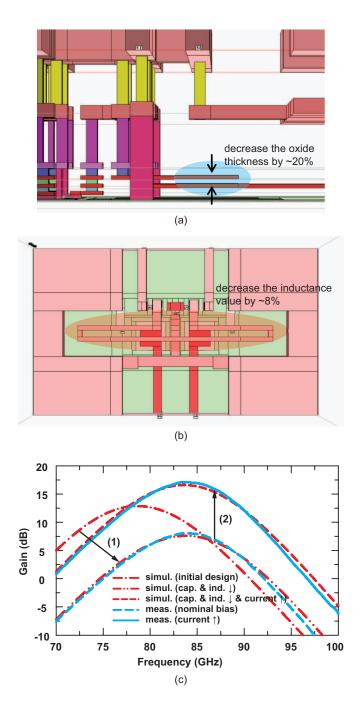

| Figure 5.4:                 | (a) Schematic and layout of the two-stage W-band cascode amplifier and (b)                                                                                                                        | 05       |

| 1 iguie 5.4.                | · · ·                                                                                                                                                                                             | 64       |

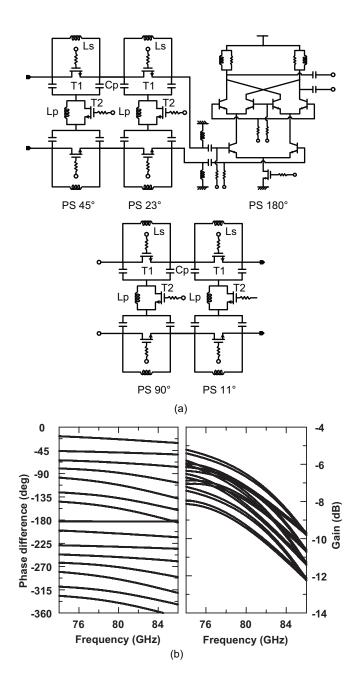

| Figure 5.5:                 | Schematic and layout of (a) $180^{\circ}$ phase shifter, (b) $90^{\circ}$ , $45^{\circ}$ , $23^{\circ}$ and $11^{\circ}$ phase shifters and (c) simulated phase difference and gain of each phase | 65       |

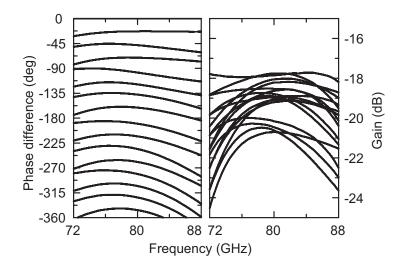

| Figure 5.6:                 | (a)Schematic and (b)Simulated phase difference and gain of the total phase shifters.                                                                                                              | 67       |

| Figure 5.7:                 |                                                                                                                                                                                                   | 68       |

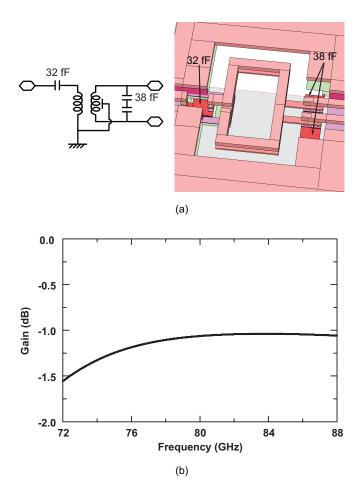

| Figure 5.8:                 | (a)Schematic, layout and (b)simulated gain of differential Wilkinson com-                                                                                                                         |          |

|                             |                                                                                                                                                                                                   | 69       |

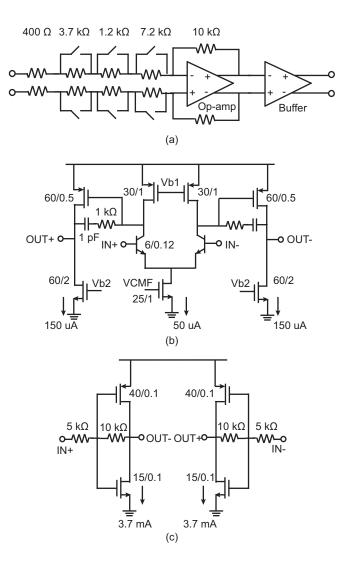

| Figure 5.9:<br>Figure 5.10: | Schematic of (a) doubler and (b)double-balanced mixer                                                                                                                                             | 69       |

| 0                           |                                                                                                                                                                                                   | 71       |

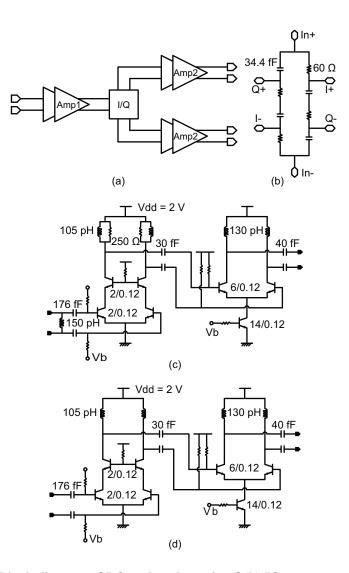

| Figure 5.11:                | (a) Block diagram of the IF amplifier, (b) the schematic of 2-stage op-amp,                                                                                                                       |          |

|                             |                                                                                                                                                                                                   | 73       |

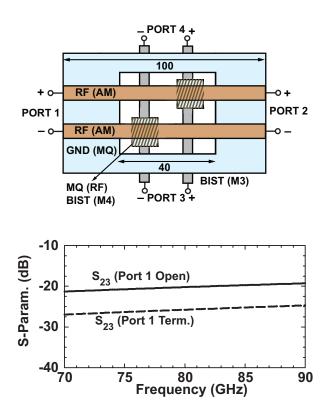

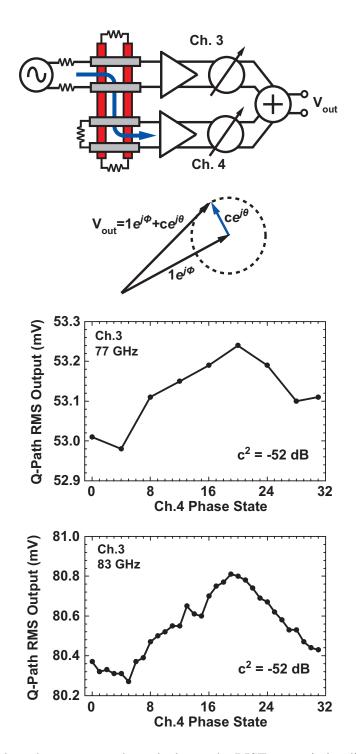

| -                           | 1 1                                                                                                                                                                                               | 74       |

| -                           |                                                                                                                                                                                                   | 75       |

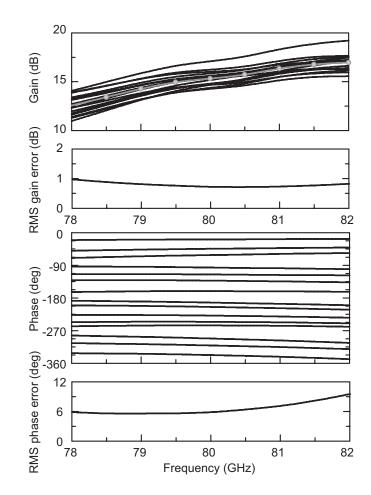

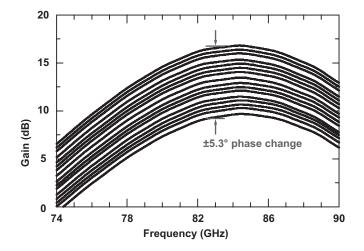

| Figure 5.14:                | Measured (a) gain, (b) phase response and (c) rms gain and phase error for                                                                                                                        | -        |

| Figure 5.15:                | 16 phase states                                                                                                                                                                                   | 76       |

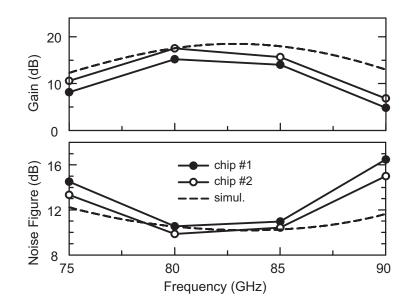

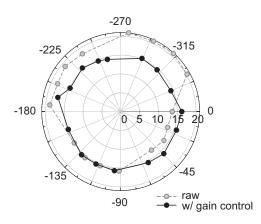

|                             | · · · ·                                                                                                                                                                                           | 77       |

| Figure 5.16:                |                                                                                                                                                                                                   | 78       |

| -                           | -                                                                                                                                                                                                 | 78       |

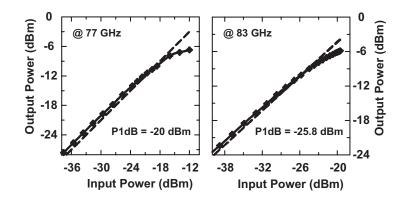

| Figure 5.18:                | Measured $P_{1dB}$ at 77 GHz and 83 GHz for VGA = 0000 (max.)                                                                                                                                     | 80       |

| Figure 5.19:                | Measured gain of a single channel at different temperatures                                                                                                                                       | 80       |

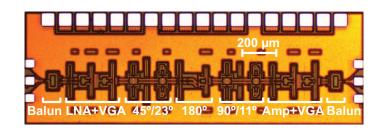

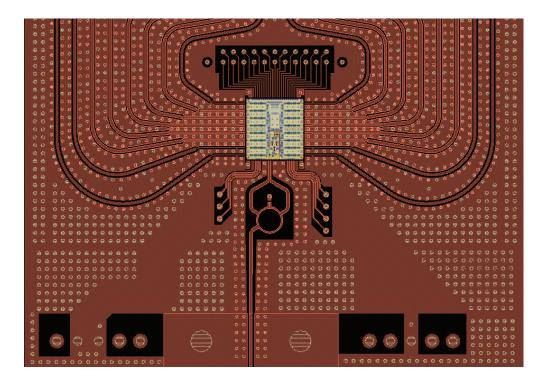

| Figure 5.20:                | Photograph of (a) single channel (2.0 x 0.65 mm <sup>2</sup> ) and (b) 16-element                                                                                                                 |          |

| Figure 5.21.                | phased arrays $(5.5 \times 5.8 \text{ mm}^2)$<br>Leakage between two channels due to the BIST transmission-line and mea-                                                                          | 81       |

| 1 iguie 5.21.               |                                                                                                                                                                                                   | 82       |

| Figure 6.1:                 | PCB board design for measuring the antenna pattern using the designed 76–                                                                                                                         |          |

| Figure 6.2:                 | PCB board design for measuring the antenna pattern using the designed 76–                                                                                                                         | 86<br>87 |

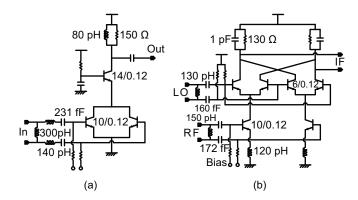

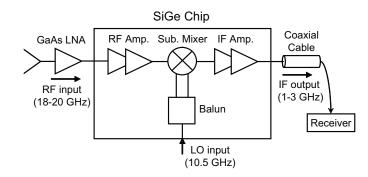

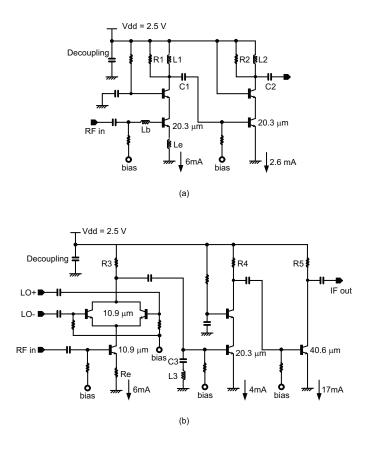

| Figure A.1:<br>Figure A.2:  | (a) Input RF amplifier (two stage design), (b) subharmonic mixer and IF                                                                                                                           | 90       |

|                             | 1                                                                                                                                                                                                 | 90       |

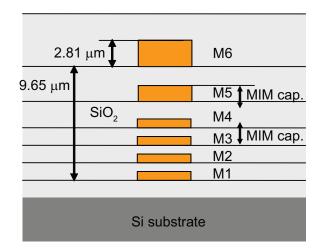

| Figure A.3:<br>Figure A.4:  | Metal stack layer of the Jazz SBC18HAZ                                                                                                                                                            | 92       |

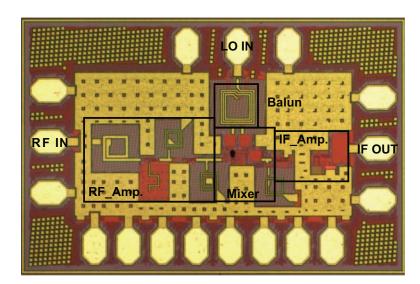

|                             | $mm^2$ including all pads.)                                                                                                                                                                       | 92       |

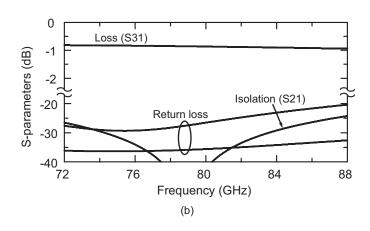

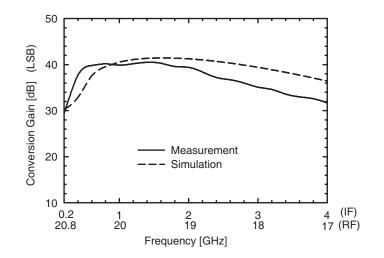

| Measured conversion gain of the subharmonic down-converter                | 93                                                      |

|---------------------------------------------------------------------------|---------------------------------------------------------|

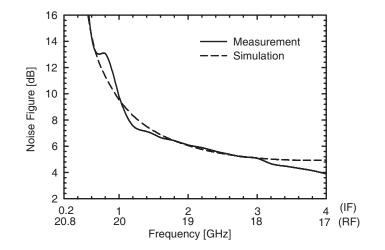

| Measured noise figure of the subharmonic down-converter                   | 93                                                      |

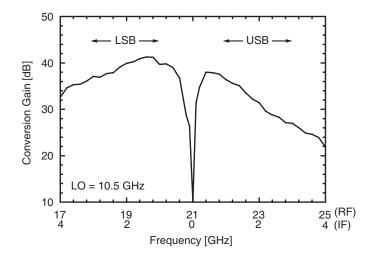

| Measured LSB and USB conversion gain of the subharmonic down-converter.   | 94                                                      |

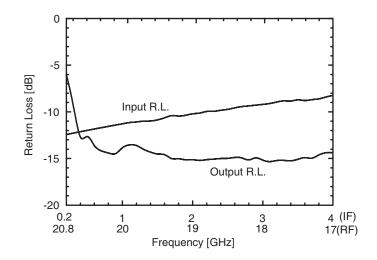

| Measured input and output return loss of the subharmonic down-converter.  | 95                                                      |

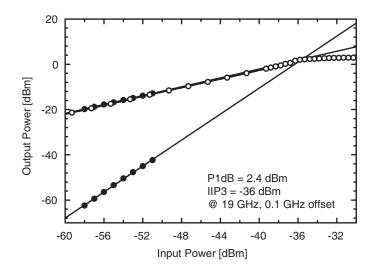

| Measured $P_{1dB}$ and IIP <sub>3</sub> of the subharmonic down-converter | 95                                                      |

|                                                                           | Measured noise figure of the subharmonic down-converter |

# LIST OF TABLES

| Table 4.1: | Comparison of three different topologies                              | 38 |

|------------|-----------------------------------------------------------------------|----|

| Table 4.2: | Phase Shifter Component values.                                       | 43 |

| Table 4.3: | Current consumption vs Temperature                                    | 57 |

| Table 4.4: | Summary of phased array performance.                                  | 58 |

| Table 5.1: | Phase shifter component values                                        | 66 |

| Table 5.2: | Performance Comparison                                                | 83 |

| Table A.1: | Measured LO and 2LO leakage at the RF and IF ports for an LO power of |    |

|            | 2.5 dBm                                                               | 94 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to sincerely thank my dissertation advisor Prof. Gabriel M. Rebeiz for his guidance and unlimited technical and moral support throughout my doctoral studies at University of California, San Diego (UCSD). His questing mind and endless enthusiasm for the research always inspired me and those were the strong motivation in my research whenever I fell into a slump. With his very well-maintained state-of-the-art labs and his expertise in the fields of the electro-magnetic wave, antenna and wireless communication, and remarkable insight on the phased arrays provided the best environment for top-notch research and the most efficient experiments and measurements. I learned so much from him - not only the academic lessons, but also valuable life lessons I will cherish for the rest of my life. Without his advice and support, all this work could not be finished. It was a great pleasure to know him and work with him, and it is a great honor for me to be one of his students.

Next, I would like to thank my dissertation committee members, Prof. Lawrence E. Larson, Prof. James Buckwalter, Prof. Gert Cauwenberghs and Prof. William S. Hodgkiss for their time, interest, and valuable comments. The distinguished faculty is the strongest driving force that makes UCSD one of the top engineering school in the world.