# **UCLA**

# **UCLA Previously Published Works**

# **Title**

Fully integrated CMOS nano-particle assembly circuit for biological detections

## **Permalink**

https://escholarship.org/uc/item/8vj4z0ns

# **Journal**

Analog Integrated Circuits and Signal Processing: An International Journal, 62(1)

## **ISSN**

1573-1979

#### **Authors**

Zhang, Lei Chang, Yu Yu, Zhiping et al.

## **Publication Date**

2010

#### DOI

10.1007/s10470-009-9320-z

Peer reviewed

#### MIXED SIGNAL LETTER

# Fully integrated CMOS nano-particle assembly circuit for biological detections

Lei Zhang · Yu Chang · Zhiping Yu · Xiangqing He · Yong Chen

Received: 10 October 2007/Revised: 22 May 2009/Accepted: 22 May 2009/Published online: 12 June 2009 © The Author(s) 2009. This article is published with open access at Springerlink.com

**Abstract** Recently, along with the booming of research and production of CMOS Integrated Bio-sensing System, selective assembly of organic nano-particles on the on-chip electrodes, which serves for specific bio-sensing and detection purposes, is in high demand in areas like biological analysis and detection, DNA probing and surveying systems and etc. In this paper, a fully integrated bio-circuit targeting at electrical selective assembly of charged nanoparticles is proposed and designed in SMIC 0.18 µm CMOS mixed signal process. The proposed circuit integrates the 16 pixels of 19  $\mu$ m  $\times$  19  $\mu$ m electrode array, counter electrode, potentiostat circuit, digital decoding circuit, as well as control logics on a single chip, and provides a rail-to-rail range of assembling voltage, a potential resolution of 8 bit, and a maximal assembling current up to 459 µA, biased at a current of 1 µA. Meanwhile, a novel electrode-reuse scheme is also proposed to further simplify the architecture and save chip area as well, without degrading the functionalities. Experimental results from on-chip selective assembly of 50 nm polystyrene nano-particles are included and discussed to verify the feasibility of the proposed circuits.

$\begin{tabular}{ll} \textbf{Keywords} & CMOS & nano-particle & assembly \\ circuit & (NAC) \cdot Fully & integration \cdot Selective & assembly \cdot \\ On-chip & potentiostat \cdot Electrode-reuse \\ \end{tabular}$

L. Zhang (⋈) · Z. Yu · X. He Institute of Microelectronics, Tsinghua University, Beijing 100084, People's Republic of China e-mail: zl99@mails.tsinghua.edu.cn

Y. Chang · Y. Chen Department of Mechanical and Aerospace Engineering, University of California, Los Angeles 90095, USA

#### 1 Introduction

Biomedical technology emerges since the past century and is believed to be one of the most promising industries in the twenty-first century together with micro- and nano-electronics industries. Recently, DNA molecule based biosensors are being reported by many famous literatures [1–3]. Naturally, the integrated bio-sensing system (IBS) which monolithically integrates the biomedical electrode arrays and ASICs in a single chip is avidly expected to greatly reduce the cost of common sensors used in the hospitals and markets.

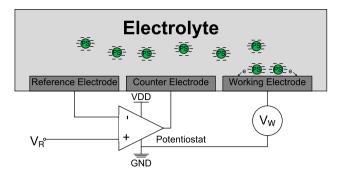

Actually, some integrated DNA sensing circuits have been implemented in standard CMOS process [4–7], which firstly relies on gold–sulphur (Au–S) bond to self-assemble a DNA monolayer on the electrode surface, and detects the complementary DNA molecules in the electrolyte in terms of electric current by applying a voltage on the activated electrode. However, the non-specific Au–S bond can not selectively assemble the DNA monolayer on the target working electrode, thus limiting the specificity and diversity of the following sensing procedure. Although efforts have been made for the patterning of DNA assembly by introducing the electric releasing scheme, it becomes complicated in process and time consuming. Therefore, the selective assembling scheme is explored and realized in this paper, and the principle is shown in Fig. 1.

In this approach, nano-particles with fluorophores in side devolve in the electrolyte buffer and become negatively (or positively) charged particles, as a positive (or negative) voltage  $V_W$  is applied on the working electrode with respect to the reference voltage, these charged nanoparticles are attracted by the electric field toward the activated working electrode, and eventually immobilized on the surface specifically due to electrochemical reactions.

Fig. 1 Principles of nano-particles assembly

The current required for the reaction is provided by the potentiostat circuit from the counter electrode, which stabilizes the electrolyte potential at  $V_R$  from the feedback mechanism.

Furthermore, since the reference electrode serving for voltage reference and electrolyte potential control purposes in conventional architecture also introduces complexities in fabrication and extra expenses in chip area, therefore, in this paper, a fully integrated nano-particle assembly circuit (NAC) with a novel electrode-reuse architecture is designed in SMIC 0.18 µm CMOS mixed signal process. In this architecture, the electrode array combines both the functionalities of working and reference electrodes, which reduced the complexity of fabrication and substantially saved the chip area. The proposed circuit is further verified by experimentations from the selective assembly of 50 nm negatively charged polystyrene nano-particles (PS) in the mixture buffer of water and methanol onto address-activated working electrode by applying an assembling voltage, which makes it being a promising candidate of improving bio-sensing specificity and diversity of IBS in the future.

#### 2 Circuit design and descriptions

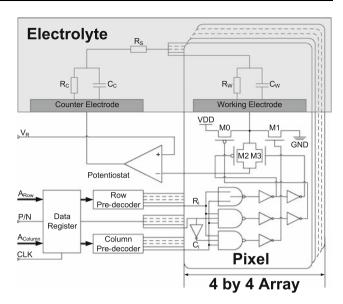

The system topology of proposed CMOS NAC is illustrated in Fig. 2. It is designed with a 16 pixel of 19  $\mu m \times 19 ~\mu m$  working electrode array and a 140  $\mu m \times 19 ~\mu m$  counter electrode. A two-stage address decoding approach (predecoding and pixel decoding) is introduced to selectively activate the working electrodes of the NAC. An on-chip potentiostat circuit is implemented to control the electrolyte potential and provide electrochemical current by utilizing the negative feedback mechanism during assembly process.

#### 2.1 Electrode-reuse architecture

As is mentioned in Sect. 2, the electrode-reuse architecture is proposed in the NAC to reduce the complexities in circuit design and fabrication and save chip area as well,

Fig. 2 System schematics of proposed CMOS NAC

which is described in Fig. 2. It can be seen that electrodes of all 16 pixels are either connected to the negative input of potentiostat circuit or shorted to the power supply VDD or ground GND by four transistors  $M_0$ ,  $M_1$ ,  $M_2$ , and  $M_3$ , depending on the state of that pixel. In fact, controlled by the pre-decoding logic and pixel logics, electrode of the activated pixel becomes the working electrode connected to VDD or GND, where nano-particles are assembled, while all the other inactivated electrodes are reused as the reference electrode in Fig. 1 to stabilize the electrolyte potential at  $V_R$ , which in turn saves the hardware expense of reference electrode.

Up on the rising edge of the clock CLK, logic states of  $A_{Row}$ , P/N, and  $A_{Column}$  are locked into the data register and propagating to the decoding stage. The decoding mechanism is realized by the two-stage decoding logic composed of row-column pre-decoder and pixel decoder. The standard transformation from input binary code to 1/N code is performed by the pre-decoder circuit, with the output being logic signals  $R_i$  and  $C_i$  for an arbitrary pixel i, where i = 1, 2,...,16, as are shown in Fig. 2. If and only if both  $R_i$  and  $C_i$ are activated (logic "11"), the electrode is shorted to VDD or GND as working electrode by the pixel logic gates, depending on the logic "1" or "0" of the state signal P/N (in fact, the logic "1" state of P/N introduces a positive assembling voltage of VDD  $-V_R$ , while logic "0" implies a negative assembling voltage of  $-V_R$  on the activated electrode); while all the other combinations of  $R_i$  and  $C_i$ (logic "00", "01", and "10") will connect it to the negative input terminal of potentiostat circuit thus functioning as the reference electrode. The true table of the proposed electrode-reuse architecture is illustrated in Table 1.

Table 1 True table of the electrode-reuse architecture

| $R_i$ | $C_i$ | P/N | Electrode state |

|-------|-------|-----|-----------------|

| 0     | ×     | ×   | Reference       |

| ×     | 0     | ×   | Reference       |

| 1     | 1     | 0   | Working (GND)   |

| 1     | 1     | 1   | Working (VDD)   |

|       |       |     |                 |

Table 2 Specifications of CMOS NAC from the experimentations

| Typical assembling voltage  | $1.8 \pm 0.2 \text{ V}$                  |

|-----------------------------|------------------------------------------|

| Min. assembling voltage     | 1 V                                      |

| Electrolyte potential range | 0-1.8 V                                  |

| Max. potential variation    | 5 mV                                     |

| Assembling current range    | $\sim\!10$ nA to $\sim\!100~\mu\text{A}$ |

| Max. signal bandwidth       | <100 kHz                                 |

|                             |                                          |

#### 2.2 Circuit design of on-chip potentiostat

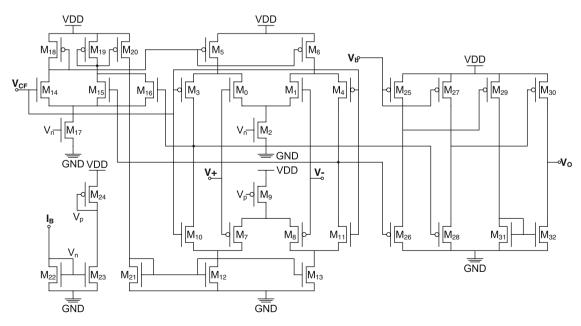

The potentiostat circuit serving for stabilizations of electrolyte potential and accommodation of electrochemical current [7–9] is the major part of the proposed NAC. To satisfy specifications in Table 2, in the NAC, an OTA with rail-to-rail input common-mode range and Class-AB output stage is introduced to serve as the potentiostat circuit, which is depicted in Fig. 3.

The potentiostat OTA uses the complimentary folded-cascode input stage composed of transistor  $M_0$  to  $M_{13}$  to

achieve the rail-to-rail input common-mode range to enable the required assembling voltage, and reduce the input-referred noise to stabilize the potential as well, while incorporates the Class-AB output stage composed of transistor  $M_{29}$  to  $M_{32}$  to provide the maximized loading capability and accommodate the assembling current requirement. Transistors  $M_{14}$  to  $M_{21}$  function as the common-mode feedback circuit and provide biasing voltage for the folded-cascode input stage.  $M_{25}$  to  $M_{28}$  are two source follower to match the DC voltage between stages, while the other biases are served by  $M_{22}$  to  $M_{24}$  from a current  $I_B=1~\mu A$ .

Post simulations are performed to verify the proposed potensiostat OTA. The results show that biasing at a current of 1  $\mu$ A the circuit is capable of providing a rail-to-rail input and output dynamic range and a unit gain bandwidth up to 42.7 MHz, while the output current headroom,  $I_{max}$ , is over 450  $\mu$ A, which meet the specifications in Table 2.

The potential variation is due to: (I) finite transconductance of the potentiostat OTA, (II) input referred noise, and (III) the input referred offset. If  $G_m^{DC}$  is the DC transconductance of the potentiostat OTA, the potential variation,  $V_{ft}$ , due to (I) can be expressed as

$$\frac{V_{ft} = I_{max}}{G_{pc}^{DC}} \tag{1}$$

According to the noise theory, transistor  $M_0$ ,  $M_1$ ,  $M_5$ ,  $M_6$ ,  $M_7$ ,  $M_8$ ,  $M_{12}$ , and  $M_{13}$  in the first stage contribute to the overall noise. The noise power spectral density,  $S_I$ , in a MOS transistor is given by [10, 11]

Fig. 3 Transistor level implementation of proposed potentiostat OTA with rail-to-rail input common-mode range and Class-AB output stage

Table 3 Summary of performances of proposed potentiostat OTA

| •                           | •                                  |                                    |                                   |

|-----------------------------|------------------------------------|------------------------------------|-----------------------------------|

| Parameters                  | $V_{CM} = 0 \text{ V}$             | $V_{CM} = 0.9 \text{ V}$           | $V_{CM} = 1.8 \text{ V}$          |

| DC transconductance         | 2.22 S                             | 5.43 S                             | 3.90 S                            |

| 3 dB bandwidth              | 1.97 kHz                           | 2.07 kHz                           | 1.94 kHz                          |

| Phase margin                | >75°                               | >80°                               | >75°                              |

| Max. output pull current    | 451 μΑ                             | 450 μΑ                             | -                                 |

| Max. output push current    | -                                  | 459 μΑ                             | 459 μΑ                            |

| Input referred offset       | 3.51 mV                            | 1.60 mV                            | 2.75 mV                           |

| Input referred noise        | $61.8 \text{ nV}/\sqrt{\text{Hz}}$ | $38.2 \text{ nV}/\sqrt{\text{Hz}}$ | $57.7 \text{nV}/\sqrt{\text{Hz}}$ |

| Overall potential variation | 4.12 mV                            | 1.93 mV                            | 3.24 mV                           |

| Potential resolution        | 8 bit                              | 9 bit                              | 9 bit                             |

| DC power dissipation        | $40.4~\mu W$                       | 50.3 μW                            | 58.0 μW                           |

| Power supply                | 1.8 V                              | 1.8 V                              | 1.8 V                             |

$$\frac{S_I = 4\gamma k T g_m + K_F I_{ds}^{A_F}}{f^{E_F} C_{ox} W L} \tag{2}$$

where  $\gamma$  is the thermal noise parameter,  $g_m$  is the transconductance,  $I_{ds}$  is the drain-source current,  $C_{ox}$ , W, and L are the gate capacitance per unit area, transistor width and length, respectively, and k, T, and f are the Boltzman constant, temperature, and frequency, respectively.  $K_F$ ,  $A_F$ , and  $E_F$  are flicker noise parameters with the typical values of  $2 \times 10^{-25}$ , 2, and 1, respectively. Since the corner frequency  $f_c$ , where thermal noise and flicker noise exhibit the same power density, is calculated as 5.4 Hz by using parameters provided by the foundry, much smaller than the unit gain bandwidth, therefore, flicker noise is negligible in the proposed OTA, and the input referred noise voltage  $\overline{V_{im}}$  can be characterized by

$$\frac{\overline{V_{im}}^2 = 8\gamma k T (g_{m0} + g_{m5} + g_{m7} + g_{m12})}{(g_{m0} + g_{m7})^2}$$

(3)

where  $g_{mj}$  is the transconductance of transistor  $M_j$ ,  $j = 0, 1, \dots, 32$ .

$\overline{V_{im}}$  can be diminished by increasing the biasing currents and aspect ratios of the input differential pairs, but trades off with the power consumption and the physical area. The spectral density input referred noise of proposed OTA on different common-mode input voltages are shown in Table 3.

Monte-Carlo simulation is also performed to characterize the input referred offset by utilizing the mismatch parameters provided by the foundry, and the results are also shown in Table 3. In the worst case with  $V_{CM}=0$  V, the overall potential variation due to the above three issues is 4.12 mV, which implies a 8 bit of potential resolution and satisfies the boundary condition in Table 2. The other circuit performances are summarized in Table 3.

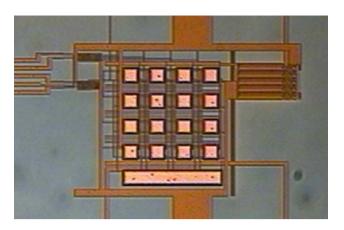

Fig. 4 Die micrograph of the CMOS NAC chip. The electrode array occupies only 170  $\mu$ m imes 140  $\mu$ m of chip area

# 3 Verification and experimentation

The proposed NAC is designed in SMIC 0.18 µm CMOS mixed signal process with 1.8 V of power supply, and the electrode topology is shown in the die micrograph illustrated in Fig. 4. The selective assembly of 50 nm negatively charged PS is validated by experimentations in terms of fluorescence and atomic force microscopy (AFM), which in turn verify the feasibility of the proposed NAC.

The 50 nm PS internalized with fluorophores in the mixture buffer of water and methanol with the concentration of 0.1% are utilized as a prototype to demonstrate the selective nano-assembly in the experiment. Meanwhile, contrast experiments, fluorescence, as well as surface morphology are also investigated for further verifications.

In the experiment, a +1.8 V of assembling voltage of the activated working electrode is applied with respect to the electrolyte potential. According to the decoding scheme, the 16 electrodes in Fig. 4 are addressed as  $\langle 0000 \rangle$ ,  $\langle 0001 \rangle$ , ...,  $\langle 1111 \rangle$  from the top-left to top-right horizontally, and from the top row to the bottom row vertically.

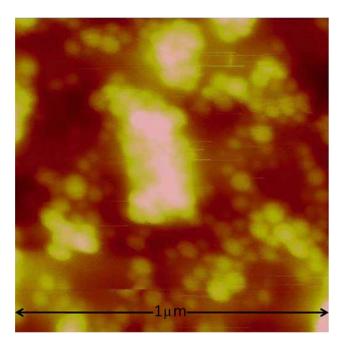

Firstly, the  $\langle 0000 \rangle$  electrode is activated for 90 s with pure water as the electrolyte, and no fluorescence is observed as is shown in Fig. 5(a). Then electrode  $\langle 0001 \rangle$  is activated for 90 s in the 1:1 mixture buffer of water and methanol with PS, and fluorescence is observed in Fig. 5(a). Thirdly, electrode  $\langle 0010 \rangle$  is activated for the mixture buffer without nano-particles, as is expected, no fluorescence is observed in Fig. 5(b). Since the green emission nature of PS is foregone from the previous experiment, it can be concluded from the contrast experiment above that the PS are evidently assembled on electrode  $\langle 0001 \rangle$  by the NAC. The AFM image in Fig. 6 shows the surface morphology of electrode  $\langle 0001 \rangle$ , which gives the direct evidence of the assembled 50 nm PS.

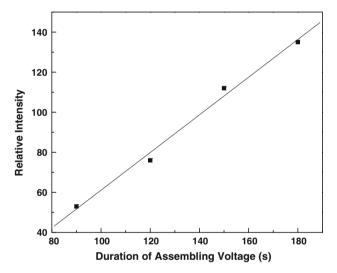

In order to characterize the time dependency of fluorescent intensity, electrode  $\langle 0011 \rangle$ ,  $\langle 0100 \rangle$ ,  $\langle 0101 \rangle$ , and  $\langle 0110 \rangle$  are

**Fig. 5** Experimental results of 50 nm PS assembly on the activated working electrodes of the CMOS NAC chip

(a) Fluorescent picture of the 50 nm PS assembly on electrode (0001) and the contrast experiment on electrode (0000) by using pure water. The duration of applied voltage is 90 s.

(b) Fluorescent picture of the 50 nm PS assembly on electrode ⟨0001⟩ and the contrast experiment on electrode ⟨0010⟩ by using the mixture buffer without PS. The duration of applied voltage is 90 s.

(c) Fluorescent picture of the 50 nm PS assembly on electrodes (0011), (0100), (0101), and (0110) of different durations of applied voltages, which are 90 s, 120 s, 150 s, and 180 s, respectively. The electrode (1110) is also activated for 90 s to characterize the dependency of assembling rate on the distance apart from the counter electrode.

**Fig. 6** The AFM picture of the electrode surface after the assembly of 50 nm PS. The area shown in this picture is 1  $\mu$ m  $\times$  1  $\mu$ m. It can be seen that the 50 nm PS nano-particles are evidently assembled on the electrode surface of the CMOS NAC

activated for 90, 120, 150, and 180 s, respectively. As is expected, Fig. 5(c) shows the gradual increment of the fluorescent intensity, while the linear time dependency of the fluorescent intensity is further illustrated Fig. 7, which implies the quantity of assembled PS on the activated electrode is proportional to the duration of the assembling voltage.

Finally, electrode  $\langle 1110 \rangle$  is also activated for 90 s, however, it appears brighter than electrode  $\langle 0001 \rangle$  and  $\langle 0011 \rangle$ , this is because it sits closer to the counter

Fig. 7 The relative fluorescent intensity as a function of duration of the assembling voltage on electrodes  $\langle 0011 \rangle$ ,  $\langle 0100 \rangle$ ,  $\langle 0101 \rangle$ , and  $\langle 0110 \rangle$ , respectively. The *solid squares* represent the relative fluorescent intensities, while the line is the linear fit of the results

electrode, nano-particles feel stronger electric field on  $\langle 1110 \rangle$  than on the other two electrodes.

#### 4 Conclusion

In this paper, a fully integrated electrode-reuse NAC targeting at electrical selective assembly of charged nanoparticles is proposed and designed in SMIC 0.18  $\mu$ m CMOS mixed signal process. The circuit integrates the 16 pixels of 19  $\mu$ m  $\times$  19  $\mu$ m electrode array, 140  $\mu$ m  $\times$  19  $\mu$ m counter electrode, potentiostat OTA, digital decoding circuit, as well as control logics on a single chip, and is capable of providing

a rail-to-rail dynamic range of assembling voltage, a potential resolution of 8 bit, and a maximal assembling current up to 459 µA, biased at a current of 1 µA. Meanwhile, a novel electrode-reuse scheme is also proposed to further simplify the electrode architecture and save chip area as well, without degrading the functionalities. Experimental results show that the proposed NAC is feasible of selectively assembling the 50 nm PS prototype on the activated working electrode by the applied voltage, while the quantity of assembled PS is proportional to the duration of the assembling voltage. In fact, the 50 nm PS particle can be conjugated with multiple bio-species (biotin, streptavidin, or DNA molecule) on the surface, and selectively assembled on the activated working electrode from the proposed approach, which significantly improves the specificity and diversity of the following sensing/detection procedure and simplifies the process, comparing to the traditional self-assembly method relying on the Au-S chemical bonds.

**Acknowledgements** This work is supported by the National Science Foundation of China (NSFC) under grants No. 60236020 and No. 90307016 and by a grant from Intel. The work is also supported by the University Program of SMIC. Meanwhile, this work is partly supported by a private research grant provided by Dr. Dan Yang in CA, USA.

**Open Access** This article is distributed under the terms of the Creative Commons Attribution Noncommercial License which permits any noncommercial use, distribution, and reproduction in any medium, provided the original author(s) and source are credited.

#### References

- Gregory Drummond, T., Hill, M. G., & Barton, J. K. (2003). Electrochemical DNA sensors. *Nature Biotechnology*, 21(10), 1192–1199.

- Li, Z., Chen, Y., Li, X., Kamins, T. I., Nauka, K., & Williams, R. S. (2004). Sequence-specific label-free DNA sensors based on silicon nanowires. *Nano Letters*, 4(2), 245–247.

- Guiducci, C., Stagni, C., Zuccheri, G., Bogliolo, A., Benini, L., Samor, B., & Ricc, B. (2002). A biosensor for direct detection of DNA sequences based on capacitance measurements. In *Pro*ceeding of ESSDERC 2002 (pp. 479–482).

- Chen, X., Jiong, L., Yijin, W., Cheng, L., Zuhong, L., & Mansun, C. (2005). A CMOS-compatible DNA microarray using optical detection together with a highly sensitive nanometallic particle protocol. *IEEE Transactions on Electronic Devices Letters*, 26(4), 240–242.

- Han, S. -J., Yu, H., Murmann, B., Pourmand, N., & Wang S. X. (2007). A high-density magnetoresistive biosensor array with drift-compensation mechanism. In *ISSCC Digest of Technical Papers*, Feb 2007, (pp. 168–594).

- Stagni, C., Esposti, D., Guiducci, C., Paulus, C., Schienle, M., & Augustyniak, M., et al. (2006). Fully electronic CMOS DNA detection array based on capacitance measurement with on-chip analog-to-digital conversion. In *ISSCC Digest of Technical Papers*, Feb 2006, (pp. 69–78).

- 7. Augustyniak, M., Paulus, C., Brederlow, R., Persike, N., Hartwich, G., & Schmitt-Landsiedel, D., et al. (2006). A 24 × 16

- CMOS-based chronocoulometric DNA microarray. In *ISSCC Digest of Technical Papers*, Feb 2006, (pp. 59–68).

- 8. Prakash, S. B., Abshire, P., Urdaneta, M., Christophersen, M., & Smela, E. (2006). A CMOS potentiostat for control of integrated MEMS actuators. In *ISCAS 2006 Proceedings*, May 2006, (pp. 5555–5558).

- Thewes, R., Paulus, C., Schienle, M., Hofmann, F., Frey, A., & Schindler-Bauer, P., et al. (2005). A CMOS medium density DNA microarray with electronic readout. *Materials Research Society Symposia Proceedings*, 869, D3.4.1–D3.4.11.

- Tsividis, Y. P. (1988). Operation and modeling of the MOS transistor. New York: McGraw-Hill.

- Sarpeshkar, R., Delbruck, T., & Mead, C. A. (1993). White noise in MOS transistors and resistors. *IEEE Circuits Devices Maga*zine, 9(6), 23–29.

Lei Zhang graduated with honors from the Department of Electronic Engineering Tsinghua University, Beijing, China, in 2003, and received his M.S. and Ph.D degrees in Tsinghua University, Beijing, China, in 2008. Recently, he is working as a postdoctoral fellow in University of California, Los Angeles, USA. His research interests cover mixed-signal and radio-frequency integrated circuits, DNA sensor fabrication and characterization, CMOS

integrated biosensing system, as well as the design and implementation of neuromorphic circuits and intelligent machines.

Yu Chang received his B.S. degree in Chemistry in National Taiwan University, Taipei, and continued his study in University of California, Los Angeles, where he achieved the M.S. degree in the biomedical interdepartmental program. By 2008, he received the Ph.D degree in the same program. His research interests cover bio-MEMS/NEMS, biomolecular electrophorectic printing lithography, and protein/DNA detections.

Zhiping Yu graduated from Tsinghua University, Beijing, China, in 1967 with B.S. degree. He received his M.S. and Ph.D degrees from Stanford University, Stanford, CA, USA in 1980, and 1985, respectively. He is presently the professor and deputy director in the Institute of Microelectronics, Tsinghua University, Beijing, China. From 1989 to 2002, he has been a senior research scientist in the Department of Electrical Engineering in Stanford University,

USA, while serving as the faculty member in Tsinghua. He returned to Tsinghua full time since Sept. 2002 and holds Pericom Microelectronics Professorship (2002–2004) established by Pericom Semiconductor Corp. in San Jose, US. His research interests include device simulation for nano-scale MOSFETs, quantum transport in nanoelectronic devices, compact circuit modeling of passive and active components in RF CMOS, and numerical analysis techniques.

Xiangqing He received the B.S. degree from Tsinghua University, Beijing, China, in 1970. She is a Professor in the Institute of Microelectronics, Tsinghua University, Beijing, China. Her research interest focuses on design for analog circuit and memory.

Yong Chen received his M.S. and Ph.D degrees in material science and engineering from the University of California, Berkeley, in 1994 and 1996, respectively. He is a Professor of mechanical and aerospace engineering, and material science and engineering, with the California NanoSystems Institute, University of California, Los Angeles (UCLA). His current research focuses on nano-fabrication, nano-electronic device and circuit, and nano-scale biological and medical sensors.