### **UC Santa Barbara**

### **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

High-Power CMOS SOI Switching and Applications in RF Signal Processing

### **Permalink**

https://escholarship.org/uc/item/8tt1c0q4

### **Author**

Hill, Cameron

### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

# High-Power CMOS SOI Switching and Applications in RF Signal Processing

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Cameron W. Hill

### Committee in charge:

Professor James F. Buckwalter, Chair

Professor Forrest Brewer

Professor Umesh Mishra

Professor Mark Rodwell

Professor Loai Salem

| The Dissertation of Cameron W. Hill is approved. |  |  |  |

|--------------------------------------------------|--|--|--|

|                                                  |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

| Defense E and D                                  |  |  |  |

| Professor Forrest Brewer                         |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

| Professor Umesh Mishra                           |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

| Professor Mark Rodwell                           |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

| Professor Loai Salem                             |  |  |  |

| Troicssor Loar Salem                             |  |  |  |

|                                                  |  |  |  |

|                                                  |  |  |  |

| Professor James F. Buckwalter, Committee Chair   |  |  |  |

High-Power CMOS SOI Switching and Applications in RF Signal Processing

Copyright © 2020

by

Cameron W. Hill

For Grampa.

### Acknowledgements

The last five years in which I have been working towards this dissertation have gone smoother than I could have imagined, especially once class and exam requirements were filled. Stories of easy sailing through a PhD program are somewhat uncommon, so in my case I particularly have to thank my adviser, Professor Jim Buckwalter. Jim has been humble and patient throughout the entire process, always giving me good direction, and listening to all of my ideas - good and bad. As the size of his group has grown from 5 to 15 or so students since I joined, he has always made the time to meet each of us every week and provide detailed feedback on all of our work. This effort from Jim on a daily basis is a large part of what makes each of his students successful, and for that I thank him.

I would also like to acknowledge the other committee members, Professors Forrest Brewer, Umesh Mishra, Mark Rodwell, and Loai Salem for their help over the years. Whether it has been on class work, soldering tips in the lab, providing new projects and directions, their contribution has been invaluable.

The Buckwalter RFIC group members have been extremely helpful over the years. Particularly my main co-authors, Hussam AlShammary and Ahmed Humza. Thanks as well to Kang Ning, Navid Hosseinzadah, Luis Valenzuela, Jeff Chien, Everett O'Malley, Ghazal Movaghar, Andrea Arias, and Mayank Singh.

I also have to acknowledge the Bucky Ballers - Kyle Clark, Greg Gate, Greg Ekberg, Zongheng Wang, Chris Kirby, Evan Jantzen, Manny Zayas, and Ricky Rustic, for showing up to ball every week. Too bad we could never get those shirts...

Finally thanks to my parents for supporting my education despite their continuous pleas for me to just "go get a job."

### Curriculum Vitæ Cameron W. Hill

#### Education

| 2020 | Ph.D. Electrical and Computer Engineering (Expected), University           |  |  |  |  |  |

|------|----------------------------------------------------------------------------|--|--|--|--|--|

|      | of California, Santa Barbara.                                              |  |  |  |  |  |

| 2015 | M.E. Electrical and Computer Engineering, Stevens Institute of Technology. |  |  |  |  |  |

| 2015 | B.E. Electrical and Computer Engineering, Stevens Institute of Technology. |  |  |  |  |  |

### **Publications**

- C.1 H. AlShammary, C. Hill, A. Hamza and J. F. Buckwalter, "Code Selective Filters in CMOS Processes for Full Duplex Communication and Interference Mitigation," GOMACTech, March, 2018.

- C.2 C. Hill, C. S. Levy, H. Al Shammary, A. Hamza and J. F. Buckwalter, "A 30.9 dBm, 300 MHz 45-nm SOI CMOS Power Modulator for Spread-Spectrum Signal Processing at the Antenna," 2018 IEEE/MTT-S International Microwave Symposium - IMS, Philadelphia, PA, 2018, pp. 423-426

- C.3 H. AlShammary, C. Hill, A. Hamza and J. F. Buckwalter, "A  $\lambda/4$ -Inverted N-path Filter in 45-nm CMOS SOI for Transmit Rejection with Code Selective Filters," 2018 IEEE/MTT-S International Microwave Symposium IMS, Philadelphia, PA, 2018, pp. 1370-1373.

- C.4 A. Hamza, H. AlShammary, C. Hill and J. Buckwalter, "A 52-dB Self-Interference Rejection Receiver using RF Code-Domain Signal Processing," 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 2019, pp. 1-4.

- C.5 C. Hill, A. Hamza, H. AlShammary and J. F. Buckwalter, "A 1.5-dB Insertion Loss, 34-dBm P1dB Power Modulator with 46% Fractional Bandwidth in 45-nm CMOS SOI," 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2019, pp. 243-246.

- C.6 H. AlShammary, C. Hill, A. Hamza and J. F. Buckwalter, "A Code-Domain RF Signal Processing Front-end for Simultaneous Transmit and Receive with 49.5 dB Self-Interference Rejection, 12.1 dBm Receive Compression, and 34.3 dBm Transmit Compression," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 143-146.

- J.1 C. Hill, C. S. Levy, H. AlShammary, A. Hamza and J. F. Buckwalter, "RF Watt-Level Low-Insertion-Loss High-Bandwidth SOI CMOS Switches," in IEEE Transactions on Microwave Theory and Techniques, vol. 66, no. 12, pp. 5724-5736. Dec. 2018.

- J.2 A. Hamza, H. Alshammary, C. Hill and J. F. Buckwalter, "A Series N-Path Code Selective Filter for Transmitter Rejection in Full-Duplex Communication," in IEEE Microwave and Wireless Components Letters, vol. 29, no. 1, pp. 38-40, Jan. 2019.

- J.3 H. AlShammary, C. Hill, A. Hamza and J. F. Buckwalter, "Code-Pass and Code-Reject Filters for Simultaneous Transmit and Receive in 45-nm CMOS SOI," in IEEE Transactions on Microwave Theory and Techniques, vol. 67, no. 7, pp. 2730-2740, July 2019.

- J.4 C. Hill, A. Hamza, H. AlShammary and J. F. Buckwalter, "Watt-Level, Direct RF Modulation in CMOS SOI With Pulse-Encoded Transitions for Adjacent Channel Leakage Reduction," in IEEE Transactions on Microwave Theory and Techniques, vol. 67, no. 12, pp. 5315-5328, Dec. 2019.

- J.5 H. AlShammary, A. Hamza, C. Hill and J. F. Buckwalter, "A Reconfigurable Spectrum-Compressing Receiver for Non-Contiguous Carrier Aggregation in CMOS SOI," in IEEE Journal of Solid-State Circuits, vol. 55, no. 2, pp. 261-271, Feb. 2020.

- J.6 H. Alshammary, C. Hill, A. Hamza and J. F. Buckwalter, "A Code-Domain RF Signal Processing Front End With High Self-Interference Rejection and Power Handling for Simultaneous Transmit and Receive," in IEEE Journal of Solid-State Circuits, vol. 55, no. 5, pp. 1199-1211, May 2020.

- J.7 A. Hamza, C. Hill, H. AlShammary and J. F. Buckwalter, "High-Rejection RF Code Domain Receivers for Simultaneous Transmit and Receive Applications," in IEEE Journal of Solid-State Circuits.

- P.1 C. Hill, K. Barresi, M. Iyengar, "System and Framework for Multi-dimensionally visualizing and interacting with large data sets" April 2017, US Patent 9613155.

- P.2 C. Hill, J. Buckwalter, "Switching Interval Modulation with Pulse Encoded Transitions," Patent Pending.

#### Abstract

High-Power CMOS SOI Switching and Applications in RF Signal Processing

by

#### Cameron W. Hill

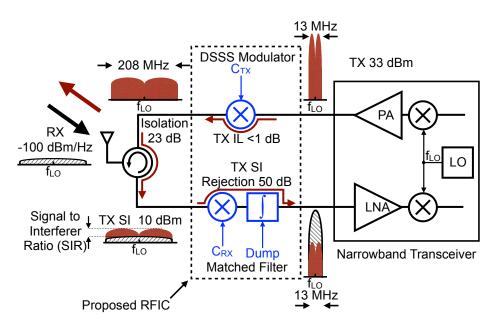

In-band full duplex (IBFD) for increased spectral efficiency but is limited by selfinterference (SI) from the transmitter to the receiver. A combination of antenna-isolation, circulators, analog cancellation, and digital cancellation can achieve high levels of SI cancellation, but is still not enough to enable high-sensitivity IBFD operation. An additional layer of cancellation can be added in the code-domain. RF code-domain DSSS-CDMA approaches have been shown to add an additional 40-50 dB of SI cancellation. However, in order to make code-domain techniques compatible with other SI cancellation techniques, the interface must be RF-invisible and placed directly at the antenna interface. This requires RF-signal processing techniques in both the TX and RX paths of the tranceiver. This work focuses on the development of high-power, high modulation bandwidth switches in cost-effective CMOS SOI processes which enable the transmitter side of code-domain SI without interfering with other self-interference cancellation techniques. First, theory groundwork of trade-offs between linearity, power-handling, and insertion loss in CMOS switches will be discussed. Then a variety of modulators based on this theory with fractional bandwidths (FBWs) approaching 50% and power handling of up to 40 dBm will be explained. Next, signal processing techniques to reduce unnecessary out-of-band (OOB) emissions will be given. Finally, the applications of these techniques in full-duplex systems, and further applications are discussed.

# Contents

| $\mathbf{C}$ | urric | ulum Vitae                                     | vi   |

|--------------|-------|------------------------------------------------|------|

| $\mathbf{A}$ | bstra | $\operatorname{\mathbf{ct}}$                   | viii |

| 1            | Intr  | roduction                                      | 1    |

|              | 1.1   | In-Band Full Duplex and Code-Domain Approaches | 1    |

|              | 1.2   | Introduction to RF Switches                    | 4    |

|              | 1.3   | Comparison of Switch Technologies              | 7    |

|              | 1.4   | Dissertation Organization                      | 10   |

|              | 1.5   | Permissions and Attributions                   |      |

| 2            | Lar   | ge Signal Compression in RF Switches           | 12   |

|              | 2.1   | SOI Switch Modeling                            | 12   |

|              | 2.2   | Extension of Fractional Bandwidth              | 21   |

|              | 2.3   | SPDT design                                    | 24   |

|              | 2.4   | Stacked FET Design and Optimization            | 26   |

|              | 2.5   | Shunt Switches                                 | 31   |

| 3            | Sta   | cked Switch Implementation in Power Modulators | 36   |

|              | 3.1   | Modulator A: Optimized Resistive Modulator     | 37   |

|              | 3.2   | Modulator B: Ladder Inductive Modulator        | 44   |

|              | 3.3   | Modulator C: Reflective Shunt Modulator        | 52   |

|              | 3.4   | Analysis and Comparisons                       | 61   |

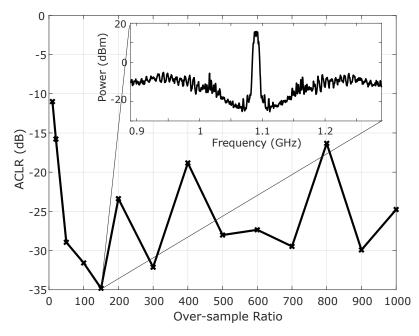

| 4            | Out   | of Band Spurs in RF signal Processors: PET     | 62   |

|              | 4.1   | Introduction                                   | 62   |

|              | 4.2   | Periodic Analysis                              | 64   |

|              | 4.3   | Random Analysis                                | 69   |

|              | 4.4   | Comparison to $\Sigma - \Delta$ Modulators     | 72   |

|              | 4.5   | Measurements                                   | 76   |

| 5  | Applications in Code-Domain Self-Interference Cancellation |                                                 |     |  |  |

|----|------------------------------------------------------------|-------------------------------------------------|-----|--|--|

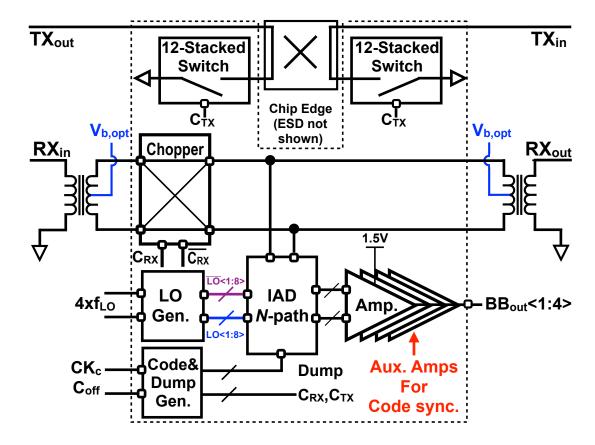

|    | 5.1                                                        | Introduction                                    | 84  |  |  |

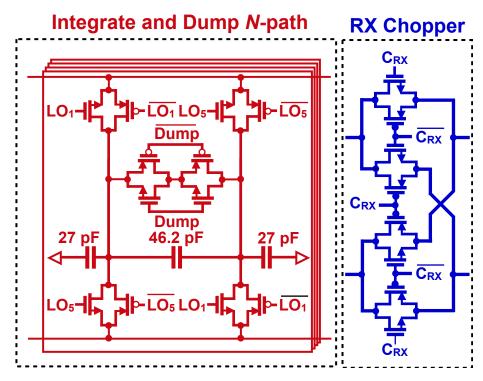

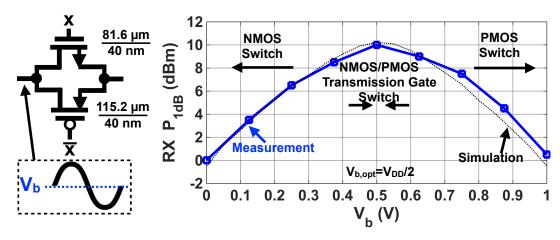

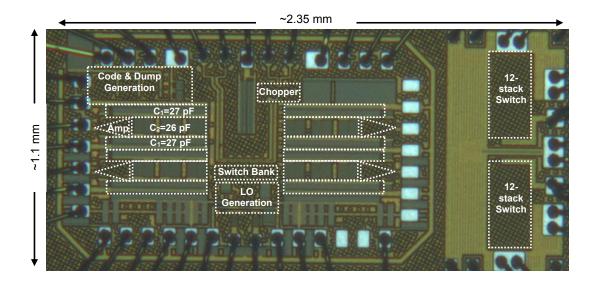

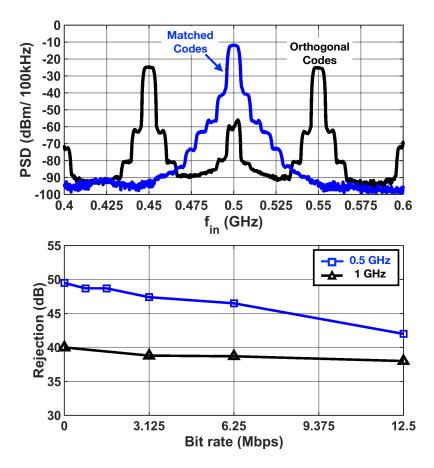

|    | 5.2                                                        | Integrated Code-Domain Tranceiver Module Design | 87  |  |  |

|    | 5.3                                                        | Measurements                                    | 92  |  |  |

| Bi | ibliog                                                     | graphy                                          | 101 |  |  |

## Chapter 1

### Introduction

### 1.1 In-Band Full Duplex and Code-Domain Approaches

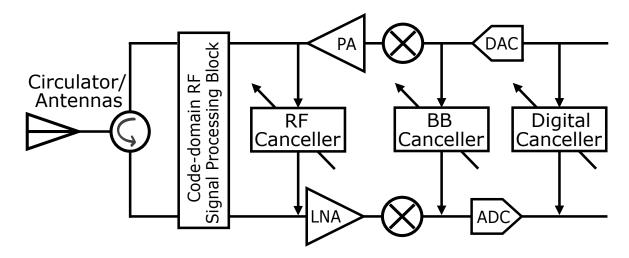

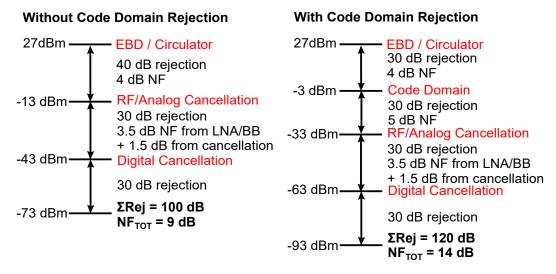

With increasing demand for wireless spectrum, in-band full-duplex (IBFD) has become an active area of research with the goal of transmitting and receiving within the same bandwidth in order to increase the network capacity. [1–3]. A number of techniques have been proposed including digital cancellation [4,5], RF cancellers [6–8], CMOS circulators [9–11], electrically balanced duplexers [12,13] and an example full duplex system diagram is shown in Fig 1.1. Each of these techniques can be combined to add another layer of cancellation. Figure 1.2 shows an outline of how much rejection can be achieved at each stage. If the sensitivity of the receiver is to approach -90 dBm with at transmit power of up to 27 dBm, then the overall rejection needs to be greater than 120 dB (assuming a moderate noise figure), and thus an additional 40-50 dB of rejection is needed when using current technology.

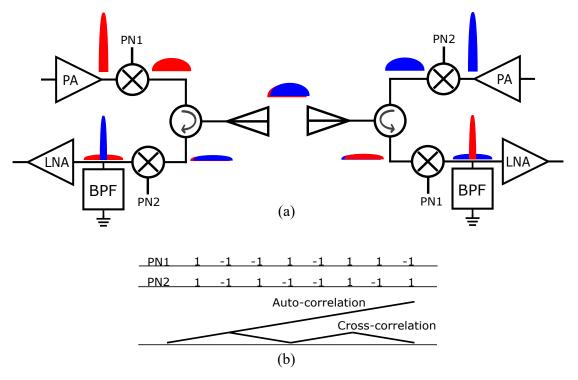

RF code-domain approaches are a recent development that have the potential to add additional rejection. With this additional rejection, the SI goals of Fig. 1.2 can potentially be met. Code-domain SI systems operate by adding a set of orthogonal codes

Figure 1.1: Example of serial full-duplex cancellation techniques in a transceiver.

Figure 1.2: Required link budget for IBFD systems with and without code-domain techniques.

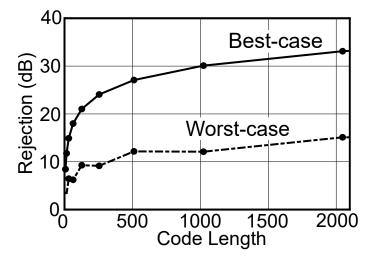

to each transmitted signal, and an integrator on each receiver to cancel undesired codes. A sketch of such a system is shown in Fig. 1.3 (a) and a diagram of the integrated waveform in Fig. 1.3 (b). The nature of adding these codes to each signal results in a much wider bandwidth than the original signal - N-times the bandwidth for an N-length code. Figure 1.4 shows that the longer the codes, the more rejection can be achieved, and thus a very wide-bandwidth is desirable. This is also shown in [14]. In order to make the code-domain systems compatible with other IBFD techniques and traditional

Figure 1.3: Cartoon of a code-domain channel and transceivers implemented at the RF interface.

Figure 1.4: TX rejection for Gold codes with increasing code length in both best and worst-case scenarios

tranceivers without adding significant bandwidth constraints, the code-domain systems must be added directly at the RF interface as shown in Fig. 1.1 and Fig. 1.3 (a).

The receive side of code-domain IBFD systems has been researched in great detail

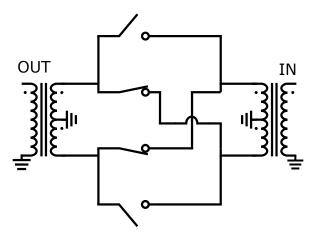

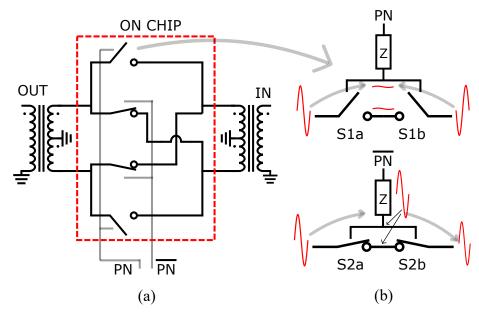

in [14–20], however the transmit code-modulation is an area that remains to be explored. The TX PN modulators must be able to handle a high power, above 30 dBm and potentially up to 40 dBm while maintaining a high modulation bandwidth. For example, for a 1-GHz carrier, and a signal bandwidth of 1-MHz, to achieve high rejection using 128-length codes, the required fractional bandwidth (FBW) capabilities of the Tx modulating switches approaches 25%. A typical approach to building a binary modulator for BPSK modulation, or in this case PN modulation is shown in Fig. 1.5 and utilize quad configured differential RF switches and back-to-back baluns. The above specifications of high power handling, low loss, and high FBW are a challenging design space for existing RF switch technologies and serve as the motivation for the majority of this work.

Figure 1.5: Typical BPSK modulator

### 1.2 Introduction to RF Switches

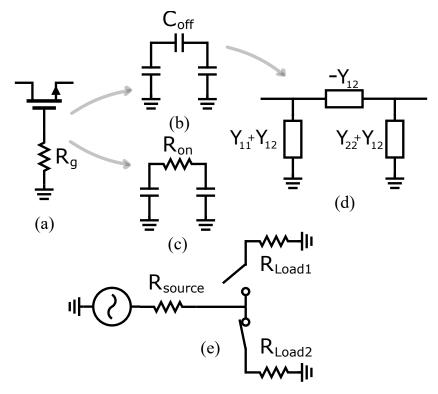

RF switches devices are designed to either be biased as completely non-conducting, or biased to be conducting as much as possible. Therefore traditional circuit/transistor design concepts like  $g_m$ ,  $f_t/f_{max}$  and gain lose their meaning. RF switches are instead often characterized through their off-capacitance,  $C_{off}$  and their on-resistance,  $R_{on}$ . Given

a sufficiently low  $R_{on}$  and  $C_{off}$ , the switch will act like an ideal switch at low frequencies where  $R_{on}$  will look like a short circuit and  $C_{off}$  will look like an open circuit. As operation moves to higher frequencies, the impedance of  $C_{off}$  will drop and look more like a short circuit, eventually having its impedance approach that of  $R_{on}$ . The cross-over frequency where the impedance of  $R_{on}$  and  $C_{off}$  is equal and the device no longer behaves as a switch is a useful metric for switch performance that de-embeds the physical switch parameters such as width and length. This figure of merit is shown in eq. (1.1).

$$FOM = \frac{1}{2\pi R_{on} C_{off}} \tag{1.1}$$

The units of this figure of merit are in frequency, and the value is often too impractically large to measure the actual cross-over frequency - in the range of hundreds of GHz to tens of THz. In practice the factor of  $2\pi$  is often ignored and the  $R_{on}C_{off}$  product is used instead for simplicity.  $R_{on}$  and  $C_{off}$  are best measured by using the the setup shown in Fig. 1.6 (a). The measured S-parameters can be converted to Y-parameters, and  $R_{on}$ and  $C_{off}$  are computed from the test frequency and  $-Y_{12}$  according the the Y-parameter equivalent circuit shown in Fig. 1.6 (d). [21].

The  $R_{on}C_{off}$  product is useful for comparing different device technologies, but doesn't evaluate more complicated switch architectures. In most cases, several switches will be combined into single-pole double-throw (SPDT) or multi-pole multi-throw (MPMT) designs to route RF signals in different directions within the switch. An example of an SPDT switch is shown in Fig. 1.6 (e). In this case, more sophisticated figures of merit are required, such as the insertion loss to the ON state port, isolation to the OFF state port, linearity characterized by input referred 1 dB compression point (P1dB) or the input referred third order intercept point (IIP3), and switching speed.

The linearity of RF switches is highly dependent on the voltage breakdown and con-

Figure 1.6: Circuit diagrams of: example switch setup (a), Off-state equivalent circuit (b), On-state equivalent circuit (c), Equivalent Y-parameters (d), and an SPDT switch (e).

trol/bias voltage of the device. Whether the switch be composed of a switching diode, III-V or silicon FET, as the RF voltage swing approaches the magnitude of the control voltage, the RF signal will become the dominant biasing signal causing unwanted turn-on or turn-off of the devices. This can be alleviated somewhat in three-terminal devices (transistors) by adding large resistors to the control line to separate the bias voltage from the RF signal. However, these large resistors in turn limit the switching speed of the devices, and thus there is a significant trade-off between switching speed and linearity of RF switches. Considering the voltage break-down and maximum biasing of the devices adds another layer to the design trade-offs and challenges. These trade-offs between technologies will be explored in the next section, and for CMOS switches in chapter 2.

To evaluate the switch designs in more detail, a different figure of merit in eq. (1.2)

can be used to capture more complicated trade-offs compared to  $R_{on}C_{off}$

$$FOM = FBW \cdot P_{1dB} \cdot \left(\frac{P_{in}}{P_{lost} + P_{drive}}\right) \tag{1.2}$$

where the final component  $\frac{P_{in}}{P_{lost}+P_{drive}}$  represents the system efficiency. This can be rewritten in terms of the insertion loss and letting  $P_{in} = P_{1dB}$  for the maximum power to give,

$$FOM = \frac{FBW \cdot P_{1dB}}{(1 - IL) + \frac{P_{drive}}{P_{1dB}}}$$

$$\tag{1.3}$$

This FOM will be used to compare the switch designs in later sections.

### 1.3 Comparison of Switch Technologies

There are a variety of RF switch technologies that span the design trade-offs outlined previously. Here an overview of the advantages of each technology will be given with a summary in Table I.

### 1.3.1 PIN diodes

First PIN diodes offer excellent choices for high speed RF switches. PIN diodes rely on long carrier life-times within the intrinsic region of the diode to create a DC current controlled resistance. A unique feature of the PIN diode is that the diode is turned on and off by a DC current rather than a voltage. This means that the ON-OFF control and the RF power are completely decoupled, as it is the frequency of operation that will determine the state of the switch rather than the absolute voltage. As a result, PIN diodes offer extremely low distortion and will only compress as the devices heat up at higher RF power levels above 20 dBm [22]. However, since the operation of the switch is frequency dependent, this means that there is a minimum RF operating frequency -

as the frequency decreases, the current through the channel will cause the device to turn on and off in an undesired fashion. Even though the switching speed of the diode can be relatively low, on the order of the 10s of ns, the frequency dependent operation prevents high FBW switching. Additionally, the use of current to control the switch leads to additional complexity with any integrated drivers needing to be voltage tolerant in order to operate correctly at high power levels. The DC control current also contributes high static power dissipation.

#### 1.3.2 MEMs

Micro-electrical mechanical (MEMs) switches offer an alternative with the best  $R_{on}C_{off}$  performance possible of up to 80 THz [23] due to their operation which physically disconnects the circuit to turn off the switch. In the ON state MEMs simply act as a metal wire. This also lends itself to very high power handling on the order of hundreds of volts. While these switches can also be manufactured on a variety of substrates at low cost, they suffer from slow switching times, difficult control design, and reliability issues. Since the arm of the switch needs to physically move, the switching time is well above the micro-second threshold, and additional difficulty arises in stability and preventing the arm from resonating at faster speeds. The driver requirements are often up 70V and require specialized circuitry to activate the switch. Finally, while newer technologies are providing more mechanically robust switches, the tolerance of the switch to vibration and repeated switching is questionable with the use of moving parts. For code-domain designs, the switching time of MEMs precludes them from being an appropriate technology.

### 1.3.3 GaN

GaN offers advantages mainly in the high breakdown voltage offered in each device. High breakdown voltage translates directly to high linearity on the condition that the control voltage is high enough to over-ride the RF voltage and keep the switch in the correct state [24,25]. While GaN has the switching speed and power handling capabilities required for code-domain switching approaches, the linearity is simply accomplished through a high drive voltage which becomes costly to implement and prohibits easy integration. Additionally, GaN processes are not yet mature enough to offer large scale and low cost production, with the cost of a single device hundreds of times larger than previously mentioned technologies.

### 1.3.4 SOI CMOS

Finally, CMOS processes offer extremely fast switching on the order of 10ps, easy integration and drive characteristics, and low cost through mass production. SOI CMOS also has the additionally benefit of very low parasitics for excellent  $R_{on}C_{off}$  metrics, 2-3 times better than GaN. The main drawback of SOI CMOS is the power handling since each switch can only have a gate or channel voltage of 1-2 V depending on the specific process and oxide thickness. This corresponds to approximately a 10 dBm compression point when the stated goal for code-domain techniques is above 30 dBm. Previous research has lead to designs that can alleviate this trade-off by adding large gate resistors to a series of stacked devices, enabling higher power handling [21, 26–29] - these types of designs are common in commercial products. As previously mentioned these resistors improve power handling and linearity at the expense of switching speed. In the next section, the optimization of these stacking techniques will be addressed as to make a convincing argument for the use of CMOS SOI for code-domain techniques which require

both high power handling and fast switching speed in high performance RF switches.

TABLE I

SUMMARY OF COMPARISONS OF SWITCH TECHNOLOGY

| Technology      | Switching        | Power    | Driver         | Cost |

|-----------------|------------------|----------|----------------|------|

| rechnology      | Speed            | Handling | Requirements   | Cost |

| PIN Diodes      | ns               | High     | Current Source | Low  |

| MEMs            | $\mu \mathrm{s}$ | High     | High Voltage   | Low  |

| FETs (GaN)      | ns               | High     | High Voltage   | High |

| FETs (SOI CMOS) | sub-ns           | Low      | CMOS Interface | Low  |

### 1.4 Dissertation Organization

This introduction provides a background and motivation for the rest of the thesis - why high-power, high-FBW switches are needed for code-domain IBFD systems, and why SOI CMOS is a desirable technology to explore with these types of switches.

Chapter 2 will explore the theory required to design and understand the operation of high-power CMOS switches and their trade-offs. A novel perspective on the large signal and compression modeling of the devices is presented and is used to optimize the RF switches for maximum modulation bandwidth. Additionally, different related architectures for faster series and shunt switches as well as their unique trade-offs and benefits will also be discussed.

Chapter 3 covers the design and measurements of three code-domain TX modulators designed with the techniques outlined in chapter 2. First an optimized resistive stacked switch modulator is presented, then a stacked ladder switch for higher modulation bandwidth, and finally, a reflective shunt modulator which offers the best metrics for combined

power handling and modulation speed.

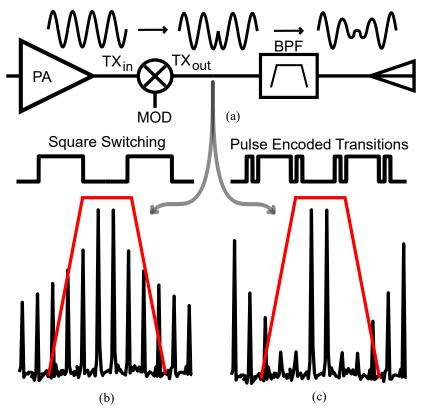

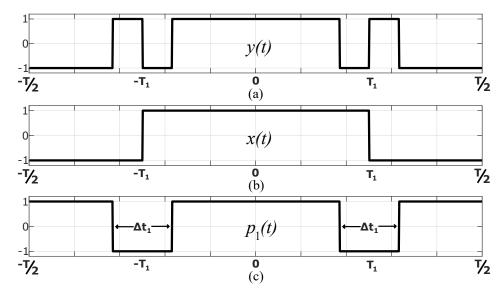

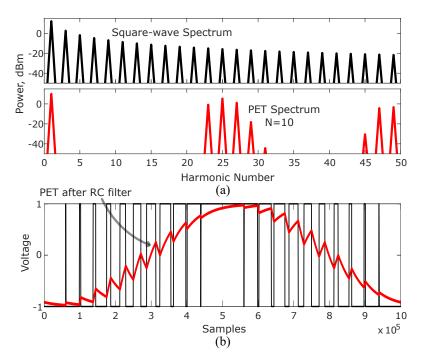

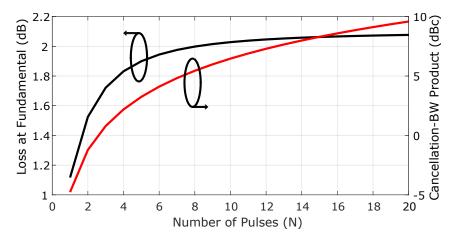

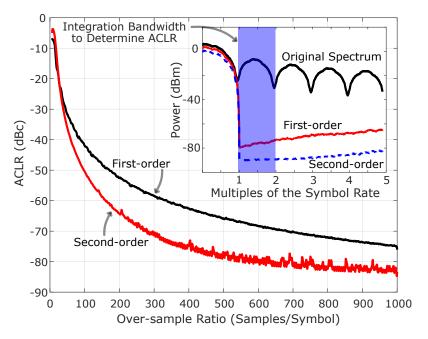

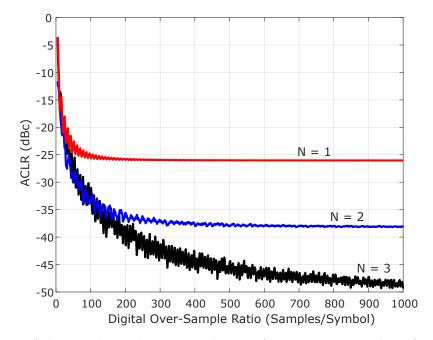

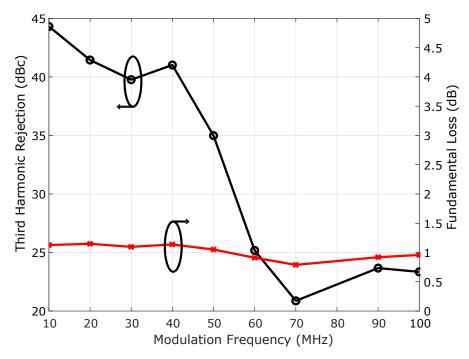

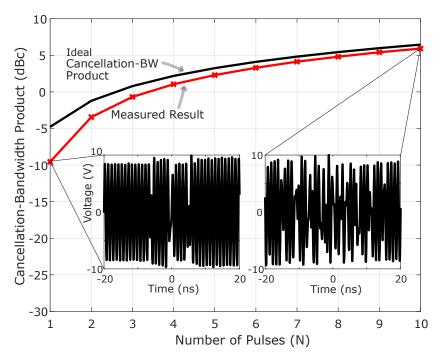

Chapter 4 explores ways to curb the generation of harmonic content that is created when using signal processing at RF approaches to PN codes. This is problem similar to those faced by switching class D amplifiers and so a comparison between established techniques and a new deterministic pulse encoded transitions (PET) method is presented.

Chapter 5 outlines some experiments conducted with the integration of both TX and RX portions of the code-domain approach onto one silicon chip. System measurements and design trade-offs unique to this integration are presented and discussed.

### 1.5 Permissions and Attributions

The content of chapter 2.1-2.4, and chapters 3.1 and 3.2 are reprinted here, with permission, and were presented and published in the proceedings of the Internation Microwave Symposium (IMS) 2018 [30] ©IEEE 2018 and expanded in the IEEE transactions on Microwave Theory and Techniques (TMTT) in December, 2018 [31] ©IEEE 2018. Chapters 2.5, 3.3 are reprinted here, with permission, and were presented and published in the proceedings of the IMS 2019 [32] ©IEEE 2019 and expanded in IEEE TMTT in December, 2019 [33] ©IEEE 2019 which included the entire content of Chapter 4. The content of chapter 5 are reprinted here, with permission, and was presented and published in the proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC) 2019 ©IEEE 2019 [17] and was expended to the IEEE Journal of Solid State Circuits (JSSC) May, 2020 [34] ©IEEE 2020.

## Chapter 2

# Large Signal Compression in RF Switches

In order to build high speed, high power switches and modulators, the operations of single CMOS switches must be understood first. This will be covered in detail with a focus on ensuring that the devices stay in "small signal" mode for as long as possible with increasing input power. To do this, the compression mechanisms in both the ON and OFF states must be considered along with how the two states may limit one-another. While this analysis focuses on SOI CMOS, many of the ideas and techniques apply to other types of switch design as well.

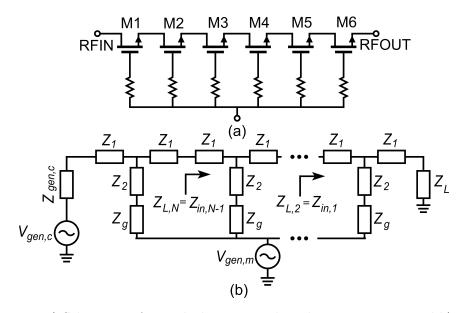

### 2.1 SOI Switch Modeling

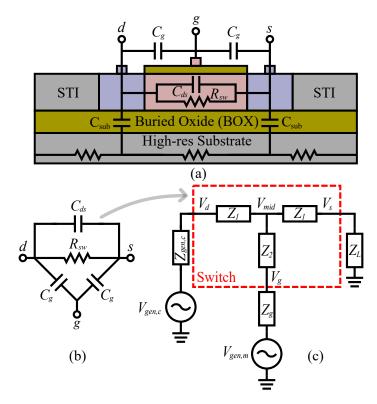

The cross section of a CMOS SOI FET conventionally used as a switch is shown in Fig. 2.1(a) and the RF circuit model is simplified to Fig. 2.1(b). The 45-nm SOI process features a high resistivity substrate ( $\sim 7500 \ \Omega \text{cm}$ ), which renders the substrate-parasitic capacitances negligible at RF frequencies, e.g., less than 10 GHz. Use of floating body

devices also allows for reduced parasitics which simplifies the switch model and maximizes the  $R_{on} \cdot C_{off}$  product of the switch [35]. The gate resistance is significant and will be added to the analysis later as an external driving impedance.

Figure 2.1: a) Diagram of intrinsic device parasitics from SOI FET structure, b) Reduced schematic for modeling, c) Switch network used for analysis after  $\Delta$ -Y transformation

The model of the switch resistance could be derived based on a continuous current-voltage relationships but results in unwieldy equations that offer little intuition. Instead, the switch resistance  $R_{sw}$  can be modeled as a discrete function of the gate voltage defined by the onset of conduction relative to the characteristic impedance of the transmission line. In other words, the ideal RF switch model assumes

$$R_{sw} = \begin{cases} R_{on} << Z_o, & V_{gs} > V_{th} \\ R_{off} >> Z_o, & V_{gs} < V_{th}, \end{cases}$$

(2.1)

where  $Z_o$  is the impedance of a generator and  $V_{th}$  is the threshold voltage of the transistor. Imperfect isolation between the source and gate implies that the on and off resistance of the switch change as a function of the RF power as a result of compression. To analyze switch under large-signal (compression) conditions, a Y-model of the switch transistor shown in Fig.2.1c) can be used. The Y model is a modification of the transistor capacitances and resistances applied to a  $\Delta - Y$  transformation of the network in Fig. 2.1b) to analyze voltages that appear at the nodes of the device. The advantage of the Y model is that it incorporates intrinsic and extrinsic source, gate and drain impedances as series elements while also extending the model to more complicated stacked-FET switches in later sections.

The resulting intrinsic Y-model impedances,  $Z_1$  and  $Z_2$ , are

$$Z_1 = \frac{(R_{sw}||1/j\omega C_{ds})}{2 + j\omega C_q(R_{sw}||1/j\omega C_{ds})}$$

(2.2)

and

$$Z_2 = \frac{1}{j\omega C_q(2 + j\omega C_q(R_{sw}||1/j\omega C_{ds}))},$$

(2.3)

where the gate-drain and gate-source capacitances are assumed to be basically equal. If the switch is on,  $R_{sw}$  is small, e.g.  $R_{on}$ , and  $Z_1 \approx R_{on}$  and  $Z_2 \approx \frac{1}{2j\omega C_g R_{on}}$ . The input impedance seen from the generator into the switch network is

$$Z_{in} = Z_1 + (Z_1 + Z_L)||(Z_2 + Z_g).$$

(2.4)

There are two signal sources of interest in this analysis, one high-frequency (or RF) generator and one low-frequency due to the modulation. Therefore, the drain, source, and gate voltages can be analyzed in superposition, using the subscript c and subscript d to represent the carrier and modulation signals, respectively. Using the Y model, the

voltages of interest at any node can be found, e.g.  $V_d = V_{d,c} + V_{d,m}$ .

$$V_{mid,c} = \frac{(Z_1 + Z_L)||(Z_2 + Z_g)|}{(Z_1 + (Z_1 + Z_L)||(Z_2 + Z_g)|)} V_{d,c}$$

(2.5)

$$V_{d,c} = \frac{Z_{in}}{Z_{gen,c} + Z_{in}} V_{gen,c} \tag{2.6}$$

$$V_{s,c} = \frac{Z_L}{Z_1 + Z_L} V_{m,c} (2.7)$$

$$V_{g,c} = \frac{Z_g}{Z_2 + Z_g} V_{mid,c} \tag{2.8}$$

The response due to a gate modulation,  $V_{gen,m}$ , reaches a similar set of equations.

$$V_{mid,m} = \frac{(Z_1 + Z_L)||(Z_1 + Z_{gen,c})}{(Z_q + (Z_1 + Z_L)||(Z_1 + Z_{gen,c}))} V_{gen,m}$$

(2.9)

$$V_{d,m} = \frac{Z_{gen,c}}{Z_1 + Z_{gen,c}} V_{mid,m}$$

(2.10)

$$V_{s,m} = \frac{Z_L}{Z_1 + Z_L} V_{mid,m} \tag{2.11}$$

$$V_{g,m} = \frac{Z_2 + (Z_1 + Z_L)||(Z_1 + Z_{gen,c})|}{Z_q + Z_2 + (Z_1 + Z_L)||(Z_1 + Z_{gen,c})|} V_{gen,m}$$

(2.12)

To compare performance, the insertion loss (IL) can be defined by  $IL = -20 \log_{10}(S_{21})$  assuming the generator and load impedance are the same. Therefore, this expression is only valid when evaluating the composite switch as a whole, and as such will not be used when discussing the loss of an individual FET component of a stacked switch.

### 2.1.1 Conditions for On-State Conduction

The condition for the switch to remain ON in the presence of RF and modulation sources is given by

$$|V_{gd,m}| - |V_{gd,c}| > V_{th}.$$

(2.13)

Since (2.8) and (2.12) allow a superposition of the RF carrier voltage and the gate modulation voltage, expressions for  $P_{1dB}$  and the switch modulation rate are interdependent, and an increase in either input power, or modulation frequency can cause the switch to compress. While (2.6) through (2.12) are used to derive expressions for the IL, power compression ( $P_{1dB}$ ) and modulation fractional bandwidth (FBW) of the switch, this can be in practice cumbersome and will only be used here for simulation. However, in the limit that  $R_{sw} = 0$ , the drain and source of the FET are effectively connected at the same node ( $Z_1 = 0$ ), and  $Z_2 = 1/(j\omega 2C_g)$  and the expressions for  $V_{gd,m}$  and  $V_{gd,c}$  reduce to

$$V_{gd,m} = \frac{1}{1 + j\omega_m 2C_g(Z_g + Z_{gen,c}||Z_L)} V_{gen,m}$$

(2.14)

and

$$V_{gd,c} = \left(\frac{-1}{1 + i\omega_c 2C_a Z_a}\right) V_{d,c}.$$

(2.15)

$$V_{gen,c,1dB} = \sqrt{1 + 4\omega_c^2 C_g^2 Z_g^2} \left( \frac{V_{gen,m}}{\sqrt{1 + 4(\omega_m C_g (Z_g + Z_{gen,c} || Z_L))^2}} - V_{th} \right) \left( \frac{Z_{in} + Z_{gen,c}}{Z_{in}} \right)$$

(2.16)

Considering (2.13) to be an equality gives a condition to calculate the 1-dB compression point in (2.16). In the simplified case of (2.14) and (2.15), this suggests a 1-dB

compression voltage of (2.16) is dependent on the input power through  $V_{gen,m}$ . Additionally, the switch compresses due to the dependence on both  $\omega_m$  and  $\omega_c$ . When the  $\omega_m = 0$ , (2.16) reduces to

$$V_{gen,c,1dB} = \sqrt{1 + 4\omega_c^2 C_g^2 Z_g^2} \left(\frac{Z_{in} + Z_{gen,c}}{Z_{in}}\right) (V_{gen,m} - V_{th}), \tag{2.17}$$

which indicates that the compression point is directly related to the threshold voltage of the switch compared to the bias voltage.

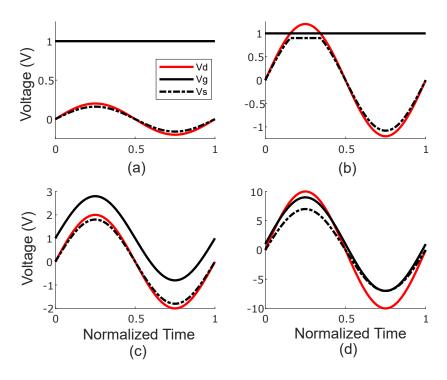

Figure 2.2: Illustration of compression with (a)  $R_g=0$ , small signal, (b)  $R_g=0$  large signal, (c)  $R_g>>0$ , conduction, and (d)  $R_g>>0$  compression

When  $Z_g$  is purely resistive, to realize the largest modulation voltage on the gate, the product of  $\omega_m C_g R_g$  must be small. To ensure that the gate voltage is swinging in phase with the drain and source voltage at the carrier frequency, the product of  $\omega_c C_g R_g$  must be large. Therefore, both the conditions for carrier and modulation voltages suggests that (2.13) is only satisfied if either the input power is low, or the modulation frequency

is low, but not both. Fig. 2.2 shows the compression mechanism in the cases when  $R_g$  is low, and when  $R_g$  is high, where  $V_{g,m}$  is chosen to be a DC offset and time is normalized to one period for illustration purposes.

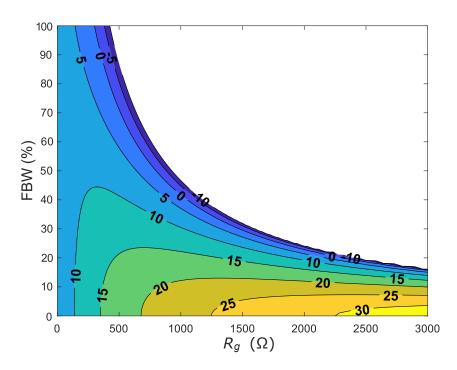

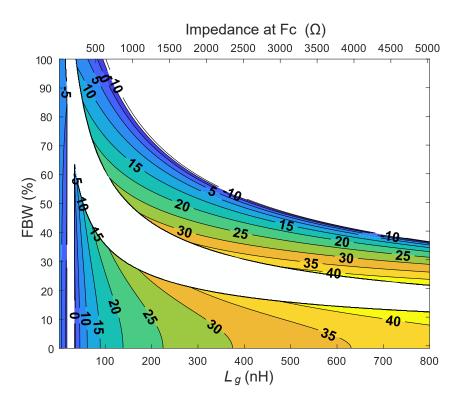

To demonstrate the trade-off between modulation bandwidth and  $P_{1dB}$  in conventional high-power RF switch design, we can define the fractional bandwidth,  $FBW = 100 \cdot F_{mod}/F_c$ . For the purposes of this analysis, the center frequency is taken to be 1 GHz. Fig. 2.3 uses (2.16) from (2.2)-(2.12) rather than the assumptions made in (2.14) and (2.15) to plot  $P_{1dB}$  contours for different values of  $R_g$  and FBW. Note that the power handling can reach 30 dBm only when the modulation frequency is quite limited, i.e. less than 10% FBW.

Figure 2.3: Contours of maximum power handling in dBm while sweeping modulation frequency and gate resistance for a 1 mm switch.

### 2.1.2 Conditions for Off-State Conduction

While adding a large resistance on the gate of the a switch allows it to remain in the on state to very high power, there are multiple conditions for the switch to remain in the OFF state with increasing input power. First,  $V_{gs}$  should remain less than the voltage threshold during the positive gate swing.

$$|V_{g,c} - V_{s,c}| - |V_{g,m} - V_{s,m}| < V_{th}$$

(2.18)

Second, the switch should remain off during a negative swing on the gate.

$$|V_{g,c} - V_{d,c}| - |V_{g,m} - V_{d,m}| < V_{th}$$

(2.19)

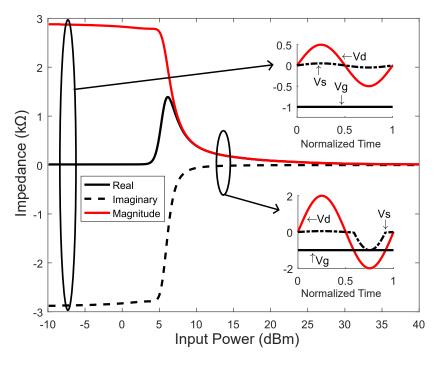

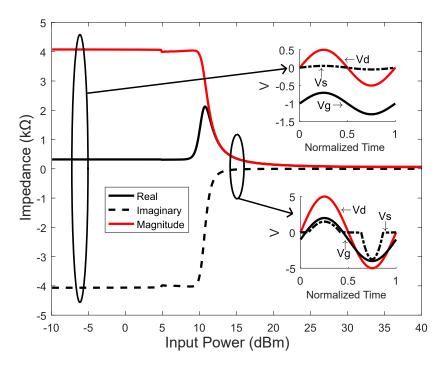

Figure 2.4: Simulated large signal input impedance of a 100  $\mu$ m switch with  $R_g = 0$  and illustrated waveforms for small and large signal operation

Figure 2.5: Simulated large signal input impedance of a 100  $\mu$ m switch with  $R_g=15K\Omega$  and illustrated waveforms for small and large signal operation

Note that the only difference between (2.18) and (2.19) is that one is dependent on the source voltage and the other on the drain voltage. These compression mechanisms are illustrated in Fig. 2.4 for a small gate impedance and Fig. 2.5 for a large gate impedance. Therefore, the switch can be operated to around 5 dBm under this condition. With a large gate impedance, positive gate swing will always occur as the input swing approaches the gate bias voltage.

Negative swings compress the switch when the voltage division generating  $V_{g,c}$  is no longer sufficient to keep  $V_{g,c}$  below  $V_{g,d}$ . With a large gate impedance, the compression of the device in the off state serves to prevent the device from experiencing high breakdown voltages, as opposed to low gate impedance devices which will experience high gate stress beyond 10 dBm. However, in both cases, the large signal input impedance drops significantly with higher input power and the isolation drops from >30-dB to <3-dB

rapidly.

Comparing Fig. 2.6 to Fig. 2.3 highlights the limitations of SPDT switches using only one device connected to each output, as the ON state is able to withstand very high power handling and modulation bandwidth, while the OFF state is limited severely by low compression points and low isolation. The solution to this discrepancy is to stack the FETs to distribute the voltage across many gates and increase the power handling of total switch. This technique will be discussed in detail later.

Figure 2.6: Contours of maximum power that satisfy (2.18) and (2.19) across  $F_{mod}$  and  $R_g$  for a 1 mm switch

### 2.2 Extension of Fractional Bandwidth

To break the trade-off between  $P_{1dB}$  and FBW, the resistive gate termination must be generalized to an arbitrary impedance. When an inductance is added to the gate, a different impedance is presented at the carrier frequency and the modulation frequency. Looking back at the approximations when  $R_{on} = 0$ , it is easy to see how this might be effective as eq. 2.14 is now proportional to  $1/\omega_m^2$ , while (2.15) remains constant for sufficiently large  $\omega C_g Z_g$  products.

In Fig. 2.7, the maximum power handling and modulation frequency possible is much higher compared to the resistive switch. Since the inductive element on the gate can store energy near the resonant frequency with the gate capacitance, the voltage across the gate can be high and cause device breakdown. The region around FBW = 20% exists due to this resonance where the peak gate voltage exceeds 2 V. This undesirable region indicates that the maximizing the  $P_{1dB}$ -FBW requires both a resistive and inductive element - the inductive element will allow high modulation bandwidth, while some resistance would prevent the gate from resonating.

Figure 2.7: Contours of maximum power handling while sweeping modulation frequency and gate inductance for a 1 mm switch in the on state.

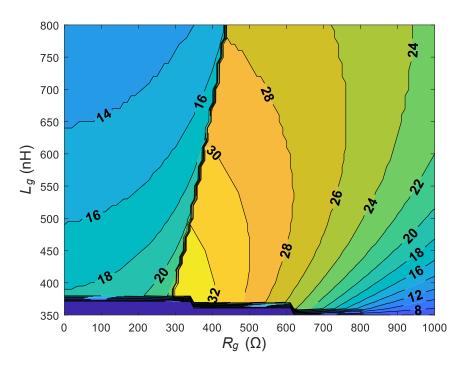

To simulate an arbitrary gate impedance,  $Z_g = R_g + j\omega L_g$ , Fig. 2.8 plots the resistive and inductive parts of  $Z_g$  for contours of FBW at 30 dBm power handling, insertion loss under 1-dB, and gate voltage less than 2 V. An interesting feature of this plot is the vertically-divided regions where the FBW jumps by nearly a factor of two between  $R_g$  values of 300  $\Omega$  to 400  $\Omega$ . This represents the required  $R_g$  necessary to suppress the resonance region such that the 30 dBm power is reached without causing device breakdown. While this shows a great improvement in FBW for high power handling in the switches, the off state will still be the limiting factor in evaluating the switches performance as the compression mechanisms are the same as outlined in the previous section.

Figure 2.8: Contours of maximum modulation frequency as a fraction of the carrier frequency under the condition that (13) is satisfied up to 30 dBm with an insertion loss less than 1-dB.

### 2.3 SPDT design

To evaluate the performance of the switch, there are several important factors to consider. By looking at the switches in an SPDT configuration rather than as a single switch, both the on and off compression points can be evaluated simultaneously. Similarly, a low isolation value from the off switch will cause an increase in insertion loss in the on switch. As discussed in section 1.2 typical evaluation of individual devices, e.g.  $\frac{1}{2\pi R_{ON}C_{OFF}}$  isn't sufficient to characterize an RF switch and all of it's parameters. To capture the effects of insertion loss, FBW, power handling, and drive power consumption, the following figure of merit can be used, as mentioned in Chapter 1,

$$FOM = FBW \cdot P_{1dB} \left( \frac{P_{in}}{P_{lost} + P_{drive}} \right) = \frac{FBW \cdot P_{1dB}}{(1 - IL) + \frac{P_{drive}}{P_{1dB}}}$$

Figure 2.9: Calculated FOM across a sweep of switch width and  $R_g$  for a simple SPDT

Figure 2.10: Calculated FOM across a sweep of switch width and  $R_g$  for a simple SPDT

The FBW and IL are linear, unitless values while all power values are in units of Watts. The FOM is specified such that an increase in FBW or  $P_{1dB}$  cannot be accompanied by a corresponding increase of insertion loss to create the illusion of an improved system. By considering the fractional value,  $P_{in}/(P_{lost} + P_{drive})$ , the net system efficiency is also evaluated. In CMOS processes, the drive power is typically small and does not strongly impact FOM. However, other processes might handle higher power with higher gate dissipation. Figure 2.9 calculates the FOM across a sweep of switch width and gate resistance to find the optimal parameters of the device that balance modulation speed and power handling.

Similarly, the same set of equations and FOM can be used to evaluate an SPDT with an inductive gate element and a  $300\Omega$  damping resistance on the gate. This optimization is shown in Fig. 2.10 and the benefit of using the inductive termination is immediately

apparent. Due to the relaxation of the FBW limitations from the inductive gate, the total gate impedance can be increased without degrading FBW and in turn improves both power handling and insertion loss for a significantly higher FOM.

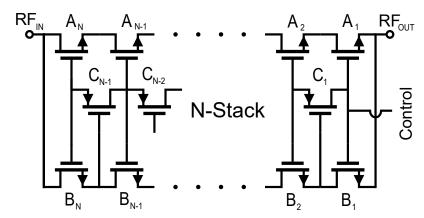

## 2.4 Stacked FET Design and Optimization

The previous analysis demonstrates that raising the load impedance on the off switch might help prevent voltage compression. With a larger load, the input impedance seen into the open switch is higher, leading to more isolation, and the output voltage swing will be able to track the gate voltage more closely leading to a higher compression point. Adding series 'stacks' of switches increases the cascaded  $Z_{in}$  at each transistor towards the source.

### 2.4.1 Resistive Stack Optimization

Figure 2.11: a) Schematic of a stacked FET switch with resistive gates and b) stacked FET switch circuit model to calculating impedance and isolation

A circuit schematic of this approach is illustrated in Fig. 2.11(a) and the equivalent

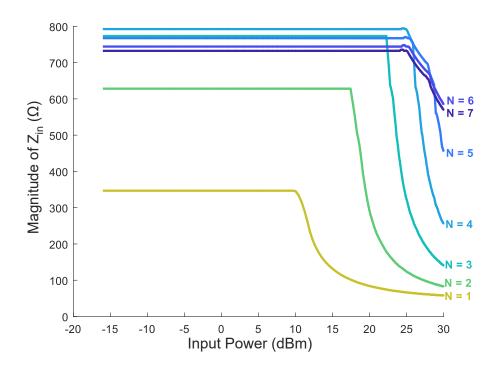

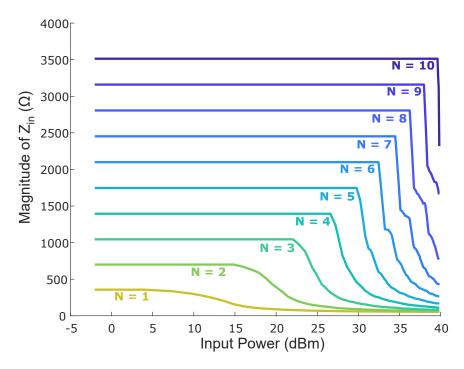

model as previously discussed in section II is shown in Fig. 2.11(b). The compression point of the switches is predicted from eqs. 2.18 and 2.19 by checking each switch in the stack to determine if compression has occurred. Beyond the compression point, the large signal behavior is approximately modeled by assuming  $V_s = V_d - V_{th}$  given that  $R_g$  is sufficiently large. Since  $V_s$  and  $V_d$  are determined by the combination of circuit parameters including  $R_{sw}$ , if  $V_s$  and  $V_d$  are known a priori, the equivalent large signal  $R_{sw}$  can be determined. This process is used to generate Figs. 2.12 and 2.13.

Figure 2.12:  $Z_{in}$  with increasing input power for N stacked FETs for 1 mm FETs with  $R_g = 1500 \ \Omega$ .

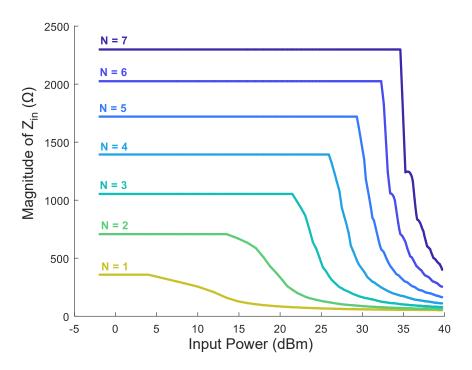

In the case of Fig. 2.12, a relatively small value for  $R_g$  was chosen to maintain high modulation bandwidth. The  $Z_{in}$  of each additional transistor increases to N=4 before the benefits of stacking begin to diminish largely due to the accumulating parallel gate resistances. Increasing the value of  $R_g$  to 20 k $\Omega$  rather than 1.5 k $\Omega$  leads to Fig. 2.13, which shows that by sacrificing some modulation speed with a larger  $R_g$ , the use of FET

stacking remains viable for larger values of N and input power.

Figure 2.13:  $Z_{in}$  with increasing input power for N stacked FETs for 1 mm FETs with  $R_q = 20 \ k\Omega$ .

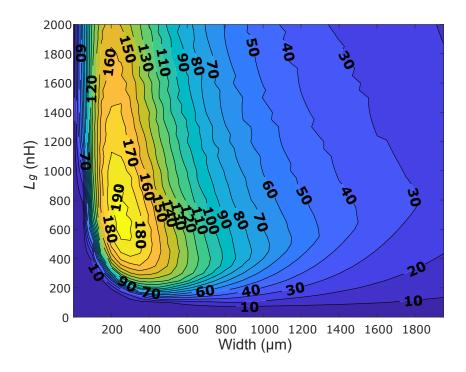

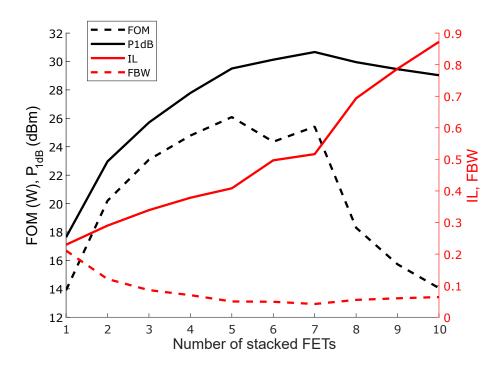

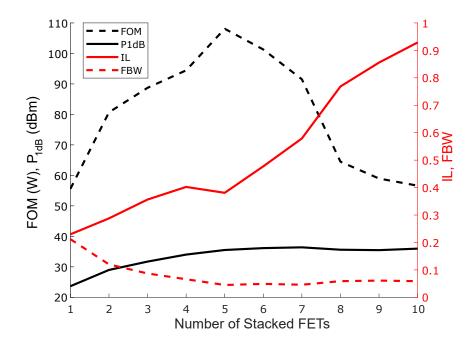

This result suggests an optimization in the number of stacked devices for higher power handling and maintaining modulation bandwidth. Revisiting the FOM in (1.3),  $P_{drive}$  increases by a factor of N to take into account the total power consumption of the stacked FETs. Again, using the SPDT model to ensure that both on and off compression, as well as IL and isolation are captured, any standard maximization algorithm can be used to determine the optimum values for N, switch width, and each individual gate resistance.

The FOM comparison is plotted in Fig 2.14 as a function of N. The corresponding  $P_{1dB}$ , IL, and maximum FBW are also plotted. The simulation indicates that the FOM is maximized between N=5 and 7 FETs while N=7 has the highest (>1 Watt) power handling. For N=6, a 30 dBm switch is realized with width = 935  $\mu$ m,  $R_{g1}=4300~\Omega$ ,  $R_{g2}=6200~\Omega$ ,  $R_{g3}=5500~\Omega$ ,  $R_{g4}=5600~\Omega$ ,  $R_{g5}=5800~\Omega$ ,  $R_{g6}=4800~\Omega$ . The tapering

of the gate resistance is performed to balance the load voltage on the switch.

Figure 2.14: Optimization of the number of stacked FETs and their parameters.

## 2.4.2 Inductive Stack Implementation

While a resistive stack can easily be integrated, developing a stacked switch with an inductive termination relies on prohibitively large numbers of inductors. Even if these inductors are moved off chip, the number required for any number of stacked FETs would be layout intensive as each transistor would need a separate inductor.

A solution is to modulate the gate impedance of the stacked FETs using a secondary stack of switches, first proposed in [36], and displayed here in Fig. 2.15. While this switch was originally proposed as a shunt switch, it is also converted to a series switch by using a large inductor on the control line in the spirit of section II-C. When the control voltage is high, the gate of the first NMOS device and the source of the first PMOS device are

biased high, turning both of the switches on. This allows the control voltage to propagate to the next stack in the ladder and so on, cascading up the switch. When the switch is on, all the gates of the primary devices,  $A_1$  through  $A_N$ , are tied together to make one large device with a composite gate length. This also makes the gate capacitance N times larger than each individual device which allows the size of the control inductor to be greatly reduced.

Figure 2.15: Modified stacked switch to enable fast switching through an inductive gate impedance in series with the control node. This architecture can also be used in a shunt configuration

When the switch is turned off, each secondary switch presents a large capacitive impedance to the gate of each primary switch. Typically, a purely capacitive gate impedance prevents any modulation from occurring, particularly if the data has a DC offset. In this case, the switches are turning on and off, presenting alternately small resistances and large capacitances.

Assuming a static capacitive load on each gate of the device, the same process used to generate Figs. 2.12 and 2.13 can be used to generate Fig. 2.16. In this case, since each capacitor is cascaded on top of the next capacitor on the stack, the effective impedance seen on each gate  $NC_{ds}$  at the Nth FET, with  $A_1$  seeing the largest impedance and  $A_N$  the smallest. Conveniently, this trend breaks the trade-off that was evident in Figs. 2.12 and 2.13 in that progressive stacks continue to add power handling capabilities without

compromising the maximum FBW.

Figure 2.16: Input impedance with increasing input power in the off state for different numbers of stacked switches for the design in Fig. 2.15 approximating the gate impedance as the capacitance from the total cascade of the secondary transistors below each switch

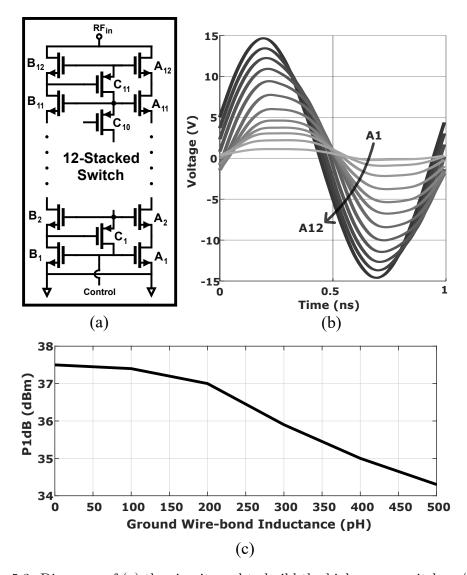

## 2.5 Shunt Switches

The ladder switch design shown in Fig. 2.15 can also be used in a shunt configuration for various applications. In this case, the control node does not need any termination and can be driven directly from digital logic. Digital logic can be used in the ON state because the RFIN node will be shunted to ground and have zero voltage swing, while in the OFF state, the RFIN voltage is distributed between each of the switches.

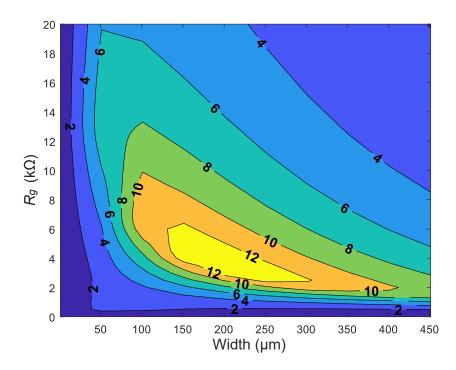

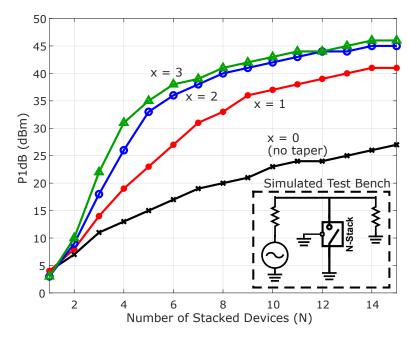

To significantly improve the voltage handling of these types of switches, a tapering approach to the secondary switches (B and C) is proposed here. Typically, power han-

dling is limited by self conduction when the switch is OFF. This is caused by the drain of  $A_1$  swinging while the gate of the device is connected to the DC-grounded control line. In order to prevent the bottom most devices from conducting in the OFF state, the voltage swing at the drain of  $A_1$  must be less than the threshold of the device. In addition, if the voltage drop across each transistor is to be approximately the same, the voltage division from the drain to the gate of each consecutive device must be a smaller fraction of the total remaining incident voltage. This means that the bottom secondary devices  $(B_1, C_1)$  must be the largest and the top secondary devices  $(B_N, C_{N-1})$  must be the smallest while the size of the primary devices  $(A_1 \to A_N)$  remain the same to ensure the highest voltage handling. Conversely, adding stacks with increasingly aggressive tapers has a significant impact on the achievable FBW. To describe this trade-off, a tapering function can be defined as

$$B_N = C_N = \frac{A_N}{N^x} \tag{2.20}$$

with  $A_N$ ,  $B_N$ , and  $C_N$  representing the size of the  $N^{th}$  device in the respective stacks as labeled in Fig. 2.15 and x representing the tapering factor.

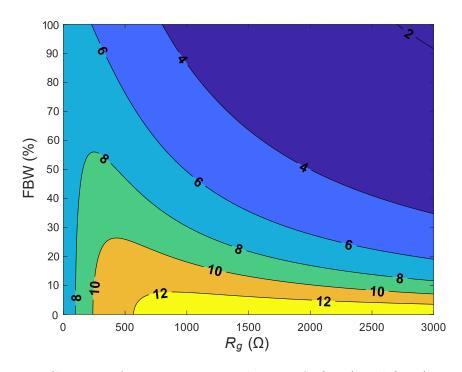

Fig. 2.17 shows the simulated P1dB of tapered stacked shunt switches with different numbers of stacked devices and increasingly aggressive device tapering factors. To maintain a constant switch resistance, the size of the primary devices, A is scaled linearly with the number of stacked devices. Adding a taper to the switch, x = 1, the power handling of the shunt switch is improved by 15-20 dB over a switch with uniform sizing, x = 0 at high numbers of stacked devices. Using more aggressive tapering, e.g. x = 2, further increases the  $P_{1dB}$  but additional tapering provides limited benefits.

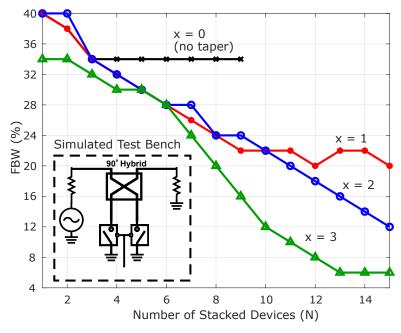

Conversely, increasing the number of stacks adds both additional gate capacitance, due to more devices in the stack and larger devices to keep the switch resistance low, and series resistance in the control line which also increases with the tapering factor. As

Figure 2.17: Effect of device stacking and tapered switch sizing for different tapering factors, x, on switch power handling.

Figure 2.18: Effect of device stacking and tapered switch sizing for different tapering factors, x, on maximum achievable FBW.

a result, the switching speed is reduced. To quantify the trade-off in the additional gate capacitance, the FBW is plotted in Fig. 2.18 for increasing stacks and tapering factors.

The test-bench uses a reflection phase shifter (RPS) so that both the on and off state have similar losses to the output and switching speed is isolated from other variables. The implementation of this RPS will be discussed later in Chapter 3. In this case, the maximum FBW is defined as the switching frequency at which the losses increase by 1 dB. Without a taper in device sizing (x = 0), increasing the number of stacked devices beyond 9 requires very large devices to maintain low switch resistance, which results in a low input impedance in the off state due to  $C_{SW}$  and modulation becomes impossible in the RPS test bench shown in Fig. 2.18. Adding the tapering function allows modulation at high values of N and thus higher power handling concurrent with modulation. From Figs. 2.17 and 2.18, the design trade-offs between power handling and FWB are clear - larger N leads to more power handling but lower maximum FBW. Ultimately, using the same tapering factor in both the B and C devices is not ideal as it is better to have larger C devices to keep the series resistance down for higher FBW.

Figure 2.19: Drain voltages for a RPS in the OFF state with a 30 dBm input when the switches are sized with (a) static sizing, and (b) a tapering technique.

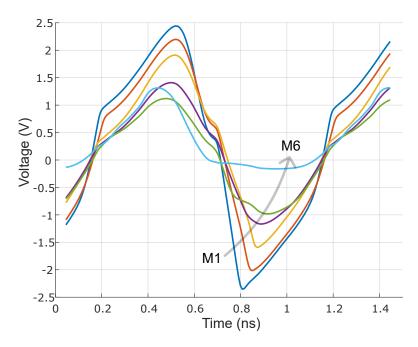

To observe the effect of tapering at the internal nodes of the switch on the OFF state,

the simulated drain voltages for each primary (A) device are shown in Fig. 2.19 (a) for a 12-stack switch used in an RPS modulator where each of the B and C devices is 1/12 the size of the A devices [36] - in this case, 150  $\mu$ m, and Fig. 2.19 (b) for a tapered 12-stack switch. The voltages across the FETs are more evenly distributed, allowing lower stress on each device and a significantly higher maximum voltage swing on the stacked switch. This leads to lower insertion loss and higher power handling.

# Chapter 3

# Stacked Switch Implementation in

# Power Modulators

Using the theory presented in the last chapter on RF switches, a variety of different styles of modulators for code-domain applications have been built and are presented in the following chapter. The first objective is to demonstrate the utility of the resistive switch optimization for building a modulator (modulator A) with the highest FOM possible. Next, a modulator (modulator B) utilizing the new type of inductively terminated RF switch will be presented to show how the switching speed can be greatly improved over any type of resistive termination. Finally, a type of modulator (modulator C) which does not use any baluns will be discussed as a way to maintain high power handling and fractional bandwidth while significantly lowering the insertion loss for better system efficiency. The target center frequency for each of these modulators is 1-GHz.

## 3.1 Modulator A: Optimized Resistive Modulator

### 3.1.1 Design

Because CMOS is fundamentally limited by the voltage swing of the RF signal, one method to improve the linearity of the system is to lower the reference impedance of the system - lowering the voltage and increasing the current for the same total power. This approach has been presented previously in [37] and [38], however without considering the implications on the modulation speed of the switches. The downside to this approach is that the switch resistance becomes relatively large compared to the load resistance, offsetting the benefits in power handling through higher insertion loss. The switch resistance might subsequently be lowered by scaling the size of the switches with a proportional cost in the gate capacitance and power consumption. Examining eqs. (2.14) and (2.15), we find that both equations rely on a  $\omega C_g Z_g$  product. If  $C_g$  increases, both the voltage handling and the maximum modulation frequency can be maintained by decreasing  $Z_g$  by the same factor. Due to the nature of (2.15) the gate voltage due to the carrier stays constant as long as the  $\omega C_g R_g$  product stays constant. This leads to an optimum switch size determined by the point when  $R_g$  becomes small enough that the constant voltage across it burns enough power to offset any benefits from lowered  $R_{sw}$

While the power handling of the switch could in theory be extended well beyond 40 dBm by lowering the reference impedance, there is a practical limit on the impedance conversion ratio that is possible without adding insertion loss. For this design, the Anaren 3A425S is an appropriate down conversion balun with an output impedance of 12.5  $\Omega$  referenced to ground on each of the differential ports. Re-optimizing with the methodology in chapter 2 gives the results in Fig. 3.1. The predicted  $P_{1dB}$  is now above 36 dBm with a peak FOM between 5 and 6 stacks. As the maximum power handling has increased by a factor of four, so has the FOM - indicating that by lowering the source

and load impedance to increase the power handling of the switch, none of the other important metrics have been negatively effected. This analysis assumes that the switch turns off completely once compression occurs. This technique predicts which switches will perform best, but, in reality, a softer compression occurs, so the actual measured compression point will be somewhat higher by a constant offset.

Figure 3.1: Optimization of the number of stacked FETs and their parameters.

Through this optimization for an N=6 stack switch, the width of each switch in the stack is 3400  $\mu$ m and the gate resistances range from  $R_g=1100~\Omega$  to  $R_g=1600~\Omega$ . Transitioning to a device model requires some adjustments to reach a  $P_{1dB}$  of 40 dBm and a FBW of 0.05 at a small sacrifice in IL. Each transistor was sized to 3800  $\mu$ m, and  $R_{g1}=1600~\Omega$ ,  $R_{g1}=1200~\Omega$  and,  $R_{g(3-6)}=800~\Omega$ . The simulated drain-source voltages are shown in Fig. 3.2 and demonstrate the reduction in the voltage stress on the devices.

Since much of the analysis up to this point relies on a gate voltage swing from -1 V to 1 V, a level shifter based on the the design outlined in [39] is used to translate basic 1 V

Figure 3.2: Simulated drain-source voltages of the resistive design operating at 40 dBm when the switch is off

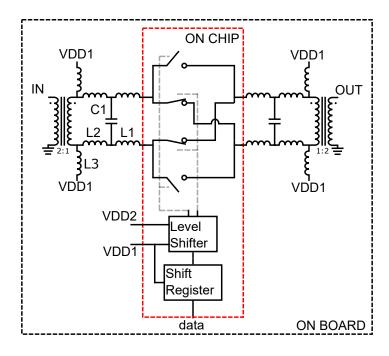

CMOS logic up to a 0-2 V swing while the RF path is biased at 1 V. A shift register was included to enable data encoding if necessary, and the schematic of the constructed chip and PCB is shown in Fig. 3.3. Additionally, in anticipation of high power dissipation within the switch, tie-throughs from metal one connecting to the handle wafer through the BOX layer were interwoven within the device cells with the intention of aiding in thermal dissipation.

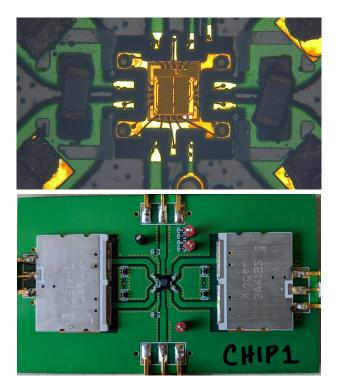

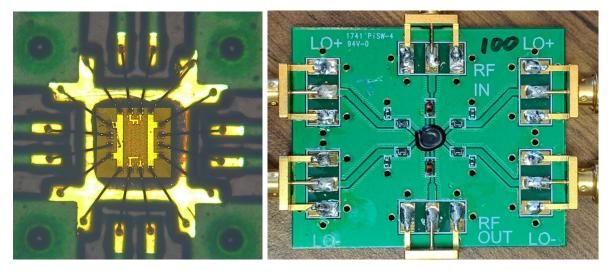

Within the differential section of the PCB, the inductive and capacitive elements are symmetrical both vertically and horizontally. L1 represents the wirebond inductance in the RF path. Because the characteristic impedance is low, any small additional wirebond inductance can cause large mismatches making evaluation of the switches difficult. To offset this wirebond inductance, the matching network consisting of C1 = 10 pF and L2 = 1 nH is used to minimize the losses. L3 = 100 nH and is used to bias the switches to 1 V. A close up of the wirebonded chip and the full test board are shown in Fig. 3.4.

Figure 3.3: Schematic of chip and testing PCB for the Resistive gate, 40 dBm modulator

Figure 3.4: Die photo and test board for modulator A. The size of the modulator is 840  $\mu m$  by 950  $\mu m$

Again, in order to de-embed the losses of the board, a version without the chip, but wirebonded directly across the chip landing area was also constructed.

Because the RF voltage is high, standard ESD cells cannot be used on the drain and source of the switches, and thus no ESD was implemented in this design. However, previous work [40] shows that ESD on the drain and source of stacked CMOS switches is possible without significantly degrading the performance of the switch.

#### 3.1.2 Measurements

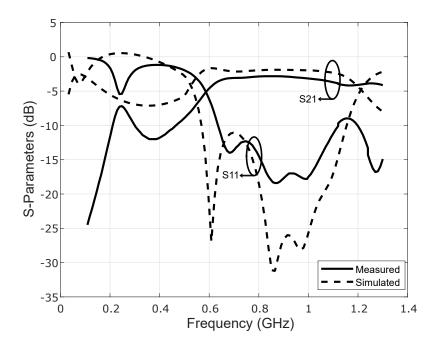

Measured and simulated S-Parameters for modulator A including the test board are shown in Fig. 3.5. The wire bond inductance was estimated at 500 pH when designing the test board and comparing the simulated and measured S-parameters indicates that the wire bond inductance is in this range though there are some additional losses.

Figure 3.5: S-Parameters for modulator A including the test-board and baluns

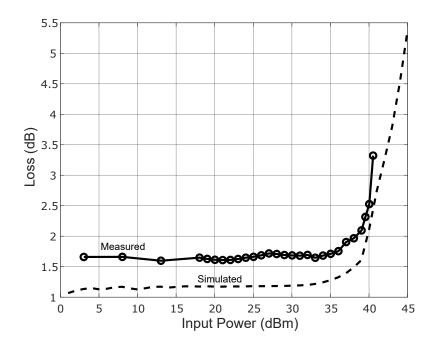

The measured and simulated  $P_{1dB}$  of modulator A are plotted in Fig. 3.6. While

Figure 3.6: Compression of modulator A with increasing input power

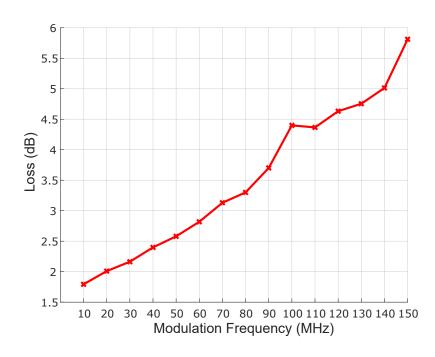

Figure 3.7: Measured loss with increasing modulation frequency for modulator A

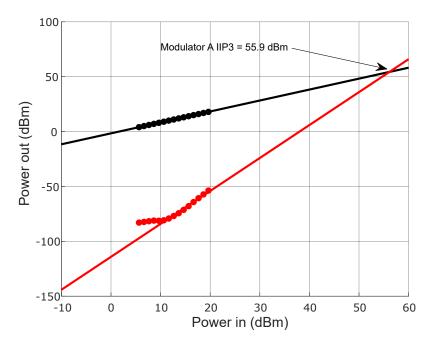

Figure 3.8:  $P_{in}$  vs.  $P_{out}$  and IM3 products to extrapolate IIP3 for modulator A at a 1 MHz offset

the insertion loss is slightly higher when measured compared to simulated, there is good agreement between the compression point which is 40.1 dBm. The measurement was conducted up to a maximum input power of 40.5 dBm. Beyond this point, the insertion loss will begin to degrade over time - gradually at first, then rapidly towards complete device failure. So long as the degradation continues to be gradual, if the input power is reduced slightly the device performance will recover to previous levels. This slow, non-catastrophic failure suggests that the switches are entering thermal run-away and that the temperature limits of the process have been reached. Simulating loss vs. temperature for modulator A indicates that the the loss gradually increases by 1dB of loss at 360°C before quickly rising to almost 20 dB at 400°C supporting the theory that thermal run-away is occurring in the switches. Because voltage compression and thermal compression occur around the same input power, it is difficult to evaluate the effect of modulation frequency on  $P_{1dB}$ . As the modulation frequency increases from 0 to 60 MHz, the compression

TABLE II

IIP3 MEASURED Vs. Two-Tone Offset

| Offset (MHz)           | 1    | 5    | 20   | 40   | 60   | 80   | 100  |

|------------------------|------|------|------|------|------|------|------|

| IIP3 (dBm) Modulator A | 55.9 | 55.9 | 56.2 | 56.5 | 56.7 | 57.2 | 55.7 |

point decreases from 40.1 dBm to 38.7 dBm. Additionally from Fig. 3.7 it's clear that the insertion loss increases relatively rapidly with modulation frequency. Therefore it's unclear if the reduced compression point at higher modulation frequency is due to higher insertion loss and thus higher temperature, or because of the effect of modulation frequency in eq. 2.16. Finally, IIP3 was measured for modulator A and is plotted in Fig. 3.8 which shows an IIP3 of 55.9 dBm in a two-tone test at a 1 MHz offset. A sweep of Two-tone offset and corresponding IIP3 is shown in Table II.

## 3.2 Modulator B: Ladder Inductive Modulator

## 3.2.1 Design

Modulator B uses the ladder switches with an inductive termination as described previously in section 2.4.2. Each RF switch is composed of a back to back set of ladder switches with their control lines connected together. This allows each switch to look like a shunt switch when in the off state as the differential configuration will cause a virtual ground at the center of the back to back switch. This is illustrated in fig. 3.9 (b). The inductive termination is then shared between the two back to back switches allowing for only 4 off-chip inductors used with the modulator.

The sizing of modulator B for each of the primary and secondary switches in this design were based on previous results in [36] with the primary switches 600  $\mu$ m in width and the secondary switches 50  $\mu$ m wide. This sizing is sufficient to demonstrate the inductive concept, however, subsequent simulations suggest that much larger switches

Figure 3.9: Modulator design with the chip edge shown (a) and the use of back to back switches to create a virtual ground (b) in modulator B.

in a lower impedance environment would allow for better performance as well as full integration with smaller inductors.

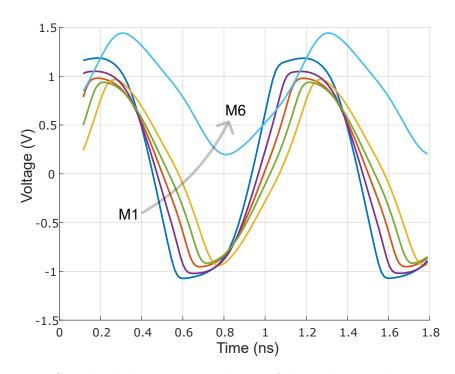

When this modified stacked switch is on, the secondary switches tie the gates of all the primary switches together leading to an equivalent gate capacitance of  $12C_g$  for back to back switches consisting of 6 stacks each. For a switch this size, a gate resistance in the range of  $50-100\Omega$  is necessary in addition to a gate inductance of 50-100 nH. To provide the necessary resistance for each of the gate elements, long, low-level metals were used to route the gate connections to the I/O pads such that the resistance is  $\sim 70\Omega$ . The simulated drain-source voltages of the switches in the off state are shown in Fig. 3.10.

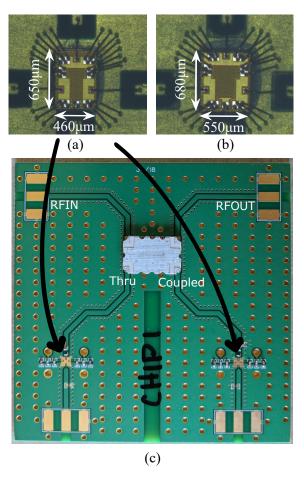

The chips were wirebonded to a PCB with two surface mount ATB 2012E-50011M baluns and four high impedance components - one for the control input of each series-series switch. Two versions of this modulator were constructed to provide a direct com-

Figure 3.10: Simulated drain-source voltages of the inductive design operating at 30dBm when the switches are off

Figure 3.11: Die photograph and constructed PCB for modulator B. The total size of the die is 570  $\mu$ m by 640  $\mu$ m. Four 100 nH inductors are placed horizontally with the baluns on the top and bottom

parison for FBW: one with resistive elements and one with inductive elements. The resistive version was mounted with 800  $\Omega$  terminations while the indutive version was

mounted with 100 nH TDK-B82496C inductors. The mounted chips are shown in Fig. 3.11. A back-to-back balun version of the PCB was also constructed in order for the baluns to be de-embedded so that the insertion loss of the switches themselves could be determined.

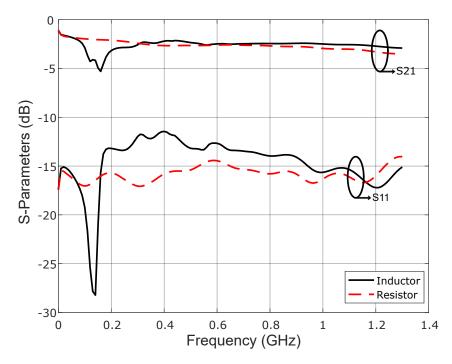

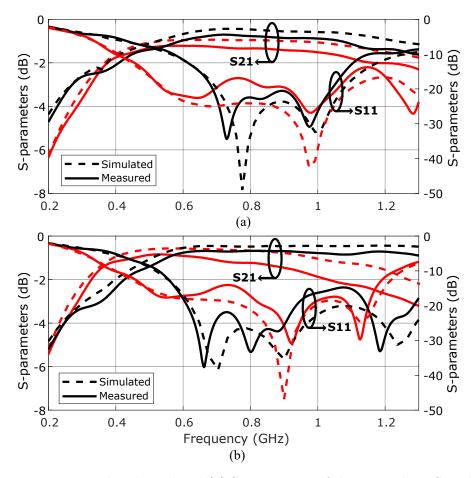

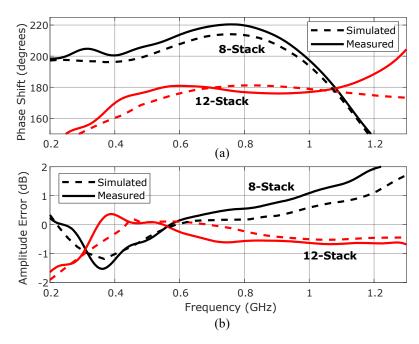

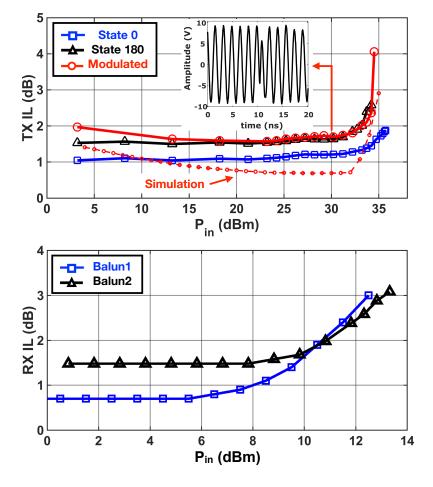

#### 3.2.2 Measurements

S-parameters of both the resistive and inductive version of modulator B are plotted in Fig. 3.12. The small signal insertion loss is 2.6 dB for the inductive version and 2.9 dB for the resistive version. Of this loss, 1.8 dB is contributed by the back-to-back balun and test board and the total switch loss is less than 1.1 dB. Above 1.3 GHz, the loss of the switch cannot be evaluated due to the balun cutoff frequency.

Figure 3.12: Measured S-parameters for resistive (dashed) and inductive (solid) switch versions of modulator B without de-embedding balun losses.

To test the power handling of the switches, a Mini-Circuits ZHL-10W-2G+ 10-Watt

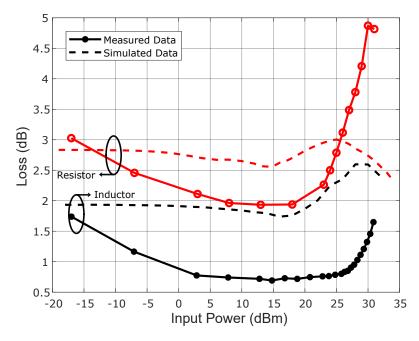

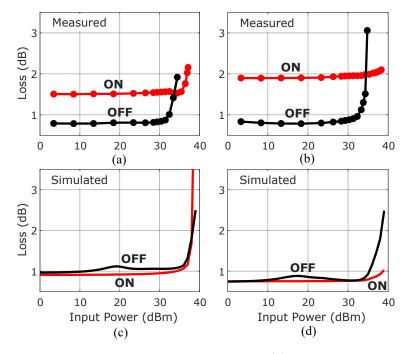

amplifier was used to generate the required output power with a carrier frequency of 1 GHz. The P1dB of this amplifier is greater than 41 dBm with an IIP3 of 53 dBm. Since modulator A was not designed with on-chip gate drivers, the switch control inputs were driven using an M8195 arbitrary waveform generator in combination with splitters and amplifiers to create the required 2 Vpp swing on all clock ports. The output was attenuated and measured using a N9030B spectrum analyzer, and all output harmonics were summed to determine the final output power. A 30 dB coupler was inserted between the amplifier and the DUT, and the input power verified using an HP437B power meter. The insertion loss and compression points are measured with increasing power for both resistive and inductive versions and are shown in Fig. 3.13. Due to the attenuation required in the high power test setup, higher order modulation harmonics became hidden below the noise floor at lower input power levels. This leads to an apparent improvement in IL as the input power is increased in the inductive design, however in simulation, or when only dominant harmonics are taken into account, this effect does not occur. The 1 dB compression point of the inductive version was measured to be 30.9 dBm compared to 25.8 dBm for the resistive version. To test reliability, the inductive design was tested for 100 hours at 30 dBm input power while being modulated at 10 MHz to ensure that both carrier and modulation signals would not cause device breakdown. No performance degradation was observed over the duration of this test. Sudden, catastrophic failure was observed when the input power approached 35 dBm.

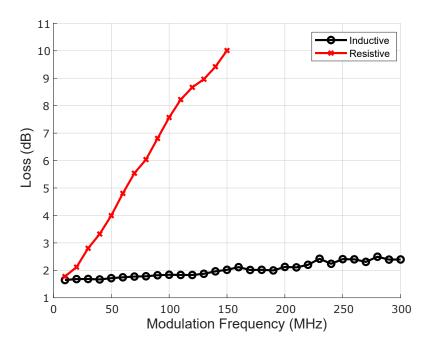

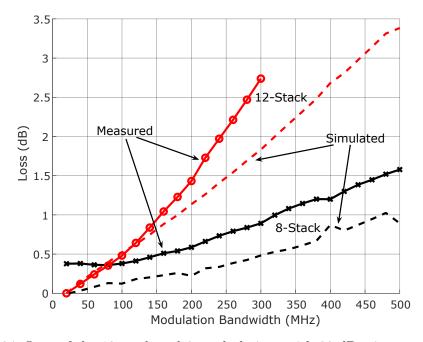

Beyond a higher compression point, the major distinction between the resistive and inductive version of modulator A is the maximum possible FBW. This is shown in Fig. 3.14 in which the inductive version is capable of handling modulation speeds of up to 300 MHz before the loss compresses by 1 dB while the resistive version compresses at 40 MHz.

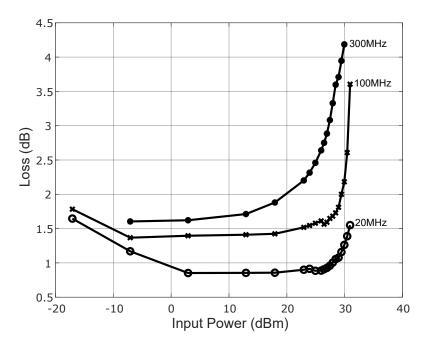

From the theory in section II, eq. 2.16 predicts that the compression point of the

Figure 3.13: Loss vs.  $P_{in}$  at 20 MHz modulation including all power from harmonics for both resistive and inductive versions of modulator B

Figure 3.14: Loss versus modulation bandwidth with 20 dBm input power considering dominant spectral lobes for both the resistive and inductive versions of modulator B

Figure 3.15: Power compression of the inductive version of modulator B with increasing modulation bandwidth

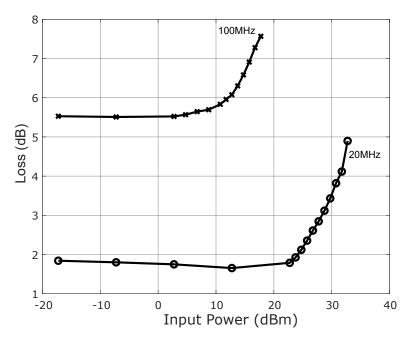

Figure 3.16: Power compression of the resistive version of modulator B at 20 MHz and 100 MHz modulation bandwidth

TABLE III

IIP3 Measured Vs. Two-Tone Offset

| THE STREET VOLUME OF THE STREET |    |      |      |      |      |      |     |

|---------------------------------|----|------|------|------|------|------|-----|

| Offset (MHz)                    | 1  | 5    | 20   | 40   | 60   | 80   | 100 |

| IIP3 (dBm) Modulator B          | 42 | 42.9 | 42.8 | 42.8 | 42.9 | 42.2 | 42  |

switches is inversely proportional to modulation frequency. To demonstrate this, the  $P_{1dB}$  of the inductive version was measured at 20, 100, and 300 MHz and is plotted in Fig. 3.15. At 100 MHz the  $P_{1dB}$  drops slightly to 30.2 dBm while at 300 MHz, the  $P_{1dB}$  drops to 25.9 dBm. Similarly, the  $P_{1dB}$  of the resistive version is plotted in Fig. 3.16. Even though the IL is very high from the slow rise times of the switch, the power compression point has also dropped more than 10 dB compared to when modulating at a lower frequency.

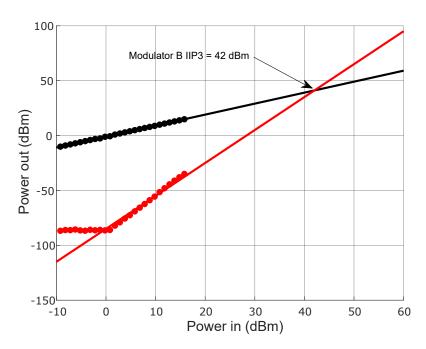

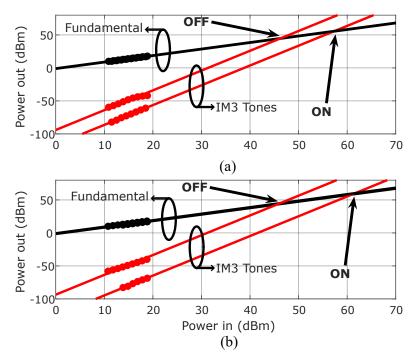

A two-tone test is performed with CF1020 circulators at the output of each signal generator to prevent crosstalk before signals were combined. Terminating the third port with a  $50\Omega$  load allows the circulators to act as isolators and improve the linearity of the test-bench. Additionally, the attenuation of the N9030B spectrum analyzer used to measure the output was set to 40 dB in order to maximize the linearity of the spectrum analyzer itself. This test setup allowed for a maximum input power of the two tones to be 21 dBm and the IIP3 of the test-bench was measured at 62 dBm. This measurement using a 1 MHz offset is shown in Fig. 3.17 and demonstrates that the IIP3 of modulator B when using an inductive gate termination is 42 dBm. The measurement was repeated at various offsets and is given in table I. Like with modulator A, the IIP3 of modulator B was measured over several offsets and the data is given in table III.

Figure 3.17:  $P_{in}$  vs.  $P_{out}$  and IM3 products to extrapolate IIP3 for the inductive version of modulator B at a 1MHz offset

## 3.3 Modulator C: Reflective Shunt Modulator

## 3.3.1 Design

The previous designs use back-to-back differential baluns to perform modulation. While these designs are good for low phase ans amplitude imbalance, and the switches allow for low loss, the baluns add an additional loss of up to 1.6 dB making them the limiting factor of the design

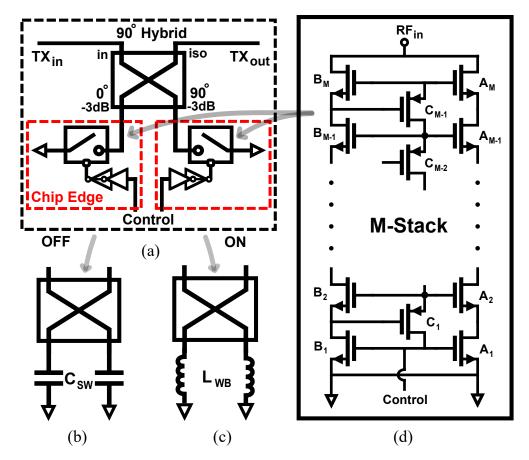

Alternatively, a reflection phase shifter (RPS) can be used to perform BPSK modulation. The proposed circuit makes use of a hybrid coupler rather than back-to-back baluns. Hybrid couplers with a loss of < 0.2 dB are readily available and, therefore, the RPS design offers significant advantages in overall loss compared to those using back-to-back baluns. The principle of operation for the RPS is to modulate the load seen by the through and coupled ports of a hybrid coupler. The reflections at these ports cancel at

Figure 3.18: (a) Schematic of the RPS modulators, (b) Equivalent circuit when switches are open, (c) Equivalent circuit when switches are closed, and (d) Schematic of stacked-FET switches for high power, high bandwidth modulation.

the input port and add constructively at the isolated port of the coupler, respectively. By changing the phase of the reflection coefficient, the relative change in phase is imparted on the summed signal at the isolated port, creating a phase shift. For 2-state phase modulation, i.e. BPSK, only two reflection coefficients are needed,  $\Gamma = 1$  and  $\Gamma = -1$ . An RF switch can be opened and closed at each output of the coupler to create either a 0 or 180 degree phase shift as shown in Fig. 3.18 (a).

When the switches are OFF, the reflection is ideally open, e.g.  $\Gamma = 1$ . However, the switch contributes some parasitic capacitance, labeled  $C_{SW}$ , to ground. The equivalent

schematic is shown in Fig. 3.18 (b). Consequently, the reflection coefficient is

$$\Gamma_{OFF} = \frac{1 - j\omega C_{SW} Z_o}{1 + j\omega C_{SW} Z_o}.$$

(3.1)

When the switches are ON, the reflection is ideally shorted, e.g.  $\Gamma = -1$ . Due to the inductance contributed by the wirebonds,  $L_{WB}$ , between the signal path and the switch and between the PCB and chip grounds as in Fig.3.18 (c), and the reflection coefficient is

$$\Gamma_{ON} = \frac{j\omega L_{WB}/Z_o - 1}{j\omega L_{WB}/Z_o + 1}.$$

(3.2)

While the effect of  $C_{SW}$  and  $L_{WB}$  would be detrimental to generating the precise reflection coefficient, the phase shift remains 180 degrees when  $C_{SW}$  and  $L_{WB}$  present equal impedance. Adding additional switches and passives could generate any desired phase shift which could have other implications for phased array design, load-pull networks or analog self interference cancellers.

Using an RPS approach does add some additional challenges in switch design. Because the incident wave is reflected off of  $\Gamma = 1$  when the switch is open, the peak voltage seen at the input of the switch is doubled. Since the hybrid coupler divides the power equally between the two ports, the incident voltage on the switches is equal to  $2/\sqrt{2} \cdot V_{TXin}$ . To handling the high voltage, the shunt switches from section 2.5 can be used.

Two versions of the RPS modulator were designed. First a 12-stack switch was used to test what the highest voltage the CMOS switches could tolerate while still having relatively fast switching speeds. Second, an impedance transformation network at the input of each switch can be used to lower the voltage requirements for the same power handling. This allows the fewer stacks to be used with larger individual devices. The total load capacitance of the switch driver remains about the same, but since the stack

has fewer series components, the gate resistance is reduced and therefore switching speed can be increased. The trade-off for this design is that the RPS will only produce the desired phase shift at the design frequency as opposed to wide-band operation in the case of the non-transformed design. After optimizing for power handling, and phase and amplitude imbalance, an impedance transformation  $Z_0$  in the range of 12.5-25  $\Omega$  requires 8 stacked FETs with FETs  $A_1$ - $A_8$  each 5 mm wide. For a design without impedance transformation, the maximum useful number of stacks is 12 with each A device having a width of 1.8 mm. The secondary device sizing of the tapered ladder switches is given in Table IV - the tapering factor for the B devices is  $x \sim 2.5$  while for the C devices  $x \sim 2$ .

TABLE IV

STACKED FET SWITCH SIZING

| FET Index (M) | 8 St                 | tack                 | 12 Stack             |                      |  |

|---------------|----------------------|----------------------|----------------------|----------------------|--|

|               | B Sizing             | C Sizing             | B Sizing             | C Sizing             |  |

| 1             | 5mm                  | 5mm                  | 1.8mm                | 1.8mm                |  |

| 2             | 1.25mm               | 1.25mm               | $450 \mu \mathrm{m}$ | $450 \mu \mathrm{m}$ |  |

| 3             | $312 \mu \mathrm{m}$ | $312 \mu \mathrm{m}$ | $112 \mu \mathrm{m}$ | $112 \mu \mathrm{m}$ |  |

| 4             | $104 \mu \mathrm{m}$ | $200 \mu \mathrm{m}$ | $38 \mu \mathrm{m}$  | $72 \mu \mathrm{m}$  |  |

| 5             | $52 \mu \mathrm{m}$  | $138 \mu \mathrm{m}$ | $19 \mu \mathrm{m}$  | $50 \mu \mathrm{m}$  |  |

| 6             | $39 \mu \mathrm{m}$  | $113 \mu \mathrm{m}$ | $14 \mu \mathrm{m}$  | $40 \mu \mathrm{m}$  |  |

| 7             | $36 \mu \mathrm{m}$  | $96 \mu \mathrm{m}$  | $13 \mu \mathrm{m}$  | $35 \mu \mathrm{m}$  |  |

| 8             | $35 \mu \mathrm{m}$  | N/A                  | $12 \mu \mathrm{m}$  | $30 \mu \mathrm{m}$  |  |

| 9-12          | N/A                  | N/A                  | $12\mu\mathrm{m}$    | $28 \mu \mathrm{m}$  |  |

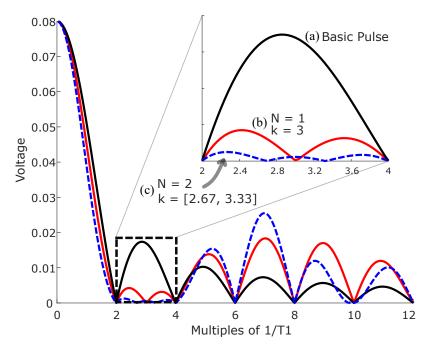

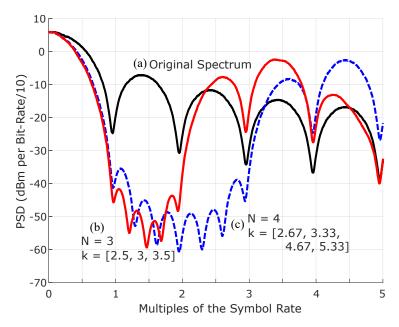

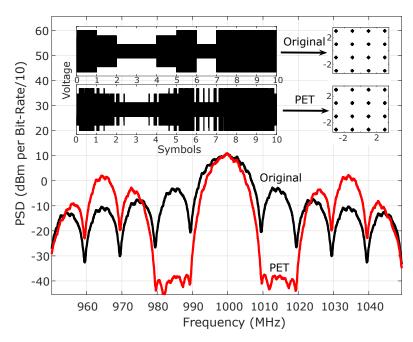

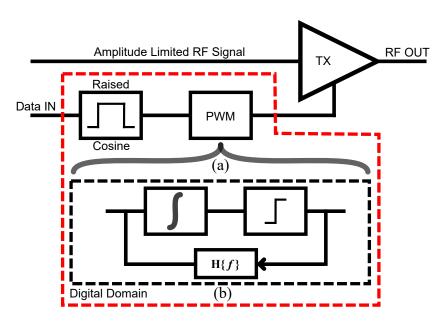

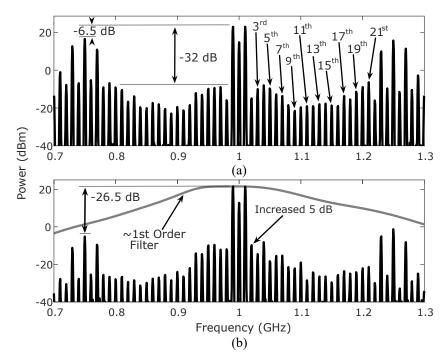

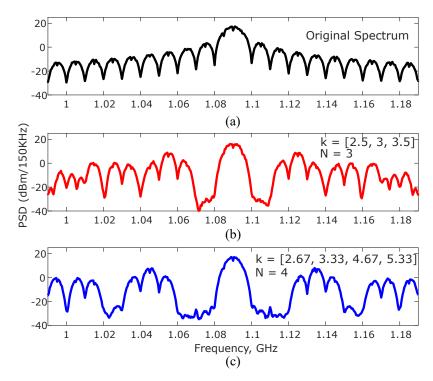

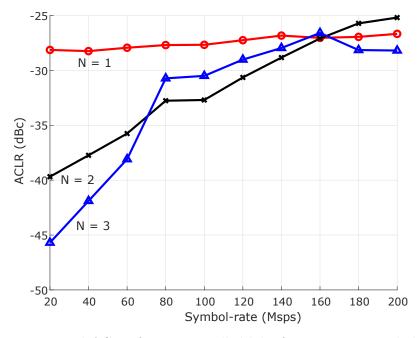

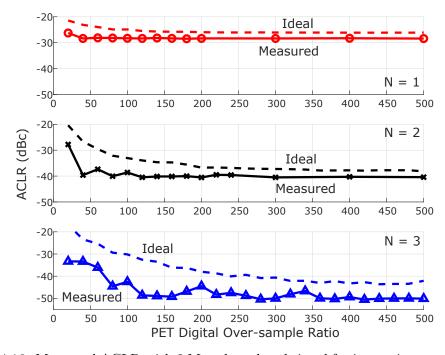

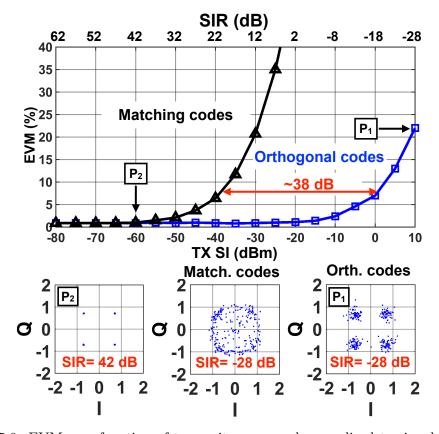

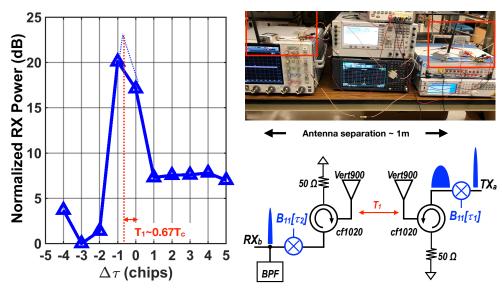

#### 3.3.2 Measurements