## UC San Diego UC San Diego Electronic Theses and Dissertations

**Title** Breaking the ISA Barrier in Modern Computing

Permalink https://escholarship.org/uc/item/8rp233s4

**Author** Venkat, Ashish

Publication Date 2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

### **Breaking the ISA Barrier in Modern Computing**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Computer Science**

by

Ashish Venkat

Committee in charge:

Professor Dean M. Tullsen, Chair Professor Andrew B. Kahng Professor Sorin Lerner Professor Timothy Sherwood Professor Deian Stefan

2018

Copyright Ashish Venkat, 2018 All rights reserved. The dissertation of Ashish Venkat is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2018

DEDICATION

To Suchetha.

### EPIGRAPH

If we knew what it was we were doing, it would not be called research, would it? —Albert Einstein

## TABLE OF CONTENTS

| Signature Pag  | ge                                                                                                                                                                                                                                                                        |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .   | iv                                                                                                                                                                                                                                                                        |

| Epigraph       |                                                                                                                                                                                                                                                                           |

| Table of Con   | tents                                                                                                                                                                                                                                                                     |

| List of Figure | esix                                                                                                                                                                                                                                                                      |

| List of Tables | xi                                                                                                                                                                                                                                                                        |

| Acknowledge    | ements                                                                                                                                                                                                                                                                    |

| Vita           | XV                                                                                                                                                                                                                                                                        |

| Abstract of th | e Dissertation                                                                                                                                                                                                                                                            |

| Chapter 1      | Introduction11.1Breaking the ISA Barrier21.1.1Cross-ISA Process Migration31.1.2Design of a Heterogeneous-ISA Chip Multiprocessor41.1.3HIPStR: Security Defense via ISA Diversification51.1.4Composite-ISA Architectures61.2Overview of Dissertation8                      |

| Chapter 2      | Background102.1Heterogeneous Architectures102.2The Path to Multi-ISA Heterogeneity132.3Return-Oriented Programming152.4ROP Mitigations17                                                                                                                                  |

| Chapter 3      | Cross-ISA Process Migration213.1Symmetrical Fat Binary223.2Multi-ISA Compilation233.3State Transformation253.4Binary Translation263.4.1Translation Block Chaining273.4.2ISA-Specific Challenges293.5Experimental Methodology313.6Results333.6.1Steady State Performance33 |

|           | 3.7 | 3.6.2         Migration Cost         33           Conclusion         39 |

|-----------|-----|-------------------------------------------------------------------------|

|           |     |                                                                         |

| Chapter 4 |     | gn of a Heterogeneous-ISA Chip Multiprocessor                           |

|           | 4.1 | Harnessing ISA Diversity                                                |

|           | 4.2 | Design Space Exploration                                                |

|           | 4.3 | Programming Environment and Memory Layout                               |

|           | 4.4 | Experimental Methodology                                                |

|           | 4.5 | Results                                                                 |

|           |     | 4.5.1 Evaluation of the Heterogeneous-ISA Architecture 52               |

|           |     | 4.5.2 Framework for ISA-Microarchitecture co-design 55                  |

|           |     | 4.5.3 ISA Affinity                                                      |

|           | 4.6 | Conclusion                                                              |

| Chapter 5 | HIP | StR: Security Defense via ISA Diversification                           |

| 1         | 5.1 | Background and Motivation                                               |

|           | 5.2 | Architectural Overview                                                  |

|           |     | 5.2.1 Security and Performance Guarantees                               |

|           |     | 5.2.2 Instruction Set Randomization                                     |

|           |     | 5.2.3   Program State Relocation   64                                   |

|           |     | 5.2.4 Heterogeneous-ISA PSR                                             |

|           | 5.3 | Assumptions and Threat Model                                            |

|           | 5.4 | Design and Implementation                                               |

|           | 5.4 |                                                                         |

|           |     | e                                                                       |

|           |     | 5.4.2 PSR-aware Execution Migration                                     |

|           |     | 5.4.3 Execution Scenarios                                               |

|           |     | 5.4.4 Performance Optimizations                                         |

|           |     | 5.4.5 Prototype Implementation of PSR                                   |

|           | 5.5 | Experimental Methodology                                                |

|           | 5.6 | Evaluation80                                                            |

|           |     | 5.6.1 Security Evaluation                                               |

|           |     | 5.6.2 Performance Evaluation                                            |

|           | 5.7 | Conclusion                                                              |

| Chapter 6 | Con | posite-ISA Architectures                                                |

|           | 6.1 | ISA Feature Set Derivation                                              |

|           | 6.2 | Compiler and Runtime Strategy                                           |

|           |     | 6.2.1 Compiler Toolchain Development                                    |

|           |     | 6.2.2 Migration Strategy                                                |

|           | 6.3 | Decoder Design and Implementation                                       |

|           |     | 6.3.1 Instruction Encoding                                              |

|           |     | 6.3.2 Decoder Analysis                                                  |

|           | 6.4 | Experimental Methodology                                                |

|           | 2   | r · · · · · · · · · · · · · · · · · · ·                                 |

|              | 6.5  | Results   |                                   |   |

|--------------|------|-----------|-----------------------------------|---|

|              |      | 6.5.1     | Performance and Energy Efficiency |   |

|              |      | 6.5.2     | Feature Sensitivity Analysis      |   |

|              |      | 6.5.3     | Feature Affinity                  | I |

|              |      | 6.5.4     | Migration Cost Analysis           |   |

|              | 6.6  | Conclu    | ision                             |   |

| Chapter 7    | Conc | luding    | Remarks                           |   |

| Bibliography |      | · • • • • |                                   | 1 |

## LIST OF FIGURES

| Figure 2.1:                               | Return-oriented Programming                                                                                                                   | 16             |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 3.1:<br>Figure 3.2:<br>Figure 3.3: | Symmetrical Fat Binary                                                                                                                        | 22<br>25<br>34 |

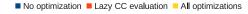

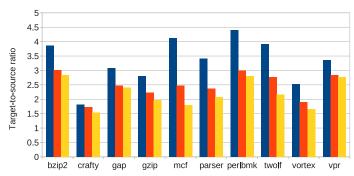

| Figure 3.4:<br>Figure 3.5:                | Optimizations made during Binary Translation from ARM to MIPS<br>Register and Immediate Caching during Binary Translation from MIPS to<br>ARM | 35<br>35       |

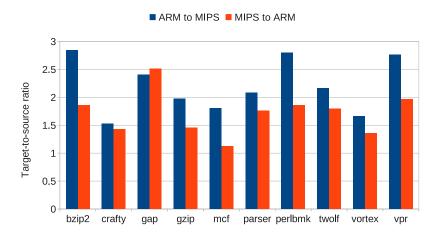

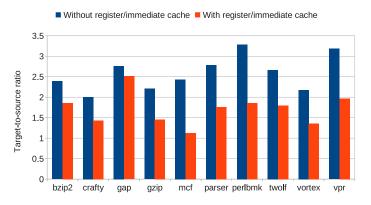

| Figure 3.6:                               | Total-to-Source Ratio                                                                                                                         | 36             |

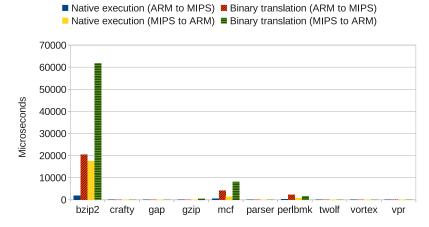

| Figure 3.7:                               | Comparison of Binary Translation with native performance                                                                                      | 37             |

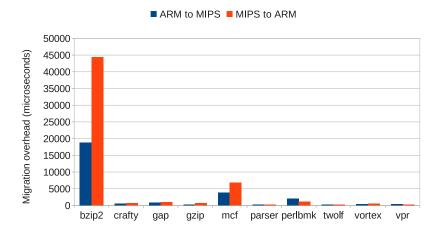

| Figure 3.8:                               | Total Migration Overhead in microseconds                                                                                                      | 38             |

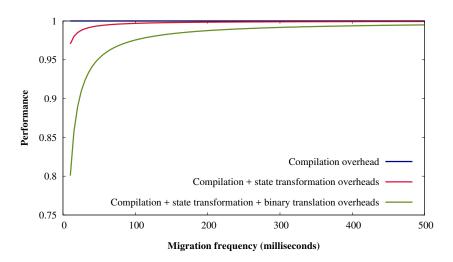

| Figure 3.9:                               | Performance vs. migration frequency                                                                                                           | 39             |

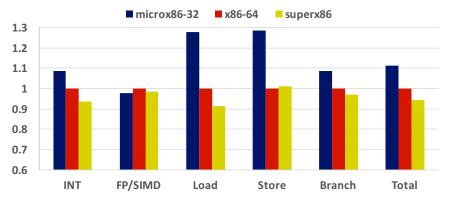

| Figure 4.1:                               | Instruction Mix                                                                                                                               | 44             |

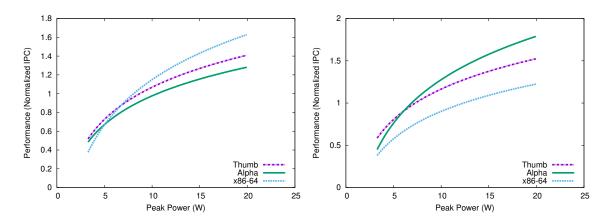

| Figure 4.2:                               | Performance comparison under different peak power budgets for two different execution phases of bzip2                                         | 45             |

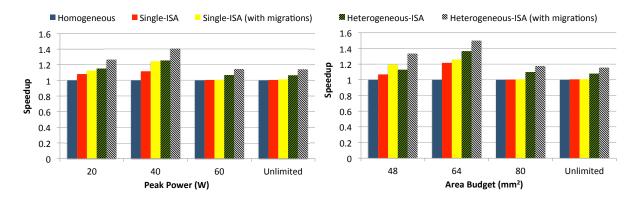

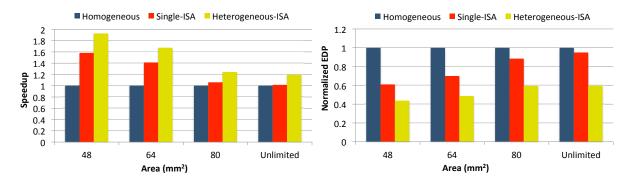

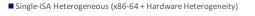

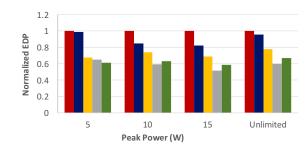

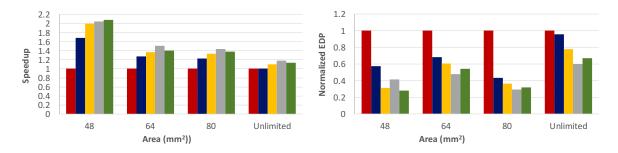

| Figure 4.3:                               | Multi-programmed Workload Performance comparison under different peak<br>power and area budgets                                               | 52             |

| Figure 4.4:                               | Energy-Delay-Product comparison for multi-programmed workloads under different peak power and area budgets                                    | 53             |

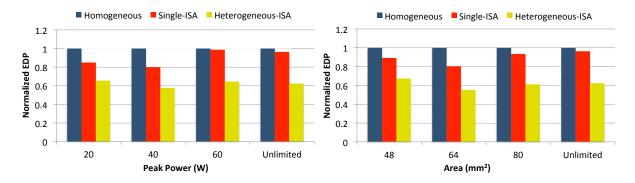

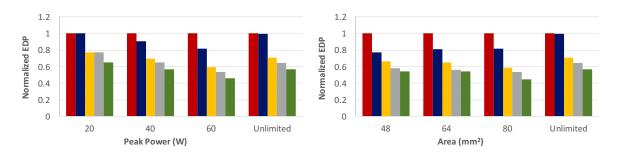

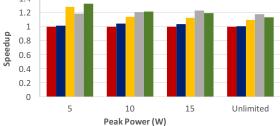

| Figure 4.5:                               | Single Thread Performance and EDP evaluation using the dynamic multicore topology                                                             | 54             |

| Figure 4.6:                               | Single Thread Performance and EDP evaluation under different area budgets                                                                     | 55             |

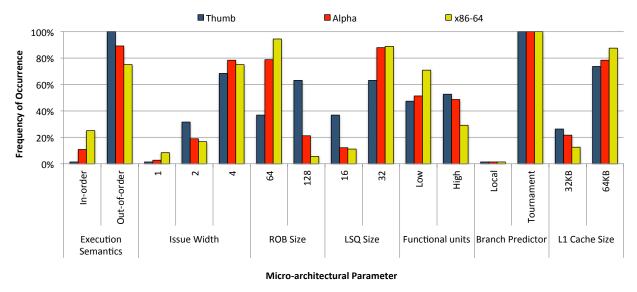

| Figure 4.7:                               | ISA-Microarchitecture co-design                                                                                                               | 56             |

| Figure 4.8:                               | Core Selection                                                                                                                                | 58             |

| Figure 4.9:                               | Split Overhead                                                                                                                                | 59             |

| C                                         |                                                                                                                                               |                |

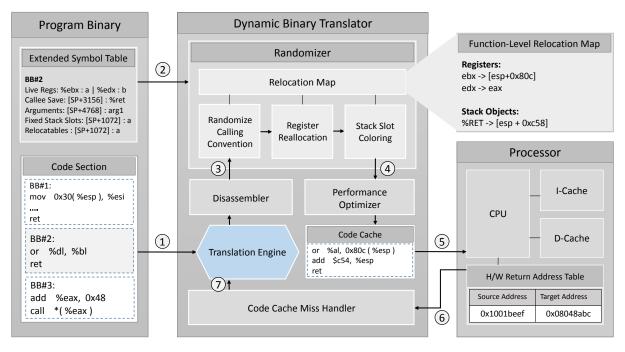

| Figure 5.1:                               | Program State Relocation Architecture                                                                                                         | 65             |

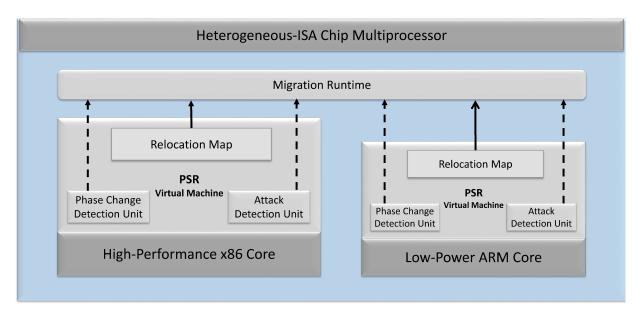

| Figure 5.2:                               | Heterogeneous-ISA Program State Relocation                                                                                                    | 67             |

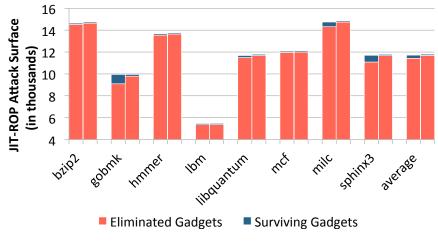

| Figure 5.3:                               | Attack Surface of a Victim Program                                                                                                            | 75             |

| Figure 5.4:                               | Classic ROP Attack Surface                                                                                                                    | 80             |

| Figure 5.5:                               | Brute Force Attack Surface                                                                                                                    | 81             |

| Figure 5.6:                               | JIT-ROP Attack Surface on (a) PSR, (b) HIPStR                                                                                                 | 82             |

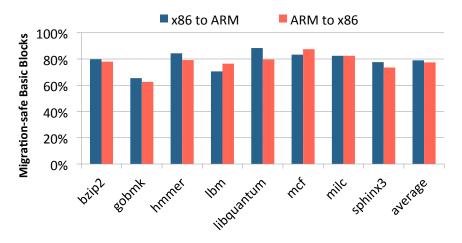

| Figure 5.7:                               | Percentage of Migration-Safe Basic Blocks                                                                                                     | 83             |

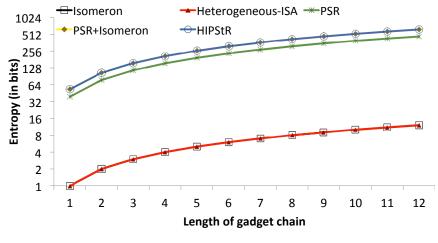

| Figure 5.8:                               | Entropy Comparison                                                                                                                            | 84             |

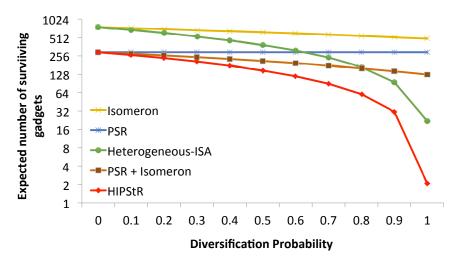

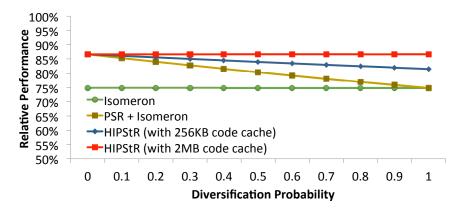

| Figure 5.9:                               | Effect of diversification on attack surface                                                                                                   | 85<br>86       |

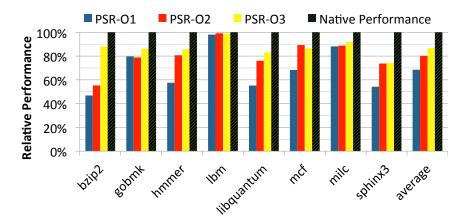

| -                                         | Performance Optimizations for PSR                                                                                                             | 86<br>87       |

| Figure 5.11:                              |                                                                                                                                               | 87<br>00       |

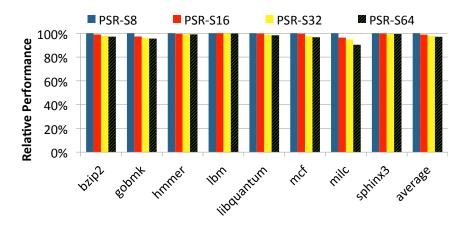

| -                                         | RAT Miss Penalty                                                                                                                              | 88             |

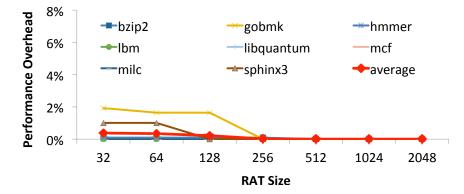

|                                           | Migration Overhead                                                                                                                            | 89<br>80       |

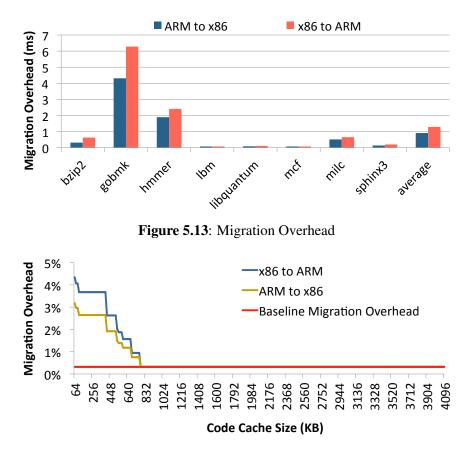

| Figure 5.14:                              | Code Cache                                                                                                                                    | 89             |

| Figure 5.15: | Integrated Performance                                                              | 90    |

|--------------|-------------------------------------------------------------------------------------|-------|

| Figure 6.1:  | Feature Sets                                                                        | 98    |

| Figure 6.2:  | Instruction Mix                                                                     | 98    |

| Figure 6.3:  | Encoding                                                                            | 103   |

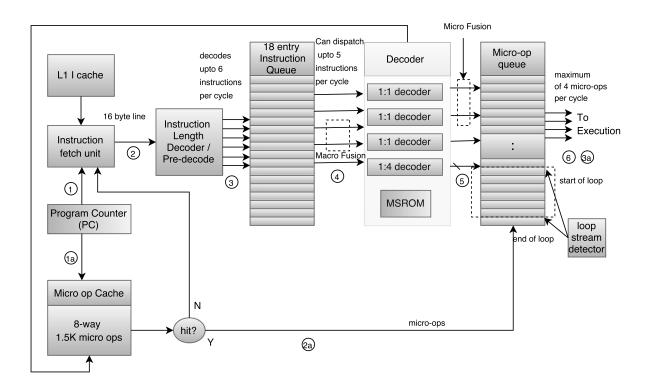

| Figure 6.4:  | Decoder                                                                             | 104   |

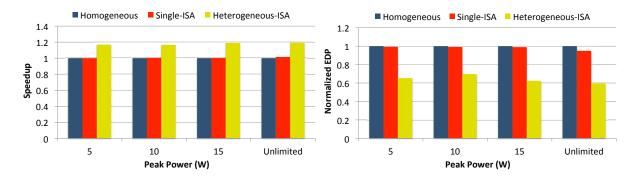

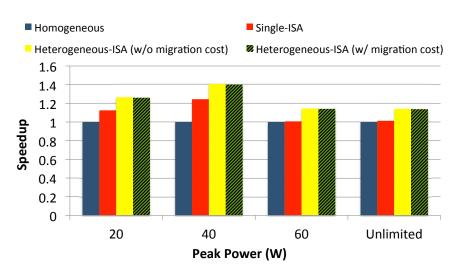

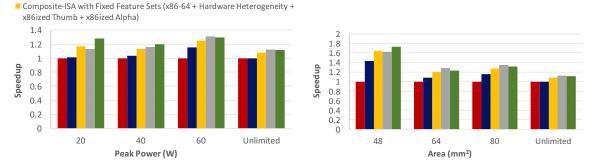

| Figure 6.5:  | Multi-programmed workload throughput comparison (higher is better)                  | 109   |

| Figure 6.6:  | Multi-programmed workload EDP comparison (lower is better)                          | 110   |

| Figure 6.7:  | Single Thread Performance (higher is better) and EDP (lower is better)              |       |

|              | comparison under Peak Power Budget                                                  | 112   |

| Figure 6.8:  | Single Thread Performance (higher is better) and EDP (lower is better)              |       |

|              | comparison under Area Budget                                                        | 112   |

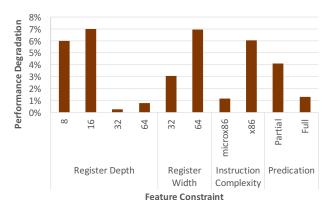

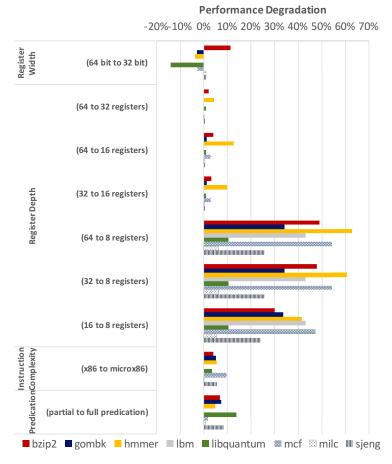

| Figure 6.9:  | Performance Degradation over Composite-ISA Designs optimized for multi-             |       |

|              | programmed workload throughput at 48mm <sup>2</sup> budget, and under different     |       |

|              | Feature Constraints                                                                 | 113   |

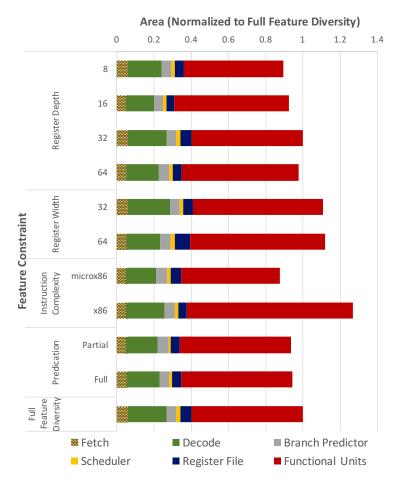

| Figure 6.10: | Transistor Investment by Processor Area normalized over that of Composite-          |       |

|              | ISA Designs optimized for multi-programmed workload throughput at 48mm <sup>2</sup> |       |

|              | budget, and under different Feature Constraints                                     | 114   |

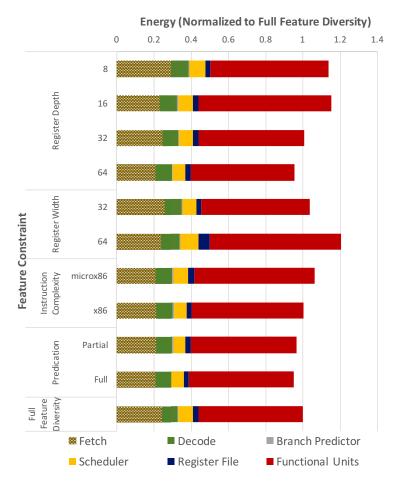

| Figure 6.11: | Processor Energy Breakdown normalized over that of Fully Custom Designs             |       |

|              | optimized for multi-programmed workload throughput at 48mm <sup>2</sup> budget, and |       |

|              | under different Feature Constraints                                                 | 115   |

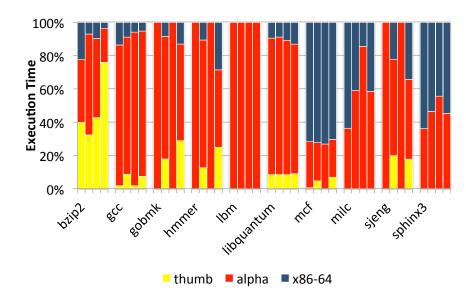

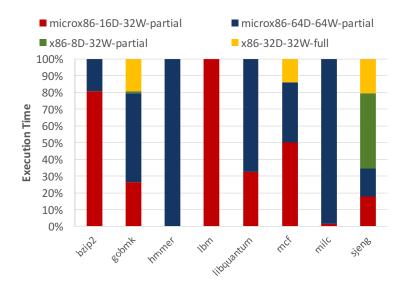

| Figure 6.12: | Execution Time Breakdown on the best composite-ISA CMP optimized for                |       |

|              | Single Thread Performance under a Peak Power Budget of 10W                          | 117   |

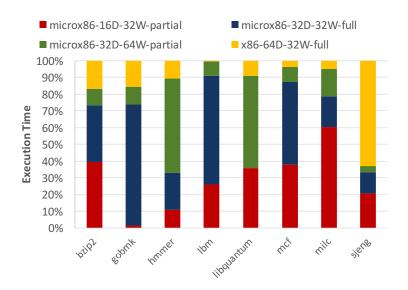

| Figure 6.13: | Execution Time Breakdown on the best composite-ISA CMP optimized for                |       |

|              | Multi-programmed Throughput under an Area Budget of $48 \text{mm}^2 \dots \dots$    | 118   |

| •            | Feature Downgrade Cost                                                              | 119   |

| Figure 6.15: | Multi-threaded Workload Throughput with Downgrade Cost                              | . 121 |

## LIST OF TABLES

| Table 3.1:<br>Table 3.2:               | Architecture detail for ARM and MIPS cores       | 32<br>37       |

|----------------------------------------|--------------------------------------------------|----------------|

| Table 4.1:<br>Table 4.2:<br>Table 4.3: | Design space of a Heterogeneous-ISA architecture | 46<br>47<br>48 |

| Table 5.1:                             | Attack Surface: Symbols and Definitions          | 76             |

| Table 5.2:                             | Architecture detail for ARM and x86 cores        | 78             |

| Table 5.3:                             | Inferences from Brute Force Simulation           |                |

| Table 5.4:                             | Performance Optimizations for PSR                | 86             |

| Table 5.5:                             | Entropy Levels for PSR                           | 87             |

| Table 6.1:                             | Feature Exploration Space                        | 106            |

| Table 6.2:                             | x86-ized versions of Thumb, Alpha, and x86-64    | 108            |

#### ACKNOWLEDGEMENTS

First and foremost, I owe immense thanks to my advisor Dean Tullsen, who has been an inspiring teacher, a prolific research mentor, and a father figure who has shaped my life in many profound ways. Dean's tireless enthusiasm of pursuing new and ambitious research ideas and his incredible dedication to science has been a constant source of motivation and inspiration to me as a young researcher. He has always encouraged me to set challenging goals for myself, and has never settled for anything but the best in everything that I do. He has provided me with a plethora of opportunities that have had a significant role to play in my growth as a researcher and an academic. I could never thank him enough for his words of wisdom and reassurance during turbulent times, and for the invaluable life lessons of ethics, empathy, and sensitivity he has given me through an exemplary lifestyle, which I will strive to emulate through the rest of my life.

My many thanks are due to my PhD committee members Tim Sherwood, Sorin Lerner, Andrew Kahng, and Deian Stefan for providing me with valuable feedback from time to time. I'd like to thank Hovav Shacham for his many useful insights and suggestions during my thesis proposal. I'd also like to take this opportunity to thank Jason Mars and Hadi Esmaeilzadeh for believing in me and for their support and encouragement throughout my PhD career.

I'd like to thank many research colleagues who have made this dissertation possible. In particular, I'd like to thank Matt DeVuyst for his mentorship during my first year. I'd also like to acknowledge Arvind Krishnaswamy, Rajan Palanivel, Koichi Yamada, and other colleagues at Intel for the many brainstorming sessions during the initial days of formulating HIPStR. I'd like to thank Doug Burger and Aaron Smith for their mentorship while I was at Microsoft. I'd also like to thank Sriskanda Shamasunder for being a diligent hacker, and for so many fun-filled conversations in the lab amidst all the craziness. I'd like to thank Harsha Basavaraj for taking up the onerous task of the RTL design of the x86 decoder. Finally, I'd like to thank my first mentee, Kazem Taram, for all his enthusiasm, hard work, and dedication that have made my mentorship an enjoyable experience. I'd like to take this opportunity to thank my lab mates – Hung-Wei Tseng, Manish Gupta, Sam Wasmundt, Andreas Prodromou, Brian Tsui, Jinghao Jia, Yishin Shih, and Zinsser Zhang. I'd also like to thank my friends from college, Freescale, Brocade, and graduate school, and my family members including my brother and sister-in-law, my parents-in-law, and my brother-in-law for always believing in me.

I owe so much to Suchetha for being an incredibly understanding and supportive wife. I thank her for an extraordinarily fun-filled life journey together that has kept my sanity through the many trials and tribulations of graduate school and academic job search. We have been through many life adventures together, and honestly none of this would matter, if not for her. The successful completion of this dissertation is due, in large part, to her unconditional love and unwavering support.

Finally, I'd like to thank my parents for being strong pillars of support throughout my life. They have always encouraged me to explore and pursue opportunities, go above and beyond my potential, think big, and never give up. I'd also like to acknowledge that my mom is my first teacher – she has taught me to be hard working and meticulous in whatever I do. My dad has had a significant influence in my life as an academic, in honing my writing and speaking skills, and in inducing, promoting, and reinforcing my love for Computer Science.

Chapter 3, in part, is a reprint of the material as it appears in proceedings of ASPLOS 2012. DeVuyst, Matthew; Venkat, Ashish; Tullsen, Dean M., Execution Migration in a Heterogeneous-ISA Chip Multiprocessor, 17th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), March, 2012. The dissertation author was the primary investigator and author of this paper.

Chapter 4, in full, is a reprint of the material as it appears in proceedings of ISCA 2014. Venkat, Ashish; Tullsen, Dean M., Harnessing ISA Diversity: Design of a Heterogeneous-ISA Chip Multiprocessor, 41st ACM International Symposium on Computer Architecture (ISCA), June, 2014. The dissertation author was the primary investigator and author of this paper. Chapter 5, in full, is a reprint of the material as it appears in proceedings of ASPLOS 2016. Venkat, Ashish; Shamasunder, Sriskanda; Shacham, Hovav; Tullsen, Dean M., HIPStR: Heterogeneous-ISA Program State Relocation, 21st ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), April, 2016. The dissertation author was the primary investigator and author of this paper.

Chapter 6, in full, is currently being prepared for submission for publication of the material. Venkat, Ashish; Basavaraj, Harsha; Tullsen, Dean M., Composite-ISA Cores: Enabling Multi-ISA Heterogeneity using a Single ISA. The dissertation author was the primary investigator and author of this material.

#### VITA

| 2008      | Bachelor of Engineering, NIE Mysuru                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------|

| 2008-2009 | Freescale Semiconductor, Bengaluru                                                                        |

| 2009-2010 | Brocade Communications, Bengaluru                                                                         |

| 2011      | Software Development Intern<br>Amazon.com, Inc., Seattle, WA                                              |

| 2012      | Graduate Technical Intern<br>Intel Corporation, Santa Clara, CA                                           |

| 2014      | Master of Science, Computer Science, University of California, San Diego                                  |

| 2014      | C. Phil. in Computer Science, University of California, San Diego                                         |

| 2015      | Research Intern<br>Microsoft Research, Redmond, WA                                                        |

| 2016      | Research Intern<br>IBM Research Labs, Haifa, Israel                                                       |

| 2011-2017 | Teaching Assistant, Department of Computer Science and Engineering<br>University of California, San Diego |

| 2011-2018 | Research Assistant, Department of Computer Science and Engineering<br>University of California, San Diego |

| 2018      | Doctor of Philosophy, University of California, San Diego                                                 |

#### PUBLICATIONS

Ashish Venkat, Harsha Basavaraj, Dean M. Tullsen. "Composite-ISA Cores: Enabling Multi-ISA Heterogeneity using a Single ISA", *Under Review*, 2018.

Andreas Prodromou, Ashish Venkat, and Dean M. Tullsen. "Deciphering Predictive Schedulers for Heterogeneous-ISA Architectures", *Under Review*, 2018.

Mohammadkazem Taram, Ashish Venkat, and Dean M. Tullsen. "Context-Sensitive Fencing: Securing Speculative Execution via Microcode Customization", *In Preparation*, 2018.

Mohammadkazem Taram, Ashish Venkat, and Dean M. Tullsen. "Mobilizing the Micro-Ops: Exploiting Context-Sensitive Decoding for Security and Energy Efficiency", *ISCA*, 2018.

Manish Gupta, Vilas Sridharan, David Roberts, Andreas Prodromou, Ashish Venkat, Dean M. Tullsen, and Rajesh Gupta. "Reliability-Aware Data Placement for Heterogeneous Memory Architecture", *HPCA*, 2018.

Ashish Venkat, Sriskanda Shamasunder, Hovav Shacham, and Dean M. Tullsen. "NuHIPStR: Heterogeneous-ISA Program State Relocation", *ASPLOS*, 2016.

Ashish Venkat, Arvind Krishnaswamy, Yamada Koichi, and Rajan Palanivel. "Binary Translation-Driven Program State Relocation", *US Patent*, 2015.

Ashish Venkat and Dean M. Tullsen. "Harnessing ISA Diversity: Design of a Heterogeneous-ISA Chip Multiprocessor", *ISCA*, 2014.

Matthew DeVuyst, Ashish Venkat, and Dean M. Tullsen. "Execution Migration in a Heterogeneous-ISA Chip Multiprocessor", *ASPLOS*, 2012.

#### ABSTRACT OF THE DISSERTATION

#### **Breaking the ISA Barrier in Modern Computing**

by

Ashish Venkat

Doctor of Philosophy in Computer Science

University of California San Diego, 2018

Professor Dean M. Tullsen, Chair

In recent years, the computing landscape has witnessed a shift towards hardware specialization in response to the rapid growth and expansion of software, changing market risks, and fundamental technological limitations. However, the largest barrier to full exploitation of heterogeneity has by far been the difficulty of programming for them. There is a pressing need for systems that allow the exploitation of highly heterogeneous platforms without creating additional programmer burden. The goal of this dissertation is to empower the hardware/software interface, specifically the Instruction Set Architecture (ISA) and the runtime system, with diverse capabilities to enable the seamless adoption of heterogeneous hardware, without breaking the traditional models of programming. Existing heterogeneous designs either constrain CPU cores to feature a single ISA or allow multiple ISAs that assign distinct jobs to distinct cores, or at best statically partition work, resulting in a tight coupling of an application to the underlying ISA. This dissertation challenges the assumption that the single-ISA constraint is necessary, and further enables programs to cross a heretofore forbidden boundary – the ISA. In particular, this dissertation describes a compiler and runtime strategy for swift and seamless process migration across diverse ISAs, and further showcases results from a massive core architecture optimization process that demonstrates the performance and energy efficiency benefits of multi-ISA heterogeneous architectures. In addition to its performance and energy efficiency benefits, this dissertation also explores and demonstrates the security potential of multi-ISA architectures to thwart several evasive variants of the Return-Oriented Programming (ROP) attack. This dissertation further alleviates the complexity concerns of multi-vendor ISA heterogeneity by studying the effect of introducing composite-ISA heterogeneity.

## Chapter 1

# Introduction

The modern computing landscape is characterized by the rapid evolution of software, changing market risks, rising security threats, and technological limitations. The microprocessor industry, fraught with these challenges, has witnessed consistently diminishing rates of improvement in the execution efficiency of high-end general-purpose CPUs that drive a considerable chunk of the world's computational demands. Consequently, the high cost of the one-size-fits-all computational model has now become increasingly apparent – general-purpose processors perform well on an average case, but they allow no individual application to run as efficiently as it would on specialized hardware. Thus, hardware specialization or heterogeneity has and will continue to play a crucial role in modern processor and system design.

Modern processor architectures employ hardware specialization in two key dimensions. While some architectures employ specialized cores to accelerate the performance of certain domain-specific workloads [san08, fus08, teg10, Qua11, PCC<sup>+</sup>14, JYP<sup>+</sup>17], others take advantage of microarchitectural heterogeneity by combining large high-performance cores and small power-efficient cores on the same chip, to create efficient designs that cater to the diverse execution characteristics of general-purpose mixed workloads [teg11, Gre11, HM08, KFJ<sup>+</sup>03, KTR<sup>+</sup>04, KTJ06, VCJE<sup>+</sup>12, cut17]. Multiple commercial offerings exist today, in general-purpose, embedded, and server markets, that exploit both dimensions. However, the largest barrier to full exploitation of heterogeneity has been the difficulty of adapting that heterogeneity to traditional programming and execution models, resulting in several otherwise efficient hardware designs to be discarded as not viable.

This dissertation introduces a new dimension of heterogeneity that exploits a fundamental abstraction of computing – the Instruction Set Architecture (ISA), while preserving the traditional models of programming and execution. Early work on single-ISA heterogeneous multicore processors [Gre11, HM08, KFJ<sup>+</sup>03, KTR<sup>+</sup>04, KTJ06] constrained CPU cores to a single ISA in order to maximize efficiency by allowing a thread to dynamically identify, and migrate to, the core to which it is most suited during a particular phase and under the current operating conditions. This dissertation challenges the assumption that the single-ISA boundary is necessary and further demonstrates that limiting an architecture to a single ISA sacrifices a critical dimension of heterogeneity.

By pulling down the boundary wall, this dissertation unlocks several previously unexplored *heterogeneous-ISA architectures* that offer greater gains in terms of performance, energy efficiency, and security. These architectures synergistically combine microarchitectural heterogeneity with ISA heterogeneity to realize more efficient designs that can effectively exploit the inherent ISA affinity of an application. In addition, these architectures have the potential to boost the overall entropy and resilience of the system to provide a formidable defense against state-of-the-art code reuse attacks.

## **1.1 Breaking the ISA Barrier**

This dissertation explores several novel and programmer-transparent hardware architecture design, compiler, and runtime techniques to enable the seamless adoption of heterogeneous-ISA architectures. First, it establishes the viability of multi-ISA heterogeneity by proposing a lowcost cross-ISA process migration infrastructure that is orders of magnitude faster than prior art. Second, it showcases the performance and energy savings potential of multi-ISA heterogeneity via a massive core architecture optimization process. Third, it proposes a security defense that takes advantage of ISA diversification to thwart many evasive variants of the Return-Oriented Programming (ROP) attack [Sha07, RBSS12]. Fourth, it significantly alleviates the complexity concerns of multi-ISA heterogeneity by proposing hardware and software techniques that recreate and in many cases, supersede the gains of multi-ISA heterogeneity using a single composite-ISA derived from a large superset.

#### 1.1.1 Cross-ISA Process Migration

Modern architectures allow us to instantly configure the frequency, voltage, cache size, and other microarchitectural parameters to increase efficiency. Yet our ISA choice is typically constrained by a decision made when our phone, laptop, or server was purchased. And yet, the choice of ISA can have a significant impact on execution efficiency. One of the primary goals of this dissertation is to allow us to now make that choice, not just individually for each program, but every few milliseconds within the execution of a single program. However, process migration across heterogeneous ISAs is a non-trivial problem. This is because the runtime program state of an application is always kept in ISA-specific form, potentially requiring expensive state transformation at the time of migration.

This dissertation proposes novel compiler and runtime mechanisms that allow for seamless and instantaneous cross-ISA process migration at less than 5% degradation in overall performance. The key components of the migration infrastructure being (1) a multi-ISA compilation framework that emits a *symmetrical fat binary* containing multiple ISA-specific text sections, a common stack frame layout, and a common ISA-agnostic data section, and (2) a migration runtime that performs dynamic binary translation until execution reaches a compiler-marked *equivalence point*, at which program state (registers and stack objects) can be safely transformed to a different ISA. To assist the creation of a *symmetrical fat binary*, we take advantage of a powerful architecture-independent intermediate representation that can act as a bridge between the ISAs, and provide hints for transforming program state at the time of migration. This work shows that careful and consistent multi-ISA compilation can enable faster and more frequent migrations by significantly minimizing the amount of runtime program state to be transformed, while simultaneously enabling most, if not all ISA-specific transformations. Furthermore, due to the relatively high frequency of compiler-marked *equivalence points*, we find that binary translation for the specific use case of cross-ISA migration calls for a different modus operandi – minimize the translation time rather than optimizing the translation itself. Overall, this work crosses a critical threshold by allowing processes to migrate across ISAs potentially every timer interrupt, while advancing prior state-of-the-art by orders of magnitude.

### 1.1.2 Design of a Heterogeneous-ISA Chip Multiprocessor

By decoupling the execution binary from historical ISA choices, the cross-ISA process migration strategy establishes the viability of multi-ISA heterogeneous architectures that show promising potential in terms of performance and energy efficiency. A critical step in the design of a multi-ISA heterogeneous architecture is choosing a diverse set of ISAs. While ISAs seem to converge over time (RISC ISAs adding complex operations, CISC ISAs translated to RISC micro-ops internally), we find that there remains sufficient diversity in existing modern ISAs to provide useful heterogeneity. This dissertation examines some key aspects that characterize ISA diversity, including code density, decode and instruction complexity, register pressure, native floating-point arithmetic vs emulation, and SIMD processing.

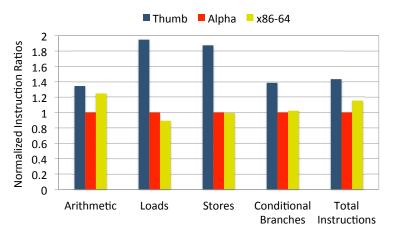

The design of a heterogeneous-ISA chip multiprocessor involves navigating a complex search space, made larger by the additional dimension of freedom. The design space we study in this work encompasses 72 software workloads, 600 single core configurations, and a 128 billion distinct heterogeneous-ISA multicore configurations that harness the diversity offered by three modern ISAs: (1) ARM's ultra-low power Thumb, (2) the traditionally RISC Alpha, and (3) the high-performance CISC x86-64. By co-designing the hardware architectures and the ISAs to provide the best aggregate architecture, we arrive at a more effective and efficient design than one composed of homogeneous cores, or even heterogeneous cores that share a single ISA. Specifically, we show that for a given peak power/area budget constraint, multi-ISA heterogeneous architectures can outperform single-ISA heterogeneous architectures by an average of 21% and save 23% in energy at no loss in performance.

The design space exploration reveals two key insights. First, different applications exhibit a natural affinity for one ISA or another, and that affinity can change as the application progresses into a different execution phase. For example, in a homogeneous-ISA setting, Thumb is not a serious candidate, because it performs so poorly for certain codes; however, as part of a multi-ISA solution, it shines for certain code regions. As a result, ISA-heterogeneity consistently offers superior performance and energy savings, even in scenarios where hardware heterogeneity alone provides diminishing returns. Second, the ISA has a significant influence on microarchitectural design choices that enable efficient transistor investment on the available silicon real estate, calling for a tighter ISA-microarchitecture co-design. In fact, by observing the results of the design space exploration, we provide the CPU architect with a set of tools to enable ISA-microarchitecture co-design and thereby better streamline their search processes.

## 1.1.3 HIPStR: Security Defense via ISA Diversification

In addition to its potential for greater performance and energy efficiency, this dissertation demonstrates that ISA heterogeneity can be seamlessly leveraged to provide a strong security defense against buffer overflow exploits such as Return-Oriented Programming (ROP) [Sha07, RBSS12]. Buffer overflow vulnerabilities form a major class of security exposures that plague the Internet today. They rank third amongst the common vulnerability types reported by the National Vulnerability Database, finishing just behind cross site and cryptographic vulnerabilities [nvd].

These vulnerabilities have been systematically exploited by code reuse attacks such as ROP to perform arbitrary malicious computation without injecting malicious code. ROP attacks hinge on the attacker being able to chain together short code snippets in the program (called gadgets) that end with a return instruction, by overflowing the stack with a carefully constructed sequence of return addresses, and other malicious data. ROP has been shown to be Turing Complete for multiple ISAs (both RISC and CISC) and for a wide range of applications.

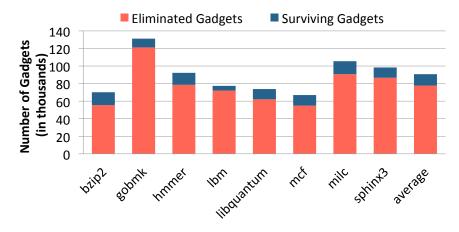

This dissertation introduces HIPStR (Heterogeneous-ISA Program State Relocation), a security defense that has the potential to radically transform the attack landscape of state-of-the-art Return-Oriented Programming. The primary motivation for HIPStR is the fact that ROP attacks thrive on two fundamental properties. First, the knowledge of the underlying ISA is critical to construct a successful exploit. Owing to its unique ability to perform seamless and instantaneous cross-ISA process migration, HIPStR significantly inhibits several code reuse attacks including the notorious JIT-based ROP attacks [SMD<sup>+</sup>13] by forcing the attacker to chain ROP gadgets across different ISAs. Second, any program including a ROP program requires some amount of program state (in the form of registers and stack objects) to perform computation. To this end, HIPStR employs dynamic binary translation to continuously randomize the register and stack state to an extent that brute force attacks [BBM<sup>+</sup>14] are rendered practically infeasible on current, or even distant future microprocessors. Overall, HIPStR offers a formidable defense against several variants of ROP attacks, and reduces their overall attack surface to such an extent that it is difficult to construct a four-gadget shellcode exploit, let alone achieve Turing-completeness.

### 1.1.4 Composite-ISA Architectures

Despite their potential for greater performance, energy efficiency, and security, the deployment of heterogeneous-ISAs on a single chip is non-trivial due to a number of practical concerns. First, integration of multiple vendor-specific commercial ISAs on a single chip is fraught with significant licensing, legal, and verification costs and barriers. Second, process migration in a heterogeneous-ISA CMP necessitates the creation of fat binaries, involves expensive binary translation and state transformation costs due to the difference in encoding schemes and application-binary interfaces (ABI) of fully disjoint ISAs.

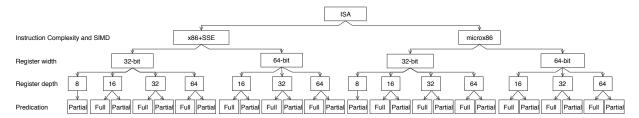

This dissertation significantly alleviates these concerns via yet another design space exploration to identify composite-ISA architectures that can recreate the effects of multi-ISA heterogeneity using a single composite-ISA. A composite-ISA is derived by leveraging a large superset ISA that resembles the Intel x86 and offers customization along five different axes of diversity: (1) register depth (8 to 32 programmable registers), (2) register width (32 vs 64-bit), (3) instruction complexity (1:1 vs 1:n micro-op encoding), (4) predication (full vs partial), and (5) specialized support (vector vs scalar). This provides the hardware designer and the compiler with far more control over the choice of ISA, with the ability to make fine-grained choices about the features of importance, maximizing the overall execution efficiency.

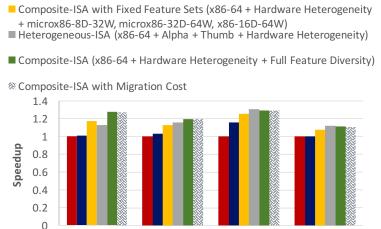

Due to the constraint of a single baseline superset ISA, we find that the derived custom ISAs can never incorporate all traits of distinct vendor-specific ISAs (such as the code compression of Thumb). However, the greater flexibility and composability of these designs offer substantial new ISA-affinity advantages. Composite-ISA heterogeneous architectures match and in many cases, supersede the efficiency gains of multi-ISA heterogeneous architectures, and further enhance existing gains due to hardware heterogeneity by an average of 19% in performance and 31% in energy savings. Furthermore, owing to the overlapping nature of the feature sets that make up the composite ISAs, the overall cost of migration drastically drops to just 0.42%. By combining the ISA-affinity advantages of multi-ISA heterogeneity and the simplicity of single-ISA heterogeneity, this research brings the best of both worlds.

## **1.2** Overview of Dissertation

Chapter 2 gives background information on heterogeneous architectures. It discusses single-ISA heterogeneous architectures in embedded, general-purpose, and server environments. It also briefly discusses some early work that evaluate the benefits, trade-offs, and complexities of multi-ISA heterogeneity and migration techniques for discrete heterogeneous-ISA machines. It further provides a primer on return-oriented programming and existing architectural and runtime support to mitigate code reuse attacks.

Chapter 3 lays out the proposed cross-ISA process migration strategy. In particular, it details our multi-ISA compilation methodology that leverages a powerful architecture-independent intermediate representation provided by LLVM [LA04a] to create a *symmetrical fat binary* that sports multiple ISA-specific text sections, but a single ISA-agnostic data section. It also discusses our runtime strategy that includes ISA-specific state transformation and binary translation for instantaneous cross-ISA process migration.

Chapter 4 outlines the design space navigation process geared at identifying an optimal heterogeneous-ISA multicore processor in terms of performance and/or energy efficiency under specific peak power and area budget constraints. It also discusses several inferences from the design space exploration that could potentially equip CPU architects with a set of tools for tighter ISA-microarchitecture co-design.

Chapter 5 proposes a security defense HIPStR (Heterogeneous-ISA Program State Relocation) that leverages ISA diversification and program state relocation to defend against several variants of the Return-Oriented Programming attack. It describes many binary code transformations for program state relocation in order to boost the entropy of the system, and details a security-aware migration policy that maximizes security with limited impact on performance.

Chapter 6 describes the design of a composite-ISA architecture that has the potential to recreate and in many cases, supersede the gains of multi-ISA heterogeneity, by implementing

composite feature sets derived using a single large superset ISA, exploiting greater flexibility in ISA choice. It presents our compiler and runtime strategy that extends the x86 backend to support and exploit the underlying composite ISAs, and enables seamless migration between the composite-ISAs. It also outlines our changes to the Intel x86 decoder both to support the decoding of the superset ISA, but also to be customized and reduced for the subset ISAs, and further studies the effect of these customizations on decoder area and peak power.

Chapter 7 summarizes the contributions of this dissertation.

## Chapter 2

# Background

This chapter provides background information related to this thesis. Section 2.1 gives a brief overview of modern heterogeneous architectures and their flavors. Section 2.2 discusses contemporary work on the benefits, trade-offs, and system design implications of ISA-heterogeneity. Section 2.3 provides the background on return-oriented programming (ROP) attacks and Section 2.4 discusses existing mitigations against ROP.

## 2.1 Heterogeneous Architectures

Prior research has shown that heterogeneous chip multiprocessors (CMPs) are capable of higher performance and energy efficiency as compared to homogeneous processors. Kumar, et al. [KFJ<sup>+</sup>03, KTR<sup>+</sup>04, KTJ06] introduced single-ISA heterogeneous multicore architectures. These architectures employ cores of different sizes, organizations, and capabilities, allowing an application to dynamically identify and migrate to the most efficient core, thereby maximizing both performance and energy efficiency. In addition, these architectures also employ cores from different process generations that may each operate at a different voltage/frequency domain and/or a different power state. Since its inception, several microarchitectural [LPD<sup>+</sup>12, PLDM15, LPD<sup>+</sup>16, LPD<sup>+</sup>14, SKKK16] and scheduling techniques [VCJE<sup>+</sup>12, VCE13, VCAH<sup>+</sup>13, ASC<sup>+</sup>16, NEE17, MNU<sup>+</sup>15, MNM<sup>+</sup>15, NAM<sup>+</sup>17, SWTB11, AEJE17, DK13] have been proposed in the literature to better harness the gains due to single-ISA heterogeneity.

Multiple commercial offerings in the embedded, GPU, and consumer markets have exploited this technology. ARM's big.LITTLE processor [Gre11] couples a high-performance out-of-order 3-way superscalar Cortex-A15 core with a low-power dual-issue inorder Cortex-A7 core. Many Qualcomm Snapdragon [Qua11] and Samsung Exynos [KKCL13] chipsets employ a variation of the big.LITTLE processor combining a high-performance Cortex-A57/Cortex-A73 with a low-power Cortex-A53 on the same chip to maximize energy efficiency. NVidia's Tegra-3 processor [teg11] employs a variable symmetric multiprocessing companion CPU core built using a low-power silicon process that operates at a lower frequency than the rest of the four cores on chip. Apple's A11 SoC [cut17] features a six-core CPU with two high-performance *Monsoon* cores and four energy-efficient *Mistral* cores.

Yet another class of heterogeneous chip multiprocessors make use of specialized hardware to accelerate the performance of a certain type of workloads. These include the integrated CPU-GPU architectures such as Intel's Sandy Bridge [san08] and AMD's fusion [fus08]. However, these architectures do not allow migration between core types at arbitrary places in the code. Current industry offerings of heterogeneous-ISA CMPs include MPSoCs in the embedded market [Tex], GPUs, and accelerators in the HPC market [teg10]. Though IBM's Cell microprocessor [KDH<sup>+</sup>05] is a heterogeneous-ISA CMP geared towards general-purpose computing, it suffers from two major concerns that make it unsuitable for general-purpose mixed workloads. First, the Synergistic Processing Elements (SPEs) use a special-purpose ISA that is suitable for only those workloads that exhibit SIMD parallelism. Second, lack of a common address space makes dynamic task migration infeasible.

Interestingly, modern datacenters already employ servers from different generations, and even different vendors, as a result of routine upgrades and competitive vendor markets [MT13,

Mor15, Mat16]. This shifting trend away from traditionally homogeneous hardware designs is further evidenced by the latest OpenPower venture of Google and Rackspace [Nic16, Mor15] that capitalizes on finer and cost-effective, albeit heterogeneous design options. While the proclivity to keep the task management runtime design relatively simple has traditionally favored the deployment of architecturally homogeneous commodity servers in datacenters [Höl10, DB13], the literature provides overarching evidence that intelligent QoS-aware management systems [WA12, MT13, DK14, PLD<sup>+</sup>15, LCG<sup>+</sup>14, LCG<sup>+</sup>15, HZL<sup>+</sup>15] that exploit microarchitectural heterogeneity can significantly improve energy efficiency while meeting the strict QoS requirements of latency-critical datacenter workloads. In fact, these strategies not only take advantage of the "unintentional" heterogeneity due to server upgrades, but call for a microarchitecturally heterogeneous datacenter by design due to its ability to cater to the diverse execution characteristics of the constantly evolving datacenter workloads in a cost-effective manner.

Several researchers have proposed design space exploration methodologies for heterogeneous architectures. Strozek, et al. [SB09] describe a process flow for automatic synthesis and evaluation of heterogeneous CMPs based on runtime profiles of certain embedded applications, given different area and power budgets. Intel's QuickIA [CSH<sup>+</sup>12] research prototype allows researchers to explore heterogeneous architectures consisting of multiple generations of Intel processors and FPGAs. Open source tools like Fabscalar [CWS<sup>+</sup>11, CWS<sup>+</sup>12], Open-Piton [BMF<sup>+</sup>16, MFN<sup>+</sup>17], and Alladin [SRWB14, SRWB15] further allow researchers to explore and analyze heterogeneous architectures of varying complexity. The search methodology we employ in this work is similar to the one described by Kumar, et al. [KTJ06]. However, our goal is to not only identify the optimal heterogeneous-ISA multicore designs, but also to lay out the first principles for ISA-microarchitecture co-design in such an architecture.

## 2.2 The Path to Multi-ISA Heterogeneity

A major contribution of this thesis is a detailed processor architecture design and compiler methodology for heterogeneous-ISA architectures [DVT12, VT14, VSST16, BSR<sup>+</sup>16]. These architectures allow cores that are already microarchitecturally heterogeneous to further implement diverse instruction sets. By exploiting ISA affinity, where different code regions within an application inherently prefer a particular ISA, they realize substantial performance and efficiency gains over hardware heterogeneity alone.

In contrast, Blem, et al. [BMS13b] claim that modern ISAs such as ARM and x86 have a rather similar impact in terms of performance and energy efficiency. However, that work compares rather similarly register pressure-constrained ISAs (ARM-32 and x86-32), keeps target-independent optimizations on and turns off machine-specific tuning, ignores feature set differences (e.g., Thumb), and makes homogeneous hardware assumptions, unlike the work on heterogeneous-ISA architectures [VT14, BSR<sup>+</sup>16, BLJ<sup>+</sup>17, NR16]. Akram and Sawalha [AS17, Akr17] perform extensive validation of the conflicting claims and conclude that the ISA does indeed have a significant impact on performance.

More contemporary studies in the literature show that ISA affinity is beneficial not just in general-purpose environments, but could potentially enable significant energy efficiency in datacenter environments [BLJ<sup>+</sup>17, NR16, ope16]. Lustig, et al. [LTPM15] describe mechanisms for cross-ISA memory consistency model translation. Wang, et al. [WYZ<sup>+</sup>17] enable offloading of binary code regions in a heterogeneous-ISA client/server environment. Furthermore, there is considerable amount of work that studies and addresses system implications of ISA-heterogeneity such as differences in page table structure and organization, system call ABI, and POSIX compatibility, via replicated OS kernel support for heterogeneous-ISA and overlapping-ISA architectures [BSA<sup>+</sup>15, BLJ<sup>+</sup>17, LBK<sup>+</sup>10].

The Tui system [SH98] describes a process migration strategy for heterogeneous-ISA

machines in the context of wide area computing. The main idea of that work is to transform the runtime program state to an intermediate form and then re-compile it to the required ISA, at the time of migration. Ferrari, et al. [FCG00] describe process introspection, a process state-capture and recovery mechanism initiated by a running process at periodic *poll points*, at which each subroutine in the call stack recursively captures and transforms its own state to suit the ISA the process is being migrated to. We borrow some techniques from both these works; however, our compiler methodology and runtime strategy is geared towards a more diverse set of ISAs in a chip multiprocessor environment, which makes the problem significantly harder and requires additional techniques and optimizations presented in this thesis.

More recently, multiple studies have advocated for an ISA-affinity driven live process/container migration in a heterogeneous-ISA datacenter environment [BLJ<sup>+</sup>17, NR16], that copies a minimal set of memory pages across the heterogeneous servers during migration and then proactively pushes the rest once execution is resumed. Such a mechanism not only considerably reduces system downtime, but accelerates the convergence to steady state by minimizing the number of remote page faults.

Finally, binary translators have long been used to port/emulate legacy binaries on heterogeneous ISAs [BSGG13]. Chen, et al. [CYH<sup>+</sup>08] describe techniques to translate ARM binaries for execution on a MIPS-like architecture. While the binary translation technique described in this thesis deals with similar challenges of ISA diversity, that work employs static translation while our work proposes dynamic translation, requiring different approaches in many cases. Managed runtimes and browsers employ dynamic binary translation to perform profile-guided optimization [HS04] of hot code regions, program sheperding, and JIT hardening [VKYP15]. Some examples of dynamic translators used for emulation include Digital's FX!32 [RH97] (which translates x86 applications to Alpha) and HP's Aries [ZT00] (which translates PA-RISC applications to IA-64). These translators use a two-phase translation, where the first phase does emulation and collects runtime profile information, and the second performs optimization. We cannot afford to have a two-phase translation, as binary translation in our case typically runs for far fewer instructions, rather than the entire program—the extra time for profiling and a two-phase translation process cannot be amortized. QEMU [Bel05] is the closest dynamic translator to the one described in our work. However, it is optimized for system emulation and our binary translator is optimized for the migration use case.

## 2.3 Return-Oriented Programming

Chapter 5 of this thesis demonstrates the security potential of heterogeneous-ISA architectures to defend against Return-Oriented Programming attacks. This section gives the necessary background information on Return-Oriented Programming (ROP).

Buffer overflow vulnerabilities have been systematically exploited by code injection attacks for many decades. These attacks, in their simplest form, inject malicious code into an application and hijack its control flow to result in rogue behavior. To prevent injection and subsequent execution of malicious code, most modern processors and operating systems have now employed Executable Space Protection [PT03b, VdV04] (dubbed as Data Execution Prevention by Windows) which ensures that a memory page is either writable or executable, but not both.

With the advent of Executable Space Protection, classical code injection has been slowly replaced by a more evasive form of attack, called Code Reuse. Typically, these attacks reuse existing code in the memory image of a process to perform malicious computation. An early example of such attacks is the *return-into-libc* attack [SD97], which exploits a buffer overflow on the stack to return into a C library function. Despite being able to subvert the control flow of an application without injecting malicious code, return-into-libc is inherently limited to the C library, and thus incapable of performing arbitrary malicious computation. In recent years, return-into-libc attacks have evolved into a more general and flexible scheme of attacks called Return-oriented Programming [RBSS12, Sha07].

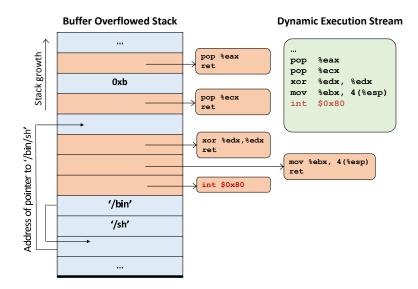

Figure 2.1: Return-oriented Programming

Return-oriented Programming (ROP) typically involves chaining together short code snippets in the program (called gadgets) that end with a return or an indirect jump instruction, by overflowing the stack with a carefully constructed sequence of return addresses, and other data required for malicious computation. Figure 2.1 shows a ROP attack that spawns a command shell. The attack begins with an attacker injecting an exploit payload on to the stack, exploiting a buffer overflow. The payload is crafted to overwrite the return address with the address of a short code snippet within the program, called a *gadget*, that ends in a return instruction. Once the gadget has executed and the instruction pointer has reached the return instruction, the stack pointer points to the address of the next gadget, and the exploit continues.

ROP hinges on the attacker being able to control the stack pointer and use it as the instruction pointer. Several evasive variants of ROP have been described in the literature that use indirect jumps in place of returns (Jump-oriented programming (JOP) [BJFL11, CDD<sup>+</sup>10, JTL14]), hijack control flow using chains of existing C++ virtual functions [STL<sup>+</sup>15, CCD<sup>+</sup>15], corrupt data variables to perform arbitrary malicious computation while staying on legitimate control-flow paths [CW14, CBP<sup>+</sup>15, HSA<sup>+</sup>16], and provide Turing-completeness on different instruction set architectures [BRSS08, Kor10]. Moreover, in JIT environments such as browsers

and the Adobe Flash, JIT-spraying techniques exploit the just-in-time compilation functionality to generate predictable chunks of exploit code in the text section, using carefully crafted JavaScripts or ActionScripts called GaJITS [RI11]. The advent of automated exploit compilers has further made ROP a formidable attack technique to defend against [SAB11].

## 2.4 **ROP** Mitigations

ROP thrives on three fundamental assumptions. First, the attacker should be able to subvert the control flow of the victim to a specific gadget, by exploiting an existing buffer overflow vulnerability. This necessitates the victim system to be void of any hardware or software control flow integrity enforcements. Second, the attacker should have prior knowledge of gadget locations in the process memory image, to overflow the stack with an appropriate sequence of return addresses. Third, the victim program must contain ample gadgets, enough to form, for example, a Turing-complete set. Not surprisingly, mitigation techniques often exploit these assumptions to defend against return-oriented programming.

Several control flow integrity (CFI) techniques have been proposed in the literature. Abadi, et al. [ABEL05] first formalized the idea of CFI. The main idea of that work is to constrain the execution of the program to a predefined control flow graph (CFG) by instrumenting the program to perform ID-checks before every indirect jump. Any jump to an invalid destination instruction (a jump target not defined in the may-point-to set) is flagged as a violation of control flow integrity. They also observe that it is difficult to implement ideal CFI statically without a runtime mechanism to track function calls and indirect jumps. There has been significant follow-up work on CFI at the hardware, runtime, and compiler levels [CPM<sup>+</sup>98, DSW11, VPMPADK13, CBD<sup>+</sup>99, OVB<sup>+</sup>06, SLZD04, Ven01].

More recent work such as CCFIR [ZWC<sup>+</sup>13], bin-CFI [ZS13], branch regulation [KOAGP12], code pointer integrity [KSP<sup>+</sup>14], and practical context-sensitive CFI [vdVAG<sup>+</sup>15] have made sig-

17

nificant strides in reducing the attack surface, by employing more fine-grained CFI, in the absence of any source or debug information, and at an acceptable degradation in performance. However, several backdoor attacks [EFG<sup>+</sup>15, CBP<sup>+</sup>15, GABP14, GAP<sup>+</sup>14, CW14, LDDLARS14, DLSM14, STL<sup>+</sup>15] have been described in the literature to bypass these techniques, thereby exposing the need for a stricter enforcement of CFI.

Numerous hardware and software techniques have been proposed to prevent *stack smashing*, i.e, overflowing the return address on the stack with a spurious jump target, to subvert control flow. StackGuard [CPM<sup>+</sup>98] is a compiler transformation that places a canary right after the return address on the stack. The validity of the canary is checked before returning control to the caller function, thereby detecting corruption of the return address before the exploit takes control. The major problem with StackGuard is that an adversary who can guess the canary value can overwrite the return address while preserving the integrity of the canary itself. Cowan, et al. [CBD<sup>+</sup>99] address this drawback using randomly generated and null-terminated canaries. While the attack remains probabilistic, the defense comes at an expense of about 6% more CPU time. Interestingly, GCC implements stack smashing protection as an optional transformation called ProPolice [Eto03]. Most software packages in standard Linux distributions, including Ubuntu, Fedora, and FreeBSD [FT09, Sun13, UT06] have been compiled with ProPolice.

StackShield [Ven01] is yet another compiler solution that uses two separate stacks – a data stack and a control stack. The control stack is exclusively used for maintaining return addresses, and the data stack is used to maintain fixed stack variables, register spills, and temporaries. While this technique reports little to no performance overhead, memory used for the control stack remains vulnerable. Inspired by StackShield, multiple hardware mechanisms [OVB<sup>+</sup>06, PZL06, XKPI02] have been proposed to exploit the hardware Return Address Stack (RAS) in order to secure the return address on the program stack. These solutions come with significant hardware complexity. First, they should detect a return address compromise with 100% accuracy in spite of speculative execution. Second, they should handle RAS overflow and underflow

scenarios with little performance impact. Finally, they should handle exceptional scenarios in the software such as *setjmp and longjmp*. ROPDefender [DSW11] attempts to address the above intricacies by emulating the secure return address stack using binary instrumentation. In similar spirit of detecting anomalies at the RAS level, Pappas, et al. [VPMPADK13] describe a detection technique that leverages the Last Branch Recording (LBR) feature of Intel processors to monitor and detect abnormal control transfer patterns.

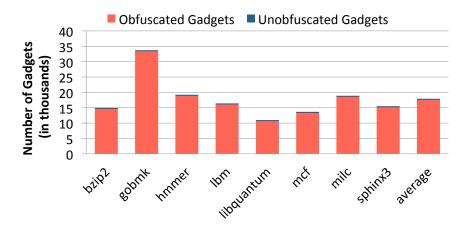

Yet another class of ROP defenses randomize the location of gadgets in the process image, making the attack only probabilistic. Several gadget location randomization techniques have been proposed in the literature, at various granularities — module (ASLR [PT03a]), basic block [WMHL12], instruction [HNTC<sup>+</sup>12], and byte [SKIH12] levels. Furthermore, several binary re-writing and gadget obfuscation mechanisms [KKP03, PPK12, BS08, CAC<sup>+</sup>08, OBL<sup>+</sup>10, PLPI13] have been proposed to restrict the number of useful gadgets in a program. These techniques can be applied orthogonally to gadget location randomization, in order to boost the entropy of a system. The performance overhead incurred by these techniques is typically proportional to the level of code obfuscation. The effectiveness of these solutions depends on the amount of entropy (number of randomizable states) they provide and the extent to which they can resist entropy exhausting attacks. In the presence of a memory disclosure vulnerability, these randomization techniques can be bypassed by simple brute-force attacks [SPP<sup>+</sup>04, BBM<sup>+</sup>14] that exploit a memory disclosure, in just a matter of a few thousand attempts.

The load-time nature of state-of-the-art randomization techniques makes them highly susceptible to just-in-time code reuse (JIT-ROP) attacks that exploit a single leaked memory disclosure to read code pages in memory, disassemble them, and reconstruct the control flow graph on-the-fly. Snow, et al. [SMD<sup>+</sup>13] show that JIT-ROP can bypass a combination of fine-grained randomization techniques in a matter of 23 seconds. Several periodic randomization and software diversification techniques [MBSN14, DLS<sup>+</sup>15, LHBF14, CHB<sup>+</sup>15, BHR<sup>+</sup>15, BDL<sup>+</sup>16, LLNB16, HHD16] have claimed immunity to these types of attacks at varying levels

of performance.

Several hardening techniques have been employed to counter JIT-spraying attacks in browsers and other JIT environments. These systems have to invariably bypass Executable Space Protection and use RWX pages in order to generate and execute code just-in-time. The cost of dynamically changing permissions (from WX to RX) for such pages is often extremely high, thereby leaving such systems vulnerable to code injection attacks. In fact, Internet Explorer is the only JIT-based system to implement secure page permissions. Some JIT environments such as the Chrome V8 engine employ a low cost solution called *guard pages* to prevent code injection. The guard pages separate heap pages from JIT pages in the application's address space. Any attempt to overwrite a guard page will be flagged as a security breach.

Both IE11 and Chrome V8 employ several fine-grained randomization techniques to secure JIT-pages. *Page Randomization* provides 16 bits of entropy by randomizing the location of JIT pages. *Constant Blinding* eliminates gaJITs by randomizing the values of constant literals used in JavaScripts and ActionScripts. *Random NOP Insertion*, a technique inspired by G-free [OBL<sup>+</sup>10], eliminates more gaJITs by randomly scattering NOPs across the code generated by the JIT compiler. Random NOP insertion is also employed by Adobe Flash. Finally, in order to suppress heap spraying attacks [Wev04], both IE11 and Chrome V8 enforce a cap on the number of heap pages that can be allocated. Interestingly, the Java Virtual Machine and Jaeger Monkey of Firefox do not employ any of the above mentioned randomization techniques, to avoid performance penalties.

20

# Chapter 3

# **Cross-ISA Process Migration**

Prior work on single-ISA heterogeneous multicore processors has demonstrated the criticality of process migration in reaping the full benefits of the underlying heterogeneity. First, process migration allows an application to adapt to phase changes by dynamically identifying and migrating execution to the core of its preference, maximizing performance and energy efficiency. Second, it helps to move processes to high-performance or low-power cores in the processor due to changes in the current operating condition and/or power state. Third, it allows migrating processes to cooler parts of the chip in the event of a thermal emergency. Fourth, process migration has traditionally enabled load balancing in environments ranging from general-purpose multicore processors to grid computing.

Cross-ISA process migration in particular is a well known difficult problem [FCG00, SH98, VBSS94]. This is because all runtime state of a program (data and code) is kept in an ISA-specific form, and migration to a different ISA could potentially involve expensive program state transformation. This chapter seeks to address these challenges and consequently establish the viability of a heterogeneous-ISA architecture. In particular, this chapter describes a multi-ISA compilation strategy and a low-overhead and programmer-transparent runtime mechanism that allow applications to seamlessly and instantaneously migrate across heterogeneous-ISA cores.

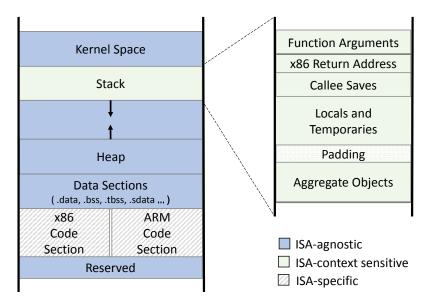

Figure 3.1: Symmetrical Fat Binary

#### **3.1** Symmetrical Fat Binary

The central piece of our cross-ISA process migration strategy is a *symmetrical fat binary* that contains multiple ISA-specific code sections, a common stack frame organization, and a common set of ISA-agnostic data and heap sections. Figure 3.1 illustrates a symmetrical fat binary that is capable of running on a heterogeneous-ISA CMP that implements both ARM and x86 cores. The symmetrical fat binary is created by a multi-ISA compiler that enforces the following set of consistency rules.

**Global Data Consistency.** In order to keep the data section ISA-agnostic, the multi-ISA compiler enforces common endianness, basic data type size, and alignment rules. This ensures all global data objects are consistently referenced at the same virtual address by both ISAs, and thereby avoids expensive pointer transformations at the time of migration.

**Code Section Consistency.** Although the fat binary contains multiple code sections, with minor changes to the page table, both code sections can be mapped such that they begin at the same address. This is possible because a core only loads its own code into its private instruction cache. Furthermore, to ensure function pointer consistency, the linker aligns functions in such a

way that they are seen at the same address in both ISAs.

**Heap Consistency.** Libraries that are responsible for dynamic memory allocation must ensure that a consistent view of the heap memory is maintained across both ISAs.

**Stack Consistency.** To avoid handling pointer inconsistencies on the stack, a common stack frame organization is enforced, as shown in Figure 3.1. In particular, the direction of stack growth, size, alignment, and organization of each stack frame must remain consistent across both ISAs. In doing so, we do not add any additional instructions, since we at most change the relative position of a stack object from the stack/frame pointer. However, each ISA is free to use the calling conventions and register allocation strategies that it finds most beneficial.

#### 3.2 Multi-ISA Compilation

Our compilation strategy is to start with a common intermediate representation, and then perform consistent backend compilation for multiple targets, to generate target-specific code for each ISA along with a common set of target-independent data sections. A by-product of the multi-ISA compilation is a set of transformation rules that are to be applied at the time of process migration, to convert the program state from one ISA-form to another. In the next few paragraphs, we describe our compilation strategy in greater detail.

**Common Intermediate Representation.** To enforce the above consistency rules, we rely on a well-defined architecture-independent intermediate representation that acts as a bridge between the different ISAs and provides hints to the runtime at the time of migration. In this work, we leverage the LLVM compiler framework [LA04b] and the Clang front-end [Lat08] to generate a common intermediate representation (LLVM bitcode), and perform target-specific backend compilation thereafter. To keep the front-end compilation ISA-agnostic, we make use of the *target-triple* functionality of Clang to specify the data types of a generic target, for all ISAs.

**Target-Independent Type Legalization.** To minimize the amount of program state to be transformed, we enforce common rules for promotion, truncation, expansion and type conversion. We allow certain exceptions during type legalization that interfere with ISA diversity - e.g., vector widening/scalarizing on x86-64, and long mode/floating point emulation on Thumb. For the most part, target-independent type legalization ensures a consistent view of global data and bitcode-level variables across all ISAs, during every stage of compilation. This is critical for generating a single version of target-independent global data sections.

**Intermediate Name Propagation.** Once the intermediate representation has been generated, we provide each bitcode-level variable with a unique name. During the subsequent code generation and optimization passes, we ensure that each target-level machine operand (both registers and fixed stack slots) is associated with its corresponding intermediate name, if any. This gives us the ability to distinguish between bitcode-level and target-level variables, which plays a key role at the time of program state transformation.

Hints for State Transformation. At the time of task migration, the runtime transforms the stack in such a way that the program appears to be executing on the migrated-to ISA from the time it was instantiated. To facilitate such a stack transformation, the multi-ISA compiler generates metadata that can be easily incorporated into a symbol-table-like data structure within the executable. The compiler will generate one such table for each ISA. The table itself holds records for each basic block or function call site in the executable, at which program state can be safely transformed, and native execution can be resumed on the migrated-to ISA. Each record of the table contains a mapping from a live register or a stack object, to its corresponding source/intermediate-level variable name.

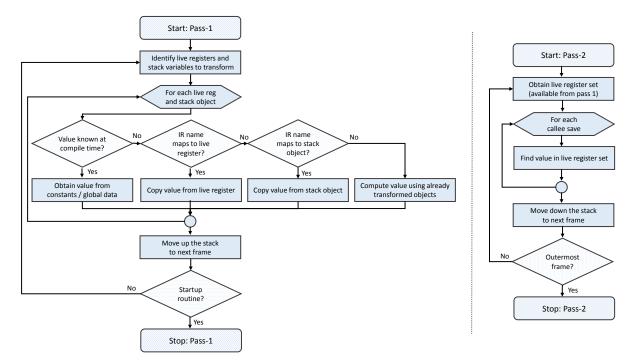

Figure 3.2: Operation of the State Transformer

# 3.3 State Transformation

To reap full benefits of ISA heterogeneity, it is critical that we dont turn off any targetspecific compiler optimization. However, due to a number of architecture-specific transformation passes such as code motion, not all points of execution in a symmetrical fat binary are migrationsafe. Therefore, the migration runtime either stalls migration or performs dynamic binary translation until execution reaches an *equivalence point* at which the program state can be safely transformed. The goal of the state transformer is to transform all inconsistent state on the stack (e.g., spilled registers, temporaries, etc) and create the final architectural register state on the migrated-to core. Figure 3.2 illustrates the working of the state transformer.