# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

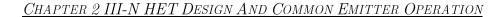

## Title

Design of III-Nitride Hot Electron Transistors

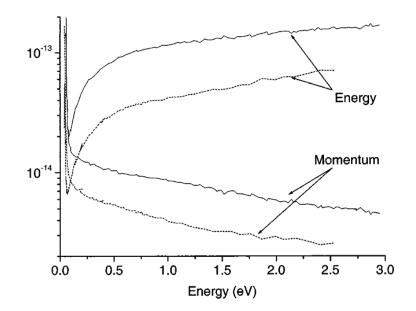

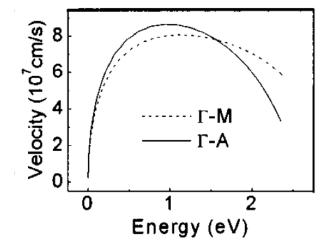

## Permalink

https://escholarship.org/uc/item/8nc0d155

**Author** Gupta, Geetak

Publication Date 2015

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA SANTA BARBARA

# Design of III-Nitride Hot Electron Transistors

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Geetak Gupta

Committee in charge: Professor Umesh K. Mishra, *Chair* Professor Mark J. W. Rodwell Professor Steven P. DenBaars Professor Debdeep Jena, Cornell University

December 2015

The Dissertation of

Geetak Gupta is approved:

Mark J. W. Rodwell

Steven P. DenBaars

Debdeep Jena

Umesh K. Mishra, Committee Chair

November 2015

# Design of III-Nitride Hot Electron Transistors

Copyright © 2015

by

Geetak Gupta

Dedicated to my parents Dr. Rajeev Gupta and Vibha Gupta

## ACKNOWLEDGEMENTS

My learning experience at UCSB would not have been possible without the help of a lot of people around me. Therefore, I acknowledge them for their contributions, not only to the work presented in this dissertation but also my individual growth.

First, I thank my advisor, Prof. Umesh Mishra, for giving me the opportunity to work in the amazing research environment provided by the UCSB in general and the Mishra Group in particular. Umesh has been a great teacher both actively and passively. When he first gave me the HET project, I did not even know that such a transistor existed. He has been a constant source of ideas, inspiration and support as I navigated through the extremes of experimental research.

I also express my gratitude to the members of my committee, Prof. Mark Rodwell, Prof. Steve DenBaars, and Prof. Debdeep Jena for their critical feedback and guidance. I did not have as many direct interactions with my committee members as I would have liked but the vast body of excellent research published by them over the years has taught me many valuable lessons. I thank Dr. Paul Maki (ONR) for providing us financial support for the HET project and the freedom to try out new ideas.

Being on the same project, Trey Suntrup was the only other person processing HETs along with me. As a result we shared many ideas and experiences. His unique perspective and attitude has played a fundamental role in developing my understanding of the HET and devices in general. The key to good device research is through great material growth. I have been fortunate in that aspect because of the awesome MOCVD and MBE growers in our group. I thank Matt Laurent for leading the MOCVD growth effort for the HET project. His willingness

to try out complete shots in the dark is what led to the development of the first working HETs. I would also like to thank Jing Lu and Haoran Li for growing MOCVD material which was instrumental in the initial development phase of the project. Elaheh Ahmadi provided the MBE material for the latter part of the HET development and grew the first HET with current gain. Her enthusiasm and hard work put new life into the HET project at a time when we were running out of ideas. The HET team (Elaheh, Matt, and Trey) has been a great group of people to work with, and I have learnt a lot being in their company.

I thank Edwin Acuna (my intern for ~ 1 year) for doing a lot of measurements for the HET project and being extremely thorough and efficient. I thank Shalini Lal for teaching me how to write papers and make presentations, and for always giving me sound advice. Sansaptak Dasgupta started the HET project and had to face some of its most difficult issues, but he got me excited about HETs and I thank him for that. I thank Steven Wienecke for all the memorable discussions on devices, anime, game of thrones, history etc. The entire Mishra Group (Dan, Nik, Ramya, Ajay, Jeong, Xun, Haoran, Cory, Matt Guidry, Karine, Maher, Silvia, Yuuki, Davide, Anchal, Brian, Chirag, and Onur) has provided a great research environment and a lively place to work. I have also had the good fortune of directly learning about processing and growth from Man Hoi Wong, Uttam Singisetti, Nidhi, Sansaptak, and Seshadri Kolluri in the early part of my studies. I thank past members of the Mishra group for leaving behind a huge wealth of knowledge which has enabled this work. I thank the staff at UCSB nanofab, especially Don, Adam, and Tony, for always keeping the RIE5, ICP1, Stepper1, Ebeam4, and the entire cleanroom in tip-top shape.

I am grateful to my friends from IITK for always encouraging me and being my family away from home. My roommates in SB over the years (Advait, Sagar, Nitin, Arvind (RIP), Gina, and Chirag) have been great to live with and made these years truly memorable. My family has been a constant source of motivation in all of my efforts. My sister and brother always keep my spirits up when I talk to them. My family living in the bay area (Fremont) have helped me adapt to living in the US. I also thank my parents (Rajeev and Vibha Gupta), my grand-parents (Ved Prakash and Magan Rani Gupta, Rajkumar and Shashi Gupta), and my entire family for maintaining a culture of learning and understanding in the family. Last but not the least, I thank my wife, Anchal Sharma, who has always supported me and has taught me many valuable life lessons. All of your efforts will guide me in my future endeavors.

Geetak Gupta

# CURRICULUM VITAE

# Geetak Gupta

## Research Interests

Solid-State Device Physics, High-frequency Amplifiers, Power electronics, Digital Electronics, Energy Efficiency, III-N Devices.

### Education

| 2015                                              | <b>Ph.D.</b> in Electrical and Computer Engineering GPA 4.0        |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------|--|--|--|

|                                                   | University of California Santa Barbara                             |  |  |  |

| 2013                                              | <b>M.S.</b> in Electrical and Computer Engineering GPA 4.0         |  |  |  |

|                                                   | University of California Santa Barbara                             |  |  |  |

| 2010                                              | <b>B.Tech.</b> in Electrical and Computer Engineering CPI 9.8/10.0 |  |  |  |

|                                                   | Indian Institute of Technology Kanpur                              |  |  |  |

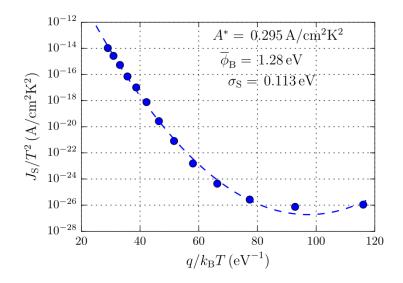

| Experience                                        |                                                                    |  |  |  |

| 2010-2015                                         | Graduate Student Researcher                                        |  |  |  |

|                                                   | University of California Santa Barbara                             |  |  |  |

| Winter-Spring                                     | Teaching Assistant, Semiconductor Device Physics                   |  |  |  |

|                                                   | University of California Santa Barbara                             |  |  |  |

| Summer 2009                                       | Undergraduate Researcher                                           |  |  |  |

|                                                   | University of California Santa Barbara                             |  |  |  |

| Honors                                            |                                                                    |  |  |  |

| 2010 Best B.Tech. Project, Electrical Engineering |                                                                    |  |  |  |

|                                                   | Indian Institute of Technology Kanpur                              |  |  |  |

| 2010                                              | Sridhar Memorial Prize (Best student, B.Tech. EE)                  |  |  |  |

|                                                   | Indian Institute of Technology Kanpur                              |  |  |  |

|                                                   |                                                                    |  |  |  |

| 2010              | <b>TODAI-IIT Scholarship</b> (Awarded to two final year students at IITK) |  |  |

|-------------------|---------------------------------------------------------------------------|--|--|

|                   | Indian Institute of Technology Kanpur                                     |  |  |

| 2006-07, 2007-08, | Academic Excellence Award                                                 |  |  |

| 2008-09           | Indian Institute of Technology Kanpur                                     |  |  |

| 2006              | All India rank 1 in National ISC Board Examinations                       |  |  |

|                   | St. Mary's Academy, Meerut                                                |  |  |

#### Journal Publications

- [1] **Geetak Gupta**, Elaheh Ahmadi, Umesh K. Mishra, "Establishment of the design space of III-N hot electron transistors for high current gain and extraction of mean free path using base thickness scaling," Submitted to EDL, 2015.

- [2] Matthew Laurent, Geetak Gupta, Donald J. Suntrup III, Umesh K. Mishra, "Barrier Height Inhomogeneity in Quarternary III-N Schottky diodes," Submitted to JAP, 2015.

- [3] Chirag Gupta, Yuuki Enatsu, **Geetak Gupta**, Umesh K. Mishra, "High breakdown voltage p-n diodes on GaN on sapphire by MOCVD," Submitted to PSS, 2015.

- [4] Donald J. Suntrup III, **Geetak Gupta**, Haoran Li, Stacia Keller, Umesh K. Mishra, "Barrier height fluctuations in InGaN polarization dipole diodes," *Applied Physics Letters*, 107, 173503, 2015.

- [5] Donald J. Suntrup III, Geetak Gupta, Haoran Li, and Umesh K. Mishra, "Measuring the signature of bias and temperature-dependent barrier heights in III-N materials using the hot electron transistor," *Semiconductor Science and Technology*, 30, 105003, 2015.

- [6] Riccardo Soligo, Srabanti Chowdhury, **Geetak Gupta**, Umesh K. Mishra, and Marco Saraniti, "The Role of the Base Stack on the AC Performance of GaN Hot Electron Transistor," *IEEE Electron Device Letters*, 36, 669-671, 2015.

- [7] Geetak Gupta, Elaheh Ahmadi, Karine Hestroffer, Edwin Acuna, and Umesh K. Mishra, "Common Emitter current gain >1 in III-N HETs with 7nm GaN/InGaN base," *IEEE Electron Device Letters*, 36, 439-441, 2015.

- [8] Geetak Gupta, Matthew Laurent, Haoran Li, Donald J. Suntrup III, Edwin Acuna, Stacia Keller, and Umesh K. Mishra, "Design Space of III-N Hot Electron Transistors using AlGaN and InGaN polarization-dipole barriers," *IEEE Electron Device Letters*, 36, 23-25, 2015.

- [9] Donald J. Suntrup III, **Geetak Gupta**, Haoran Li, and Umesh K. Mishra, "Measurement of the hot electron mean free path and the momentum relaxation rate in GaN," *Applied Physics Letters*, 105, 263506, 2014.

- [10] Matthew Laurent, Geetak Gupta, Steven Wienecke, Azim Muqtadir, Stacia Keller, Steven DenBaars, and Umesh K. Mishra, "Extraction of net interfacial polarization charge from Al<sub>0.54</sub>In<sub>0.12</sub>Ga<sub>0.34</sub>N/GaN high electron mobility transistors grown by metalorganic chemical vapor deposition," *Journal of Applied Physics*, 116, 183704, 2014.

- [11] **Geetak Gupta**, Matthew Laurent, Jing Lu, Stacia Keller, and Umesh K. Mishra "Design of polarization-dipole-induced isotype heterojunction diodes for use in III-N hot electron transistors," *Applied Physics Express*, 7, 014102, 2014.

- [12] Shalini Lal, Jing Lu, Geetak Gupta, Brian Thibeault, Steven P. Denbaars, and Umesh K. Mishra "Impact of Gate-Aperture Overlap on the Channel-Pinch-off in InGaAs/InGaN-based Bonded Aperture Vertical Electron Transistor (BAVET)," *IEEE Electron Device Letters*, 34, 1500, 2013.

- [13] Jing Lu, Dan Denninghoff, Ramya Yeluri, Shalini Lal, **Geetak Gupta**, Matthew Laurent, Stacia Keller, Steven P. DenBaars, and Umesh K. Mishra, "Very high channel conductivity in ultra-thin channel N-Polar GaN/(AlN, InAlN, AlGaN) high electron mobility hetero-junctions grown by metalorganic chemical vapor deposition," *Applied Physics Letters*, 102, 232104, 2013.

- [14] Sansaptak Dasgupta, Jing Lu, Nidhi, Ajay Raman, Christophe Hurni, Geetak Gupta, James S. Speck, and Umesh K. Mishra, "Estimation of Hot Electron Relaxation Time in GaN using Hot Electron Transistors," *Applied Physics Express*, 6, 034002, 2013.

- [15] Seshadri Kolluri, Stacia Keller, Dave Brown, Siddharth Rajan, Geetak Gupta, Umesh K. Mishra, "Influence of AlN interlayer on the anisotropic electron mobility and the device characteristics of N-polar AlGaN/GaN metal-insulator-semiconductor high electron mobility transistors grown on vicinal substrates," *Journal of Applied Physics*, 108, 074502, 2010.

#### <u>Conference Publications</u>

- [1] Geetak Gupta, Elaheh Ahmadi, Umesh K. Mishra, "Common Emitter Current Gain >1 in III-N Hot Electron Transistors by Enabling GaN/InGaN Base Scaling Using Novel Base Contact Methodology," *International Symposium on Compound Semiconductors*, Santa Barbara, June 2015.

- [2] Matthew Laurent, Donald J. Suntrup III, Geetak Gupta, Stacia Keller, Umesh K. Mishra, "Measurement of AlInGaN/GaN Schottky Diode Barrier Height by

Temperature-dependent Current-Voltage Measurements," *International Symposium* on Compound Semiconductors, Santa Barbara, June 2015.

- [3] Chirag Gupta, Enatsu Yuuki, **Geetak Gupta**, Stacia Keller, Umesh K. Mishra, "Ultra-Low N-Type Doping and High Breakdown Voltage (Field ~ 1.5MV/cm) in GaN P-N Diodes Grown on Sapphire by MOCVD," *International Symposium on Compound Semiconductors*, Santa Barbara, June 2015.

- [4] Donald J. Suntrup III, **Geetak Gupta**, Haoran Li, Stacia Keller, Umesh K. Mishra, "Measurement of the hot electron mean free path in GaN," *APS March Meeting*, San Antonio, Texas, 2015.

- [5] Matthew A. Laurent, Geetak Gupta, Azim Muqtadir, Stacia Keller, Umesh K. Mishra, "Extraction of Net Interfacial Polarization Charge from MOCVD-grown AlInGaN/GaN Heterostructures," *Electronic Materials Conference*, Santa Barbara, USA, June 2014.

- [6] **Geetak Gupta**, Matthew Laurent, Donald J.Suntrup III, Stacia Keller, Umesh K. Mishra, "Estimation of hot-electron mean free path in GaN using a III-N Hot Electron Transistor," *Electronic Materials Conference*, Santa Barbara, USA, June 2014.

- [7] Geetak Gupta, Matthew Laurent, Haoran Li, Donald J.Suntrup III, Edwin Acuna, Stacia Keller, Umesh K. Mishra, "Common Emitter operation of III-N HETs using AlGaN and InGaN polarization dipole induced barriers," *Device Research Conference*, Santa Barbara, USA, June 2014.

- [8] **Geetak Gupta**, Jing Lu, Stacia Keller, Umesh K. Mishra, "Reduction of reverse bias leakage using polarization induced barriers in III-N Isotype Heterojunctions for use in III-N Hot Electron Transistors," *International Workshop on Nitrides*, Sapporo, Japan, October 2012.

- [9] **Geetak Gupta**, Jing Lu, Shalini Lal, Stacia Keller, Umesh K. Mishra, "CF<sub>4</sub> Plasma Treatment for Leakage Reduction in N-Polar III-N Hot Electron Transistors with Collector-Up Structure," *International Symposium on Compound Semiconductors*, University of California Santa Barbara, CA, USA, August 2012.

- [10] Jing Lu, Dan Denninghoff, Matthew Laurent, Geetak Gupta, Stacia Keller, Steven P. Denbaars, Umesh K. Mishra, "Influence of a Thin InAlN Cap Layer on the Device Performance of N-Polar InAlN/GaN MISHEMTs Grown by MOCVD," *International Symposium on Compound Semiconductors*, University of California Santa Barbara, CA, USA, August 2012.

- [11] Geetak Gupta, Jing Lu, Ajay Raman, Sansaptak Dasgupta, Stacia Keller, Umesh K. Mishra, "DC Characteristics of N-Polar AlGaN/GaN/AlGaN Collector Up Hot Electron Transistors," *Electronic Materials Conference*, Pennsylvania State University, College Park, PA, USA, June 2012.

- [12] Seshadri Kolluri, Stacia Keller, Dave Brown, Siddharth Rajan, **Geetak Gupta**, Umesh K. Mishra, "Influence of AlN interlayer on the anisotropic electron mobility and the device characteristics of N-polar AlGaN/GaN MIS-HEMTs grown on vicinal

substrates," *International Symposium on Compound Semiconductors*, University of California Santa Barbara, CA, USA, August 2009.

## Invited Talks

- [1] Geetak Gupta, Matthew Laurent, Donald J. Suntrup III, Haoran Li, Stacia Keller, Umesh K. Mishra, "Design and Fabrication of III–N Hot Electron Transistors," *Nitrides Seminar*, University of California Santa Barbara, February, 2014.

- [2] Geetak Gupta, Jing Lu, Sansaptak Dasgupta, Matthew Laurent, Stacia Keller, Umesh K. Mishra, "III–N Hot Electron Transistors," *Teledyne Scientific and Imaging*, Thousand Oaks, CA, USA, April 2013.

- [3] Umesh K. Mishra, Dan Denninghoff, Jing Lu, **Geetak Gupta**, "Recent Advances in High Frequency Semiconductor Devices," *Lester Eastman Conference*, Brown University, Providence, RI, USA, August 2012.

# ABSTRACT

## Design of III-Nitride Hot Electron Transistors

#### Geetak Gupta

III-Nitride based devices have made great progress over the past few decades in electronics and photonics applications. As the technology and theoretical understanding of the III-N system matures, the limitations on further development are based on very basic electronic properties of the material, one of which is electron scattering (or ballistic electron effects). This thesis explores the design space of III-N based ballistic electron transistors using novel design, growth and process techniques. The hot electron transistor (HET) is a unipolar vertical device that operates on the principle of injecting electrons over a high-energy barrier ( $\phi_{BE}$ ) called the emitter into an n-doped region called base and finally collecting the high energy electrons (hotelectrons) over another barrier ( $\phi_{BC}$ ) called the collector barrier. The injected electrons traverse the base in a quasi-ballistic manner. Electrons that get scattered in the base contribute to base current. High gain in the HET is thus achieved by enabling ballistic transport of electrons in the base. In addition, low leakage across the collector barrier (I<sub>BCleak</sub>) and low base resistance (R<sub>B</sub>) are needed to achieve high performance. Because of device attributes such as vertical structure, ballistic transport and low-resistance n-type base, the HET has the potential of operating at very high frequencies. Electrical measurements of a HET structure can be used to understand high-energy electron physics and extract information like mean free path in semiconductors.

The III-Nitride material system is particularly suited for HETs as it offers a wide range of  $\Delta E_c s$  and polarization charges which can be engineered to obtain barriers which can inject hot-electrons and have low leakage at room temperature. In addition, polarization charges in the III-N system can be engineered to obtain a high-density and high-mobility 2DEG in the base, which can be used to reduce base resistance and allow vertical scaling.

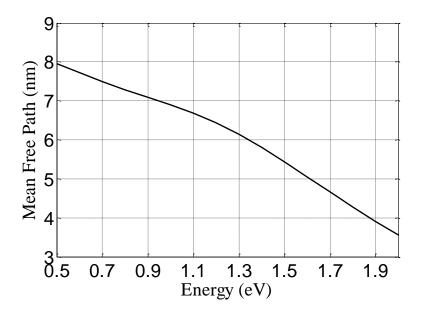

With these considerations in mind, III-N HETs had been explored in our research group earlier and gave us encouraging common base IV characteristics. Common emitter transistor operation was, however, not observed due to high R<sub>B</sub> and I<sub>BCleak</sub>. This thesis discusses several design and process challenges associated with the HET in general and specific to the III-N system. Many of these challenges like R<sub>B</sub>, I<sub>BCleak</sub>, and high energy injection were solved using novel combinations of hetero-structure and polarization engineering, device fabrication, and growth. Common-Emitter operation (with current gain  $\sim 0.1$ ) was demonstrated in III-N HETs for the first time using injection and collector barriers induced by AlGaN and InGaN polarization-dipoles. In order to improve current gain, different parts of the III-N HET base which contribute to scattering, were identified. A novel base contact methodology using selective etching of GaN with respect to AlN was developed to enable base scaling. Aggressive scaling of all parts of the base was then used to increase current gain. A maximum gain of ~3.5 was demonstrated using a 1.5nm AlN layer as the emitter, 2nm GaN base and 2nm In<sub>0.2</sub>Ga<sub>0.8</sub>N as the collector P-D. This is the highest reported DC current gain in III-N HETs to date. The III-N HET structure was also used to extract the mean free path of hot-electrons ( $\lambda_{mfp} = 6nm$ ) in GaN. The extracted value of mean free path has significant implications for any scaled devices which use ballistic or quasi-ballistic electron transport. We believe that the work presented in this dissertation provides a pathway for high gain in III-N HETs and eventual realization of their high frequency potential.

# TABLE OF CONTENTS

| ACKN | IOWLED                         | GEN   | 1ENTS                               | V    |

|------|--------------------------------|-------|-------------------------------------|------|

| CURR |                                |       | ΆΕ                                  | VIII |

| ABST | RACT                           |       |                                     | XIII |

| TABL | E OF CO                        | NTE   | NTS                                 | XVI  |

| 1    | INTRO                          | DDU   | CTION                               | 1    |

|      | 1.1                            | Ho    | T ELECTRON TRANSISTOR OPERATION     | 4    |

|      | 1.1                            |       | Design Principles                   |      |

|      | 1.2                            | Hıs   | TORICAL PERSPECTIVE ON HETS         |      |

|      | 1.2                            | .1    | Tunnel Injection                    |      |

|      | 1.2                            | .2    | Resonant Tunnel Injection           |      |

|      | 1.2                            | .3    | Thermionic Injection                | 20   |

|      | 1.3                            | Mo    | DTIVATION FOR III-N HETS            |      |

|      | 1.3                            | .1    | High-Frequency Amplifier            |      |

|      | 1.3                            | .2    | Probe for Material Properties       |      |

|      | 1.4                            | Syn   | NOPSIS OF DISSERTATION              |      |

| 2    | III-N F                        | IET C | DESIGN AND COMMON EMITTER OPERATION |      |

|      | 2.1                            | AL    | GAN BASED DESIGN                    |      |

|      | 2.1                            | .1    | Growth and Fabrication              |      |

|      | 2.1                            | .2    | Diode and Transistor Results        |      |

|      | 2.1                            | .3    | Issues                              |      |

|      | 2.2                            | ALC   | GaN and InGaN P-D Design            |      |

|      | 2.2                            | .1    | Growth and Fabrication              |      |

|      | 2.2                            | .2    | Diode and Transistor Results        |      |

|      | 2.3                            | Co    | MMON EMITTER OPERATION              |      |

|      | 2.3                            | .1    | Turn-On                             | 51   |

|      | 2.3                            | .2    | Active                              |      |

|      | 2.3                            | .3    | Breakdown                           |      |

|      | 2.4                            | Sur   | MMARY                               |      |

| 3    | BASE                           | тніс  | KNESS SCALING FOR CURRENT GAIN      | 61   |

|      | 3.1 GAN SCALING WITH ALGAN P-D |       |                                     |      |

|      | 3.1                            | .1    | Device Performance                  | 63   |

|      | 3.2                            | GA    | N Scaling with AlN P-D              | 65   |

|      | 3.2                            | .1    | Fabrication                         | 67   |

|   | 3.2<br>3.2        |                                         | Structure and Growth<br>Device Performance |     |  |  |

|---|-------------------|-----------------------------------------|--------------------------------------------|-----|--|--|

|   | 3.3               | -                                       | aN Thickness Scaling                       |     |  |  |

|   | 3.3<br><i>3.3</i> |                                         | Structure and Growth                       |     |  |  |

|   | 3.3<br>3.3        |                                         | Device Performance                         |     |  |  |

|   | 3.4               |                                         | 1MARY                                      |     |  |  |

| 4 |                   |                                         | RON TRANSPORT IN III-NITRIDES              |     |  |  |

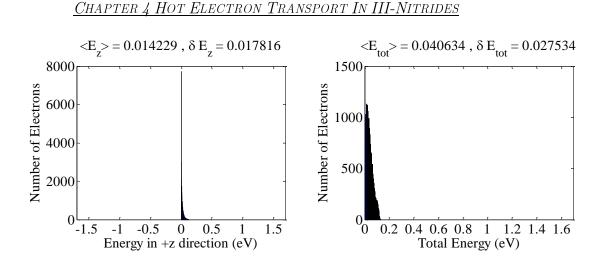

|   | 4.1               | QUA                                     | ALITATIVE DESCRIPTION OF HOT ELECTRONS     | 80  |  |  |

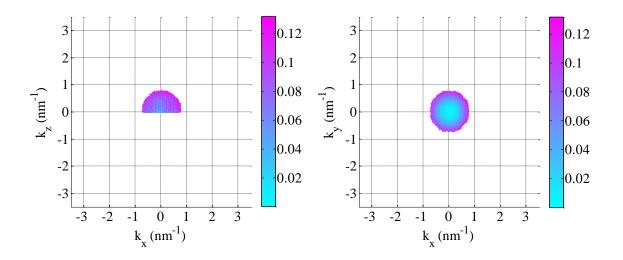

|   | 4.1               | .1                                      | Monte Carlo simulations                    | 80  |  |  |

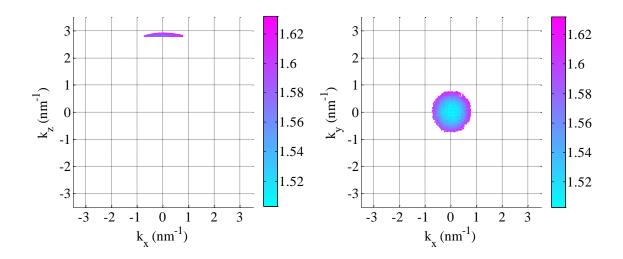

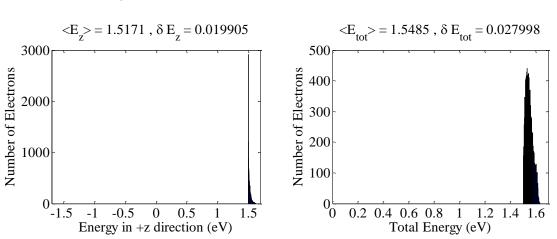

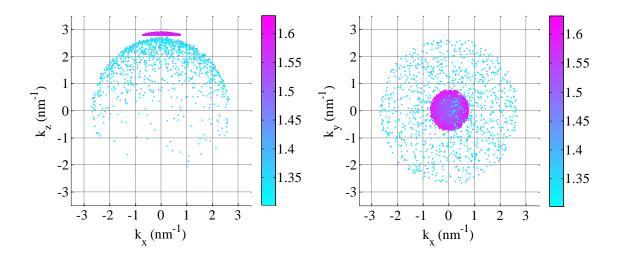

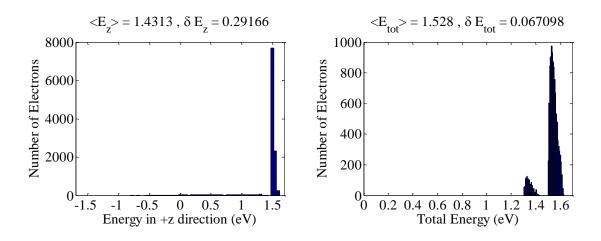

|   | 4.1               | .2                                      | k-space maps of Hot-Electrons              | 82  |  |  |

|   | 4.2               | Sca                                     | TTERING AND MEAN FREE PATH                 |     |  |  |

|   | 4.2               | .1                                      | Definition and Mechanisms                  | 89  |  |  |

|   | 4.2               | .2                                      | $\lambda_{MFP}$ in GaN using HETs          | 93  |  |  |

|   | 4.3               | Нот                                     | ELECTRON INJECTION AND COLLECTION          | 99  |  |  |

|   | 4.3               | .1                                      | Injection                                  |     |  |  |

|   | 4.3               | .2                                      | Collection                                 | 103 |  |  |

|   | 4.4               | Sum                                     | 1MARY                                      | 105 |  |  |

| 5 | HIGH              | HIGH COMPOSITION INGAN QUANTUM WELL HET |                                            |     |  |  |

|   | 5.1               | ING                                     | AN QW HET DESIGN                           | 107 |  |  |

|   | 5.2               | Con                                     | IDUCTIVITY OF 2DEG AT ALN/INGAN INTERFACE  | 107 |  |  |

|   | 5.2               |                                         | Structure, Growth, and Results             | 107 |  |  |

|   | 5.2               | .2                                      | AIN/InGaN HEMTs                            | 111 |  |  |

|   | 5.3               | Sun                                     | 1MARY                                      | 113 |  |  |

| 6 | CONC              | CONCLUSION AND FUTURE WORK 114          |                                            |     |  |  |

|   | 6.1               | Con                                     | ICLUSION                                   | 114 |  |  |

|   | 6.2               | FUT                                     | URE WORK                                   | 115 |  |  |

|   | 6.2               | .1                                      | Base Resistance                            | 115 |  |  |

|   | 6.2               | .2                                      | Breakdown Voltage                          |     |  |  |

|   | 6.2               | .3                                      | RF Operation                               | 123 |  |  |

| 7 | REFEF             | RENCE                                   | Ξδ                                         | 127 |  |  |

| 8 | APPENDIX A        |                                         |                                            |     |  |  |

| 9 | APPEI             | NDIX                                    | В                                          | 142 |  |  |

# **1 INTRODUCTION**

There has been a huge progress in the field of III-Nitride based technologies in the past few decades. This material system has been researched since the 1970s[1], but difficulties in developing a viable growth technique limited the progress. It first attracted widespread attention with the demonstration of the InGaN-based blue light-emitting diode (LED) and laser in the mid-1990s[2], [3]. Since then, tremendous progress has been made towards both understanding of nitride material properties[4], [5] and growth[6], [7] as well as fabrication of electronic[8] and photonic devices with excellent performance.

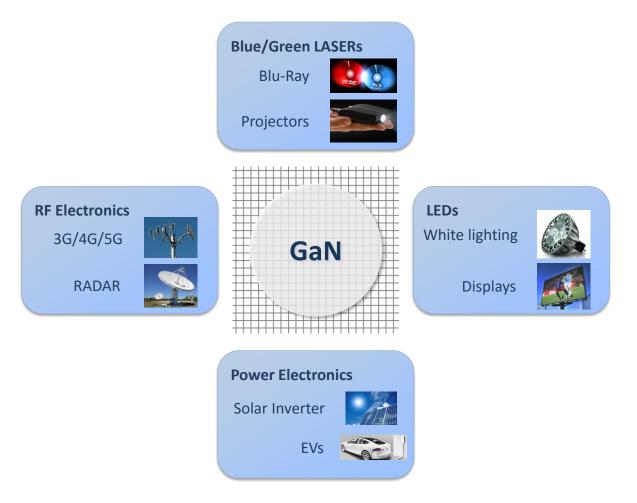

Nitride semiconductors have a very unique set of properties making them attractive for various applications. Broadly, the major applications of III-N based technologies can be classified into four categories namely, blue/green LASERs, LEDs, power electronics, and RF electronics (Figure 1.1). The large direct bandgap (0.7eV to 6.2eV) that can be covered with the Al-In-Ga-N alloy system allows the use of these semiconductors in further advancing the LED and laser technology from UV[9] to infrared frequencies. In recent years, there has been demonstration of green lasers operating at 535 nm[10] using InGaN quantum wells. Nitride-based solar cells[11] have recently demonstrated excellent external quantum efficiency and spectral response. Besides favorable optoelectronic properties, the III-Nitrides also possess excellent electronic transport properties. Due to the presence of high spontaneous and piezoelectric polarization in the III-Nitride system, high charge density 2DEG with ~1-2x10<sup>13</sup> cm<sup>2</sup> charge and ~2000 cm<sup>2</sup>/V.s mobility have been demonstrated[12].

Figure 1.1 Applications of III-Nitride material system based technologies

The presence of polarization also enables some unique design possibilities. Excellent high frequency performance of InAlN/GaN based Ga-Polar HEMTs with maximum  $f_T \sim 450$  GHz and maximum  $f_{MAX} \sim 550$  GHz[13] have been obtained recently. Power densities of 32W/mm at 4GHz (55% PAE)[14] and 10W/mm at 40GHz (34% PAE)[15] have been demonstrated in Ga-Polar HEMTs. N-Polar III-N HEMTs offer the unique advantage of a built in back barrier and the ability to scale channel thickness both of which can improve gate control and provide significant advantages for scaling. AlGaN/GaN based N-Polar HEMTs have shown  $f_T.L_G$  product of 16.8 GHz.µm ( $L_G = 40$ nm)[16] and InAlN/GaN based N-Polar HEMTs have

recently shown  $f_T \sim 200$  GHz and  $f_{MAX} \sim 400$  GHz[17]. Power density of 12W/mm at 4GHz (55% PAE)[18] have also been shown in N-Polar HEMTs. In the area of power electronics, III-Nitride based devices, due to their capabilities of supporting high breakdown voltage and low on resistance,  $R_{on}$ , have already emerged as an efficient and important technology for various applications[19].

Despite the remarkable progress in III-Nitride based device technologies, the pathway to obtaining ultra-high frequency ( $f_T > 500$  GHz) transistors based on the InAlGaN/GaN HEMT technology is unclear. The low electron saturation velocity in the 2DEG combined with parasitic delays[20], [21] could limit the possibility of obtaining an ultra-high frequency III-N HEMT with considerable breakdown voltage and hence high output power. Bipolar devices (HBT) in the III-N system have shown high gain and high breakdown voltages, but have limited high-frequency performance benefits. The major issue in the III-N HBT is the presence of a p-type layer which has very low conductivity due to the deep acceptor nature of Mg in GaN[22]. This has prevented widespread use of bipolar devices in the III-Nitrides.

Towards this goal, we explore III-Nitride based Hot Electron Transistors. The Hot Electron Transistor (HET) is a vertical unipolar device operating in a regime where high electron velocities via quasi-ballistic transport are attainable. Even though scattering rates are high in the III-Nitrides, current gain is achievable in the HET as discussed in Chapter 3-5. With appropriate scaling technologies and reduction of parasitic delays the III-N HET could be used as an ultra-high frequency device as discussed later in this chapter and in Chapter 6.

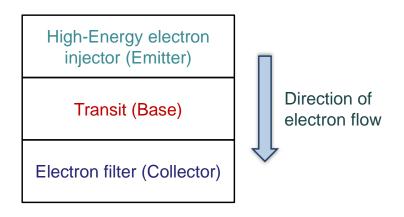

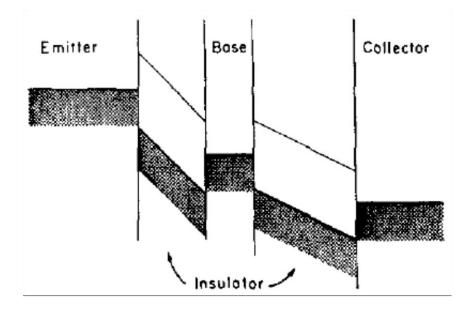

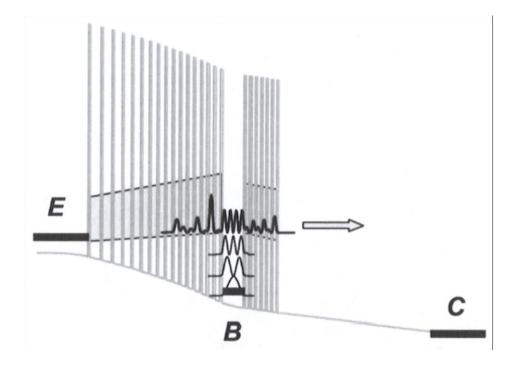

Figure 1.2 General Description of a HET

The complex non-equilibrium electron transport in the device and its dependence on several scattering mechanisms also makes the HET an extremely interesting scientific tool to understand fundamental electron transport in the III-Nitrides. This chapter discusses the basic operation principles of a HET, the family of HET designs, key advantages provided by the III-N system for HETs, and a discussion on the potential uses of a III-N HET.

# **1.1** Hot Electron Transistor Operation

The most general description of a HET consists of three distinct regions (Figure 1.2), a highenergy electron injector (emitter), a transit region (base), and an electron energy filter (collector). The emitter, in non-equilibrium, injects electrons into the base (hot electrons) such that they have a high energy compared to the thermal energy when they enter the base. The base has a thermal population of electrons (cold electrons) either due to bulk doping or some other means (modulation doping, polarization doping etc.). The thermal population of electrons in the base effectively screens the collector from the emitter. As the injected hot electrons traverse the base, they suffer from scattering which can be elastic or inelastic and finally they

reach the collector. The collector acts as an energy filter for electrons at the collector edge of the base. It allows hot electrons to go across but blocks cold electrons for a wide range of non-equilibrium across it. Electrons which have suffered from scattering in the base therefore are not hot enough to cross the collector and get reflected back. These electrons eventually become part of the cold electron population in the base and contribute to base current. The electrons at the collector edge of the base which have sufficient energy, make it across the collector and form the collector current. The next few pages briefly discuss phenomenon related to each part of the transistor to develop a general understanding of a HET. This will enable discussions on advantages/disadvantages of various HET designs in different material systems until a more detailed description is developed in later chapters (Chapter 5 in particular).

#### Hot Electron Injection

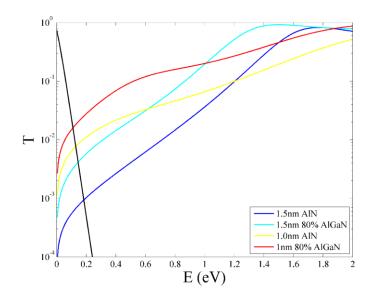

The hot electron injector is typically made using an energy barrier e.g. tunnel barrier, resonant tunnel barrier, superlattice etc. The simplest emitter is a unipolar diode with a heterojunction, schottky or electrostatic barrier at the emitter-base interface. This ensures that electrons entering the base have energy greater than or equal to the barrier height. As the emitter-base junction is forward biased, electrons are injected into the base by thermionic emission over this barrier. The general approach to calculating currents in a quantum mechanical model is by using,

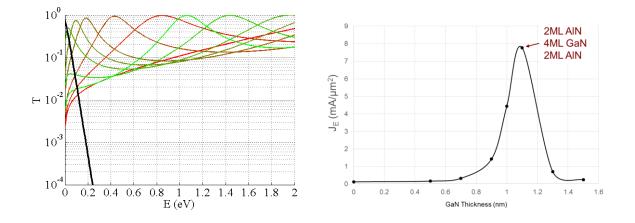

$$J_{z} = \frac{2q}{(2\pi)^{3}} \iiint \frac{1}{\hbar} \frac{\partial E(k)}{\partial k_{z}} T_{A-B}(E(k,z),k) f_{A}(E(k)) \left(1 - f_{B}(E(k))\right) dk_{x} dk_{y} dk_{z}$$

where  $J_z$  is the electron current flowing from region A  $\rightarrow$  B and  $f_A$  and  $f_B$  are the Fermi-levels in the two regions. In order to evaluate this expression, the first thing needed is the tunneling probability of electrons across the emitter barrier. Since these structures are uniform along the x and y dimensions, the electron momentum is conserved along x and y as electrons transit across the emitter-base interface. The transmission probability therefore depends only on the electron  $k_z$  and the E(k,z)<sup>1</sup>. E(z) is basically the band diagram of the system. Near conductionband minima, E(k) is a simple parabolic relationship. With these three idealizations, it is possible to write a computer code for calculating transmission probability across arbitrary structures<sup>2</sup>. Even with the transmission probability, a complicated integral has to be performed to calculate  $J_z$ . With a few more approximations i.e. parabolic bands on both sides,  $(1-f_B) \sim 1$ , and the Boltzmann approximation, the contributions of the  $k_x$  and  $k_y$  components to  $J_z$  can be integrated independently. All that is left is the  $k_z$  integral which can be performed numerically. Results of such calculations for actual HET structures will be presented later. To summarize, since  $k_x$  and  $k_y$  are conserved, hot electron injection only produces shifts in the  $\langle k_z \rangle^3$  of the electron distribution. Consider the case of a simple step-down potential with a thermal distribution of electrons on the higher-potential side (left side). To the left of the step,  $\langle k_x \rangle =$  $\langle k_{v} \rangle = \langle k_{z} \rangle = 0$  and  $\langle \Delta k \rangle \sim kT$ . As electrons cross the barrier,  $\langle k_{x} \rangle = \langle k_{v} \rangle = 0$ , but  $\langle k_{z} \rangle \sim kT$ .

$<sup>^{1}</sup>$  E(k,z) is a description of the electron potential energy as a function of momentum and position.

<sup>&</sup>lt;sup>2</sup> Code for calculation of transmission probability and current density across arbitrary band diagrams written by Trey Suntrup.

$<sup>^{3}</sup>$  <k> is the ensemble average momentum of the electron distribution.

$\sqrt{2m\phi_{EB}/\hbar^2}$ , where  $\phi_{EB}$  is the height of the step. Thus, in a HET, hot-electrons entering the base have a large k<sub>z</sub> compared to k<sub>x</sub> and k<sub>y</sub>.

## Hot Electron Collection

The collector in a HET can also be made using an electron energy filter like tunnel barrier, resonant tunnel barrier, superlattice etc. The simplest collector is again a unipolar diode with a heterojunction, schottky or electrostatic barrier at the base-collector interface. Just like the emitter barrier, the collector barrier too acts as a  $k_z$  filter. Only electrons with a high enough  $k_z$  have high transmission probabilities across the collector. The collector also has a drift region with an electric field that sweeps away collected electrons towards the collector contact layer.

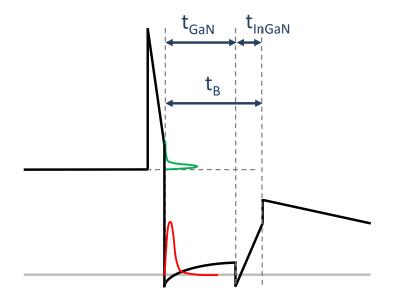

## Base Transit

The base is a transit region where a fraction of the injected hot-electrons suffer from scattering events due to various interaction mechanisms. The fraction that suffers from scattering events is determined by the length of the base, the average scattering rate of electrons in the base, and the electron velocity. The scattering mechanisms can be elastic (ionized impurities, alloy etc.) or inelastic (inter and intra-valley acoustic and optical phonons etc.). Elastic scattering mechanisms result in momentum relaxation but not energy relaxation whereas inelastic scattering events can result in both. Since both emitter and collector barriers are  $k_z$  filters, the HET is sensitive to energy as well as momentum relaxation. As hot-electrons enter the base, they have a high  $\langle k_z \rangle$ . During base transit, therefore, the hot-electron  $\langle k_z \rangle$  decreases due to scattering events. A fraction of the injected electrons thus gets reflected at the collector. It can

be assumed that these reflected electrons eventually fully relax in energy and momentum to become part of the thermal electron population in the base. The hot-electron scattering process is discussed in more detail in Chapter 4.

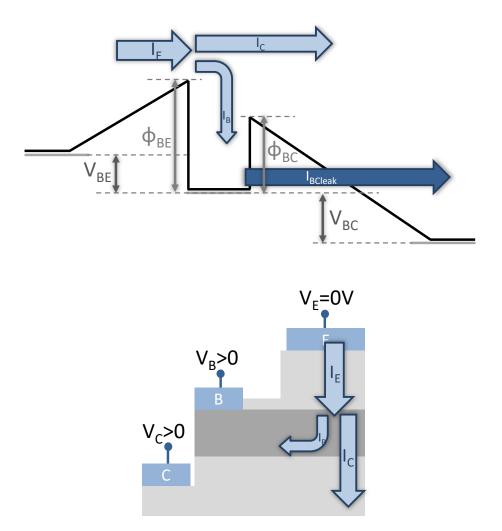

Figure 1.3 (a) Schematic conduction band-diagram and (b) Layer structure illustrating the various electron current paths in a HET under normal bias conditions

## Non-Equilibrium Fermi Levels and Transistor Action

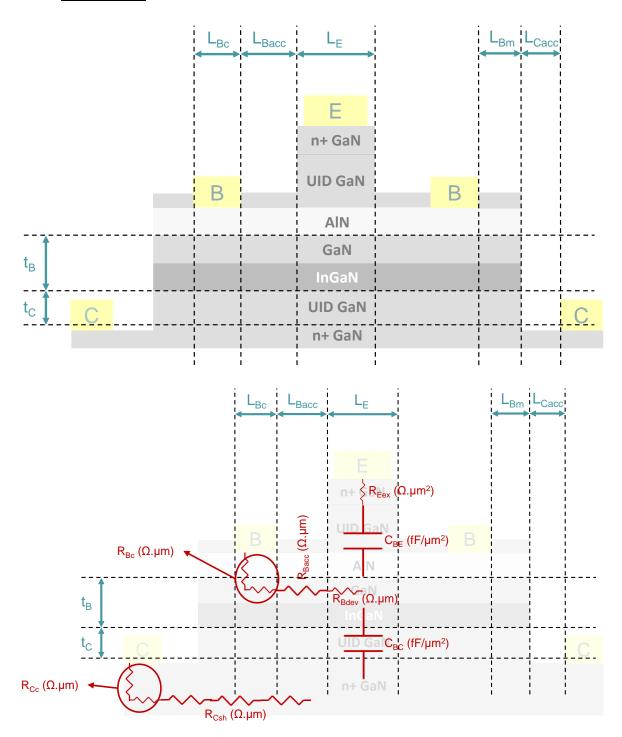

The HET has three Fermi-levels, emitter, base and collector which are controlled via external sources of voltage or current. This means that in each of these three regions, the density of electrons is high enough for there to be a well-defined Fermi-level. The only reason, thus, for having a large thermal population of electrons in the base is to provide a constant Fermi-level across the entire base. If the electron density/mobility is low, the Fermi-level will change along the direction of current flow and result in resistive voltage drops which degrade device performance. The device structure used for a HET is a double-mesa structure (Figure 1.3) which means that  $J_E$  and  $J_C$  flow vertically while  $J_B$  flows laterally. Thus, the base resistance ( $R_B$ ) is a sum of contact resistance and lateral sheet resistance. The emitter resistance however is a vertical resistance.

Transistor action in a HET is achieved by fixing the emitter Fermi-level to ground ( $V_E = 0V$ ), applying a small positive bias on the base ( $V_B > 0$ ) and a larger positive bias on the collector ( $V_C > V_B$ ). The positive bias on the base results in a net flow of electrons from the emitter towards the base. The electron distribution changes as electrons traverse the base and the final distribution is partially relaxed in energy and momentum. A fraction of the final electron distribution is thus unable to make it across the collector barrier and gets reflected back. This forms the base current ( $J_B$ ) of the device. The fraction of the electron distribution with a large enough  $k_z$  that makes it across the collector barrier, forms the collector current ( $J_C$ ). As  $V_B$  is increased, the forward bias across the emitter-base junction ( $V_{BE}$ ) increases, thus resulting in more current injection (higher  $J_E$ ). The  $J_C$  and  $J_B$  increase proportionally resulting

in the first primary property of a transistor called *transconductance*. To a first order,  $J_C$  and  $J_B$  do not change as  $V_C$  is increased, thus resulting in the second primary property of a transistor called *saturation*. With these two properties, it is possible to call the device a *transistor*. In reality, as  $V_C$  is increased,  $J_C$  increases thus resulting in output conductance ( $R_{out}$ ). In addition, the leakage of thermal electrons from the base across the collector ( $J_{BCleak}$ ) increases with  $V_C$ . The  $V_C$  at which the  $J_{BCleak}$  becomes comparable to  $J_C$  is termed as the breakdown voltage ( $V_{Cbr}$ ). Therefore, for the HET to be a *useful transistor*, a few more conditions need to be imposed.

## 1.1.1 Design Principles

## DC Performance

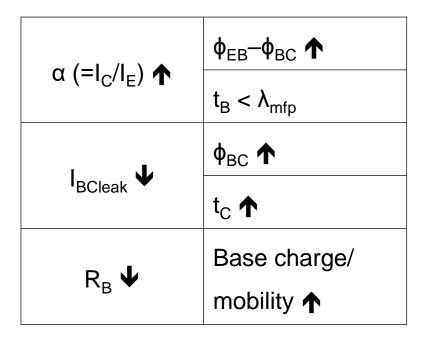

In order to design a HET that is useful at DC, a few more parameters are defined here. Transfer ratio ( $\alpha$ ) is defined as  $\alpha = J_C/J_E$  and current gain ( $\beta$ ) is defined as  $\beta = J_C/J_B$ . For good DC performance,  $\alpha \sim 1$  and  $\beta$  as large as possible are needed. This ensures that most of the injected electrons are collected and the device gain is high. A large V<sub>Cbr</sub> (or low J<sub>BCleak</sub>) is needed for a large saturation regime and low R<sub>B</sub> is required for uniform biasing of the entire device area.

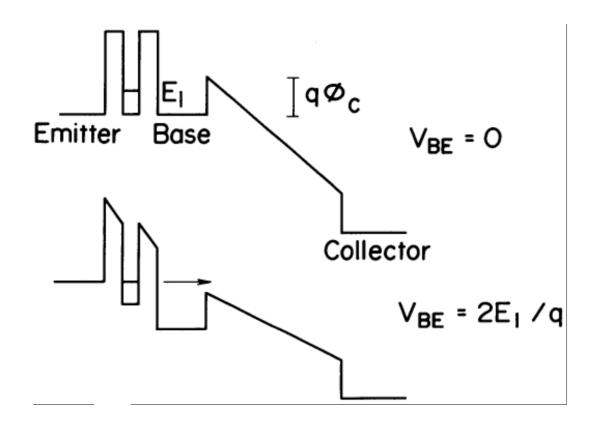

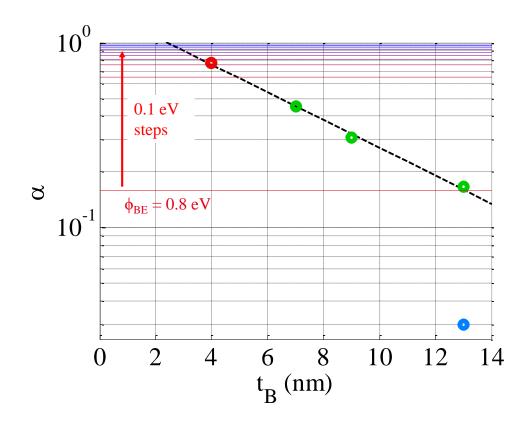

Using these additional DC metrics, the design space for HETs can be further narrowed down. A thin base  $t_B < L_{mfp}$  (scattering mean free path for hot-electrons) is needed to ensure ballistic transport of hot-electrons and thus, maximum  $\alpha$ . Quantum mechanical reflection of hot-electrons at the collector barrier can occur even if the electron energy is larger than the

Figure 1.4 Design tradeoffs in a HET for DC performance

collector barrier height. A large difference between emitter and collector barrier heights ( $\phi_{EB}$ - $\phi_{BC}$ ) is therefore required to reduce the effect of such reflections. A large collector barrier height ( $\phi_{BC}$ ) and thickness (t<sub>C</sub>) are needed to block leakage currents across the collector and thus reduce J<sub>BCleak</sub>. In order to reduce R<sub>B</sub>, high electron concentration and mobility are required in the base. From the summary in Figure 1.4, it is clear that there are a few tradeoffs inherent to even the most general HET. A large  $\phi_{BC}$  decreases J<sub>BCleak</sub> but also decreases  $\alpha$  and  $\beta$  since the injection energy ( $\phi_{EB}$ ) has to be larger than  $\phi_{BC}$  for high gain. A thin base increases  $\alpha$  and  $\beta$  but can also result in higher R<sub>B</sub>.

## AC Performance

|                         | Transit 🗸                  | $t_{b} \Psi$ , $t_{c} \Psi$ |

|-------------------------|----------------------------|-----------------------------|

| f <sub>⊤</sub> <b>↑</b> | C <sub>cb</sub> ↓          | t <sub>c</sub> ↑            |

|                         | Charging $oldsymbol{\Psi}$ | I <sub>c</sub> ♠            |

|                         | R <sub>B</sub> ↓           |                             |

| f <sub>max</sub> ♠      | C <sub>cb</sub> ↓          | t <sub>c</sub> ↑            |

Figure 1.5 Tradeoffs in a HET for high-frequency performance

This part discusses the general tradeoffs inherent to the HET for RF performance. The highfrequency figures of merit for a transistor are the current gain cutoff frequency  $f_T$  and the power gain cutoff frequency  $f_{MAX}$ . Both of these are defined in terms of parameters of the small signal equivalent circuit which is very similar to that of an HBT.

$$\frac{1}{2\pi f_T} = \tau_B + \tau_C + \frac{\partial V_{BE}}{\partial J_C} (C_{je} + C_{cb}) + C_{cb} (R_{ex} + R_C)$$

$$f_{MAX} = \sqrt{\frac{f_T}{2\pi R_{bb} C_{cb}}}$$

The  $f_T$  is divided into two parts, transit delays and RC delays. The first term is the base transit delay and its value is  $\tau_B = t_B/v_B$ , where  $t_B$  is the base thickness and  $v_B$  is the ballistic velocity of electrons in the base. To a first order, the ballistic velocity can be approximated by just the

#### <u>Chapter 1 Introduction</u>

group velocity of electrons at the injection energy. The second term is the collector transit delay and its value is  $\tau_{\rm C} = t_{\rm C}/2v_{\rm s}$ , where  $t_{\rm C}$  is the collector thickness and  $v_{\rm s}$  is the saturated electron velocity in the collector drift region. The third term contains the capacitances of each junction and the dynamic resistance of the device. The final term is an RC delay related to the base-collector capacitance. In order to increase  $f_{\rm T}$ , thus,  $v_{\rm B}$  and  $v_{\rm s}$  need to be large. The capacitances are inversely proportional to the thickness of the barriers. Therefore, the barrier thicknesses need to be large for low capacitances. The device needs to be operating at high current densities for low dynamic resistance. Finally, the parasitic resistances need to be small. To increase  $f_{\rm MAX}$ , low base resistance and low  $C_{\rm cb}$  are needed. As summarized in Figure 1.5, this introduces additional tradeoffs in the device design.  $t_{\rm C}$  is one of the most critical parameters as it plays a role in determining J<sub>BCleak</sub>,  $\tau_{\rm C}$ , and  $C_{\rm cb}$ .

## **1.2** Historical Perspective on HETs

A brief introduction to the Hot Electron Transistor family is presented below. Since most textbooks and review articles do not have an adequate description of these devices, this section serves as a brief introduction to the several transistor topologies which can be termed as Hot Electron Transistors keeping in mind the description in the earlier section. The base transit and collection mechanism is very similar for most of the HET topologies made in the past. This classification is therefore based on the different injection mechanisms used for HETs.

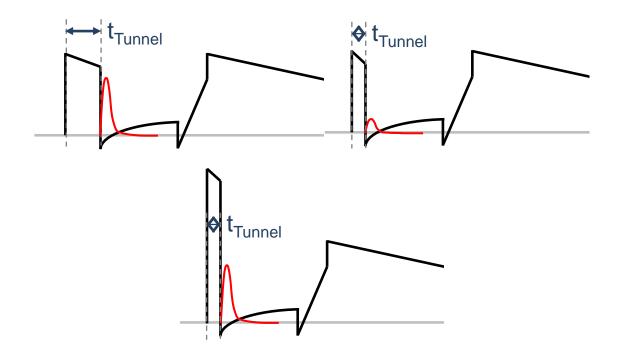

## 1.2.1 Tunnel Injection

The emitter-base current in this class of HETs is a tunneling current through a barrier, either by direct tunneling or Fowler-Nordheim tunneling. Historically, the first proposal of a hot electron device was made by Mead[23] in 1961. His proposed device, the MOMOM (metaloxide-metal-oxide-metal) transistor, was based on electrons tunneling through a thin oxide into a high energy state in the metal base (Figure 1.6).

Figure 1.6 The MOMOM (metal-oxide-metal-oxide-metal) HET[23]

These high-energy electrons were then able to surmount the second oxide barrier and get collected in the metal electrode. The oxides used here were  $Al_2O_3$  and  $Ta_2O_5$ . The MOMOM was a potentially fast device for two main reason; it employed a thin base region which resulted in low transit times for the injected electrons and the metal base layer enabled low  $R_B$ . Since the mean free path of hot electrons in metals is short, and pinhole-free thin metal layers were difficult to fabricate, current gain was not demonstrated in these transistors. The low injection

and collection efficiency due to traps resulted in the discontinuation of further research in these devices.

The hot electron camel transistor was proposed by Shannon in 1979[24]. The injection mechanism here was based on tunneling of electrons across a metal-semiconductor junction. The entire structure was made from Si. The simplest structure used a Schottky metal on top of an n+ base layer as the injector. Another structure had a thin p+ layer between the metal

Figure 1.7 The Hot-Electron Camel Transistor[25]

and the n+ base in order to increase injection energy (Figure 1.7)[25]. The collector for both cases was a 'camel' diode which was an n-p-n unipolar diode. The collector barrier height was determined primarily by the doping and thickness of the p-type layer. A maximum current gain of 10 was demonstrated in these devices. However, a large output conductance was observed in the transistors and the large current gain was obtained only at large collector bias.

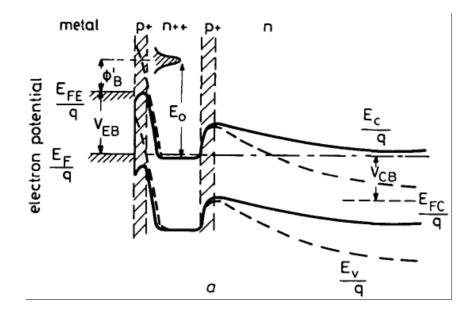

The THETA (tunneling hot electron transistor amplifier) was proposed by Heiblum in 1981[26]. The device structure employed a thin layer of  $Al_{0.35}Ga_{0.65}As$  as a tunnel emitter. An n-type GaAs layer with an ohmic metal contact on top was used as the source of electrons as opposed to a schottky metal contact in the previous designs. The base collector heterojunction was graded to reduce quantum mechanical reflection, and an  $Al_{0.25}Ga_{0.75}As$  layer was used as the collector (Figure 1.8). A maximum current gain of 50 was demonstrated in these devices. The THETA was also used as a spectrometer to measure the energy spectrum of the injected

Figure 1.8 Tunneling Hot Electron Transistor Amplifier (THETA)[26]

hot electrons[27]. The low  $\Gamma$ -L valley separation in the III-As material system however limited the possibility of high injection energies. Also, as the barrier heights achievable in

AlGaAs/GaAs heterojunctions are small, the THETA was typically operated at 77K or lower thereby severely limiting its use in practical applications.

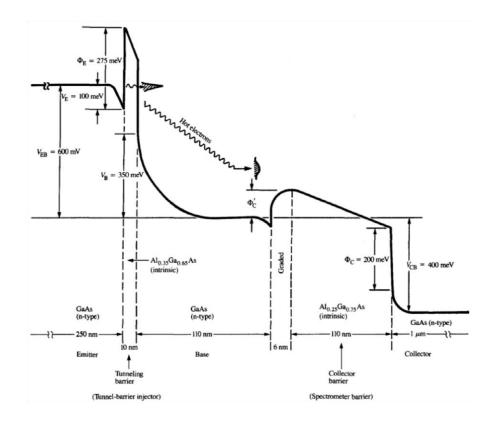

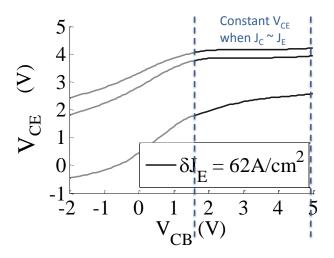

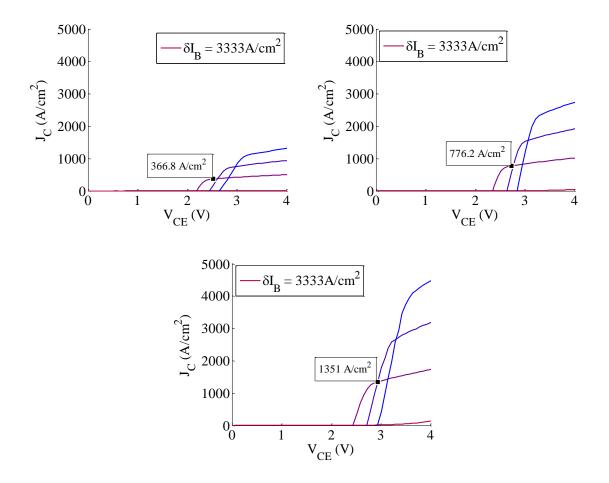

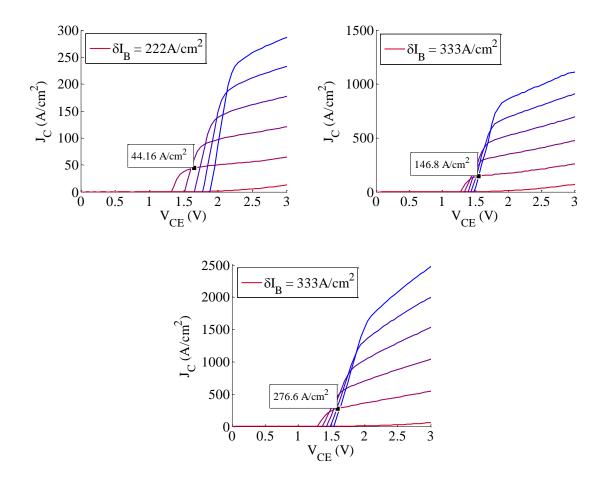

Recently, III-N HETs using tunnel injection have also been demonstrated (Figure 1.9)[28]. These transistors operate at room temperature and have demonstrated differential current gain ( $\delta I_C / \delta I_B > 1$ ). However, the differential gain was observed only at very high collector bias and for a very small range of base current. The DC gain was < 1 and the devices suffered from very high output conductance. At present, III-N HET research is still in its early

Figure 1.9 III-N Tunneling HET[28]

stages and the fundamental material properties of III-Nitrides allow for plenty of room for improvement. This work will expand upon the design methodology for III-N HETs and show

that room temperature DC gain with low output conductance and reasonable breakdown can indeed be achieved.

# 1.2.2 Resonant Tunnel Injection

This class of HETs use a resonant tunneling diode structure to inject electrons into the base at a specific energy. As an extension, some designs also use a superlattice diode structure to inject electrons into the base at a specific energy.

Figure 1.10 Resonant Tunnel HET[29]

The first Resonant Tunnel HET was demonstrated by Yokoyama in 1985 using an Al<sub>0.33</sub>Ga<sub>0.67</sub>As/GaAs/Al<sub>0.33</sub>Ga<sub>0.67</sub>As resonant tunnel diode as the hot electron injector[29]. The base was just n-type doped GaAs and the collector was again Al<sub>0.2</sub>Ga<sub>0.8</sub>As (Figure 1.10). The

emitter diode here exhibited a negative differential resistance which is expected in a Resonant Tunnel diode structure. This transistor had a current gain of 5. Using InGaAs/InAlAs RT structures, the current gain was increased to > 10[30]. High frequency performance with  $f_T =$ 121GHz was also demonstrated[31]. These transistors were however operated at 77K or lower thus limiting their use in practical applications.

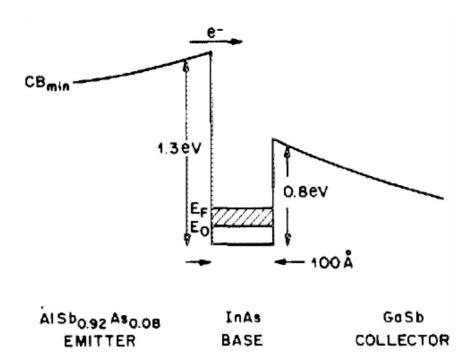

Figure 1.11 Superlattice HET[32]

Superlattice injectors were introduced very recently by Daoud in 2008[32]. This transistor used an InAs/AlSb superlattice as the hot electron injector and collector (Figure 1.11). A maximum current gain of ~5 was demonstrated at room temperature. High frequency performance with  $f_T = 75$ GHz and  $f_{MAX} = 88$ GHz was also shown[33]. The breakdown voltage of these devices, however, was only ~1V due to the small barrier heights achievable in this material/design.

### 1.2.3 Thermionic Injection

This class of HETs use thermionic injection similar to a schottky diode in order to inject hot electrons into the base. The electrons entering the base thus have an energy greater than the barrier height.

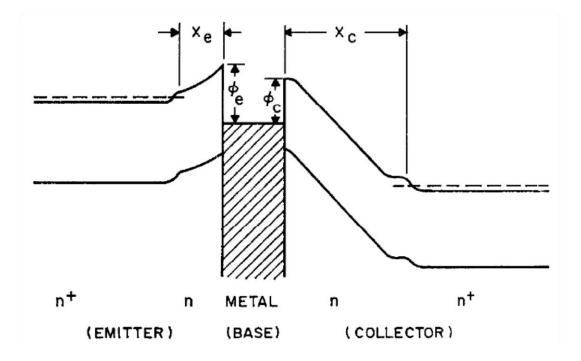

Figure 1.12 Semiconductor-Metal-Semiconductor (SMS) HET[34]

Metal base transistors which employ thermionic rather than tunneling injection of hot carriers into the base, were proposed by Geppert[35], Atalla[36] and Sze[34] in 1962 in the form of a semiconductor-metal-semiconductor (SMS) structure (Figure 1.12). The current gain was higher in these structures as compared to the MOMOM structures, but was still smaller than 0.5. This was related to various transport factors including the quantum mechanical reflection of electrons across the base-collector barrier.

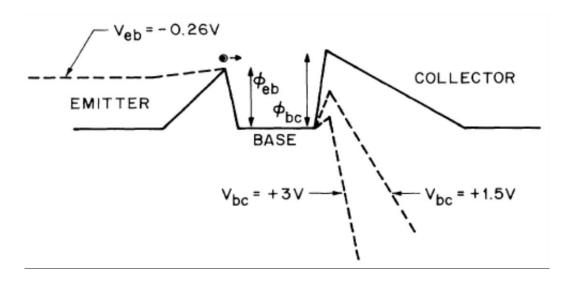

Figure 1.13 Planar doped barrier HET[37]

Unipolar diodes made using n-p-n structures (planar doped barriers) have also been used to implement emitter and collector barriers to construct a HET. Shannon demonstrated this transistor using Si in 1981[25] with a current gain of  $\sim 20$  at RT. The transistor however had very high output conductance. Hayes demonstrated it using GaAs in 1985[37] and performed hot electron spectroscopy measurements using the HET structure (Figure 1.13). These measurements were performed at 4.2K.

In 1987, Levi demonstrated room temperature operation of a thermionic HET using an AlSb/InAs heterostructure for hot-electron injection[38] (Figure 1.14). The high base-collector barrier due to the InAs/GaSb heterojunction of 0.8 eV facilitated room temperature operation of this HET by reducing the  $J_{BCleak}$ . Gain of ~ 10 was demonstrated at room temperature thus making this structure the highest performance HET of all. However, HETs still lagged behind vertical bipolar devices like the InP/InGaAs HBT in terms of current

Figure 1.14 InAs/IIISb HET[38]

density, output conductance, and high frequency performance thus leading to a decline in research interest in HETs.

# **1.3** Motivation for III-N HETs

A discussion on the potential applications of HETs is incomplete without a serious discussion on HBTs as the two devices are very similar in many aspects. The HBT is a device capable of high drive currents and high gain. The vertical structure enables it to have great scalability. In contrast to the HET, HBTs in material systems like III-As, III-P, Si/Ge have shown excellent DC performance with very high gain and low base resistance. They have also shown excellent performance for applications in high frequency circuits beyond 100GHz[39], [40] and the  $f_{MAX}$ of InP HBTs has crossed 1THz[41].

HBTs in the III-N system, however, have had very limited success. The key contributing factor to this has been the lack of high conductivity in p-type layers in the III-N material system. The p-type dopant of choice in the III-N system is Mg which has a very high activation energy (~200meV) resulting in ~ 1% ionization[42]. Thus, it is very difficult to obtain layers with low sheet resistance. Although some solutions like polarization doping have been proposed, their full potential is yet to be realized. GaN being wide bandgap also makes it very difficult to find metals with a large enough work function to make a low barrier p-type contact. Thus, the high frequency performance of III-N HBTs is severely limited at present.

III-N HEMTs, on the other hand, have shown excellent performance for high-frequency and high-power circuits in the millimeter wave regime.  $f_{MAX}$  of ~500GHz has been demonstrated in III-N HEMTs. This success can be attributed to the presence of high density/mobility 2DEGs and large  $\Delta E_c s$  available in the III-N system. HEMTs in the III-As/III-P material systems have also shown excellent high frequency performance with maximum  $f_T$ > 600GHz[43] and  $f_{MAX}$  >1THz[44].

HETs have been used extensively as scientific tools to investigate materials properties of several material systems. However, HET technologies in all previously explored material systems have not been able to compete with existing HBT and HEMT technologies for high frequency applications. The HET topologies discussed earlier have a few limitations. III-As based HETs typically suffer from high leakage currents at room temperature due to small barrier heights. The same issue exists for metal-semiconductor HETs based on GaAs or Si. Metal-oxide based HETs suffer from high trap densities at interfaces. The best performing HET in the past has been the AlSb/InAs/GaSb structure[38] with a gain of 10 at room

temperature. However, the devices demonstrated had relatively large output conductance and low current density. The structure also did not have much room for vertically scaling the base to increase gain without heavily sacrificing base resistance. In conclusion, at the time, HBTs provided a much better method of achieving high gain, low base resistance, low output conductance, and high current density simultaneously.

A III-N based HET offers the unique opportunity to achieve high gain and breakdown at room temperature along with vertical scalability and high-frequency performance unachievable in previous HET designs. Being a unipolar device, the HET can potentially have much lower base resistance compared to a bipolar III-N device. Ballistic operation can enable electron velocities much higher than vertical bipolar or lateral HEMTs. The presence of polarization in the III-N system also provides some key advantages. Polarization induced 2DEG in the base with high mobility (~1500 cm<sup>2</sup>/Vs), and high density (~2x10<sup>13</sup> cm<sup>-2</sup>) can be used to achieve very low base resistance[45]. Polarization dipoles can also be used to induce barriers in the system without too much build-up of strain[46], [47]. The III-N system also has high  $\Delta E_{cs}$ , making it a suitable material system for the HET.

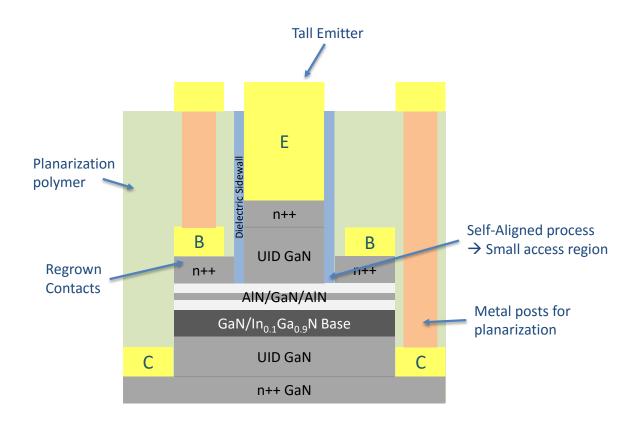

### 1.3.1 High-Frequency Amplifier

The RF metrics for a III-N HET are very similar to the III-As/III-P HBT. It has been shown in HBTs that the key requirements to achieve THz operation are,

• Ultra-low Contact Resistances: Contact resistivities of the order of  $10\Omega\mu m^2$  are required for all contacts. Low contact resistances of similar order of magnitude have

been shown to the III-Nitrides by using high n-type doping[48] and low band-gap InGaN[49].

- Low Base Resistance: Self-aligned process for low access resistance and a base sheet resistance of the order of 1 kΩ/sq. is typically required. Base resistance is more important for f<sub>MAX</sub> and can be reduced by lateral scaling. Low sheet resistances have been shown in 2DEGs in III-N HEMTs[45]. However, in a HET, low base 2DEG resistance is required irrespective of emitter bias. This aspect is discussed in more detail later.

- High Current Density: J<sub>C</sub> ~ 1 MA/cm<sup>2</sup> (or 10 mA/μm<sup>2</sup>) is required for low dynamic resistance. Owing to high density of states in the III-N system, theoretically, these numbers are achievable. The specific design used to achieve HETs in the III-N system, however, can introduce some complications as discussed in later chapters.

- High Collector Velocity: Collector transit delay forms a major portion of the total device delay (affects f<sub>T</sub>) and hence a high collector velocity is required. Here, III-N HETs are at a slight disadvantage compared to III-As/III-P HBTs as the saturated drift velocity in III-N system is lower. This is a material constraint and will eventually determine the high-frequency potential of the device.

The key ingredients for high-frequency performance in HETs are present in the III-N system. Full band Monte-Carlo simulations for III-N HETs predict  $f_T > 100$ GHz for current densities of ~ 100kA/cm<sup>2</sup>[50]. However, at this point it is difficult to make any strong claims regarding the ultimate high-frequency potential of HETs. As discussed later in this thesis, the specific device designs will play a key role in determining whether the high-frequency potential can be

realized practically. A more detailed discussion on the high-frequency tradeoffs for III-N HETs is presented in Appendix B.

### **1.3.2** Probe for Material Properties

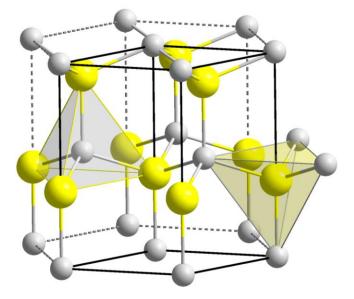

Figure 1.15 Wurtzite crystal structure of GaN and related alloys

III-Nitrides have a wurtzite type crystal structure which lacks inversion symmetry thus, giving rise to some of the most interesting properties of this material system. The electronic band structure of the III-N system has been studied theoretically in detail and many key aspects are well understood. However, there is no way to directly measure the behavior of high energy electrons. The HET can be used as a spectroscopic tool enabling us to probe high energy electron behavior directly using electrical measurements.

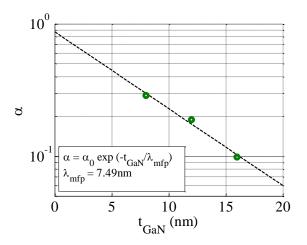

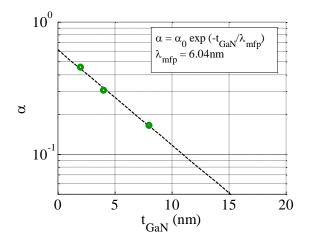

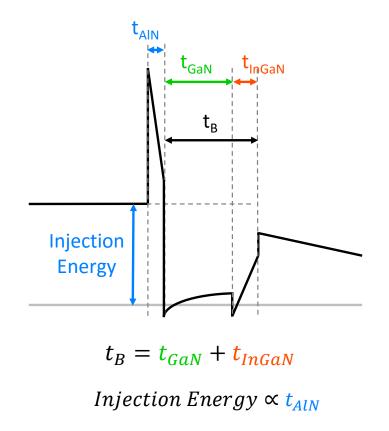

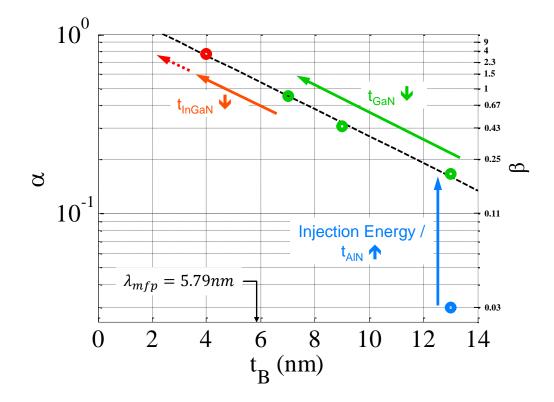

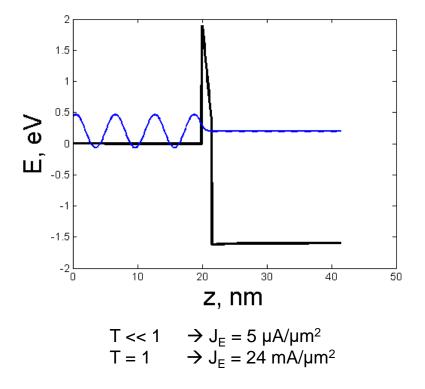

The transit length of electrons can be changed by varying the base thickness. With a longer transit distance, more electrons are likely to get scattered and not cross over the collector[51], [52]. Keeping the injection and collector barrier fixed, the mean free path of hot-

electrons can be extracted from transfer ratio vs base thickness for the given energy window. This experiment repeated for different energy windows can yield a very detailed measurement of high energy scattering rates in the III-N material system.

The energy distribution of hot-electrons can also be mapped by a slightly different structure[37]. If the collector barrier is made higher than the emitter barrier, none of the injected electrons get collected. As the collector bias is increased, the collector barrier gets lowered allowing more electrons to pass through. The exact electron distribution as a function of energy (collector barrier) can thus be extracted.

Since the collector of a HET is just an energy spectrometer for hot-electrons, it can be used it to study changes in injection energy of the HET. As demonstrated later, the best injection barrier for III-N HETs is a polarization-dipole based barrier. Lateral fluctuations in composition and thickness of the dipole layer can lead to non-uniformities in injection barrier height and thus injection energy of the hot-electrons. Defects like threading dislocations can provide pathways for electrons to be injected at energies lower than the injection barrier. Such non-uniformities can be observed and studied quantitatively using the collector of a HET as a spectrometer for injection energy[53]. The HET can therefore also be used to study material properties like defects and non-uniformities.

Electron velocity in the base can be calculated by subjecting the device to a magnetic field perpendicular to transport direction[54]. A magnetic field decreases the electron  $k_z$  and increases  $k_x$  and  $k_y$  thus decreasing current gain. The amount of decrease in  $k_z$  (and gain)

depends on the electron velocity. Thus, group velocity vs energy can be mapped out for GaN using only electrical measurements of a III-N HET.

# 1.4 Synopsis of Dissertation

This thesis is organized as follows,

- Chapter 1 introduces the Hot Electron Transistor and its operation and design principles. It also gives a brief history of the HET family and discusses the potential applications of a III-N based HET.

- Chapter 2 discusses the design of a HET in the III-N system using polarization-dipoles.

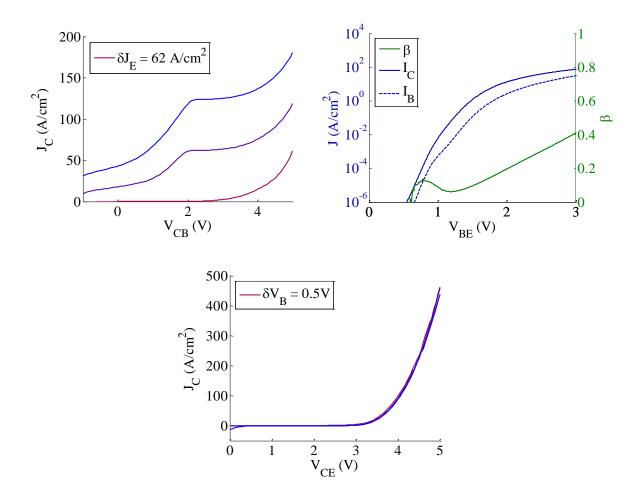

Common emitter operation (β ~ 0.1) is shown for the first time in III-N HETs using this design methodology.

- Chapter 3 introduces a novel device design and process using AlN as an etch stop layer for base contacts, in order to enable base scaling. Current gain ~ 3.5 is demonstrated using this AlN based design.

- Chapter 4 describes hot-electron transport in detail and discusses the experiments conducted to find hot-electron mean free path.

- Chapter 5 discusses an InGaN quantum well HET design for high gain and discusses some challenges associated with the growth of such a structure. The conclusion and future directions are presented in Chapter 6.

# 2 III-N HET DESIGN AND COMMON

# **EMITTER OPERATION**

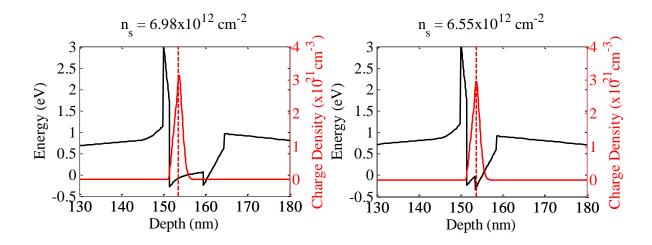

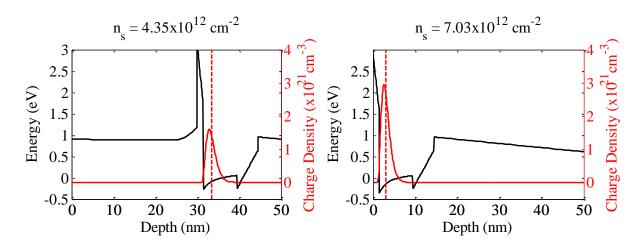

This chapter introduces the basics of III-N HET design in order to derive the design constraints for good DC performance. Polarization engineering is a strong tool used in III-N HET design and its role is discussed in detail here. All the designs discussed in this thesis are simulated using BandEng, a self-consistent 1D Poisson-Schrodinger solver. The HET requires two unipolar back to back diodes such that there is a potential well formed in between. The simplest diode designs in the III-N system can be made using polarization-dipole (P-D) or heterojunction barriers. Both these methods can be used to design either of the two diodes needed for a HET.

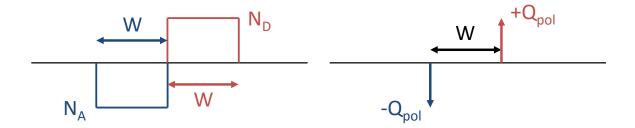

The P-D barrier uses the basic concept of dipole charges to induce barriers in the conduction band. Planar doped barriers also use a similar concept to form barriers but the dipoles are formed by alternating p and n type ionized dopants. The barrier height is roughly proportional to the dipole moment of the charges. Using dopants, however, it is very difficult to achieve very large dipole moments as the doping concentration required is large. Consider for example a dipole composed of ionized dopants of both polarities where the width of the ionized dopant layer is the same for both (Figure 2.1).

Figure 2.1 Charge profile of planar-doped and polarization-dipole barriers

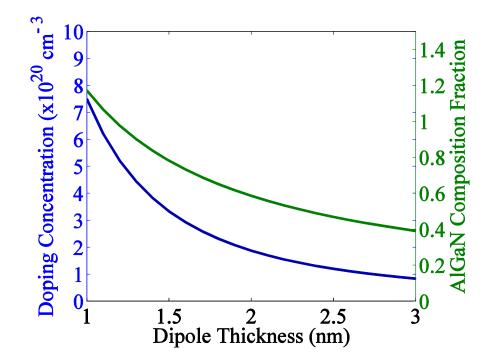

Charge neutrality implies,  $N_A W = N_D W \Rightarrow N_A = N_D$ . The potential barrier due to such a charge distribution is then,  $\phi_B = \frac{q}{\epsilon} N_A W^2$  and the dipole moment of this charge distribution is  $p = N_A W^2$ . Therefore, in order to induce a barrier of 1.5eV, the required dipole moment can be calculated to be  $p \cong 7.5 \times 10^6 \ cm^{-1}$ . If there are no restrictions on W, then even a low dopant density can be used to achieve the required barrier over a large distance. However, as we will see later, in a ballistic electron device, distance is a strong constraint and it is preferred to induce barriers over as small distances as possible. Figure 2.2 shows the doping concentration required as a function of dipole thickness in order to induce a 1.5eV barrier. The required doping is extremely large and difficult to practically realize. The same barrier can also be induced by a P-D layer (say AlGaN) sandwiched between two GaN layers. The polarization discontinuity between the materials leads the formation of a net polarization charge at the interface of GaN/AlGaN. The polarity of the charge is opposite for the two interfaces thus forming a dipole. As the Al fraction in AlGaN increases, the net polarization charge induced at the interface increases. Figure 2.2 also shows the Al fraction required to induce the same 1.5eV barrier using an AlGaN P-D layer. By using AlN and AlGaN, it is thus possible to achieve very large barriers over extremely thin dipole layers. The same argument applies for

InGaN induced barriers. P-Ds are therefore an extremely strong tool that is special to the III-N material system. It should be noted that in real P-D barriers, the use of heterojunctions also introduces  $\Delta E_{Cs}$  in the band diagram which complicate the picture, however, the argument presented here still holds.

Figure 2.2 Comparison of a 1.5eV barrier induced by planar doping and polarization dipoles. The required doping concentration and AlGaN composition are plotted as a function of the dipole thickness.

Heterojunction barriers are formed over a distance that is practically zero. P-D barriers on the other hand need a finite dipole thickness to form a barrier. For ballistic devices where distance is a strong constraint, heterojunction barriers can therefore have a significant advantage over P-D barriers. However, in III-Nitrides, heterojunctions cannot be decoupled from polarization discontinuities. Additional band engineering is needed to mitigate any negative effects that might result from polarization. Another issue with heterojunction diodes

in the III-N system is that most AlInGaN alloys are strained to GaN and have a finite critical thickness before the material loses its structural integrity. The implications of such issues on specific HET designs will be discussed throughout this thesis.

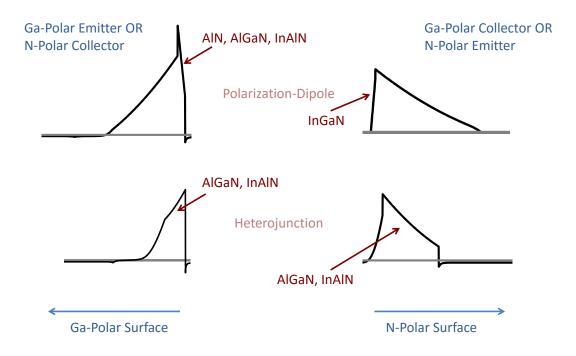

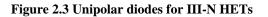

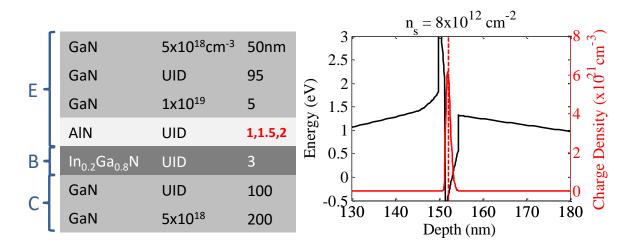

To summarize, there are 4 possible III-N HET designs within this framework (Figure 2.3) and 4 additional designs if the polarity of the structure is reversed (Figure 2.4). This thesis will focus only on the four Ga-Polar HET designs. A detailed discussion on the advantages/disadvantages of N-Polar HETs is presented elsewhere[52][53]. For the purpose of this discussion, it is sufficient to state that N-Polar HETs are at a disadvantage to Ga-Polar HETs in terms of current gain. Theoretically, any of these designs could be used to make a working transistor, however, taking into account III-N growth and DC figures of merit, some designs can have significant advantages. This chapter discusses Design 1 and Design 2 in detail to find out the best collector barrier design for a III-N HET.

Figure 2.4 III-N HET Designs

# 2.1 AlGaN based Design

The growth and electrical characteristics of AlGaN/GaN heterostructures have been extensively studied in the III-N HEMT community. This motivated the use of AlGaN based Design 1 as the first design to be investigated in this work. Design 1 was also used to study III-N HETs in previous work[55].

The E-B barrier (top barrier) here is formed by a thin high composition AlGaN layer which acts as an electrostatic polarization-dipole. The height of this barrier can be increased by increasing the AlGaN thickness or composition. Due to a net positive polarization charge at the E-B interface, electrons accumulate in the base to form a 2DEG which can provide high base conductivity. The base here is a GaN layer. The B-C barrier (bottom barrier) is also formed by an AlGaN layer. The negative polarization-charge at the B-C interface partially depletes base charge. The height of the B-C barrier is thus a sum of the depletion potential and the  $\Delta E_c$  between GaN and AlGaN. As discussed earlier, a thick collector barrier can help reduce J<sub>BCleak</sub>, however, in this design since the collector barrier is made entirely of AlGaN, its thickness is limited by the amount of strain that the layer can handle before strain relaxation. For a 30% AlGaN layer, the critical thickness is 20-30nm [56]. The depletion of base charge due to negative polarization charge at the B-C interface degrades base resistance. Hence, this design adds two more tradeoffs on top of the ones that are present in the general HET.

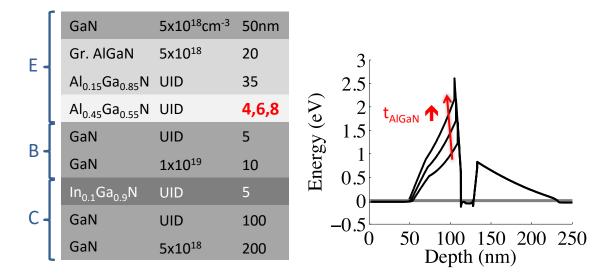

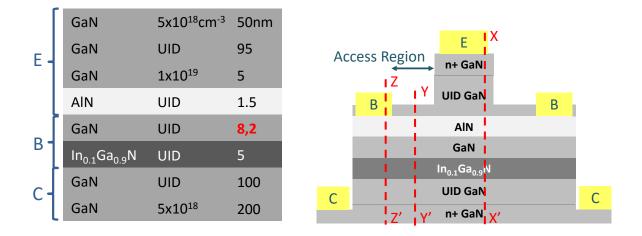

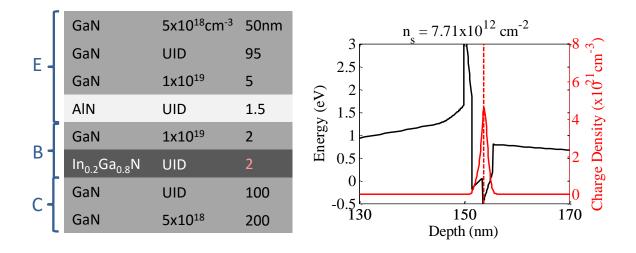

### 2.1.1 Growth and Fabrication

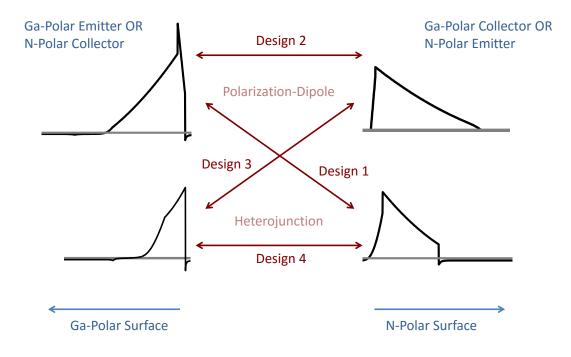

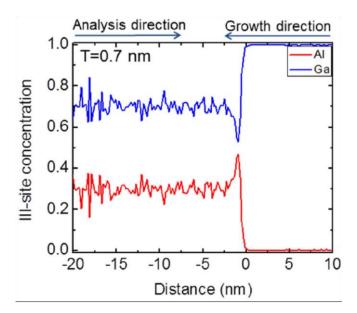

Previous work used primarily MBE as the growth technique[57]. It has been shown that MBE has high vertical leakages due to presence of Ga metal in threading dislocations[58]. This work, therefore, starts out with MOCVD as the growth technique. The device structure grown by MOCVD uses a  $Al_{0.45}Ga_{0.55}N$  polarization-dipole to form the E-B barrier. This layer was intended to be pure AlN but due to unintentional Ga incorporation during growth, it turns out to be AlGaN[59] (Figure 2.5). Since the Ga incorporation is unintentional, the higher growth rate of AlGaN in comparison to AlN results in an AlGaN layer thicker than what was intended i.e. an intended 4nm AlN layer could turn out to be ~ 8nm ~ 50% AlGaN. A 15% AlGaN layer is added on top in order to increase the 2DEG density. The B-C barrier is formed using a 20nm 30% AlGaN layer. The GaN base thickness used here is 15nm. Figure 2.6 shows the detailed layer structure and resulting conduction band-diagram of the structure grown.

Figure 2.5 Atom Probe of MOCVD grown AlN layers[59]

Figure 2.6 (a) Layer structure and (b) band diagram of AlGaN based HET

To test this structure, individual diodes were first grown on both Bulk GaN (Lumilog) and GaN on Sapphire. The diode structures were processed by a simple RIE etch and ohmic contact deposition. The full HET structure was then grown on Bulk GaN to test transistor performance.

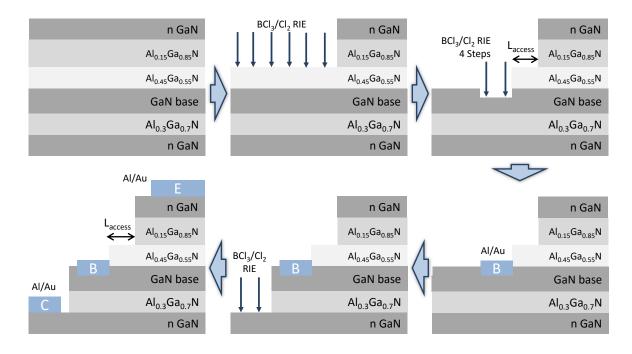

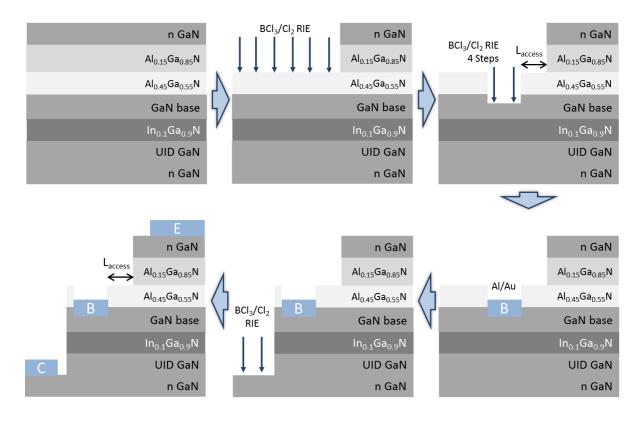

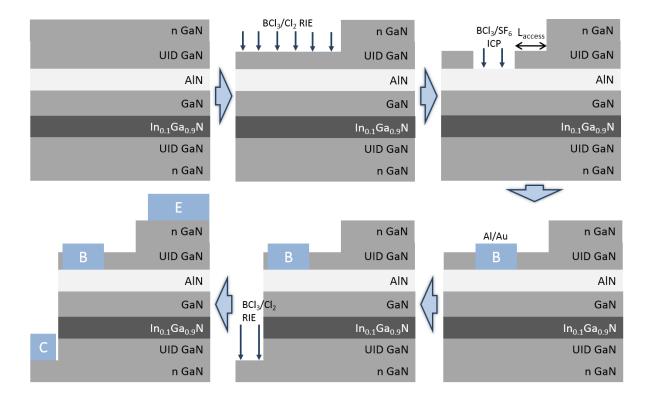

Fabrication of the HET began with  $BCl_3/Cl_2$  (20/5sccm, 10mT) based low power (15W) RIE timed to stop within 20nm of the 45% AlGaN layer (Figure 2.7). This preserves the base 2DEG in the access regions of the device. The GaN etch rate using this chemistry was measured to be ~ 6nm/min. The etched surface was very smooth (< 1nm RMS roughness) even after 15min of etching. This etch also showed very little selectivity between GaN and AlGaN. A second etch, using the same conditions, was used to etch into the GaN base layer and was followed by deposition of Al/Au base contacts. Small variations in etch rate, lack ofprecise values of layer thicknesses, lack of etch selectivity, and small errors in the AFM measurements for etch calibration make this step the most tricky and critical step of the entire process. Since the base thickness is only ~ 10nm, an error of even a few nanometers can result

Figure 2.7 Process Flow for the III-N HETs

in an excessive under-etch or over-etch both of which can be disastrous for the HET. Therefore, across the sample, different dies with different etch times for the second etch were fabricated simultaneously to ensure that at least some of them form ohmic base contacts. This two-step etch process for base contacts was developed as a part of this work. A final etch was performed to expose the collector contact layer. This was followed by emitter and collector ohmic contact deposition in the same step.

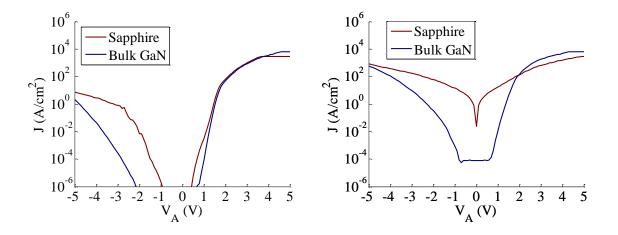

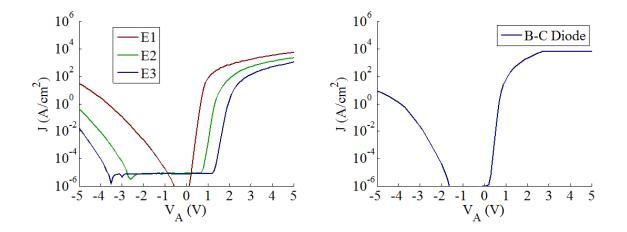

### 2.1.2 Diode and Transistor Results

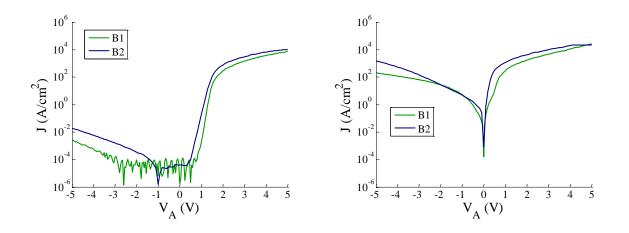

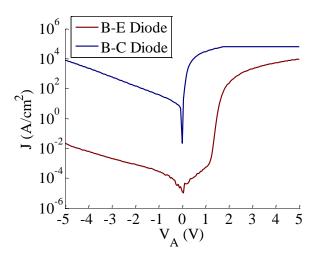

The E-B diode was rectifying on both Bulk GaN and Sapphire with a difference of  $\sim 3$  orders of magnitude between forward and reverse currents at 5V bias (Figure 2.8a)[46]. The key difference between the two substrates was lower reverse leakage and absence of kinks in forward bias regime on Bulk GaN. The B-C diode was barely rectifying when grown on

Figure 2.8 I-V characteristics of (a) E-B and (b) B-C diodes grown separately on both Bulk GaN and Sapphire

Sapphire (Figure 2.8b). On Bulk GaN the diode showed clear rectification. It could hold only  $\sim$  3V however before reverse leakages became comparable to forward current.

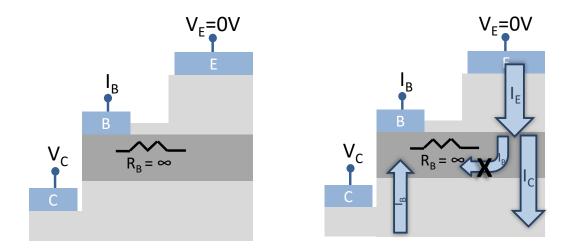

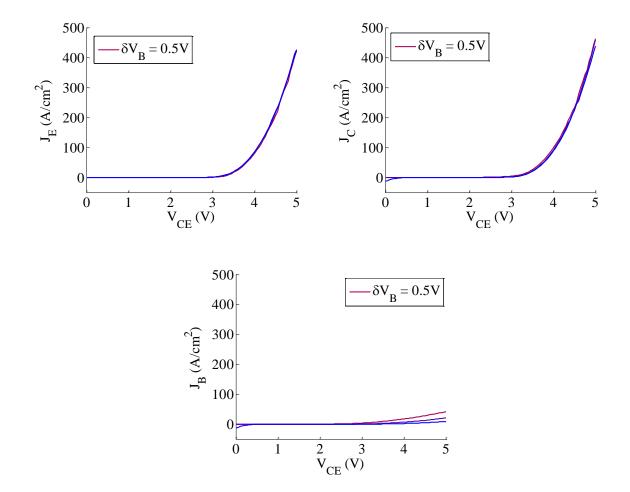

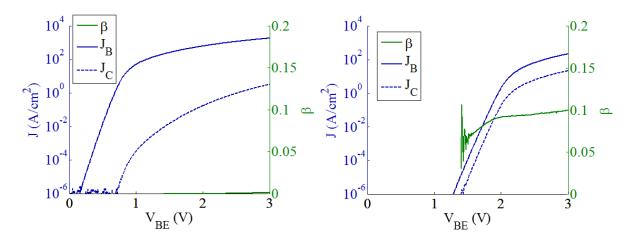

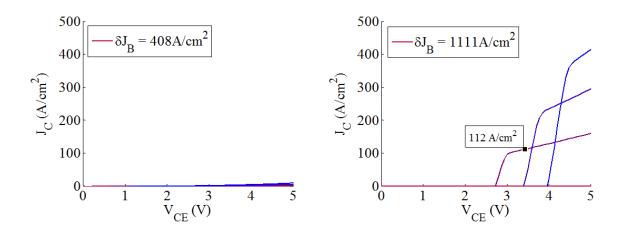

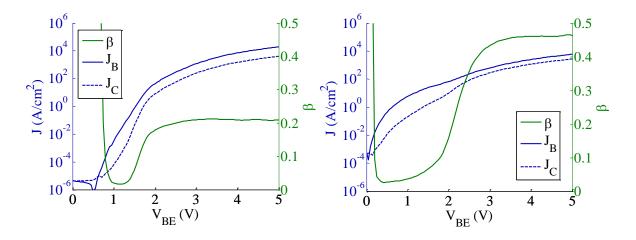

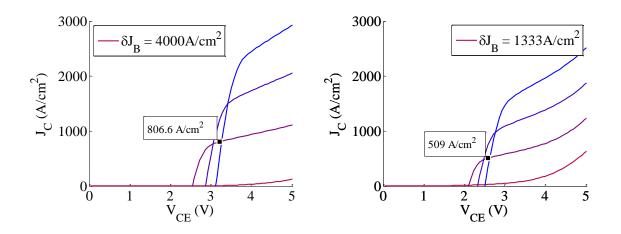

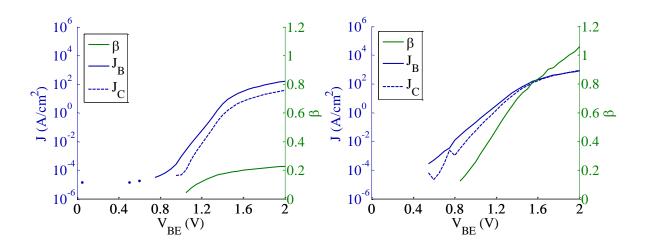

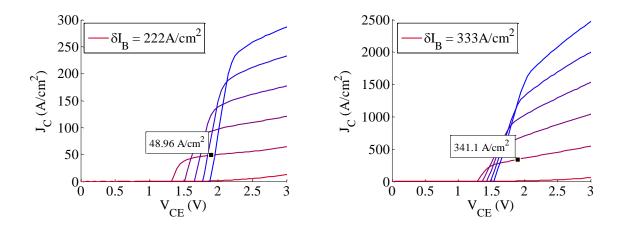

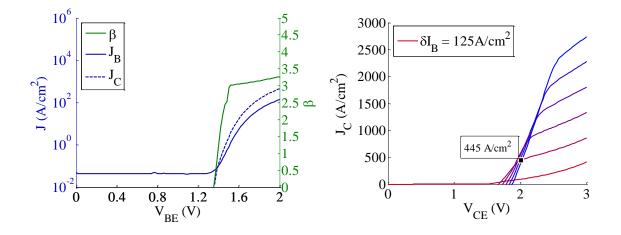

The base contacts on the full transistor structure were not ohmic. They exhibited a very large turn on voltage before any appreciable current flow. When measured in Common Base (CB) configuration, the transistor had saturating IV characteristics with  $\alpha \sim 1$  (Figure 2.9a). The  $\beta$  extracted from Gummel Plot was however < 1 (Figure 2.9b). However, in the Common Emitter (CE) configuration, only leakage was observed (Figure 2.9c). The lack of CE modulation contradicts the seemingly high gain observed in CB. This discrepancy, which was also observed in the previous work done on III-N HETs, is discussed in detail next.

Figure 2.9 (a) Common Base (b) Gummel Plot and (c) Common Emitter characteristics of the AlGaN HET

### 2.1.3 Issues

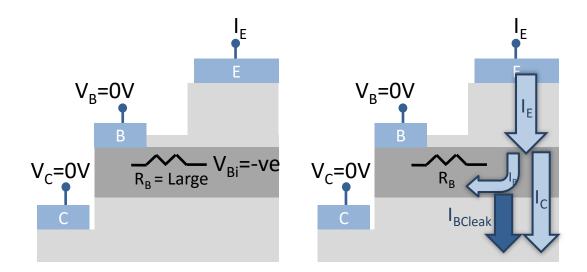

The first clue to understanding the discrepancy lies in the base contacts. To understand the cause of non-ohmic base contacts, we look closely at the device structure and fabrication steps. The base charge in our III-N HET design is primarily due to a 2DEG at the emitter-base interface induced by the AlGaN polarization-charge in the emitter layer structure. The bottom part of the base layer is depleted due to the presence of a net negative polarization-charge at

the GaN/AlGaN interface. In order to form base contacts, we etch away the emitter layer completely under the base contact thus resulting in a loss of the 2DEG under the base contact. Since the rest of the base is completely depleted due to the back-side polarization-charge, the net result is a complete lack of charge under the base contacts.

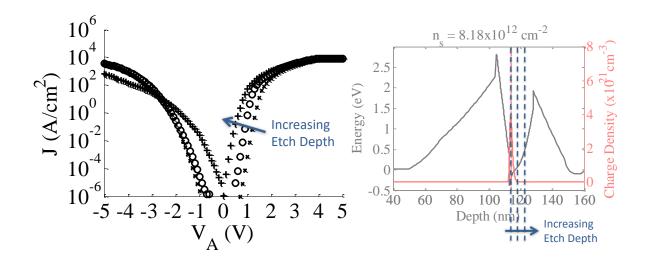

Figure 2.10 (a) I-V characteristics and (b) band-diagram of the B-C diode with increasing etch depth clearly showing barrier lowering

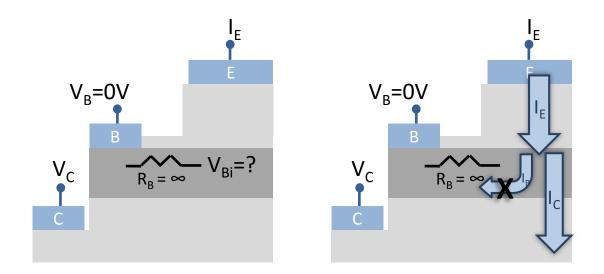

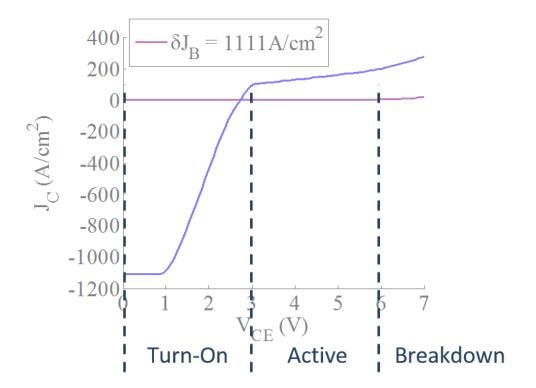

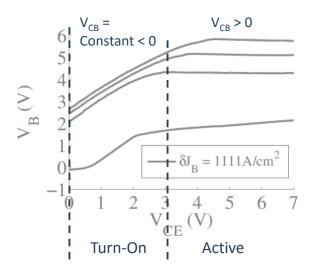

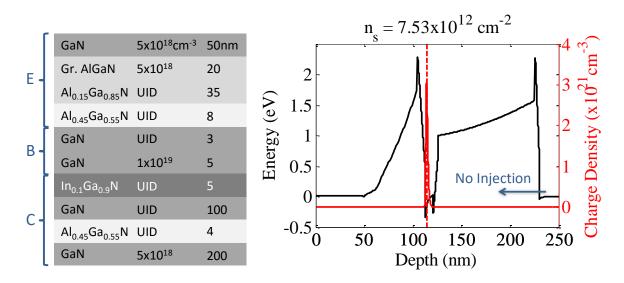

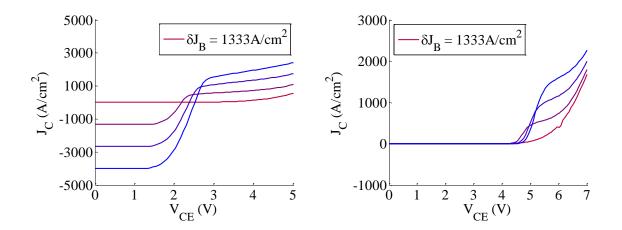

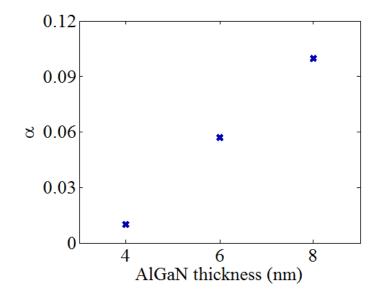

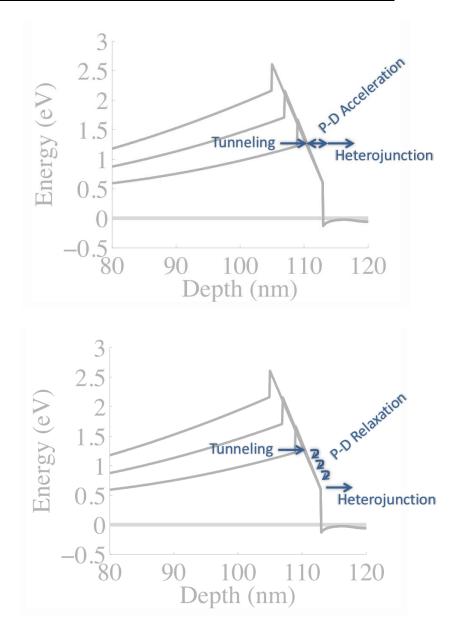

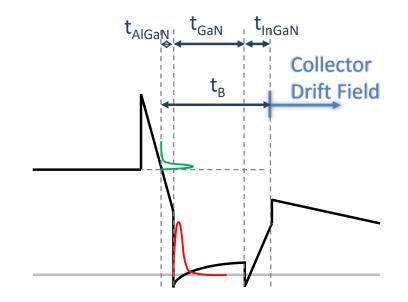

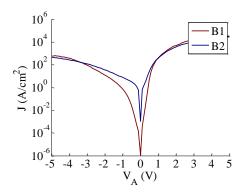

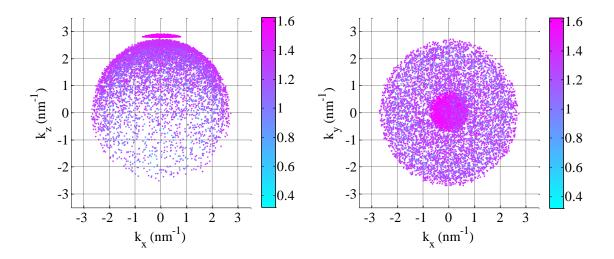

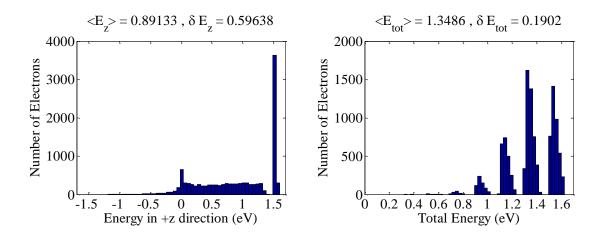

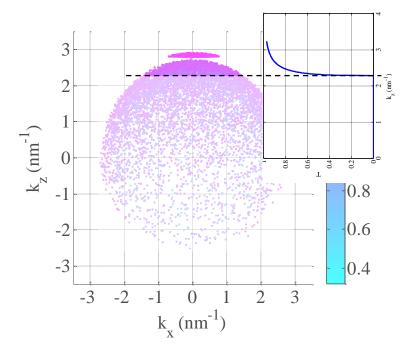

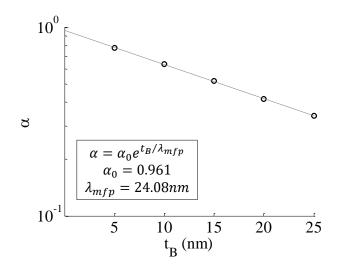

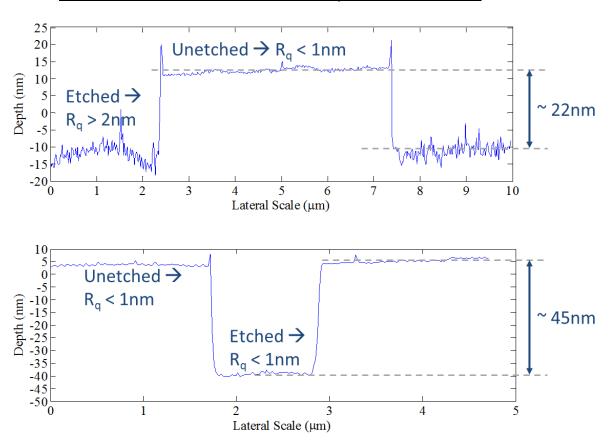

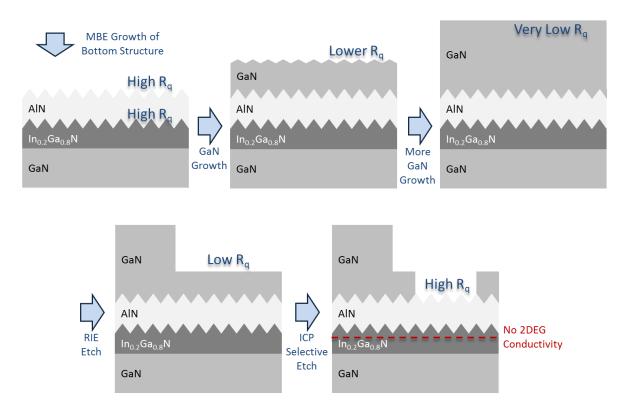

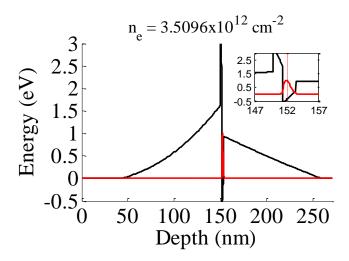

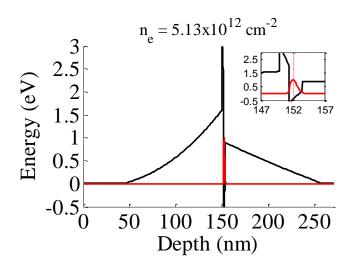

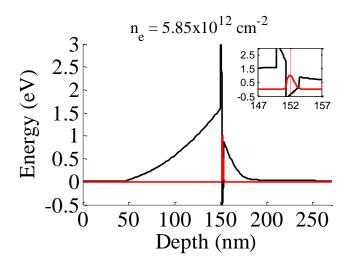

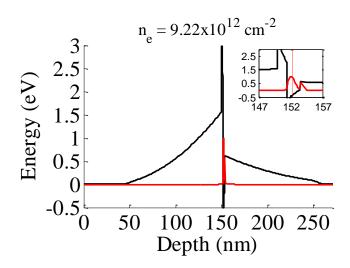

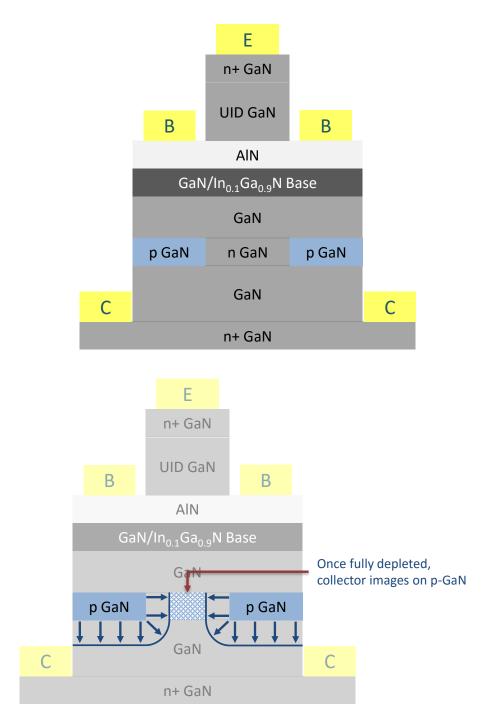

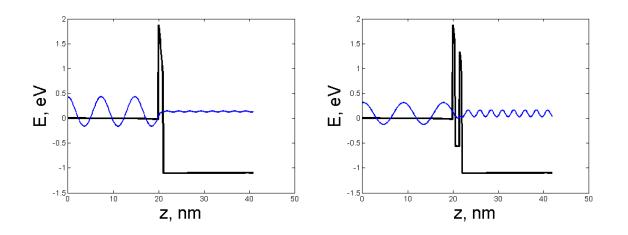

To test this hypothesis, B-C diodes were measured on fabricated HET structures. In the two-step etch process for base contacts, different etch depths were used for the second etch into the GaN base layer. As a result, the B-C diodes have varying GaN thickness on top (Figure 2.10). With increasing etch depth, a decrease in FB turn-on of the B-C diodes was observed. This confirms that the base contact is sitting on top of a completely depleted GaN layer. The potential drop in the depleted layer decreases as etch depth increases thus decreasing the B-C diode turn-on. The lack of ohmic base contacts can thus be explained by absence of charge below the base contact.