# **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

#### **Title**

Modeling, Characterization and Simulation of On-Chip Power Delivery Networks and Temperature Profile on Multi-Core Microprocessors

#### **Permalink**

https://escholarship.org/uc/item/8n3866xf

#### **Author**

Li, Duo

#### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Modeling, Characterization and Simulation of On-Chip Power Delivery Networks and Temperature Profile on Multi-Core Microprocessors

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Duo Li

December 2010

Dissertation Committee:

Dr. Sheldon X.-D. Tan, Chairperson

Dr. Yingbo Hua

Dr. Frank Vahid

| The Dissertation of Duo Li is app | proved:             |    |

|-----------------------------------|---------------------|----|

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   |                     |    |

|                                   | Committee Chairpers | on |

University of California, Riverside

#### ACKNOWLEDGMENT

There are many thanks to many people who made this dissertation possible.

First of all, I would like to thank my Ph.D. advisor Dr. Sheldon Tan for the continuous support to my Ph.D. study and research work. Thank him for guiding me on my research road and providing me the great lab research environment. I could not have finished my dissertation successfully without his encouragement, sound advice, good teaching and lots of good ideas.

Besides my advisor, I would like to thank the rest of my Ph.D. dissertation committee members Dr. Yingbo Hua and Dr. Frank Vahid, for their encouragement, comments and questions.

I would like to thank all my labmates for their support and encouragement. I could not have had the better understanding on my research without the frequent discussions with them.

I would like to thank my parents Daping Li and Yuqin Cong for giving birth to me, rasing me, teaching me, supporting me and loving me all the time.

Last but not the least, I would like to thank my lovely wife Shan Shan. Thanks for being with me together during my Ph.D. study in US.

#### ABSTRACT OF THE DISSERTATION

Modeling, Characterization and Simulation of On-Chip Power Delivery Networks and Temperature Profile on Multi-Core Microprocessors

by

#### Duo Li

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, December 2010 Dr. Sheldon X.-D. Tan, Chairperson

Reliable on-chip power delivery is a challenging design task for sub-100nm and below VLSI technologies as voltage IR drops become more and more pronounced. This situation gets worse as technology continues to scale down. And efficient verification of power integrity becomes critical for design closure. In addition, the increasing process-induced variability makes it even worse for reliable power delivery networks. The process induced variations manifest themselves at different levels (wafer level, die-level and within a die) and they are caused by different sources (lithograph, materials, aging, etc.). In this dissertation, for power delivery networks without considering process variations, we propose an efficient simulation approach, called ETBR (Extended Truncated Balanced Realization), which uses MOR (Model Order Reduction) to speedup the simulation. To make ETBR more accuracy, we further introduce an error control mechanism into it. For power delivery networks with considering process variations, we propose varETBR (variational Extended Truncated Balanced Realization), a reduced Monte-Carlo simulation approach, which can handle a large number of variables and different variation distributions. To further speedup

the MOR process used in the fast simulation, a hierarchical Krylov subspace projection based MOR approach, hiePrimor, is proposed.

Besides the on-chip power delivery, excessive on-chip temperature has also become a first-tier design constraint as CMOS technology scales into the nanometer region. The exponential increase of power density of the high-performance microprocessors leads to the rapid rising of the average chip temperature. Higher temperature has significant adverse impacts on chip package cost, performance, and reliability. Multi-core techniques provide a viable solution to temperature/power problems. However, designing thermal efficient multi-core microprocessors remains a challenging problem as the temperature in each core can be dramatically different and the resulting large temperature gradients can produce mechanical stress and degrade the chip reliability. In this dissertation, we investigate a new architecture-level dynamic thermal characterization problem from a behavioral modeling perspective to address the emerging thermal related analysis and optimization problems for high-performance multi-core microprocessor design. We propose a new approach, called ThermPOF, to build the thermal behavioral models from the measured or simulated thermal and power information at the architecture level. And then we extend ThermPOF into ParThermPOF, a parameterized thermal behavioral modeling approach that can handle different parameters in multi-core microprocessor design and optimization.

# **Contents**

| Lı | st of ' | lables  |                                                                  | X    |

|----|---------|---------|------------------------------------------------------------------|------|

| Li | st of l | Figures |                                                                  | xii  |

| 1  | Intr    | oductio | n                                                                | 1    |

|    | 1.1     | Motiva  | ations                                                           | . 1  |

|    |         | 1.1.1   | Modeling and simulation of on-chip power delivery networks       | . 1  |

|    |         | 1.1.2   | Modeling and simulation of temperature profile on multi-core mi- |      |

|    |         |         | croprocessors                                                    | 3    |

|    | 1.2     | Object  | ives and main results of this dissertation                       | . 5  |

|    | 1.3     | Organi  | ization of this dissertation                                     | . 7  |

| 2  | ETE     | BR: Ext | ended Truncated Balanced Realization for On-Chip Power Grid      | d    |

|    | Netv    | work Aı | nalysis                                                          | 8    |

|    | 2.1     | Power   | grid network models                                              | 10   |

|    | 2.2     | New e   | xtended balanced truncation method: ETBR                         | . 11 |

|    |         | 2.2.1   | Review of standard TBR                                           | . 11 |

|    |         | 2.2.2   | Review of fast TBR method: Poor man's TBR                        | . 13 |

|    |         | 2.2.3   | Response Gramian and fast computation method                     | . 14 |

|      | 2.2.4  | Extended truncated balanced realization method: ETBR            | 16       |

|------|--------|-----------------------------------------------------------------|----------|

|      | 2.2.5  | Time complexity analysis and comparison                         | 17       |

|      | 2.2.6  | Statistical point of view                                       | 19       |

| 2.3  | Numer  | rical examples of ETBR                                          | 19       |

|      | 2.3.1  | Comparison with the EKS method                                  | 20       |

|      | 2.3.2  | Results on circuits with many different switching timings       | 28       |

| 2.4  | IR dro | p analysis problem                                              | 30       |

| 2.5  | New re | eduction based IR drop analysis method                          | 31       |

|      | 2.5.1  | Error estimation in the time domain                             | 33       |

|      | 2.5.2  | Effective resistance                                            | 34       |

|      | 2.5.3  | Dynamic error control                                           | 35       |

|      | 2.5.4  | The new IR drop analysis algorithm flow                         | 37       |

| 2.6  | Numer  | rical examples of ETBR_IR                                       | 38       |

| 2.7  | Summ   | ary                                                             | 44       |

| varI | TRR: Y | Variational Extended Truncated Balanced Realization for On-Chip |          |

|      |        | Network Analysis                                                | 46       |

| 3.1  |        | onal model for power grid networks                              |          |

| 3.2  |        | ariational analysis method: varETBR                             |          |

| 0.2  | 3.2.1  | Extended truncated balanced realization scheme                  |          |

|      | 3.2.2  | The new variational ETBR method                                 |          |

|      | 3.2.3  | Statistical interpretation of Grammian                          |          |

| 3.3  |        | utation of variational response Grammian                        |          |

| 3.4  | -      | rical examples                                                  |          |

| 2.5  | Cumm   |                                                                 | 50<br>61 |

3

| 4 | hieP | Primor: Hierarchical Krylov Subspace Based Reduction of Large Intercon-  |     |

|---|------|--------------------------------------------------------------------------|-----|

|   | nect | s                                                                        | 66  |

|   | 4.1  | Review of subspace projection based MOR methods                          | 69  |

|   | 4.2  | Hierarchical projection MOR method: hiePrimor                            | 71  |

|   |      | 4.2.1 A walkthrough example                                              | 71  |

|   |      | 4.2.2 The hiePrimor algorithm                                            | 73  |

|   |      | 4.2.3 The algorithm flow for hiePrimor                                   | 77  |

|   | 4.3  | Moment matching connection                                               | 77  |

|   | 4.4  | Circuit partitioning                                                     | 80  |

|   | 4.5  | Numerical examples                                                       | 81  |

|   | 4.6  | Summary                                                                  | 87  |

| 5 | The  | rmPOF: Architecture-level Thermal Characterization For Multi-Core Mi-    |     |

|   | crop | processors                                                               | 89  |

|   | 5.1  | Architecture-level thermal modeling problem                              | 91  |

|   | 5.2  | Review of generalized pencil-of-function method                          | 94  |

|   | 5.3  | New architecture-level thermal behavioral modeling method                | 98  |

|   |      | 5.3.1 The ThermPOF algorithm flow                                        | 98  |

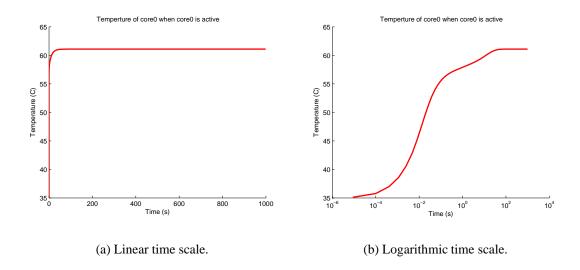

|   |      | 5.3.2 Logarithmic scale sampling for poles and residues extraction       | 99  |

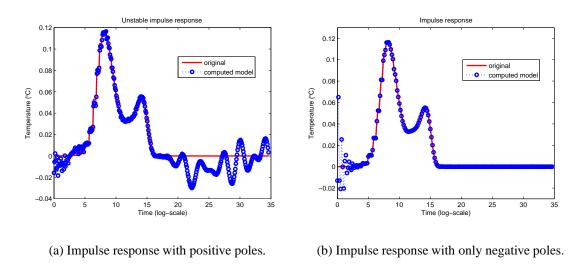

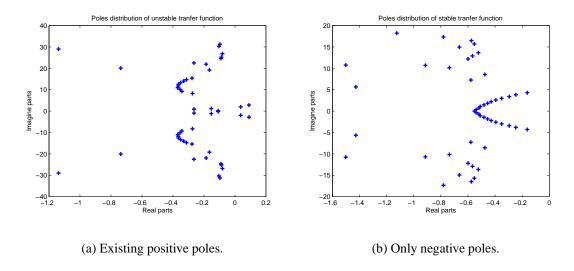

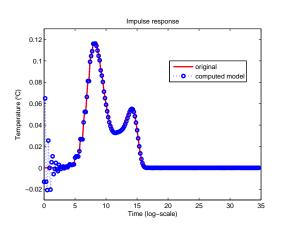

|   |      | 5.3.3 Stable poles and residues extraction                               | 101 |

|   |      | 5.3.4 Recursive computation of temperature responses and time complexity | 106 |

|   | 5.4  | Reduction of thermal models                                              | 107 |

|   | 5.5  | Numerical examples                                                       | 110 |

|   | 5.6  | Summary                                                                  | 116 |

| 118 |

|-----|

| 120 |

| 125 |

| 125 |

| 126 |

| 127 |

| 128 |

| 129 |

| 130 |

| 134 |

| 134 |

| 136 |

| 138 |

| 144 |

| 146 |

| 146 |

|     |

| 149 |

| 151 |

|     |

# **List of Tables**

| 2.1 | Test circuits                                                                 | 20       |

|-----|-------------------------------------------------------------------------------|----------|

| 2.2 | CPU times (in seconds) comparison of ETBR and IEKS ( $q=6$ )                  | 28       |

| 2.3 | CPU times (in seconds) comparison of ETBR, parallelized ETBR and IEKS         |          |

|     | (q = 10)                                                                      | 28       |

| 2.4 | Benchmark circuits                                                            | 38       |

| 2.5 | Performance comparison (CPU seconds) of UltraSim, ETBR and ETBR_IR            | 39       |

| 2.6 | Accuracy comparison (max IR drop values) of UltraSim, ETBR and ETBR_IR        | 39       |

| 2.7 | Performance comparison (CPU seconds) of reduction time in ETBR_IR             |          |

|     | between single core and Quad-Core                                             | 44       |

| 2.8 | Performance comparison (CPU seconds) between ETBR_IR and ETBR_IR_TH           | IREAD 44 |

| 3.1 | Power Grid (PG) benchmarks                                                    | 57       |

| 3.2 | CPU times (s) comparison of varETBR and Monte Carlo ( $q=50,p=10$ ) .         | 61       |

| 3.3 | Projected CPU times (s) comparison of varETBR and Monte Carlo ( $q=50$ ,      |          |

|     | p=10,10000 samples)                                                           | 62       |

| 3.4 | Relative errors for the mean of max voltage drop of varETBR compared          |          |

|     | with Monte Carlo on the 2000th node of $ibmpg1$ ( $q = 50$ , $p = 10$ , 10000 |          |

|     | samples) for different variation ranges and different numbers of variables .  | 63       |

| 3.5 | Relative errors for the variance of max voltage drop of varETBR compared          |

|-----|-----------------------------------------------------------------------------------|

|     | with Monte Carlo on the 2000th node of $ibmpg1$ ( $q = 50$ , $p = 10$ , 10000     |

|     | samples) for different variation ranges and different numbers of variables . 63   |

| 3.6 | CPU times (s) comparison of StoEKS and varETBR ( $q=50,p=10$ ) with               |

|     | 10000 samples for different numbers of variables                                  |

| 4.1 | Reduction time comparison of PRIMA and hierrimor ( $k = 4, q = n \times k$ ) 85   |

| 4.2 | Reduction time for different numbers of partitions ( $k = 4, q = n \times k$ ) 86 |

| 4.3 | Reduction time for different numbers of ports (Ckt7, $k=4$ , $q=n\times k$ ) 86   |

| 4.4 | Reduction time comparison of PRIMA and hiePrimor with parallel com-               |

|     | puting settings $(k = 4, q = n \times k)$                                         |

| 5.1 | Difference when temperatures achieve the steady state                             |

| 5.2 | Statistics of the difference between measured and computed temperatures 113       |

| 5.3 | The maximal and minimum error peaks ( $M=50$ )                                    |

| 5.4 | Statistics of the errors between measured and computed temperatures ( ${\cal M}=$ |

|     | 50)                                                                               |

| 5.5 | The maximal and minimum error peaks and means ( $M=30$ ) 115                      |

| 5.6 | Speedup when $M=30$ compared to $M=50.$                                           |

| 6.1 |                                                                                   |

|     | Errors of the peaks                                                               |

| 6.2 | Average errors and relative errors between the computed and given temper-         |

# **List of Figures**

| 1.1  | The power grid model                                                      | 2  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | The quad-core architecture                                                | 4  |

| 2.1  | The power grid model used                                                 | 11 |

| 2.2  | Transient waveform at the 200th node of Ckt2                              | 21 |

| 2.3  | The simulation errors of ETBR and IEKS of Ckt2                            | 22 |

| 2.4  | Transient waveform at the 5th current source of Ckt2                      | 22 |

| 2.5  | Transient waveform at the 200th node of Ckt2 with fast changing inputs    | 23 |

| 2.6  | The simulation errors of ETBR and IEKS on Ckt2 with fast changing inputs. | 23 |

| 2.7  | The transient waveform at the 5th current source of Ckt2                  | 24 |

| 2.8  | Transient waveform at the 200th node of Ckt2 with fast changing inputs    | 24 |

| 2.9  | The simulation errors of ETBR and IEKS on Ckt2 with fast changing inputs. | 25 |

| 2.10 | Transient waveform at the 200th node of Ckt9 (RLC)                        | 25 |

| 2.11 | The simulation errors of ETBR and IEKS on Ckt9 (RLC)                      | 26 |

| 2.12 | Transient waveform at node 17 of a real industry circuit                  | 26 |

| 2.13 | Input current waveform at node 17 of a real industry circuit              | 27 |

| 2.14 | Transient waveforms of current sources switching at different time        | 29 |

| 2.15 | The transient waveform and errors at the 100th node ( $q = 5$ )           | 30 |

| 2.16 | The transient waveform and errors at the 300th node ( $q=5$ )               | 30 |

|------|-----------------------------------------------------------------------------|----|

| 2.17 | Input current waveform at the node 10510 of Ckt4 (the first one-tenth)      | 32 |

| 2.18 | Voltage waveform at the node 10510 of Ckt4 (the first one-tenth)            | 32 |

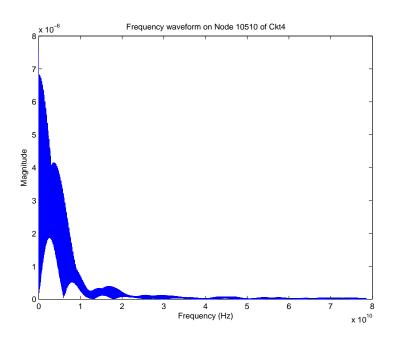

| 2.19 | Frequency waveform at the node 10510 of Ckt4 (the first one-tenth)          | 33 |

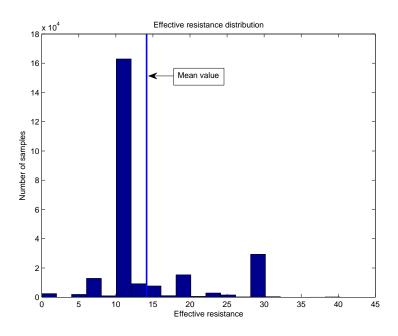

| 2.20 | Effective resistance distribution of Ckt4                                   | 36 |

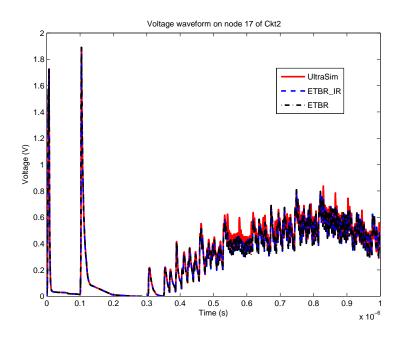

| 2.21 | Voltage waveform at the node 17 of Ckt2                                     | 40 |

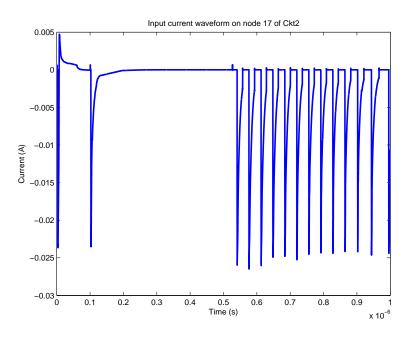

| 2.22 | Input current waveform at the node 17 of Ckt2                               | 40 |

| 2.23 | Voltage waveform at the node 10510 of Ckt4                                  | 41 |

| 2.24 | Input current waveform at the node 10510 of Ckt4                            | 41 |

| 2.25 | Voltage waveform at the node 107 of Ckt5                                    | 42 |

| 2.26 | Input current waveform at the node 107 of Ckt5                              | 42 |

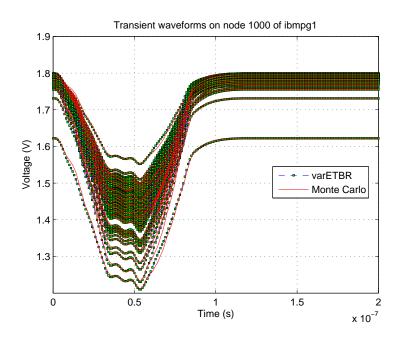

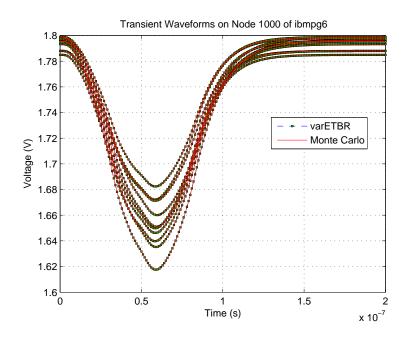

| 3.1  | Transient waveform at the 1000th node (n1_20583_11663) of $ibmpg1$ ( $p =$  |    |

|      | 10, 100 samples)                                                            | 59 |

| 3.2  | Transient waveform at the 1000th node (n3_16800_9178400) of ibmpg6          |    |

|      | (p = 10, 10  samples).                                                      | 59 |

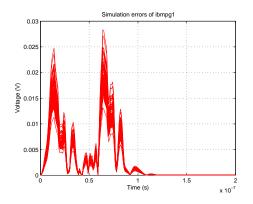

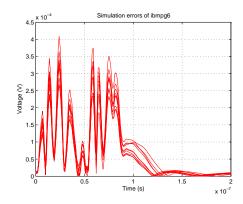

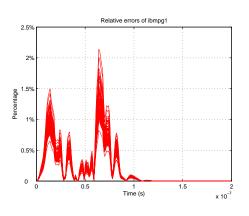

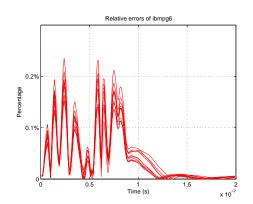

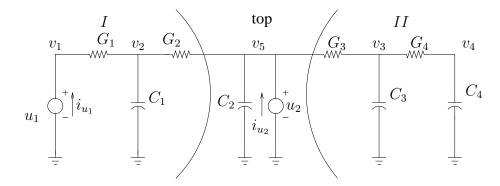

| 3.3  | Simulation errors of <i>ibmpg1</i> and <i>ibmpg6</i>                        | 60 |

| 3.4  | Relative errors of $ibmpg1$ and $ibmpg6$                                    | 60 |

| 3.5  | Voltage distribution at the 1000th node of ibmpg1 (10000 samples) when      |    |

|      | t = 50ns.                                                                   | 61 |

| 4.1  | A partitioned RC circuit.                                                   | 71 |

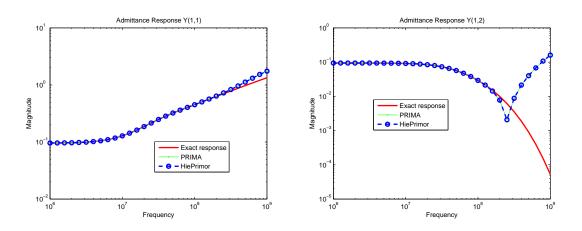

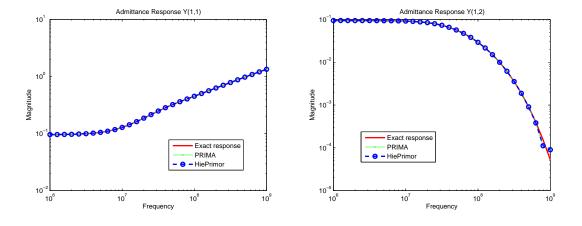

| 4.2  | Accuracy comparison of PRIMA and hie<br>Primor in Ckt1 when $k=4.\ .\ .\ .$ | 82 |

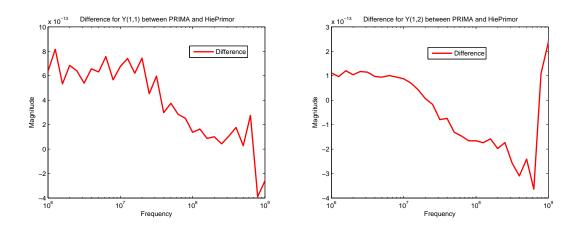

| 4.3  | Difference between PRIMA and hie<br>Primor in Ckt1 when $k=4$               | 83 |

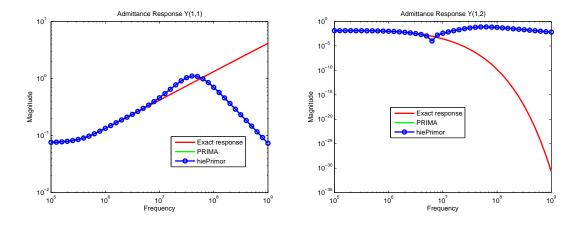

| 4.4  | Accuracy comparison of PRIMA and hie Primor in Ckt7 when $k = 4$            | 83 |

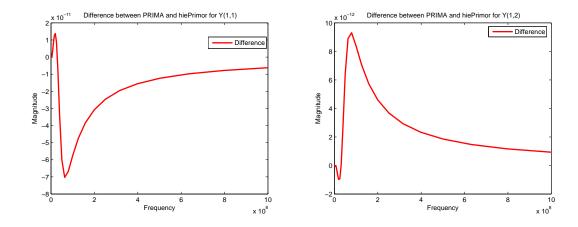

| 4.5  | Difference between PRIMA and hiePrimor in Ckt7 when $k = 4$                 |

|------|-----------------------------------------------------------------------------|

| 4.6  | Accuracy comparison of PRIMA and hiePrimor in Ckt1 when $k=8.\ \dots\ 84$   |

| 4.7  | Accuracy comparison of PRIMA and hiePrimor in Ckt7 when $k=8.\ \dots\ 85$   |

| 5.1  | The quad-core architecture                                                  |

| 5.2  | The abstracted model system                                                 |

| 5.3  | GPOF algorithm for poles and residues extraction                            |

| 5.4  | The flow of extracting one transfer function                                |

| 5.5  | The transient temperature change of core0 when core0 is excited by 20W      |

|      | power input                                                                 |

| 5.6  | Unstable and stable impulse response for Core0                              |

| 5.7  | Poles distributions of unstable and stable extracted transfer function 102  |

| 5.8  | Impulse and step response computed by inaccurate model with large error     |

|      | in the starting time                                                        |

| 5.9  | Impulse and step response computed by accurate model with both improve-     |

|      | ments                                                                       |

| 5.10 | Impulse and step response with $L=200.$                                     |

| 5.11 | The recursive computation step                                              |

| 5.12 | Comparison results of core0's temperature when all cores are active (driven |

|      | by 20W powers)                                                              |

| 5.13 | Comparison results of cache's temperature when all cores are active (driven |

|      | by 20W powers)                                                              |

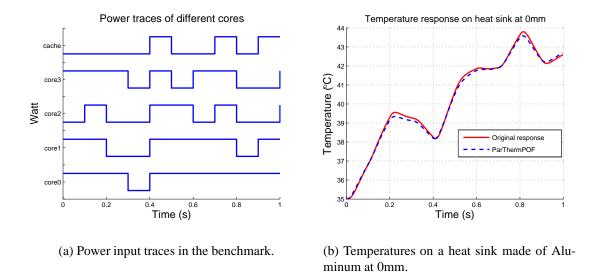

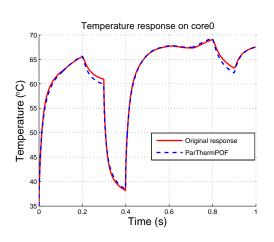

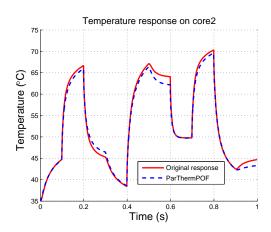

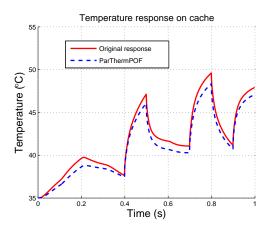

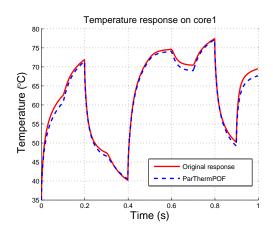

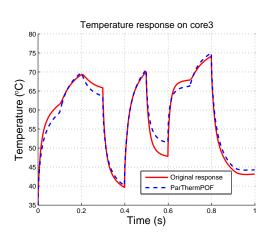

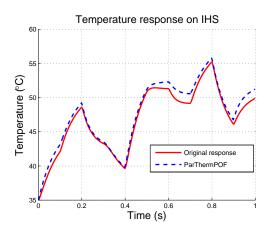

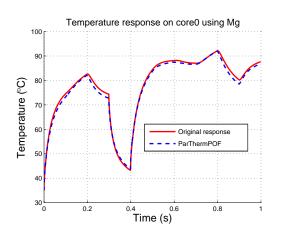

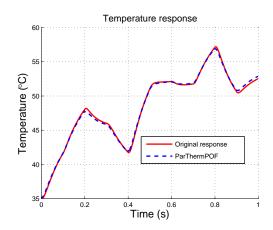

| 5.14 | Thermal simulation results on given power input traces                      |

| 5.15 | Thermal simulation results on given power input traces                      |

| 5.16 | Thermal simulation results on given power input traces                      |

| 6.1  | Quad-core architecture                                                                       |

|------|----------------------------------------------------------------------------------------------|

| 6.2  | 3D structure of quad-core processor                                                          |

| 6.3  | Temperature responses at various locations in quad-core processor when                       |

|      | only core0 is active                                                                         |

| 6.4  | Temperature distributions on the whole chip with package using different                     |

|      | heat sink materials when all cores and cache are active                                      |

| 6.5  | Abstracted system                                                                            |

| 6.6  | GPOF algorithm for poles and residues extraction                                             |

| 6.7  | The proposed <i>ParThermPOF</i> flow                                                         |

| 6.8  | Response surfaces at 3 time points when only core0 is active                                 |

| 6.9  | Step and impulse responses of one of the coefficients. The $\boldsymbol{x}$ axis is the time |

|      | in logarithmic scale and $y$ axis is the relative temperature to the ambient                 |

|      | temperature                                                                                  |

| 6.10 | Coded variable matrix X                                                                      |

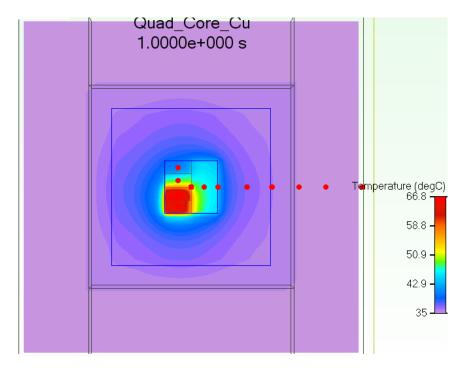

| 6.11 | Given temperature distribution on the whole chip package when using a                        |

|      | Copper heat sink at $t = 1s$                                                                 |

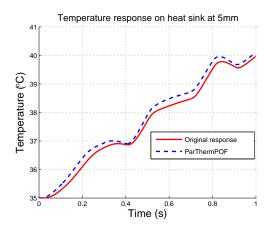

| 6.12 | Thermal simulation results on specific values of parameters                                  |

| 6.13 | Thermal simulation results on specific values of parameters                                  |

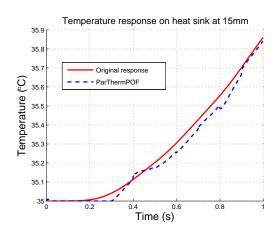

| 6.14 | Thermal simulation results on specific values of parameters                                  |

| 6.15 | Thermal simulation results on specific values of parameters                                  |

| 6.16 | Thermal simulation results on specific values of parameters                                  |

| 6.17 | Thermal simulation results on specific values of parameters                                  |

# **Chapter 1**

# Introduction

## 1.1 Motivations

## 1.1.1 Modeling and simulation of on-chip power delivery networks

Reliable on-chip power delivery is one of the difficult challenges for sub-100nm and below VLSI technology as voltage IR drops become more and more pronounced. This situation gets worse as technology continues to scale down. It has been reflected by the facts that more power has to be delivered into the chips for more packed devices, and supply voltage continues to decrease, which results in a decreased noise margin for signal transition, and makes transistor more vulnerable to supply voltage degradation. So efficient verification of power integrity becomes critical for final design power integrity closure.

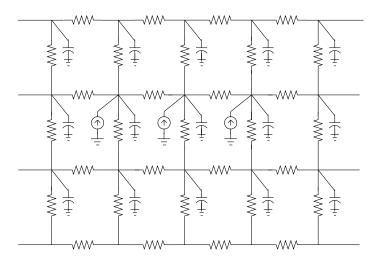

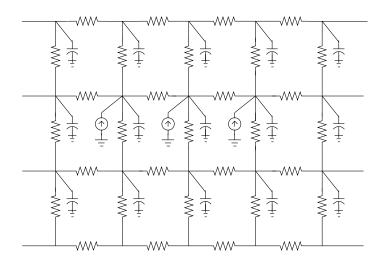

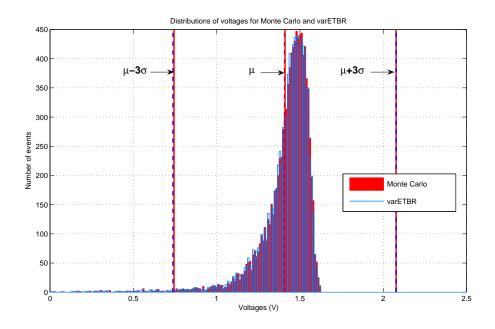

The power delivery networks used in most of the research can be modeled as RC/RLC networks, as shown in Fig. 1.1 which is a part of large power grid networks. There are known time-variant current sources inside the power grid networks. Those current sources can be obtained by gate level logic simulations of the circuits. Some nodes having known

voltage are modeled as constant voltage sources.

Figure 1.1: The power grid model.

Many research works have been done on efficient simulation of on-chip power grid networks. Methods such as multigrid-like [48, 73], hierarchical [83, 32], partition-based [37], fast iterative [9, 67] and random walk based [59] help improve scalability of power gird network analysis. Extended Krylov subspace based methods (EKS) [79, 32] uses both a power grid system and its input signals to reduce the original circuits before the simulation. Due to efficiency of Krylov subspace based reduction techniques, EKS can deal with very large power grid circuits.

Another issue for reliable on-chip power delivery is the increasing process-induced variability [62, 46]. The process induced variations manifest themselves at different levels (wafer level, die-level and within a die) and they are caused by different sources (lithograph, materials, aging etc) [10, 45]. One of the process variabilities comes from the voltage drop variations in on-chip power distribution networks. Voltage drop has significant impacts on the circuit timing [51]. The voltage drop of power grid networks subject to leakage current variations was first studied in [16, 17]. In [72, 50], impulse responses are used

to compute the mean and variances of node voltage responses caused by general current variations. Methods proposed in [20, 19] use orthogonal polynomial chaos expansion of random processes to represent and solve for the stochastic responses of linear systems. The methods have been improved by the StoEKS method [42, 41], where reduction is performed on the variational circuit matrices before the simulation.

# 1.1.2 Modeling and simulation of temperature profile on multi-core microprocessors

As CMOS technology is scaled into the nanometer region, the power density of high-performance microprocessors has increased drastically. The exponential power density increase will in turn lead to average chip temperature to raise rapidly [5]. Higher temperature has significant adverse impacts on chip package cost, performance, and reliability. Excessive on-chip temperature leads to slower transistor speed, more leakage power consumption, higher interconnect resistance, and reduced reliability [22, 6, 52].

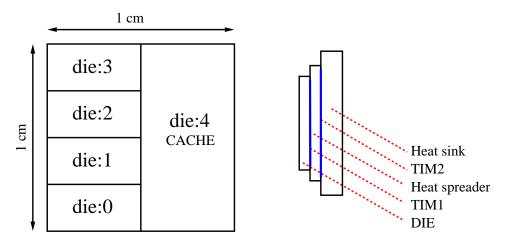

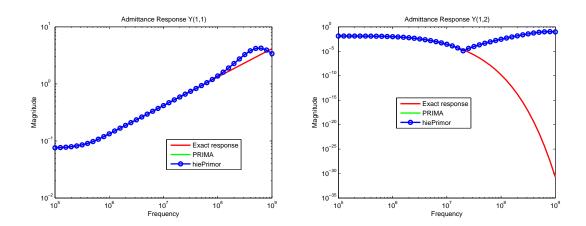

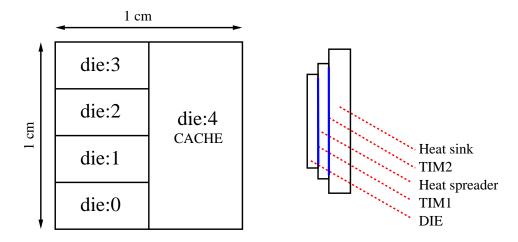

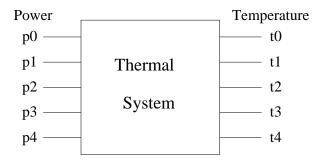

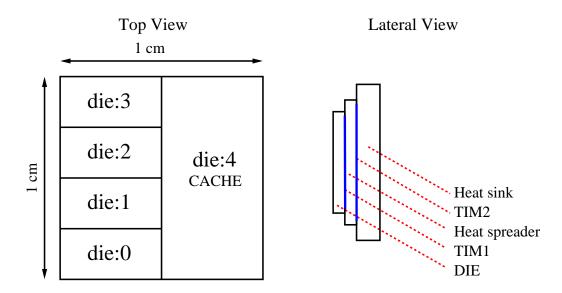

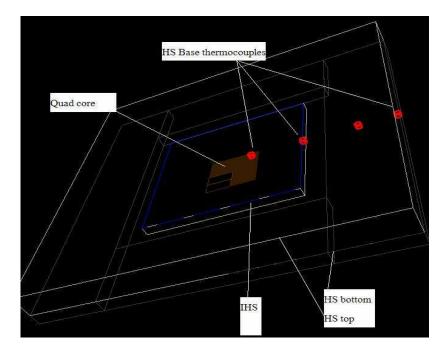

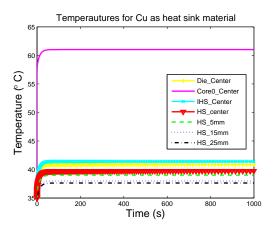

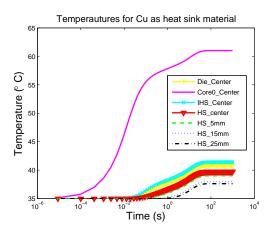

Multi-Core techniques, where multiple CPU-cores and caches are integrated into a single chip, provide a viable solution to the temperature/power problems [38, 3, 4]. The architecture of the Intel Quad-Core microprocessor is shown in Fig. 1.2, where there are four CPU cores (die 0 to die 3) and one shared cache core (die 4). TIM here stands for thermal interface material.

Multi-Core processing allows one to increase the total throughput by task-level parallel computing with lower voltage and frequency to meet power and thermal constraints. The proliferation of this technique provides both opportunities and challenges for future massive parallel computing. One difficult issue confronting designers is the unpredictable heat and thermal effects, which are caused by the placement of cores and caches and changing

Figure 1.2: The quad-core architecture.

program loads. Furthermore, local hot spots, which may have much higher temperatures compared to the average die temperature, are becoming more prevalent in microprocessor chips [52]. This is especially the case for multicore processors as the temperature in each core can be dramatically different and the resulting large temperature gradients can produce mechanical stress and degrade the chip reliability. Hence it is very important to verify the temperatures and estimate the related performance (power, timing, yield) and reliability limits during the thermal-aware floorplanning and architecture design under various loads among different cores and caches [71].

To facilitate this temperature-aware architecture design, it is important to have accurate and fast thermal estimation at the architecture level [27]. Both architecture and CAD tool communities are currently lacking accurate and practical tools for thermal architecture modeling. Existing work on the HotSpot project [26, 71] tried to solve this problem by generating the architecture thermal model in a bottom-up way based on the floorplanning of the function units. But this method may not be accurate for real industry designs as many approximations are made during the modeling. It may also difficult to set up for new architectures with different thermal and packaging configurations [81]. To compute the

thermal responses by solving the basic thermal transfer equations using numerical methods like the finite element method, finite difference method is very expensive, especially for different thermal conditions and package configurations during the design stage. Hence, the need for efficient, accurate, and parameterized architecture thermal models, especially for emerging multicore microprocessors has never been greater.

# 1.2 Objectives and main results of this dissertation

The main objectives of this dissertation is to develop new modeling and simulation methods for on-chip power delivery networks and temperature profile on multi-core microprocessors. The major achievements accomplished in this dissertation as follows:

- A new model order reduction based simulation approach, called ETBR (Extended Truncated Balanced Realization), is proposed. In ETBR, both a system and its input signals are used to reduce the original circuit matrices. But different from the (improved) extended Krylov subspace methods, EKS/IEKS [79, 32], ETBR performs singular value decomposition (SVD) on response Gramian to reduce the original system while with the similar computation costs as EKS and a more accurate reduction framework: truncated balanced realization.

- We extend ETBR to ETBR\_IR for efficient IR drop analysis based on the sampling-based reduction and simulation framework. ETBR\_IR tries to dynamically compensate error losses from the reduction during the simulation process of reduced models. It introduces an error check mechanism based on the system residuals, which is an exact error indicator, as well as the novel effective resistance concept to compute the errors in terms of more useful voltage drop values.

- For large power grid network analysis considering process variations, a new scalable statistical simulation approach, called varETBR, is proposed To consider the variational parameters, we extend the concept of response Grammian proposed in ETBR to the variational response Grammian. Then Monte Carlo based numerical integration is employed to multiple-dimensional integrals. varETBR is very scalable for large networks with a large number of random variables.

- To speedup the MOR (Model Order Reduction) process used in the fast simulation, a hierarchical Krylov subspace projection based MOR approach, hiePrimor, is proposed. It combines the partitioning strategy and the Krylov subspace method to speed up the reduction process. hiePrimor is a very general hierarchical model order reduction technique and it works for general parasitic interconnect circuits modeled as RLC circuits.

- A new thermal behavioral modeling approach, called ThermPOF, is proposed for fast temperature estimation at the architecture level for multi-core microprocessors. ThermPOF builds the transfer function matrix from the measured or simulated thermal and power information. It improves generalized pencil-of-function (GPOF) method [24, 25, 64] to extract the poles and residues of the transfer functions. Further, the size of thermal models can be reduced by a Krylov subspace reduction method to speedup the simulation process [77]. ThermPOF is a top-down, black-box approach, meaning it does not require any internal structure of the systems and it is very general and flexible.

- We extend ThermPOF into ParThermPOF, a parameterized dynamic thermal behavioral modeling approach for emerging thermal-related analysis and optimization

problems for high-performance multi-core microprocessor design. ParThermPOF consists of two steps: first, a Response Surface Method (RSM) based on low-order polynomials is applied to build the parameterized models at each time point for all the given sampling nodes in the parameter space (except for time). Second, ThermPOF is employed to build the transfer-function-based models for each time-varying coefficient of the polynomials generated in the first step.

# 1.3 Organization of this dissertation

The organization of this dissertation is as follows: In Chapter 2, we first propose a new fast simulation method ETBR (Extended Truncated Balanced Realization) for on-chip power delivery network. To make ETBR more accurate, we then extend ETBR into ETBR\_IR with an error control mechanism. For large power grid network analysis considering process variations, we propose a novel scalable statistical simulation approach, called varETBR, in Chapter 3. Then, in Chapter 4, we propose a new hierarchical Krylov subspace based reduction method, called hiePrimor, to speed up the traditional reduction process for RC/RLC circuits. In Chapter 5 and Chapter 6, we investigate a new architecture-level dynamic thermal characterization problem from a behavioral modeling perspective to address the emerging thermal related analysis and optimization problems for high-performance multi-core microprocessor design. We propose a new approach, called ThermPOF, to build the thermal behavioral models from the measured or simulated thermal and power information at the architecture level. And then we extend ThermPOF into ParThermPOF, a parameterized thermal behavioral modeling approach that can handle different parameters in multi-core microprocessor design and optimization. Finally Chapter 7 concludes the dissertation.

# Chapter 2

**ETBR: Extended Truncated Balanced**

Realization for On-Chip Power Grid

**Network Analysis**

In this chapter, we propose a novel model order reduction based simulation approach. This approach, called ETBR, performs singular value decomposition (SVD) on response Gramian to reduce the original system while with the similar computation costs of EKS/IEKS [79, 32]. ETBR is based on a more accurate reduction framework: truncated balanced realization, which was shown to be more accurate than Krylov subspace method used in EKS/IEKS method.

The proposed method is very amenable for threading-based parallel computing, as the response Gramian, which is used to construct the projection matrix, is computed in a Monte-Carlo-like sampling style and each sampling can be computed in parallel. This contrasts with all the Krylov subspace based methods like the EKS method, where moments have to be computed in a sequential order. The feature is important as the multi-core

architectures and multi-core computing are becoming commonplace [30, 70]. ETBR can naturally exploit task-level threading-oriented parallelism based on multicore architectures to significantly boost the simulation performance. ETBR also avoids the explicit moment representation of the input signals, which have well-known numerical problems in the past. Instead, it uses spectrum representation of input signals by fast Fourier transformation. As a result, ETBR is much more flexible for different types of input sources and can better capture the high frequency contents than EKS and this leads to more accurate results for fast changing input signals. Numerical examples, on a number of large RLC networks up to one million nodes, show that ETBR is indeed more accurate than the EKS/IEKS method especially for current sources rich in high-frequency components. ETBR also shows similar computational costs of EKS but smaller memory footprint in a single CPU, but is much faster than EKS when parallelism is explored.

Then we propose an efficient IR drop analysis approach, called ETBR\_IR, based on the sampling-based reduction and simulation framework. The new approach tries to dynamically compensate error losses from the reduction during the simulation process of reduced models. ETBR\_IR introduces an error check mechanism based on the system residuals, which is an exact error indicator, as well as the novel effective resistance concept to compute the errors in terms of more useful voltage drop values. The on-the-fly error reduction works well for compensating high frequency accuracy loss related to disruptive tap current waveforms in typical industry power grid networks. The new method also presents a new way to closely combine model order reduction and simulation to achieve the overall efficiency of simulation. The proposed method provide an efficient way to easily trade errors for speedup to suit different applications. Numerical examples show the proposed IR drop analysis method can significantly reduce the errors of the existing ETBR method,

and meanwhile it can lead to up 10X speedup over the the latest commercial power grid simulator, UPS, in UltraSim, with about 1-2% errors on a number of real industry circuits.

# 2.1 Power grid network models

The power grid networks in this chapter are modeled as RC networks with known time-variant current sources, which can be obtained by gate level logic simulations of the circuits. Fig. 2.1 shows the power grid models used in this chapter. For a power grid, some nodes having known voltage are modeled as constant voltage sources. For C4 power grids, the known voltage nodes can be internal nodes inside the power grid. Given the tap current source vector, u(t), the node voltages can be obtained by solving the following differential equations, which is formulated using modified nodal analysis (MNA) approach,

$$Gv(t) + C\frac{dv(t)}{dt} = Bu(t)$$

$$y(t) = L^{T}v(t)$$

(2.1)

where  $G \in R^{n \times n}$  is the conductance matrix,  $C \in R^{n \times n}$  is the matrix resulting from storage elements. v(t) is the vector of time-varying node voltages and branch currents of voltage sources. y(t) is the observed output voltage vector. u(t) is the vector of independent power sources, and  $B \in R^{n \times p}$  is the input selector matrix and  $L \in R^{n \times l}$  is the output selector matrix. p and l are the number of input and output terminals respectively.

Figure 2.1: The power grid model used.

## 2.2 New extended balanced truncation method: ETBR

In this chapter, we propose an extended truncated balanced realization method, called ETBR, for efficient simulation of power grid networks. The new method features two improvements over existing approaches. First, the input signals are represented in its spectrum form in frequency domain directly by fast Fourier transformation. Second, fast balanced truncation method is used to perform the reduction, which has global accuracy [43, 56].

In the following, we first review the balanced truncation method and then the fast Gramian computation method.

#### 2.2.1 Review of standard TBR

Given a system in a standard state-space form

$$\dot{x}(t) = Ax(t) + Bu(t)

y(t) = Cx(t)$$

(2.2)

where  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times p}$ ,  $C \in \mathbb{R}^{p \times n}$ , y(t),  $u(t) \in \mathbb{R}^{p}$ . The controllable and observable Grammians are the unique symmetric positive definite solutions to the Lyapunov equations.

$$AX + XA^{T} + BB^{T} = 0$$

$A^{T}Y + YA + C^{T}C = 0$  (2.3)

Since the eigenvalues of the product XY are invariant under similarity transformation, we can perform a similarity transformation  $(A_b = T^{-1}AT, B_b = T^{-1}B, C_b = CT)$  to diagonalize the product XY such that

$$T^{-1}XYT = \Sigma = diag(\sigma_1^2, \sigma_2^2, \dots, \sigma_n^2)$$

(2.4)

where the Hankel singular values of the system  $(\sigma_k)$ , are arranged in a descending order. If we partition the matrices as

$$\begin{bmatrix} W_1^T \\ W_2^T \end{bmatrix} XY \begin{bmatrix} V_1 & V_2 \end{bmatrix} = \begin{bmatrix} \Sigma_1 & 0 \\ 0 & \Sigma_2 \end{bmatrix}$$

(2.5)

where  $\Sigma_1 = diag(\sigma_1^2, \sigma_2^2, \dots, \sigma_r^2)$  are the first r largest eigenvalues of Gramian product XY and  $W_1$  and  $V_1$  are corresponding eigenvectors. A reduced model can be obtained as follows

$$\dot{x}(t) = A_r x(t) + B_r u(t)

y(t) = C_r x(t)$$

(2.6)

where  $A_r = W_1^T A V_1$ ,  $B_r = W_1^T B$ ,  $C_r = C V_1$ . The error in the transfer function of the order r approximation is bounded by  $2\sum_{i=r+1}^N \sigma_k$ . In the TBR procedure, the computational cost is dominated by solving Lyapunov equations  $O(n^3)$ , which makes it too expensive to

apply to integrated circuits problems and thus an efficient Gramian approximation technique is highly appreciated.

#### 2.2.2 Review of fast TBR method: Poor man's TBR

Existing Gramian approximation technique, PMTBR [55], is restricted to a state-space model (2.2) with  $A = A^T$  and  $C = B^T$ . This is the case for RC and RL circuits. In this symmetric case, it is easy to see that, both Gramians are equal and are obtained by solving the Lyapunov equation

$$AX + XA^T + BB^T = 0 (2.7)$$

Since X is symmetric, it is orthogonally diagonalizable, i.e., there exists  $T^{-1} = T^T$  such that  $T^T X T = \Sigma$ . Then, we have

$$T^T X X T = (T^T X T)(T^T X T) = (\Sigma)^2$$

(2.8)

which means, in this symmetric case, the eigenspace of Gramian product XX is exactly the eigenspace of each X and we only need to find the dominant invariant subspace of an approximated Gramian  $\hat{X}$ . In frequency domain, the Gramian X can also be computed from the expression

$$X = \int_{-\infty}^{+\infty} (j\omega I - A)^{-1} B B^{T} (j\omega I - A)^{-H} d\omega$$

(2.9)

where superscript H denotes Hermitian transpose. Let  $\omega_k$  be kth sampling point. If we define

$$z_k = (j\omega_k I - A)^{-1}B (2.10)$$

then X can be approximated as

$$\hat{X} = \sum w_k z_k z_k^H = ZW^2 Z^H \tag{2.11}$$

where  $Z = [z_1, z_2, \dots, z_n]$ . W a diagonal matrix with diagonal entries  $w_{kk} = \sqrt{w_k}$ .  $w_k$  comes from a specific numerical quadrature method. Since  $\hat{X}$  is symmetric, it is orthogonally diagonalizable.

$$\hat{V}^T \hat{X} \hat{V} = \begin{bmatrix} \hat{V}_1^T \\ \hat{V}_2^T \end{bmatrix} \hat{X} \begin{bmatrix} \hat{V}_1 & \hat{V}_2 \end{bmatrix} = \begin{bmatrix} \hat{\Sigma}_1 & 0 \\ 0 & \hat{\Sigma}_2 \end{bmatrix}$$

(2.12)

where  $\hat{V}^T\hat{V}=I$ .  $\hat{V}$  converges to the eigenspaces of X and the dominant eigenvectors  $\hat{V}_1$  can be used as the projection matrix in a model reduction approach  $(A_r=\hat{V}_1^TA\hat{V}_1,B_r=\hat{V}_1^TB)$ .

## 2.2.3 Response Gramian and fast computation method

Follow the similar strategy of EKS method, we consider the input signals of the system into TBR based reduction framework so that efficient reduction can be done by converting an MIMO system into an SIMO system.

For a linear system in (2.1), we first define the frequency-domain *Response Gramian*,

$$X_r = \int_{-\infty}^{+\infty} (j\omega C + G)^{-1} Bu(j\omega) u^T(j\omega) B^T(j\omega C + G)^{-H} d\omega$$

(2.13)

which is different from the Gramian concepts in the traditional TBR based reduction framework. Notice that in the new Gramian definition, the input signals  $u(j\omega)$  is considered. As

a results,  $(j\omega C+G)^{-1}Bu(j\omega)$  actually is the system response with respect to the input signal  $u(j\omega)$  and resulting  $X_r$  becomes response Gramian.

To fast compute the response gramian  $X_r$ , which essential essentially one-dimensional integral with respect to the complex frequency  $\omega$ . We can use Monte-Carlo-based method to estimate the numerical value as done in [53]. Specifically, let  $\omega_k$  be kth sampling point over the frequency range. If we further define

$$z_k^r = (j\omega_k C + G)^{-1} Bu(j\omega_k)$$

(2.14)

then  $\hat{X}$  can be computed approximately by numerical quadrature methods

$$\hat{X}_r = \sum_k w_k z_k^r z_k^{rH} = Z_r W^2 Z_r^H$$

(2.15)

where  $Z_r$  is a matrix whose columns are  $z_k^r$  and W a diagonal matrix with diagonal entries  $w_{kk} = \sqrt{w_k}$ .  $w_k$  comes from a specific quadrature method.

For the truncated balanced based reduction, we need to compute the eigen-composition of  $\hat{X}_r$  to obtain the projection matrix, which consists of eigen vectors of  $\hat{X}_r$ . Since the approximate Gramian  $\hat{X}_r$  is symmetric, we can obtain the project matrix by singular value decomposition of  $Z_r$ . To see this, if we have SVD of  $Z_r = V_r S_r U_r^T$ , then we can have the eigen decomposition of  $\hat{X}_r = V_r S_r^2 V_r^T$ . After this, we can reduce the original matrices into small ones and then perform the transient analysis on the reduced circuit matrices.

Also we find that weights  $w_k$  are not important for the SVD process. The weight matrix W will not change the subspace of  $Z_r$  as it simple multiplies each vector in  $Z_r$  with a constant. In our algorithm, we just simple ignore the weights and we use simple linear or logarithmic sampling methods to perform the sampling (to be discussed later).

Notice that we need frequency response of input signal  $u(j\omega_k)$  in (2.14). This can be obtained by fast Fourier transformation on the input signals in time domain.

#### 2.2.4 Extended truncated balanced realization method: ETBR

In this subsection, we give the algorithm flow of the proposed ETBR method, which is summarized in *Algorithm* 1.

**Algorithm 1: Extended Truncated Balanced Realization method (ETBR)**

**Input:** Circuit of G, C, B, u(t), number of samples: q, transient simulation step interval.

**Output:** Node voltage responses v(t) for the given simulation interval.

- 1. Convert all the input signals u(t) into u(s) using FFT.

- 2. Select q frequency points  $s_1, s_2, \ldots, s_q$  over the frequency range

- 3. Compute  $z_k^r = (s_k C + G)^{-1} B u(s_k)$

- 4. Form the matrix  $Z_r = [z_1^r, z_2^r, \dots, z_q^r]$

- 5. Perform SVD on  $Z_r$ ,  $Z_r = V_r S_r U_r^T$

- 6.  $\hat{G} = V_r^T G V_r, \hat{C} = V_r^T C V_r, \hat{B} = V_r^T B$

- 7. Simulate  $(\hat{G}, \hat{C}, \hat{B}, u(t))$

- 8. Obtain the original waveforms  $v(t) = V_r v(t)$

Note that, like the EKS method, we use congruence transformation for the reduction process with orthogonal columns in the projection matrix (using Arnoldi or Arnoldi-like process), the reduced system must be stable. As far as simulation is concerned, this is good enough. If all the observable ports are also the current source nodes, i.e.  $y(t) = B^T v(t)$ , where y(t) is the voltage vector at all observable ports, the reduced system is passive.

Compared with the existing approaches like EKS/IKES methods, ETBR shows several advantages and features. First ETBR method is much more amenable for parallel computing than EKS as each  $z_i^k$  in (2.14) can be computed in parallel. Thus ETBR is more efficient than EKS when the threading-based parallel computing is explored as shown in

the Numerical examples. Second, it is more accurate over wide band frequency ranges due to the global samplings. Third, it avoids the explicit moment representation of the input signals, which can lead more accurate results than the EKS method when signals are rich in high frequency components. ETBR can deal with any type of time-domain and frequency-domain input signals. While the EKS method can only deal with input signals in piecewise linear form.

## 2.2.5 Time complexity analysis and comparison

In this subsection, we analyze the computational costs for both ETBR and EKS and compare with the EKS methods.

In ETBR, there are two major computing steps, sampling and SVD. Let's look at the cost of each step. For sampling, we basically need to solve the (2.14) q times. Typically solving a  $n \times n$  linear matrix takes  $O(n^{\beta})$  (typically,  $1.1 \le \beta \le 1.5$  for matrix factorizations and  $O(n^{\alpha})$  (typically,  $1 \le \alpha \le 1.2$ ) for solving (forward and backward substitutions). So the time complexity for this step is  $O(qn^{\beta} + qn^{\alpha})$ . For the second step, the singular value decomposition (SVD) will take  $O(nq^2)$  for a  $n \times q$  matrix. Another computing cost comes from converting the input signals into the frequency spectrum form. Assume that we have m current sources, the samplings we use for the FFT is l, FFT takes  $O(l\log l)$  to finish. Hence the cost associated with input signals is  $O(ml\log l)$ . Typically we set l=128, which gives sufficient accuracy. So the total computational cost of ETBR is

$$O(qn^{\beta} + qn^{\alpha} + nq^2 + ml\log l). \tag{2.16}$$

If all the sampling can be computed in parallel, computing (2.14) will become  $O(n^{\beta} + n^{\alpha})$

assuming very small overheads incurred to manage the threads. The total computational cost of ETBR will become

$$O(n^{\beta} + n^{\alpha} + nq^2 + ml\log l). \tag{2.17}$$

For one-point (expanded at one frequency point) EKS, it also have two major computing costs: compute the response moments and orthonormalize them similar to the QR decomposition. For the first step, it will take one matrix factorization and q steps solving (forward and backward substitutions). The computing cost is  $O(qn^{\alpha} + n^{\beta})$ , where  $O(qn^{\alpha})$  (typically,  $1 \le \alpha \le 1.2$  for sparse circuits) is q step solving. The orthonormalization will take about  $O(nq^2)$  to finish. Again, we need to calculate the computing cost for transforming the input signals into the moment form. It can be shown that the computing cost is  $O(qk^2m)$  [32], where k is the number of piecewise segments in each current sources, and m the number of current sources. Hence the final computational cost for EKS is

$$O(qn^{\alpha} + n^{\beta} + nq^2 + qk^2m) \tag{2.18}$$

It can be seen that EKS will be more efficient due to smaller number of factorizations in a single CPU. But if parallel computing is allowed, ETBR become much better. But if iteration solvers are used, which are typically more fast and memory efficient than the LU-based direct solvers for RLC networks [63], both approaches will have the same computational costs in a single CPU.

#### 2.2.6 Statistical point of view

The proposed method in a sense can be viewed as special SVD-based principal component analysis (PCA) method used in statistical variable reduction transformation.

For a linear dynamic system formulated in state space equations (MNA) in (2.1), if complex frequency s is a vector of random variables with uniform distribution in the frequency domain. Then the state responses  $V(s) = (G + sC)^{-1}Bu(s)$  become random variables in frequency domain. Its covariance matrix can be computed as

$$E\{V(s)V(s)^{T}\} = X_{r}$$

(2.19)

where  $E\{x\}$  stands for computing the mean of random variable x.  $X_r$  is defined in (2.13). The response Gramian essentially can be viewed as the covariance matrix associated with state responses. ETBR procedure performs the principal component analysis transformation of the mentioned random process with a uniform distribution.

# 2.3 Numerical examples of ETBR

The proposed ETBR algorithm has been implemented using MATLAB 7.0 and tested on an Intel Xeon 3.0GHz dual CPU workstation with 2GB memory and an Intel quad-core 3.0GHz CPU workstation with 16GB memory. All the test circuits are randomly generated RC or RLC power grid networks up to one million nodes (R on the order of  $\Omega$ , C on the order of pF and L on the order of pH), as shown in Table 2.1. Efficient matrix computations benefit from sparse matrix structure and a parser implemented by Python.

To solve circuits with one million nodes in MATLAB, an external linear solver package

Table 2.1: Test circuits Test Ckts #Nodes **#Sources** Ckt1 1,000 100 Ckt2 10,000 100 Ckt3 10,000 1,000 Ckt4 100,000 1,000 Ckt5 100,000 4,000 Ckt6 500,000 5,000 20,000Ckt7 500,000 Ckt8 1,000,000 50,000 100 Ckt9 (RLC) 6,000 Ckt10 (RLC) 250,000 100

UMFPACK [2] is used, which is linked with MATLAB using MATLAB mexFunction. For ETBR, we use a non-LU-decomposition solver in UMFPACK. While for EKS, the LU decomposition solver is used. The reason why we choose different solver for them is ETBR only solves one column in the right hand side, so LU decomposition may cost too much and cannot be reused in ETBR. While in EKS, LU decomposition can be reused to solve several columns in the right hand side, number of columns depending on the selected reduced order, so doing LU decomposition is an efficient way in EKS. We remark that the selection of solvers is the best for both ETBR and EKS. The comparison is more fair for them.

# 2.3.1 Comparison with the EKS method

In sequel, we will compare our ETBR with IEKS [32], first in accuracy and then in CPU times. In all the test cases, to make a fair comparison, the reduction order q is set to 6 for IEKS and the number of frequency samples used for ETBR is also set to 6. Note that for the RLC circuits Ckt1-Ckt8, the results are collected on an Intel dual CPU workstation

with 2GB memory, and for the RLC circuits Ckt9 and Ckt10, the results are collected on an Intel quad-core workstation with 16GB memory.

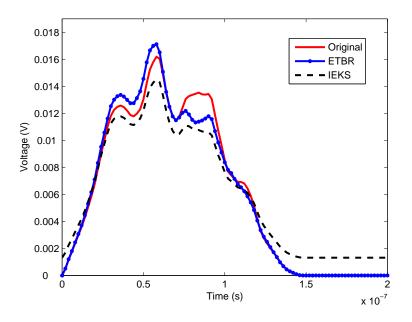

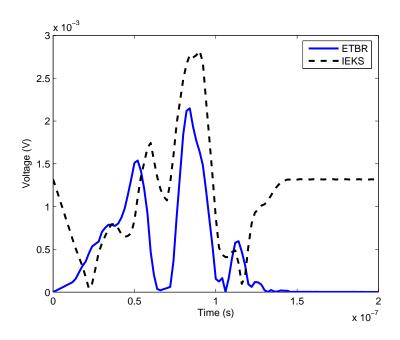

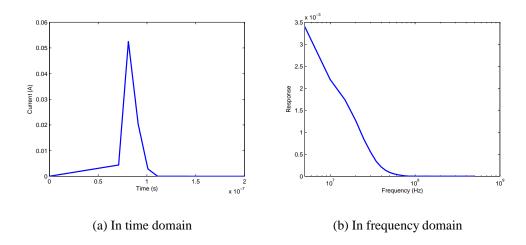

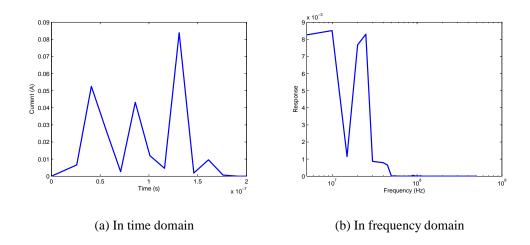

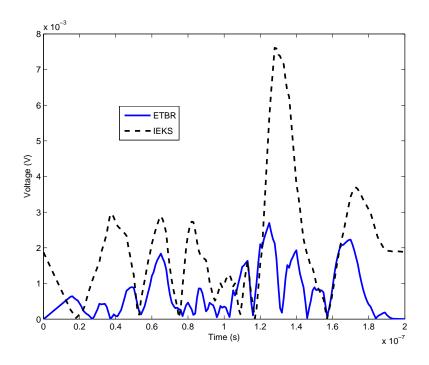

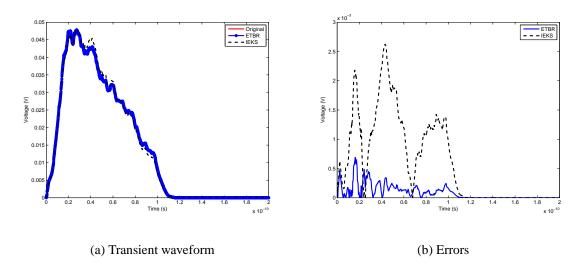

Fig. 2.2 shows the simulation results of ETBR and IEKS at the 200th node of Ckt2. The simulation errors compared with SPICE results are shown in Fig. 2.3. One of the input signal waveforms in both time domain and frequency domain is as shown in Fig. 2.4. Through Fig. 2.3, we can see that ETBR is more accurate than IEKS over the entire simulation time.

Figure 2.2: Transient waveform at the 200th node of Ckt2.

In the second testing case, we change the input signals so that they can have more fast changing spikes as shown in Fig. 2.7(a). In other words, current sources are rich in high-frequency components.

We find that ETBR's results are much better than EKS's as shown in Fig. 2.5. From the simulation errors comparison in Fig. 2.6, we can see that ETBR is almost  $3 \times$  more accurate than IEKS (the maximum error: ETBR 0.003 vs IEKS 0.01). This is not a surprise for us if we notice that the input signals shown in Fig. 2.7(b) have much more high frequency

Figure 2.3: The simulation errors of ETBR and IEKS of Ckt2.

Figure 2.4: Transient waveform at the 5th current source of Ckt2.

components from  $10^7 \mathrm{MHz}$  to  $10^8 \mathrm{MHz}$  than the input signals shown in Fig. 2.4(b).

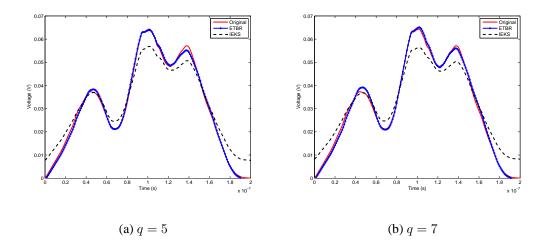

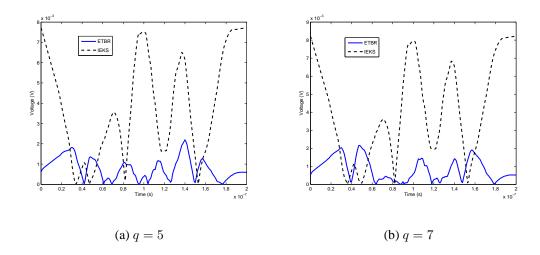

We can try different reduced orders for Ckt2 to set q=5 and q=7. The results are shown in Fig. 2.8 and Fig. 2.9. We can see that ETBR is still more accurate than EKS as long as both of them use the same reduced order. And the CPU times of ETBR depends on the reduced order. If we want to achieve more accuracy, we need more reduced orders

Figure 2.5: Transient waveform at the 200th node of Ckt2 with fast changing inputs.

Figure 2.6: The simulation errors of ETBR and IEKS on Ckt2 with fast changing inputs. which results in more CPU times.

For the RLC circuits, ETBR also holds much more accuracy than EKS. Fig. 2.10 and Fig. 2.11 show the transient simulation waveforms and errors of both ETBR and EKS at

Figure 2.7: The transient waveform at the 5th current source of Ckt2.

Figure 2.8: Transient waveform at the 200th node of Ckt2 with fast changing inputs. the 200th node of Ckt9 (RLC).

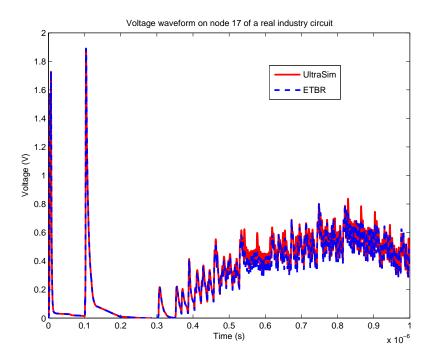

There may be many high frequency components in the input signals in the real industry circuits. In this situation, we in general need more samplings to improve the accuracy. Now we perform ETBR on a real industry circuit of 154514 nodes, 624 current sources and 25001 simulation time steps. We also perform latest UltraSim UPS (power network solver) on the same case. UltraSim UPS is a commercial power grid simulator from Cadence

Figure 2.9: The simulation errors of ETBR and IEKS on Ckt2 with fast changing inputs.

Figure 2.10: Transient waveform at the 200th node of Ckt9 (RLC).

and the results of UltraSim UPS are considered as golden in this chapter. The number of samplings in ETBR is still set to 10. But still the results are accurate enough as shown in Fig. 2.12. This circuit has rapid changing transient waveforms due to the reason that the

Figure 2.11: The simulation errors of ETBR and IEKS on Ckt9 (RLC).

Figure 2.12: Transient waveform at node 17 of a real industry circuit.

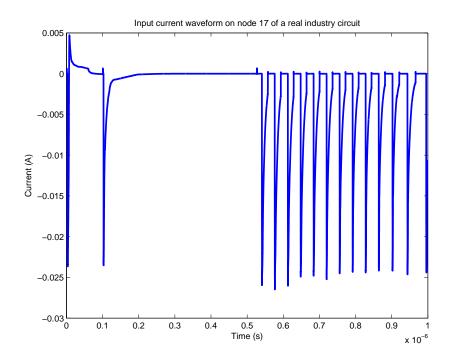

Figure 2.13: Input current waveform at node 17 of a real industry circuit.

current sources are changing very fast, as shown in Fig. 2.13.

Finally, we compare the CPU time of the two algorithms on a set of power grid networks up to one million nodes. The capacity of our implementation is mainly limited for Ckt1-Ckt8 by the physical memory of our machine (2GB).

Table 2.2 shows the CPU times of both ETBR (including the cost of FFT) and IEKS on the given set of circuits using the same reduction order q=6. "—" means out-of-memory error. We find that EKS is a bit faster for small circuits. But for Ckt6 and larger circuits, the CPU times are almost the same for both methods. For the largest circuit Ckt8, EKS cannot even finish owning to the memory constraint; while ETBR runs through all the circuits. This clearly shows that ETBR is more memory efficient by using a non-LU decomposition solver than EKS.

Table 2.3 shows the CPU times if parallelism is explored in ETBT. PETBR means par-

Table 2.2: CPU times (in seconds) comparison of ETBR and IEKS (q = 6)

| Test Ckts   | ETBR (s) | EKS (s) |

|-------------|----------|---------|

| Ckt1        | 0.23     | 0.08    |

| Ckt2        | 1.28     | 0.89    |

| Ckt3        | 1.8      | 1.4     |

| Ckt4        | 20.4     | 18.8    |

| Ckt5        | 28.6     | 25.3    |

| Ckt6        | 152      | 151     |

| Ckt7        | 162      | 160     |

| Ckt8        | 562      | _       |

| Ckt9 (RLC)  | 0.20     | 0.11    |

| Ckt10 (RLC) | 6.5      | 4.4     |

Table 2.3: CPU times (in seconds) comparison of ETBR, parallelized ETBR and IEKS (q = 10)

| Test Ckts | # Nodes   | # Sources | ETBR | PETBR | EKS |

|-----------|-----------|-----------|------|-------|-----|

| Ckt11     | 1,750,000 | 25,000    | 232  | 32    | 355 |

| Ckt12     | 3,400,000 | 50,000    | 514  | 68    | 640 |

| Ckt13     | 7,000,000 | 100,000   | 1349 | 167   | _   |

allelized ETBR. The results are collected on an Intel quad-core (3GHz CPU) workstation with 16GB memory. We assume that Step 3 in *Algorithm* 1 can be fully parallelized. So the total CPU time of parallelized ETBR is the max CPU time out of all the sub-processes in parallelized Step 3 plus CPU time of serial parts in ETBR, such as FFT and SVD. For Krylov subspace method, such as EKS/IEKS, each moment is computed based on previous one, hence it is hardly to be parallelized. We can see that ETBR is now is a order of magnitude faster than EKS and ETBR.

## 2.3.2 Results on circuits with many different switching timings

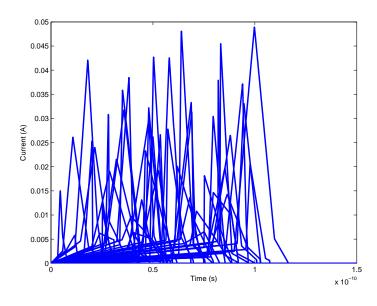

In this subsection, we show the results of ETBR and EKS are also very accurate for power grid circuits excited by input currents with many different switching timings (peaks).

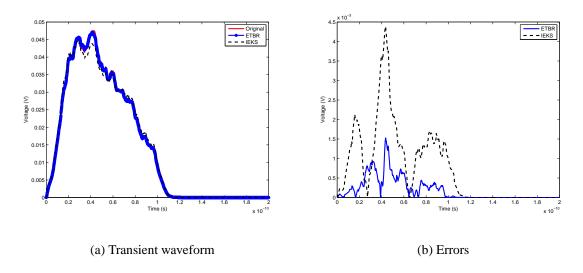

The used benchmark circuit has 1000 nodes and each node has a current source, which switches at a different time (the peaks are different for each of them) as shown in Fig. 2.14. The resistor and capacitor values of this circuit are randomly generated. R is on the order of  $10^{-2}\Omega$ , and C is on the order of  $10^{-15}$ F. The capacitance is really small. Fig. 2.15 and Fig. 2.16 show the simulation waveforms and errors on 100th and 300th nodes (q = 5). We can see ETBR is still very accurate.

We remark that if the circuit has very small capacitances such that the whole circuit become DC with respect to their input signal spectrum, then both ETBR and model order reduction in general cannot be applied in this case. But this is a very unrealistic case for general interconnect circuits modeled as RLC/RLCK circuits.

Figure 2.14: Transient waveforms of current sources switching at different time

Figure 2.15: The transient waveform and errors at the 100th node (q = 5).

Figure 2.16: The transient waveform and errors at the 300th node (q=5).

# 2.4 IR drop analysis problem

The power grid networks in this charpter are modeled as RC networks with known timevariant tap current sources as shown in 2.1, which can be obtained by gate level logic simulations of the circuits under assumption that transistor circuit simulation and power grid network simulation are separated. Such RC model is still valid at least for the on-chip level power grid networks for current technologies [47].

The on-chip power grids, one important integrity issue is excessive voltage IR drops due to the unavoidable wire resistance (and inductive effects when inductance are large). IR drop based power grid integrity analysis is different from the general transient analysis in that designers are mainly interested in the voltage drops in the tap current sources as the tap currents are where the power grid network are connected with the logic circuits and IR drops mainly matter from the logic circuit perspective. As a result in our program L=B and P=1 in (2.1). This implies the passive model order reduction can be achieved and it will also lead to more efficient reduction-based simulation for power grid networks as shown later.

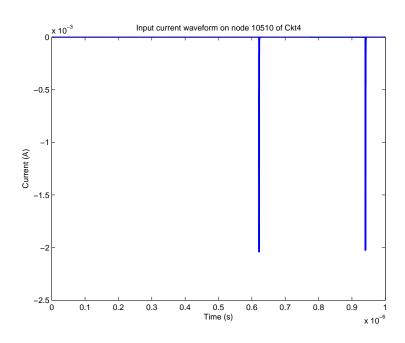

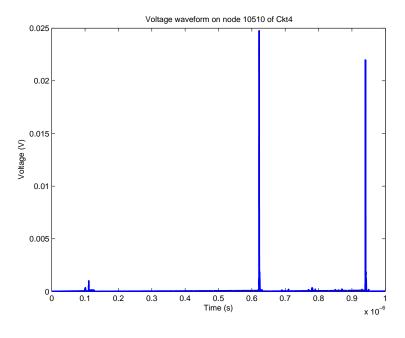

Second, for IR drop analysis, what matter are the excessive voltage drops occurring at a few time instances over the simulation period for each node. This is especially the case for real industry power grid networks, where the tap currents are very disruptive in nature as shown in Fig. 2.17 and so are the IR drops as shown in Fig. 2.18. Fig. 2.19 shows the frequency spectrum of the current shown in Fig. 2.17, which have shapes like sinc functions due to the impulse shapes of currents in time domain.

## 2.5 New reduction based IR drop analysis method

For IR drop analysis, many industry circuits exhibit rapid changing tap current waveforms as shown in Fig. 2.17. Such impulse-like current waveforms will have the frequency spectrum similar to sinc function in frequency domain as shown in Fig. 2.19, which has a long tail and thus is significant across wide frequency range. This requires large number of samplings to make ETBR accurate, which degrades its performance.

Figure 2.17: Input current waveform at the node 10510 of Ckt4 (the first one-tenth).

Figure 2.18: Voltage waveform at the node 10510 of Ckt4 (the first one-tenth).

In this chapter, we propose to reduce the errors during the transient simulation of the reduced models. In the new method, we monitor errors for the transient waveforms from

Figure 2.19: Frequency waveform at the node 10510 of Ckt4 (the first one-tenth).

the reduced model and switch to the original models when errors are large. Our Numerical examples show such large errors typically occur around the large voltage drop (spikes) and the proposed method can accurately estimate large voltage drops while still maintain decent speedup over traditional methods. We first present how errors are estimated in the time domain.

### 2.5.1 Error estimation in the time domain

One important aspect of the proposed method is to have accurate a priori error estimation at each time step  $t_i$ .

We propose to use the residual error information of the original on the states obtained from the reduced models. Specifically, for system (2.1), assume that  $h_i$  is the time step at time  $t_i$  and  $v_r(t_i)$  and  $v_r(t_{i-1})$  are the voltage vectors in the reduced systems at time  $t_i$  and  $t_{i-1}$  after the time discretization. Then we can define the residual error in time domain as

$$R(t_i) = GVv_r(t_i) + (C/h_i)V(v_r(t_i) - v_r(t_{i-1})) - Bu(t_i)$$

(2.20)

$$= (G + C/h_i)Vv_r(t_i) - (C/h_i)Vv_r(t_{i-1}) - Bu(t_i)$$

(2.21)

where  $Vv_r(t_i)$  is an approximation of the original state  $v(t_i)$ , V is the project matrix computed from ETBR and  $V \in R^{n \times q}$ , q is the reduced order. Notice that if  $Vv_r(t_i)$  is exactly equal to  $x(t_i)$ , the residual error should be zero. As a result, the norm of  $R(t_i)$ ,  $||R(t_i)||$  can serve as a good error indicator for the reduced model at  $t_i$ . Practically, we take  $||R(t_i)||_{\infty}$  as the error indicator, which is the maximum absolute value of the element in  $R(t_i)$ .

Notice that we are only interested in the tap current nodes and the largest IR drop must happen in one tap current node. As a result, we do not need to check the all the nodes. The new residual formula considering only tap current nodes becomes

$$R_{tap}(t_i) = B^T(G + C/h_i)Vv_r(t_i) - B^T(C/h_i)Vv_r(t_{i-1}) - B^TBu(t_i)$$

(2.22)

Although  $R(t_i)$  still involves the original matrices G and C, only matrix multiplications are involved. The time complexity of (2.21) is  $O(p \times q)$ , where p is the number of nodes and q is the size of the reduced model.

#### 2.5.2 Effective resistance

The residual definition in (2.22) mainly give the current residual as  $u(t_i)$  mainly contains the tap current sources (with only a few voltage sources normally). However, to effectively

control the errors, we need to know how much voltage errors such as current residuals will cause. As a result, we need to map from the current residual to the voltage residual (difference).

We introduce the effective resistance to perform the mapping. The effective resistance at time  $t_i$  is defined as

$$r_{eff}(t_i) = \frac{\max(v(t_i) - v_{dc}(t_i))}{\max(R_{tap}(t_i))}$$

(2.23)

where max means taking the maximum value of a vector. To compute  $r_{eff}(t_i)$ , we have to know the exact response solved from the original system  $v(t_i)$ . Actually we do not need to compute the effective response at every time step. Instead, we only compute it at the first step and the steps where errors are large and the original solutions are solved.

Our Numerical examples show that the effective resistances are quite consistent through the time steps for each circuit. Fig. 2.20 show the histogram for the effective resistance distribution all over the time steps of Ckt4 in the experimental section. It can seen that the effective resistance is dominated by values around 12. Practically we compute the average effective resistance  $r_{avg}$  all over the effective resistance computed seen so far to estimate the allowed maximum current residual.

## 2.5.3 Dynamic error control

To control the errors, we need to determine the maximum allowed current residual  $i_{r,max}$ . If the  $max(R_{tap}(t_i))$  is larger than  $i_{r,max}$ , the original model will be solved. Otherwise, the reduced model is solved. The  $i_{r,max}$  will be computed as

$$i_{r,max} = \frac{v_{ir,max} \times \alpha_{th}}{r_{avg}} \tag{2.24}$$

Figure 2.20: Effective resistance distribution of Ckt4.

where  $v_{ir,max}$  is the largest IR drop seen so far and  $0 < \alpha_{th} < 1$  is a user-defined threshold specifying the percentage of the allow voltage difference with respect to the largest voltage drop seen so far. Typically  $\alpha_{th}$  is around 0.01 to 0.05.

At the beginning, the maximum voltage drop  $v_{ir,max}$  may be small and it can lead to the necessary solving of the original models. To avoid this problem, the initial current residual is determined by the largest current value,  $I_{max}$ , of all the current sources over all the time steps.

$$i_{r,max} = I_{max} \times \alpha_{th} \tag{2.25}$$

So the actual allowed current residual will take the larger one of the two  $i_{r,max}s$ '.

### 2.5.4 The new IR drop analysis algorithm flow

In this subsection, we summarize all the steps we discuss before. We first present the proposed ETBR\_IR method in *Algorithm* 2.

Algorithm 2: ETBR based IR drop analysis (ETBR\_IR)

**Input:** Circuit of G, C, B, u(t), number of samples: q, transient simulation step interval. **Output:** Max IR drop for the given simulation interval.

- 1. Convert all the input signals u(t) into u(s) using FFT.

- 2. Select q frequency points  $s_1, s_2, \ldots, s_q$  over the frequency range.

- 3. Compute  $z_k^r = (s_k C + G)^{-1} B u(s_k)$ .

- 4. Form the matrix  $Z_r = [z_1^r, z_2^r, \dots, z_q^r]$ .

- 5. Perform SVD on  $Z_r$ ,  $Z_r = V_r S_r U_r^T$ .

- 6.  $\hat{G} = V_r^T G V_r, \hat{C} = V_r^T C V_r, \hat{B} = V_r^T B$

- 7. Solve the ith step  $(\hat{G},\hat{C},\hat{B},u(t))$ , and get  $\hat{v}(t)$ .  $v(t)=V_r\hat{v}(t)$ .

- 8. Substitute v(t) into (G, C), and get right hand side  $w_1$ .  $w = B \times u$ .

- 9. Compute current residual error R = abs(w w1). If  $||R||_{\infty}$  is less than allowed residual  $i_{r,max}$ , then goto step 11, else goto step 10.

- 10. Solve the ith step (G, C, B, u(t)), and get v(t). Update  $r_{avq}$  and  $i_{r,max}$ . Goto step 11.

- 11. Compute max IR drop. i = i + 1. Goto step 7.

- 12. Finish all the time steps and return max IR drop.

In the new algorithm, ETBR\_IR first reduces the original circuits from step 1 to 6 using ETBR method. Then from step 7 to step 11, it performs the simulation on the reduced model. At the same time, it watches out for the error in each time step. If the error is larger than the given voltage IR drop threshold, ETBR\_IR switches the simulation to the original model to get accurate results and then switch back the reduced model for the next step until we finish all the time step.

# 2.6 Numerical examples of ETBR\_IR

The proposed *ETBR\_IR* algorithm has been implemented using C++ and CSparse package [12]. ETBR\_IR has been tested on a workstation with Intel quad-core 2.0GHz CPU and 8GB memory. All the benchmarks are power or ground grids from real industry designs. The statistics are summarized in Table 2.4. In the table, #Nodes means the total number of nodes in one test circuit. #VS means the total number of voltage sources and #IS means the total number of current sources. #Time Steps means the total number of simulation time steps.

In the experimental setting, the  $\alpha_{th}$  is set to 0.05 except for Ckt6 and Ckt7 where  $\alpha_{th}$  is set to 0.01. Also the number of samplings is set to 10 for all the case in *ETBR\_IR*.

Table 2.4: Benchmark circuits Test Ckts #Nodes #VS #IS #Time Steps Ckt1 249475 5177 25001 Ckt2 154514 0 624 25001 Ckt3 60999 20901 250001 1 42222 Ckt4 0 10654 250001 Ckt5 49303 0 48756 79001 Ckt6 70127 28928 100001 1 Ckt7 75758 28048 100001

We compare ETBR\_IR with original ETBR and UltraSim version 7.1, which is a commercial simulation tool from Cadence. UltraSim UPS (UltraSim Power network Solver) is the power grid analysis tool in UltraSim. It is an improved LU solver for power grid network analysis. We consider UltraSim UPS as the standard one, due to the reason that those real industry benchmarks are too large and too challenging for SPICE to solve it. We first show the performance comparison results in Table 2.5.

Table 2.5 shows the performance in CPU seconds of ETBR\_IR, comparing with original

Table 2.5: Performance comparison (CPU seconds) of UltraSim, ETBR and ETBR\_IR

| Test Ckts | UltraSim (s) | ETBR (s) | ETBR_IR (s) | ETBR speedup | ETBR_IR speedup |

|-----------|--------------|----------|-------------|--------------|-----------------|

| Ckt1      | 49653        | 236      | 278         | 210.39       | 178.61          |

| Ckt2      | 6906         | 104      | 122         | 66.40        | 56.61           |

| Ckt3      | 6130         | 350      | 1122        | 17.51        | 5.46            |

| Ckt4      | 3969         | 234      | 629         | 16.96        | 6.31            |

| Ckt5      | 3969         | 551      | 1182        | 7.20         | 3.34            |

| Ckt6      | 6144         | 803      | 1020        | 7.65         | 6.02            |

| Ckt7      | 6523         | 765      | 950         | 8.53         | 6.87            |

| Avg.      |              |          |             | 47.81        | 37.60           |

ETBR and UltraSim. From Table 2.5, we can see ETBR\_IR can finish much faster than UltraSim for Ckt1 and Ckt2. It can archive about 37X speedup in average. We notice that *ETBR\_IR* favors circuits with less current sources as shown for Ckt1 and Ckt2 where we see much higher speedup. This is due to the less time spent on the mapping results from reduced models to the original one. For other cases such as Ckt5 where the #IS is almost equal to #Nodes, ETBR\_IR still can finish 3x faster than UltraSim.

Table 2.6: Accuracy comparison (max IR drop values) of UltraSim, ETBR and ETBR\_IR

| Test Ckts | UltraSim (mV) | ETBR (mV) | ETBR_IR (mV) | ETBR error | ETBR_IR error |

|-----------|---------------|-----------|--------------|------------|---------------|

| Ckt1      | 1087.855      | 1087.812  | 1087.812     | 0.00%      | 0.00%         |

| Ckt2      | 1899.810      | 1890.496  | 1890.500     | 0.49%      | 0.49%         |

| Ckt3      | 12.230        | 6.021     | 12.222       | 50.77%     | 0.07%         |

| Ckt4      | 24.734        | 15.549    | 24.707       | 37.14%     | 0.13%         |

| Ckt5      | 8.424         | 5.055     | 8.363        | 39.99%     | 0.72%         |

| Ckt6      | 196.300       | 181.251   | 197.468      | 7.67%      | 0.60%         |

| Ckt7      | 255.920       | 196.102   | 252.613      | 23.37%     | 1.29%         |

| Avg.      |               |           |              | 22.78%     | 0.47%         |

Table 2.6 shows the accuracy in maximum IR drop values of ETBR\_IR compared with ETBR and UltraSim. Here we consider results from UltraSim UPS as the golden and errors

Figure 2.21: Voltage waveform at the node 17 of Ckt2.

Figure 2.22: Input current waveform at the node 17 of Ckt2.

are computed as the relative errors to the golden results in percentage.

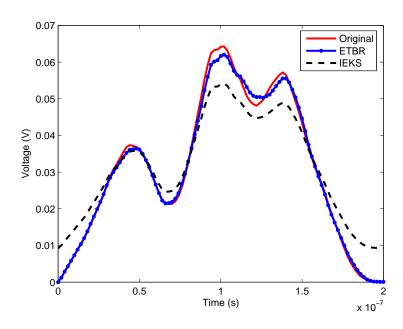

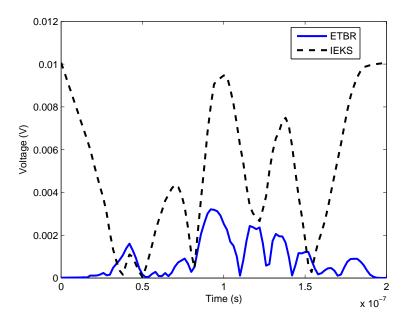

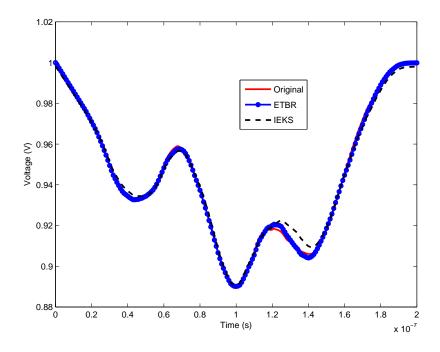

We can see that the max IR drop values computed by UltraSim and ETBR\_IR are almost

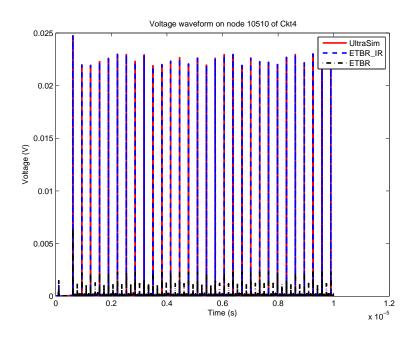

Figure 2.23: Voltage waveform at the node 10510 of Ckt4.

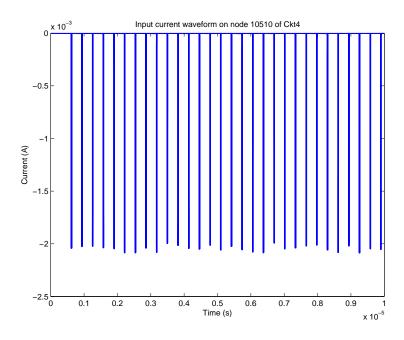

Figure 2.24: Input current waveform at the node 10510 of Ckt4.

the same. The max difference is less than 2%, and the average difference is less than 1%.

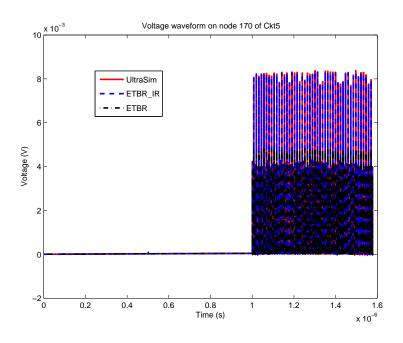

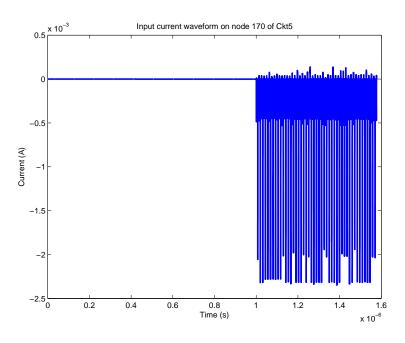

Fig. 2.21, Fig. 2.23 and Fig. 2.25 show the voltage waveforms on the max IR drop node

Figure 2.25: Voltage waveform at the node 107 of Ckt5.

Figure 2.26: Input current waveform at the node 107 of Ckt5.

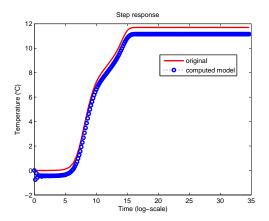

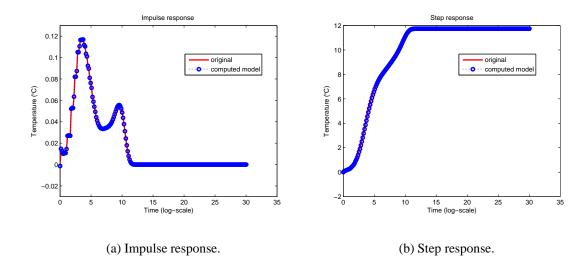

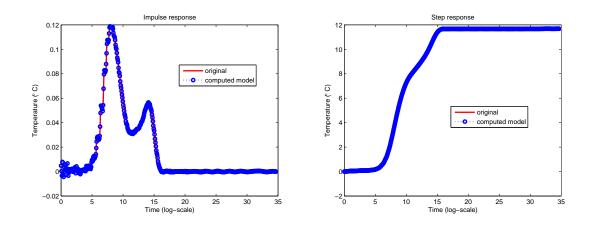

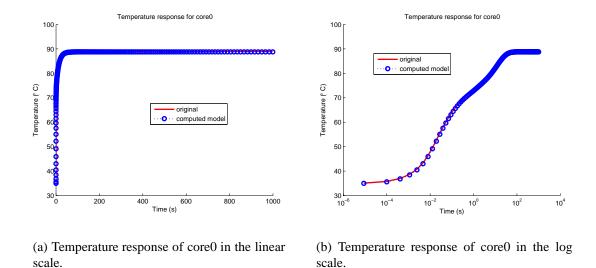

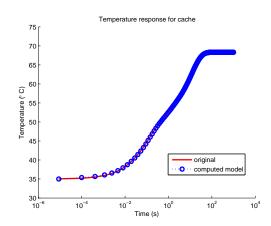

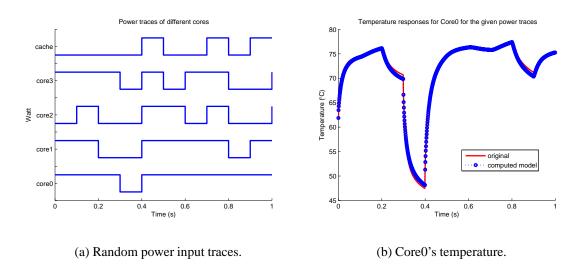

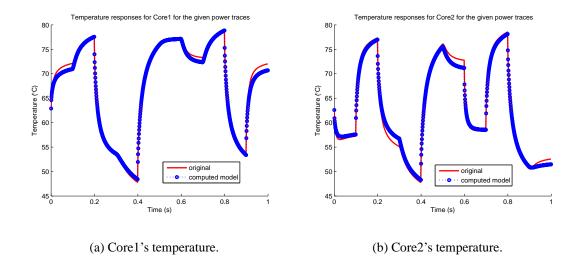

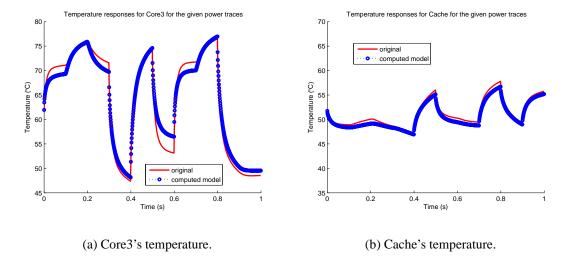

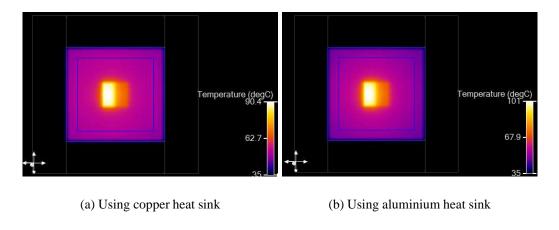

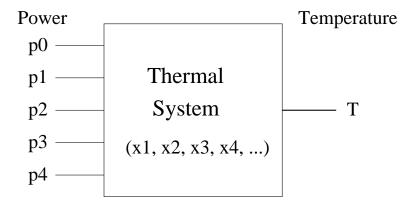

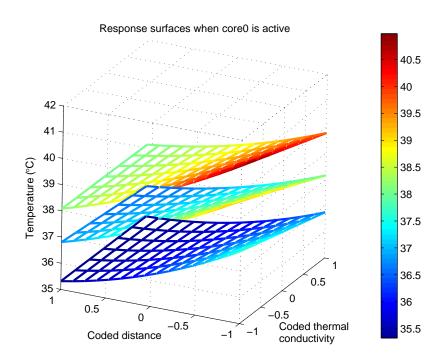

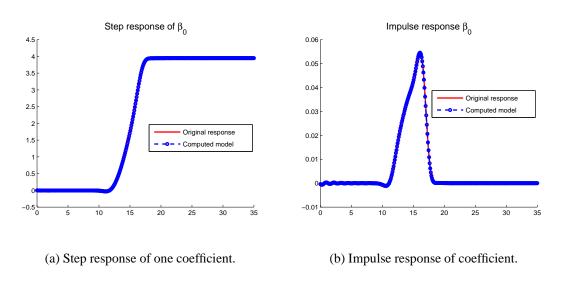

of Ckt2, Ckt4 and Ckt5, respectively. The max IR drop values computed by ETBR\_IR are sufficiently accurate for the practice purpose. As we can see that the voltage drops are very