# **UC Santa Barbara**

### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

ICs, Modules, and Links for 200-300GHz Wireless Communications

### **Permalink**

https://escholarship.org/uc/item/8kh452n5

#### **Author**

Soylu, Utku

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

# ICs, Modules, and Links for 200–300 GHz Wireless Communications

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Utku Soylu

### Committee in charge:

Professor Mark Rodwell, Chair Professor James Buckwalter Professor Upamanyu Madhow Professor Loai Salem

| The Dissertation of Utku Soylu is approved. |

|---------------------------------------------|

|                                             |

|                                             |

| Professor James Buckwalter                  |

|                                             |

| Professor Upamanyu Madhow                   |

|                                             |

| Professor Loai Salem                        |

|                                             |

| Professor Mark Rodwell, Committee Chair     |

### ICs, Modules, and Links for 200–300 GHz Wireless Communications

Copyright © 2023

by

Utku Soylu

To my parents, Yasemin and İrfan, and my brother, Ufuk, for their unlimited love and support.

### Acknowledgements

First and foremost, I would like to express my sincere gratitude to my advisor, Prof. Mark Rodwell, for granting me this valuable opportunity. I consider it a privilege to be under his guidance as his student, and I feel extremely fortunate to have had the opportunity to work with him throughout my Ph.D. studies. He has been a great teacher and mentor throughout my graduate studies at UCSB.

I would like to express my gratitude to the members of my Ph.D. committee: Prof. James Buckwalter, Prof. Upamanyu Madhow, and Prof. Loai Salem. Their valuable feedback on areas that required improvement and their unwavering support have been truly appreciated. I am immensely grateful for the productive and instructive weekly meetings we had with Prof. Buckwalter's and Prof. Madhow's teams. The collaboration we fostered was highly beneficial to my research.

I would like to express my deepest gratitude to both the past and current members of the Rodwell group, as their tremendous help and support have been invaluable to me. I extend my heartfelt thanks to Amirreza Alizadeh, Ahmed Ahmed, Ali Farid, Arda Simsek, Seungchan Lee, Ceylin Bormali, and Logan Whitaker for their contributions to my research. Each of them played a role in my growth, and I gained valuable insights through my interactions with them. In particular, I would like to extend a special thank you to Amirreza Alizadeh, Ahmed Ahmed, and Ali Farid for their guidance throughout my Ph.D. journey. Their assistance and support in areas such as IC design, module design, and measurements have been instrumental to my progress. Additionally, I feel incredibly fortunate to have had the opportunity to work with visiting professor Munkyo Seo during my second year of the Ph.D. His foundational work laid the groundwork upon which I built my transceivers. I would also like to express my appreciation to the former members of the device group: Brian Markman, Yihao Fang, and Hsin-Ying Tseng, for

their valuable interactions and contributions.

Being a part of the ComSenTer and SRC community has been an absolute blessing. It has afforded us a remarkable opportunity to collaborate and engage with esteemed researchers from leading universities worldwide. I am deeply grateful for the invaluable collaboration and interaction we have had with the distinguished ComSenTer professors, industry liaisons, and SRC industry members. Their contributions and unwavering support have played a vital role in the advancement and achievements of our research endeavors. I would like to extend my heartfelt appreciation to the Semiconductor Research Consortium (SRC) ComSenTer program for their generous funding.

I would like to express my gratitude to Teledyne Scientific and Imaging for their invaluable support in IC fabrication. I am especially thankful to Dr. Miguel Urteaga for providing practical insights and considerations in mm-wave IC and packaging design. I am also grateful to UCSB Cleanroom for their assistance in antenna fabrication. Furthermore, I would like to extend my appreciation to Royal Circuits and Bay Area Circuit for their exceptional PCB fabrication and assembly services. The contributions of Kyocera, Advotech, and MicroQ in module assembly are also greatly appreciated. Lastly, I would like to thank RapidDirect for their assistance in mechanical component fabrication. Their support has been instrumental in the successful execution of my project.

Last but not least, I would like to thank my family, my parents, Yasemin and İrfan, and my brother, Ufuk. Without their unconditional love and support, I could not achieve.

# Curriculum Vitæ

### Utku Soylu

#### Education

| 2023 | Ph.D. in Electrical and Computer Engineering, University of Cali-    |

|------|----------------------------------------------------------------------|

|      | fornia, Santa Barbara.                                               |

| 2019 | M.S. in Electrical and Computer Engineering, University of Cali-     |

|      | fornia, Santa Barbara.                                               |

| 2018 | B.S. in Electrical and Electronics Engineering, Boğaziçi University, |

|      | İstanbul, Turkey.                                                    |

### **Professional Experience**

| 9/2018 - 6/2023 | Research Assistant at the High-Frequency Electronics Group at Uni-                |

|-----------------|-----------------------------------------------------------------------------------|

|                 | versity of California, Santa Barbara, USA.                                        |

| 6/2021 - 9/2022 | Summer Internship at IBM T. J. Watson Research Center, Yorktown Heights, NY, USA. |

| 6/2021 - 8/2021 | Summer Internship at Nokia Bells, Murray Hill, NJ, USA.                           |

#### **Publications**

- 1. U. Soylu, A. Alizadeh, M. Seo, A. S. H. Ahmed, M. J. W. Rodwell, "A 202 GHz Link Using Planar Transceiver Modules," submitted, 2023 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA.

- 2. **U. Soylu**, A. Alizadeh, M. Seo, M. J. W. Rodwell, "280-GHz Frequency Multiplier Chains in 250-nm InP HBT Technology," *IEEE Journal of Solid-State Circuits (JSSC)*, Sept., 2023.

- 3. U. Soylu, A. Alizadeh, A. S. H. Ahmed, M. Seo, M. J. W. Rodwell, "A 272 GHz InP HBT Direct-Conversion Transmitter with 14.1 dBm Output Power," 2023 18th European Microwave Integrated Circuits Conference (EuMIC), Berlin, Germany.

- 4. **U. Soylu**, A. Alizadeh, M. Seo, M. J. W. Rodwell, "A 280 GHz InP HBT Direct-Conversion Receiver with 10.8 dB NF," 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Diego, CA, USA.

- 5. U. Soylu, A. Alizadeh, M. Seo, M. J. W. Rodwell, "A 280 GHz (x8) Frequency Multiplier Chain in 250 nm InP HBT," 2022 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Phoenix, AZ, USA.

- 6. U. Soylu, A. S. H. Ahmed, M. Seo, A. Farid, M. J. W. Rodwell, "200 GHz Low Noise Amplifiers in 250 nm InP HBT Technology," 2021 16th European Microwave Integrated Circuits Conference (EuMIC), London, UK.

- 7. A. Alizadeh, U. Soylu, L. Whitaker, M. J. W. Rodwell, "200-GHz Transmitter and Receiver Modules using Microstrip Patch Antennas on Glass and ICs in 250-nm InP HBT," in progress, *IEEE Transaction on Microwave Theory and Techniques (TMTT)*.

- 8. A. Alizadeh, **U. Soylu**, N. Sharma, G. Xu, M. J. W. Rodwell, "D-Band Power Amplifier with 27 dBm Peak Output Power and 14.9% PAE in 250-nm InP HBT Technology," submitted, 2023 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA.

- 9. M. J. W. Rodwell, A. S. H. Ahmed, M. Seo, **U. Soylu**, A. Alizadeh, N. Hosseinzadeh, "IC and Array Technologies for 100-300GHz Wireless," 2022 IEEE Custom Integrated Circuits Conference (CICC), Newport Beach, CA, USA.

- 10. M. J. W. Rodwell, A. Farid, A. S. H. Ahmed, M. Seo, **U. Soylu**, A. Alizadeh, N. Hosseinzadeh, "100-300GHz Wireless: ICs, Arrays, and Systems," 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA.

- 11. M. Seo, A. S. H. Ahmed, **U. Soylu**, A. Farid, Y. Na, M. J. W. Rodwell, "A 200 GHz InP HBT Direct-Conversion LO-Phase-Shifted Transmitter/Receiver with 15 dBm Output Power," 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA.

- 12. A. S. H. Ahmed, **U. Soylu**, M. Seo, M. Urteaga, J. F. Buckwalter, M. J. W. Rodwell, "A 190-210GHz Power Amplifier with 17.7-18.5 dBm Output Power and 6.9-8.5% PAE," 2021 IEEE MTT-S International Microwave Symposium (IMS), Atlanta, GA, USA.

- 13. A. S. H. Ahmed, **U. Soylu**, M. Seo, M. Urteaga, M. J. W. Rodwell, "A compact H-band power amplifier with high output power," 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA.

- 14. A. Simsek, A. S. H. Ahmed, A. Farid, **U. Soylu**, M. J. W. Rodwell, "A 140GHz two-channel CMOS transmitter using low-cost packaging technologies," 2020 IEEE Wireless Communications and Networking Conference Workshops (WCNCW), Seoul, Korea (South).

- 15. J. P. Sculley, B. Markman, U. Soylu, Y. Fang, M. Urteaga, A. D. Carter, M. J. W. Rodwell, P. D. Yoder, "Monte Carlo Investigation of Traveling Accumulation Layers in InP Heterojunction Bipolar Transistor Power Amplifiers," 2019 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA.

#### Abstract

ICs, Modules, and Links for 200–300 GHz Wireless Communications

by

#### Utku Soylu

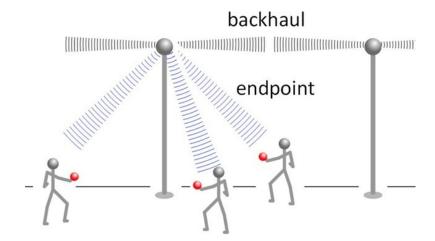

There is an increasing demand for high data-rate wireless communications in endpoint and backhaul links. In this research, we develop next-generation wireless communication systems (200–300 GHz), as millimeter frequencies provide vast amounts of available bandwidth, and shorter wavelengths permit many elements in physically compact arrays. This thesis focuses on building the necessary hardware and infrastructure for such systems.

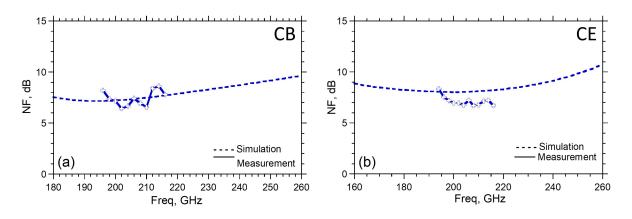

First, we investigate two important building blocks: low noise amplifiers (LNAs) and frequency multipliers. We present a comprehensive study on multi-stage LNA design based on low total (cascaded) noise figure, i.e., noise measure (NM). 200 GHz LNAs in common-base (CB) and common-emitter (CE) topologies were presented with record noise figure among HBT technologies:  $7.4\pm0.7\,\mathrm{dB}$  over  $196-216\,\mathrm{GHz}$  (CB) and  $7.2\pm0.4\,\mathrm{dB}$  over  $196-216\,\mathrm{GHz}$  (CE). 280 GHz frequency multipliers (8:1 and 16:1) are presented with record spectral purity. The 8:1 frequency multiplier generates  $-0.6\,\mathrm{dBm}$  output power and has a 3-dB bandwidth of 48 GHz. Spurious harmonics are suppressed by more than 28 dBc over the 3-dB bandwidth of 44 GHz. Spurious harmonics are suppressed by more than 26 dBc over the 3-dB bandwidth.

Next, 200 and 280 GHz broadband transceivers in Teledyne 250 nm InP HBT technology are presented. The 280 GHz transmitter IC has a peak conversion gain of 21.6 dB with 36 GHz of 6-dB modulation bandwidth, and dissipates 1535 mW. The measured saturated output power is 14.1 dBm at 272 GHz. The 280 GHz receiver IC has a peak

conversion gain of 22 dB with 34.5 GHz of 6-dB modulation bandwidth, and dissipates 455 mW. The measured double sideband (DSB) noise figure is 10.8 dB at 281.5 GHz. These are the record output power and noise figure reported at and around 280 GHz. The 200 GHz transmitter IC has a record output power (15.3–16.5 dBm) and efficiency (2.71–3.57%) over 195–200 GHz. The 200 GHz receiver IC has a record DSB noise figure (7.7–9.3 dB) over 200–212 GHz.

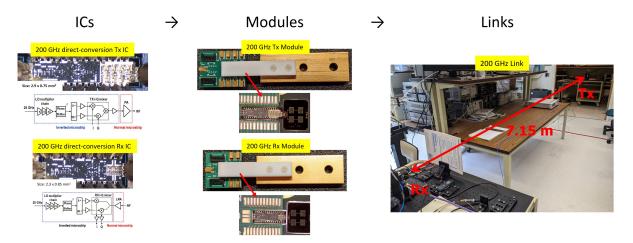

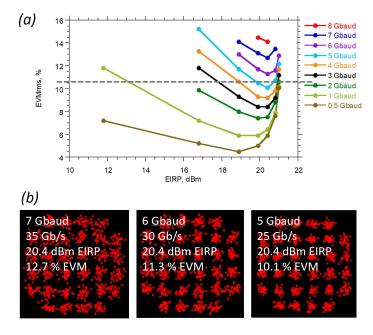

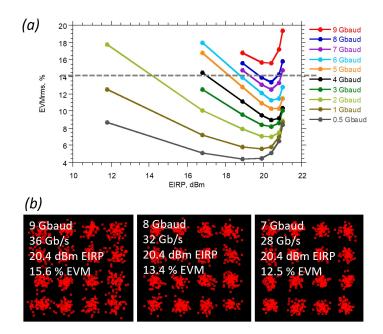

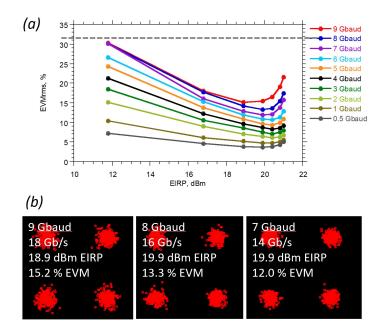

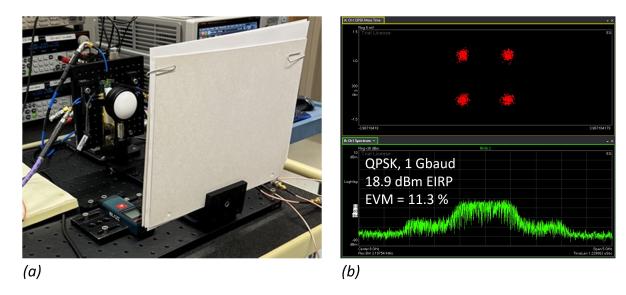

Finally, we demonstrate packaged 200 GHz 1-channel transmitter and receiver modules with series-fed microstrip patch antennas on glass. The packaged transmitter module has effective isotropic radiated power (EIRP) of 21.6 dBm with 20 GHz 3-dB modulation bandwidth and 62° E-plane and H-plane 3-dB beamwidth. The packaged receiver module has a 14 GHz 3-dB modulation bandwidth and 62° E-plane and H-plane 3-dB beamwidth. Modules can support a wide range of modulation schemes (i.e., QPSK, 16QAM). The link measurements at 7.15 meters showed 13.4% error vector magnitude (EVM) during 32 Gb/s, 16 quadratic-amplitude modulation (QAM) transmission. The integrated transmitter and receiver modules can be used for a broad range of applications, including wireless backhaul, imaging, and radar applications.

# Contents

| Cı | ırricı | ılum <b>V</b>       | Vitae                                       | vii  |

|----|--------|---------------------|---------------------------------------------|------|

| Al | ostra  | $\operatorname{ct}$ |                                             | ix   |

| Li | st of  | Figure              | es                                          | xiii |

| Li | st of  | Tables              | 3                                           | xix  |

| 1  | Intr   | oducti              | on                                          | 1    |

|    | 1.1    | Milllin             | neter Wave Wireless Communications          | . 1  |

|    | 1.2    |                     | tation Contributions and Organization       |      |

|    | 1.3    |                     | ssions and Attributions                     |      |

| 2  | Mill   | imeter              | -Wave Low Noise Amplifier Fundamentals      | 6    |

| _  | 2.1    |                     | uction                                      |      |

|    | 2.2    |                     | n InP HBT Technology                        |      |

|    | 2.3    |                     | oise Amplifier Design                       |      |

|    | 2.5    | 2.3.1               | Determining Bias Condition                  |      |

|    |        | 2.3.1 $2.3.2$       | Displaying source impedance for minimum M   |      |

|    |        | 2.3.3               | - • •                                       |      |

|    |        |                     | Area Scaling and Degeneration               |      |

|    | 0.4    | 2.3.4               | Input/Output Matching Network and Cascading |      |

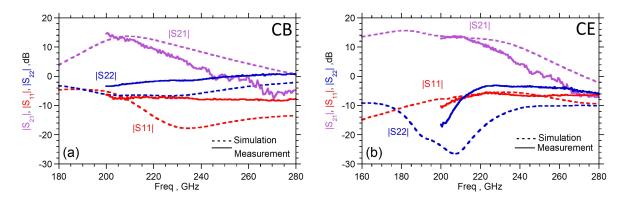

|    | 2.4    |                     | rement Results                              |      |

|    |        | 2.4.1               | S-Parameter Measurements                    |      |

|    |        | 2.4.2               | Power Measurements                          |      |

|    |        | 2.4.3               | Noise Measurements                          |      |

|    | 2.5    | Summ                | ary and Conclusion                          | . 19 |

| 3  | Mill   | imeter              | -Wave Frequency Generation Fundamentals     | 20   |

|    | 3.1    | Introd              | $\operatorname{uction}$                     | . 20 |

|    | 3.2    | Freque              | ency Multiplier Chain Design                | . 22 |

|    |        | 3.2.1               | Multiplier Chain Spurious Harmonics         |      |

|    |        | 3.2.2               | Balanced Frequency Doubler Cell             |      |

| Bi | bliog              | graphy                  |                                                                   |      |      | 88                 |

|----|--------------------|-------------------------|-------------------------------------------------------------------|------|------|--------------------|

| 7  | Con                | clusions                | s and Future Work                                                 |      |      | 86                 |

|    | 6.3                | 6.2.4                   | Long-range Transmission Setup Long-range Transmission Experiments |      |      | <br>83             |

|    |                    | 6.2.2                   | Short-range Transmission Setup                                    |      |      | <br>78             |

| 6  | <b>200</b> 6.1 6.2 | Introdu<br>Transm       | nk Experiments ction                                              |      |      |                    |

|    | 5.4                |                         | ry and Conclusion                                                 |      |      |                    |

|    | 5.3                | 5.3.1                   | ement Results                                                     |      |      | <br>66             |

|    | <b>F</b> 0         | 5.2.2 5.2.3 5.2.3       | 200 GHz Transmitter and Receiver ICs                              |      |      | <br>61<br>64       |

| 5  | 200<br>5.1<br>5.2  | Module                  | ction                                                             |      |      | <br>56             |

|    | 4.5                |                         | Transmitter IC CW Characterization                                |      |      |                    |

|    | 4.4                | 4.4.1<br>4.4.2          | Receiver IC CW Characterization                                   |      |      | <br>47<br>49       |

|    | 4.3                | 4.3.1<br>4.3.2          | $ \begin{array}{llllllllllllllllllllllllllllllllllll$             |      |      | <br>45<br>46       |

|    | 4.0                | 4.2.2<br>4.2.3<br>4.2.4 | LO Driver                                                         | <br> | <br> | <br>41<br>42<br>43 |

|    | 4.1<br>4.2         | Introdu<br>Receive      | ction                                                             |      |      | <br>39             |

| 4  | 280                |                         | ranceiver Design                                                  |      |      | 38                 |

|    | 3.3<br>3.4         | Measure                 | Single-ended to Differential Conversion                           |      |      | <br>31             |

# List of Figures

| 1.1 | Spatially-multiplexed mm-wave base stations for backhaul links and mm-wave wireless communication for the user endpoint ( <i>Courtesy of Prof.</i>  |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.0 | Mark J W. Rodwell)                                                                                                                                  | 2   |

| 1.2 | Building steps for mm-wave communications: IC design, module design, and link experiments                                                           | 3   |

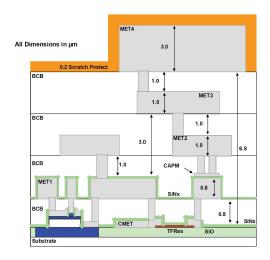

| 2.1 | Cross-section view of 250 nm InP HBT technology                                                                                                     | 8   |

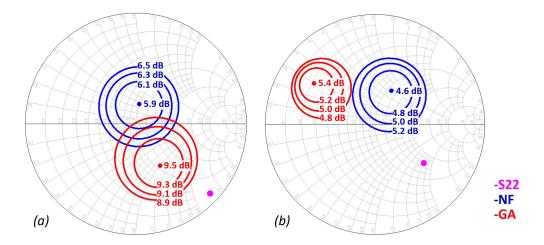

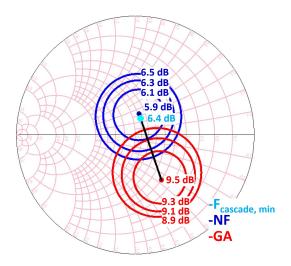

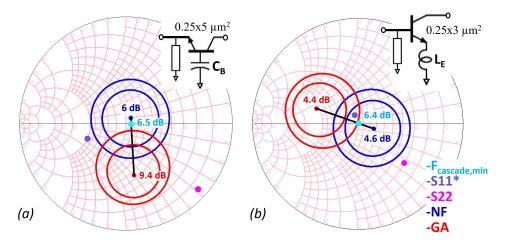

| 2.2 | $S_{22}$ , NF and GA circles at 200 GHz. Data is for (a) $(0.25 \times 5 \ \mu \text{m}^2)$ HBT                                                     |     |

|     | in CB configuration with 200 fF base capacitance and (b) (0.25 $\times$ 3 $\mu$ m <sup>2</sup> )                                                    |     |

|     | HBT in CE configuration, biased at $V_{\rm CB}$ =0.4 and $J_{\rm E}$ =0.5 mA/ $\mu$ m                                                               | 9   |

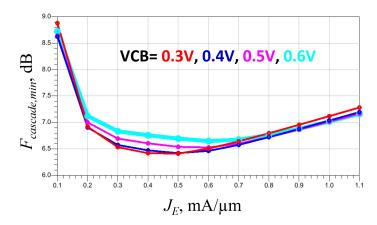

| 2.3 | Minimum $F_{cascade}$ as a function of emitter current density $(J_{\rm E})$ and collector-                                                         |     |

|     | base voltage $(V_{\rm CB})$ for a $0.25 \times 5 \mu{\rm m}^2$ HBT in CB configuration with 200 fF                                                  | 4.0 |

| 0.4 | base capacitance at 200 GHz.                                                                                                                        | 10  |

| 2.4 | CAD display, in Keysight ADS, of the contours of constant noise figure and available gain (GA) in the plane of the source reflection coefficient. A |     |

|     | Python script draws a line (black) between the centers of the NF and GA                                                                             |     |

|     | circles, computing the minimum noise measure along this line. Data is for                                                                           |     |

|     | an $0.25 \times 5 \ \mu\mathrm{m}^2$ HBT in CB configuration with $200\mathrm{fF}$ base capacitance                                                 |     |

|     | biased at $V_{\rm CB}$ =0.4 and $J_{\rm E}$ =0.5 mA/ $\mu$ m, simulated at 200 GHz                                                                  | 11  |

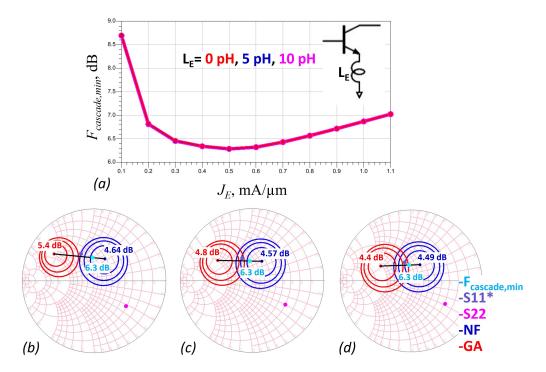

| 2.5 | (a) Minimum $F_{cascade}$ as a function of emitter current density $(J_{\rm E})$ and                                                                |     |

|     | emitter degeneration ( $L_{\rm E}$ ) for a 0.25 $	imes$ 3 $\mu{\rm m}^2$ HBT in CE configuration                                                    |     |

|     | biased at $V_{\text{CB}}=0.4 \text{ V}$ . The minimum M impedance, $S_{11}$ conjugate, $S_{22}$ , NF                                                |     |

| 2.0 | and GA circles: (b) $L_{\rm E}=0$ pH, (c) $L_{\rm E}=5$ pH, (d) $L_{\rm E}=10$ pH                                                                   | 12  |

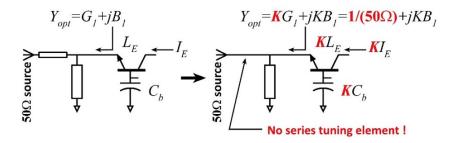

| 2.6 | (a) Input matching network without proper emitter junction area scaling,                                                                            | 4.0 |

| 0.7 | (b) input matching network with proper emitter junction area scaling                                                                                | 13  |

| 2.7 | (a) Input matched CB stage and (b) input matched CE stage with proper                                                                               | 10  |

| 20  | emitter junction area scaling.                                                                                                                      | 13  |

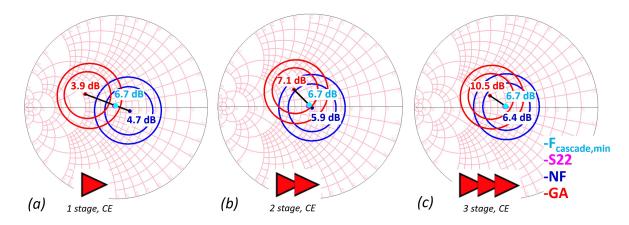

| 2.8 | Minimum $F_{cascade}$ impedance, $S_{22}$ , NF and GA circles for cascaded stages                                                                   | 1 1 |

|     | in CE configuration: (a) 1 stage, (b) 2 stages, (c) 3 stages                                                                                        | 14  |

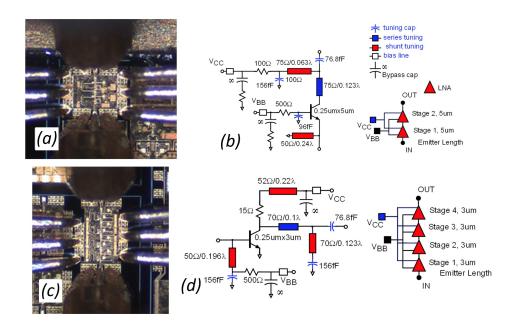

| <ul><li>2.9</li><li>2.10</li></ul> | CB amplifier: (a) die photo and (b) amplifier circuit diagram. The die area, including DC routing and pads is $0.49 \times 0.425 \text{ mm}^2$ . CE amplifier: (c) die photo and (d) amplifier circuit diagram. The die area, including DC routing and pads is $0.45 \times 0.63 \text{ mm}^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                   |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                    | CE amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                   |

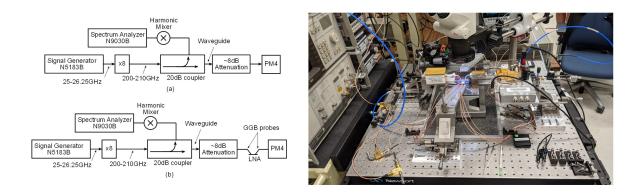

| 2.11                               | Power measurement setup: (a) Calibration phase and (b) measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 7                  |

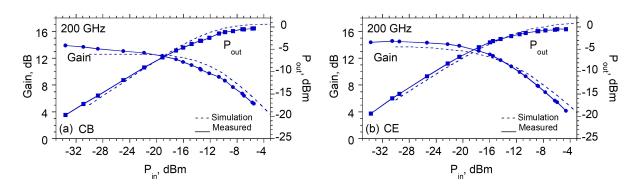

| 2.13                               | phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17<br>17<br>18<br>18 |

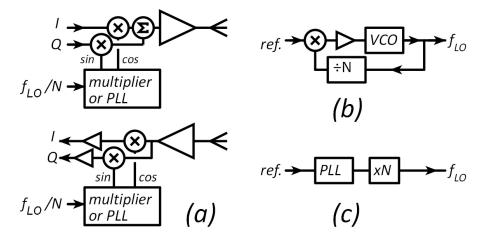

| 3.1                                | (a) Millimeter-wave transceiver architectures with (b) PLLs and (c) multiplier chains for on-chip LO generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                   |

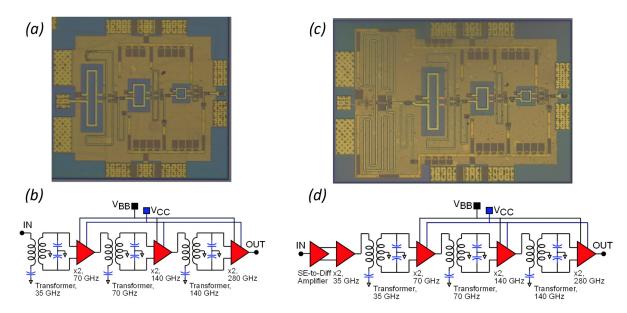

| 3.2                                | (a) Die photograph and (b) block diagram of the 8:1 frequency multiplier; the die area is $0.92 \mathrm{mm} \times 0.8 \mathrm{mm}$ , while the core area, without DC routing and pads, is $0.7 \mathrm{mm} \times 0.56 \mathrm{mm}$ . (c) Die photograph and (d) block diagram of the 16:1 frequency multiplier; the die area is $1.2 \mathrm{mm} \times 0.8 \mathrm{mm}$ , while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

|                                    | core area, without DC routing and pads, is $1 \text{ mm} \times 0.75 \text{ mm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                   |

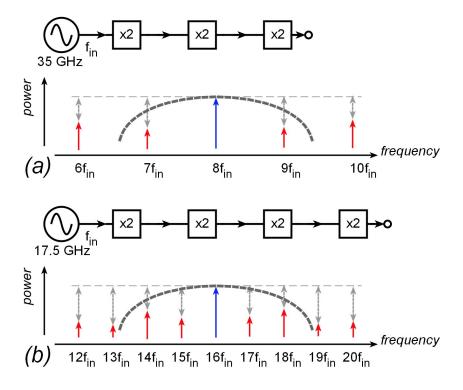

| 3.3                                | The output spectrum of (a) 8:1 FMC and (b) 16:1 FMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                   |

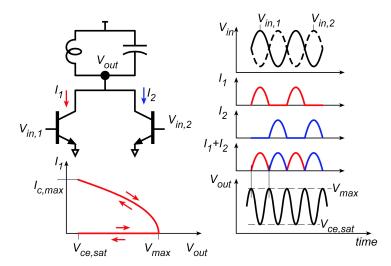

| 3.4                                | Balanced frequency doubler voltage waveforms, current waveforms, and transistor loadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26                   |

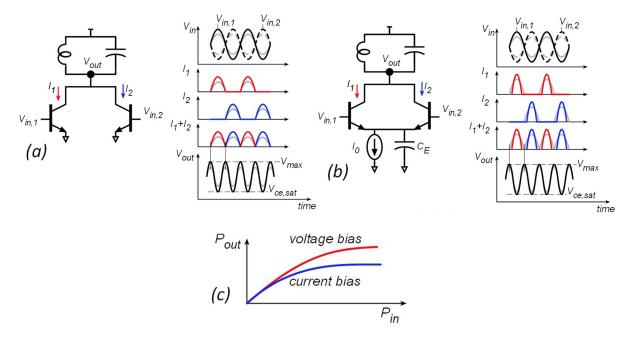

| 3.5                                | Balanced frequency doubler with voltage and current waveforms with varying drive power for designs with (a) fixed voltage bias, and (b) fixed emitter current bias. The fixed emitter current bias design shows a smaller variation (c) of output power with variations of input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                   |

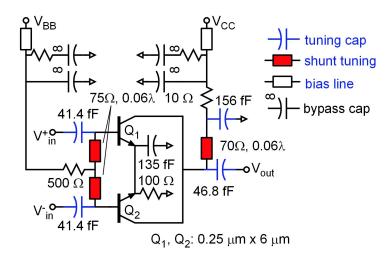

| 3.6                                | Schematic diagram of the 140 GHz to 280 GHz frequency doubler with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ۷,                   |

|                                    | input and output matching networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                   |

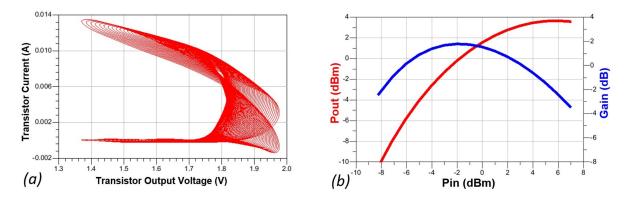

| 3.7                                | (a) Simulated loadline ( $I_c$ vs. $V_{CE}$ ) where $P_{\rm in}$ is swept from $-12{\rm dBm}$ to $2{\rm dBm}$ . (b) Simulated $P_{\rm out}$ vs. $P_{\rm in}$ characteristics of the 140 to 280 GHz frequency doubler. The transistor current displayed in the loadline includes only the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ displayed in the collector electron transport current and not the $C_{\rm cb}dV_{\rm cb}/dt$ | 00                   |

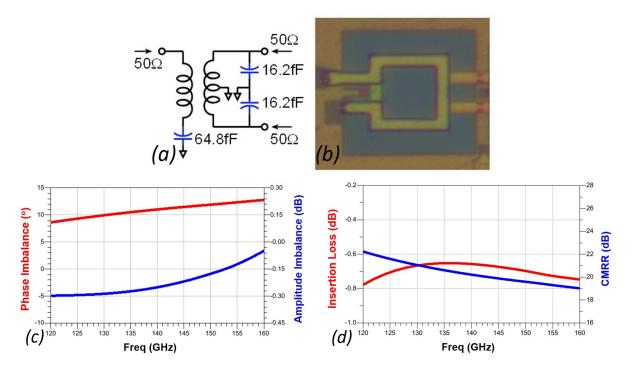

| 3.8                                | placement current associated with the collector-base capacitance 140 GHz transformer balun (a) schematic, (b) die photograph, (c) simu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                   |

| <b>9.</b> 0                        | lated phase and amplitude imbalance, and (d) simulated insertion loss and CMRR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                   |

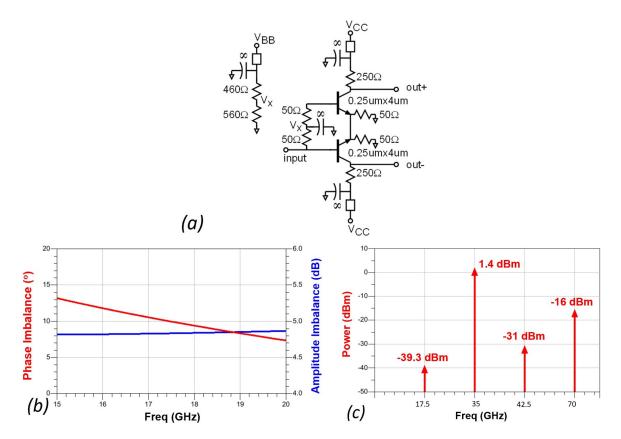

| 3.9                                | Active balun (a) schematic and (b) simulated phase and amplitude imbalance. (c) The simulated output spectrum of the 1 <sup>st</sup> doubler stage integrated with the active balun, with $P_{\rm in}=-13{\rm dBm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                   |

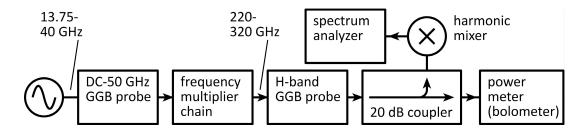

| 3 10                               | Experimental setup for characterizing the frequency doubler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                   |

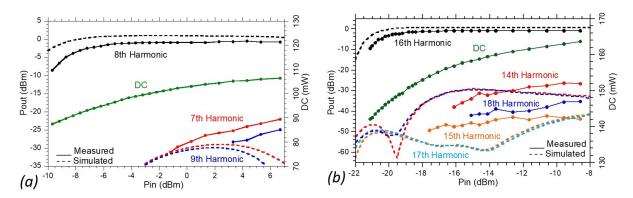

| 3.11 | Measured $P_{\text{out}}$ vs. $P_{\text{in}}$ for the desired and spurious harmonics for the (a) 8:1 multiplier with a 35 GHz input and the (b) 16:1 multiplier with a                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 17.5 GHz input                                                                                                                                                                                                                                                                                                               |

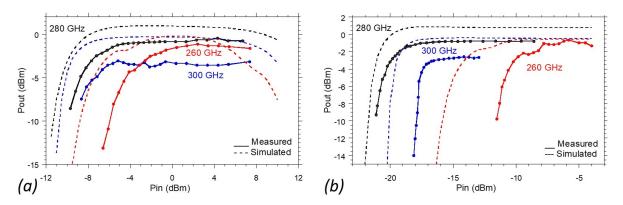

| 3 19 | Measured $P_{\text{out}}$ vs $P_{\text{in}}$ at 260 GHz, 280 GHz, and 300 GHz for (a) the 8:1                                                                                                                                                                                                                                |

| 0.12 | multiplier and (b) the 16:1 multiplier                                                                                                                                                                                                                                                                                       |

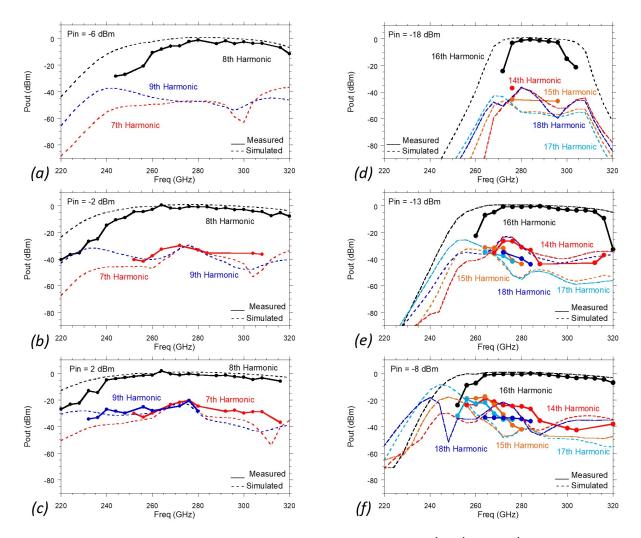

| 2 12 | Measured and simulated output power at the 7 <sup>th</sup> , 8 <sup>th</sup> , and 9 <sup>th</sup> harmonics of                                                                                                                                                                                                              |

| 0.10 | the input frequency, for the 8:1 frequency multiplier chain, at (a) $-6 \mathrm{dBm}$ ,                                                                                                                                                                                                                                      |

|      | (b) $-2 \mathrm{dBm}$ , and (c) $2 \mathrm{dBm}$ input power. Measured and simulated output power at the $14^{\mathrm{th}}$ through $18^{\mathrm{th}}$ harmonics of the input frequency, for the 16:1 frequency multiplier chain, at (d) $-18 \mathrm{dBm}$ , (e) $-13 \mathrm{dBm}$ , and (f) $-8 \mathrm{dBm}$ input power |

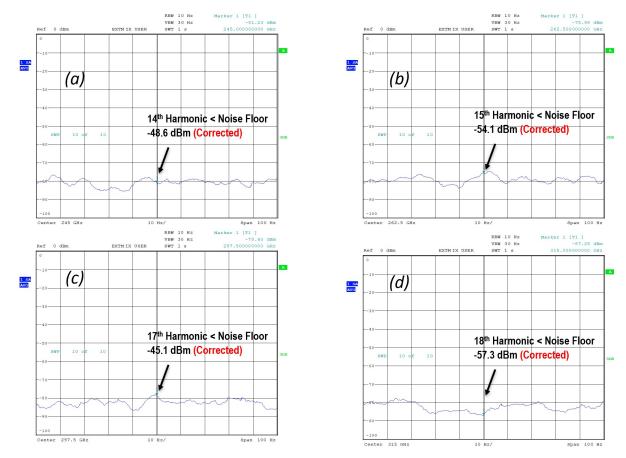

| 2 11 | Output spectrum of the 16:1 frequency multiplier chain, as measured by                                                                                                                                                                                                                                                       |

| 3.14 | the harmonic mixer and spectrum analyzer, given $-18\mathrm{dBm}$ input power at 17.5 GHz. All spurious harmonics within the 220–330 GHz band are                                                                                                                                                                            |

|      | below the instrument noise                                                                                                                                                                                                                                                                                                   |

|      |                                                                                                                                                                                                                                                                                                                              |

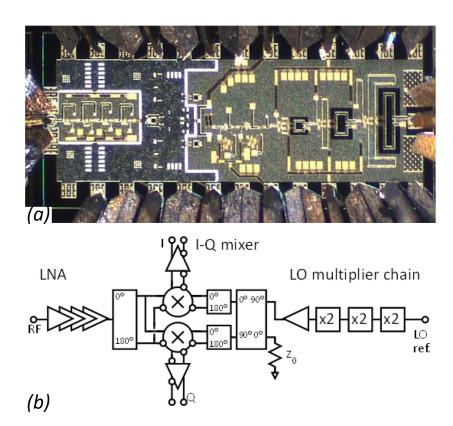

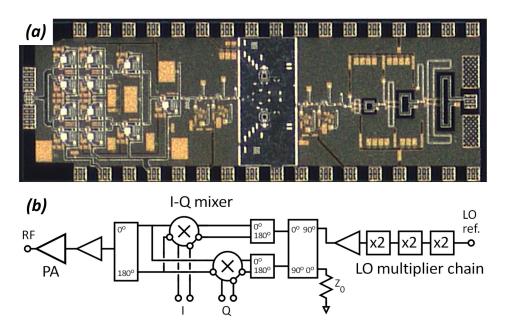

| 4.1  | 280 GHz direct-conversion receiver: integrated circuit photograph (a), and                                                                                                                                                                                                                                                   |

|      | block diagram (b). The IC is $2.0 \mathrm{mm} \times 0.8 \mathrm{mm}$                                                                                                                                                                                                                                                        |

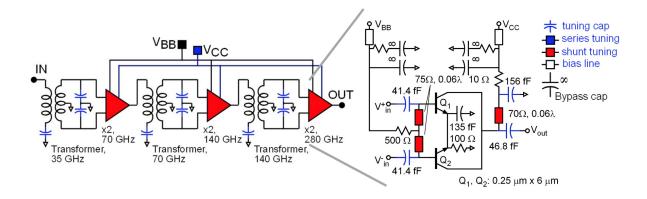

| 4.2  | Circuit schematics of the LO multiplier (8:1)                                                                                                                                                                                                                                                                                |

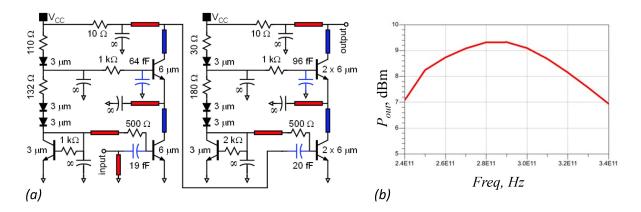

| 4.3  | LO Driver: (a) circuit schematic, (b) simulated $P_{\text{out}}$ vs frequency 4                                                                                                                                                                                                                                              |

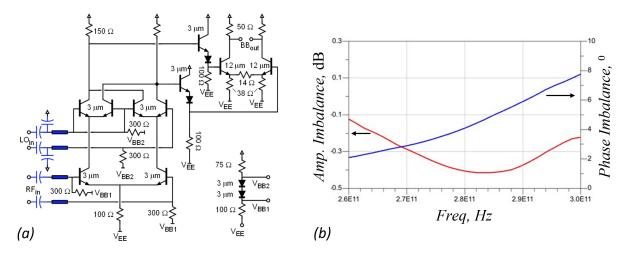

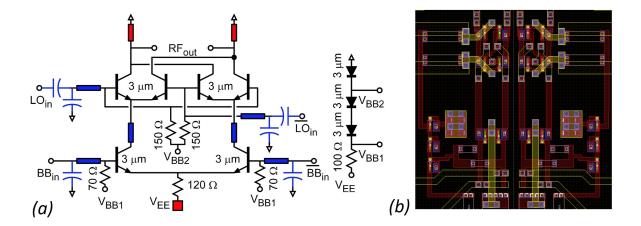

| 4.4  | Down-conversion $I$ - $Q$ Mixer: (a) circuit schematic, (b) simulated amplitude and phase imbalance vs frequency                                                                                                                                                                                                             |

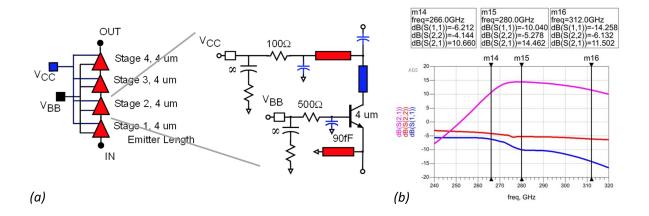

| 4.5  | LNA: (a) circuit schematic, (b) simulated S-parameters                                                                                                                                                                                                                                                                       |

| 4.6  | 280 GHz direct-conversion transmitter: integrated circuit photograph (a), and block diagram (b). The IC is 2.8 mm x 0.92 mm                                                                                                                                                                                                  |

| 4.7  | Up-conversion $I$ - $Q$ Mixer: (a) circuit schematic, (b) layout                                                                                                                                                                                                                                                             |

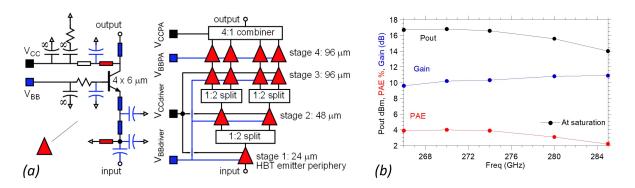

| 4.8  | PA: (a) circuit schematic, (b) measured $P_{\text{out}}$ , PAE and Gain vs frequency                                                                                                                                                                                                                                         |

| 1.0  | (designed by Dr. Ahmed Ahmed)                                                                                                                                                                                                                                                                                                |

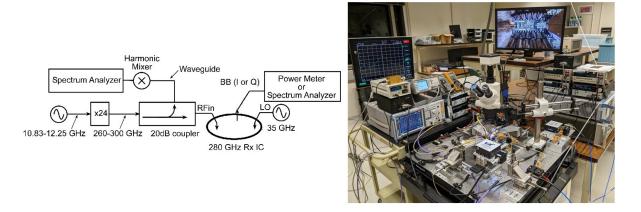

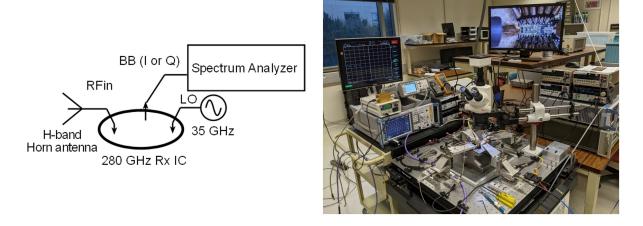

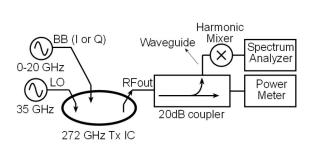

| 4.9  | Receiver continuous wave (CW) testing setup                                                                                                                                                                                                                                                                                  |

| 4.10 | Conversion gain vs. RF frequency: (a) at a fixed 280 GHz LO frequency,                                                                                                                                                                                                                                                       |

| 1110 | (b) at a fixed 1 GHz output frequency                                                                                                                                                                                                                                                                                        |

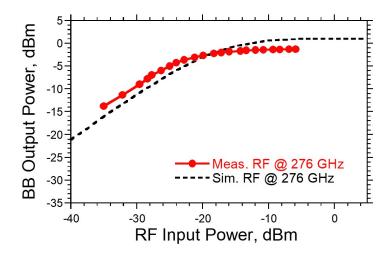

| 4.11 | Baseband output power vs. RF input power at $f_{LO} = 280 \mathrm{GHz}$                                                                                                                                                                                                                                                      |

|      | Receiver noise figure measurement by the gain method                                                                                                                                                                                                                                                                         |

|      | Measured vs simulated receiver DSB noise figure                                                                                                                                                                                                                                                                              |

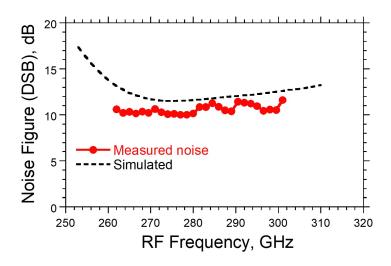

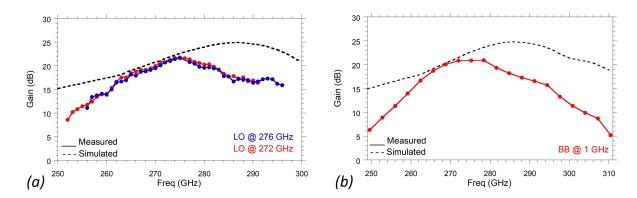

|      | Transmitter continuous wave (CW) testing setup                                                                                                                                                                                                                                                                               |

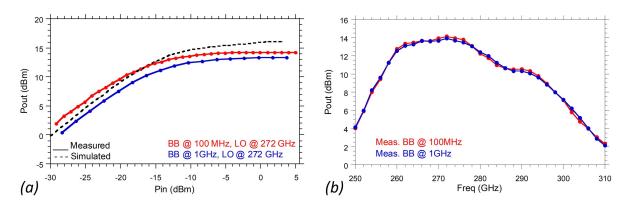

|      | Conversion gain vs. RF frequency: (a) at a fixed LO (272, 276 GHz)                                                                                                                                                                                                                                                           |

|      | frequency, (b) at a fixed 1 GHz input BB frequency                                                                                                                                                                                                                                                                           |

| 4.16 | (a) RF output power vs. baseband input power, (b) saturated RF output                                                                                                                                                                                                                                                        |

|      | power vs. RF frequency                                                                                                                                                                                                                                                                                                       |

|      | _ v                                                                                                                                                                                                                                                                                                                          |

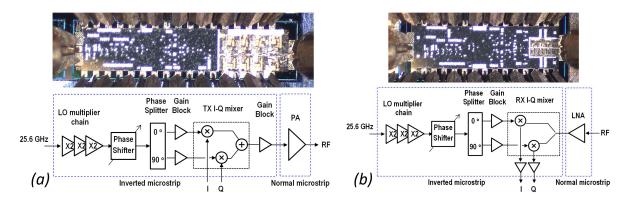

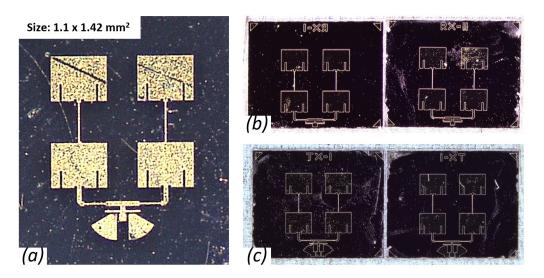

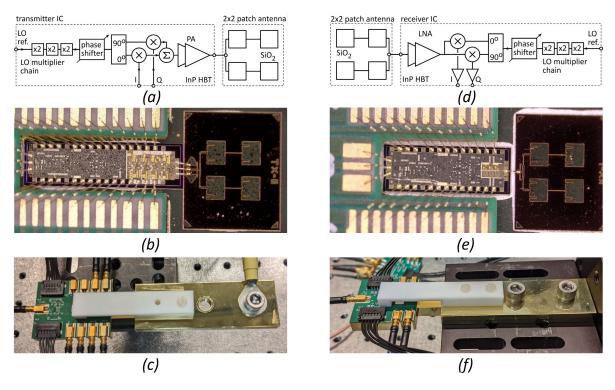

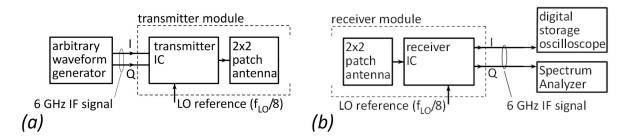

| 5.1  | (a) A 200 GHz direct-conversion transmitter: chip photo (top) and block diagram (bottom). Chip size: $2.9  mm \times 0.75  mm$ . (b) A 200 GHz direct-conversion receiver: chip photo (top) and block diagram (bottom). Chip |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | size: $2.3  mm \times 0.85  mm$ (designed by Prof. Munkyo Seo)                                                                                                                                                               | 57   |

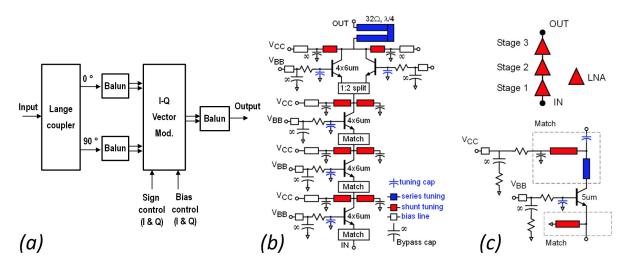

| 5.2  | Circuit schematics: (a) phase shifter, (b) PA, (c) LNA                                                                                                                                                                       | 57   |

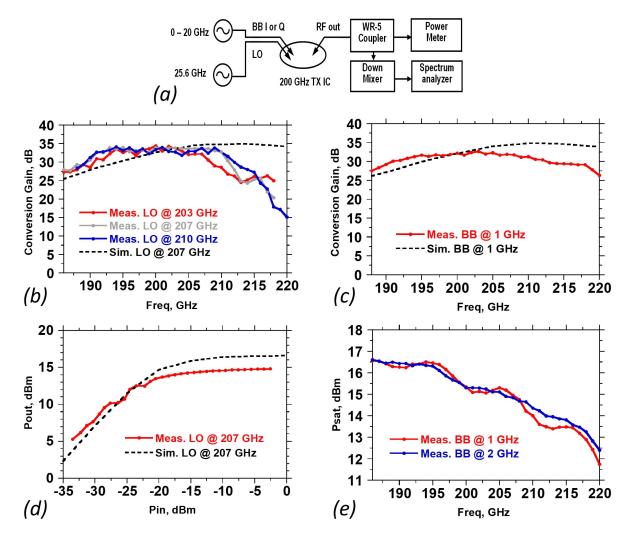

| 5.3  | (a) On-wafer transmitter IC testing setup. Transmitter IC measurement                                                                                                                                                        | •    |

| 0.0  | results: (a) conversion gain vs. baseband frequency at a fixed LO, (c)                                                                                                                                                       |      |

|      | conversion gain vs. LO frequency at a fixed baseband frequency, (d) RF                                                                                                                                                       |      |

|      | output power vs. baseband input power at 1 GHz, (e) saturated RF power                                                                                                                                                       |      |

|      | vs. RF frequency                                                                                                                                                                                                             | 58   |

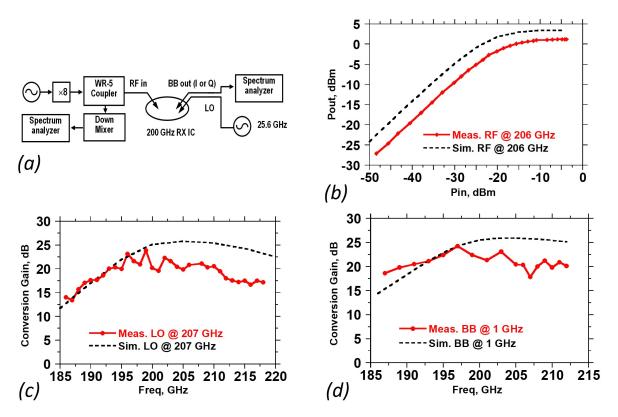

| 5.4  | (a) On-wafer receiver IC testing setup. Receiver IC measurement results:                                                                                                                                                     | 00   |

| 0.1  | (b) baseband output power vs. RF input power, LO is at 207 GHz, (c)                                                                                                                                                          |      |

|      | conversion gain vs. RF frequency at a fixed LO, (d) conversion gain vs.                                                                                                                                                      |      |

|      | RF frequency at a fixed baseband frequency                                                                                                                                                                                   | 59   |

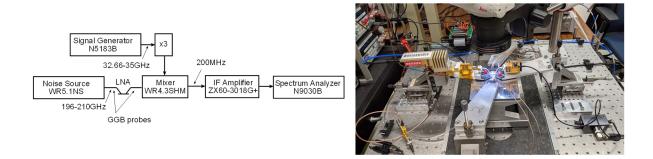

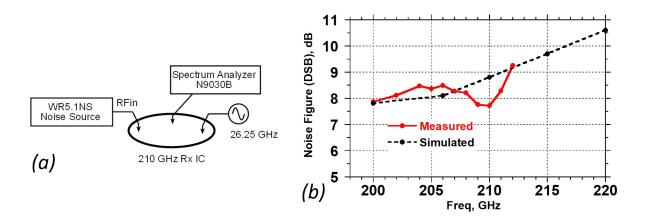

| 5.5  | (a) Receiver IC noise testing setup. (b) Measured noise figure                                                                                                                                                               | 60   |

| 5.6  | (a) A photograph of the $50\Omega$ matched corporate-fed $2\times 2$ series patch an-                                                                                                                                        |      |

|      | tenna array on 2 mil fused silica substrate. Tuned antennas for (b) receiver                                                                                                                                                 |      |

|      | module, (c) transmitter module (designed by Dr. Amirreza Alizadeh, and                                                                                                                                                       |      |

|      | fabricated by UCSB cleanroom)                                                                                                                                                                                                | 61   |

| 5.7  | Over-the-air antenna testing setup                                                                                                                                                                                           | 62   |

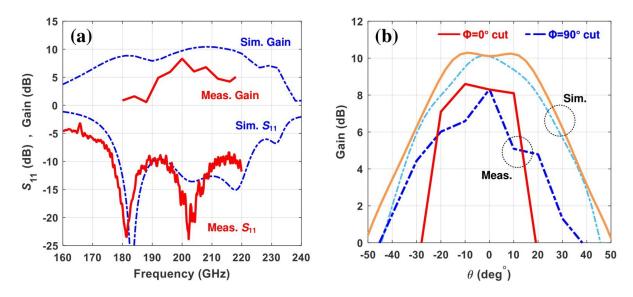

| 5.8  | $50\Omega$ matched $2\times 2$ patch antenna array results: (a) simulated and mea-                                                                                                                                           |      |

|      | sured gain and S11 vs. frequency, (b) gain vs. $\theta$ for $\phi = 0^{\circ}$ and $90^{\circ}$                                                                                                                              | 63   |

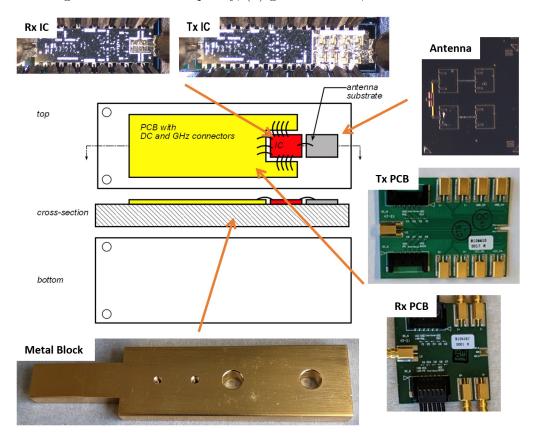

| 5.9  | Module cartoon drawing for the top and side views                                                                                                                                                                            | 63   |

| 5.10 | 200 GHz transmitter module: (a) block diagram, (b) photograph showing                                                                                                                                                        |      |

|      | the InP HBT transmitter IC and the patch antenna array on fused silica,                                                                                                                                                      |      |

|      | and (c) view of the full module, showing the PCB, connectors, heat sink,                                                                                                                                                     |      |

|      | and PTFE radome. 200 GHz receiver module: (a) block diagram, (b) pho-                                                                                                                                                        |      |

|      | tograph showing the InP HBT receiver IC and the patch antenna array on                                                                                                                                                       |      |

|      | fused silica, and (c) view of the full module, showing the PCB, connectors,                                                                                                                                                  |      |

|      | heat sink, and PTFE radome                                                                                                                                                                                                   | 64   |

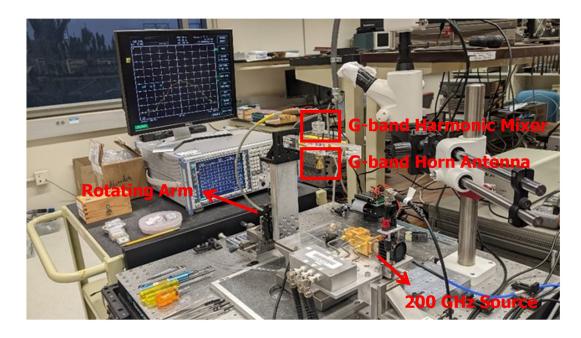

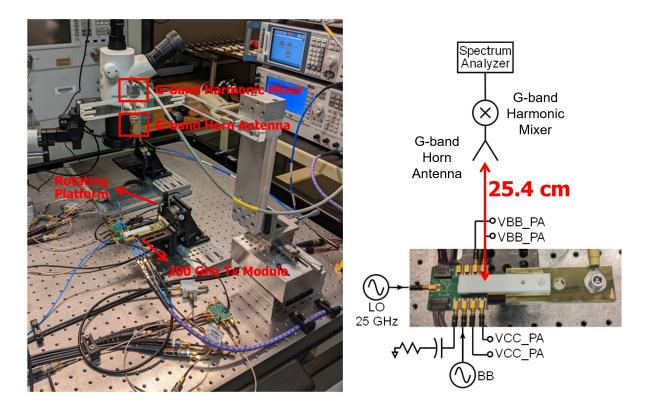

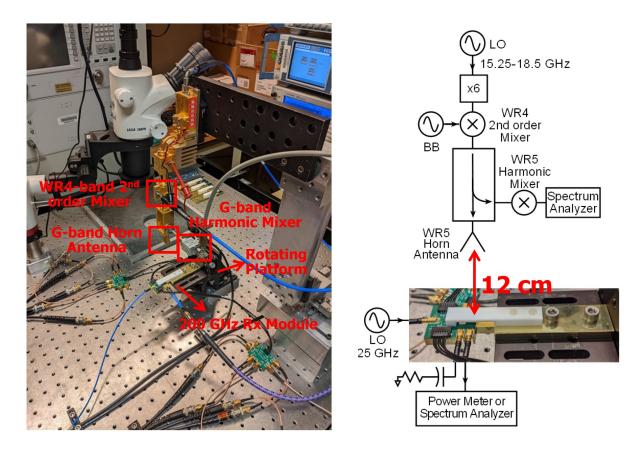

|      | Over-the-air transmitter module testing setup                                                                                                                                                                                | 65   |

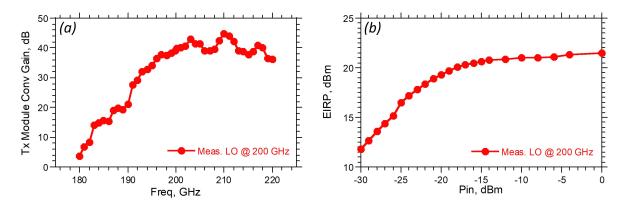

| 5.12 | (a) Measured conversion gain of the Tx module vs. RF frequency. (b)                                                                                                                                                          |      |

|      | Measured EIRP of the Tx module vs. baseband input power at 1 GHz                                                                                                                                                             | 66   |

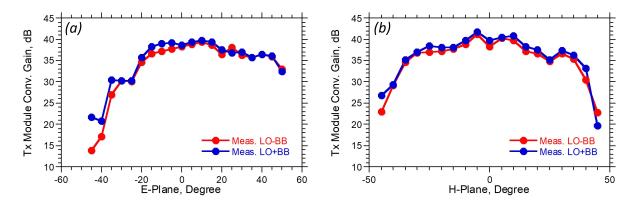

| 5.13 | Measured conversion gain of the Tx module vs. $\theta$ for (a) $\phi = 0^{\circ}$ and (b)                                                                                                                                    |      |

| 1    | $90^{\circ}$                                                                                                                                                                                                                 | 67   |

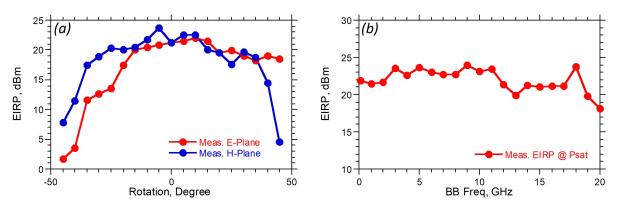

| 5.14 | Peak EIRP of the Tx module vs. (a) $\theta$ for $\phi = 0^{\circ}$ and $90^{\circ}$ , and (b)                                                                                                                                | 0.   |

| F 1F | baseband frequency                                                                                                                                                                                                           | 67   |

|      | Over-the-air receiver module testing setup                                                                                                                                                                                   | 68   |

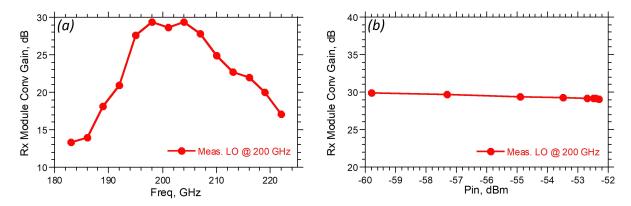

| 0.16 | Measured conversion gain of the Rx module vs. (a) RF frequency, and (b)                                                                                                                                                      | eo   |

| 5 17 | RF input power at 201 GHz                                                                                                                                                                                                    | 69   |

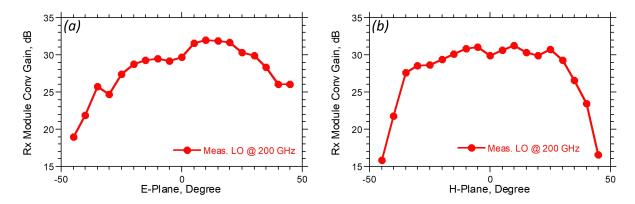

| J.11 | Measured conversion gain of the Rx module vs. $\theta$ for (a) $\phi = 0^{\circ}$ and (b) $90^{\circ}$ .                                                                                                                     | 69   |

|      | AUI                                                                                                                                                                                                                          | 11.7 |

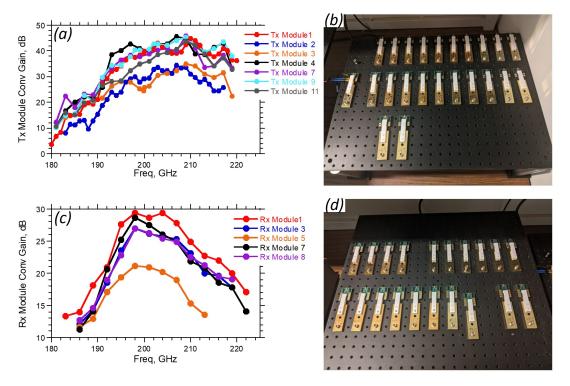

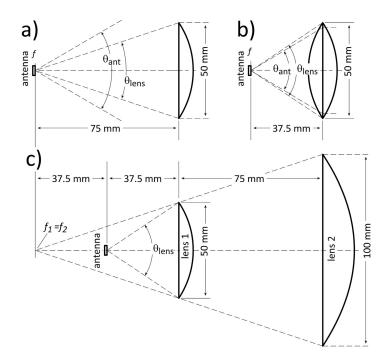

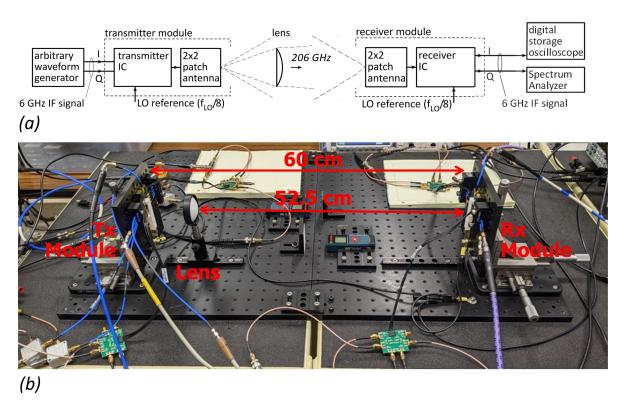

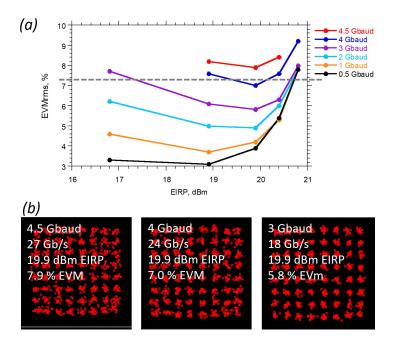

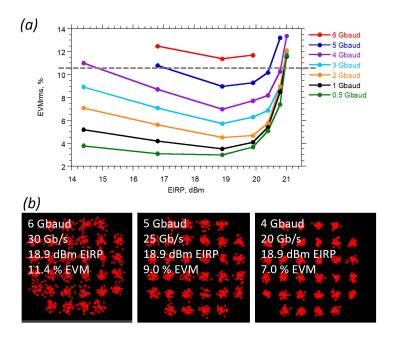

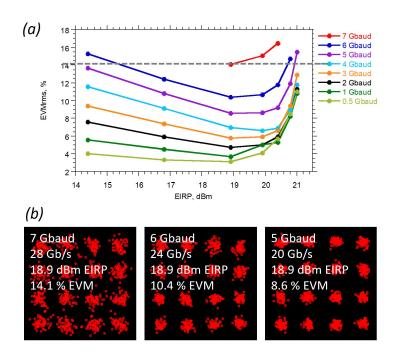

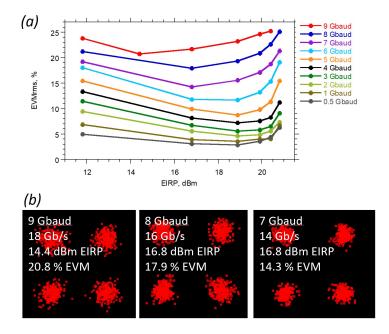

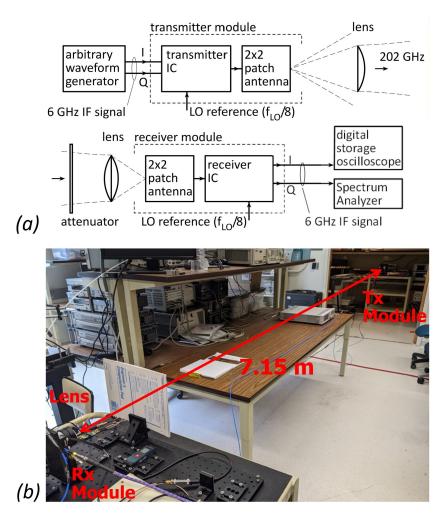

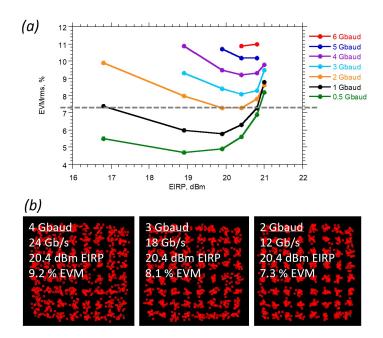

| 5.18 | (a) Measured conversion gain of all the working Tx modules, (b) photo of all the assembled Tx modules. (c) Measured conversion gain of all the working Rx modules, (b) photo of all the assembled Rx modules                                                                                                                                                                                                               | 70       |