# **UC Riverside**

# **UC Riverside Electronic Theses and Dissertations**

## **Title**

Radio Frequency Switch Design for 5G Communication and ESD Design on Advanced Technology

#### **Permalink**

https://escholarship.org/uc/item/8h09b4rb

## **Author**

Zhang, Feilong

# **Publication Date**

2019

# **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution-NonCommercial License, available at <a href="https://creativecommons.org/licenses/by-nc/4.0/">https://creativecommons.org/licenses/by-nc/4.0/</a>

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Radio Frequency Switch Design for 5G Communication and ESD Design on Advanced Technology

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Feilong Zhang

March 2019

Dissertation Committee:

Dr. Albert Wang, Chairperson

Dr. Sheldon Tan Dr. Ming Liu

| The Dissert | ation of Feilong Zhang is approved: |

|-------------|-------------------------------------|

|             |                                     |

| -           |                                     |

|             |                                     |

|             |                                     |

| -           |                                     |

|             |                                     |

| -           | Committee Chairperson               |

University of California, Riverside

## Acknowledgements

Foremost, I would like to express my utmost gratitude to my PhD advisor, Prof. Albert Wang for his guidance throughout my research at UCR. With his encouragement, support and supervision, I was motivated to learn about circuit design knowledge, critical thinking and time arrangement skills. Prof. Wang's motivation, integrity and immense knowledge inspired me. I hope to take what I learned from Prof. Wang with me and continue to thrive in my future career.

I would also like to extend my appreciation to Prof. Sheldon Tan and Prof. Ming Liu for serving as a member of my dissertation committee. I am grateful for their time and effort in reviewing my dissertation and their insightful comments.

It's my great pleasure to work with my fellow labmates, Dr. Fei Lu, Dr. Chenkun Wang, Dr. Qi Chen, Mr. Cheng Li, Mr. Mengfu Di and Ms. Zijin Pan, for the discussions and guidance. Their support and talent filled my PhD life with happiness and encouragement.

I appreciate Skyworks for providing me an opportunity to join as an internship. I want to thank my manager Dr. Weiheng Chang, my mentor Dr. Xingyi Hua, and my colleges Dr. Paul Wu and Dr. Yuting Chang. Their knowledge and unselfish share is invaluable throughout my life.

Last but not the least, I would like to express my sincerest gratitude to my parents for their support and love. Without your encouragement, I could not be able to finish my education path. Thank you.

#### ABSTRACT OF THE DISSERTATION

Radio Frequency Switch Design for 5G Communication and ESD Design on Advanced Technology

by

#### Feilong Zhang

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, March 2019 Dr. Albert Wang, Chairperson

The evolving 5G requires high data rate, low latency and broad coverage. Many new technologies are developed to fulfill these requirements, including multi RAT, carrier aggregation, advanced slot-based framework, mm-wave bands, beamforming and MIMO. These technologies require high isolation and harmonic filtering, low insertion loss, high linearity and fast switching RF front-end switches. In this dissertation, a design example of 3.5GHz switch is depicted in chapter 2 and an ESD protected 28GHz travelling wave switch is shown in chapter 3, which achieves comparable performance with state-of-art design and is the first ESD protected travelling wave switch on SOI.

On the other hand, as IC process evolving, traditional CMOS technology cannot fulfill the high speed and low power requirements. Therefore, advanced processes, FinFET and FDSOI technology start to be widely used, following with rising of cost and increase design complexity. Therefore, ESD reliability becomes a major concern. In chapter 4, we proposed a high area efficiency Cell-by-Cell SCR, which can save die area and provide less degradation on RF, mmwave and high-speed circuit performance due to its low parasitic associated with smaller area. To lower the trigger voltage, Cell-by-Cell DTSCR is proposed. Temperature effect of diode, SCR and DTSCR is illustrated, where the large performance variation across temperature of DTSCR rise a question mark for ESD designer.

Successful simulation before silicon is essential for first-silicon success and time-to-market, especially for high cost advanced technologies. So does for ESD protection. In chapter 5, 3D mixed-mode TCAD ESD simulation flow for FinFET devices is depicted. This flow covers mainstream ESD device type, including diode, ggMOS and SCR. Besides device level ESD simulation, chip level fast dynamic ESD protection simulation methodology using Verilog-A is developed. This methodology is verified with silicon and shows its capability to cover novel ESD devices and various ESD protection circuitry in chapter 6.

# CONTENTS

| Chapter 1. Introduction of 5G front-end                             | 1  |

|---------------------------------------------------------------------|----|

| 1.1. 5G background                                                  | 1  |

| 1.2. 5G RF front-end                                                | 2  |

| 1.3. 5G RF switch design challenges                                 | 5  |

| Chapter 2. Introduction of ESD protection                           | 7  |

| 2.1. Chip level ESD models                                          | 7  |

| 2.2. ESD design window                                              | 9  |

| 2.3. ESD protection strategy                                        | 10 |

| Chapter 3. 3.5GHz series-shunt RF switch design in SOI              | 14 |

| 3.1. SOI technology                                                 | 14 |

| 3.1.1. FDSOI and PDSOI                                              | 15 |

| 3.2. RF switch design matrix                                        | 16 |

| 3.2.1. Insertion loss                                               |    |

| 3.2.2. Isolation                                                    | 17 |

| 3.2.3. Linearity                                                    |    |

| 3.2.4. Power handling ability                                       |    |

| 3.2.5. Figure of merits                                             | 23 |

| 3.3. 3.5GHz T/Rx Switch design consideration                        | 23 |

| 3.4. 3.5GHz T/Rx Switch design in SOI                               | 25 |

| 3.4.1. Negative voltage generator design                            |    |

| 3.4.2. Switch Topology and design                                   | 30 |

| Chapter 4. Millimeter Wave Switch design in SOI for 5G applications | 35 |

| 4.1. Introduction of mm-wave switch design                          | 35 |

| 4.2. Travelling wave switch basics                                  | 37 |

| 4.3. Travelling wave switch design in SOI                           | 41 |

| 4.3.1. Circuit design                                               | 41 |

| 4.3.2. Microstrip Line design                                      | 44 |

|--------------------------------------------------------------------|----|

| 4.3.3. Measurement result                                          | 47 |

| 4.4. Travelling wave switch ESD protection and co-design           | 47 |

| 4.4.1. ESD PROTECTION                                              | 47 |

| 4.4.2. Co-design                                                   | 48 |

| 4.5. Measurement and discussion                                    | 50 |

| Chapter 5. High area efficiency ESD device and temperature concern | 54 |

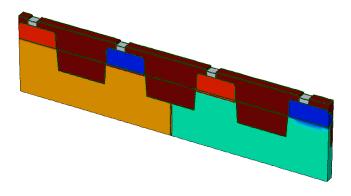

| 5.1. Cell-By-Cell SCR                                              | 54 |

| 5.1.1. Cell-By-Cell SCR ESD structure                              | 55 |

| 5.1.2. TLP measurement results                                     | 58 |

| 5.1.3. Scalability and layout perspective                          | 60 |

| 5.1.4. Theoretical analysis of cell-by-cell SCR                    | 63 |

| 5.2. Cell-by-Cell DTSCR structure                                  | 66 |

| 5.3. Temperature awareness in DTSCR structure design               | 68 |

| 5.3.1. Experimental Result and device physics                      | 69 |

| 5.3.2. TCAD simulation on DTSCR structure                          | 74 |

| Chapter 6. FinFET ESD design with 3D TCAD                          | 78 |

| 6.1. FinFET Technology                                             | 79 |

| 6.1.1. Comparison with FDSOI technology                            | 80 |

| 6.2. FinFET ESD design                                             | 80 |

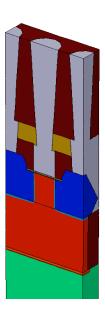

| 6.2.1. Systematic ESD protection design method                     | 80 |

| 6.2.2. ESD protection device layout in FinFET                      | 83 |

| 6.3. FinFET ESD protection devices                                 | 83 |

| 6.3.1. Gated diode:                                                | 83 |

| 6.3.2. STI diode                                                   | 84 |

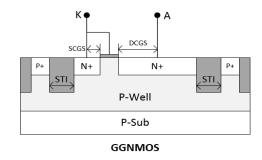

| 6.3.3. Grounded-Gate MOS (GGMOS)                                   | 85 |

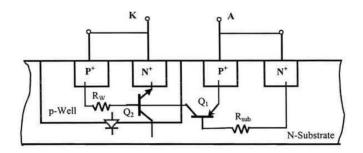

| 6.3.4. SCR                                                         | 86 |

| 6.4. 3D TCAD simulation for FinFET ESD protection devices          | 87 |

| 6.4.1. TCAD process of creating 3D FinFET device                   |    |

| 6.4.2. ESD simulation setup                                        | 92 |

| 6.4.3. Simulation guide ESD design                           | 95  |

|--------------------------------------------------------------|-----|

| Chapter 7. Full-Chip ESD Protection Simulation Methodology   | 102 |

| 7.1. Introduction of Circuit level ESD Protection Simulation | 102 |

| 7.2. Design Validation and Discussions                       | 107 |

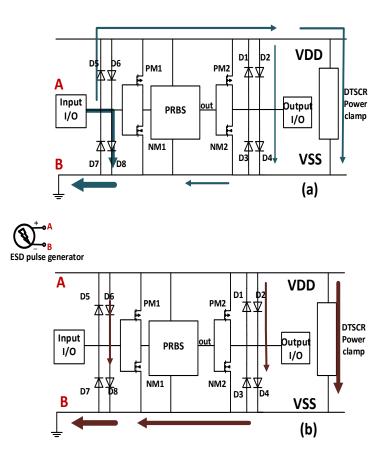

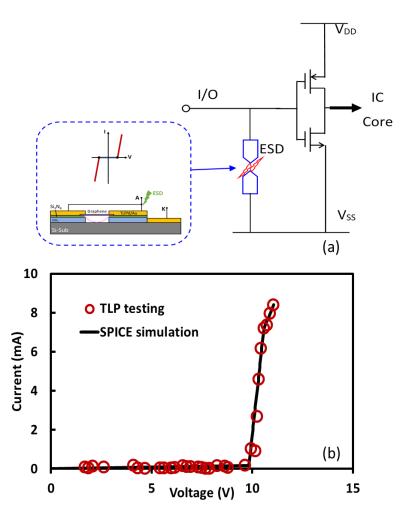

| 7.2.1. Input Buffer with Full ESD Protection                 | 107 |

| 7.2.2. Large IC with Snapback DTSCR ESD Protection           | 115 |

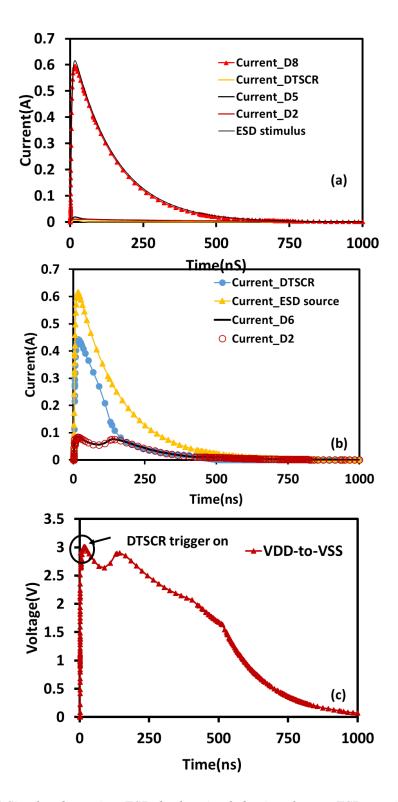

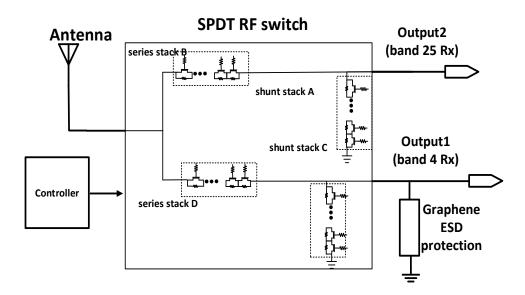

| 7.2.3. RF Switch Circuit with Graphene NEMS ESD Structure    | 118 |

| 7.2.4. Multiple power domain ESD failure                     | 122 |

| Chapter 8. Conclusion                                        | 124 |

|                                                              |     |

# LIST OF FIGURES

| Figure 1-1 3GPP 5G time-line                                                                                                                      | 1    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1-2 The FCC is driving key spectrum initiatives to enable 5G. [1]                                                                          | 2    |

| Figure 1-3 Front-end-module block diagram [2]                                                                                                     | 3    |

| Figure 1-4 illustration of MIMO and Beamforming [3]                                                                                               | 4    |

| Figure 1-5 Proposed 5G architecture                                                                                                               | 5    |

| Figure 1-6 Cross-talk between switch blocks in switch array                                                                                       | 6    |

| Figure 2-1 ESD test models                                                                                                                        | 7    |

| Figure 2-2 ESD protection device characterization instruments                                                                                     | 9    |

| Figure 2-3 ESD design window                                                                                                                      | . 10 |

| Figure 2-4 ESD protection diagram for HBM                                                                                                         | . 11 |

| Figure 2-5 Diode-string for ESD protection of mixed voltage application                                                                           | . 12 |

| Figure 2-6 GGMOS for ESD protection of mixed voltage application                                                                                  | . 12 |

| Figure 2-7 CDM ESD protection scheme                                                                                                              | . 13 |

| Figure 3-1 SOI penetrating RF switch market [4]                                                                                                   | . 14 |

| Figure 3-2 SOI cross section [5]                                                                                                                  | . 15 |

| Figure 3-3 Simplified SNR in receiver                                                                                                             | . 17 |

| Figure 3-4 Layout concern in switch design                                                                                                        | . 18 |

| Figure 3-5 RxBn caused by BSW isolation.                                                                                                          | . 19 |

| Figure 3-6 Kink effect.                                                                                                                           | . 20 |

| Figure 3-7 Body connection of SOI NFET                                                                                                            | . 20 |

| Figure 3-8 A sample of negative voltage generator output load-line                                                                                | . 21 |

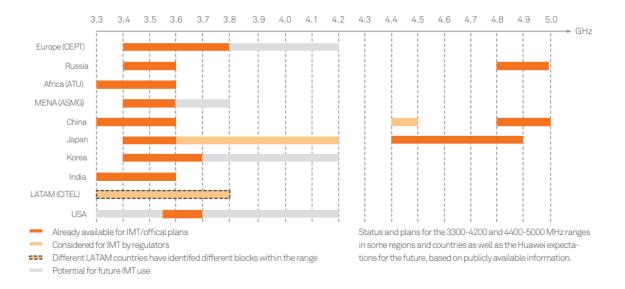

| Figure 3-9 Global availability and planning of the 3300-4200 MHz and 4400-5000 MF cy ranges [source. Huawei – 5G Spectrum public policy position] |      |

| Figure 3-10 Control diagram of antenna switch and band switch                                                                                     | . 26 |

| Figure 3-11 Block diagram of SPDT switch core and bias                                                                                            | . 26 |

| Figure 3-12 Block diagram of negative voltage generator                                                                                           | . 28 |

| Figure 3-13 Current flow during CLK rising to VDD \                                                                                               | . 28 |

| Figure 3-14 Current flow during CLK falling to GND                                                                                                | . 29 |

| Figure 3-15 Layout of designed negative voltage generator                                                                                         | . 29 |

|                                                                                                                                                   |      |

| Figure 3-16 Simulation result of designed charger pump.                                                                                                                                                                | . 30 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

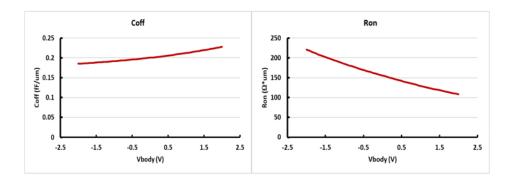

| Figure 3-17 Ron and Coff change with body-biasing voltage                                                                                                                                                              | . 30 |

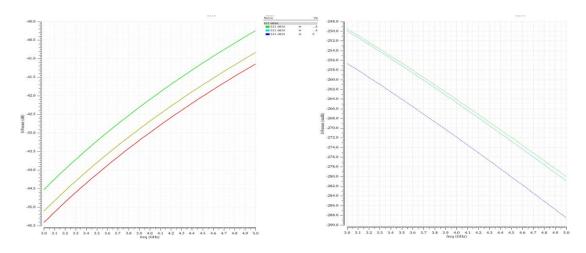

| Figure 3-18 Simulated I.L. and Isolation with body bias voltage change                                                                                                                                                 | . 32 |

| Figure 3-19 Schematic of SPDT switch core                                                                                                                                                                              | . 32 |

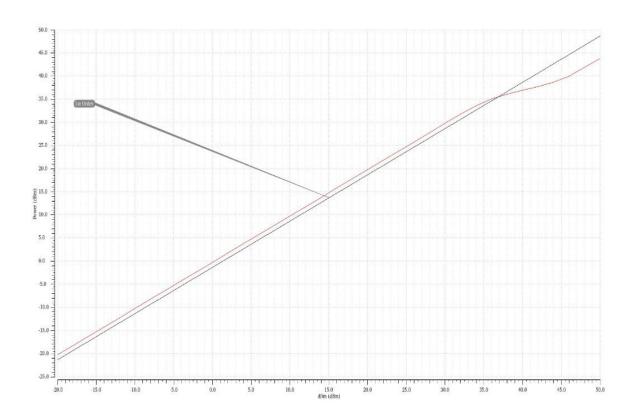

| Figure 3-20 Simulated input P1dB of the SPDT switch                                                                                                                                                                    | . 33 |

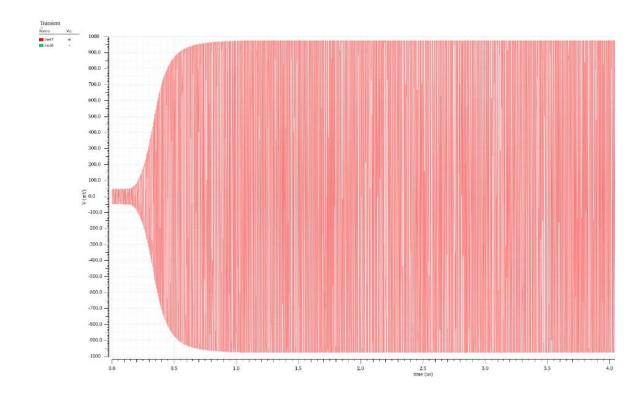

| Figure 3-21Simulated switching time of designed SPDT switch                                                                                                                                                            | . 34 |

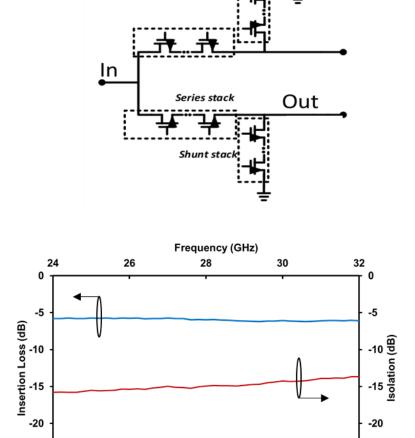

| Figure 4-1 measurement result of SPDT switch on 28GHz using series-shunt topology [23]                                                                                                                                 |      |

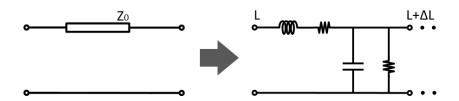

| Figure 4-2 Equivalent circuit of transmission line                                                                                                                                                                     | . 38 |

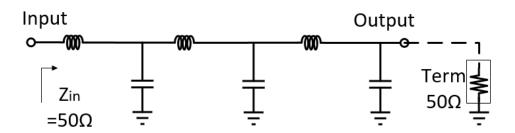

| Figure 4-3 schematic of artificial transmission line                                                                                                                                                                   | . 38 |

| Figure 4-4 Schematic of a SPST travelling wave switch                                                                                                                                                                  | . 39 |

| Figure 4-5 Input impedance of on and off state of SPST switch                                                                                                                                                          | . 40 |

| Figure 4-6 Simulated S21 of on and off state                                                                                                                                                                           | . 40 |

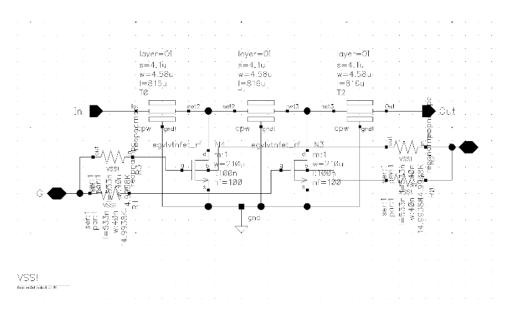

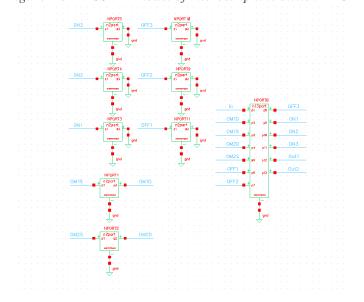

| Figure 4-7 Schematic of the SPDT traveling wave switch design in this work                                                                                                                                             | . 42 |

| Figure 4-8 Extracted S parameter file with on/off state                                                                                                                                                                | . 43 |

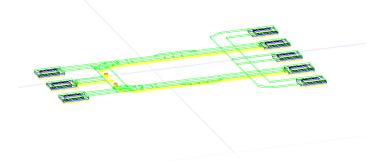

| Figure 4-9 HFSS EM model of microstrip line switch BEOL                                                                                                                                                                | . 43 |

| Figure 4-10 Cadence co-simulation test bench with extracted EM model                                                                                                                                                   | . 43 |

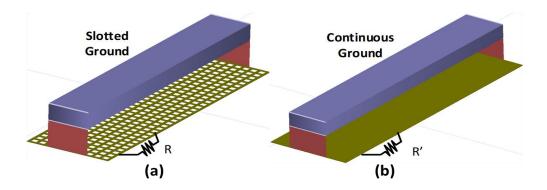

| Figure 4-11 Comparison of microstrip lines: (a) Case-1 uses ML9-ML1 with slots in the ML1 ground plane, (b) Case-2 uses ML9-ML1 without slots in the ML1 ground plane                                                  |      |

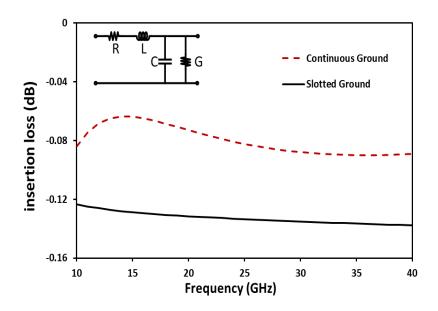

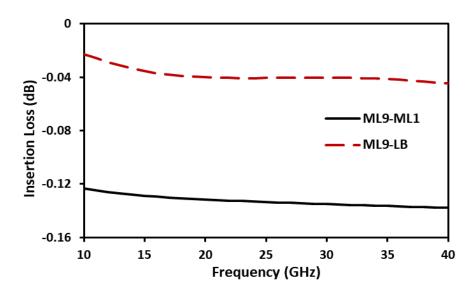

| Figure 4-12 Insertion loss (normalized to the same $\beta L$ ) for the two $50\Omega$ microstrip line by HFSS simulation.                                                                                              |      |

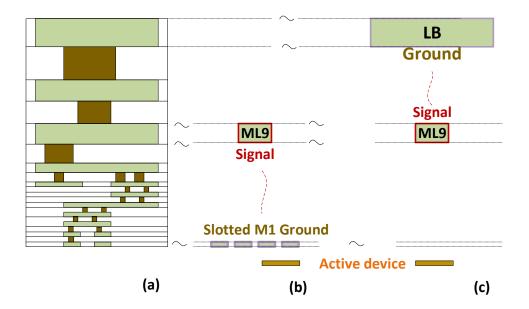

| Figure 4-13 Illustration of the two microstrip line cases: (a) 11-metal stack in 22nm SC (b) Case-1 of ML9-ML1 with slots, (c) Case-3 of ML9-LB microstrip lines. The distances of ML9-ML1 and ML9-LB are almost same. |      |

| Figure 4-14 Comparison of insertion loss (normalized to the same βL) between Case-1 ML9-ML1 with slots and Case-3 of ML9-LB microstrip lines by HFSS simulation                                                        |      |

| Figure 4-15 4-diode-string ESD protection is used to protect the 28GHz switches                                                                                                                                        | . 48 |

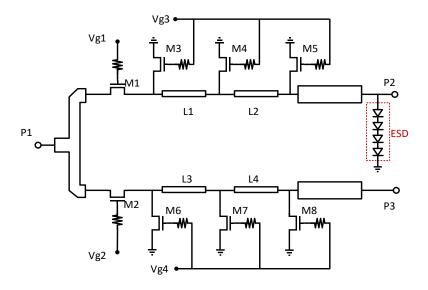

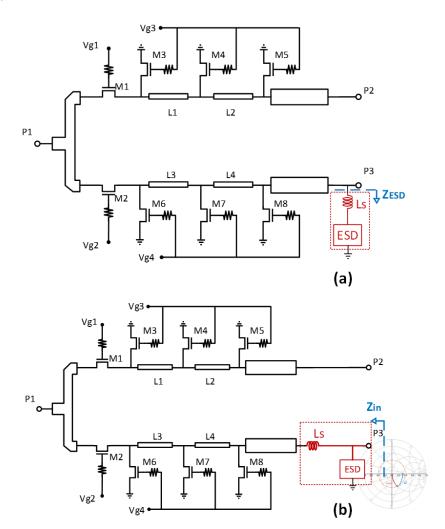

| Figure 4-16 (a) Conventional broadband ESD protection co-design method (b) ESD codesign used in this work                                                                                                              |      |

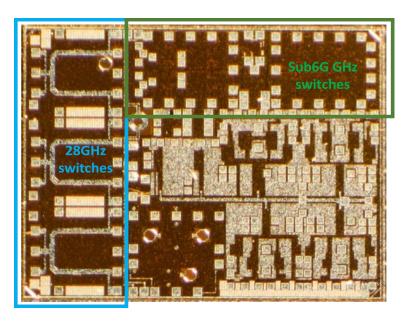

| Figure 4-17 Die photo for designed 28GHz switches and sub6GHz switches                                                                                                                                                 | .50  |

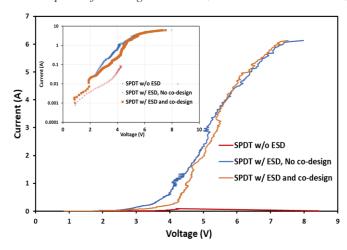

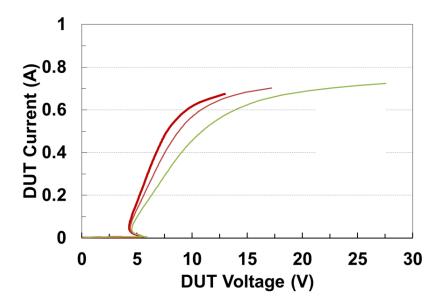

| Figure 4-18 Measured 100ns TLP I-V curve for SPDT switch of three splits featuring (without ESD protection, (2) with ESD protection, but no co-design optimization, (3) with ESD                                       |      |

| protection and co-design optimized. In the top-right corner, the current is presented in log scale with the same color code5                                                                                                     |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

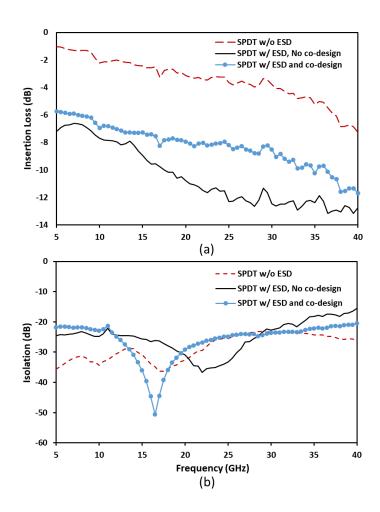

| Figure 4-19 Measured insertion loss and isolation for SPDT switch of three splits featuring (1) without ESD protection, (2) with ESD protection, but no co-design optimization, (3) with ESD protection and co-design optimized. |    |

| Figure 5-1 Top view of conventional SCR ESD layout: (a) multi-finger layout and (b) classic parallel finger layout.                                                                                                              | 55 |

| Figure 5-2 TCAD simulation result of planar SCR shows that body pickup conducts ver small current during the whole ESD event.                                                                                                    | •  |

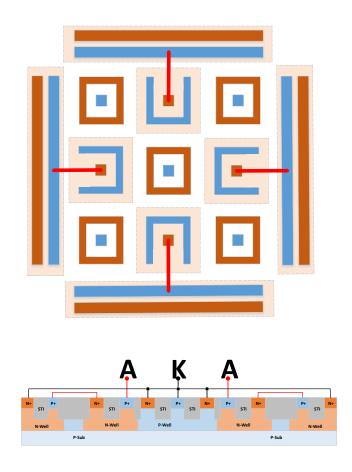

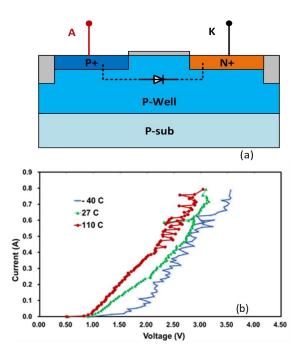

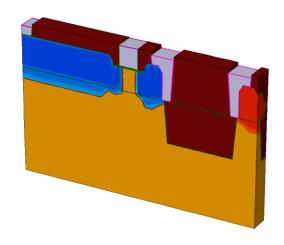

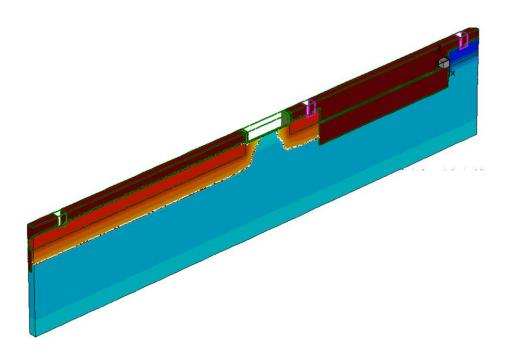

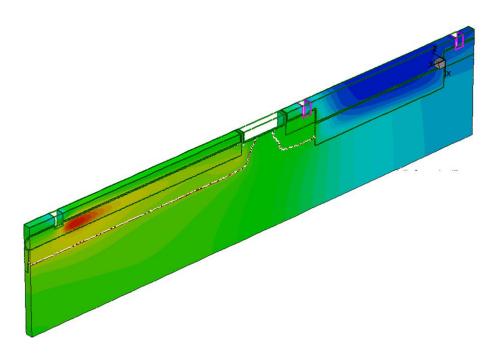

| Figure 5-3 Cross section of designed Cell-by-Cell SCR from TCAD                                                                                                                                                                  | 57 |

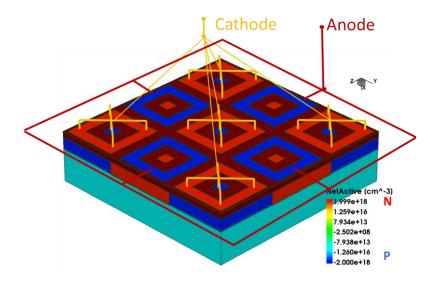

| Figure 5-4 3D view of designed Cell-by-Cell SCR structure                                                                                                                                                                        | 58 |

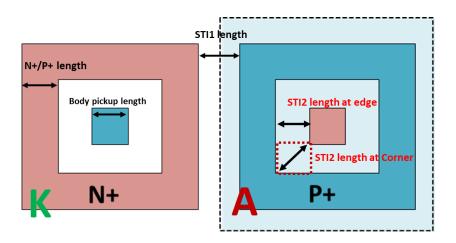

| Figure 5-5 Detailed view of A-cell and K-cell. STI is isolation.                                                                                                                                                                 | 59 |

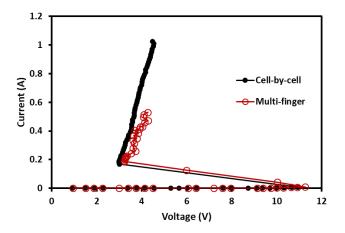

| Figure 5-6 Measured ESD discharging I-V curves for the SCR ESD cell array and multi-finger SCR ESD structures by TLP.                                                                                                            |    |

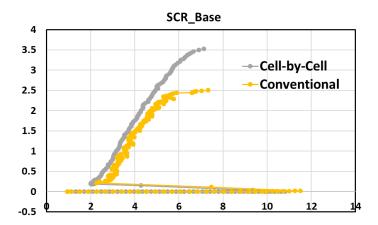

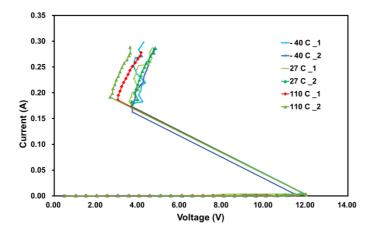

| Figure 5-7 Measurement result of Cell-by-Cell and Conventional SCR on 22nm FDSOI                                                                                                                                                 |    |

| Figure 5-8 Measurement result of Cell-by-Cell and Conventional SCR with 0.5um STI1 length                                                                                                                                        |    |

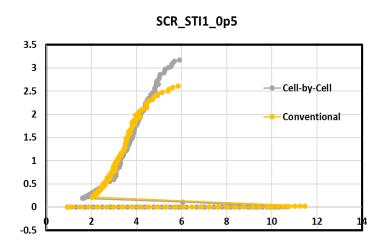

| Figure 5-9 Layout for 4×4 Cell-by-Cell SCR array6                                                                                                                                                                                | 63 |

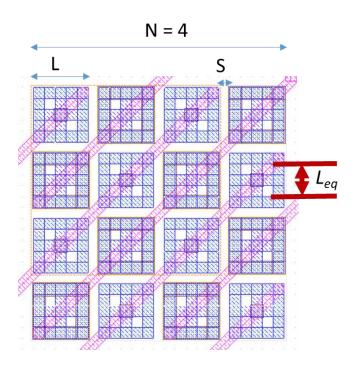

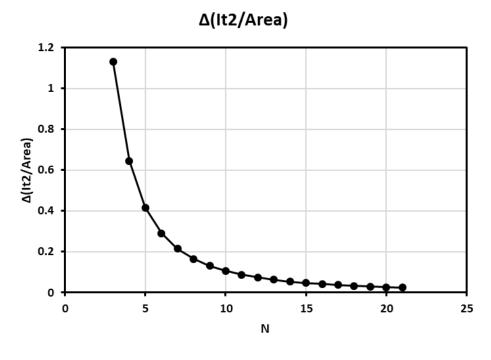

| Figure 5-10 Area efficiency relationship to array size                                                                                                                                                                           | 65 |

| Figure 5-11 Increasing rate related to array size6                                                                                                                                                                               | 65 |

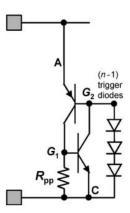

| Figure 5-12 Schematic of DTSCR structure.                                                                                                                                                                                        | 66 |

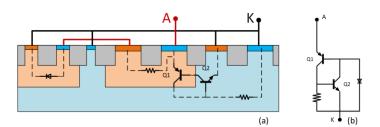

| Figure 5-13 Structure of Cell-by-Cell DTSCR                                                                                                                                                                                      | 67 |

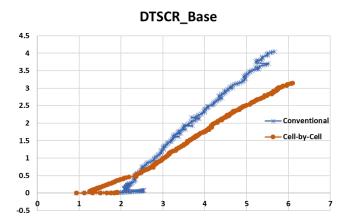

| Figure 5-14 Measured TLP I-V curve of Cell-by-Cell and conventional DTSCR                                                                                                                                                        | 68 |

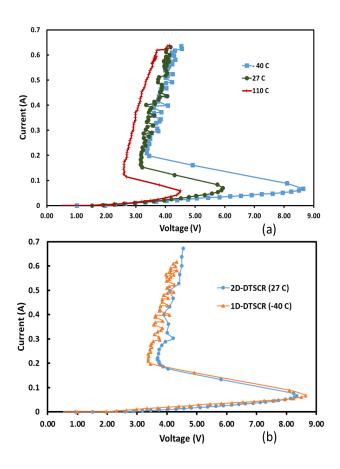

| Figure 5-15 (a) Cross-section of Gated-diode (b) TLP measurement result of Gated-diode under different temperature. (Width = 30um)                                                                                               | 69 |

| Figure 5-16 (a) Cross-section of designed SCR structure; (b)TLP measurement result of SCR under different temperature. (Width = 30um)                                                                                            |    |

| Figure 5-17 (a) Cross-section of designed DTSCR; (b) equivalent circuit of DTSCR structure                                                                                                                                       | 71 |

| Figure 5-18 (a) TLP measurement result of 1-diode DTSCR under different temperature (b) TLP measurement result of 1-diode DTSCR and 2-diodes DTSCR                                                                               |    |

| Figure 5-19 Schematic of a full protected input buffer with DTSCR serves as power                                                                                                                                                |    |

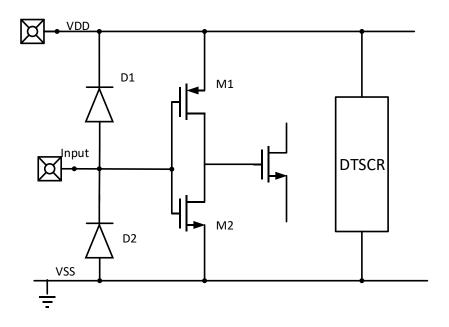

| clamp 7                                                                                                                                                                                                                          | 74 |

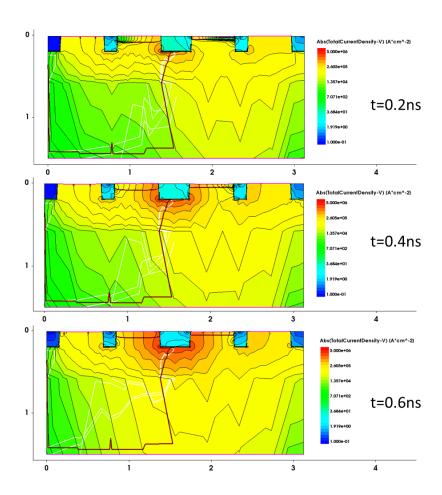

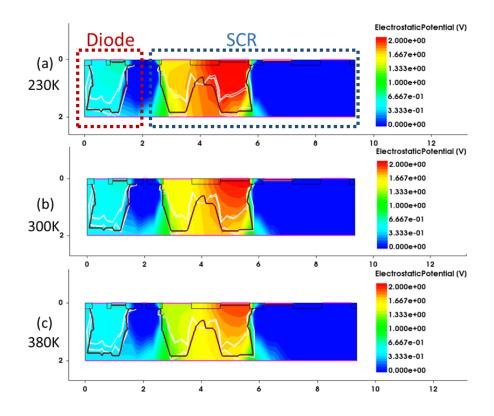

| Figure 5-20 Electrostatic potential distribution on DTSCR at 0.4ns under different temperature: (a) 230K; (b) 300K; (c) 380K |    |

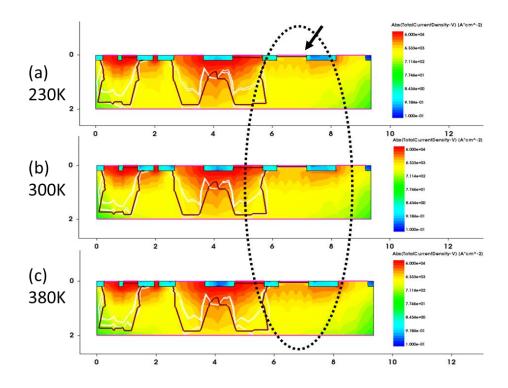

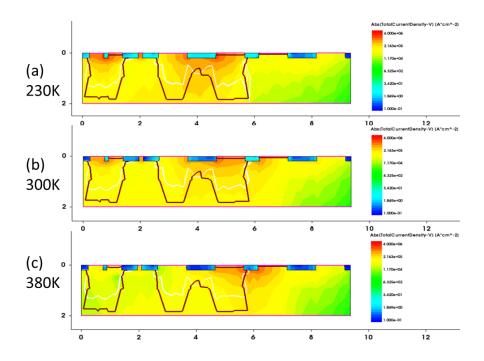

|------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5-21 Current density distribution on DTSCR at 0.4ns under different temp(a) 230K; (b) 300K; (c) 380K                  |    |

| Figure 5-22 Current density distribution on DTSCR at 4ns under different tempe (a) 230K; (b) 300K; (c) 380K                  |    |

| Figure 6-1 CMOS development road map [45]                                                                                    | 79 |

| Figure 6-2 (a) 3D FinFET structure; (b) cross-section across the fin                                                         | 80 |

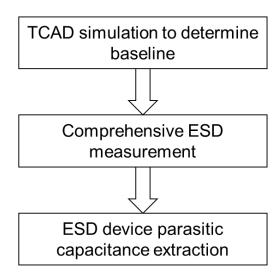

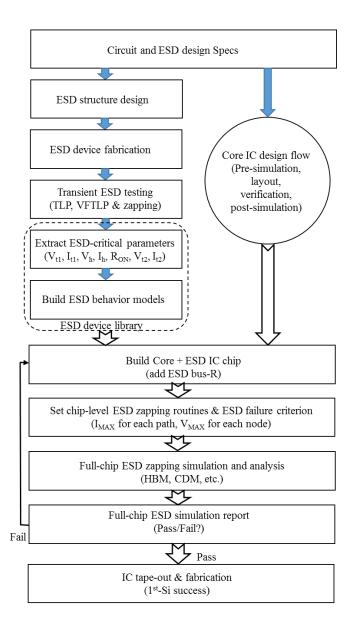

| Figure 6-3 ESD test-chip design flow                                                                                         | 81 |

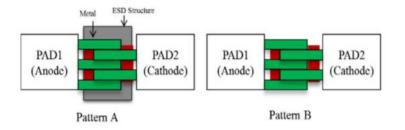

| Figure 6-4 De-embedding ESD testing patterns A (full ESD structure) and B (Si removed)                                       |    |

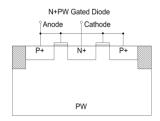

| Figure 6-5 Cross-section of planar Gated-diode (N+/PW Gated-diode)                                                           | 84 |

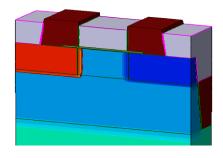

| Figure 6-6 Structure of gated diode in FinFET                                                                                | 84 |

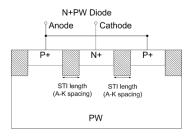

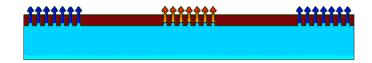

| Figure 6-7 planar STI diode x-section (N+/PW diode)                                                                          | 85 |

| Figure 6-8 Vertical STI diode in FinFET.                                                                                     | 85 |

| Figure 6-9 Planar GGNMOS cross-section                                                                                       | 86 |

| Figure 6-10 3D structure of GGNMOS in FinFET                                                                                 | 86 |

| Figure 6-11 Cross-section of planar SCR                                                                                      | 87 |

| Figure 6-12 3D structure of SCR in FinFET.                                                                                   | 87 |

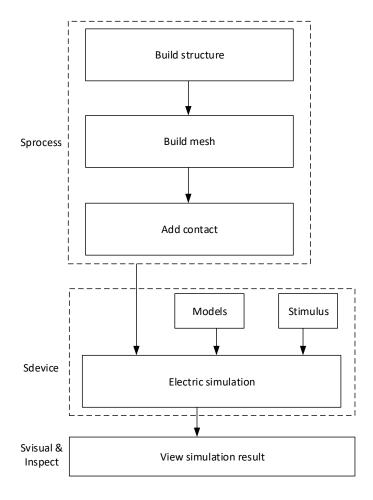

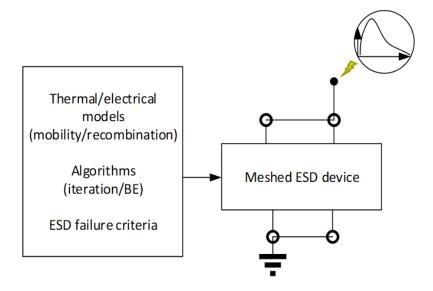

| Figure 6-13 Mixed-mode TCAD simulation flow                                                                                  | 88 |

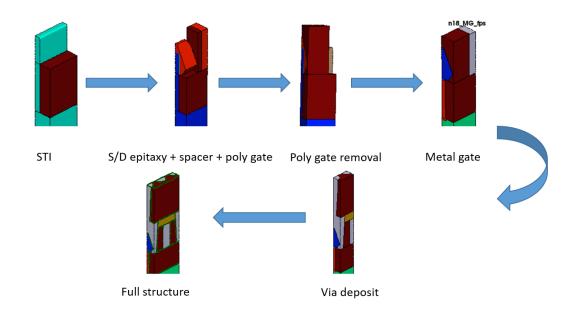

| Figure 6-14 TCAD process to build a FinFET                                                                                   | 89 |

| Figure 6-15 Process of Source/Drain epitaxy                                                                                  | 90 |

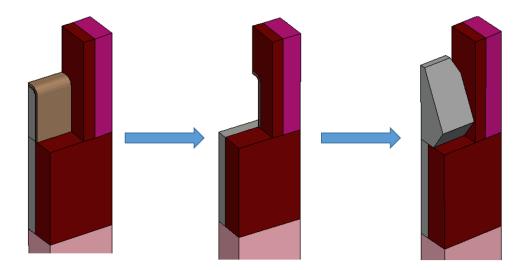

| Figure 6-16 Final structure of FinFET built in TCAD                                                                          | 91 |

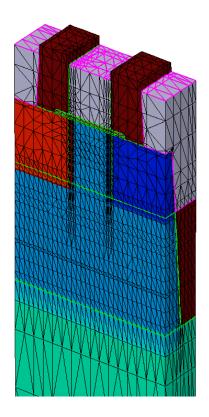

| Figure 6-17 Mesh of a TCAD built Gated-diode in FinFET process                                                               | 92 |

| Figure 6-18 Sdevice simulation bench                                                                                         | 93 |

| Figure 6-19 ESD simulation related models                                                                                    | 94 |

| Figure 6-20 Doping concentration                                                                                             | 95 |

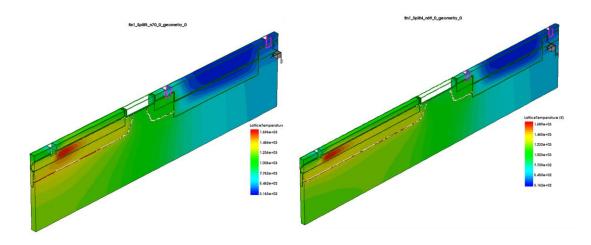

| Figure 6-21 Lattice temperature                                                                                              | 96 |

| Figure 6-22 Current density                                                                                                  | 96 |

| Figure 6-23 Simulated I-V curve of GGNMOS with snapback                                                                      | 97 |

| Figure 6-24 Mixed-mode TCAD simulated result of GGNMOS with different fin number (width)98                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-25 Mixed-mode simulation result of GGNMOS with different gate length 99                                                                                                                                                                                                          |

| Figure 6-26 Lattice temperature simulation show minor change between GGNMOS with different gate length                                                                                                                                                                                    |

| Figure 6-27 Mixed-mode simulation result of GGNMOS with different DCGS length 100                                                                                                                                                                                                         |

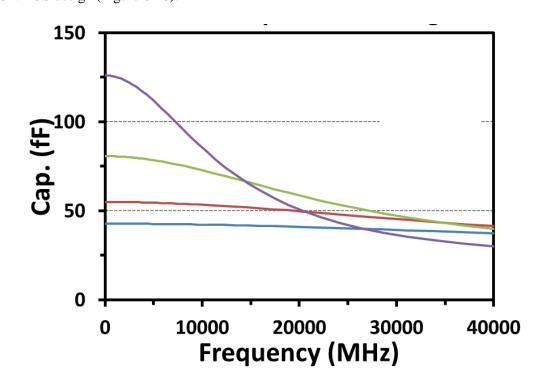

| Figure 6-28 TCAD simulation result of parasitic capacitance                                                                                                                                                                                                                               |

| Figure 7-1 A flow chart for the new full-chip circuit-level ESD protection circuit simulation and analysis method                                                                                                                                                                         |

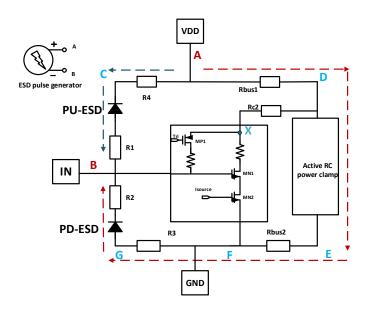

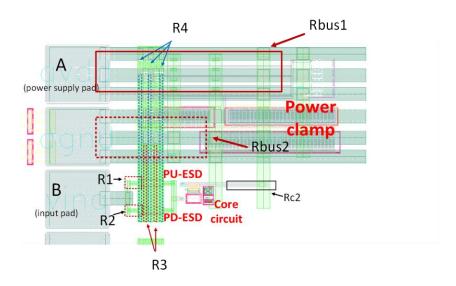

| Figure 7-2 Simplified functional diagram for the input buffer IC with full ESD protection for chip-level ESD protection circuit simulation. The key ESD metal resistances were extracted from its layout below                                                                            |

| Figure 7-3 Layout of the ESD-protected input buffer IC where key ESD metal resistances are extracted for full-chip ESD circuit simulation                                                                                                                                                 |

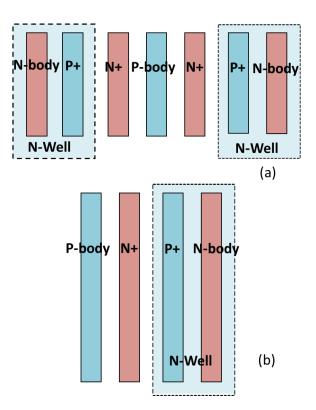

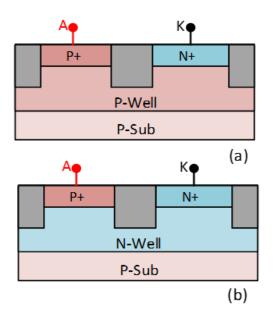

| Figure 7-4 Simplified cross-sections for the STI ESD diodes in this work: (a) N+/P-well PD-ESD diode and (b) P+/N-well PU-ESD diode                                                                                                                                                       |

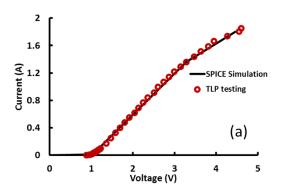

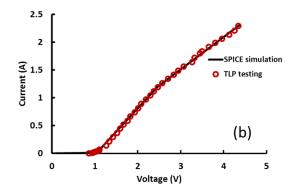

| Figure 7-5 Transient ESD I-V curves measured by TLP for, (a) N+/P-well diode (forward ESD mode), (b) P+/N-well diode (forward ESD mode) and (c) P+/N-well diode (reverse ESD mode), match well with SPICE simulation using the extracted ESD behavior models accordingly.                 |

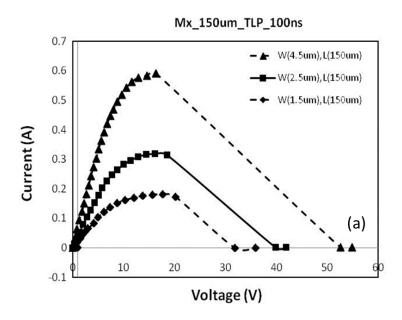

| Figure 7-6 Transient ESD I-V curves by TLP testing for an example M <sub>X</sub> metal stack (M3-M7) used for ESD interconnects in this work                                                                                                                                              |

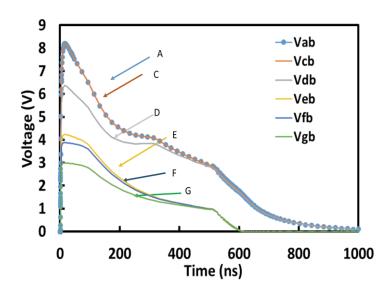

| Figure 7-7 Simulated transient node voltages for the ESD-protected input buffer IC using the new ESD simulation method under an ND mode $2KV$ HBM ESD zapping to the input pad (B) against $V_{DD}\left(A\right)$ . Note that all voltages are referred to node-B                         |

| Figure 7-8 Simulated branch currents (Left axis) and core circuit transistor voltages (Right axis) under the ND mode ESD zapping from Input pad (B) to $V_{DD}$ (A)                                                                                                                       |

| Figure 7-9 An EMMI image under HBM zapping reveals a hot spot at the PU-ESD diode, indicating an ESD weak point in the design                                                                                                                                                             |

| Figure 7-10 A functional schematic for the ESD-protected PRBS IC where gated ESD diodes (D1-D8) protect I/O pins and the power clamp is a DTSCR                                                                                                                                           |

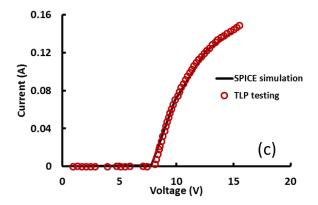

| Figure 7-11 ESD I-V curves by TLP testing (Blue) agree well with SPICE simulation (Orange) using the extracted ESD behavior models for: (a) gated diode and (b) DTSCR116                                                                                                                  |

| Figure 7-12 Two exemplary full-chip ESD simulation cases: (a) positive Input-to- $V_{SS}$ HBM zapping, and (b) positive $V_{DD}$ -to- $V_{SS}$ zapping. The arrowed lines indicate the possible ESD discharging paths with the thickness suggesting the amount of ESD discharging current |

| Figure 7-13 Simulated transient ESD discharging behaviors for two ESD zapping cases: (a) Input-to- $V_{SS}$ , and (b) $V_{DD}$ -to- $V_{SS}$ .                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7-14 A non-traditional above-Si gNEMS ESD protection structure: (a) gNEMS cross-section and ESD circuit scenario, and (b) ESD discharging I-V curves by TLP testing and SPICE simulation using its behavior device model match each other well. TLP testing shows $V_{t1}\sim10V$ and $I_{t2}\sim8.4$ mA for the gNEMS ESD device |

| Figure 7-15 A functional schematic of SPDT RF antenna switch circuit made in 45nm SOI CMOS with a gNEMS ESD protection fabricated by post-CMOS processing                                                                                                                                                                                |

| Figure 7-16 (a) Simulated ESD current distribution for the SPDT circuit with gNMES ESD protection at the output pin. (b) Simulated output voltage for the ESD-protected SPDT circuit peaks at above 30V due to poor $R_{ON}$ of gNMES ESD device                                                                                         |

| Figure 7-17 A multiple power domain IC with ESD protection: (a) ESD protection schematics, (b) simulated transient voltage at the $V_{DD2}$ pad in comparison with the node breakdown voltage.                                                                                                                                           |

# LIST OF TABLES

|        | Table 3-1 design parameters of SPDT switch                                         | . 31 |

|--------|------------------------------------------------------------------------------------|------|

|        | Table 3-2 Simulation result of design SPDT switch in comparison with SKYA21038     | . 34 |

|        | Table 4-1 Meaningful mm-wave switch performance comparison.                        | . 53 |

|        | Table 5-1 Summary for the measured ESD critical parameters for the SCR ESD cell ar | ray  |

| and mu | ulti-finger SCR ESD structures by TLP measuring                                    | . 60 |

# Chapter 1. Introduction of 5G front-end

#### 1.1. 5G background

As demand grows for ubiquitous wireless connectivity and the promise of new and previously unimagined applications, such as autonomous vehicles, artificial intelligence, telemedicine and virtual reality. These applications requires advanced algorithm, hardware processing speed and advance wireless communication techniques.

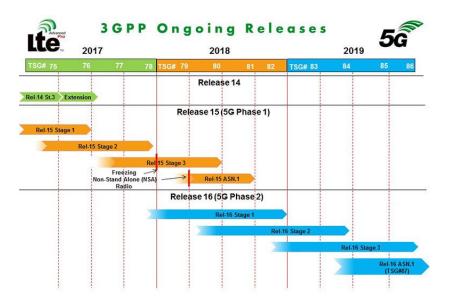

5G (5th Generation) is the latest generation of cellular mobile communications. 5G performance targets high data rate, reduced latency, energy saving, cost reduction, higher system capacity, and massive device connectivity. 3rd Generation Partnership Project (3GPP) submitted 5G NR (New Radio) as its 5G communication standard proposal. 5G NR include bands below 6 GHz (FR1), and higher frequencies above 24 GHz and into the millimeter waves range (FR2). As shown in Figure 1-1, the first phase of 5G specifications in Release-15 will be completed by April 2019 to accommodate the early commercial deployment, which focus on FR1 bands below 6GHz (n77, n78, n79).

Figure 1-1 3GPP 5G time-line

The second phase in Release-16 is due to be completed by April 2020 for submission to the International Telecommunication Union (ITU) as a candidate of IMT-2020 technology [1]. The ITU IMT-2020 specification demands speeds up to 20 Gbps. To achieve this, several technologies are under developing, including multi-RAT (radio-access-technology), advanced modulation (i.e. CP-OFDM, DFT-OFDM), advanced framework (higher frequency subcarrier and shorter slot), wide channel bandwidths (up to 100MHz for one channel), massive MIMO, beamforming tracking and advanced small cell techniques. The details will be discussed in Chapter 2.

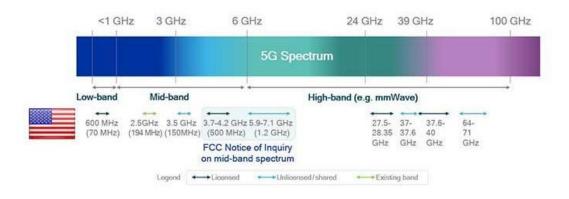

Figure 1-2 shows the key spectrum Federal Communications Commission (FCC) is driving toward 5G. The 3.5GHz and 28GHz frequency bands will be the first commercial 5G bands with highest potential for global harmonization over time.

Figure 1-2 The FCC is driving key spectrum initiatives to enable 5G. [1]

#### 1.2. 5G RF front-end

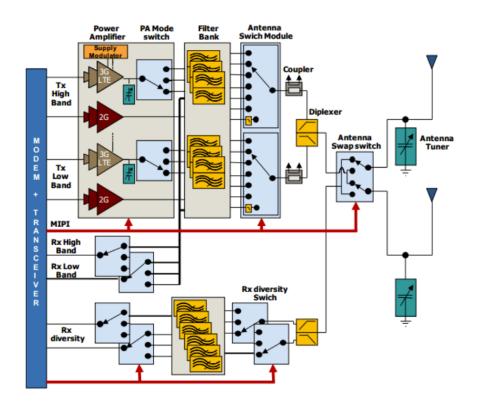

In a radio receiver circuit, the radio frequency front end (RFFE) is a generic term for all the circuitry between a receiver's antenna inputs up to the mixer stage. It consists of all the components in the receiver that process the RF signal from antenna before converting to intermediate frequency (IF), and in the transmitter that amplify the RF signal before signal been sent out to antenna. The main blocks include Antenna switch module (ASM), Band switch (BSW), diplexer, duplexer, filter,

low-noise amplifier (LNA), power amplifier (PA), matching networks and Mobile Industry Processor Interface (MIPI).

Figure 1-3 Front-end-module block diagram [2]

As wireless communication technology evolves, an increasing number of RFFE components are integrated in the front-end module with smaller chip size. Back to 1990s, cell phone only support GSM bands, however, nowadays a typical 4G cell phone can support more than 10 bands. The rising band number increases complexity of RF front-end design complexity. For example, LNA needs different input matching inductors for different bands, and the source degeneration inductor have to be designed with trade off with noise performance to balance it across different bands. PA needs to cover wider bandwidth with flat frequency response but not sacrifice power efficiency. More duplexers are added to front-end module with shrank size. Antenna switch is required to support more bands, which increase the difficulty of maintaining a good isolation.

When it comes to 5G FR1, more sub-6GHz bands will be included and the new assigned n77, n78 and n79 bands across 3500MHz – 5000MHz uses time division duplexing (TDD), which require T/Rx switches to switch between transmitting and receiving.

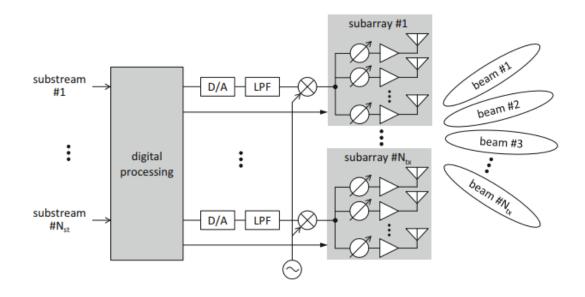

Figure 1-4 illustration of MIMO and Beamforming [3]

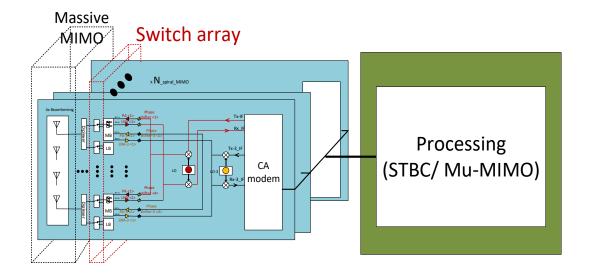

For 5G FR2, RF front end will show higher complexity. Due to lower power amplifier output powers, higher path losses, and higher shadowing losses from the decreased diffraction and dispersion effects, transmissions in the mm-wave bands have significantly less favorable link budgets. However, the shorter wavelength in the mm-wave bands means more antennas can be packed into the same physical area. Therefore, multiple antenna techniques such as Multiple-Input Multiple-Output (MIMO) and beamforming are anticipated to perform an important role in 5G system. In addition, massive MIMO benefits for reducing latency and simplifying the MAC layer. Beamforming techniques require accurate phase control of the RF signal. Thus, high accuracy, small size phase shifter is needed, as well as small size antenna array. Moreover, With RF beamforming being deployed with a large scale antenna array, Time Division Duplexing (TDD) is a good alternative to Frequency Division Duplexing due to the ability to leverage uplink/downlink

reciprocity in controlling the beamforming operation. Therefore, in 5G RFFE, there will be massive T/Rx switches and antenna switches, which can be designed as a switch array on the same chip.

Figure 1-5 Proposed 5G architecture

#### 1.3. 5G RF switch design challenges

As mentioned before, the number of antenna switches and T/Rx switches will increase in 5G RFFE. Coming with the increase number and complicated 5G techniques are various design challenges.

The first problem comes with the increase of supported bands. More bands supported means more branches of the antenna switch. During the operation of antenna switch, only one branch is connected to the input signal, while all other branches are off. The parasitic capacitance of these off branches will cause leakage of the RF power, which results in degradation of the insertion loss. The existence of the parasitic capacitance also degrades matching. The increasing number of switch also rise a problem of interference. Cross-talk between different switch can distort the desired RF signal, which was usually eliminated with proper layout and increasing the distance between switch

blocks. However, for 5G RF front end, with limited area, this is hardly applicable. Metal cage concept is proposed to solve this problem, which uses FIB to each a trench around the switch blocks and fill in silver powder. In this way, the emitted EM signal is shielded from each other.

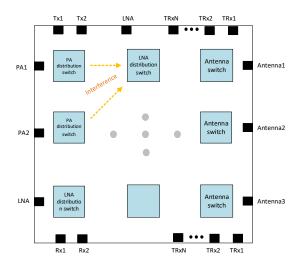

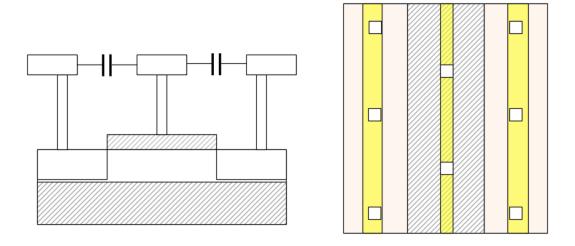

Figure 1-6 Cross-talk between switch blocks in switch array

More severe challenge occurs in high frequency. For 5G FR2, mm-wave switch is required. Under high frequency as 28GHz, the performance of conventional series-shunt type switch is hard to fulfill the requirements due to the high leakage from off branch capacitance. Various switch topology has been reported, including distributed switch, series-shunt with matching inductors and travelling wave switch. The details will be discussed in Chapter 3.

# Chapter 2. Introduction of ESD protection

Electrostatic (ESD) failure is a major reliability concern to integrated circuits (ICs) and electronic systems (i.e., smart phones). As IC technology node continue shrinking into nanometer domain, ESD protection is emerging as a key IC design challenge, especially for high-frequency operating at multi-GHz and high-speed ICs with data rates beyond tens gigabits per second. The ESD phenomenon originates from transfer of electrostatic charges between two objects of different electrical potential and the resulting fast and large ESD transients can damage ICs.

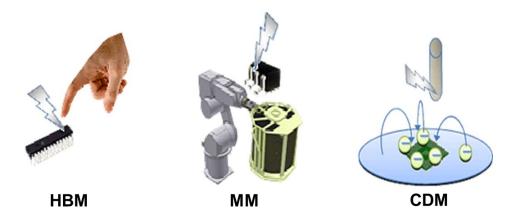

Figure 2-1 ESD test models

#### 2.1. Chip level ESD models

According to the discharging scenario, there are four primary ESD models considered in the microelectronics industry: Human Body Model (HBM), Machine Model (MM) and Charged Device Model (CDM) for on-chip ESD and IEC standard for system level ESD. One emerging ESD protection design challenges along with IC technology scaling-down is the ESD Design Window Shrinking Effect. The human body model represents a human body discharging through the IC module to ground. The equivalent circuit for HBM is a  $1.5 \mathrm{k}\Omega$  resistor in series with a 100pF capacitor. The capacitor is charged to the specified ESD voltage, and then the switch is closed and the current flows through the Device. Machine model represents fabrication or packaging machine

discharge to device. The waveform of machine model is bidirectional damped oscillation. Both MM and HBM ESD events occur between any two pins, therefore, an ESD discharging path is required between every two pins. Charged device model depicts the scenario of changed chip discharge to outside conductor. The charge is induced by friction and the discharge is from one pin to outside. Comparing with HBM, CDM is a very high current event, but occurs in a very short time interval. Due to the fast ESD surge, slow response ESD is not suitable for CDM protection because of the overshoot phenomena. The IC failure under CDM is often caused by gate-oxide (Gox) breakdown, while for HBM and MM, the failure is often caused by thermal breakdown.

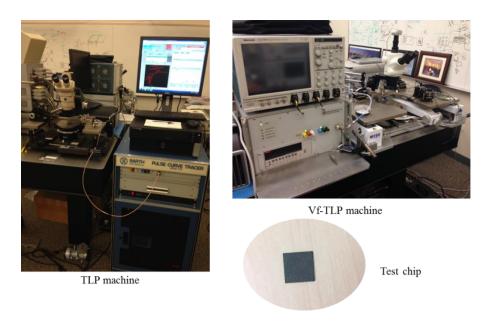

To characterize ESD device performance under these ESD events. Transmission-Line-Pulse (TLP) is developed to characterize ESD device performance under HBM. Different from HBM tester which is a one-time transient test, TLP is a quasi-static ESD test. It strikes ESD device with increasing steps of voltage. The measured voltage and current on device is integrated in a time slot (20%-70%) to generate a series of points under a set of pulse voltage. TLP usually has a duration time of 100ns to simulate the same power as HBM pulse. HBM tester can only give a result of pass or fall, however, TLP can provide more insightful results for the ESD device performance. CDM has faster rise time and duration, correspondingly, vf-TLP was developed. Vf-TLP usually has a duration time in range of 2ns to 10ns. Under this high frequency, simple dc cable is not suitable. For vf-TLP measurement, GS probe and coaxial cable for RF measurement are utilized.

Figure 2-2 ESD protection device characterization instruments

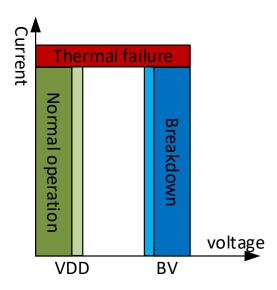

#### 2.2. ESD design window

ESD device design has to fit in ESD design window as shown in Figure 2-3, an ESD Design Window is defined by the breakdown voltage (BV) and power supply voltage (VDD) of the core circuit under protection with a proper safe margin for practical IC designs. An ESD protection solution requires accurate design of ESD-critical parameters including the ESD triggering voltage, current ( $V_{t1}$ ,  $I_{t1}$ ), the ESD holding voltage and current ( $V_h$ ,  $I_h$ ), the ESD discharging resistance ( $R_{ON}$ ). The trigger voltage (or turn-on voltage) of the ESD device is required to be lower than the breakdown voltage to discharge ESD current and clamp ESD voltage down before the core circuit is damaged. On the other hand, to prevent the ESD device trigger on under normal operation, trigger voltage is required to be higher than the supply voltage. Moreover, the holding point also has restricted requirements. To prevent the ESD protection device fall into latch-up state after one ESD strike, the holding voltage is usually required to be higher than the supply voltage. Therefore, after the ESD surge pass, the supply voltage cannot sustain the ESD device in snapback states. Another

solution is also widely used, where the holding current is designed to be much higher than the supply current. In this case, supply current can't keep the ESD device in snapback state. For snapback devise, such as GGMOS and SCR, one important rule is that the breakdown voltage  $(V_{t2})$  should be higher than the trigger voltage  $(V_{t1})$  to ensure the ESD device can be uniformly triggered on. As IC technology node mitigating to below 40nm nodes, ESD design window shrinking effect becomes an emerging challenge for ESD protection designer.

Figure 2-3 ESD design window

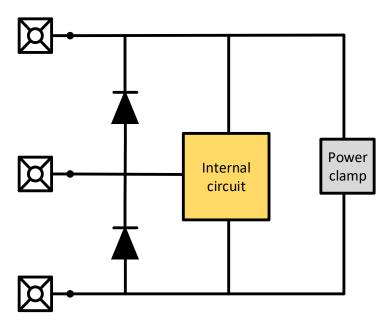

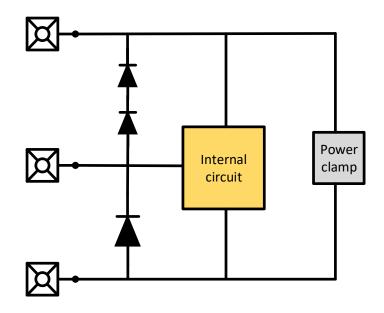

#### 2.3. ESD protection strategy

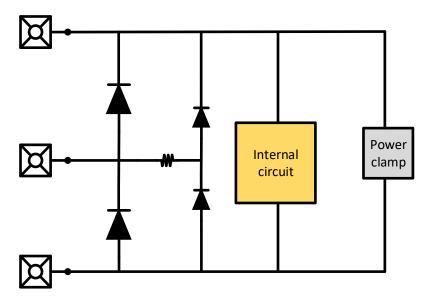

One of the most widely used ESD protection strategies for HBM is to use double diodes on the I/O pin, one to the supply bus and the other to the ground bus. Figure 2-4 shows the protection schematic. The power clamp turns off during normal operation and turn on during an ESD event to provide a very low resistance discharge path between power rail. The discharge path of all passible HBM zapping is illustrate below. For a positive pulse with respect to power supply, the current passes through the upper diode to the supply pin. For a negative pulse with respect to ground, the

current passes through the lower diode and out the signal pin. For a negative pulse with respect to the supply pin, the current flows into the supply pin, flow through the power clamp, and then passes through the diode connected from the pin to ground. For a positive pulse with respect to ground, the current passes through the upper diode, along the supply rail to the power clamp, through the clamp, and out the ground pin.

Figure 2-4 ESD protection diagram for HBM

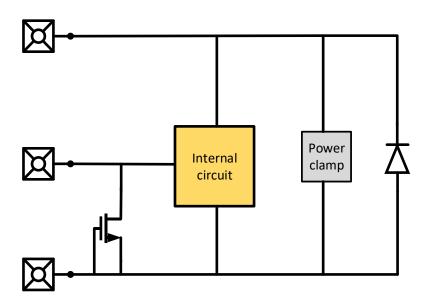

For mixed-voltage circuits where the input power can be higher than the supply voltage, this strategy is not applicable as the up diode will conduct current to supply pins. In this case, a simple solution is to replace the up diode to diode string to prevent ESD protection turning on. GGMOS is usually used to provide bidirectional ESD protection to the input pins. Since GGMOS has high trigger voltage than input signal amplitude, it will not cause signal leakage. Under positive ESD zapping from input pin to ground pin, the GGMOS will trigger on and fall into snapback region to provide a low resistance discharging path. For the negative pulse, the GGMOS will work as a diode connect MOS and conduct ESD current to grounded pins.

Figure 2-5 Diode-string for ESD protection of mixed voltage application

Figure 2-6 GGMOS for ESD protection of mixed voltage application

CDM usually high current and rapid discharge. The main ESD failure mechanism is gate oxide break down. Therefore, the input pins need to be paid extra notice. Due to the high ESD peak current (~10A), even if the diode turn on resistance is very small (~1 $\Omega$ ), a high voltage (10V) will stress the input buffer gate oxide can cause ESD failure. Thus, 2-statge ESD protection scheme is

commonly used for CDM protection. The first stage discharges the most portion of the ESD current and the second stage is used to clamp the ESD voltage down to safe level.

Figure 2-7 CDM ESD protection scheme

# Chapter 3. 3.5GHz series-shunt RF switch design in SOI

#### 3.1. SOI technology

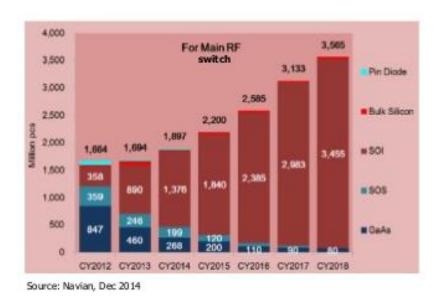

Figure 3-1 shows the historical market share of different RF switch process [4]. Benefiting from high mobility and high power handling ability, PHEMT and GaAs had been used for RF switch for a long time. Recently, silicon-on-insulator (SOI) technique featuring low parasitic capacitance, good isolation and high integration ability starts to dominant RF switch market after 2012.

Figure 3-1 SOI penetrating RF switch market [4]

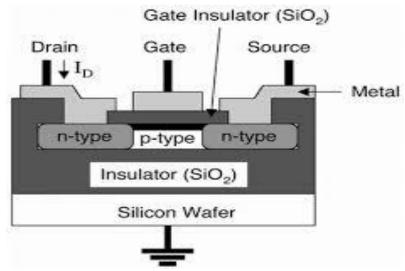

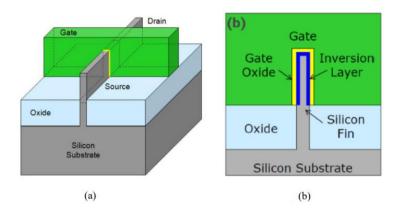

Figure 3-2 shows a cross-section of SOI FET. Where a buried oxide (BOX) layer isolates the substrate and transistor. Combined with shallow-trench-isolation (STI), transistor is isolated from each other. The utilization of BOX can minimize parasitic capacitances associated with junction-to-well diode, and to reduce substrate coupling, which enables high isolation between each circuit block. It is also worth notice that MEMS is penetrating to market and its market share is growing. This chapter will focus on RF switch design on SOI process.

Figure 3-2 SOI cross section [5]

#### 3.1.1. FDSOI and PDSOI

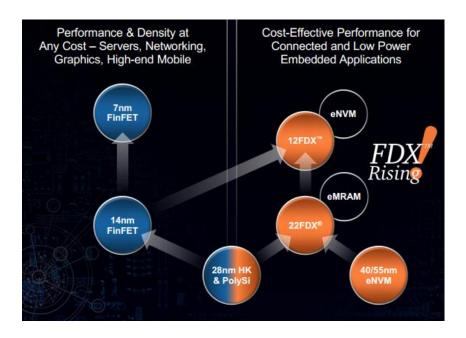

Depending on the depletion region, SOI can be divided into partial depletion (PDSOI) and fully depletion (FDSOI). Partially depleted SOI has been successfully leveraged for high-performance microprocessors and most other SOI applications for almost a decade. Although FD-SOI has been commercially used for a long time, its focus has always been on ultra-low power applications. Recently, the high-performance world is looking at advanced devices such as ultra-thin body FDSOI MOSFETs and multiple-gate MOSFETs (i.e. FinFET) as potential ways to drastically cut power consumption and leakage while preserving high performance and minimizing short channel effects.

FDSOI has several advantages over PDSOI. Since FDSOI uses un-doped or slightly doped channel, the random fluctuations in threshold voltage are minimized. When transistor body is floating in PDSOI, body charge will be introduced by ion-implant when source-drain voltage is very high. These body charge can rise body potential V<sub>BS</sub> and therefore reduce threshold voltage. This is called "floating bod effect" or "kink effect" for analog design. One method widely used to minimize floating-body effects is to use fully depleted (FD) SOI devices. In FD devices, the SOI

film thickness is (much) smaller than the channel depletion width, and therefore the body charge is fixed. Moreover, FDSOI can achieve better leakage control and power consumption are drastically reduced. From 22nm, FDSOI is designed with ultra-thin channel, which enables body bias technique. However, the ultra-thin channel around 6nm is challenging in fabrication and eliminates its application in high power area.

#### 3.2. RF switch design matrix

RF switch is a key block in FEM. The main specifications of RF switch are Insertion loss (IL) in signal paths, isolation between ports, power handling capability, switching time and linearity. In general, small signal performance of RF devices are characterized by their S-Parameters. For RF switches, there are three S-parameters of significant importance to this project: S11, S21, and S31. These are also known as the reflection coefficient, insertion loss, and isolation, respectively. For large signal behavior, power handling ability and linearity is main concern. Switching time represents the time consumes for a switch turns on form off states, which characterizes its transient behavior.

#### 3.2.1. Insertion loss

Insertion loss is defined as the ratio between output and input RF power or a ratio of the signal level in a test configuration without switch to that with switch. The insertion loss of antenna switch is mainly determined by the on-state resistance (Ron) in series branch as explained in equation 2-1, which is irrelevant to frequency and also known as resistive insertion loss. The frequency dependent part of the insertion loss comes from off-state capacitance.

$$IL = -20\log \frac{2R_0}{2R_0 + R_{on}}$$

2-1

The insertion loss of switch can degrade the overall front end performance in both transmitter and receiver side, especially for antenna switch. In RF receiver, a LNA is used to minimize the noise figure (NF) induced of the following stage according to Friis-equation. However, RF signal will go through antenna switch and duplexer before reaching LNA. This loss will directly add to the system NF. Every amount of insertion loss in antenna switch needs much extra effort spent on improving LNA design. More importantly, the system NF directly contributes to RF system sensitivity with equation 2-2.

$$Rx_{Sensitivity} = -174 + 10 \times \log(BW_{[Hz]} + NF_{[dB]} + SNR_{[dB]})$$

2-2

Figure 3-3 Simplified SNR in receiver

The degradation of Rx sensitivity reduces signal coverage as Coverage area reduces approximately 1% per 0.1 dB of IL. High IL also directly degrades the passive efficiency, which results in lower PA efficiency (PAE). PAE degrades approximately 1% per 0.1 dB of IL, which is large enough to determine the market of a FEM.

#### 3.2.2. Isolation

Isolation is defined as the ratio of RF power leaked to the off-state branch to input signal power.

Isolation of RF switches depends on the off-state capacitance as expressed in equation 2-3. On SOI process, the body of a FET has two configuration. For floating body connection, the parasitic

capacitance is smaller comparing with body connected FET. However, floating body can cause linearity problem due to kink effect.

$$Iso = -20log \frac{2R_0}{2R_0 + 1/\omega C_{off}}$$

2-3

To improve the isolation of switch, layout works is one of the main concern. To reduce the parasitic capacitance between metal lines, M1 is better to keep away from each other. To keep low resistance of signal path, M1 connected to source and drain needs to be wider. To lower the capacitance between Vias, via is better to be placed in cheese pattern as shown in Figure 3-4.

Figure 3-4 Layout concern in switch design

Poor isolation of switch can degrade RF system performance in some cases. For example, the uplink of Band28 spans from 703MHz to 748MHz while the down link of Band 29 is 717-728MHz. Due to the fact that B29 only has downlink and its frequency overlaps with Band 28 Tx, B29 Rx and B28 Tx is usually covered with one off-chip acoustic filter and a switch is used to considering cost and size. Under B29 and other band (i.e. B12) carrier-aggregation case, where B29 Rx and

B12 Tx turns on at the same time. The RxBn of B12 Tx power shown as noise to B29 Rx, which can cause severe degradation to receiver sensitivity as shown in Figure 3-5.

Figure 3-5 RxBn caused by BSW isolation.

# 3.2.3. Linearity

The linearity of RF switch is characterized by its gain compression point (P1dB) and Third Order Input Intercept Point (IIP3). As shown in Figure 3-6, kink effect for floating body SOI FET will degrades the linearity of switch. Therefore, for switches requiring high linearity, body is better to be connected.

Figure 3-6 Kink effect

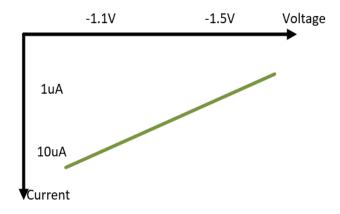

Moreover, there are some typical causes of linearity degradation. To improve linearity, the body is usually connected as shown in Figure 3-7, where the PMOS acts as a diode connection. When the FET is switched off, the gate is biased with negative DC voltage ( $V_g$ <0V). PMOS turns on and draw the body voltage to negative. This configuration ensures the P-well/N-plus junction keeping off, which is harmful to the linearity of switch as it causes power drop out.

Figure 3-7 Body connection of SOI NFET

• ESD drop out

When RF signal power is large enough that the peak voltage is higher than the turn-on voltage of ESD device, RF signal is clamped. Thus, linearity degrades severely.

### • RF-Control coupling

When high power RF signal path (PA, switch) is placed around the control signal line, or the bonding wires are placed closed to each other, the RF signal can couple into control line and change control states. For example, turn on the off-state branch. Therefore, degrades linearity

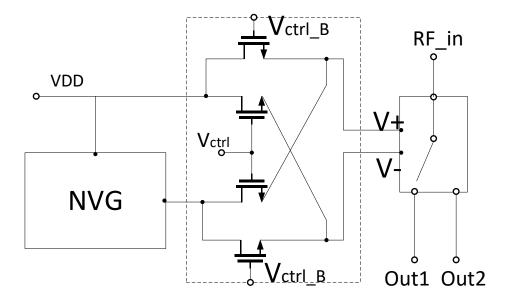

## • Body biasing – NVG loading

As mentioned before, diode connection PMOS is usually used to connect the body of FETs. When the switch turns off from on-state, the voltage on gate node drops to negative with a negative voltage generator (NVG). As the PMOS turns on to draw the body voltage down, it sinks current. When the switch have a lot of branches, this can be a problem when the loading capability of the NVG is not enough. The result is the output negative voltage rise up and linearity degrades.

Figure 3-8 A sample of negative voltage generator output load-line

## 3.2.4. Power handling ability

When we say "power handling ( $P_{max}$ )" for switches, what we mean is the power level that will correspond to the onset of gain compression. The on-state power handling ability is highly related to the current handling ability of transistors while the off-state power handling ability is related to breakdown voltage. To improve on-state power handling ability, wider transistor size is desired. However, for the off-state power handling, the breakdown voltage is limited by process parameters, i.e. doping level, thickness of gate oxide, etc. To improve the power handling ability, FETs are stacked to distribute the large RF power. The process of determining stack number is expressed in equation 2-4 to equation 2-7. Due to substrate and gate leakage,  $V_{ds}$  distribution is imbalance across the FETs. End devices will see a larger  $V_{ds}$  swing, which limit the power handling ability. To improve voltage imbalance, forward coupling capacitor can be used, which however can cause RF simulation convergence problem sometimes. Width modulation is another method. By making end FET wider, the voltage can show better balance. Reminder the fact that source-drain breakdown voltage is related to the channel length of FETs. Thus, by increasing gate length of end FETs, the power handling ability can be improved. This method is called length modulation.

$$Maximum \ output \ power = P_{max}$$

2-4

$$V_{pk} = \sqrt{2 \times P_{watt} \times Z_0}$$

2-5

$$V_{max} = V_{pk} (1 + \frac{VSWR - 1}{VSWR + 1})$$

2-6

$$Stack\ height = \frac{V_{max}}{BV_{dss}}$$

2-7

## 3.2.5. Figure of merits

There are two types of figure of merit for switch process. The first one is the product of onstate resistance and off-state capacitance ( $R_{on}*C_{off}$ ). This figure of merit is used to identify the small signal capability of the switch process. The lower the figure of merit, the better performance it can achieve on insertion loss and isolation. As technology developing, the figure of merit is getting smaller. For the state-of-art, The FOM can reach as low as around 100 [6]. Another type of figure of merit is proposed to identify the power handing and isolation capability of switch process. It takes breakdown voltage into consideration and expressed as ( $R_{on}*C_{off}/BV$ ).

## 3.3. 3.5GHz T/Rx Switch design consideration

Spectrum availability for IMT in the 3300-4200 and 4400-5000 MHz ranges is increasing globally. The 3400-3600 MHz frequency band is allocated to Mobile Service on a co-primary basis in almost all countries throughout the world. Administrations will make available different portions of the 3300-4200 and 4400-5000 MHz ranges at different times, incrementally building large contiguous blocks.

The 3GPP 5G NR specification will support 3300-3800 MHz from the start (n78), using a TDD access scheme (Figure 3-9). In line with the release plans from many countries, the 3300-3800 MHz band will be the primary 5G band with greatest potential for global harmonization over time.

Figure 3-9 Global availability and planning of the 3300-4200 MHz and 4400-5000 MHz frequency ranges [source. Huawei – 5G Spectrum public policy position]

As mentioned in Chapter 1, many new technologies are invented for 5G FR1 under 6GHz. Utilization of large system bandwidth is considered as an effective method to significantly increase per-user throughput and overall system capacity. Carrier aggregation (CA) technology is developed to combine two or more carriers, in the same or different frequency bands, into one data channel to enhance the data capacity. 5G NR supports carrier aggregation with 16 component carriers. Moreover, Carrier aggregation of LTE and 5G NR carriers is also possible which is known as Dual Connectivity (DC). Multiband RF radio signals can interfere with each other because of insufficient filter attenuation. This means there is a higher probability of desense in CA applications if isolation or cross-isolation between transmit and receive paths is insufficient. Therefore, High switch isolation and harmonic filtering are required to mitigate this situation [7][8].

For 3GPP Release 15 it was agreed that an OFDM-based waveform with Cyclic Prefix (CP-OFDM) will be supported for both 5G NR download and upload. DFT-S-OFDM based waveform will be also supported, complementary to CP-OFDM waveform and used for an enhanced mobile broadband (eMBB) uplink up to at least 40GHz. CP-OFDM waveform features higher peak-

average power ratio (PAPR), which rise higher requirements on switch linearity. On the other hand, under high PAPR, power amplifier (PA) faces more restricted trade-off between linearity and efficiency. Thus, low insertion loss switch is required to relief PA design challenges [9].

To reduce latency, evolution in the slot-based framework used in LTE has been developed for 5G. LTE has 15 kilohertz subcarrier spacing, with 1 millisecond slots (or subframe) each supporting 14 symbols. Similarly, 5G allows for a 15 kHz subcarrier with a 1 millisecond slot for 14 symbols, in a deliberate attempt to align 4G with 5G. But 5G has other options, including 30 kHz subcarrier with a 500 microsecond slot, 60 kHz with a 250 microsecond slot, and 120 kHz with a 125 microsecond slot. The shorter slot requires faster TDD switching. Therefore, switching time also meets more restrict specifications.

In conclusion, these new technologies introduced to realizing 5G FR1 requires high switch isolation, high harmonic filtering, low insertion loss, high linearity and fast switching 3.5GHz RF switch.

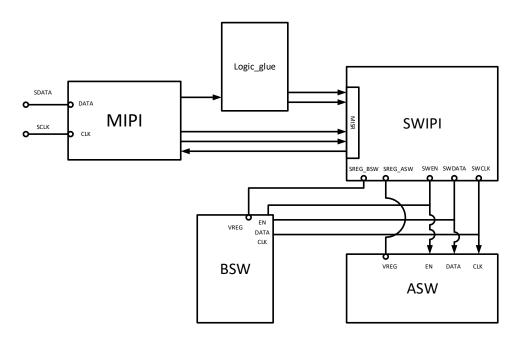

#### 3.4. 3.5GHz T/Rx Switch design in SOI

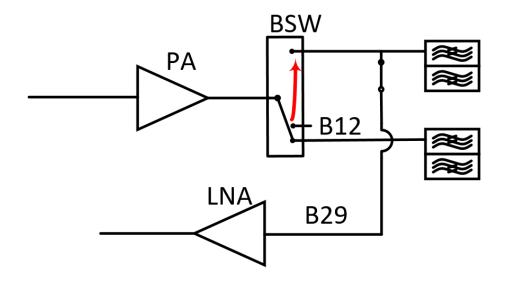

The MIPI Interface standard defines industry specifications to interface chipsets and peripherals in mobile-connected devices. In the mobile industry the solutions are used in smartphones, tablets, laptops and hybrid devices. The basic configuration of the RFFE MIPI interface and control diagram of antenna switch (ASW) and band switch (BSW) are shown in Figure 3-10. Two control signal line coveys the serial bidirectional data signal (SDATA) and the clock signal (SCLK) into MIPI interface, then the data is processed and send to internal SWIPI. SWIPI process the input data with MISR (multi-inpuit-shift-register) and assign the data to slave interface according to register enclosed in MIPI word [10]. Figure 3-11 shows the bias diagram of designed SPDT switch. Where a negative voltage generator (NVG) is utilized to generate a negative

bias voltage to off branch. Quadrature connected transistors are used to swap the control voltage. The control voltage VDD is supposed to be supplied from a LDO regulator to eliminate the interference from control signal to RF signal.

Figure 3-10 Control diagram of antenna switch and band switch

Figure 3-11 Block diagram of SPDT switch core and bias

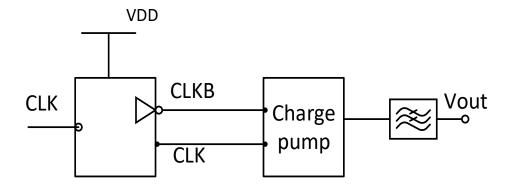

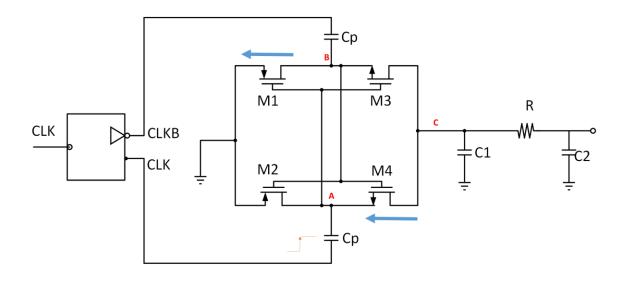

## 3.4.1. Negative voltage generator design

Charger pump is wide used in analog and RF circuit design, such as PLL, DC-DC converter and negative voltage generator. To generate a negative bias voltage, a circuit using charge pump concept is used as a negative voltage generator. Figure 3-12 shows the block diagram. A two phase clock generator creates two clock signal with same frequency and 180 degree phase shift. These two clock signal input to charge pump and drive the charge pump draw charge from capacitor to generate a negative voltage. The output of the charger pump is noisy due to clock punch through. Thus, a low-pass RC filter is used to remove the ripple, with a cost of delayed response time. The schematic of the charge pump is shown in figure. M1 and M2 are PMOS while M3 and M4 are NMOS. Two capacitors Cp are used to connect M1 drain and M2 drain. When CLK changes from zero (0V) to high voltage  $(V_{DD})$ . Due to the fact that charge in capacitor can't discharge immediately, voltage across capacitor stays the same. Therefore, voltage at node A rises the same amount as CLK. CLKB is out of phase with CLK. Thus, in the same time, node B drops a voltage equals to – V<sub>DD</sub>. Therefore, M3 is open and M2 is also open. During this clock cycle, M3 draws current from output capacitor C1, and M2 conducts current to ground (Figure 3-13). Therefore, voltage of node A decrease to 0V and forms a voltage equals to V<sub>DD</sub> across Cp. In the meantime, a negative voltage forms at node C. for the next clock phase, voltage of node A drops to -V<sub>DD</sub>, which opens M4 and drain current from C1 to lower node C voltage. In the same while voltage of B rises to  $V_{DD}$  to conduct current to ground through M1 (Figure 3-14). As analyzed here, during each clock cycle, M1 and M4 or M2 and M3 pair work together to draw charge from capacitor C1 to generate a negative voltage. Finally a negative voltage –V<sub>DD</sub> appears at output.

Figure 3-12 Block diagram of negative voltage generator

Figure 3-13 Current flow during CLK rising to VDD \

Figure 3-14 Current flow during CLK falling to GND

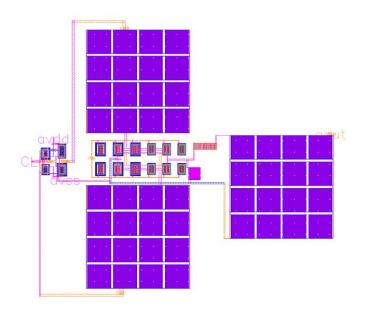

By setting the resistor R and capacitor C2 response time, the ripple on output negative voltage is filter out to generate a purified voltage to bias switch. The simulation result is shown in Figure 2 16. The output can reach -790mV.

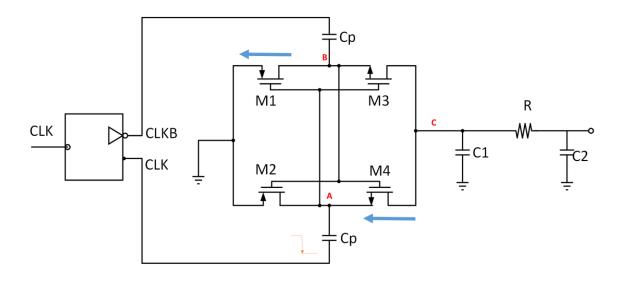

Figure 3-15 Layout of designed negative voltage generator

Figure 3-16 Simulation result of designed charger pump.

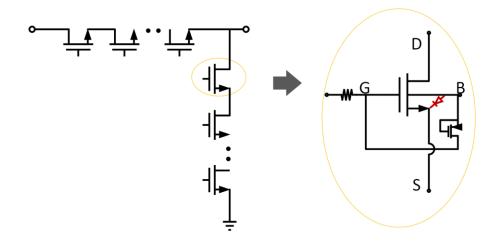

### 3.4.2. Switch Topology and design

To cover the wide bandwidth at sub-6GHz frequency range, series-shunt topology is a good candidate. The process used for this design is 22nm FDSOI (fully-depleted SOI) process. The advantage of FDSOI is that the threshold voltage features very low variation due to the fully-depleted channel does not have doping, therefore, the threshold voltage variation caused by channel doping process variation is eliminated. Another advantage is the body-bias technique. By applying voltage at the back node, the transistor performance can be tuned as shown in Figure 3-17.

Figure 3-17 Ron and Coff change with body-biasing voltage

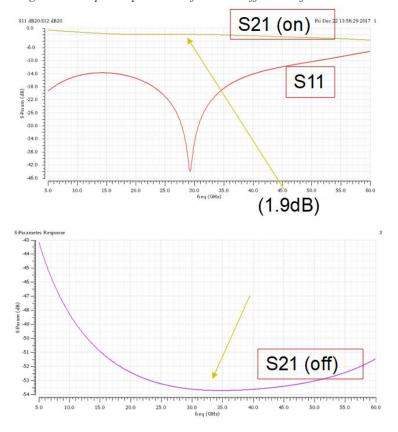

Figure 3-19 shows the schematic of the SPDT switch. 8 MOSs are stacked to handle a RF power up to 37 dBm. A  $50 \text{K}\Omega$  resistor is connected to the gate to AC-float the gate node. The purpose is to prevent RF signal leakage and reduce RF voltage stress on gate oxide. So does for the body connection. To balance the voltage swing across each MOS, a 10K resistor is connected between source and drain for each MOS. For shunt branch, the stack number is the same as series branch considering power handling ability. The width and length of the series and shunt branch is listed in Table 3-1.

|        | Stack Number | Width (um) | Length (nm) | $\operatorname{Rg}\left(\Omega\right)$ | Rds (Ω) |

|--------|--------------|------------|-------------|----------------------------------------|---------|

| Series | 8            | 2000       | 20          | 50                                     | 10K     |

| Shunt  | 8            | 300        | 20          | 50                                     | 12K     |

Table 3-1 design parameters of SPDT switch

As shown in Figure 3-17 before. Decreasing bias voltage of NMOS with decrease its off-state capacitance and increase it's off-state resistance. This will benefit to the overall isolation performance of the SPDT switch.

Vb\_Sh1 Vg\_Sh1 Vg1 OUT1 RF\_IN Vb2 OUT2 Vg2 Vg\_Sh2 Vb\_Sh2

Figure 3-18 Simulated I.L. and Isolation with body bias voltage change

Figure 3-19 Schematic of SPDT switch core

Figure 3-18 confirms this assumption. When bias voltage changes from 0V to -0.8V, the isolation improves around 1dB from 3000-5000MHz. The insertion loss also improves slightly with a number of 0.006dB. The large signal performance of the designed SPDT switch is also simulated. Figure shows the high linearity of designed switch which achieved a 1dB gain compression point at 37dBm. The switching time is also simulated in time domain. The simulation result shows the turn on switching time is 0.3us.

Figure 3-20 Simulated input P1dB of the SPDT switch

Figure 3-21Simulated switching time of designed SPDT switch

As a comparison, the simulation results are put in Table 3-2 in comparison with a industrial SPDT switch. The simulation result shows comparable performance with the industrial product.

| Specs.          | Performance (simulation) | SKYA21038<br>(data sheet) |  |

|-----------------|--------------------------|---------------------------|--|

| Frequency range | 3GHz-5GHz                | 0.6GHz-6GHz               |  |

| Insertion loss  | <0.3dB                   | 0.5dB@2.4GHz              |  |

| Isolation       | >40dB                    | 38dB@2.4GHz               |  |

| P1dB            | 36.5dBm@3.5GHz           | 31dBm@2.4GHz              |  |

| Switching speed | 0.5us                    | 2~5us*                    |  |

\* From SKYA21052 Antenna switch SP12T

Table 3-2 Simulation result of design SPDT switch in comparison with SKYA21038

# Chapter 4. Millimeter Wave Switch design in SOI for 5G applications

RF switches are essential components for the RF front-ends of smartphone systems, especially for 5<sup>th</sup> generation (5G) mobile systems featuring rich frequency channels and utilizing time division duplexing transceiver architecture in millimetre-wave bands. To improve the power efficiency and sensitivity of transceivers, RF switches are required to have low insertion loss and high isolation. On the other hand, high integration has been a pursuit of IC designs for cellular chipsets for long. These are key design challenges in RF IC designs for 5G systems, especially for above-6GHz designs. From 3GPP 5G proposal, the high frequency bands around 28GHz and 38GHz will be used in FR2. In this chapter, I will present a travelling wave based 28GHz SPDT RF switch with robust on-chip ESD protection designed and fabricated in a foundry 22nm fully depleted SOI technology. This fully ESD-protected mm-wave SPDT switch covers the n257 and n258 bands of 5G systems, and demonstrates good insertion loss and isolation compatible to the state-of-the-art utilizing other process technologies. This design also shows the feasibility of high level integration with sub-6GHz RF front-ends in SOI CMOS.

#### 4.1. Introduction of mm-wave switch design

Historically, high-performance RF switch design mostly uses III–V semiconductor-based processes or silicon-on-sapphire (SOS) technologies due to its high mobility and high power handling ability [11]. In these process a metal layer is often applied to the back side of die, which is very convenient to form a ground plane for microstrip line and mm-wave circuit design [12][13][14]. However, III–V semiconductor-based (for example, GaAs, and InP) and SOS technologies uses expensive substrate and features poor integration capability with digital circuits most of which use commercial silicon-based technologies. Bulk silicon process offers good capability of system integration and low cost, but suffers from poor linearity and high loss as high

power RF signal coupling to the low-resistivity silicon substrate [15][16][17]. Triple-well technique was reported, which shows improvement of the performance. In recent years, by using high-resistivity (HR) substrate, HR SOI technology has been penetrating into the switch market. With buried oxide isolate transistor and substrate, SOI reduced parasitic capacitance and substrate loss [18]-[19]. Trap-rich (TR) layer was late introduced to capture the free carriers at the interface of buried oxide (BOX) layer and HR Si substrate and eliminate parasitic surface conduction at the interface. SOI process achieves a balance between performance and cost, while maintains a capability of integration.

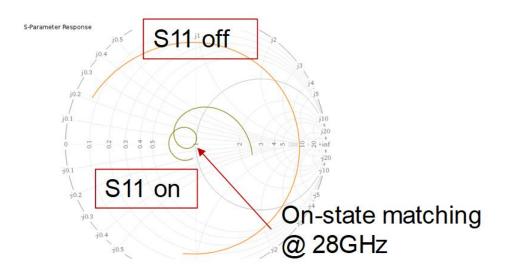

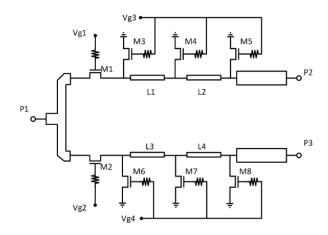

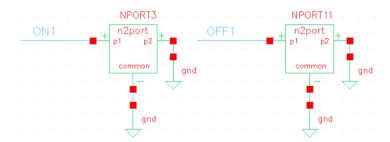

Figure 4-1 measurement result of SPDT switch on 28GHz using series-shunt topology [23]

-25

-25

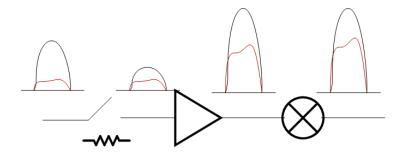

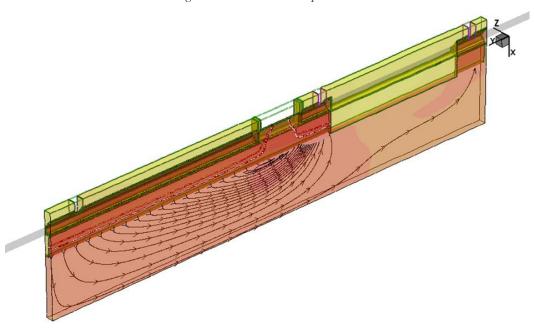

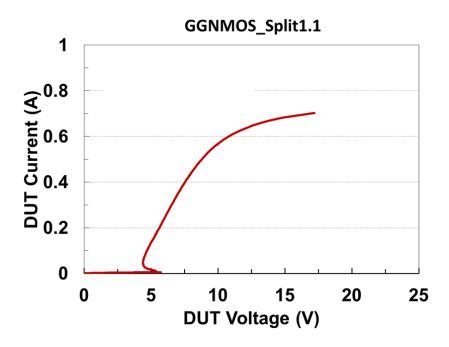

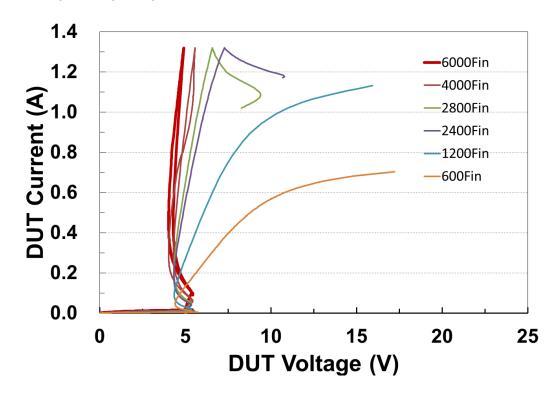

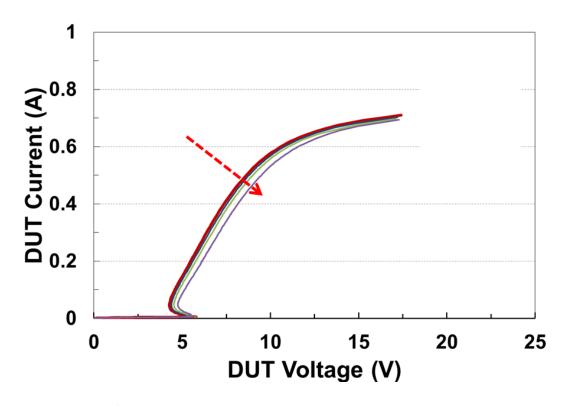

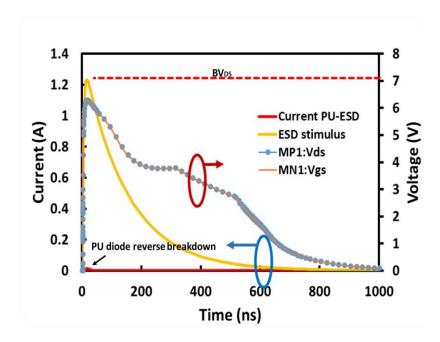

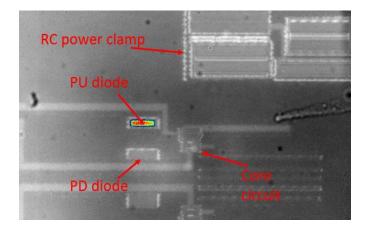

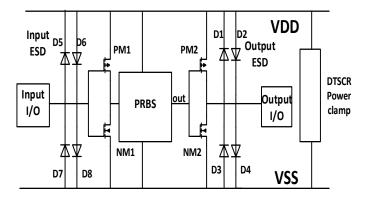

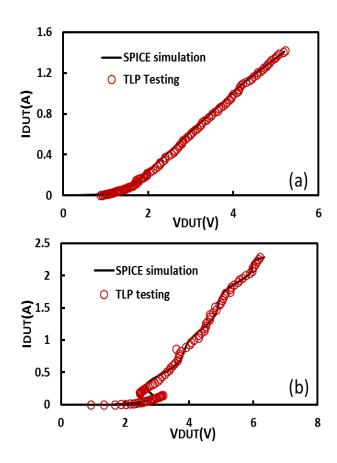

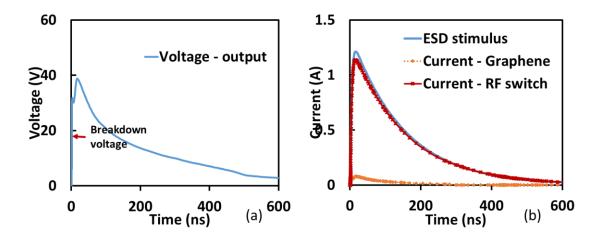

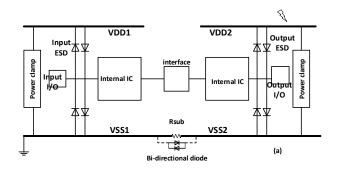

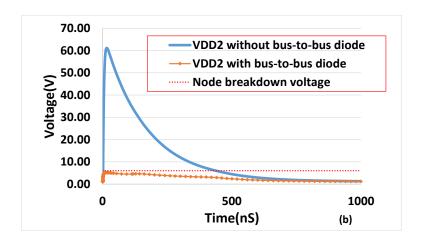

Various topology is also reported for millimeter-wave switch design. The key fact that affects the design of mm-wave circuit is that as the frequency increase, the wavelength decrease to the scale of a circuit. Therefore, some electrical component can't be seen as a lumped device as in several gigahertz range. For example, transmission lines are used as conductor to replace simple one layer metal line. In several gigahertz frequency range, i.e. LTE, GSM bands, series-shunt type switch is widely used. In this topology, a shunt branch is added after the series branch to improve the isolation. However, mm-wave circuit is more sensitive to parasitic capacitance. The parasitic capacitance of the off branches in series-shunt switch degrades insertion loss and return loss to a large degree. Figure 4-1 shows the measurement result of our previous design on 28GHz using series-shunt topology [23]. The switch can only reach an insertion loss around 6dB and isolation worse than 16dB.