## **UC Berkeley**

### **UC Berkeley Previously Published Works**

### **Title**

An Input Inductor Flying Capacitor Multilevel Converter Utilizing a Combined Power Factor Correcting and Active Voltage Balancing Control Technique for Buck-Type AC/DC Grid-Tied Applications

### **Permalink**

https://escholarship.org/uc/item/8bz2x11w

### **Authors**

Bayliss, Roderick S., III Pilawa-Podgurski, Robert C. N.

### **Publication Date**

2024-07-01

Peer reviewed

©2024 IEEE

Proceedings of the 25th IEEE Workshop on Control and Modeling for Power Electronics (COMPEL 2024), Lahore, Pakistan, June 24-27, 2024

An Input Inductor Flying Capacitor Multilevel Converter Utilizing a Combined Power Factor Correcting and Active Voltage Balancing Control Technique for Buck-Type AC/DC Grid-Tied Applications

Roderick S. Bayliss III R. C. N. Pilawa-Podgurski

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# An Input Inductor Flying Capacitor Multilevel Converter Utilizing a Combined Power Factor Correcting and Active Voltage Balancing Control Technique for Buck-Type AC/DC Grid-Tied Applications

Roderick S. Bayliss III

Dept. of Electrical Engineering and Computer Sciences

University of California, Berkeley

Berkeley, CA, U.S.A.

rodbay@berkeley.edu

Robert C. N. Pilawa-Podgurski

Dept. of Electrical Engineering and Computer Sciences

University of California, Berkeley

Berkeley, CA, U.S.A.

pilawa@berkeley.edu

Abstract—This paper presents a novel circuit topology and control strategy for use in single-phase buck-type power factor correction (PFC) ac-dc rectifiers. We propose a topological change to the flying capacitor multilevel (FCML) converter to place inductors at the input rather than the conventional output along with a novel control strategy for ac-dc operation. The proposed topology retains the high efficiency and power density advantages of the FCML topology while enabling improved control of the input current for PFC operation, and better EMI performance for the same magnetic energy storage. An active flying capacitor voltage balancing control technique is presented, which enables high bandwidth (e.g., 120 Hz) control of the flying capacitor voltages. The new circuit topology and enabling control technique are demonstrated in a six-level, 240  $V_{\rm rms}/48~V_{\rm dc}$ , 817 W hardware prototype.

#### I. Introduction

Data center power delivery and other grid-connected applications require a target output dc voltage that is significantly lower than the incoming mains voltage. Additionally, high power factor current must be drawn from the mains interface, requiring a power factor correction (PFC) rectifier. Often, a two-stage approach is employed where the incoming mains voltage is rectified to an intermediate dc voltage higher than the peak of the mains. This intermediate dc voltage is then processed by a second step-down converter to a lower voltage (e.g., 48 V). This two-stage power conversion approach suffers from a cascade of efficiency penalties and lower power density due to the increased effective conversion ratio associated with step-up and step-down operation.

Single-stage rectification directly generates the target voltage from the mains voltage. Given that the target voltage is lower than the peak of the mains, a buck-type PFC rectifier [1], [2] is typically employed. Despite having to turn the converter OFF during the portions of the line cycle where the input voltage magnitude is lower than the output voltage, sufficiently

high power factor and current THD can be obtained with the input and output voltages typical of data center power delivery (e.g.,  $v_{\rm ac} = 240\,{\rm V_{rms}}, V_{\rm out} = 48\,{\rm V_{dc}})$  [3]. Hold-up capacitors and/or twice-line-frequency power pulsation filter capacitors that are typically required in this application provide sufficient energy storage to maintain the dc voltage to the load when the ac-dc stage is turned OFF.

This work employs the flying capacitor multilevel (FCML) converter [4] as the power stage. The FCML converter has the high performance characteristics of small magnetics volume due to reduced inductor volt-seconds and utilization of highperformance low voltage switches [5]. In the buck-type PFC application, however, there are two challenges in utilizing this topology addressed by this work: 1) the input current of the converter must be controlled to achieve both high power factor and low distortion, a challenge for the traditional FCML converter variant where the inductor is placed at the output; and 2) the flying capacitor voltages must track a large signal, twice-line-frequency reference to realize the benefits of the FCML converter. The first challenge is addressed through a topological variant of the traditional FCML converter, termed the input inductor FCML converter, discussed in Section II, while the second challenge is addressed through active flying capacitor voltage balancing and is discussed in Section III. Experimental verification of the proposed topology and control scheme is provided in Section IV.

## II. INPUT INDUCTOR FLYING CAPACITOR MULTILEVEL CONVERTER

The input inductor FCML converter [6]–[9] is a topological variation of the standard output inductor FCML converter. This converter topology belongs to a class of converters with "nonpulsating" port currents [6], enabling a reduction in required input current filtering. This topology was shown to be a promising candidate in buck-type PFC applications in [7].

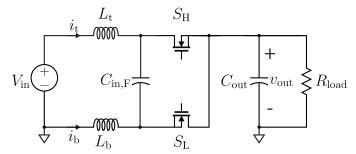

Fig. 1: Circuit diagram of an input inductor buck dc-dc converter.

A schematic drawing an input inductor buck dc-dc converter is shown in Fig. 1 and a drawing of a six-level input inductor FCML rectifier is shown in Fig. 2. The converter maintains the same input-output voltage characteristic as an output inductor FCML converter with  $V_{\rm out} = DV_{\rm in}$  where D is the duty cycle applied to all high-side switches  $S_{\rm H}$  and  $S_{{\rm H},k}$ .

Compared to the output inductor FCML converter, the input inductor variant requires significantly less input current filtering for the same peak magnetic energy storage, a useful proxy for inductor size [10]. This is a consequence of the topology's "nonpulsating" port currents property. First, we derive the total stored magnetic energy in both an output inductor buck converter and an input inductor buck converter. We assume the inductance of all inductors are chosen such that the inductor current ripple ratio  $\alpha = \Delta i_L/I_L$  is the same, where  $\Delta i_L$  is the peak-to-peak current ripple and  $I_L$  is the average current in inductor L.

The peak energy  $E_{L_{\rm o}}$  stored in the inductor  $L_{\rm o}$ , which carries an average current  $I_{\text{out}}$ , for the output inductor buck converter can be derived as

$$E_{L_{o}} = \frac{1}{2} L_{o} I_{pk}^{2} = \frac{1}{2} L_{o} \left( I_{out} + \frac{\Delta i_{L_{o}}}{2} \right)^{2}$$

$$= \frac{1}{2} L_{o} I_{out}^{2} \left( 1 + \frac{\alpha}{2} \right)^{2}. \tag{1}$$

The inductance  $L_0$  is then defined by the desired current ripple ratio  $\alpha$ ,

$$L_{\rm o} = \frac{D(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw} I_{\rm out}}$$

(2)

yielding a peak inductor energy of

$$E_{L_{\rm o}} = \frac{D(V_{\rm in} - V_{\rm out})I_{\rm out}(1 + \alpha/2)^2}{2\alpha f_{\rm sw}}.$$

(3)

The input inductor buck converter, shown schematically in Fig. 1, contains two inductors  $L_{\rm t}$  and  $L_{\rm b}$ . We derive the average inductor currents relative to the output current  $I_{\rm out} = v_{\rm out}/R_{\rm load}$  by performing a charge balance on  $C_{\rm in,F}$

in order to establish a comparison against the output inductor buck converter:

$$I_{C_{\text{in,F}}} = -DI_{\text{b}} + (1-D)I_{\text{t}} = 0$$

(4)

$$I_{\rm b} = \frac{1 - D}{D} I_{\rm t} \tag{5}$$

$$I_{\rm b} + I_{\rm t} = I_{\rm out} \tag{6}$$

$$I_{\rm t} = DI_{\rm out}, \ I_{\rm b} = (1 - D)I_{\rm out}.$$

(7)

The peak energy  $E_{L_t}$  stored in  $L_t$  is

$$E_{L_{t}} = \frac{1}{2} L_{t} \left( I_{t} + \frac{\Delta i_{L_{t}}}{2} \right)^{2}$$

$$= \frac{1}{2} L_{t} \left( DI_{\text{out}} + \frac{\alpha DI_{\text{out}}}{2} \right)^{2}$$

$$= \frac{1}{2} L_{t} D^{2} I_{\text{out}}^{2} \left( 1 + \frac{\alpha}{2} \right)^{2}$$

(8)

As in the output inductor buck converter, the inductances are defined by the desired current ripple ratios  $\alpha$ :

$$L_{\rm t} = \frac{D(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw} I_{\rm t}} = \frac{(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw} I_{\rm out}}$$

(9)

$$L_{\rm t} = \frac{D(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw} I_{\rm t}} = \frac{(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw} I_{\rm out}}$$

(9)

$$E_{L_{\rm t}} = \frac{(V_{\rm in} - V_{\rm out})D^2 I_{\rm out} (1 + \alpha/2)^2}{2\alpha f_{\rm sw}}.$$

(10)

While the peak energy  $E_{L_{\mathrm{b}}}$  stored in  $L_{\mathrm{b}}$  is

$$E_{L_{b}} = \frac{1}{2} L_{b} \left( I_{b} + \frac{\Delta i_{L_{b}}}{2} \right)^{2}$$

$$E_{L_{b}} = \frac{1}{2} L_{b} \left( (1 - D) I_{\text{out}} + \frac{\alpha (1 - D) I_{\text{out}}}{2} \right)^{2}$$

$$= \frac{1}{2} L_{b} (1 - D)^{2} I_{\text{out}}^{2} (1 + \alpha/2)^{2}$$

(11)

$$L_{\rm b} = \frac{D(V_{\rm in} - V_{\rm out})}{\alpha f_{\rm sw}(1 - D)I_{\rm out}}$$

(12)

$$E_{L_{\rm b}} = \frac{D(V_{\rm in} - V_{\rm out})(1 - D)I_{\rm out}(1 + \alpha/2)^2}{2\alpha f_{\rm sw}}.$$

(13)

Finally, the total peak magnetic energy is derived as

$$E_{L_{\rm t}} + E_{L_{\rm b}} = \frac{D(V_{\rm in} - V_{\rm out})I_{\rm out}(1 + \alpha/2)^2}{2\alpha f_{\rm sw}},$$

(14)

which is identical to (3). Thus the total peak magnetic energy in an input inductor buck converter is the same as that of an output inductor buck converter under the constraint of equal current ripple ratio in all inductors. For an FCML converter, given a level count N, all of the inductors within both an input and output N-level FCML converter are subjected to the same voltages. Additionally, the inductors carry the same average currents as the corresponding inductors in the buck converters. Thus the preceding analysis is directly applicable and the property of constant total peak magnetic energy across both the input and output inductor variants holds.

Typically, the input current of PFC converters must adhere to conducted emissions standards (e.g., CISPR 32) and the input inductor variant offers a distinct advantage over the

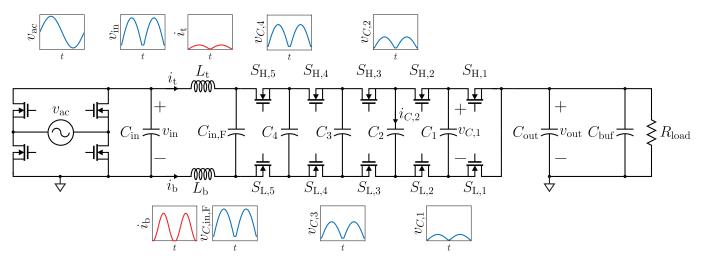

Fig. 2: Circuit diagram of an ac-dc PFC rectifier utilizing a six-level input inductor FCML converter with an input synchronous rectifier.  $C_{\rm out}$  serves to buffer switching frequency ripple while  $C_{\rm buf}$  performs twice-line frequency power buffering.

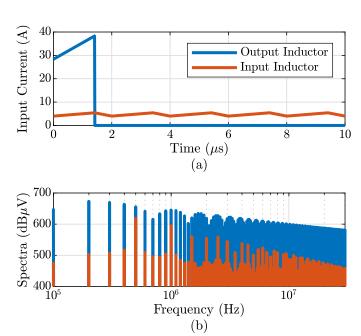

Fig. 3: Simulation comparison of the input current waveform in (a) the time-domain and (b) spectra in the frequency-domain between an output inductor and input inductor FCML converter. Both converters employ a six-level FCML converter operating at the same dc-dc operating point of:  $V_{\rm in}=339\,{\rm V},\ V_{\rm out}=48\,{\rm V},\ P_{\rm out}=1.6\,{\rm kW},\ f_{\rm sw}=100\,{\rm kHz}.$  The inductances of the three inductors were chosen such that the inductor current ripple ratio was 30%. The spectra voltage is the voltage that would be measured across a  $50\,\Omega$  resistor conducting the input current (as would occur in a line impedance stabilization network). As noted in Section II, the peak magnetic energy stored in the two converters is the same.

output inductor variant in this regards. To assess the filtering effort required, we define the input current as the current supplied by the grid assuming the grid behaves as a perfect voltage source (i.e., the current that flows through  $S_{H,N-1}$ for the output inductor FCML converter and  $i_t$  for the input inductor FCML converter). Fig. 3 shows a comparison in the input current spectra between an input inductor and output inductor FCML converter. Both converters in this simulation study operate at the same input/output voltages, output power, and switching frequency. Since both inductors operate at the same ripple ratio, the total magnetic energy is the same. However, due to the "nonpulsating" continuous input current property of the input inductor FCML converter, the input current spectra are significantly reduced: up to 175  $dB\mu V$  over the frequency range of 150 kHz-3 MHz. This reduction in input current disturbance will result in a reduced input filter volume and/or loss to meet the same input current emissions specification.

Finally, in comparison with the output inductor variant, the input inductor FCML converter reduces the effort required for power factor correction control. Since  $L_{\rm t}$  is directly in series with the rectified input voltage source, control of  $i_{\rm t}$ directly controls the input current. In comparison, for the output inductor FCML converter, controlling the output inductor current does not directly dictate the input current as  $\langle i_{\rm in} \rangle = D \langle i_L \rangle$  where  $\langle x \rangle$  denotes the average value of x over a switching period and D is the duty cycle applied to the highside switches. Additionally, the input and flying capacitors within the output inductor FCML converter present a reactive power draw to the grid [2]. To compensate this reactive power draw and maintain high power factor, the inductor current reference must be modified to be bipolar rather than strictly positive. This presents control challenges for the active balancing controller as the inductor current crosses zero.

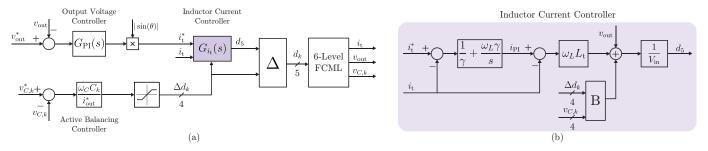

Fig. 4: Block diagram for the implemented combined active flying capacitor voltage balancer and inductor controller for a six-level input inductor FCML converter. (a) Overall control structure. (b) Inductor current controller which includes both feedback decoupling and a PI controller. Block **B** represents the feedback decoupling between the active flying capacitor voltage balancer and the inductor current controller, shown explicitly in (20). Block  $\Delta$  generates individual duty cycles from the collection of  $d_{N-1}$  and  $\Delta d_k$  as in (21).

### III. CONTROLLER DEVELOPMENT

A significant challenge associated with using an FCML converter in a buck-type PFC application is the large-signal, time-varying input voltage. That is, the voltages on  $C_{\rm in}$  and  $C_{\rm in,F}$  follow a rectified sinusoid value with a frequency of twice the mains frequency (e.g., 120 Hz). In order to utilize low voltage switches, the voltages on the flying capacitors within the converter must maintain a "balanced" distribution where  $v_{C,k} = (kv_{\rm in})/(N-1)$  where k ranges from 1 to N-2. If this flying capacitor voltage distribution is not maintained, excessive voltage stress will be applied to the switches, potentially resulting in converter failure. Typically, the FCML converter is operated with symmetric phase shifted-PWM (PS-PWM); in this scheme each high-side switch is modulated with the same duty cycle and switch gating signals are evenly phase shifted [4], yielding passive balancing of the flying capacitor voltages [11], [12]. The bandwidths of passive balancing are often insufficient to allow the flying capacitors to track a twice-line-frequency reference as would be required in a buck-type PFC application [2].

### A. Plant Model

Active flying capacitor voltage balancing changes the modulation scheme of the converter to achieve the desired flying capacitor voltage distribution. The derivation of this control law is similar to the derivations of [13], [14] and was shown to be effective in an output inductor FCML converter for buck-type PFC applications in [15]. We use state space averaging [16] to analyze the plant and make the simplifying approximation that  $v_{C_{\rm in,F}} \approx v_{C_{\rm in}}$ . First, we develop a model for the flying capacitor voltages assuming that the high-side switches  $S_{{\rm H},k}$  are driven by switching signals  $q_k$  which have duty cycles  $d_k$ :

$$\langle i_{C,k} \rangle = C_k \frac{\mathrm{d}}{\mathrm{d}t} \langle v_{C,k} \rangle = \langle (q_{k+1} - q_k)(i_t + i_b) \rangle$$

$$\approx \langle q_{k+1} - q_k \rangle \langle i_t + i_b \rangle$$

$$= (d_{k+1} - d_k)(I_t + I_b) \tag{15}$$

$$= \Delta d_k (I_t + I_b), \tag{16}$$

where  $I_{\rm t}=\langle i_{\rm t}\rangle$ . Thus the flying capacitor voltages respond primarily to  $\Delta d_k$ , the differences in duty cycles of adjacent

switch pairs. To develop a plant model for the top inductor current  $i_t$ , we analyze the voltage across  $L_t$ :

$$\langle v_{L_{t}} \rangle = \left\langle v_{C,\text{in}} q_{N-1} - v_{\text{out}} - \sum_{k=1}^{N-2} (q_{k+1} - q_{k}) v_{C,k} \right\rangle$$

$$\tag{17}$$

$$L_{\rm t} \frac{\mathrm{d}}{\mathrm{d}t} \langle i_{\rm t} \rangle \approx \langle v_{C,\rm in} \rangle d_{N-1} - \langle v_{\rm out} \rangle - \sum_{k=1}^{N-2} \Delta d_k \langle v_{C,k} \rangle. \tag{18}$$

The inductor current thus primarily responds to a weighted sum of all of the duty cycles and the output voltage  $v_{\rm out}$ . We can focus exclusively on the flying capacitor voltages  $v_{C,k}$  and the top inductor current  $i_{\rm t}$  as the control objectives are to regulate the input current and the flying capacitor voltages. The active flying capacitor voltage balancer can thus adjust  $\Delta d_k$  to control the flying capacitor voltages  $v_{C,k}$  and the inductor current controller can adjust  $d_{N-1}$  to control the inductor current  $i_{\rm t}$ . As in [15], feedback decoupling [13], [17] can be employed to remove the dependence of the inductor current on the output of the active flying capacitor voltage balancer  $\Delta d_k$ . Fig. 4 shows a control block diagram of the implemented control strategy.

### B. Controller Design

The duty cycle control law is thus given by:

$$\Delta d_k = \frac{\omega_C C_k}{i_{\text{out}}^*} = \frac{\omega_C C_k V_{\text{out}}}{i_t^* V_{\text{in}}}$$

(19)

$$d_{N-1} = \frac{1}{V_{\text{in}}} \left( (i_{\text{PI}} - i_{\text{t}}) L_{\text{t}} \omega_L + v_{\text{out}} + \sum_{k=1}^{N-2} \Delta d_k v_{C,k} \right)$$

(20)

$$d_k = d_{k+1} - \Delta d_k, \ k \in (1, N-2), \tag{21}$$

where  $i_{\rm PI}$  is the output of the PI controller shown in Fig. 4(b). The following control parameters were chosen empirically:  $\omega_L = 2\pi \cdot 2.78 \, {\rm kHz}, \; \omega_C = 2\pi \cdot 477 \, {\rm Hz}, \; \gamma = 0.35.$

The output of the active balancer  $\Delta d_k$  is followed by a saturation block with symmetrical limits of  $\pm 1\%$ . Near the zero-crossing of the grid voltage, the slew rates of the flying capacitor voltages are largest and the inductor currents are

smallest. These two properties result in large control actions from the active flying capacitor voltage balancer. By introducing a saturation block, the destabilizing effect of excessively large  $\Delta d_k$  can be avoided and minimal switch voltage stress maintained. Compared to [13], the inductor current controller uses measured flying capacitor voltages (rather than their quiescent values) when calculating the feedforward component of  $d_{N-1}$  (i.e.,  $\Delta d_k v_{C,k}$  rather than  $\Delta d_k \cdot k V_{\rm in}/(N-1)$  in (21)). This design choice resulted in improved current quality, particularly near the zero-crossings of the grid voltage. As in [15], by introducing scaling constant  $\gamma$  to the PI controller's proportional and integrator terms (cf. [13]), a larger phase margin and high-frequency gain are achieved. However, the system is no longer designed to be first-order, one of the objectives in [13].

### IV. EXPERIMENTAL RESULTS

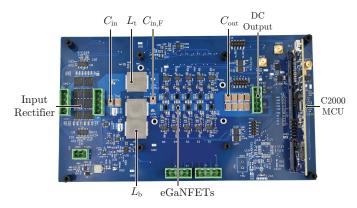

Fig. 5: Photograph of the hardware prototype. A component list of the power stage is provided in Table I. Dimensions:  $222\,\mathrm{mm}\times127.5\,\mathrm{mm}$ .

TABLE I: System Specifications and List of Main Components

| Parameter           | Value                                            |

|---------------------|--------------------------------------------------|

| $v_{ m ac}$         | $208\text{-}240\mathrm{V_{rms}}$                 |

| $V_{ m dc}$         | 48 V                                             |

| $P_{ m out}$        | $820\mathrm{W}$                                  |

| $f_{ m sw}$         | $100\mathrm{kHz}$                                |

| Power Semicond.     | $1.8\mathrm{m}\Omega$ 100 V EPC 2302             |

| Rectifier           | $61 \mathrm{m}\Omega$ 650 V STL57N65M5           |

| $L_{ m t}$          | 15 $\mu$ H (IHLP6767DZER150M11)                  |

| $L_{ m b}$          | $3 \mu H (IHLP6767DZER1R5M11)^*$                 |

| $C_{ m buf}$        | 162 mF (380LX183M063A082)                        |

| $C_{ m in}$         | $4.4 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$  |

| $C_{\mathrm{in,F}}$ | 11 $\mu$ F (C5750X6S2W225K250KA)                 |

| $C_{ m out}$        | $30.8 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$ |

| $C_1$               | $8.8 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$  |

| $C_2$               | $13.2 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$ |

| $C_3$               | $17.6 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$ |

| $C_4$               | $22 \mu\text{F} \text{ (C5750X6S2W225K250KA)}$   |

<sup>\*</sup> $L_{\rm b}$  is composed of two 1.5  $\mu{\rm H}$  inductors in series.

A hardware prototype, shown in the annotated photograph of Fig. 5, was developed to validate the proposed topol-

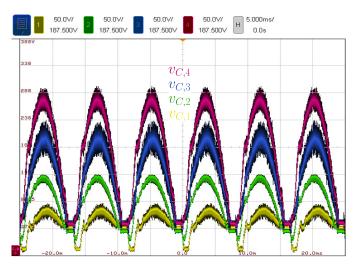

Fig. 6: Measured flying capacitor voltages. The flying capacitor voltages are able to track their reference values sufficiently well to limit the peak switch voltage stress.

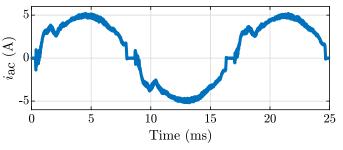

(a) Measured line current. The input current achieves a power factor of 0.9898 as measured by a Keysight PA2201A power analyzer.

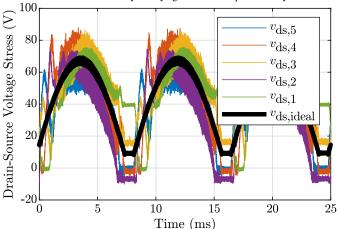

(b) Measured switch drain-source voltage stress. Ideally, the peak switch drain-source voltage is  $v_{\rm in}/(N-1)$  (plotted in black). This ideal voltage stress is achieved only when all flying capacitor voltages are at the balanced distribution

Fig. 7: Measured input voltage and current and switch voltage stress when operating at  $v_{\rm ac}=240\,{\rm V_{rms}},\ V_{\rm out}=48\,{\rm V},$  and  $P_{\rm out}=817\,{\rm W}.$  High fidelity control of the input current to achieve high power factor and sufficient flying capacitor voltage balancing to limit the peak switch voltage stress are the most pertinent goals of the controller. The peak switch voltage stress is  $88.37\,{\rm V}.$

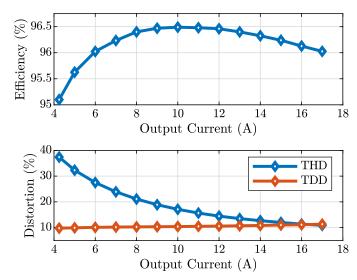

Fig. 8: Measured efficiency and line current THD and TDD for the operating point  $v_{\rm ac}=208\,{\rm V_{rms}},\ V_{\rm out}=48\,{\rm V}.$  The measured peak efficiency is 96.49% at  $P_{\rm out}=480\,{\rm W}.$  The measured line current passes the IEC61000-3-2 Class A harmonic limits for all measured points.

ogy and control structure. Relevant system specifications and component parameters are given in Table I. A second order generalized integrator (SOGI) [18] was used to generate the reconstructed grid voltages for phase-locking. A discrete  $10\,\mu\mathrm{H}$  inductor was inserted in series with the ac power supply to emulate realistic grid inductance.

As can be observed in Fig. 6, the flying capacitor voltages track the rectified sinusoidal reference, indicating low voltage stress on the switches. Fig. 7 shows the measured input current and switch voltage stress. The input inductor current  $i_{\rm t}$  tracks its rectified sinusoid reference, yielding high power factor and low THD input current. Additionally, as evidenced by Fig. 7(b), the active flying capacitor voltage balancing controller is able to maintain low switch voltage stress across the full ac cycle. Switch drain-source voltage stress is calculated as the differences in adjacent flying capacitor voltages for  $v_{\rm ds,2,3,4}$ .  $v_{\rm ds,5} = v_{C,\rm in,F} - v_{C,5}$  and  $v_{\rm ds,1} = v_{C,1}$ . The peak switch voltage stress is 88.37 V.

At an input voltage of  $208\,\mathrm{V_{rms}}$ , the converter achieves a full-power (820 W) efficiency of 95.64% at a power factor of 0.993 and current THD of 9.79% and a peak efficiency of 96.49% at an output power of  $480\,\mathrm{W}$ . At an input voltage of  $240\,\mathrm{V_{rms}}$ , the converter achieves a full-power efficiency of 95.72% at a power factor of 0.990 and current THD of 12.75% as measured by a Keysight PA2201A power analyzer. Fig. 8 shows the efficiency and line current distortion characteristic with respect to output current. Total demand distortion (TDD) is defined as TDD = THD  $\cdot I_1/I_D$ , where THD is the total harmonic distortion,  $I_1$  the fundamental current magnitude and  $I_D$  the rated fundamental current. From 25% power to full load, the TDD is below 12%. Across this power range, the measured line current harmonics stay well within the

IEC61000-3-2 Class A limits.

### V. CONCLUSION

This paper presents an input inductor FCML converter for a buck-type PFC rectifier utilizing active flying capacitor voltage balancing. The input inductor topology reduces both the control and filtering effort required for achieving high quality mains current compared to an output inductor topology. Additionally, the FCML converter enables high power density through a reduction in magnetics volume and high efficiency through the utilization of low voltage switches compared to a two-level converter. To utilize the FCML converter in this application, an active flying capacitor voltage balancing control scheme was developed which operates in tandem with the input current controller. The proposed topology and controller were validated on a hardware prototype resulting in a peak efficiency of 96.49% and a current THD of 9.79% at full load converting  $208\,V_{\rm rms}$  to  $48\,V.$

### REFERENCES

- H. Endo, T. Yamashita, and T. Sugiura, "A high-power-factor buck converter," in PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, Jun. 1992, pp. 1071–1076 vol.2.

- [2] E. Candan, N. C. Brooks, A. Stillwell, R. A. Abramson, J. Strydom, and R. C. N. Pilawa-Podgurski, "A Six-Level Flying Capacitor Multilevel Converter for Single-Phase Buck-Type Power Factor Correction," *IEEE Transactions on Power Electronics*, vol. 37, no. 6, pp. 6335–6348, Jun. 2022.

- [3] N. Brooks and R. Pilawa-Podgurski, "Hybrid Switched-Capacitor Converter Design: State-Space Dynamical Modeling and Passive Device Characterization," PhD Thesis, EECS Department, University of California, Berkeley, Aug. 2023.

- [4] T. A. Meynard and H. Foch, "Multi-level conversion: high voltage choppers and voltage-source inverters," in PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, Jun. 1992, pp. 397–403 vol.1.

- [5] J. Azurza Anderson, G. Zulauf, J. W. Kolar, and G. Deboy, "New Figure-of-Merit Combining Semiconductor and Multi-Level Converter Properties," *IEEE Open Journal of Power Electronics*, vol. 1, pp. 322– 338, 2020.

- [6] R. Tymerski and V. Vorperian, "Generation and classification of PWM DC-to-DC converters," *IEEE Transactions on Aerospace and Electronic Systems*, vol. 24, no. 6, pp. 743–754, Nov. 1988.

- [7] W. W. Weaver and P. T. Krein, "Analysis and applications of a current-sourced buck converter," in APEC 07 Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition. Anaheim, CA, USA: IEEE, Feb. 2007, pp. 1664–1670.

- [8] A. Abdulslam and P. P. Mercier, "8.2 A Continuous-Input-Current Passive-Stacked Third-Order Buck Converter Achieving 0.7W/mm2 Power Density and 94% Peak Efficiency," in 2019 IEEE International Solid- State Circuits Conference - (ISSCC), Feb. 2019, pp. 148–150.

- [9] —, "A Battery-Connected Inductor-First Flying Capacitor Multilevel Converter Achieving 0.77W/mm2 and 97.1% Peak Efficiency," in 2021 IEEE Custom Integrated Circuits Conference (CICC), Apr. 2021, pp. 1–2.

- [10] F. Krismer, "Modeling and optimization of bidirectional dual active bridge DC-DC converter topologies," Doctoral Thesis, ETH Zurich, Zürich, 2010.

- [11] T. Meynard, M. Fadel, and N. Aouda, "Modeling of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 44, no. 3, pp. 356–364, Jun. 1997.

- [12] R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "On the Role of Switch Output Capacitance on Passive Balancing within the Flying Capacitor Multilevel Converter," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), Jun. 2022, pp. 1–6.

- [13] O. Tachon, M. Fadel, and T. Meynard, "Control of Series Multicell Converters by Linear State Feedback Decoupling," 7th European Conference on Power Electronics and Applications EPE' 97, pp. 588–593, Sep. 1997.

- [14] R. K. Iyer, I. Z. Petric, R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A High-Bandwidth Parallel Active Balancing Controller for Current-Controlled Flying Capacitor Multilevel Converters," in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2023, pp. 775–781.

- [15] R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, "A Combined Power Factor Correcting and Active Voltage Balancing Control Technique for Buck-Type AC/DC Grid-Tied Flying Capacitor Multilevel Converters," in 2023 IEEE 24th Workshop on Control and Modeling for Power Electronics (COMPEL), Jun. 2023, pp. 1–5.

- [16] R. D. Middlebrook and S. Cuk, "A general unified approach to modelling switching-converter power stages," in 1976 IEEE Power Electronics Specialists Conference, Jun. 1976, pp. 18–34.

- [17] E. G. Gilbert, "The Decoupling of Multivariable Systems by State Feedback," SIAM Journal on Control, vol. 7, no. 1, pp. 50–63, Feb. 1969

- [18] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in 2006 37th IEEE Power Electronics Specialists Conference, Jun. 2006, pp. 1– 6.