## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

### **Title**

Automatically Tuning Collective Communication for One-Sided Programming Models

### **Permalink**

https://escholarship.org/uc/item/8bg8c2rk

### **Author**

Nishtala, Rajesh

### **Publication Date**

2009

Peer reviewed|Thesis/dissertation

### Automatically Tuning Collective Communication for One-Sided Programming Models

by

### Rajesh Nishtala

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Katherine A. Yelick, Chair Professor James W. Demmel Professor Panayiotis Papadopoulos

Fall 2009

## Automatically Tuning Collective Communication for One-Sided Programming Models

Copyright 2009 by Rajesh Nishtala

#### Abstract

Automatically Tuning Collective Communication for One-Sided Programming Models

by

Rajesh Nishtala

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Katherine A. Yelick, Chair

Technology trends suggest that future machines will rely on parallelism to meet increasing performance requirements. To aid in programmer productivity and application performance, many parallel programming models provide communication building blocks called *collective communication*. These operations, such as Broadcast, Scatter, Gather, and Reduce, abstract common global data movement patterns behind a simple library interface allowing the hardware and runtime system to optimize them for performance and scalability.

We consider the problem of optimizing collective communication in Partitioned Global Address Space (PGAS) languages. Rooted in traditional shared memory programming models, they deliver the benefits of sophisticated distributed data structures using language extensions and one-sided communication. One-sided communication allows one processor to directly read and write memory associated with another. Many popular PGAS language implementations share a common runtime system called GASNet for implementing such communication. To provide a highly scalable platform for our work, we present a new implementation of GASNet for the IBM BlueGene/P, allowing GASNet to scale to tens of thousands of processors.

We demonstrate that PGAS languages are highly scalable and that the one-sided communication within them is an efficient and convenient platform for collective communication. We show how to use one-sided communication to achieve  $3\times$  improvements in the latency and throughput of the collectives over standard message passing implementations. Using a 3D FFT as a representative communication bound benchmark, for example, we see a 17% increase in performance on 32,768 cores of the BlueGene/P and a  $1.5\times$  improvement on 1024 cores of the CrayXT4. We also show how the automatically tuned collectives can deliver more than an order of magnitude in performance over existing implementations on shared memory platforms.

There is no obvious best algorithm that serves all machines and usage patterns demonstrating the need for tuning and we thus build an automatic tuning system in GASNet that optimizes the collectives for a variety of large scale supercomputers and novel multicore architectures. To understand the large search space, we construct analytic performance

models use them to minimize the overhead of autotuning. We demonstrate that autotuning is an effective approach to addressing performance optimizations on complex parallel systems.

Dedicated to Rakhee, Amma, and Nanna for all their love and encouragement

# Contents

| Li | st of                  | Figures                                                      | 7  |  |  |  |

|----|------------------------|--------------------------------------------------------------|----|--|--|--|

| 1  | Intr                   | roduction                                                    | -  |  |  |  |

|    | 1.1                    | Related Work                                                 | •  |  |  |  |

|    |                        | 1.1.1 Automatically Tuning MPI Collective Communication      | •  |  |  |  |

|    | 1.2                    | Contributions                                                | 2  |  |  |  |

|    | 1.3                    | Outline                                                      | ,  |  |  |  |

| 2  | Experimental Platforms |                                                              |    |  |  |  |

|    | 2.1                    | Processor Cores                                              | 8  |  |  |  |

|    | 2.2                    | Nodes                                                        | 8  |  |  |  |

|    |                        | 2.2.1 Node Architectures                                     | 6  |  |  |  |

|    |                        | 2.2.2 Remote Direct Memory Access                            | 1  |  |  |  |

|    | 2.3                    | Interconnection Networks                                     | 1: |  |  |  |

|    |                        | 2.3.1 CLOS Networks                                          | 1: |  |  |  |

|    |                        | 2.3.2 Torus Networks                                         | 1  |  |  |  |

|    | 2.4                    | Summary                                                      | 1' |  |  |  |

| 3  | One                    | e-Sided Communication Models                                 | 19 |  |  |  |

| •  | 3.1                    | Partitioned Global Address Space Languages                   | 19 |  |  |  |

|    | 9                      | 3.1.1 UPC                                                    | 20 |  |  |  |

|    |                        | 3.1.2 One-sided Communication                                | 2  |  |  |  |

|    | 3.2                    | GASNet                                                       | 2  |  |  |  |

|    | J                      | 3.2.1 GASNet on top of the BlueGene/P                        | 2  |  |  |  |

|    |                        | 3.2.2 Active Messages                                        | 28 |  |  |  |

| 4  | Col                    | lective Communication                                        | 29 |  |  |  |

| 4  | 4.1                    | The Operations                                               | 29 |  |  |  |

|    | 4.1                    | 4.1.1 Why Are They Important?                                | 30 |  |  |  |

|    | 4.2                    | Implications of One-Sided communication for Collectives      | 3  |  |  |  |

|    | 4.4                    |                                                              | 3. |  |  |  |

|    |                        |                                                              |    |  |  |  |

|    |                        |                                                              | 32 |  |  |  |

|    |                        |                                                              | 33 |  |  |  |

|    |                        | 4.2.4 Optimizing the Synchronization and Collective Together | 3  |  |  |  |

|   | 4.3 | Collectives Used in Applications         | 35         |

|---|-----|------------------------------------------|------------|

| 5 | Roc | v                                        | 38         |

|   | 5.1 |                                          | 36         |

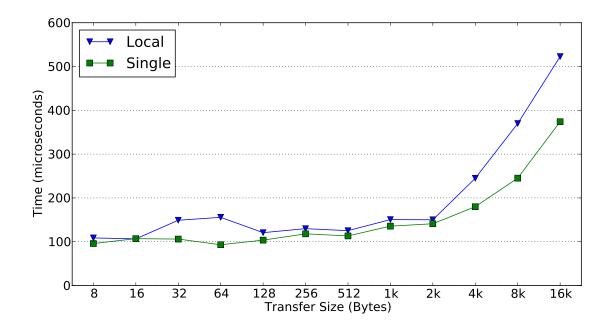

|   |     | 5.1.1 Leveraging Shared Memory           | 36         |

|   |     | 5.1.2 Trees                              | 40         |

|   |     | 5.1.3 Address Modes                      | 49         |

|   |     | 5.1.4 Data Transfer                      | 51         |

|   |     | 5.1.5 Nonblocking Collectives            | 52         |

|   |     |                                          | 55         |

|   |     |                                          | 56         |

|   | 5.2 |                                          | 58         |

|   | · - |                                          | 58         |

|   |     | 1                                        | 59         |

|   |     |                                          | 60         |

|   |     |                                          | 62         |

|   | 5.3 |                                          | 64         |

|   | 5.5 |                                          | 66         |

|   |     |                                          | 69         |

|   |     |                                          | 68<br>68   |

|   |     |                                          |            |

|   | F 1 |                                          | 72         |

|   | 5.4 | 11                                       | 72         |

|   |     | *                                        | 74         |

|   |     | · ·                                      | 76         |

|   | 5.5 | Summary                                  | 78         |

| 6 |     | v                                        | <b>3</b> C |

|   | 6.1 | 9                                        | 80         |

|   |     |                                          | 82         |

|   |     |                                          | 86         |

|   | 6.2 |                                          | 86         |

|   |     | 6.2.1 Performance Model                  | 89         |

|   |     | 6.2.2 Nonblocking Collective Performance | 89         |

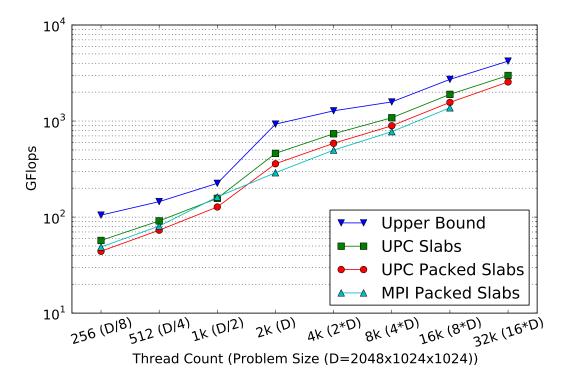

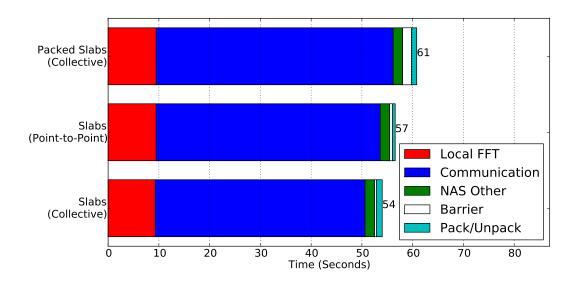

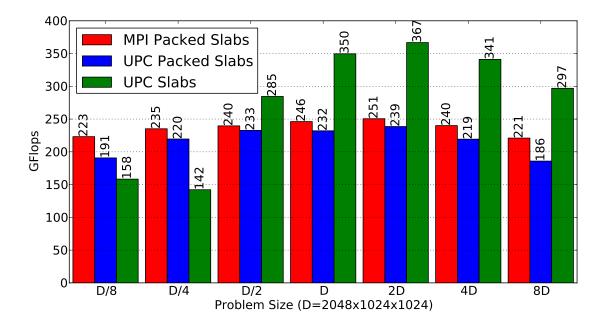

|   | 6.3 | Application Example: 3D FFT              | 90         |

|   |     | 6.3.1 Packed Slabs                       | 92         |

|   |     | 6.3.2 Slabs                              | 94         |

|   |     | 6.3.3 Summary                            | 94         |

|   |     | ·                                        | 95         |

|   | 6.4 |                                          | 99         |

| 7 | Col | ectives for Shared Memory Systems 10     | )1         |

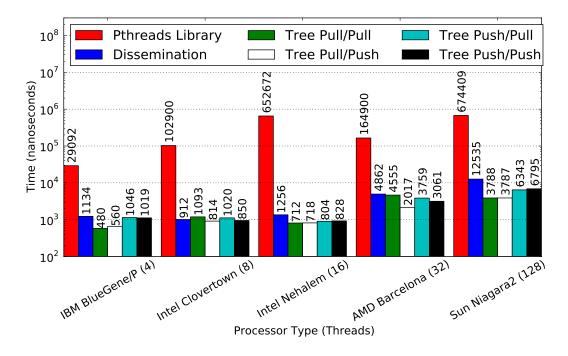

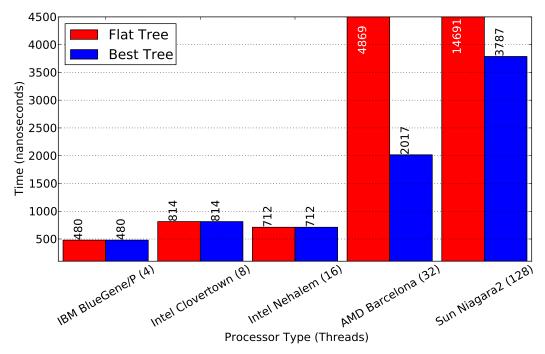

| • | 7.1 | Non-rooted Collective: Barrier           |            |

|   | 7.2 | Rooted Collectives                       |            |

|   | 1.4 | 7.2.1 Reduce                             |            |

|   |     | 1.2.1 1water                             | J          |

|    |       | 7.2.2 Other Rooted Collectives                 | 110 |

|----|-------|------------------------------------------------|-----|

|    | 7.3   | Application Example: Sparse Conjugate Gradient | 113 |

|    | 7.4   | Summary                                        | 115 |

| 8  | Soft  | ware Architecture of the Automatic Tuner       | 117 |

|    | 8.1   | Related Work                                   | 118 |

|    | 8.2   | Software Architecture                          | 119 |

|    |       | 8.2.1 Algorithm Index                          | 119 |

|    |       | 8.2.2 Phases of the Automatic Tuner            | 120 |

|    | 8.3   | Collective Tuning                              | 122 |

|    |       | 8.3.1 Factors that Influence Performance       | 122 |

|    |       | 8.3.2 Offline Tuning                           | 123 |

|    |       | 8.3.3 Online Tuning                            | 124 |

|    |       | 8.3.4 Performance Models                       | 125 |

|    | 8.4   | Summary                                        | 129 |

| 9  | Tea   | ms                                             | 132 |

|    | 9.1   | Thread-Centric Collectives                     | 132 |

|    |       | 9.1.1 Similarities and Differences with MPI    | 133 |

|    | 9.2   | Data-Centric Collectives                       |     |

|    |       | 9.2.1 Proposed Collective Model                | 135 |

|    |       | 9.2.2 An Example Interface                     | 135 |

|    |       | 9.2.3 Application Examples                     |     |

|    | 9.3   | Automatic Tuning with Teams                    | 142 |

|    |       | 9.3.1 Current Status                           | 144 |

| 10 | Con   | nclusion                                       | 146 |

| Bi | bliog | graphy                                         | 150 |

# List of Figures

| 2.1  | Sun Constellation Node Architecture                                               | 9  |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | Cray XT4 Node Architecture                                                        | 10 |

| 2.3  | Cray XT5 Node Architecture                                                        | 10 |

| 2.4  | IBM BlueGene/P Node Architecture                                                  | 11 |

| 2.5  | Example Hierarchies with 4 port switches                                          | 13 |

| 2.6  | Example 16-node 5-stage CLOS Network                                              | 13 |

| 2.7  | Sun Constellation System Architecture                                             | 15 |

| 2.8  | Example 8x8 2D torus Network                                                      | 16 |

| 3.1  | UPC Pointer Example                                                               | 21 |

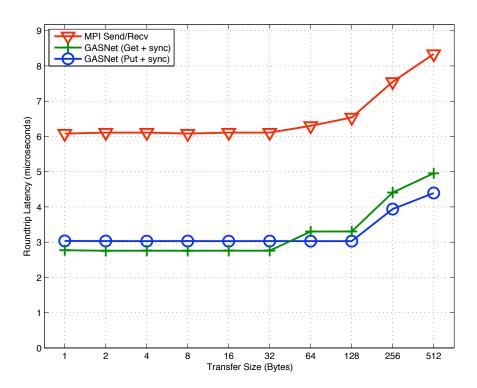

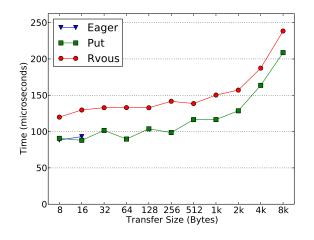

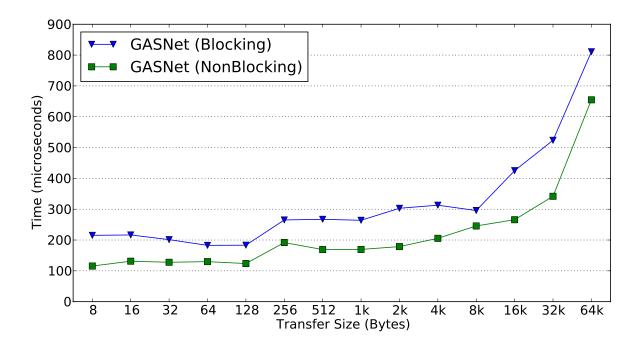

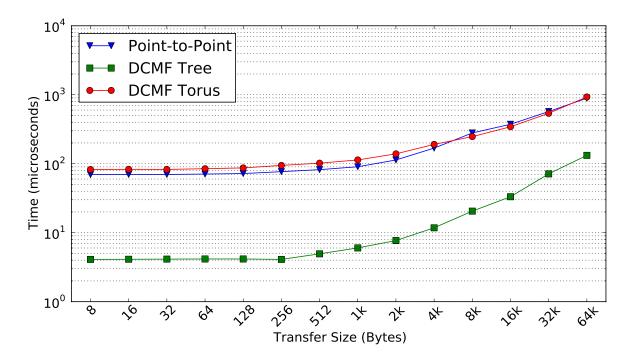

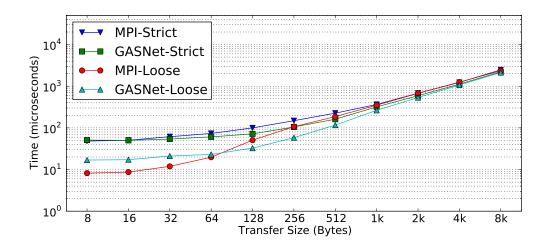

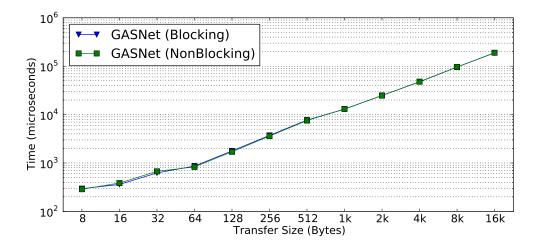

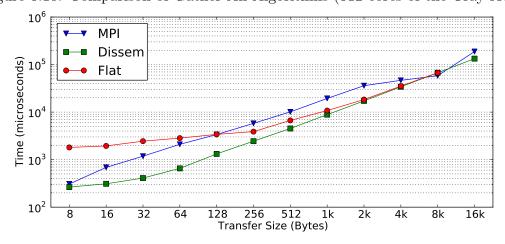

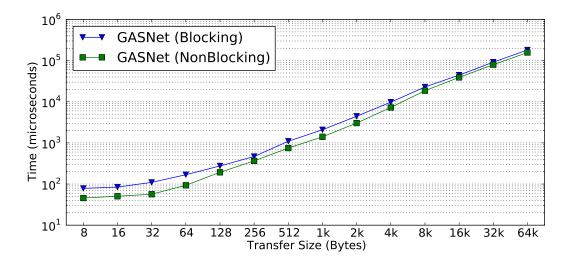

| 3.2  | Roundtrip Latency Comparison on the IBM BlueGene/P                                | 26 |

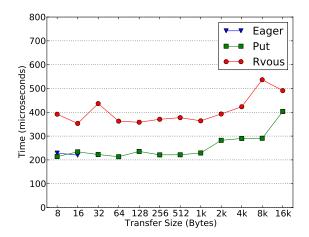

| 3.3  | Flood Bandwidth Comparison on the IBM BlueGene/P                                  | 26 |

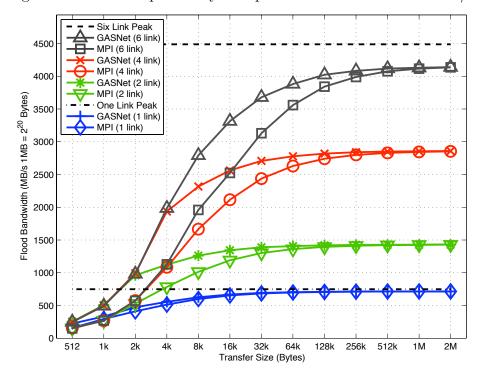

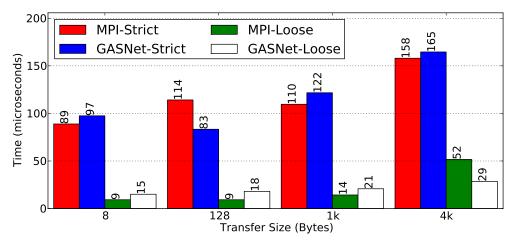

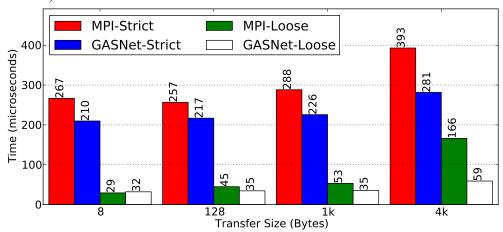

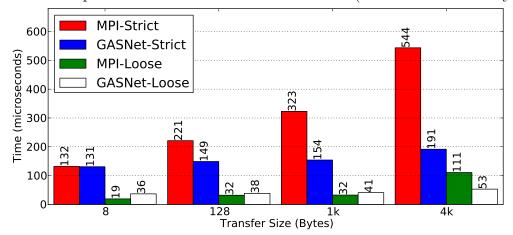

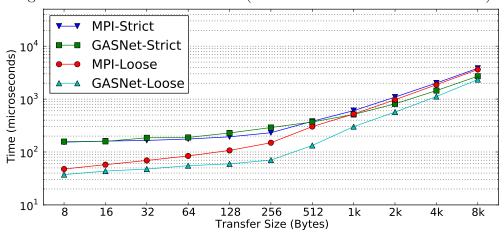

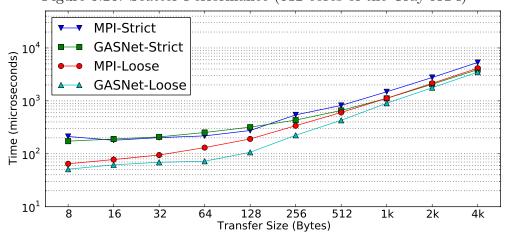

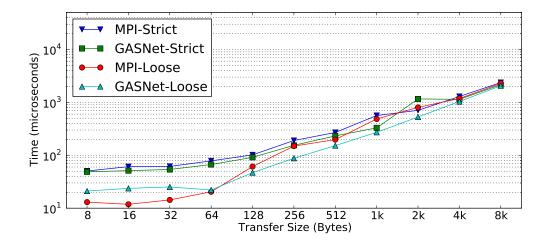

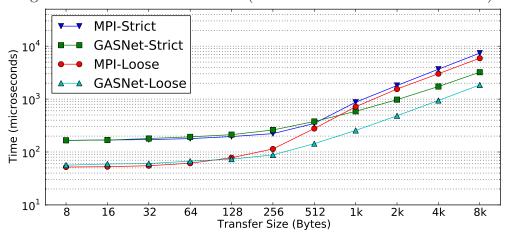

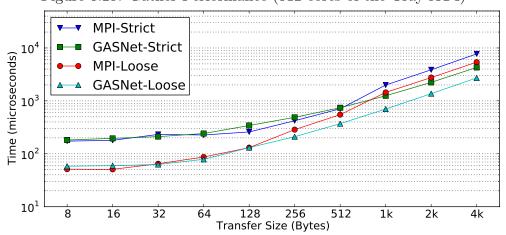

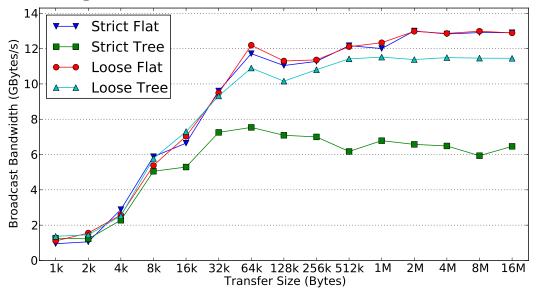

| 4.1  | Comparison of Loose and Strict Synchronization (1024 cores of the Cray XT4)       | 35 |

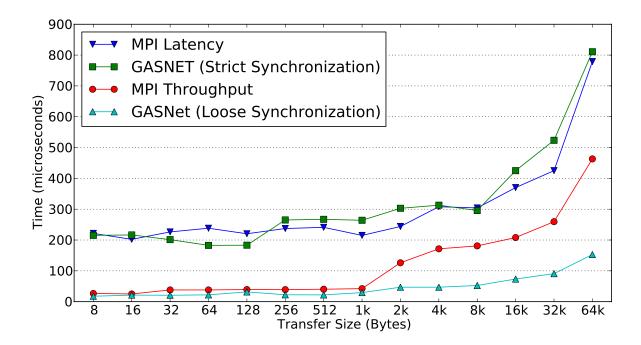

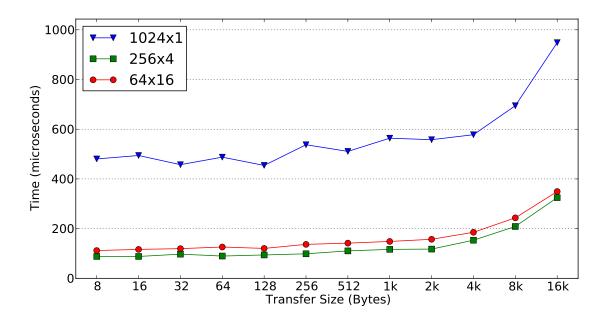

| 5.1  | Leveraging Shared Memory for Broadcast (1024 cores of the Sun Constellation)      | 40 |

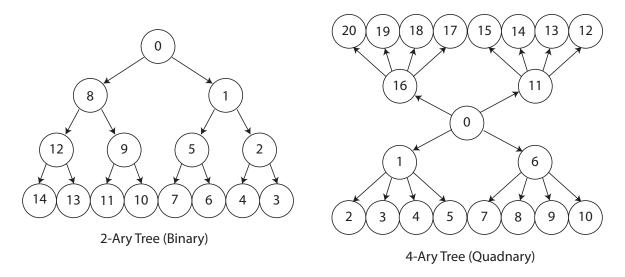

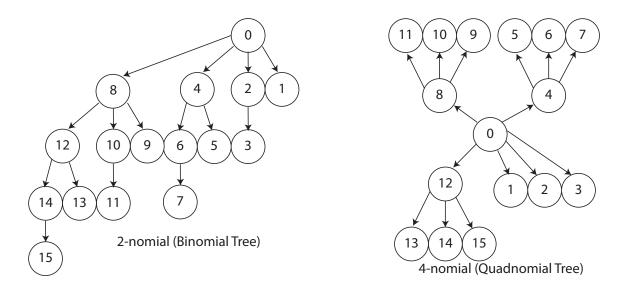

| 5.2  | Example K-ary Trees                                                               | 42 |

| 5.3  | Algorithm for K-ary Tree Construction                                             | 42 |

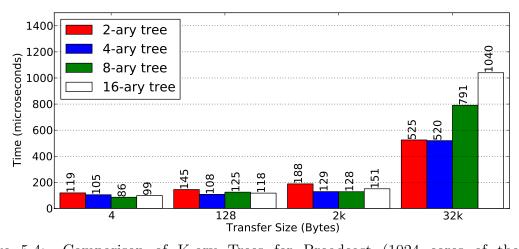

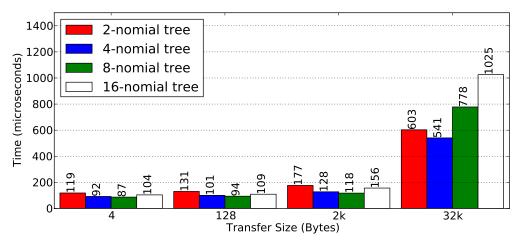

| 5.4  | Comparison of K-ary Trees for Broadcast (1024 cores of the Sun Constellation)     | 43 |

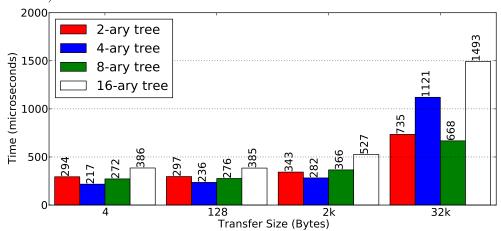

| 5.5  | Comparison of K-ary Trees for Broadcast (2048 cores of the Cray $XT4$ )           | 43 |

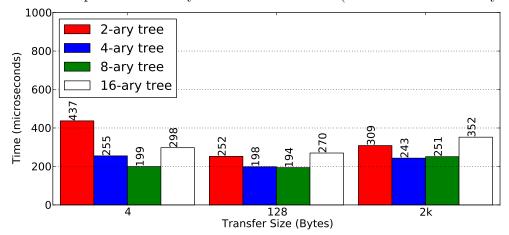

| 5.6  | Comparison of K-ary Trees for Broadcast (3072 cores of the Cray $XT5$ )           | 43 |

| 5.7  | Example K-nomial Trees                                                            | 44 |

| 5.8  | Algorithm for K-nomial Tree Construction                                          | 44 |

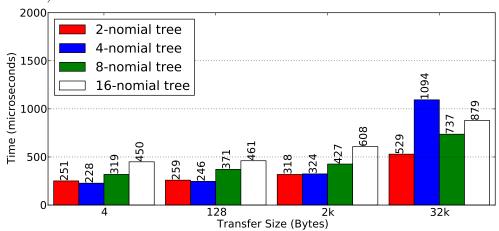

| 5.9  | Comparison of K-nomial Trees for Broadcast (1024 cores of the Sun Constel-        |    |

|      | lation)                                                                           | 45 |

|      | Comparison of K-nomial Trees for Broadcast (2048 cores of the Cray $XT4$ ) .      | 45 |

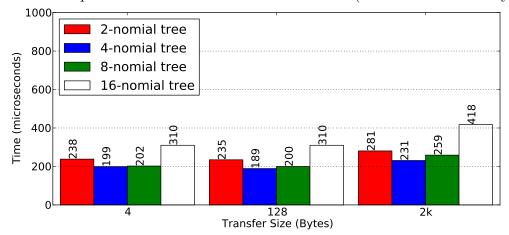

|      | Comparison of K-nomial Trees for Broadcast (3072 cores of the Cray $XT5$ ) .      | 45 |

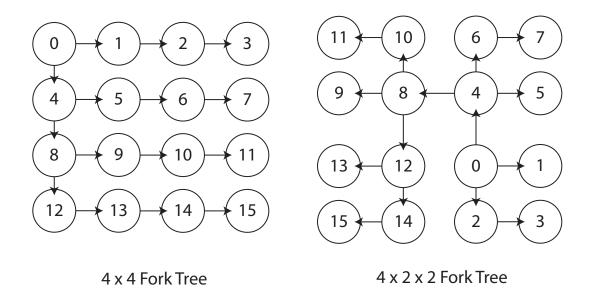

|      | Example Fork Trees                                                                | 47 |

|      | Algorithm for Fork Tree Construction                                              | 47 |

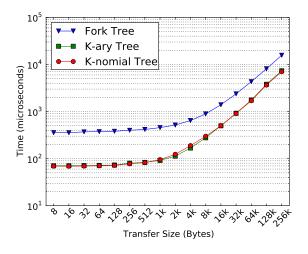

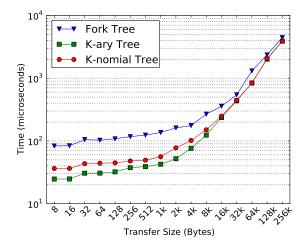

| 5.14 | Comparison of Tree Shapes for Strict Broadcast (2048 cores of the IBM Blue-       |    |

|      | Gene/P)                                                                           | 48 |

| 5.15 | Comparison of Tree Shapes for Loose Broadcast (2048 cores of the IBM Blue-Gene/P) | 48 |

| 5.16 | Address Mode comparison (1024 cores of the Sun Constellation)                     | 50 |

| 5.17 | Comparison of Data Transfer Mechanisms (1024 cores of the Sun Constellation) | 52 |

|------|------------------------------------------------------------------------------|----|

| 5.18 | Comparison of Data Transfer Mechanisms (2048 cores of the Cray XT4)          | 52 |

| 5.19 | Example Algorithm for Signaling Put Broadcast                                | 54 |

| 5.20 | Nonblocking Broadcast (1024 cores of the Cray XT4)                           | 55 |

|      | Hardware Collectives (2048 cores of the IBM BlueGene/P)                      | 56 |

|      | Comparison of GASNet and MPI Broadcast (1024 cores of the Sun Constel-       |    |

|      | lation)                                                                      | 57 |

| 5.23 | Comparison of GASNet and MPI Broadcast (2048 cores of the Cray XT4) .        | 57 |

|      | Comparison of GASNet and MPI Broadcast (1536 cores of the Cray XT5) .        | 57 |

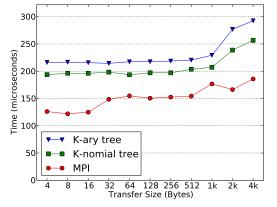

|      | Scatter Performance (256 cores of the Sun Constellation)                     | 61 |

|      | Scatter Performance (512 cores of the Cray XT4)                              | 61 |

|      | Scatter Performance (1536 cores of the Cray XT5)                             | 61 |

|      | Gather Performance (256 cores of the Sun Constellation)                      | 63 |

|      | Gather Performance (512 cores of the Cray XT4)                               | 63 |

|      | Gather Performance (1536 cores of the Cray XT5)                              | 63 |

|      | Sun Constellation Reduction Performance (4 bytes)                            | 65 |

|      | Sun Constellation Reduction Performance (1k bytes)                           | 65 |

|      | Strictly Synchronized Reduction Performance (2048 cores of the Cray XT4).    | 65 |

|      | Loosely Synchronized Reduction Performance (2048 cores of the Cray XT4).     | 65 |

|      | Strictly Synchronized Reduction Performance (1536 cores Cray XT5)            | 65 |

|      | Loosely Synchronized Reduction Performance (1536 cores Cray XT5)             | 65 |

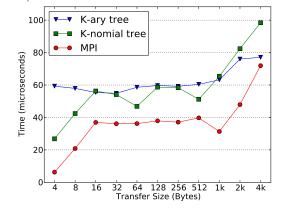

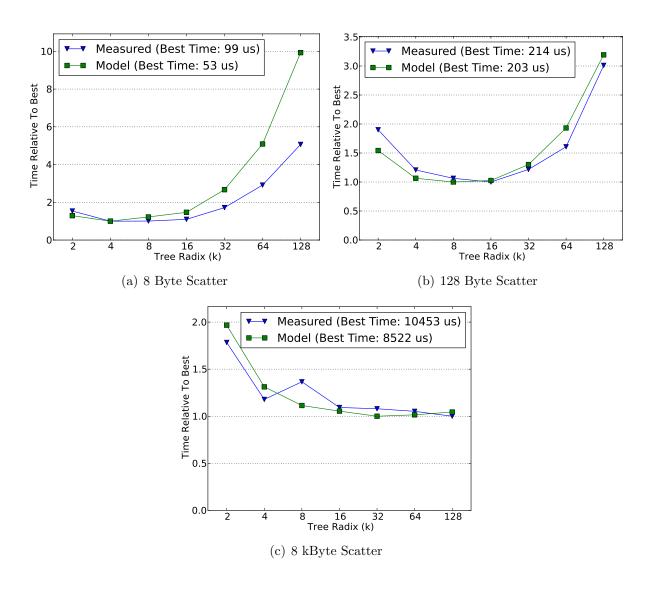

|      | Scatter Model Validation (1024 cores of the Sun Constellation)               | 68 |

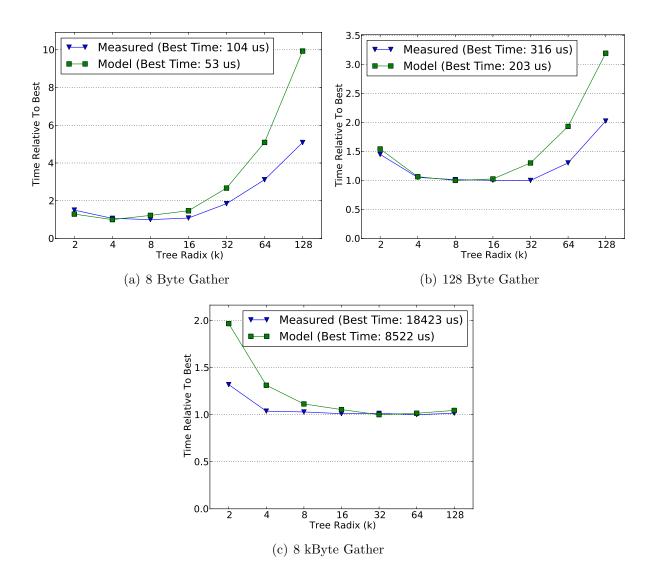

|      | Gather Model Validation (1024 cores of the Sun Constellation)                | 70 |

|      | Broadcast Model Validation (1024 cores of the Sun Constellation)             | 71 |

|      | Reduce Model Validation (1024 cores of the Sun Constellation)                | 73 |

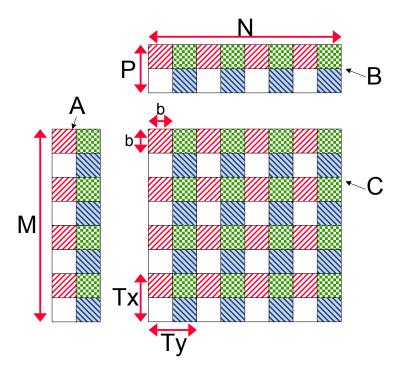

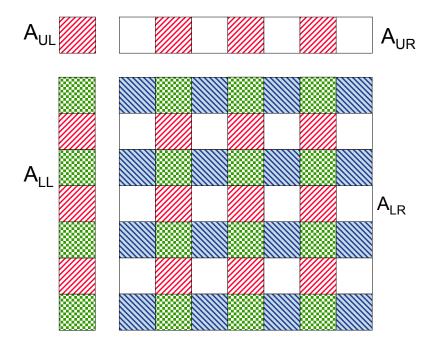

|      | Matrix Multiply Diagram                                                      | 75 |

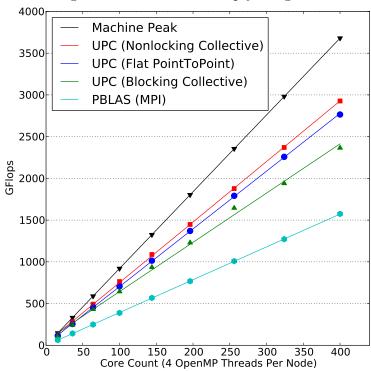

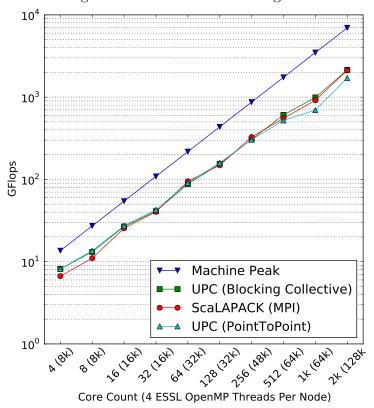

|      | Weak Scaling of Matrix Multiplication (Cray XT4)                             | 75 |

|      | Factorization Diagram                                                        | 77 |

|      | Weak Scaling of Dense Cholesky Factorization (IBM BlueGene/P)                | 77 |

|      | (                                                                            |    |

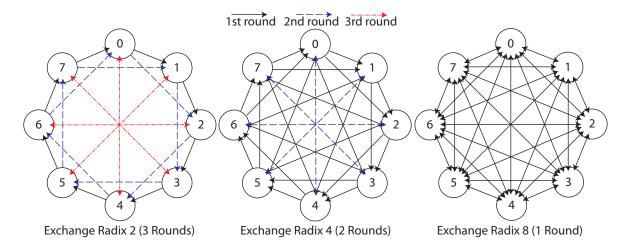

| 6.1  | Example Exchange Communication Pattern                                       | 81 |

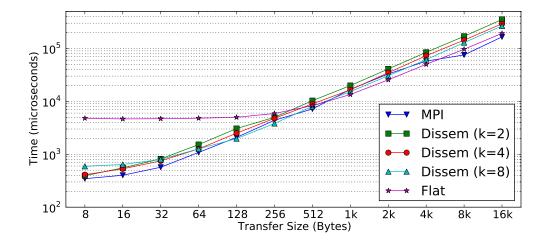

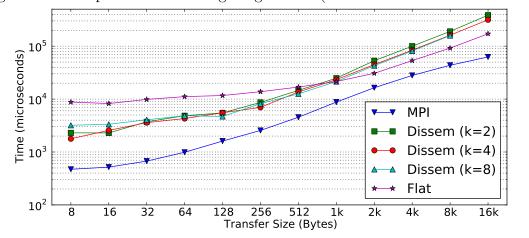

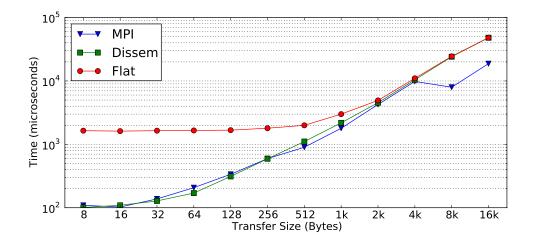

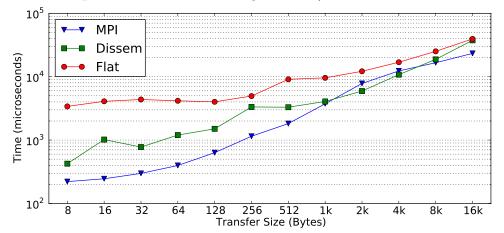

| 6.2  | Comparison of Exchange Algorithms (256 cores of Sun Constellation)           | 83 |

| 6.3  | Comparison of Exchange Algorithms (512 cores of the Cray XT4)                | 83 |

| 6.4  | Comparison of Exchange Algorithms (1536 cores of Cray XT5)                   | 83 |

| 6.5  | 8 Byte Exchange Model Verification (1024 cores of the Sun Constellation)     | 85 |

| 6.6  | 64 Byte Exchange Model Verification (1024 cores of the Sun Constellation) .  | 85 |

| 6.7  | 1 kByte Exchange Model Verification (1024 cores of the Sun Constellation) .  | 85 |

| 6.8  | Nonblocking Exchange (256 cores of Sun Constellation)                        | 86 |

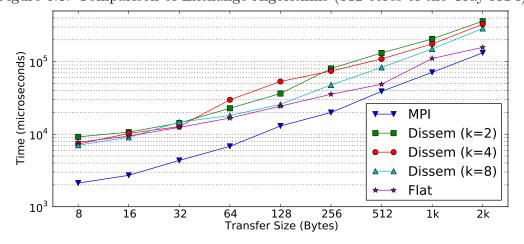

| 6.9  | Comparison of Gather All Algorithms (256 cores of Sun Constellation)         | 88 |

| 6.10 | Comparison of Gather All Algorithms (512 cores of the Cray XT4)              | 88 |

| 6.11 | Comparison of Gather All Algorithms (1536 cores of Cray XT5)                 | 88 |

|      | Nonblocking Gather-to-All (256 cores of Sun Constellation)                   | 90 |

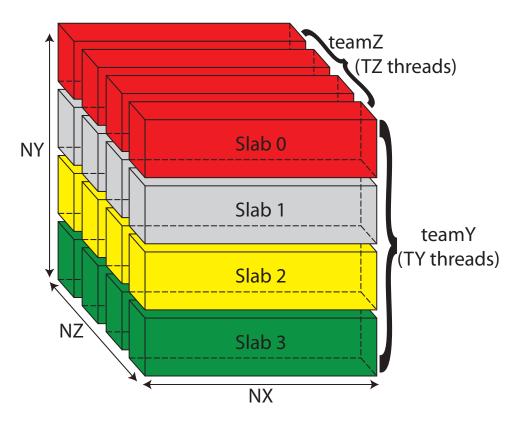

|      | 2D decomposition for FFT                                                     | 91 |

| 6.14 | FFT Packed Slabs Algorithm                                                   | 93 |

|      |                                                                              |    |

| $6.16 \\ 6.17$                         | FFT Slabs Algorithm                                                                                                                                                        | 94<br>96<br>97<br>98            |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

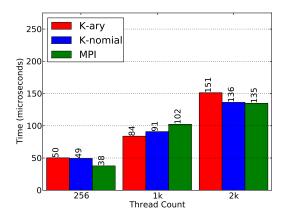

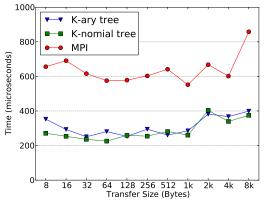

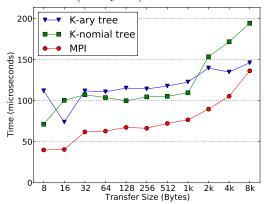

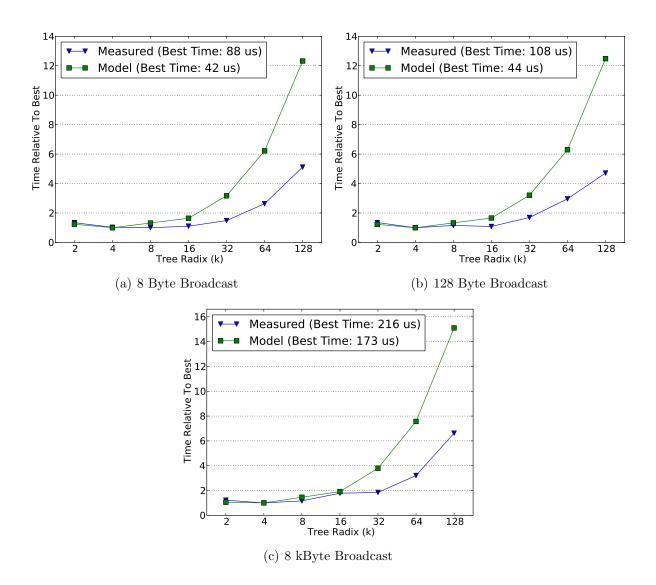

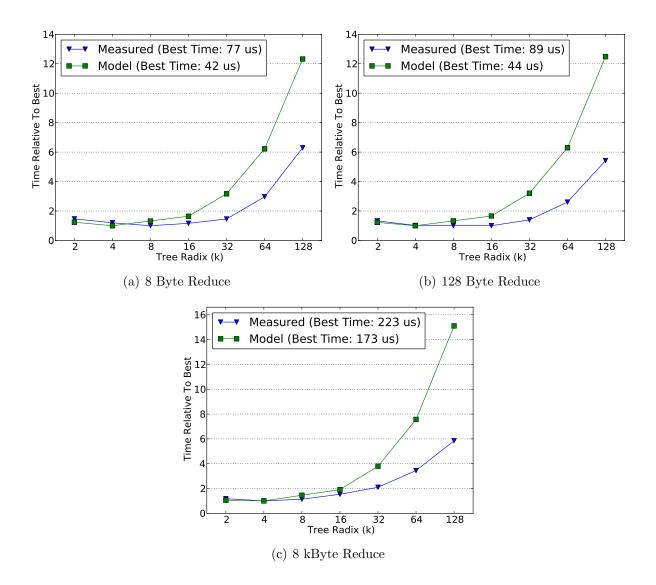

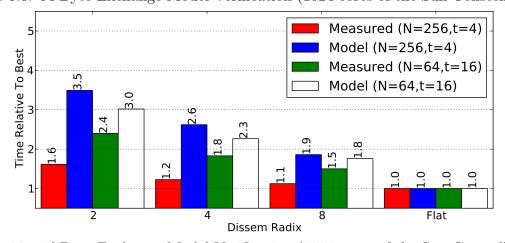

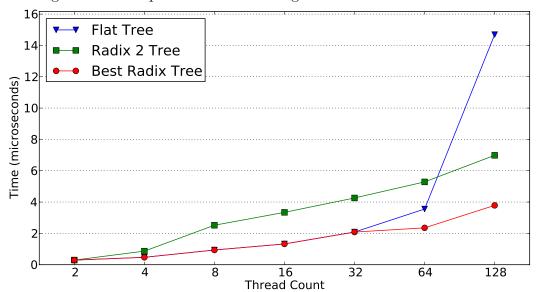

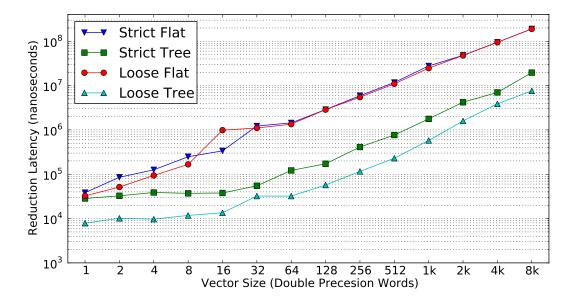

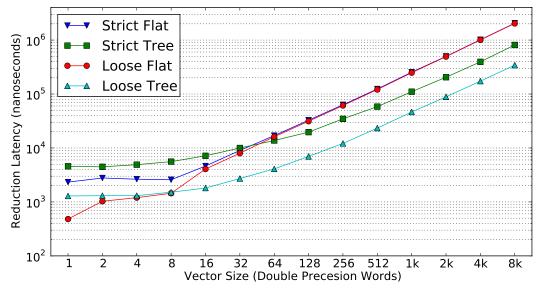

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Comparison of Barrier Algorithms for Shared Memory Platforms Comparison of Barrier Algorithms Flat versus Best Tree Comparison of Barrier Tree Radices on the Sun Niagara2 | 104<br>105<br>105<br>107<br>109 |

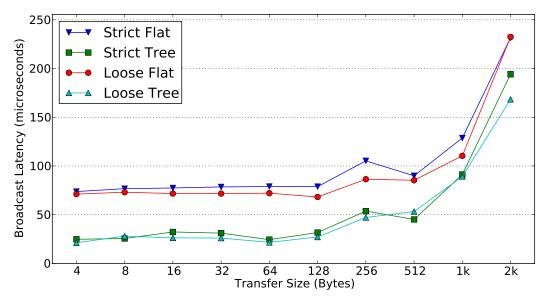

| 7.7<br>7.8<br>7.9                      | Comparison of Broadcast Algorithms on the Sun Niagara2 (128 threads) for Large Message Sizes                                                                               | 111<br>114<br>114               |

| 8.1<br>8.2                             | Flowchart of an Automatic Tuner                                                                                                                                            | 120                             |

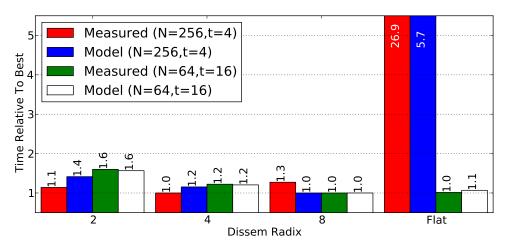

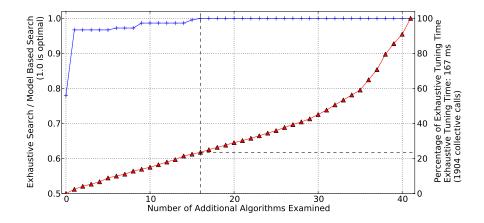

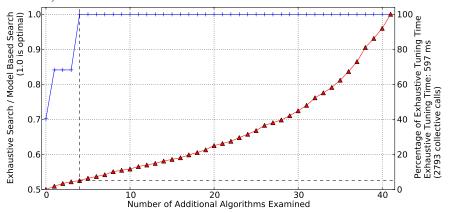

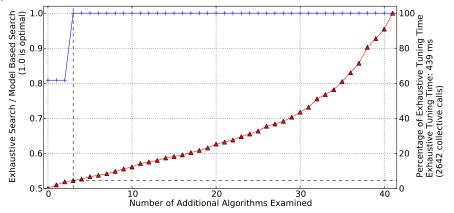

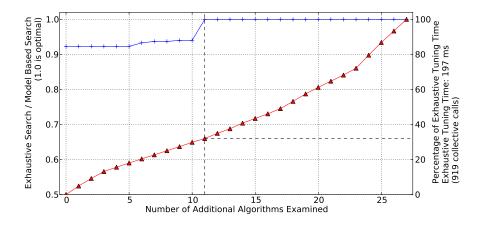

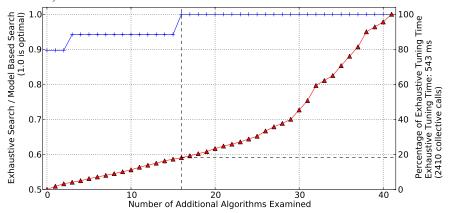

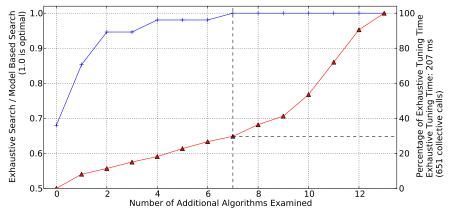

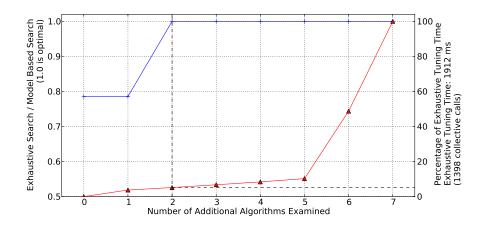

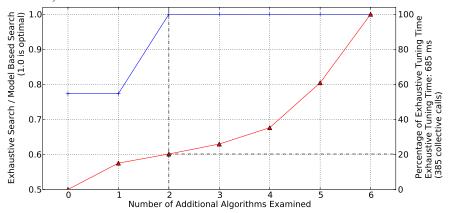

| 8.3                                    | Constellation)                                                                                                                                                             | 126<br>126                      |

| 8.4                                    | Guided Search using Performance Models: 8-byte Broadcast (3072 cores Cray XT5)                                                                                             | 126                             |

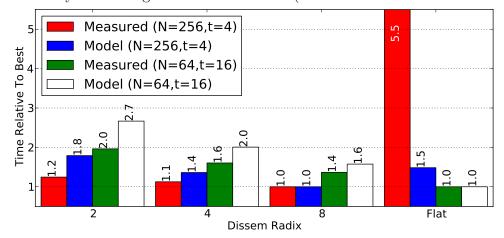

| 8.5                                    | Guided Search using Performance Models: 128-byte Scatter (1024 cores Sun Constellation)                                                                                    | 128                             |

| 8.6                                    | Guided Search using Performance Models: 128-byte Scatter (512 cores Cray XT4)                                                                                              | 128                             |

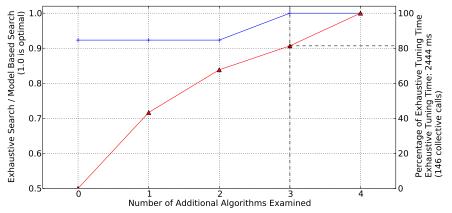

| 8.7<br>8.8                             | Guided Search using Performance Models: 128-byte Scatter (1536 cores Cray XT5)                                                                                             | 128                             |

| 8.9                                    | Constellation)                                                                                                                                                             | 130                             |

| 8.10                                   | XT4)                                                                                                                                                                       | 130                             |

|                                        | Cray XT5)                                                                                                                                                                  | 130                             |

| 9.1<br>9.2<br>9.3<br>9.4               | Strided Collective Examples                                                                                                                                                | 137<br>139<br>140<br>141        |

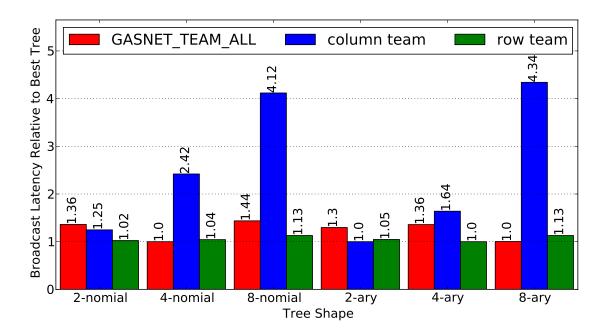

| 9.5                                    | Comparison of Trees on Different Teams (256 cores of the Sun Constellation)                                                                                                | 144                             |

### Acknowledgments

Firstly, I would like to thank my advisor, Kathy Yelick, for all her guidance, patience, enthusiasm, and encouragement through the years. Since first introducing me to the BeBOP group she has been a fantastic mentor. In addition to her invaluable technical advice, Kathy always ensured that I remained focused on the larger research and career goals. Her energy is inspiring.

I also owe a lot to Jim Demmel for his advice through the years. I will never forget how he spent a couple of days out of his busy schedule to patiently help me edit my first technical report, "When Cache Blocking Works and Why." His ability to explain complex mathematical concepts has allowed me to understand many interesting research projects outside my area of expertise. I am very fortunate to have Kathy and Jim as my mentors.

I greatly appreciate the help Dave Patterson and Panos Papadopoulos have given by agreeing to sit on my dissertation committee. Their feedback during the qualifying exam as well as during the dissertation was very useful.

I would like to thank the entire Berkeley UPC team, particularly Paul Hargrove, Dan Bonachea, Christian Bell, Costin Iancu, Wei Chen, Yili Zheng and Jason Duell for all their help. I would not have been able to do any of the work described in this thesis without their advice, foundations, and frameworks upon which my work was built.

Kaushik Datta has been my officemate for the past few years and we seem to find ourselves in similar situations and deadlines. He has been a great friend and collegue with whom I could discuss any subject related or not to computer science. Our Birkball games, Xbox breaks, Cheeseboard runs, and occasional ski trips to Lake Tahoe have made even the most frustrating days of graduate school seem fun.

I would like to thank all the members of the BeBOP group for their time and support to discuss my ideas. Rich Vuduc provided me guidance and assistance early on and is a great role model. I also would particularly like to thank Mark Hoemmen, Shoaib Kamil, Sam Williams, Marghoob Mohiyuddin, Ankit Jain, and Eun-Jin Im for their useful insights and suggestions on my work.

Outside of Berkeley I would like to thank George Almasi and Calin Cascaval at IBM for their help and mentorship during my summer internship and various conferences. They have provided an invaluable outside perspective.

In the Parallel Computing lab I found a nice sense of community. I had a chance to discuss parallel and distributed computing ideas with several of my colleagues who helped me frame my work so that it appeals to a broader audience. In particular I would like to thank Heidi Pan, Chris Batten, Krste Asanovic, Benjamin Hindman, Jimmy Su, Amir Kamil, Sarah Bird, Andrew Waterman, Bryan Catanzaro, and Jike Chong for their stimulating discussions and questions. I would also like to thank Jon Kuroda, Jeff Anderson-Lee, Tammy Johnson, and Laura Rebusi for all their help.

Rakhee, I could not have finished this without you. You always believed in me even when I didn't. Your love and emotional support mean more to me than I can ever put into words. Guess what, there's an "arm" between us now!

Finally, I am deeply grateful to my parents. Ever since my first days in elementary school you have always taught me to never cut corners, be meticulous and patient, and give

everything I have to whatever I do. These are critical lessons that I have relied on over the years. I will never be able to thank you enough for your sacrifices to ensure that I received a quality education. We've come a long way from the little boy that used to cry at the gate saying he didn't want to go to school 25 years ago.

This work was supported by the Director, Office of Science, Office of Advanced Scientific Computing Research, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. In addition this project was also supported in part by the Department of Energy under contracts DE-FC02-06ER25753 and DE-FC02-07ER25799. This research used resources of the National Energy Research Scientific Computing Center, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. In addition this research used resources of the Argonne Leadership Computing Facility at Argonne National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02- 06CH11357. This research also used resources of the National Center for Computational Sciences at Oak Ridge National Laboratory, which is supported by the Office of Science of the Department of Energy under Contract DE-AC05-00OR22725. The Texas Advanced Computing Center (TACC) at The University of Texas at Austin provided HPC resources that have contributed to the research results reported within this dissertation. This research was also supported by Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227).

## Chapter 1

## Introduction

As computational power continues to grow at an exponential rate, many large-scale parallel and scientific applications that were once considered too large and expensive are now within reach. Scientists are able to solve many interesting problems that impact all aspects of society, but many scientific simulations still require orders of magnitude more processing power than what is currently available today. In the past, the growth in high end computing needs have always been met by a combination of increased clock rate and increasing processor counts. However, given the recent technology limits[17], clock rates will remain virtually constant and future increases will be achieved almost entirely by increasing the number of processor cores.

This puts us at an interesting cross-roads in parallel computing. Currently the only way to scale the performance of a large parallel machine is to add many more processors and create better networks to connect these processors together. Current petascale supercomputers have hundreds of thousands of processor cores, and as the numbers of processor cores grow, the efficiency of many applications will be adversely affected. Applications that were only designed to scale to thousands of processors will see very poor scalability as we try to run them on the next generation of parallel machines. This will force us to reexamine some of the fundamental ways that we approach designing and using parallel languages and runtime systems.

Communication in its most general form, meaning the movement of data between cores, within cores, and within memory systems, will be the dominant cost in both running time and energy consumption. Thus, it will be increasingly important to avoid unnecessary communication and synchronization, optimize communication primitives and schedule communication to avoid contention and maximize use of bandwidth. The wide variety of processor interconnect mechanisms and topologies further aggravate the problem and necessitate either (1) a platform specific implementation of the communication and synchronization primitives or (2) a system that can automatically tune the communication and synchronization primitives across a wide variety of architectures. In this work we focus on the latter.

A new class of languages, called Partitioned Global Address Space (PGAS) languages, has emerged to aid in the performance and scalability of high performance applications [171].

Rooted in traditional shared memory programming models, these languages expose a global address space that is logically partitioned across the processors. The global address space allows programmers to create sophisticated distributed data structures that aid in building both regular and irregular applications. In order to present the global address space that is similar to traditional shared memory programming, these languages use one-sided communication. In this communication model, a processor is allowed to directly read and write the data of another without interrupting the application on the remote processor. Such semantics have been shown to increase performance by decoupling the synchronization from the data movement that is present in a two-sided communication model.

To aid the productivity of the application writers, many popular parallel languages and libraries, such as Unified Parallel C (UPC)[159] and the Message Passing Interface (MPI)[125], provide collective operations. These collective operations encapsulate common datamovement and inter-processor communication patterns, such as broadcasting an array to all the other processors or having all processors exchange data with every other processor. The abstraction is intended to shift the responsibility of optimizing these common operations away from the application writer, who is probably an application domain expert, into the hands of the implementers of the runtime systems. While this problem has been well studied in the two-sided communication model community, the primary focus of this dissertation will be to understand and improve the performance and productivity benefits of collective operations in PGAS languages (such as UPC, Titanium[96], and Co-Array Fortran[132]) and libraries (such as MPI-2[124]) that rely on one-sided communication. The semantic differences between one- and two-sided communication pose interesting and novel opportunities for tuning collectives.

While both MPI and the PGAS languages were designed for scientific computing, the problem of optimized collective communication has the potential to also impact applications written in the popular MapReduce model [67, 41]. In this programming model, the program is broken into two phases: Map and Reduce. In the Map phase the input data is transformed into a set of key-value pairs. In the Reduce phase all the values with the same keys are aggregated together. In addition, work by Michael Isard et al. [104] on the Dryad system has shown how the MapReduce framework can be extended to handle arbitrary directed acyclic computational graphs. Scheduling the computation and performing the aggregation operations found in these models in a scalable way are similar to the collective operations that we present in this work. Thus we argue that the techniques that we describe in this work are not limited to scientific computing.

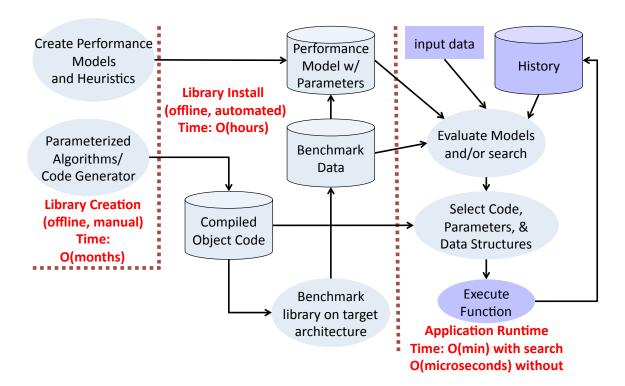

As system vendors work to develop systems with unprecedented levels of concurrency, we are also witness to a large variety of processors and the networks that connect these processors together, which, combined with systems scale, makes it prohibitively expensive to hand-tune any collective implementation for each of these different machines. This necessitates a system that can automatically tune these collectives on a wide variety of processor architectures and networks. Automatic tuning is the method in which a library generates a set of implementations for the same algorithm and selects one of them based on a combination of search (i.e. running the implementation and measuring the performance), performance models, and other heuristics. The technique of automatic tuning has been proven

successful in a wide variety of serial applications such as Dense Linear Algebra[32, 166], Sparse Linear Algebra[99, 164], and spectral methods[85, 144]. Part of this dissertation will explore the design and construction of a system that can automatically tune the collectives. These automatically tuned collectives are incorporated into GASNet[35], the highly portable runtime layer currently used in several PGAS language implementations. To start, we will present a new implementation of GASNet designed for the BlueGene/P architecture, which serves as both a highly scalable platform for our collective tuning work and an interesting and valuable implementation of GASNet in its own right. This work has implications for many parallel language efforts, because GASNet is used in the Berkeley UPC[30] compiler, the GCCUPC compiler [92], Titanium[96], the Rice Co-Array Fortran[132] compiler, Cray Chapel[6] and other experimental projects.

### 1.1 Related Work

Since collective communication is such a critical part of many applications, there have been many papers and projects that have been devoted to optimizing these collectives. They have ranged from projects that provide algorithmic optimizations of these operations [44, 20, 79, 155, 118, 107] to work that focuses on optimizing collectives for very specific networks[145, 117, 14]. Most of these consider collectives in a two-sided communication model. Our main contribution is analyzing and optimizing collectives in a one-sided communication model that is found in many PGAS languages. The algorithms that are found in the literature will be part of our search space. Our work will determine how effective these algorithms are in practice in a one-sided communication model.

Many researchers have studied collective communication in the context of MPI, e.g., [142, 154]. All collective functions in the MPI 2.0 specification are blocking. Hoefler et al [97] discuss the implementation of non-blocking MPI collective operations in LibNBC and evaluate the communication and computation overlapping effects in applications. GASNet collective functions are non-blocking and support 9 different combinations of synchronization modes which enable more aggressive communication overlapping but makes the tuning space much larger. In addition, the GASNet collective implementation tailors the collective operations for one-sided communication model and targets the collective needs for Partitioned Global Address Space languages.

## 1.1.1 Automatically Tuning MPI Collective Communication

Automatic tuning [166, 85, 164] is a widely used technique in high performance computing for accommodating rapidly changing computer architectures, different machine configurations and various application input data. Applying automatic tuning to communication optimization is not a new technique. Brewer[42] discusses various techniques to automatically tune a communication runtime for a variety of platforms. In this work, techniques for tuning the communication alongside the application kernels to present good performance were shown. Our work draws on some of these concepts and helped guide the software architecture for the automatic tuning system, but our work goes well beyond these techniques

by discussing systems at very large scale; our largest experiments are conducted with 32,768 processor cores.

Recent related work has also focused on automatically tuning the collective operations found in MPI. Pješivac-Grbović et al [142] present a system to automatically select the best collective implementation by a decision algorithm based on quadtree data structure. The quadtree is used during application run-time to pick the best algorithm for a given collective and to minimize the time needed for search. Star-MPI [80] also uses online autotuning to dynamically tune collective operations for different application workloads.

Our automatic tuning system will examine a similar set of parameters as these other projects (such as processor count, message size, machine latency, machine bandwidth, etc.), however the addition of the looser synchronization modes and the impact of overlapping communication and computation through collectives will be novel additions to the automatic tuner. In addition, our collective library targets programming models that use one-sided communication which is different than the message passing model examined by previous work. The mechanisms, such as quad-trees, that previous work has shown have influenced the software architecture for the automatic tuner. Our system is also the first portable high performance implementations of the collectives for PGAS languages.

### 1.2 Contributions

In this dissertation we will show how programming models that use one-sided communication provide unique opportunities for optimizing collective communication. Since PGAS languages, which are the main set of languages that use one-sided communication, are designed with productivity and performance portability in mind, any optimized collective library that is designed must be able to adapt to whatever environment the user desires. We will also show that an automatic tuning system that will chose the best algorithms of these collectives on a wide variety of processors and interconnects can be built.

This dissertation makes the following contributions to the field:

- We outline the difference between one- and two-sided communication and show how it impacts the design and implementation of the collective communication library.

- We describe our implementation of the one-sided GASNet communication layer for the IBM BlueGene systems. We use this to demonstrates scalability of the GASNet interface and UPC language on top of it to tens of thousands of processors.

- We showcase the need for automatic tuning of collectives by studying a large set of algorithms for the major collective communication operations on both shared and distributed memory platforms and show how a few example applications can benefit from optimized collective communication. We target both large clusters with different network and processor configurations as well as modern multicore systems.

- Our distributed memory performance results demonstrate that this new collective communication library, which selects from a large set of possible algorithms, achieves

up to a 65% improvement in performance over MPI for a one-to-many collective and up to a 69% improvement in performance over MPI for a many-to-many collective.

- Results show that tuning collectives for shared memory decrease the latency for a Barrier synchronization by two orders of magnitude compared to what is found in traditional libraries. The results also show that by further tuning the collective communication for these platforms we can realize another 70% improvement in overall latency.

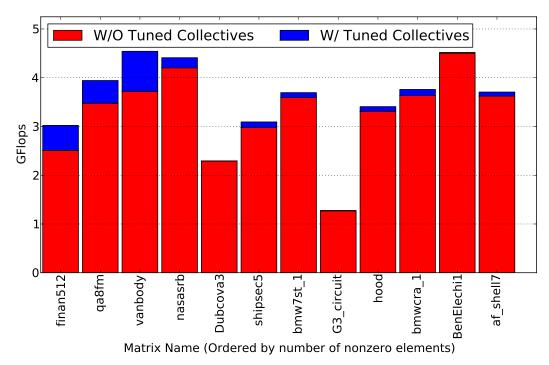

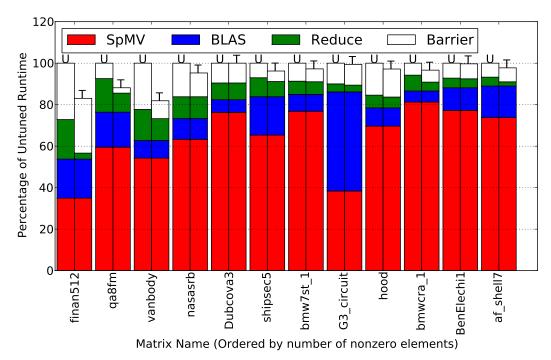

- We also demonstrate how the collectives can improve the performance of higher level algorithms largely due to better overlap with computation to achieve a 46% improvement in performance over MPI for a 3D FFT, a communication bound benchmark, on 1024 cores of the Cray XT4. The tuned collectives also show a 1.86× improvement in the performance of Parallel DGEMM on 400 cores of the Cray XT4 when compared against the PBLAS [52] and comparable performance for Dense Cholesky factorization on 2k cores of the IBM BlueGene/P. By tuning the collectives in Sparse Conjugate Gradient on shared memory platforms we see a 22% improvement in overall application performance when comparing against the untuned collectives.

- We construct performance models for these various algorithms using the LogGP framework to better understand performance tradeoffs in the different algorithms and to identify performance upper bounds that can serve as useful limits when tuning.

- We describe a software architecture that can *automatically tune* these operations for a variety of processor and network types and show how performance models can be used to prune the search space and aid in the automatic tuning process. In many cases the performance model picks the best algorithm, negating the need for search. However when search is needed, the performance model can guide the search and cut down the time needed for a search.

- We propose a novel interface to the collective communication library that is designed for Partitioned Global Address Space Languages. The interface allows users to specify the data that the collectives act upon rather than the traditional methods which rely on the user specifying exactly which threads are involved in the collective.

- We present the first automatically tuned collective library available for Partitioned Global Address Space Languages and use it in some of the largest scale runs of any PGAS programs to date.

## 1.3 Outline

The discussion starts with how modern systems are organized into compute nodes and how these nodes are connected together to form a large parallel system in Chapter 2. The design of these systems reveals the different mechanisms for communicating between cores and hence a non-uniform access time when data is located on two different nodes. In Chapter 3 we show how the Partitioned Global Address Space languages address this and particularly how the one-sided communication model found in these languages aims to aid productivity and performance. We also detail how a one-sided communication library can be written on top of modern network hardware taking advantage of a variety of the available features. As a case study we use the IBM BlueGene/P.

Having built up a one-sided messaging framework we then turn our attention to the collective communication operations, operations designed to perform globally coordinated communication. We start by introducing the different collectives in Chapter 4 and highlight how the collectives found in Partitioned Global Address Space languages differ from MPI collectives in subtle but important ways. Chapters 5 and 6 go into further detail about how these different collective operations can be implemented and present benchmarks showing performance on our experimental platforms. Along with discussing the various algorithms we also show how performance models can be constructed to better understand the performance and aid in choosing the optimal algorithms.

While collective communication is normally targeted at distributed memory systems, collective communication operations can also be useful on shared memory systems built from one or more multicore chips. These arise either within the nodes of a larger distributed memory platform or on their own. The collective operations often stress the limits of the shared memory structures on these systems. As core counts continue to grow at a rapid pace, the number of cores within a chip and within a multicore system will soon be large enough where naïve collective algorithms realize poor scalability. We show how tuning a collectives library can aid in performance for these platforms in Chapter 7.

One of the continuing themes throughout the dissertation is to show the wide variety of algorithms (and parameters) that are available to perform a particular collective operation. In Chapter 8 we show the software architecture that can automatically tune these operations for a wide variety of platforms. We also show how the performance models can play a critical role to reduce the overheads associated with tuning without sacrificing the quality of the resultant algorithms.

In many applications, it is useful to perform collective operations over a subset of the threads rather than all of them. We call this subset a *team*. In Chapter 9 we show two different ways to construct teams. The first is a traditional method in which the user explicitly specifies the members. The second allows the user to specify only the data that is involved in the collective and it is up to the runtime system to automatically construct the teams. We present how such an interface would work and can be integrated into the language runtime systems.

We conclude the dissertation in Chapter 10 with a summary of the points raised and possible directions for future work.

## Chapter 2

## Experimental Platforms

Over the past several years we have witnessed to a tremendous increase in computational power, more than three orders of magnitude in ten years on the fastest machines in the world. In order to facilitate scientific discovery, computer engineers continually deliver machines that can deliver significantly more computational power, and until very recently, these increases in computational power have been delivered by increasing the clock rates of the processors and creating novel hardware mechanisms that allow serial applications to run faster. However, due to the technical challenges associated with constantly delivering computational improvements through this method [17], the performance improvements are now being delivered by connecting more processors together to create systems that have 10s of thousands and 100s of thousands of processors and relying on parallelism (and hence the programmer) to deliver the performance. Modern high end systems are built as a hierarchy in which different processors communicate through an interconnection network. This interconnection network is built out of a combination of switches that allow all the processors to be connected in some topology, typically some form of mesh or tree. There are many points in the design space on how to connect the switches and busses together [60]. One of the central aims of this dissertation is to analyze how to effectively utilize these different interconnection networks and build a software package that can automatically tune itself to the interconnection network of the platform it is installed on.

To organize the discussion we focus on four different large scale platforms: the Cray XT5 at Oak Ridge National Labs (Jaguar)[105], the IBM BlueGene/P at Argonne National Labs (Intrepid)[103], the Sun Constellation System at the Texas Advanced Computing Center (Ranger)[84], and the Cray XT4 at the National Energy Research Scientific Computing Center (Franklin)[83]. As of November 2009, these machines are respectively ranked  $1^{st}$ ,  $8^{th}$ ,  $9^{th}$ , and  $15^{th}$  on the Top500 list[5], the list of the 500 most powerful computers in the world. These platforms will also be the test beds for our experimental work. Throughout the rest of this chapter we will discuss some of the features that are common to these interconnection networks and how they differ.

The rest of this chapter is organized from the smallest processing core out to the large data-center switches that connect all the various nodes together.

### 2.1 Processor Cores

At the center of the systems lies a set of processing cores. These are hardware units that are capable of executing a serial sequence of instructions and update the contents of memory through a connection to the memory system [139]. A core also typically contains some of its own fast memory known as a *cache*. Through advances in modern silicon technology, a few of these processing cores can be placed on the same physical die termed *multicore* processors. Currently, the preferred method of communicating data amongst the various cores is to have them update and read a *shared* address space so that updates to one location in memory are visible to the other cores. Because the per-core caches may also hold copies of data, a coherence protocol is used to ensure that the cached copies are consistent.

This raises issues of when data is safe to read and write. There has been a wide body of literature [60, 169] analyzing how a memory system can be built including special atomic instructions, instructions with multiple memory accesses whose effects are guaranteed to be run to completion if the instruction is started. For example, a test and set operation involves read, a test to ensure that the variable has not been set, and then a write operation to set it. Atomicity ensures that no other core can access the variable during this sequence of operations. With these special mechanisms synchronization constructs are built to ensure that the data written to the shared memory space is safely written and read. In this dissertation we focus more on how these cores communicate efficiently with each other rather than focusing how to leverage the best performance out of these cores. The latter is the subject of much other related work [138].

### 2.2 Nodes

A node is a collection of multicore processors, the associated memory and the interface to the network. For all our platforms, all the cores within a node have access to the entire memory space on that node through a cache coherence shared memory system. In this section we go into greater depth of the different node architectures of our platforms as well as an important common feature to all of them that we will leverage for our communication system, Remote Direct Memory Access (RDMA).

### 2.2.1 Node Architectures

Each of the different platforms has a different node architecture. They have many similarities amongst them but they have key differences that make them interesting for our analysis. The following architectural discussion highlights some of the salient features. We focus on those features that are directly relevant to the shared memory and communication issues that are relevant to collective communication.

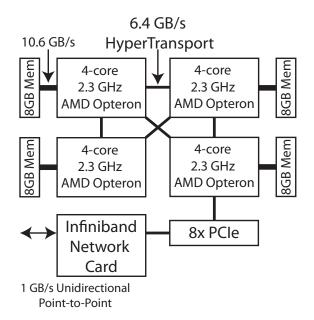

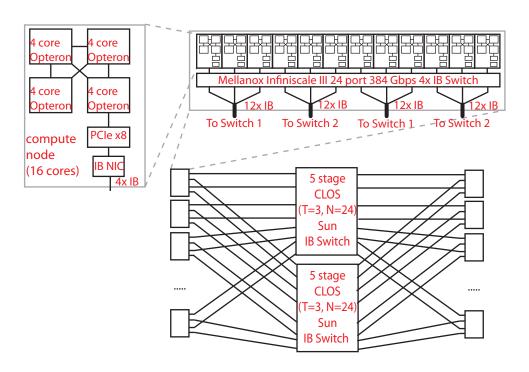

Figure 2.1: Sun Constellation Node Architecture

#### Sun Constellation

We first start our analysis with a "traditional" cluster node. The work by Culler et al. [59] and Sterling et al. [152] among others showed how to connect commodity machines through a network to produce a system that can deliver significant performance through commodity parts. As our representative example for this class of systems we choose the Sun Constellation system. The compute node of the Sun Constellation system is a SunBlade x6420 [7]. A simple block diagram of this is shown in Figure 2.1. The node contains 4 AMD quad-core Opteron (Barcelona) chips for a total of 16 cores. Each of the sockets are connected together through AMD's Hypertransport interface capable of a bandwidth of 6.4GB/s between the chips. The sockets are connected to their own memory at a much larger 10.6 GB/s. Thus, even though the system appears to have a uniform shared memory, there is a notion of locality. Accesses to memory attached to the socket will be about twice as fast as accesses to another socket's memory. Each of the sockets has three Hypertransport links. One of the sockets must dedicate one of these links for the network interface and thus two out of the four sockets are connected fully connected and the other two are not directly connected to each other.

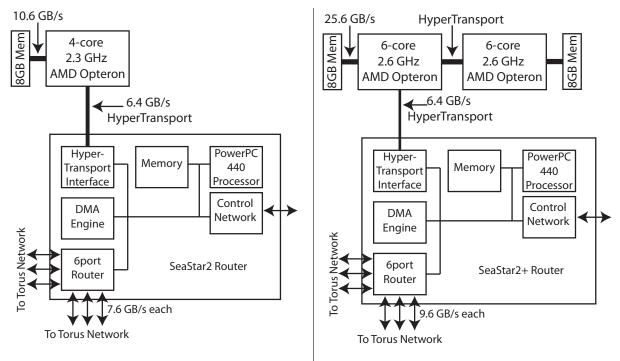

### Cray XT

The next platform we analyze is the Cray XT4[9]. A block diagram of the node is shown in Figure 2.2. The compute node of the Cray XT4 has a single quad-core 2.3 GHz AMD Opteron (Budapest). Attached to the processors is 8 GB of DRAM connected over a link that delivers 10.6 GB/s. In addition the processor is directly attached to the SeaStar2

Figure 2.2: Cray XT4 Node Architecture

Figure 2.3: Cray XT5 Node Architecture

routing chip over a 6.4GB/s AMD Hypertransport link. This routing chip has 6 links to the rest of the network to connect the node to the rest of the system in a 3D-torus network. Each of the 6 links transport data in a different direction in the 3-dimensional space. We discuss the 3D-torus and how the different network chips are connected together in much greater depth in Section 2.3. Unlike "traditional" cluster architectures the nodes that compose the Cray XT4 system are not commodity components. It has been customized so that the network interface connects directly into the processor rather than through a normal I/O bus that most systems have. This system also only has one socket and thus all the cores within the node are equidistant from each other unlike the Sun Constellation.

The Cray XT5 is the next generation version of the Cray XT4. The compute nodes of the Cray XT5 (shown in Figure 2.3) have two hex-core AMD Opteron processors (Istanbul) running at 2.6 GHz leading to a total of 12 cores per node. One of the processors is directly connected to a SeaStar2+ routing chip (an updated version of the SeaStar2).

### IBM BlueGene/P

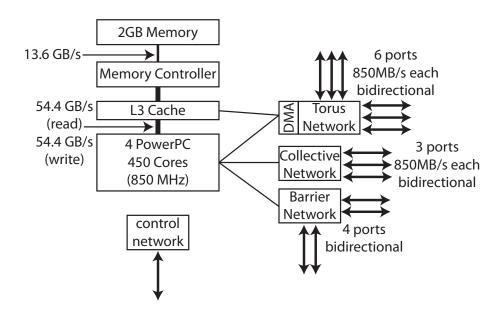

The last platform that we analyze is the IBM BlueGene/P[150]. The BlueGene/P is a custom design from IBM. It uses 4 IBM PowerPC 450 cores running at 850MHz connected to another 3D torus network. The four cores are connected to the L3 through eight 13.6 GB/s unidirectional links for a total of 54.4 GB/s in each direction. The L3 cache is connected into the memory at 13.6 GB/s. Figure 2.4 shows a high-level block diagram of the architecture.

Unlike the other platforms though the network is much more tightly integrated with the processing elements and node elements. The torus network interface, for example, is able

Figure 2.4: IBM BlueGene/P Node Architecture

to talk directly to the L3 cache rather than having to go through a Hypertransport like device. This platform also has a custom collective network and barrier network to support hardware collectives.

### 2.2.2 Remote Direct Memory Access

One of the features common to all the systems is a Direct Memory Access (DMA) device that is attached directly to the network card. This is hardware that allows the network interfaces to directly read and write data to the memory (or the L3 cache in the case of the BlueGene/P) without having the processors actively manage communications that are in progress. In addition these devices also allow remote nodes to directly read or write the memory hence we call this feature Remote Direct Memory access or (RDMA). As we will show this is a natural fit to the one-sided programming model that will be discussed in greater depth in Chapter 3.

In order to allow such mechanisms to properly work, the operating system pages that are being written or read will need to be resident in the memory. Related work [26] has developed a system that can manage these resources to enable efficient communication with RDMA. Our related work [128, 28] has also shown how these features can be utilized to realize significant performance advantages. We go into much greater depth about these concepts and how they relate to the collective communication in Sections 5.1.5 and 6.3.

### 2.3 Interconnection Networks

The next step in the hierarchy is to analyze the network topologies that connect the different nodes together. In an ideal environment all the nodes are directly connected to each other to minimize the time spent transferring the data. However, this ideal case would require that each node have N hardware connection endpoints (where N is the total number of nodes) leading to a total of  $N^2$  connections amongst them in the network. For any significant value of N this approach quickly becomes infeasible. Thus, to minimize the amount of network resources, data is transferred by routing it over many links before getting to the final destination, which adds a notion of distance between nodes. We define the distance metric here as the number of links between two communicating nodes. Our experimental platforms present two very different approaches to constructing network topologies: a CLOS network (or Fat Tree), which is a network built hierarchically out of switches; and a Torus network in which the nodes are laid out in a mesh. In the latter, each node is directly connected to its peers.

In all the networks we analyze, data is sent between the nodes through the network by quantizing the transfers into units called *packets*. These packets are then switched and routed through the network until they reach the final destination. One of the keys to a packet switched network is that the nodes do not need to have knowledge of how to send the data. The network contains all of the intelligence to properly route the packets. In addition, since the data is quantized into different packets, there is no need for all the packets between a source and destination node to take the same path through the network. In a torus network, for example, there are many paths between two nodes that have the same Manhattan distance and hence any one of these routes is equally valid. There have been many studies and related work[140] analyzing the performance and optimal routing techniques for these packets. While packet switched networks are the most common today, there are other network routing technologies, such as wormhole routing [16], however these are beyond the scope of this dissertation.

### 2.3.1 CLOS Networks

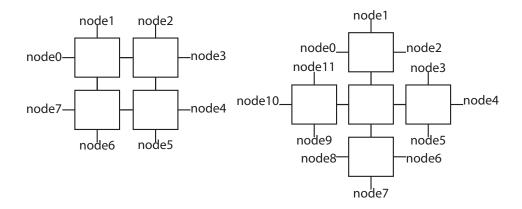

At the core of many modern interconnection networks is a *switch*. A switch is a device that will look at the destination address of a packet and route it to the appropriate output port. In our work we consider the switch as a black box that can route data from any port to any other port on the switch. These switches can be built up in a hierarchy. However the more switches that are added between the source and destination nodes, the higher the latency between them.

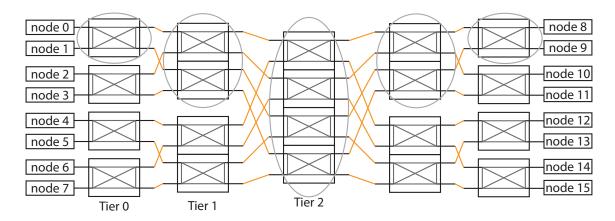

Figure 2.5 shows two example switch configurations with 4-port switches. In the example on the left, two out of the four ports are connected to other switches. Thus to send a packet from node 0 to node 2 the data will need to traverse through two switches. Another possible way to build up the switches in a hierarchy is to arrange them so that for each P port switch P-1 ports are connected to different nodes and the last one is connected to a higher level switch (as shown in the right of Figure 2.5). At the higher level we have one

Figure 2.5: Example Hierarchies with 4 port switches

Figure 2.6: Example 16-node 5-stage CLOS Network

switch that connects all the other lower level switches. This approach allows many more nodes to be connected into the network. However, to communicate with a node that is not co-located on the same switch it will take an additional two hops adding to the latency of the communication. Further aggravating the problem, if the link to the switch has bandwidth B then all the nodes that are co-located on the switch will have to share the bandwidth to the central switch and thus effectively delivering a bandwidth of B/3. For large switching networks this can be a problem since it dramatically reduces the network performance.

To circumvent this bottleneck Charles Clos demonstrated how to connect many P port switches to form a larger switched network [54]. The key observation is that by adding redundant switches in the middle of the network one can get better end-to-end bandwidth. The switching network is broken up into T tiers. At tier 0 half of the ports of the switches are connected to the nodes and the other half are connected to the internal switching network. They are connected in a butterfly pattern similar to the one used in the Fast Fourier Transform (FFT) [58]. We can reclassify ports of the switch as "inputs" and "outputs."

For a four port switch there are 2 inputs and 2 outputs. At each level the switches are grouped into sets of  $(P/2)^t$  switches where P is the number of ports on the switch and t is the tier number. For a fully connected four port switch network there are 16 nodes with 8 switches at the tier 0 level (shown in Figure 2.6). At tier 1 there are 8 switches organized in groups of 2 and at the final level there are 4 switches in a group of 4. To simplify the explanation we analyze the first group of switches at each tier and look at their connectivity. The extension to the rest of the switching network is straightforward. The total number of groups that connect to a higher level can be defined as P/2. For a group at tier t there are  $(P/2)^{(t+1)}$  inputs and outputs. The  $i^{th}$  output from group g at tier t is connected to the  $((P/2) \times i + g)^{th}$  input at tier t + 1. In the example in Figure 2.6 to send a packet from node 0 to node 4 the packet will traverse 5 stages in the switching network. However, to send a message from node 0 to node 3 it will only need to traverse 3 stages since the switches at tier 1 will not forward the data. This gives the rise to a notion of locality in such a network. Nodes can be "close" (few network hops) or "far" (more network hops).

Nodes are connected to the switching network with one link. However, notice that the number of links that connect adjacent tiers double. There are twice as many links that connect groups in tier 0 to tier 1 than nodes to the switching network. Hence, this network has the desirable property that there is a uniform bandwidth between any pair of nodes, also termed a "Fat Tree." Thus different groups of nodes can communicate with each other without interfering on or being interfered by traffic amongst other nodes hence alleviating the problem with our original switching networks. The Fat Tree configuration however comes at a cost of many more switches.

A theoretical property that is important for analyzing networks is the bisection bandwidth of the network. This defined as the sum of the bandwidth across the minimum number of links that need to be cut in order to separate the network into two disjoint parts of equal size. This is an approximation for how efficiently the network can handle communication patterns in which all the nodes talk to all the other nodes. Chapter 6 goes into much greater depth on these communication patterns and their applications. In our example with 4 port switches, 8 links need to be cut to separate the network into two equal halves of 8 nodes each. In general for a full Fat Tree there are as many links to the root switching group as the number of input nodes. Thus Fat Trees are said to have full-bisection bandwidth. As we will shortly show, this is not always the case.

In practice the switches have a lot more ports. On the Sun Constellation switches, each switching chip has 24 ports. Figure 2.7 shows how a real Fat Tree network is implemented as hierarchy of units. At the periphery 12 nodes are connected to the input side of the network. This group of 12 nodes and the associated switch are then connected into two 3 tier (5 stages) CLOS network with 24 port switches. Thus there are a total of seven stages in the network: the 5-stage main switch plus the switches at the periphery for input and output. The second 5-stage switch is provided for extra bandwidth and redundancy. The system has a total 3,936 compute nodes with 16 cores each for a total of 15,744 cores.

Figure 2.7: Sun Constellation System Architecture

Figure 2.8: Example 8x8 2D torus Network

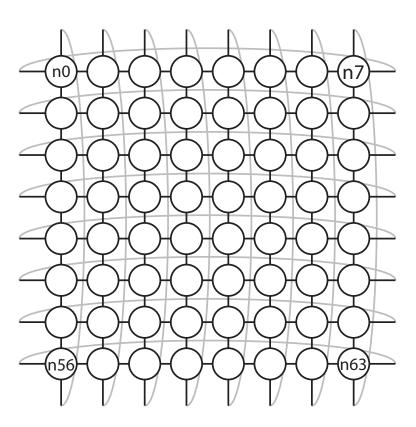

#### 2.3.2 Torus Networks

One of the main drawbacks with full-CLOS network is the large number of switches that are needed to provide the connectivity. Thus in the second network model, the network interface cards are responsible for both injecting and receiving packets into the network as well as routing the packets within the network. One way to build such a system is to logically lay the processors out in a grid and then connect neighboring processors together to create a mesh. To further increase the network bandwidth and decrease the distances between the corners, the ends of each of the dimensions of the Torus network wrap around. Figure 2.8 shows an example of a set of processors laid out in a torus network. The torus can be generalized to an arbitrary rectangular prism. For a d dimensional torus with an edge of the prism having k nodes, there are a total of  $k^d$  nodes that must be connected. In order to send a message from one corner of the torus to the other, there are many possible routes that have the same Manhattan distance and thus choosing the best route on the torus requires the network cards at each of the nodes to intelligently route the signals. Three of our experimental platforms (the IBM BlueGene/P, the Cray XT4 and the Cray XT5) use this network topology. Logically the neighbors within the torus are directly connected together, however, in a real deployment physical distances between groups of nodes prevent the symmetric network performance between nodes co-located on the same rack and nodes located on different racks. Thus even though these nodes might logically be neighbors there is still a notion of distance that must be taken into account.

The bisection bandwidth of the torus networks however tends to be much smaller than Fat Tree networks with the same node counts. For a d dimensional torus network with k nodes per dimension  $2 \times k^{d-1}$  links need to be cut to separate the network into two halves. Thus the bisection bandwidth is an order of magnitude smaller than the total number of nodes. This has important implications about properly mapping applications to the network to ensure that the communication is more localized.

Another more subtle downside to the torus networks are that they require all the points in the torus network to be fully populated with nodes (or at least active network cards) in order to properly handle the routing and deliver the advertised performance. Whereas in a full-CLOS network, since the network card are not relied upon to handle the routing, the system does not have to be fully populated to realize the full performance.

### 2.4 Summary

In summary, our experimental platforms have a lot of similarities and differences that will make them a good basis for understanding our parallel communication primitives for the rest of the dissertation. Table 2.1 provides a summary of the salient information that will be important for the rest of the dissertation. We will focus on how common communication patterns (namely collective communication) can be optimized for various networks. The platforms have different characteristics that affect the performance, which make them interesting for the analysis. The techniques we describe, however, are will be applicable to a broad range of platforms and not limited to these platforms.

|                   | Cray       | Cray       | IBM        | Sun           |

|-------------------|------------|------------|------------|---------------|

|                   | XT4        | XT5        | BlueGene/P | Constellation |

| Machine Name      | Franklin   | Jaguar     | Intrepid   | Ranger        |

| Machine Location  | NERSC      | ORNL       | ALCF       | TACC          |

| Top500 Rank       | 15         | 1          | 8          | 9             |

| (November 2009)   |            |            |            |               |

| Processor Type    | AMD        | AMD        | IBM        | AMD           |

|                   | Opteron    | Opteron    | PowerPC    | Opteron       |

|                   | (Budapest) | (Istanbul) | 450        | (Barcelona)   |

| Clock Rate (GHz)  | 2.3        | 2.6        | 0.85       | 2.3           |

| # Cores/Processor | 4          | 6          | 4          | 4             |

| # Processors/Node | 1          | 2          | 1          | 4             |

| # Cores / Node    | 4          | 12         | 4          | 16            |

| Peak Perf. /Node  | 36.8       | 124.8      | 13.6       | 147.2         |

| (GFlop/sec) †     |            |            |            |               |

| Memory BW         | 10.6       | 25.6       | 13.6       | 10.6          |

| (GB/s)            |            |            |            |               |

| # Nodes           | 9,572      | 18,688     | 40,960     | 3,936         |

| Network Topology  | 3D Torus   | 3D Torus   | 3D Torus   | 7-stage CLOS  |

| Network BW        | 7.6        | 9.6        | 0.85       | 1             |

| (GB/s)            | (2-way)    | (2-way)    | (2-way)    | (1-way)       |

| One-way Network   | 6.2        | 5.2        | 1.5        | 2.3           |

| Latency $(\mu s)$ |            |            |            |               |

Table 2.1: Experimental Platforms ( $^{\dagger}$ All of our platforms support a peak of 4 double-precision floating point operations per cycle.)

## Chapter 3

## One-Sided Communication Models

As described in Chapter 2, modern high end systems are built as a hierarchy of multicore chips that are combined into shared memory nodes, and the nodes are further combined into large networks that form a distributed memory system. Thus, when implementing programming models on such systems and optimizing communication patterns, one must considered both shared and distributed memory in the underlying system. A the programming level, one can also consider multiple forms of communication, including reading and writing to shared variables or explicitly sending messages. In this chapter we describe some of these programming language issues and describe the main focus of this thesis: Partitioned Global Address Space languages. We then describe the one-sided communication model underlying these languages and a our own implementation of the GASNet one-sided model for the IBM BlueGene/P architecture. We end with some performance comparisons between our one-sided communication and more traditional two-sided in terms of their performance characteristics, revealing some of the performance advantages of the one-sided model.

## 3.1 Partitioned Global Address Space Languages

Two distinct parallel programming models are commonly found on a variety of systems today: (1) message passing and (2) shared memory. Message passing is a shared-nothing programming model. In order for different processor cores to communicate with each other they have to explicitly send messages amongst themselves. One of the major criticisms of a message passing model is that both sides have to agree on when messages are being sent and received and thus, typically, all communication has to be known ahead of time. The ubiquity of MPI (the Message Passing Interface) [125] demonstrates that this is indeed a usable and portable programming model that can tackle a wide range of systems. However, distributed data structures, such as distributed queues, are very difficult to encode since both sides have to agree upon when an enqueue of an event, for example, will occur. For highly asynchronous or irregular applications such a restriction can be very inconvenient.

At the other end of the spectrum is shared memory programming. In this approach the entire address space is shared and thus any thread that is part of that address space will have the ability to read and write the data of any other thread. These programming models

are typically found within nodes of a larger system rather than across large systems. Since all the memory is shared it is possible to build distributed data structures however one has to take great care to ensure that there are no race conditions when two threads modify a common memory location. In addition, to keep the illusion of shared memory to the end programmer, hardware has to create complicated mechanisms, such as cache coherency systems, that are difficult to scale to large levels of parallelism. Thus, even though both approaches have gained popularity in the community, they each have limitations that make them far from an ideal programming model.

Recently a new class of languages have emerged with aims of bridging these two distinct styles of parallel programming. The primary aim of these new languages, called Partitioned Global Address Space (PGAS)[171] languages, is to provide a single programming model for shared memory and distributed memory platforms (and combinations of them) by exposing a globally shared address space to the user. These languages also explicitly expose memory affinity and non-uniform memory access to the end user by having each thread be logically associated with a part of the shared global address space. The shared address space allows the processors to directly read and write remote data without notifying the application running on the remote processor through language level one-sided operations (i.e. put and get versus send and receive). Similar to traditional shared memory programming, the user is responsible for handling any race conditions that might arise. Unlike efforts that combine shared-memory and message passing together, such as OpenMP and MPI, the PGAS languages provide one programming model across the system rather than relying on two distinct programming models that must be melded together. Thus the PGAS languages aim to deliver the same performance with a uniform programming model across all the threads. Many related projects have shown the performance and productivity advantages of such an approach [47, 49, 64].

Since the languages explicitly expose the non-uniform nature of memory access times to the memory of different processors, operations to local data (i.e. the portion of the address space that a particular processor has affinity to) will tend to be much faster than operations on remote data (i.e. any part of the shared data space that a processor does not have affinity to). Thus, unlike traditional shared memory programming, the languages necessitate global data re-localization operations in order to improve performance which will be served by the collective operations. One of the primary focuses of the dissertation will be to analyze the interaction between these collective operations and the one-sided communication model. Some of these interactions are unique to PGAS languages and do not arise in two-sided parallel programming models like MPI.

### 3.1.1 UPC

There are many different variations of PGAS languages that each have different design goals and programming styles but all of them fundamentally share the idea of a global address space in which a thread has affinity to part of that address space. To better understand what these languages offer we explore one of the more popular PGAS languages, Unified Parallel C (UPC). UPC is the PGAS dialect of ISO C99 [102] and thus UPC is a

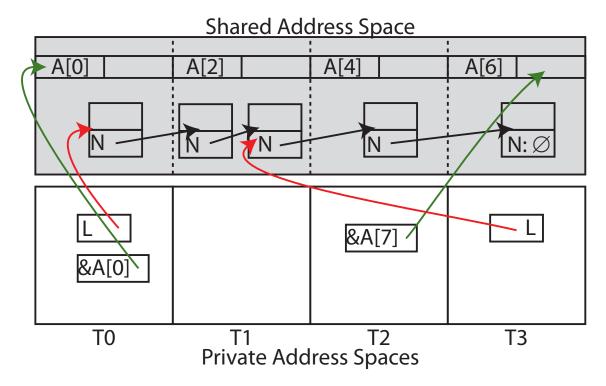

Figure 3.1: UPC Pointer Example

complete superset of C; any valid C program is a valid UPC program. To allow data to be read or accessed remotely UPC introduces the **shared** type qualifier into the language. Only variables declared with the **shared** qualifier will be part of the shared address space and all other variables are part of the private address space. By explicitly specifying the sharing UPC avoids the problem of inadvertant race conditions on data that the threads are not expecting to be altered by other threads.

UPC also provides C-style pointers to the shared address space that allow programmers to build distributed data structures. The UPC pointer also supports pointer arithmetic and dereferencing of variables that have affinity to different threads. In Figure 3.1 we show an example of a few of the different types of pointers in UPC. We can declare a linked list node with the following type:

```

typedef struct link_list_elem_{

int value;

shared struct link_list_elem_ *N;

} link_list_elem_t;

```

The linked list elements can then be instantiated and connected together to form the example shown in the figure. Notice that all the nodes do not need to have the same number of elements. We can declare pointers in the private address space to the shared linked list that can point to arbitrary locations in the list as follows:

```

shared link_list_elem_t *L;

```

In addition to using pure shared pointers UPC also allows the user to declare distributed arrays. To declare a shared array spread across 4 processors such that each processor has affinity to a set of two contiguous elements we use the following declaration:

#### shared int [2] A[2\*THREADS];