## UC Berkeley UC Berkeley Previously Published Works

## Title

Novel nanocomposite-superlattices for low energy and high stability nanoscale phasechange memory.

Permalink https://escholarship.org/uc/item/885828d7

**Journal** Nature Communications, 15(1)

## Authors

Wu, Xiangjin Khan, Asir Lee, Hengyuan <u>et al.</u>

**Publication Date**

2024-01-22

## DOI

10.1038/s41467-023-42792-4

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <u>https://creativecommons.org/licenses/by/4.0/</u>

Peer reviewed

Article

# Novel nanocomposite-superlattices for low energy and high stability nanoscale phasechange memory

Received: 3 October 2023

Accepted: 20 October 2023

Published online: 22 January 2024

Check for updates

Xiangjin Wu<sup>1,10</sup>, Asir Intisar Khan <sup>1,10</sup>, Hengyuan Lee<sup>2</sup>, Chen-Feng Hsu <sup>2</sup>, Huairuo Zhang <sup>3,4</sup>, Heshan Yu<sup>5,6</sup>, Neel Roy<sup>1</sup>, Albert V. Davydov <sup>3</sup>, Ichiro Takeuchi <sup>5</sup>, Xinyu Bao<sup>7</sup>, H.-S. Philip Wong<sup>1</sup> & Eric Pop <sup>1,8,9</sup>

Data-centric applications are pushing the limits of energy-efficiency in today's computing systems, including those based on phase-change memory (PCM). This technology must achieve low-power and stable operation at nanoscale dimensions to succeed in high-density memory arrays. Here we use a novel combination of phase-change material superlattices and nanocomposites (based on  $Ge_4Sb_6Te_7$ ), to achieve record-low power density  $\approx 5 \text{ MW/cm}^2$  and  $\approx 0.7$  V switching voltage (compatible with modern logic processors) in PCM devices with the smallest dimensions to date ( $\approx 40$  nm) for a superlattice technology on a CMOS-compatible substrate. These devices also simulta*neously* exhibit low resistance drift with 8 resistance states, good endurance ( $\approx 2 \times 10^8$  cycles), and fast switching ( $\approx 40$  ns). The efficient switching is enabled by strong heat confinement within the superlattice materials and the nanoscale device dimensions. The microstructural properties of the Ge<sub>4</sub>Sb<sub>6</sub>Te<sub>7</sub> nanocomposite and its high crystallization temperature ensure the fast-switching speed and stability in our superlattice PCM devices. These results re-establish PCM technology as one of the frontrunners for energyefficient data storage and computing.

The rapid growth of big-data, high performance computing, and numerous data-centric artificial intelligence applications have inspired continued demand for robust and low-power nonvolatile memory<sup>1-5</sup>. Among emerging technologies, phase-change memory (PCM) based on chalcogenides could bridge the performance gap between existing data storage solutions such as flash (nonvolatile, but relatively slow) and dynamic random-access memory (fast, but volatile)<sup>6-8</sup>. In addition, PCM also benefits from large memory window (>100× ratio between resistance states) and multilevel operation, which are useful for brain-inspired computing applications<sup>4,9-12</sup>.

PCM based on traditional phase-change materials like Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST225) is known to suffer from high switching power and resistance drift, i.e., gradual change of its resistance states over time<sup>13,14</sup>. Recent progress on PCM devices has focused on lowering their reset energy<sup>15-19</sup>, however the on/off ratio<sup>17,19</sup>, endurance<sup>17-19</sup>, uniformity and process compatibility<sup>15,16</sup> need improvement. Some efforts<sup>20-22</sup> have also increased the PCM speed, but at the expense of reduced thermal stability<sup>20</sup>, larger set voltage<sup>20,21</sup> or larger reset current<sup>22</sup>. In recent years, phase change materials arranged in superlattice (SL) stacks with alternating layers of GeTe/Sb<sub>2</sub>Te<sub>3</sub><sup>12,23-27</sup>, TiTe<sub>2</sub>/Sb<sub>2</sub>Te<sub>3</sub><sup>10,28</sup>, GeSb<sub>2</sub>Te<sub>4</sub>/

<sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA, USA. <sup>2</sup>Corporate Research, Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, Taiwan. <sup>3</sup>Materials Science and Engineering Division, National Institute of Standards and Technology, Gaithersburg, MD, USA. <sup>4</sup>Theiss Research, Inc., La Jolla, CA, USA. <sup>5</sup>Department of Materials Science and Engineering, University of Maryland, College Park, MD, USA. <sup>6</sup>School of Microelectronics, Tianjin University, Tianjin, China. <sup>7</sup>Corporate Research, Taiwan Semiconductor Manufacturing Company (TSMC), San Jose, CA, USA. <sup>8</sup>Department of Materials Science & Engineering, Stanford University, Stanford, CA, USA. <sup>9</sup>Precourt Institute for Energy, Stanford University, Stanford, CA, USA. <sup>10</sup>These authors contributed equally: Xiangjin Wu, Asir Intisar Khan. eenail: epop@stanford.edu Sb<sub>2</sub>Te<sub>3</sub><sup>29</sup>, and Sb<sub>2</sub>Te<sub>3</sub>/GST225<sup>30,31</sup> have enabled lower switching current and resistance drift of PCM, due to structural and electro-thermal confinement caused by van der Waals (vdW) interfaces within such superlattices<sup>25,32-34</sup>. However, to-date SL materials have not been optimized for the well-known trade-off between speed and stability (especially at higher temperatures) of PCM devices<sup>9,20,35</sup>, while SL memory cells have not yet been demonstrated with nanoscale dimensions. In other words, can SL-based PCMs maintain advantages as they approach the limits of (size) scaling, or is their performance curtailed by fundamental trade-offs?

To probe these limits, here we demonstrate  $\approx 40$  nm nanoscale PCM devices with the first superlattices based on  $Ge_4Sb_6Te_7$  (GST467), a new nanocomposite<sup>36</sup> with higher crystallization and lower melting temperature than traditional PCM materials, consisting of epitaxial SbTe nanoclusters within a Ge-Sb-Te matrix<sup>37</sup>. These SbTe nanoclusters serve as a precursor for crystallization, also increasing the switching speed of GST467. Thus, by introducing GST467 into our superlattice PCM devices we simultaneously achieve record-low  $\approx$ 5 MW/cm<sup>2</sup> switching power density, ultra-low  $\approx 0.7$  V switching voltage, sub-1.5 pl switching energy, fast switching speed ( $\approx 40$  ns), low resistance drift with 8 resistance states and high endurance ( $\approx 2 \times 10^8$ cycles). The efficient operation is enabled by strong heat confinement within the superlattice interfaces and nanoscale dimensions, while the unique microstructural properties of GST467 and its higher crystallization temperature facilitate the simultaneously faster switching speed and improved stability, going beyond the fundamental trade-off for PCM technology. From a materials perspective, this also represents the first time that the combination of bottom-up natural interfaces (in the nanocomposite) and top-down superlattice interfaces are simultaneously implemented in the same memory material, giving rise to the superior device performance.

#### **Results and discussion**

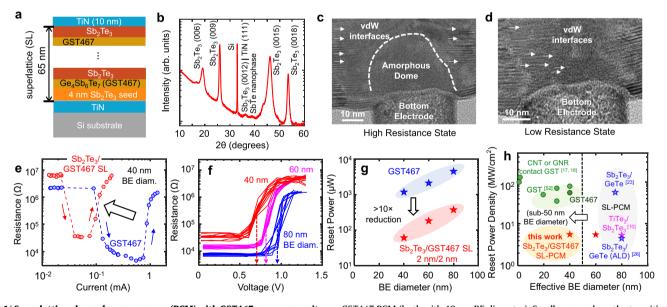

As shown in Fig. 1a, we deposited the superlattice material stacks either onto TiN films (for x-ray analysis) or onto TiN bottom electrodes (for mushroom-cell PCM devices). These superlattices consist of 15 periods of alternating layers of Sb<sub>2</sub>Te<sub>3</sub> ( $\approx$  2 nm) and GST467 ( $\approx$  2 nm), sputtered at 180 °C followed by a 15-min in-situ anneal at 200 °C (see details in Methods: Materials deposition). We cap the films with TiN (10 nm) or TiN/Pt (10/10 nm/nm) top electrodes sputtered without breaking vacuum to complete the fabrication of our memory devices. Our mushroom-cell PCM devices have bottom electrode (BE) diameters between 40 nm and 80 nm.

X-ray diffraction (XRD) spectra in Fig. 1b confirm the polycrystallinity of our as-deposited Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice film, with the same deposition conditions as our PCM devices. The sharp out-ofplane XRD peaks of Sb<sub>2</sub>Te<sub>3</sub> correspond to the highly oriented SL layers parallel to the substrate. The same XRD figure also shows the presence of SbTe nanophase (from the GST467 nanocomposite material<sup>36</sup>). The transmission electron microscope (TEM) image in Fig. 1c shows the cross-section of one of our mushroom-cell devices (with  $\approx 40$  nm TiN BE) in the *high resistance* state (HRS) after  $\approx$  5000 electrical cycles. revealing an amorphous dome surrounded by preserved vdW-like interfaces (zoomed-in TEM and diffraction pattern in supplementary Fig. S1). Figure 1d displays the TEM cross-section of another mushroom-cell PCM device (also with ≈ 40 nm BE diameter) in the low resistance state (LRS) after ≈ 5000 electrical cycles, showing the presence of SL interfaces and vdW-like gaps (zoomed-in TEM in supplementary Fig. S2a). Thus, the vdW interfaces in our nanoscale superlattice PCM devices are sufficiently restored in the LRS after electrical cycling, which agrees with the previous literature for superlattice PCM with different materials and larger BE diameters<sup>24,25,38</sup>. The unoperated regions of the superlattice also show vdW-like interfaces

Fig. 1 | Superlattice phase-change memory (PCM) with GST467 nanocomposite. a Schematic, and b X-ray diffraction (XRD) of Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice (SL) material stack on a TiN (20 nm thick)/Si substrate showing the polycrystallinity of the as-deposited SL. TEM cross-sections of **c** a nanoscale mushroom-cell device with 40 nm BE diameter in the high resistance state (HRS) and **d** a similar device in the low resistance state (LRS). Both devices and the superlattice films in **b** had 2/ 2 nm/nm Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattices, and both device TEMs were taken after  $\approx$ 5000 electrical cycles. Dashed line in **c** outlines the amorphous region of the SL (in HRS) on top of the BE, surrounded by vdW-like SL interfaces (small arrows). VdWlike interfaces are restored throughout the device in the LRS in **d**, in agreement with previous reports on other SL-PCM<sup>24,38</sup>. **e** Measured dc read resistance vs. current, showing  $\approx$  10x reduction of reset current for superlattice PCM compared to control

GST467 PCM (both with 40 nm BE diameter). Small arrows show the transitions from HRS to LRS and from LRS to HRS. **f** Read resistance vs. voltage for superlattice PCM devices with varying BE diameters (from 40 nm to 80 nm) showing sub-1 volt switching of our PCM devices. For each device, 10 different cycles are shown. Reset voltage (marked by colored dashed arrows) is defined as the voltage needed for a  $\approx$  10× resistance increase from LRS. **g** Reset power scales with BE diameter for both our superlattice PCM and control GST467 PCM, as expected (see resistance vs. reset power in Fig. S4b). Superlattice-like PCM devices show >10x reduction of reset power across different BE diameters, down to 40 nm. **h** Reset power density for various sub-100 nm PCM technologies<sup>10,17,18,23,26,51,52</sup>. This work enables the lowest reset power density to-date among nanoscale PCMs with sub-50 nm diameters. Here GST refers to Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>.

(zoomed-out TEM in Supplementary Fig. S2b), including some atomic reconfiguration known to occur during deposition kinetics<sup>39</sup>.

Resistance (R) versus current (I) measurements in Fig. 1e show nearly an order of magnitude reduction of reset (switching) current in our well-cycled (>5000 times) Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice device compared to control GST467 devices with same total film thickness  $(\approx 65 \text{ nm})$  and BE diameter ( $\approx 40 \text{ nm}$ ). For reset programming (LRS to HRS), we used 1/20/1 ns pulses and for set (HRS to LRS), we used pulses with 1/30/50 ns rise/width/fall time. Resistance states were read with a 50-mV direct current (dc) bias, and the measurement setup was further detailed elsewhere<sup>12,40</sup>. Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice devices show higher LRS than control GST467 devices due to larger cross-plane electrical resistivity of the superlattice, caused by the internal vdW-like interfaces<sup>33</sup>. These interfaces also enable substantial heat confinement, leading to the significant reduction of reset current in the PCM with high-quality superlattices (here Sb<sub>2</sub>Te<sub>3</sub>/GST467), as detailed in earlier studies<sup>25,32-34,38</sup>. We also demonstrated similar behavior in a different superlattice (Sb<sub>2</sub>Te<sub>3</sub>/GST225) on  $a \approx 40$  nm bottom electrode in Supplementary Fig. S3. Although both GST467- and GST225-based superlattice PCMs with  $\approx 40$  nm BE diameter (smallest to date) show low reset current, the former has additional advantages of simultaneously fast switching and better thermal stability, as we will explore below.

Measured *R* vs. voltage (*V*) in Fig. 1f reveals sub-1 V switching for our Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice PCM with varying BE diameters, from 40 nm to 80 nm. For the  $\approx$  40 nm devices, the reset voltage (*V*<sub>reset</sub>) is  $\approx$ 0.7 V, the lowest to-date demonstrated in PCM technology. Sub-1 V operation makes this superlattice PCM compatible with modern logic processors<sup>41</sup>, which can enable embedded memory-logic integration for high-performance computing and Internet of Things<sup>42,43</sup>.

In Supplementary Fig. S4a we demonstrate that the reset current of the same set of devices scales properly (here by a factor of four) even at nanoscale dimensions, as we reduce the BE diameter from  $\approx$ 80 nm to  $\approx$  40 nm. The lowest reset current is  $I_{\text{reset}} \approx 85 \,\mu\text{A}$  in our  $\approx$ 40 nm devices, and this can be further reduced by downscaling the BE diameter, as explored with electro-thermal simulations in Supplementary Fig. S5. The reset power,  $P_{\text{reset}}$ , is obtained from *R* vs. power (*P*) (Supplementary Fig. S4b) and scales with BE diameter for both Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice PCM and control GST467 devices as shown in Fig. 1g. The same Fig. 1g also displays >10× reduction of reset power for Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice devices vs. control GST467 across all BE diameter devices in this work.

Our  $\approx 40$  nm Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice PCM devices display  $P_{\text{reset}}$  of  $\approx 60 \,\mu\text{W}$ , which can be further reduced by downscaling the BE diameter below 40 nm. Adjusted by the BE area, the corresponding switching power density is  $\approx 5 \,\text{MW/cm}^2$ , an order of magnitude lower than any comparable sub-50 nm diameter PCM devices reported to date (Fig. 1h). Supplementary Fig. S6 displays the scaling trends of reset power vs. BE diameter, showing how the reset power could be reduced below 10  $\mu$ W in high-density superlattice PCM devices with critical dimension below  $\approx 10 \,\text{nm}$ .

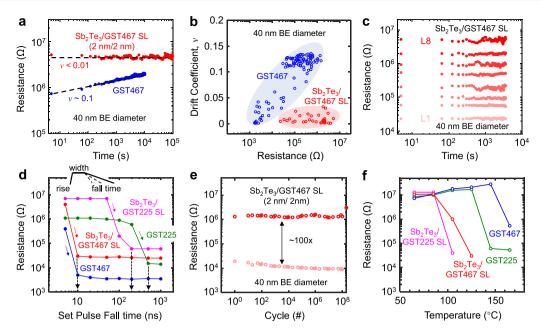

We now turn to features of resistance drift, speed, and stability in our superlattice PCM. Resistance drift is already known to be low in other types of superlattice PCM (with larger diameter), based on reports from our group<sup>31</sup> and others<sup>10,27</sup>. Here we confirm that low resistance drift (with coefficient v < 0.01) is maintained in our nanoscale  $\approx 40$  nm Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice devices (Fig. 2a) compared to control PCM based on GST467 ( $v \approx 0.1$ ). We further find that the low resistance drift of our superlattice PCM is maintained across different resistance states (Fig. 2b). Thus, we are able to demonstrate eight distinct resistance states with low drift in our  $\approx 40$  nm superlattice PCM devices (Fig. 2c and Supplementary Fig. S7), which is promising for high-density multi-level data storage.

In terms of switching speed, PCM devices are usually limited by the set transition, from HRS to LRS. Here, we find that our GST467based superlattice PCMs are  $> 3\times$  faster than other superlattice PCM types and > 10× faster than common (i.e., single-material) PCM devices (see details below). To understand where the benefits come from, in Fig. 2d we compare our GST467-based superlattice PCM with GST225-based superlattice PCM and with common memory cells using either GST225 or GST467. In this figure, the rise time and pulse widths are fixed at 1 ns and 30 ns, respectively, while varying the pulse fall time. Our GST467-based superlattice PCM devices are faster ( $\approx$  40 ns) than GST225-based superlattice devices ( $\approx$  200 ns) for same 40 nm BE diameter. Our previous reports<sup>24,30</sup> on both GST225-based<sup>30</sup> and GeTe-based<sup>24</sup> superlattice PCM showed similar set switching speed at a similar voltage. Thus GST467-based superlattice PCM presents an advantage of faster switching speed over other superlattice-type PCM devices.

We observe that the faster switching speed of GST467-based superlattice PCM originates from the intrinsically faster speed of GST467 (≈40 ns) compared to GST225 PCM (≈500 ns) and GeTe  $(\approx 220 \text{ ns})^{24}$  based superlattice devices. We note that an even faster set speed could be achieved, however at the expense of a larger set voltage. Previous reports<sup>36,37</sup> on GST467 nanocomposite confirmed the presence of the SbTe nanophase (also evident from our TEMs in Supplementary Fig. S8 and Supplementary Fig. S9a) grown coherently with the cubic Ge-Sb-Te matrix along  $\{111\}_{cubic}$  crystallographic planes. The thickness of two-atom-thick SbTe<sup>36,37</sup> in the (001) direction is  $\approx$ 0.35 nm (Supplementary Fig. S8e); thus the SbTe nanoclusters are still expected to be present within the  $\approx 2 \text{ nm Ge}_4\text{Sb}_6\text{Te}_7$  thin layers across the superlattice stack. The presence of SbTe nanophase within the GST467-based superlattice stack is also confirmed in our XRD measurements (Fig. 1b). Such SbTe nanoclusters act as nucleation sites and enable faster switching in GST467-based superlattice PCM. Moreover, a similarity in the bonding between amorphous and crystalline GST467<sup>37</sup> also indicates that a structure in the amorphous state serves as a precursor for the faster crystallization<sup>21</sup> of this material. We further note that the microstructure of GST467 in our superlattice Sb<sub>2</sub>Te<sub>3</sub>/ GST467 devices can also be influenced by the adjacent Sb<sub>2</sub>Te<sub>3</sub> layers, which could introduce some structural frustration and help control the PCM device performance.

Cycling measurements in Fig. 2e reveal that our  $\approx$  40 nm superlattice PCM devices can simultaneously achieve a large resistance window (>100×) and large endurance over >10<sup>8</sup> switching cycles. The robustness of the simultaneously low reset voltage and large on/off ratio in our superlattice devices is further displayed in Supplementary Fig. S10. Resistance vs. temperature measurements in Fig. 2f demonstrate higher temperature stability of the HRS of GST467-based superlattice PCM, compared to our control superlattice devices with GST225, thanks to the better thermal stability of GST467 vs. GST225. This is attributed to a higher crystallization temperature in GST467 ( $\approx$  200 °C) vs. GST225 ( $\approx$ 150 °C), confirmed by temperature dependent XRD (Supplementary Fig. S9a) and sheet resistance (Supplementary Fig. S9b) of both materials.

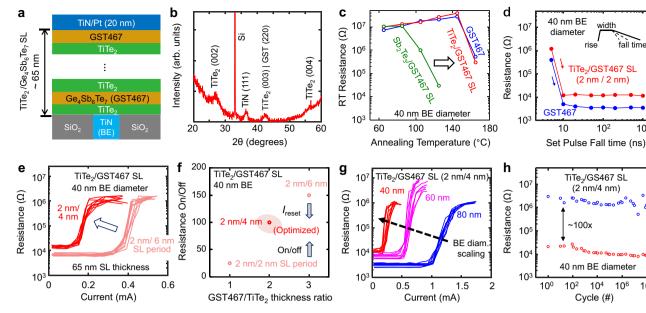

Supplementary Fig. S11 shows that the retention of our Sb<sub>2</sub>Te<sub>3</sub>/ GST467 superlattice PCM is  $\approx 10^5$  hours at 83 °C (close to the productlevel requirement of 10<sup>5</sup> hours at 85 °C<sup>44</sup>). The high-temperature retention of Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice devices can still be limited by the lower crystallization temperature of Sb<sub>2</sub>Te<sub>3</sub><sup>45</sup>. To enable even better temperature stability in our superlattice PCM, we next replaced the Sb<sub>2</sub>Te<sub>3</sub> layers with a thermal barrier material of higher melting temperature, TiTe<sub>2</sub><sup>28,46</sup> and fabricated TiTe<sub>2</sub>/GST467 superlattice devices, as shown in Fig. 3a (schematic) and supplementary Fig. S12 (high resolution TEM). These films are deposited by sputtering, very similar to our Sb<sub>2</sub>Te<sub>3</sub> layers, except for an in-situ annealing step at 300 °C (see further details in Methods: Materials deposition). XRD spectra in Fig. 3b confirm the out-of-plane features of the as-deposited TiTe<sub>2</sub>/GST467 superlattice film on a TiN/Si substrate, where the TiN surface is chosen to mimic the PCM bottom electrode composition. High-resolution TEM cross-sections of well-cycled ( $\approx 10^4$  times) TiTe<sub>2</sub>/

**Fig. 2** | **Resistance drift, speed, reliability, and endurance of GST467-based superlattice PCM. a** High resistance state (HRS) vs. time, showing low drift in Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice PCM vs. control GST467, both devices with  $\approx$  40 nm BE diameter. Dashed lines are fit to  $R(t) \sim (t/t_0)^v$ , where v is the drift coefficient, t is the time after programming, and  $t_0$  is a constant. **b** Drift coefficient v as a function of resistance state for the same superlattice (SL, red symbols) and non-superlattice (blue symbols) devices. **c** Eight resistance states with low drift maintained > 1 hour in our GST467-based superlattice PCM with 40 nm diameter, enabling a multi-level cell with up to 3 bits. **d** Effect of fall times on set transition for four types of PCM, as labeled. All pulses have 1 ns rise time and 30 ns widths, and all devices have 40 nm diameter. The minimum fall times to reach the LRS are marked with black dashed arrows. The GST467-based devices can switch with >10x shorter set fall time ( $\approx$  10x faster switching) compared to control devices based on GST225, for both superlattice PCM. Set voltages for Sb<sub>2</sub>Te<sub>3</sub>/GST467, Sb<sub>2</sub>Te<sub>3</sub>/GST25,

GST467 and GST225 are 0.65 V, 0.8 V, 1.2 V, and 1.3 V, respectively. **e** Endurance up to 2 × 10<sup>8</sup> cycles measured for our GST467-based superlattice PCM with 40 nm BE diameter, maintaining a 100× resistance window. **f** High-temperature HRS stability of our superlattice PCM compared to control devices. After programming to HRS, devices were annealed for 30 min at successively higher temperatures. We reached each of the upper resistance levels by single-shot reset pulses from the LRS. DC resistances are measured back at room temperature after each annealing event. The higher crystallization temperature of GST467 enables higher temperature stability of PCM based on it. The larger HRS ≈ 10 MΩ in Fig. 2f (vs. Figure 1e and Fig. 2e) is due to differences in the amorphous volume originating from the different pulsing schemes. In addition, fabrication-induced variations between devices can also contribute to observed differences in HRS. All resistances in (**a-f**) are measured with 50 mV dc bias. Devices in **a-d** and **f** were well-cycled (> 5000 cycles) before measurements.

GST467 superlattice PCM devices in the HRS and LRS are shown in Supplementary Fig. S13 and Fig. S14, respectively.

Temperature-dependent measurements of the HRS confirm the significantly higher temperature stability of TiTe<sub>2</sub>/GST467 superlattice devices compared to those based on Sb<sub>2</sub>Te<sub>3</sub>/GST467 (Fig. 3c). Supplementary Fig. S11 shows that the retention of our TiTe<sub>2</sub>/GST467 superlattice PCM is  $\approx 10^{5}$  h at 120 °C, promising for applications that require higher temperature retention<sup>42</sup>. Our TiTe<sub>2</sub>/GST467 superlattice PCM also maintains fast switching speed ( $\approx 40$  ns) in devices with  $\approx 40$  nm bottom electrode (Fig. 3d). Therefore, our nanoscale TiTe<sub>2</sub>/GST467 devices offer simultaneously fast switching speed *and* higher temperature stability, by combining the unique properties of the GST467 nanocomposite with the thermal barrier properties of TiTe<sub>2</sub>, within a superlattice structure.

Electrical measurements of 40 nm BE diameter TiTe<sub>2</sub>/Ge<sub>4</sub>Sb<sub>6</sub>Te<sub>7</sub> superlattice devices further show that both the reset current (Fig. 3e) and the resistance on/off ratio (Fig. 3f) can be simultaneously optimized by varying the thickness of the GST467 layer within an SL period (the TiTe<sub>2</sub> layer is fixed at  $\approx$  2 nm and the total SL thickness is  $\approx$  65 nm). Thus, low switching current of  $\approx$  180 µA and resistance on/off ratio of  $\approx$  100 are simultaneously achieved in a 2/4 nm/nm TiTe<sub>2</sub>/GST467 superlattice device with 40 nm BE diameter, whereas *R* vs. *V* for the same device (Supplementary Fig. S15) confirms the sub-1V switching operation with *V*<sub>reset</sub>  $\approx$  0.85 V. We also note that the reset current measured here is  $\approx$  2× higher (for the same diameter) than for the Sb<sub>2</sub>Te<sub>3</sub>/GST467 devices (Fig. 1e and Supplementary Fig. S4a) due to the smaller LRS in TiTe<sub>2</sub>/GST467, which is attributed to the higher electrical conductivity of TiTe<sub>2</sub><sup>28,47</sup>. Figure 3g displays the scaling of

reset current with BE diameter (from  $\approx$  80 nm down to  $\approx$  40 nm) for 2/ 4 nm/nm TiTe<sub>2</sub>/GST467 superlattice devices and shows the clear pathway towards further lowering the reset current. Our optimized 2/ 4 nm/nm TiTe<sub>2</sub>/GST467 superlattice devices with  $\approx$  40 nm BE diameter also show good endurance for >10<sup>8</sup> switching cycles, maintaining a resistance on/off ratio  $\approx$  100 (Fig. 3h).

The sharp vdW-like interfaces within the superlattice are responsible for the significant reduction of reset power in our SL-PCM. Previous studies<sup>23,48</sup> had suggested that crystalline-to-crystalline transition through Ge atom movement may be responsible for switching in Sb<sub>2</sub>Te<sub>3</sub>/GeTe superlattice PCM. In contrast, our nanoscale superlattice PCM devices show a thermally-driven crystalline-toamorphous transition (Fig. 1c, supplementary Fig. S1, Fig. S13, Fig. S16a, b). The low switching power originates from heat confinement of the vdW-like interfaces within the superlattice. We note that some interfacial reconfiguration between the superlattice layers can occur after electrical cycling, or during the delicate TEM sample preparation and imaging. However, van der Waals-like gaps appear sufficiently restored after cycling back to the LRS, enabling the heat confinement and low reset current in superlattice PCM<sup>24,25</sup>. Very recently, using nano-calorimetry<sup>49</sup> we also found that the melting temperature of Sb<sub>2</sub>Te<sub>3</sub>/GST225 superlattices is ≈ 380 °C (240 °C lower than that of bulk GST225), providing additional insights into the lowpower switching of these devices. Furthermore, a smaller active volume of the amorphous region (supplementary Fig. S1) compared to GST225 PCM<sup>28</sup> can also contribute to the reduced switching power of our SL-PCM devices. The low energy switching of superlattice PCM in this work is further aided by the nanoscale device dimensions

10<sup>3</sup>

10<sup>8</sup>

Fig. 3 | Superlattice devices with GST467 nanocomposite and TiTe<sub>2</sub> thermal barriers. a Schematic of TiTe<sub>2</sub>/GST467 superlattice device, TiTe<sub>2</sub> forming thermal barriers<sup>28</sup> and GST467 as the phase-change layers. b XRD of TiTe<sub>2</sub>/ GST467 superlattice (SL) on a TiN (20 nm thick)/Si substrate showing the polycrystallinity of the as-deposited SL. c Comparing the high-temperature stability of HRS in a TiTe<sub>2</sub>/GST467 superlattice device with a Sb<sub>2</sub>Te<sub>3</sub>/GST467 superlattice device and a GST467 control device (all with 40 nm BE diameter). The HRS of TiTe<sub>2</sub>/ GST467 and control GST467 devices are similar, with no re-crystallization for >3 hours at 145 °C. Measurement protocols are described in Fig. 2f. Room temperature (RT) is 20 °C. d Effect of fall times on set transition for TiTe<sub>2</sub>/GST467 and control GST467 devices. Devices have 40 nm BE diameter, and all pulses have 1 ns rise time and 30 ns widths. Measurement protocols are described in Fig. 2d. Both device types show fast switching speed of  $\approx$  40 ns. **e** Effect of SL period thickness on

$(\approx 40 \text{ nm BE diameter})$  compared to other superlattice PCM demonstrations<sup>12,24,30</sup>. Additional improvement in the switching energy of our superlattice PCM devices could be possible by further narrowing the reset pulse width<sup>50</sup>.

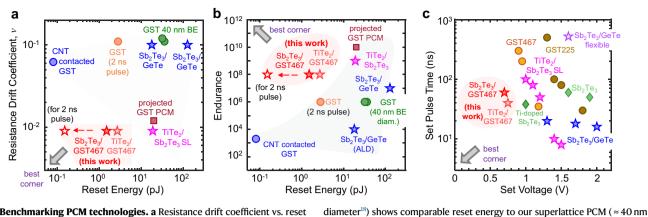

Finally, we compare our GST467-based superlattice PCM with previous demonstrations, including superlattice devices (of larger BE diameters)<sup>10,18,23,26,50-53</sup>, by plotting both drift coefficient (Fig. 4a) and endurance (Fig. 4b) vs. reset energy as well as switching speed vs. switching voltage (Fig. 4c). Our ultra-scaled 40 nm BE diameter devices demonstrate simultaneously low switching energy with large resistance on/off ratio, low resistance drift with multilevel operation, fast switching speed and high endurance, thus approaching the "best corners" of the benchmarking plots. We find a reset energy <1.5 pJ  $(\approx 60 \,\mu\text{W}$  reset power multiplied by 20 ns reset pulse, limited by our measurement instrument) in our  $\approx 40 \text{ nm}$  superlattice devices. Because PCM could be reset<sup>50</sup> with pulse widths down to  $\approx 2 \text{ ns}$ . we estimate the reset energy for our smallest (  $\approx 40$  nm) device could be as low as <0.15 pJ (hollow red stars in Fig. 4a, b), which can be further reduced by scaling down the PCM device dimensions, beyond the records achieved in this work. Figure 4c shows the set time vs. set voltage trade-off (i.e., a smaller set time can be achieved at the expense of a larger set voltage) in PCM technology9. Our GST467 nanocomposite-superlattice devices are near the best corner, with low set voltage and short set pulse time compared to other PCM demon- $Sb_{2}Te_{3}^{21,54}$ , GST225, doped strations using and other superlattices<sup>10,12,23,55</sup>. Thus, the GST467-based superlattice PCM in this work offers a unique simultaneous advantage of faster switching speed and better retention over other superlattice-type (GeTe/Sb<sub>2</sub>Te<sub>3</sub><sup>12,23-27</sup>, TiTe<sub>2</sub>/Sb<sub>2</sub>Te<sub>3</sub><sup>10,28</sup>, GeSb<sub>2</sub>Te<sub>4</sub>/Sb<sub>2</sub>Te<sub>3</sub><sup>29</sup>, and Sb<sub>2</sub>Te<sub>3</sub>/GST225<sup>30,31</sup>) PCM

devices. Additionally, our nanoscale superlattice devices with the smallest dimensions to date ( $\approx 40$  nm) for a superlattice technology on a CMOS-compatible substrate further ascertain the promise of this technology for future high-density and energy-efficient PCM.

Thus, our nanocomposite-based superlattice PCMs (both Sb<sub>2</sub>Te<sub>3</sub>/GST467 and TiTe<sub>2</sub>/GST467) exhibit significantly reduced reset energy, sub-1 V switching, lower resistance drift, and better endurance compared to those of traditional PCMs. The low reset energy, sub-1 V operation, and fast switching position them among the leading next-generation memory candidates for on-chip logic and memory heterogeneous integration<sup>43,56,57</sup>. In addition, we find TiTe<sub>2</sub>/GST467 has better retention at high temperatures and could be promising as embedded memory for automotive applications<sup>42</sup>. Meanwhile, Sb<sub>2</sub>Te<sub>3</sub>/GST467 with simultaneously large on/off ratio and low resistance drift is well-positioned for emerging analog computing applications<sup>4,58</sup>.

In summary, we demonstrated nanoscale superlattice (SL) phasechange memory devices down to  $\approx 40 \text{ nm}$  dimensions, based on Ge<sub>4</sub>Sb<sub>6</sub>Te<sub>7</sub> nanocomposite, and achieved low switching energy ( $\approx$  1.5 pJ), fast switching speed ( $\approx$  40 ns), and good endurance (>10<sup>8</sup> cycles). The low-power operation is enabled by strong heat confinement within the material superlattice, integrated with the nanoscale  $\approx$  40 nm bottom electrode. The robustness of our nanoscale devices is confirmed using three different superlattices: Sb<sub>2</sub>Te<sub>3</sub>/GST467, TiTe<sub>2</sub>/ GST467, and Sb<sub>2</sub>Te<sub>3</sub>/GST225. Among these, the microstructural properties of GST467 enable faster switching, while its higher crystallization temperature leads to better thermal stability. This work provides key materials and engineering insights towards the design and optimization of energy-efficient PCM, and could inspire the

**Fig. 4** | **Benchmarking PCM technologies. a** Resistance drift coefficient vs. reset energy, and **b** endurance vs. reset energy. Block arrows point to the desirable "best corners" with low resistance drift, high endurance, and low reset energy. Our GST467 nanocomposite-superlattice devices display some of the best overall characteristics, compared to all other existing PCMs<sup>10,18,21,23,26,50-53,54</sup>. The reset energy in our work (red filled star) is limited by our -20 ns pulse width and instrumentation,<sup>12,40</sup> which are not fundamental limits<sup>13,50</sup>. With 2 ns pulse widths<sup>50</sup> the reset energy of our 40 nm superlattice PCM is projected (hollow red star) to reach  $\approx$  0.15 pJ. GST-based PCM with carbon nanotube (CNT) electrodes ( $\approx$  1.7 nm

diameter), but devices with CNT electrodes have limited endurance and high resistance drift (blue circles). This also shows that our reset energy can be reduced further, by decreasing the BE diameter. **c** Set pulse time vs. set voltage. The block arrow points to the desirable "best corner" with low set voltage and short set pulse time. Our GST467 nanocomposite-superlattice PCM is located near the best corner, compared to other existing PCMs<sup>10,12,21,23,54,55</sup>. To simplify notation, GST refers to the GST225 stoichiometry in the entire figure.

industry-scale adoption of nanoscale superlattice phase-change materials for low-power and high-density storage.

#### Methods

#### Material deposition

Before the deposition of the superlattice (SL) materials, the bottom TiN surface was in-situ cleaned by Ar ion etching for 10 minutes using 50 W radio-frequency (RF) bias to remove any native oxide. For the deposition of the Sb<sub>2</sub>Te<sub>3</sub>/Ge<sub>4</sub>Sb<sub>6</sub>Te<sub>7</sub> (GST467) SL, first,  $a \approx 4$  nm thick Sb<sub>2</sub>Te<sub>3</sub> seed layer was deposited on the bottom TiN at room temperature (sputter chamber base pressure  $< 10^{-7}$  Torr). Then, the temperature in the sputter chamber was raised to  $\approx 180 \,^{\circ}\text{C}$ at a rate of 10 °C/min. and 15 periods of GST467 ( $\approx 2 \text{ nm}$ ) and Sb<sub>2</sub>Te<sub>3</sub> ( $\approx$  2 nm) alternating layers were deposited at  $\approx$  180 °C followed by an annealing of the stack at 200 °C for 15 min to ensure better crystallinity (total SL stack thickness  $\approx 65$  nm). For the deposition of the GST467 layer we used 20 sccm Ar flow, 12 W dc power, 2 mTorr pressure while for sputtering Sb<sub>2</sub>Te<sub>3</sub> we used 30 sccm Ar flow, 35 W rf power, 4 mTorr pressure. The period thickness was chosen based on our measurements of SL cross-plane thermal conductivity of a similar SL stack (Sb<sub>2</sub>Te<sub>3</sub>/GST225) to ensure low thermal conductivity (higher heat confinement) as well as low resistance drift<sup>30,31</sup>

For the deposition of the TiTe<sub>2</sub>/GST467 superlattice, TiTe<sub>2</sub> and GST467 alternating layers ( $\approx 65 \text{ nm}$  SL thickness in total) were deposited on the bottom TiN at  $\approx 180 \,^{\circ}\text{C}$  followed by in-situ annealing at 300  $^{\circ}\text{C}$  for 30 min in the sputter chamber. TiTe<sub>2</sub> layers were sputtered with 30 sccm Ar flow, 30 W rf power, 4 mTorr pressure, and for the deposition of the GST467 layer we used 20 sccm Ar flow, 12 W dc power, 2 mTorr pressure. For the optimization of the TiTe<sub>2</sub>/GST467 SL-PCM devices, we fabricated SLs with varying periods e.g., with 2/2 nm/nm, 2/4 nm/nm and 2/6 nm/nm of TiTe<sub>2</sub>/GST467.

#### Device fabrication

After the deposition of the SL layers, we let the sputtering chamber cool down to room temperature and then deposit a  $\approx$  10 nm TiN capping layer in situ (reactive sputtering of Ti with N<sub>2</sub>; 30 sccm Ar, 15 sccm N<sub>2</sub>, 3 mTorr pressure at 100 W dc power for Ti). The TiN layer acts as a capping layer to protect the SL from oxidation and as part of the top electrode for the PCM devices. For the SL-PCM devices, we also subsequently deposit  $\approx$  10 nm Pt (25 sccm Ar, 2 mTorr pressure at 100 W

dc power) at room temperature as part of the rest of the top electrode to complete the fabrication process.

#### Data availability

All data needed to evaluate the conclusions in this paper are available within the paper and the Supplementary Information file.

#### References

- Ambrogio, S. et al. Equivalent-accuracy accelerated neuralnetwork training using analogue memory. *Nature* 558, 60–67 (2018).

- 2. Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. *Nature* **608**, 504–512 (2022).

- 3. Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. *Nature* **601**, 211–216 (2022).

- Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. *Nat. Nanotechnol.* 15, 529–544 (2020).

- 5. Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. *Nat. Electron.* **1**, 333–343 (2018).

- 6. Wuttig, M. & Yamada, N. Phase-change materials for rewriteable data storage. *Nat. Mater.* **6**, 824–832 (2007).

- 7. Raoux, S., Xiong, F., Wuttig, M. & Pop, E. Phase change materials and phase change memory. *MRS Bull.* **39**, 703–710 (2014).

- 8. Khan, A. I. et al. Two-fold reduction of switching current density in phase change memory using  $Bi_2Te_3$  thermoelectric interfacial layer. IEEE Electron Device Lett. **41**, 1657–1660 (2020).

- Zhang, W., Mazzarello, R., Wuttig, M. & Ma, E. Designing crystallization in phase-change materials for universal memory and neuroinspired computing. *Nat. Rev. Mater.* 4, 150–168 (2019).

- Ding, K. et al. Phase-change heterostructure enables ultralow noise and drift for memory operation. *Science*. **366**, 210–215 (2019).

- Kuzum, D., Jeyasingh, R. G. D., Lee, B. & Wong, H.-S. P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. *Nano Lett.* **12**, 2179–2186 (2012).

- Khan, A. I. et al. Ultralow-switching current density multilevel phase-change memory on a flexible substrate. *Science*. **373**, 1243–1247 (2021).

- 13. Wong, H.-S. P. et al. Phase change memory. *Proc. IEEE* **98**, 2201–2227 (2010).

- Article

- Boniardi, M. et al. Statistics of resistance drift due to structural relaxation in phase-change memory arrays. *IEEE Trans. Electron Devices* 57, 2690–2696 (2010).

- Yang, Z. et al. Designing conductive-bridge phase-change memory to enable ultralow programming power. *Adv. Sci.* 9, 2103478 (2022).

- Wang, J.-J. et al. Tailoring the oxygen concentration in Ge-Sb-O alloys to enable femtojoule-level phase-change memory operations. *Mater. Futur.* 1, 45302 (2022).

- 17. Wang, X. et al. Minimizing the programming power of phase change memory by using graphene nanoribbon edge-contact. *Adv. Sci.* **9**, 2270159 (2022).

- Xiong, F., Liao, A. D., Estrada, D. & Pop, E. Low-power switching of phase-change materials with carbon nanotube electrodes. *Science*. 332, 568–570 (2011).

- Tung, M. C. et al. Nanoscale phase change memory arrays patterned by block copolymer directed self-assembly. in *Proc.SPIE* vol. 1205406 (2022).

- 20. Shen, J. et al. Toward the speed limit of phase-change memory. *Adv. Mater.* **35**, 2208065 (2023).

- Rao, F. et al. Reducing the stochasticity of crystal nucleation to enable subnanosecond memory writing. *Science*. **358**, 1423–1427 (2017).

- 22. Bruns, G. et al. Nanosecond switching in GeTe phase change memory cells. *Appl. Phys. Lett.* **95**, 43108 (2009).

- Simpson, R. E. et al. Interfacial phase-change memory. Nat. Nanotechnol. 6, 501–505 (2011).

- Khan, A. I. et al. Electro-thermal confinement enables improved superlattice phase change memory. *IEEE Electron Device Lett.* 43, 204–207 (2022).

- Boniardi, M. et al. Evidence for thermal-based transition in superlattice phase change memory. *Phys. status solidi – Rapid Res. Lett.* 13, 1800634 (2019).

- Yoo, C. et al. Atomic layer deposition of Sb<sub>2</sub>Te<sub>3</sub>/GeTe superlattice film and its melt-quenching-free phase-transition mechanism for phase-change memory. *Adv. Mater.* **34**, 2207143 (2022).

- Zhou, L. et al. Resistance drift suppression utilizing GeTe/Sb<sub>2</sub>Te<sub>3</sub> superlattice-like phase-change materials. *Adv. Electron. Mater.* 6, 1900781 (2020).

- Shen, J. et al. Thermal barrier phase change memory. ACS Appl. Mater. Interfaces 11, 5336–5343 (2019).

- Feng, J. et al. "Stickier"-surface Sb<sub>2</sub>Te<sub>3</sub> templates enable fast memory switching of phase change material GeSb<sub>2</sub>Te<sub>4</sub> with growth-dominated crystallization. ACS Appl. Mater. Interfaces 12, 33397–33407 (2020).

- Khan, A. I. et al. Unveiling the effect of superlattice interfaces and intermixing on phase change memory performance. *Nano Lett.* 22, 6285–6291 (2022).

- Wu, X. et al. Understanding interface-controlled resistance drift in superlattice phase change memory. *IEEE Electron Device Lett.* 43, 1669–1672 (2022).

- Sklénard, B. et al. Electronic and thermal properties of GeTe/Sb<sub>2</sub>Te<sub>3</sub> superlattices by ab initio approach: Impact of Van der Waals gaps on vertical lattice thermal conductivity. *Appl. Phys. Lett.* **119**, 201911 (2021).

- Kwon, H. et al. Uncovering thermal and electrical properties of Sb<sub>2</sub>Te<sub>3</sub>/GeTe superlattice films. *Nano Lett.* **21**, 5984–5990 (2021).

- Ning, J. et al. Low thermal conductivity phase change memory superlattices. 10.48550/arxiv.2209.15227 https://doi.org/10. 48550/arxiv.2209.15227 (2022).

- Hauser, J. J. Hopping conductivity in amorphous antimony. *Phys. Rev. B.* 9, 2623 (1974).

- Kusne, A. G. et al. On-the-fly closed-loop materials discovery via Bayesian active learning. *Nat. Commun.* 11, 5966 (2020).

- 37. Khan, A. I. et al. Energy efficient neuro-inspired phase change memory based on  $Ge_4Sb_6Te_7$  as a novel epitaxial nanocomposite. *Adv. Mater.* **7**, 2300107 (2023).

- Térébénec, D. et al. Improvement of phase-change memory performance by means of GeTe/Sb<sub>2</sub>Te<sub>3</sub> superlattices. *Phys. status* solidi – Rapid Res. Lett. **15**, 2000538 (2021).

- Momand, J. et al. Dynamic reconfiguration of van der Waals gaps within GeTe-Sb<sub>2</sub>Te<sub>3</sub> based superlattices. *Nanoscale* 9, 8774–8780 (2017).

- Neumann, C. M. et al. Engineering thermal and electrical interface properties of phase change memory with monolayer MoS<sub>2</sub>. *Appl. Phys. Lett.* **114**, 82103 (2019).

- Yeap, G. et al. 5 nm CMOS Production Technology Platform featuring full-fledged EUV, and High Mobility Channel FinFETs with densest 0.021µm<sup>2</sup> SRAM cells for Mobile SoC and High Performance Computing Applications. in 2019 IEEE International Electron Devices Meeting (IEDM) 36.7.1-36.7.4 https://doi.org/10.1109/IEDM19573.2019.8993577 (2019).

- Cappelletti, P. et al. Phase change memory for automotive grade embedded NVM applications. J. Phys. D. Appl. Phys. 53, 193002 (2020).

- Mohammad, K., Tekeste, T., Mohammad, B., Saleh, H. & Qurran, M. Embedded memory options for ultra-low power IoT devices. *Microelectronics J.* 93, 104634 (2019).

- 44. Gleixner, B. et al. Data retention characterization of phase-change memory arrays. in 2007 IEEE International Reliability Physics Symposium Proceedings. 45th Annual 542–546 https://doi.org/10.1109/ RELPHY.2007.369948 (2007).

- Zhu, M. et al. Uniform Ti-doped Sb<sub>2</sub>Te<sub>3</sub> materials for high-speed phase change memory applications. *Appl. Phys. Lett.* **104**, 053119 (2014).

- 46. Cordes, H. & Schmid-Fetzer, R. Phase equilibria in the Ti-Te system. J. Alloys Compd. **216**, 197–206 (1995).

- Ding, K. et al. Low-energy amorphization of Ti<sub>1</sub>Sb<sub>2</sub>Te<sub>5</sub> phase change alloy induced by TiTe<sub>2</sub> nano-lamellae. Sci. Rep. 6, 30645 (2016).

- Kolobov, A. V., Fons, P., Saito, Y. & Tominaga, J. Atomic reconfiguration of van der Waals gaps as the key to switching in GeTe/ Sb<sub>2</sub>Te<sub>3</sub> superlattices. ACS Omega 2, 6223–6232 (2017).

- Zhao, J. et al. Probing the melting transitions in phase-change superlattices via thin film nanocalorimetry. *Nano Lett.* https://doi. org/10.1021/acs.nanolett.3c01049 (2023).

- 50. Stern, K. et al. Uncovering phase change memory energy limits by sub-nanosecond probing of power dissipation dynamics. *Adv. Electron. Mater.* **7**, 2100217 (2021).

- Wu, J. Y. et al. A 40 nm Low-Power Logic Compatible Phase Change Memory Technology. in 2018 IEEE International Electron Devices Meeting (IEDM) 27.6.1–27.6.4 https://doi.org/10.1109/IEDM.2018. 8614513 (2018).

- 52. H.-S. P. Wong, et al. Stanford Memory Trends. Accessed: May 2, 2023. [Online]. Available: https://nano.stanford.edu/stanfordmemory-trends.

- 53. Ghazi Sarwat, S. et al. Projected mushroom type phase-change memory. *Adv. Funct. Mater.* **31**, 2106547 (2021).

- 54. Zhu, M. et al. One order of magnitude faster phase change at reduced power in Ti-Sb-Te. *Nat. Commun.* **5**, 4086 (2014)

- 55. Zhou, X. et al. Phase-change memory materials by design: a strain engineering approach. *Adv. Mater.* **28**, 3007–3016 (2016).

- Lee, W. J., Kim, C. H. & Kim, S. W. A last-level cache management for enhancing endurance of phase change memory. in 2021 36th International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC) 1–4 (2021). https://doi.org/10. 1109/ITC-CSCC52171.2021.9501266.

- 57. Kaul, A., Luo, Y., Peng, X., Yu, S. & Bakir, M. S. Thermal Reliability Considerations of Resistive Synaptic Devices for 3D CIM System Performance. in 2021 IEEE International 3D Systems Integration

Conference (3DIC) 1–5 https://doi.org/10.1109/3DIC52383.2021. 9687612 (2021).

Nandakumar, S. R. et al. Phase-change memory models for deep learning training and inference. in 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS) 727–730 https://doi.org/10.1109/ICECS46596.2019.8964852 (2019).

#### Acknowledgements

This work was performed in parts at the Stanford Nanofabrication Facility (SNF), Stanford Nano Shared Facilities (SNSF) and Corporate Research, Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu 30075, Taiwan and is supported in part by the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI) and in part by Semiconductor Research Corporation. A.I.K. acknowledges support from the Stanford Graduate Fellowship. The work at the University of Maryland was partly supported by ONR MURI N00014-17-1-2661. H.Z. acknowledges support from the U.S. Department of Commerce, NIST under financial assistance award 70NANB22H101. A.V.D. acknowledges support from the Material Genome Initiative funding allocated to NIST.

#### Author contributions

X.W. and A.I.K. contributed equally. A.I.K. and E.P. conceived the idea. A.I.K. and X.W. designed the experiments, performed all the material deposition and device fabrication with help from H.L. and X.B. X.W. carried out the electrical measurements with help from A.I.K. and H.L. X.W. analyzed the data with input from A.I.K, H.-S.P.W, and E.P. C.-F.H. performed superlattice transmission electron microscopy characterization and A.I.K. and H.Y. performed X-ray diffraction measurements and nanocomposite materials characterization with input from E.P. and I.T. H.Z. and A.V.D. performed the TEM/STEM characterization of the GST467 nanocomposite. N.R. performed electro-thermal simulation with mentorship from A.I.K. A.I.K., X.W., and E.P. wrote the manuscript. All authors discussed the results and edited the manuscript. E.P. and H.-S.P.W. supervised the work.

#### **Competing interests**

The authors declare no competing interests.

#### **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-023-42792-4.

**Correspondence** and requests for materials should be addressed to Eric Pop.

**Peer review information** *Nature Communications* thanks the anonymous reviewers for their contribution to the peer review of this work. A peer review file is available.

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/ licenses/by/4.0/.

© The Author(s) 2024