#### **UC Irvine**

#### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Low-Power Integrated Circuits For Biomedical Applications

#### **Permalink**

https://escholarship.org/uc/item/85k517t0

#### **Author**

Karimi Bidhendi, Alireza

#### **Publication Date**

2019

#### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution-NonCommercial-NoDerivatives License, available at <a href="https://creativecommons.org/licenses/by-nc-nd/4.0/">https://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Peer reviewed|Thesis/dissertation

## $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

## ${\bf Low\text{-}Power\ Integrated\ Circuits\ For\ Biomedical\ Applications}$ ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical Engineering

by

Alireza Karimi Bidhendi

Dissertation Committee: Professor Payam Heydari, Chair Professor Zoran Nenadic Professor An H. Do

## **DEDICATION**

To my parents whom their encouragement, moral support and unconditional love gave me strength to be the best of myself.

## TABLE OF CONTENTS

|              |                                 | P                                                                                                                     | age                                          |

|--------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| $\mathbf{L}$ | IST (                           | OF FIGURES                                                                                                            | $\mathbf{v}$                                 |

| $\mathbf{L}$ | IST (                           | OF TABLES                                                                                                             | ix                                           |

| $\mathbf{A}$ | CKN                             | OWLEDGMENTS                                                                                                           | $\mathbf{x}$                                 |

| $\mathbf{C}$ | URR                             | ICULUM VITAE                                                                                                          | xi                                           |

| $\mathbf{A}$ | BST                             | RACT OF THE DISSERTATION                                                                                              | xiv                                          |

| 1            | Intr                            | roduction                                                                                                             | 1                                            |

| <b>2</b>     | Ultı                            | ra Low-Power Brain Signal Acquisition Front-Ends                                                                      | 4                                            |

|              | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introduction                                                                                                          | 4<br>9<br>11<br>16<br>21<br>22<br>24<br>30   |

| 3            |                                 | CMOS MedRadio Transceiver with Supply-Modulated Power Saving hnique for an Implantable Brain-Machine Interface System | 32                                           |

|              | 3.1<br>3.2<br>3.3<br>3.4        | Introduction                                                                                                          | 32<br>36<br>37<br>40<br>43<br>44<br>48<br>49 |

|              |                                 | 3.5.1 Direct-Modulation Transmitter                                                                                   | 49<br>49                                     |

|   | 3.6            | Experim    | ental Results                                                | 51 |

|---|----------------|------------|--------------------------------------------------------------|----|

|   |                | 3.6.1 R    | Receiver Electrical Measurements                             | 52 |

|   |                | 3.6.2 T    | ransmitter Electrical Measurements                           | 54 |

|   |                | 3.6.3 V    | Vireless Connection Measurement Setup and Results            | 55 |

|   |                | 3.6.4 N    | Multi-User Coexistence and Interference Testing              | 56 |

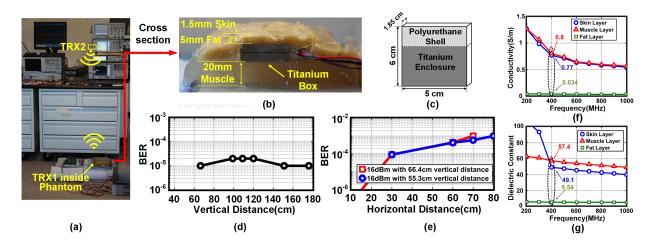

|   |                | 3.6.5 in   | n-vitro Phantom Measurements                                 | 58 |

|   | 3.7            | Conclusion | on                                                           | 61 |

| 4 | A F            | Fast Star  | t-up Crystal Oscillator Using Precise Dithered Injection and | 1  |

|   | $\mathbf{Act}$ | ive Indu   | ctance                                                       | 62 |

|   | 4.1            | Introduc   | tion                                                         | 62 |

|   | 4.2            | Backgrou   | and the proposed ideas                                       | 66 |

|   | 4.3            | Precise I  | Dithered Signal Injection                                    | 67 |

|   |                | 4.3.1 P    | Problem Statement: Damped Driven Oscillator                  | 68 |

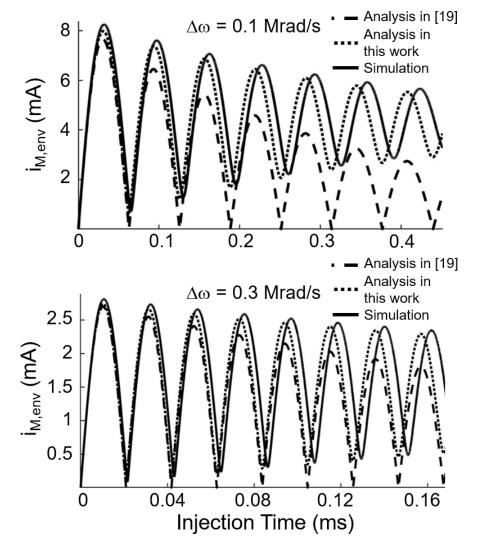

|   |                | 4.3.2 A    | analysis of the Motional Current's Envelope                  | 70 |

|   |                | 4.3.3 S    | ensitivity to Timing and Injection Frequency Inaccuracies    | 73 |

|   |                | 4.3.4 In   | nterpretation of the Analysis                                | 75 |

|   |                | 4.3.5 R    | Relaxation Oscillator Implementation                         | 76 |

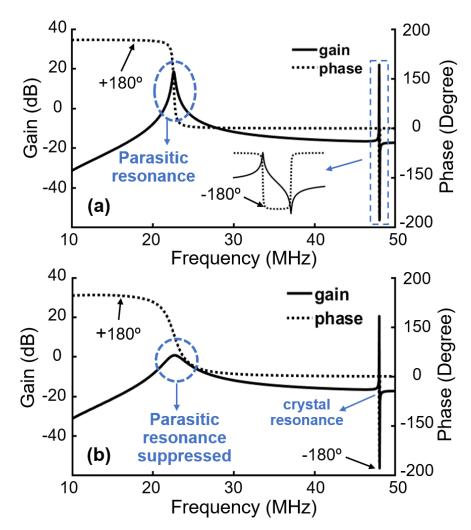

|   | 4.4            | Active In  | nductor                                                      | 78 |

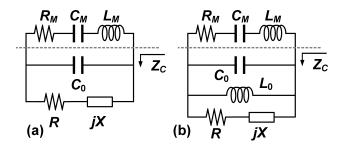

|   |                | 4.4.1 E    | Effects of $C_0$ on XO Start-up                              | 78 |

|   |                | 4.4.2 P    | Proposed $R_N$ Boosting Method                               | 79 |

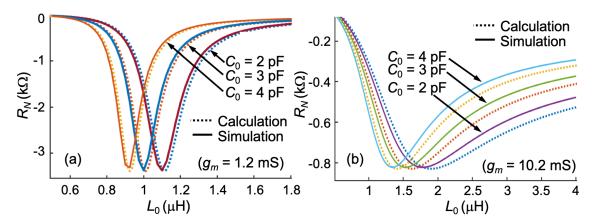

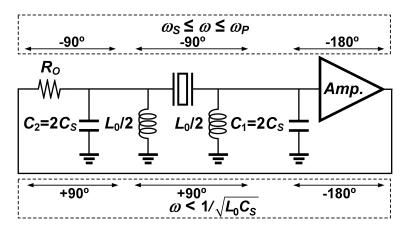

|   |                | 4.4.3 D    | Design Considerations for Active Inductor Implementation     | 81 |

|   |                | 4.4.4 C    | Circuit Implementation                                       | 83 |

|   | 4.5            | Measure    | ment Results                                                 | 87 |

|   | 4.6            | Conclusion | on                                                           | 93 |

| B | iblios         | raphy      |                                                              | 94 |

## LIST OF FIGURES

|            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

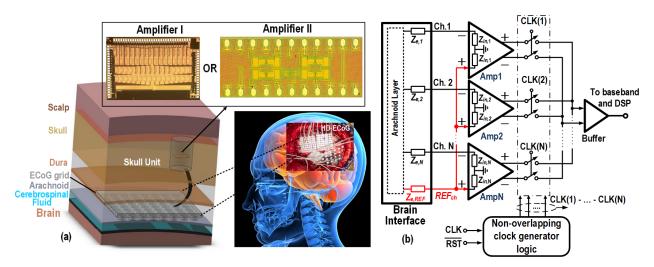

| 2.1        | Proposed AFE: (a) A cross-sectional view of the envisioned fully implantable BSA circuit, enclosed within a skull unit module. The BSA circuit is connected to a subdurally implanted high-density (HD)-ECoG electrode grid that senses brain signals. (b) Block diagram of the structure showing the brain interface electrodes with their corresponding impedances and BSA comprised of an array of fully differential amplifiers, serializer and buffer | 8    |

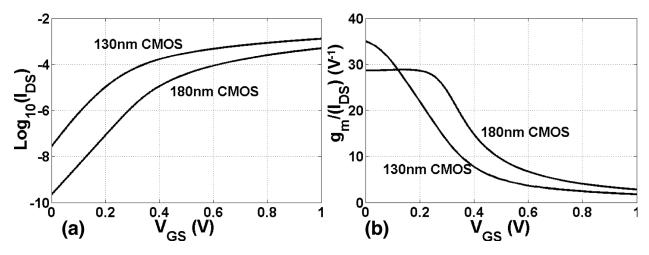

| 2.2        | (a) Drain-source current $(I_{DS})$ vs. gate-source voltage $(V_{GS})$ for the two technologies. (b) $g_m/I_{DS}$ vs. $V_{GS}$ for the two technologies. W/L = $20\mu m/2\mu m$ with 10 fingers, $V_{DS} = 1V$ for both transistors and body temperature of 37 is                                                                                                                                                                                          |      |

| 0.0        | considered for simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10   |

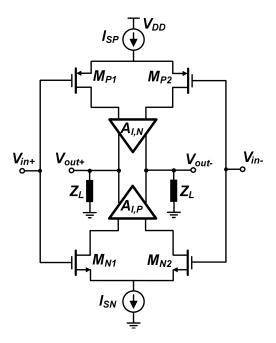

| 2.3<br>2.4 | Complementary input structure of the OTA used in Amplifier I (a) Amplifier I comprising a closed-loop amplifier with capacitive feedback and its die microphotograph, and (b) the schematic of the complementary                                                                                                                                                                                                                                           | 12   |

|            | NMOS-PMOS OTA [47]                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13   |

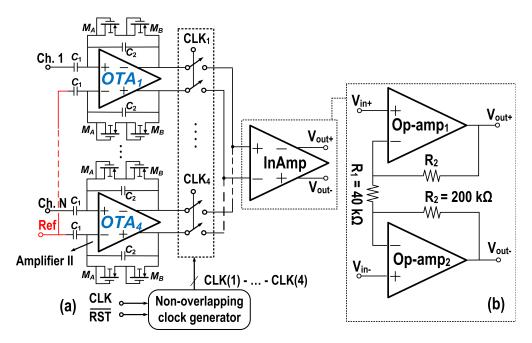

| 2.5        | BSA II: (a) overall topology, including 4 Amplifier II circuits and one InAmp                                                                                                                                                                                                                                                                                                                                                                              |      |

|            | (b) InAmp implementation                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16   |

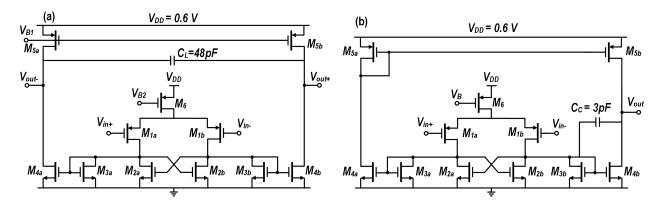

| 2.6        | (a) OTA schematic used in Amplifier II (b) Op-amp schematic used in InAmp                                                                                                                                                                                                                                                                                                                                                                                  | 17   |

| 2.7        | CMFB circuit used in Amplifier II                                                                                                                                                                                                                                                                                                                                                                                                                          | 20   |

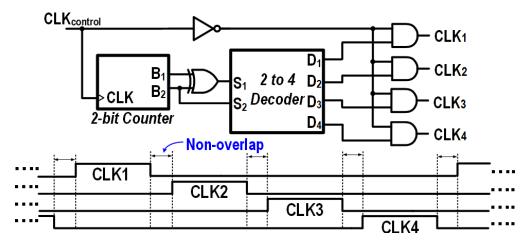

| 2.8        | Non-overlapping clock signals applied to serializer switches                                                                                                                                                                                                                                                                                                                                                                                               | 21   |

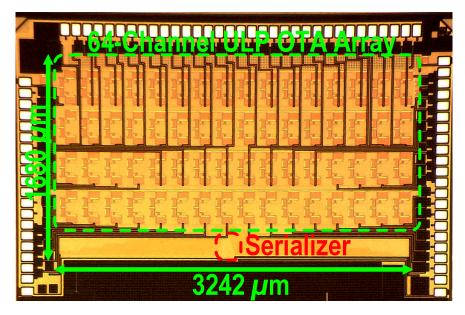

| 2.9        | Die microphotograph of BSA I with 64-channel amplifier array and serializer                                                                                                                                                                                                                                                                                                                                                                                | 2.2  |

| 0.10       | [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22   |

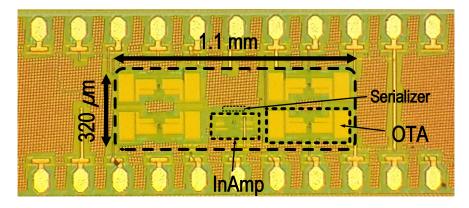

|            | Die microphotograph of the BSA II with 4-channel amplifier array and serialize                                                                                                                                                                                                                                                                                                                                                                             | r 22 |

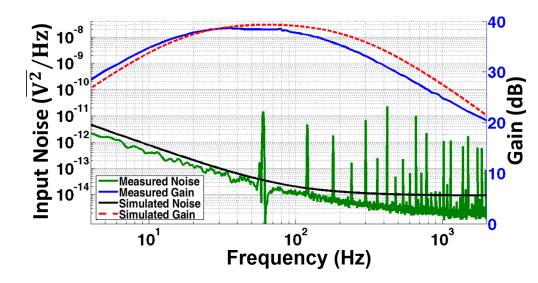

| 2.11       | Measured and simulated Amplifier I gain and noise responses. Note that the sharp peaks were due to 60 Hz harmonics on the unshielded cables [47]                                                                                                                                                                                                                                                                                                           | 23   |

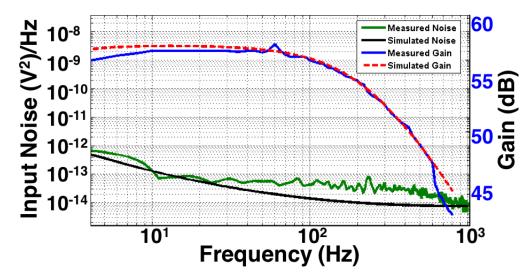

| 2 12       | Measured and simulated gain and noise responses for a single channel of BSA I                                                                                                                                                                                                                                                                                                                                                                              |      |

| 2.13       |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 21 |

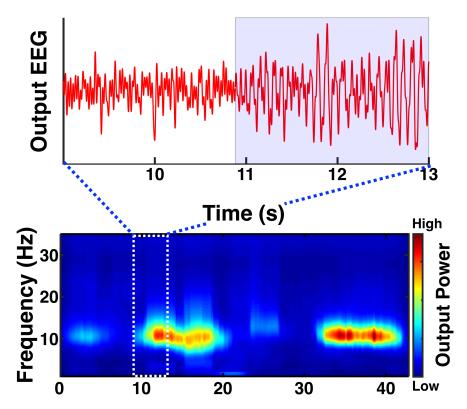

| 0          | Oz with 10 dB increase in the posterior dominant alpha rhythm (8–12 Hz)                                                                                                                                                                                                                                                                                                                                                                                    |      |

|            | amplitude when the subject closed his eyes (arrow). The subject closed his                                                                                                                                                                                                                                                                                                                                                                                 |      |

|            | eyes at 10 and 32 s and opened again at 20 and 42 s [47]                                                                                                                                                                                                                                                                                                                                                                                                   | 25   |

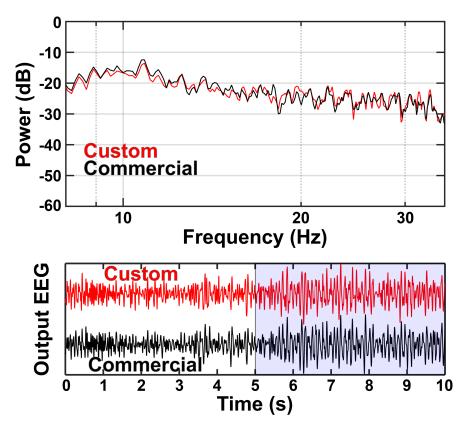

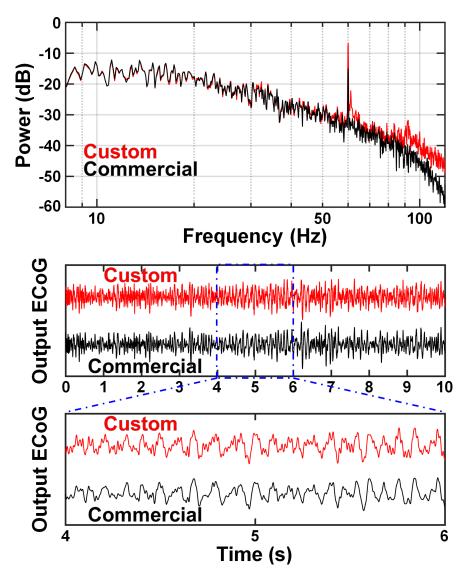

| 2.14       | Top: PSD of the BSA II (red) and commercial (black) bioamplifier from                                                                                                                                                                                                                                                                                                                                                                                      |      |

|            | 30 s of EEG data. Bottom: EEG $\alpha/\beta$ -band (8–35 Hz) time-series data from                                                                                                                                                                                                                                                                                                                                                                         |      |

|            | channel Oz (referenced to AFz) using the BSA II (red) and commercial (black)                                                                                                                                                                                                                                                                                                                                                                               |      |

|            | bioamplifiers. The subject was instructed to alternate between eyes-open                                                                                                                                                                                                                                                                                                                                                                                   |      |

|            | (white background) and eyes-closed (blue background)                                                                                                                                                                                                                                                                                                                                                                                                       | 26   |

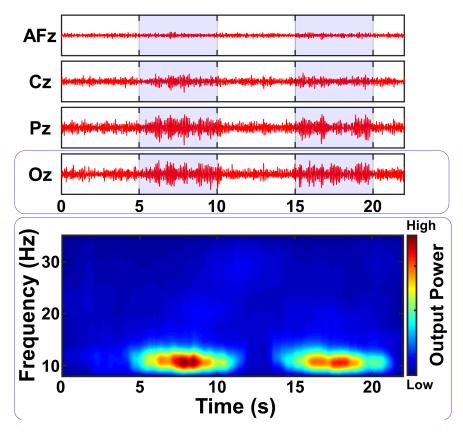

|      | BSA II EEG $\alpha/\beta$ -band (8–35 Hz) time-series data (top) and spectrogram (bottom) from channel AFz, Cz, Pz, and Oz (all referenced to AFz) as the subject was instructed to alternate between eyes-open (white background) and eyes-closed (blue background). The channel-multiplexed data from the custom designed IC were demultiplexed in software |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Electrodes 28 and 24 were used as the reference and ground, respectively $2$                                                                                                                                                                                                                                                                                  |

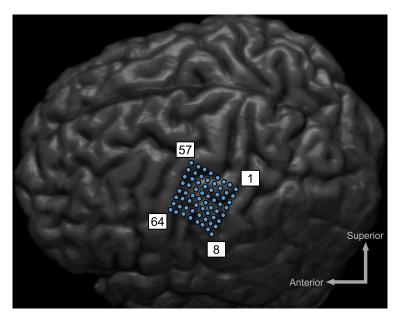

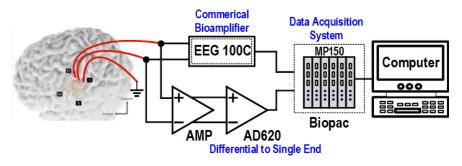

| 2.17 | In vivo ECoG measurement setup                                                                                                                                                                                                                                                                                                                                |

| 2.18 | Top: PSD of the BSA II (red) and commercial (black) bioamplifier from 30 s of ECoG data. Middle: Filtered (8–120 Hz) time-series data from the implanted ECoG grid with the BSa II (red) and commercial (black) bioamplifier. Bottom: Zoomed-in view of the recorded ECoG                                                                                     |

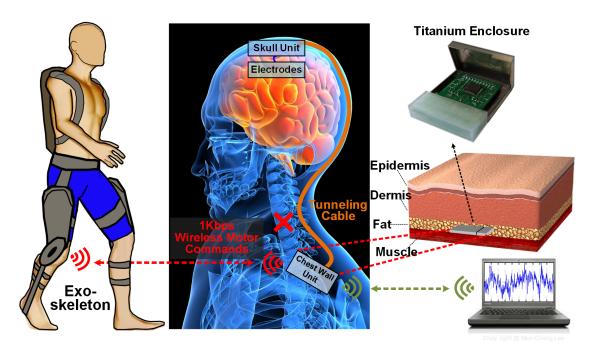

| 3.1  | Proposed fully-implantable BMI system for restoration of walking, with a signal acquisition front-end (skull unit) and signal processing and wireless communication modules (chest wall unit). This system bypasses the injured spinal cord and enables direct brain control of an exoskeleton                                                                |

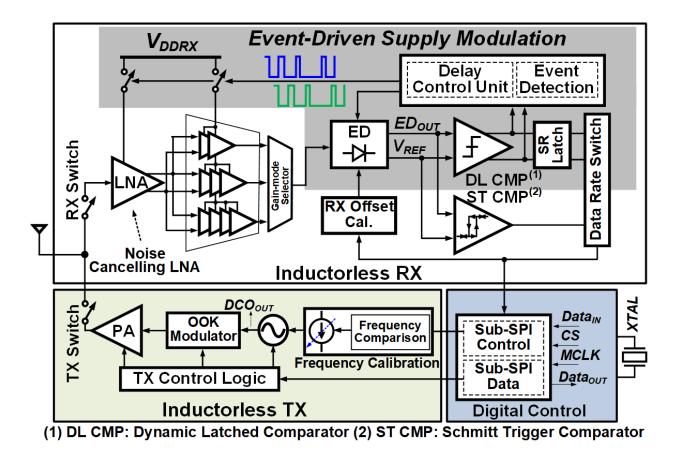

| 3.2  | The architecture of the proposed low-power OOK TRX                                                                                                                                                                                                                                                                                                            |

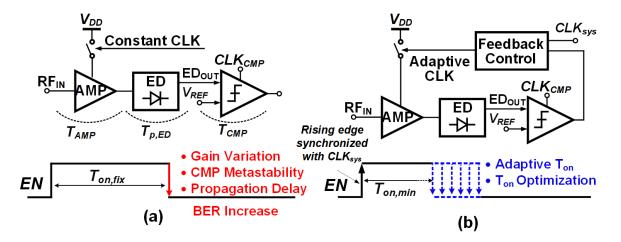

| 3.3  | (a) Envelope detector based receiver with a fixed pulse-width. (b) The proposed EDSM receiver with adaptive feedback control loop                                                                                                                                                                                                                             |

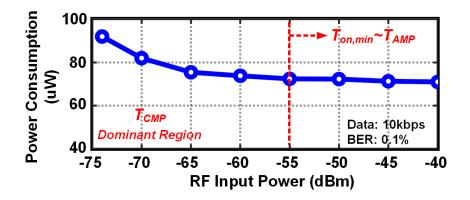

| 3.4  | Simulated RX power consumption vs. the input power                                                                                                                                                                                                                                                                                                            |

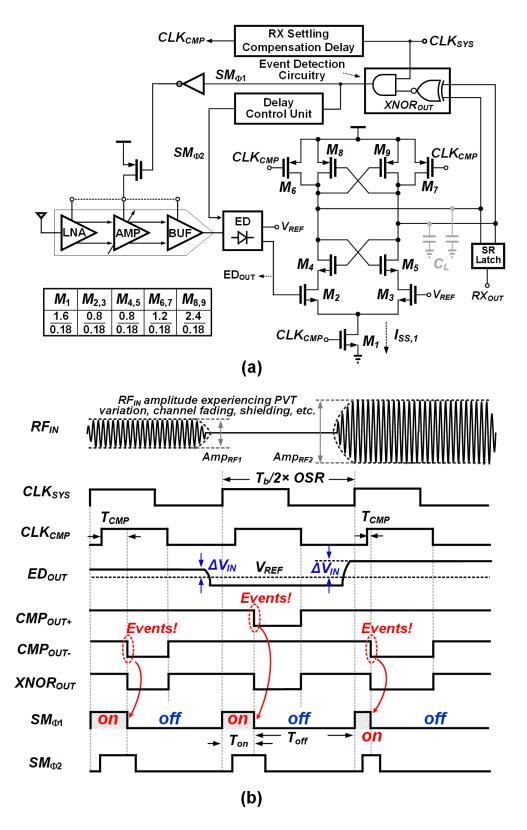

| 3.5  | (a) Event-Driven supply modulated RX schematic. (b) The timing diagram of EDSM RX                                                                                                                                                                                                                                                                             |

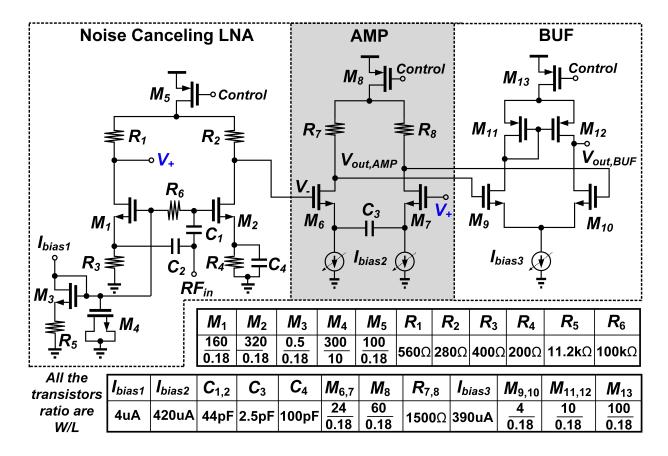

| 3.6  | The schematic of noise canceling low-noise amplifier, capacitively-degenerated                                                                                                                                                                                                                                                                                |

| 3.7  | cascaded gain stage unit and differential to single-ended buffer                                                                                                                                                                                                                                                                                              |

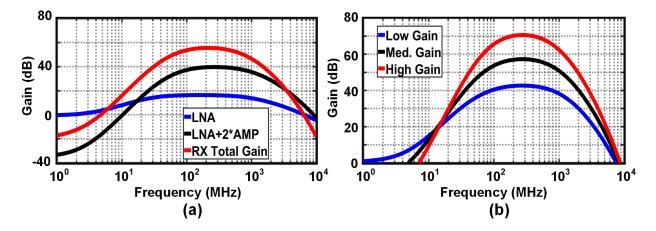

| 3.8  | gain curves of receiver in different gain-modes                                                                                                                                                                                                                                                                                                               |

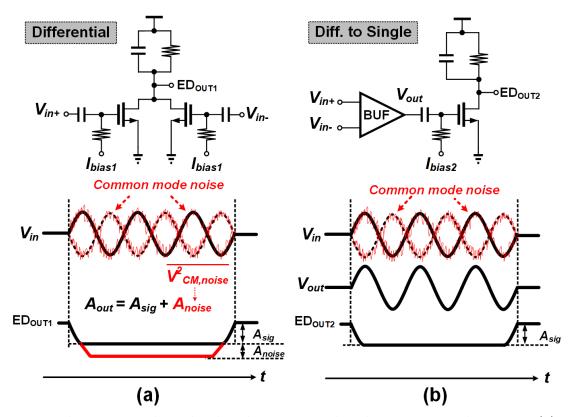

|      | active differential architecture. (b) differential-to-single first approach 4                                                                                                                                                                                                                                                                                 |

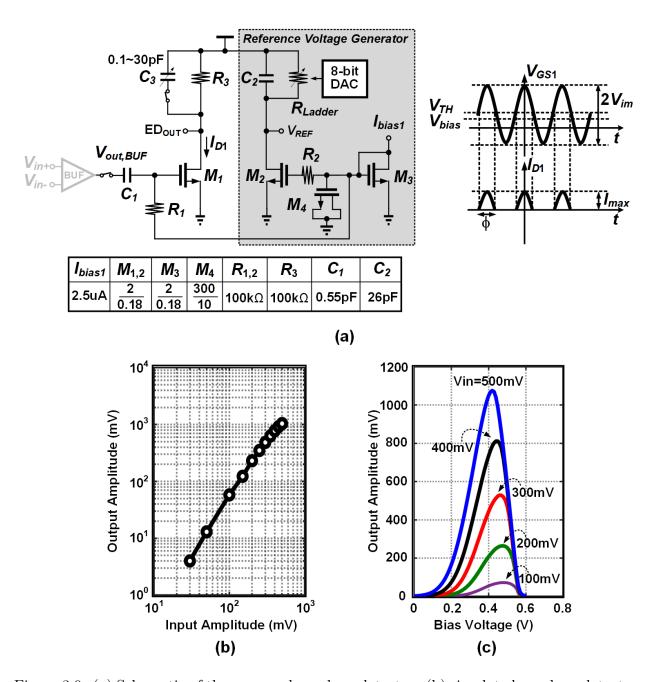

| 3.9  | (a) Schematic of the proposed envelope detector. (b) simulated envelope de-                                                                                                                                                                                                                                                                                   |

|      | tector output amplitude with different input amplitude. (c) simulated output                                                                                                                                                                                                                                                                                  |

|      | DC voltage vs. input bias voltage                                                                                                                                                                                                                                                                                                                             |

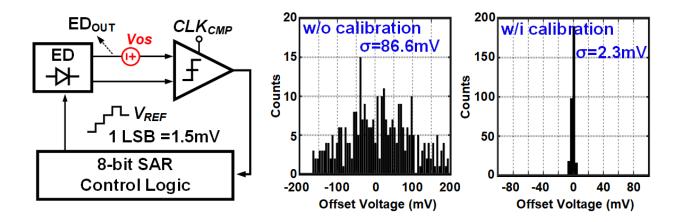

| 3.10 | Offset calibration system and Monte-Carlo simulation results                                                                                                                                                                                                                                                                                                  |

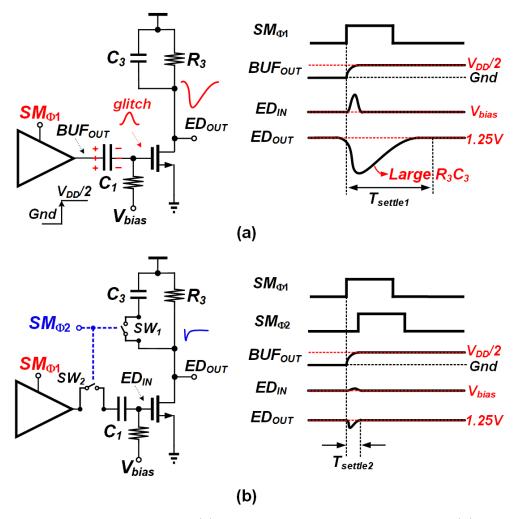

| 3.11 | The settling time of (a) conventional envelope detector. (b) the proposed                                                                                                                                                                                                                                                                                     |

|      | envelope detector with acceleration switch                                                                                                                                                                                                                                                                                                                    |

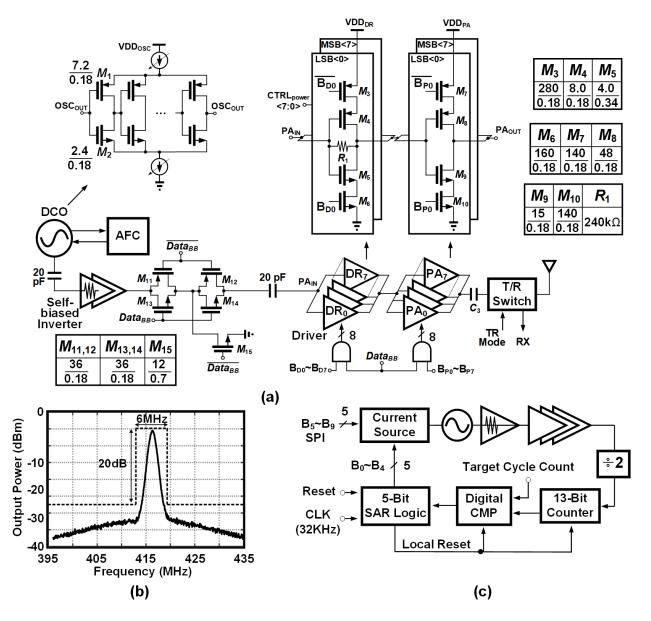

| 3.12 | (a) The schematic of proposed direct-modulation transmitter. (b) Measured                                                                                                                                                                                                                                                                                     |

|      | TX output power spectrum. (c) AFC block diagram                                                                                                                                                                                                                                                                                                               |

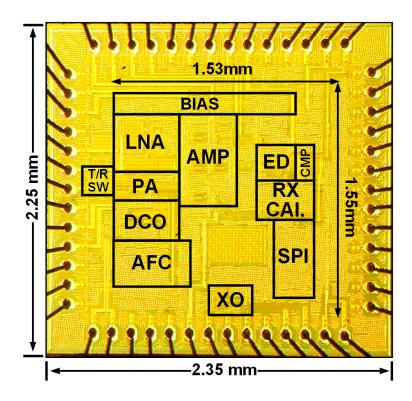

| 3.13 | Chip micrograph with main circuit blocks labeled                                                                                                                                                                                                                                                                                                              |

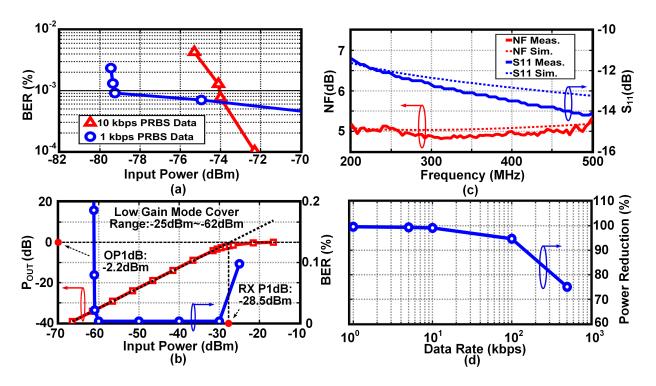

|      | RX electrical measurement results: (a) Measured BER with different data-                                                                                                                                                                                                                                                                                      |

|      | rate. (b) Linearity and BER measurement in low-gain mode. (c) Measured                                                                                                                                                                                                                                                                                        |

|      | S11 and NF. (d) Input data rate vs. power saving percentage 5                                                                                                                                                                                                                                                                                                 |

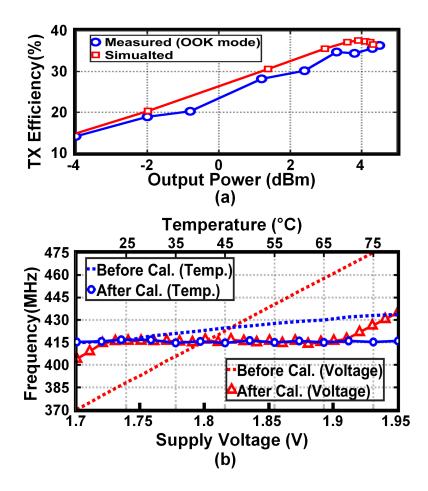

| 3.15 | (a) TX efficiency vs. output power. (b) Frequency variation before and after                                                                                                                                                                                                                                                                                  |

|      | using AFC                                                                                                                                                                                                                                                                                                                                                     |

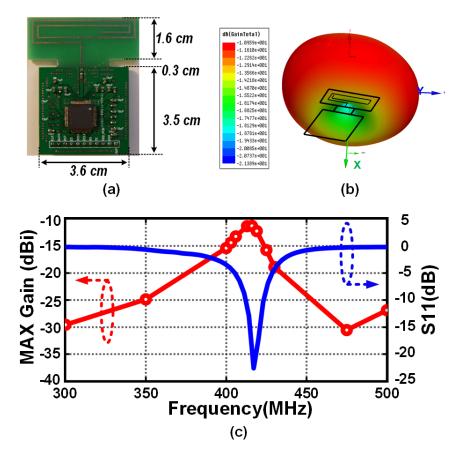

| 3.16         | (a) PCB including an on-board loop-antenna and TQFP packaged IC. (b) Simulated antenna radiation pattern. (c) Measured antenna gain and $S_{11}$ vs.                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.17         | frequency                                                                                                                                                                                                          |

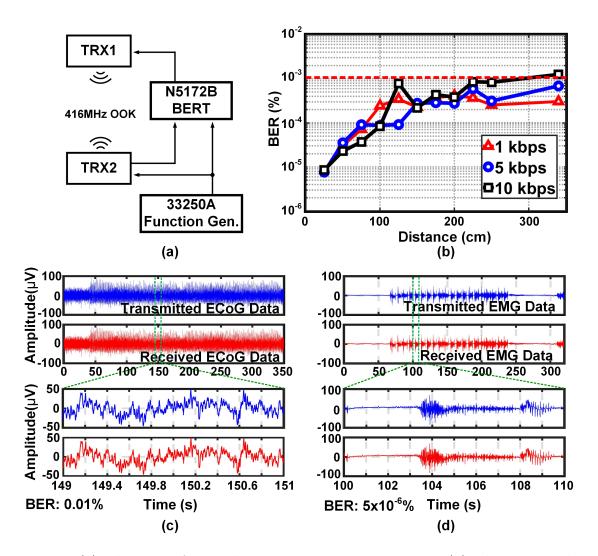

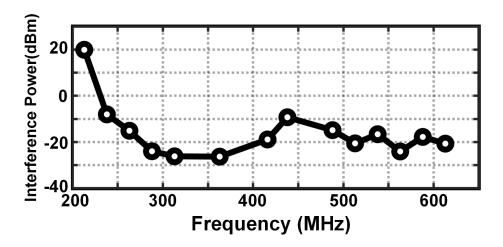

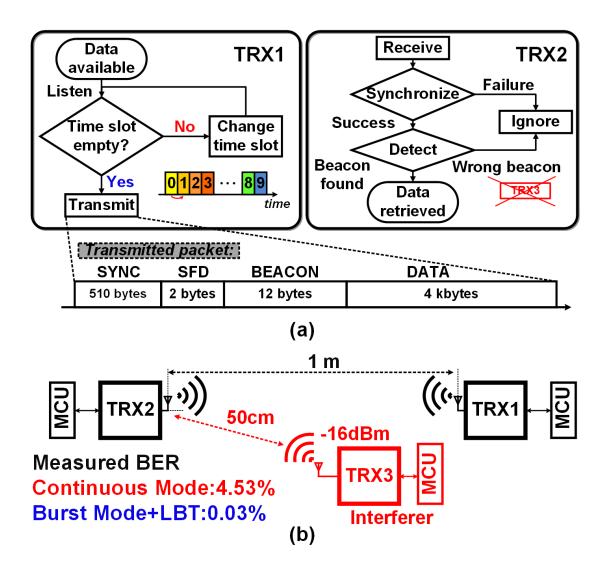

| 3.18<br>3.19 |                                                                                                                                                                                                                    |

| 3.20         | ·                                                                                                                                                                                                                  |

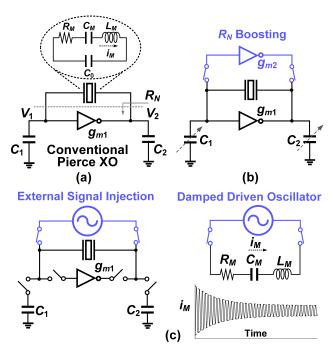

| 4.1          | (a) Pierce XO (b) boosting negative resistance by modifying capacitors and amplifier's gain (c) kick starting the oscillator using an external periodic source and oscillation amplitude behavior under injection. |

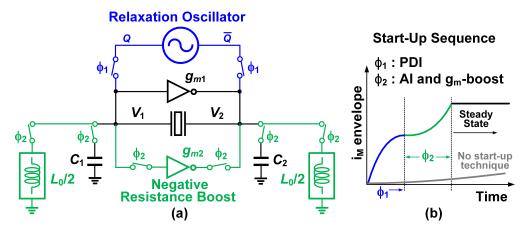

| 4.2          | (a) Proposed implementation of the fast starting XO (b) oscillation amplitude growth with the start-up aids and without them                                                                                       |

| 4.3          | Envelope of the $i_M$ for $\Delta \omega = 0.1$ and 0.3 Mrad/s                                                                                                                                                     |

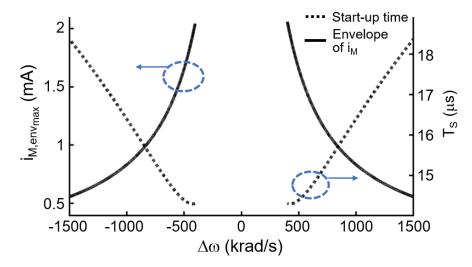

| 4.4          | Effect of injection frequency inaccuracy on maximum value of $i_{M,env}$ and overall $T_S$ , given injection stops at $t = T_{OPT}$ and $R_N = 50R_M$                                                              |

| 4.5          | Effect of injection timing inaccuracy on overall $T_S$ for the sample crystal parameters. $R_N$ is assumed to be $50R_M$                                                                                           |

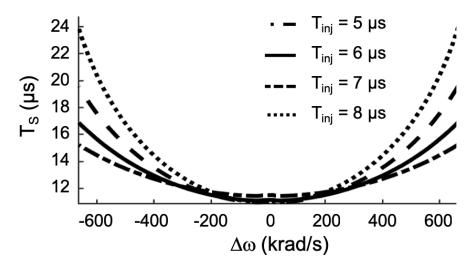

| 4.6<br>4.7   | RXO circuit implementation                                                                                                                                                                                         |

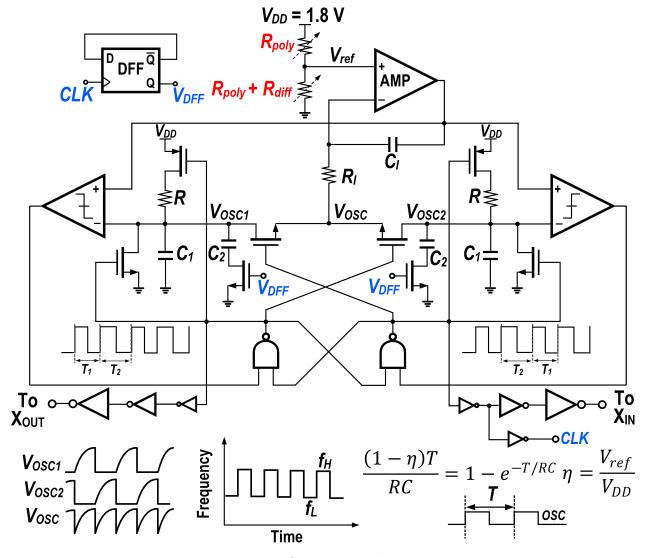

| 4.8<br>4.9   | One-port linear model of the XOs in (a) [121] and (b) this work $R_N$ at 48 MHz after addition of $L_0$ for amplifier's transconductance gain of (a) 1.2 mS and (b) 10.2 mS                                        |

| 4.10         | Simplified phase shift around the loop of Pierce XO at different frequency ranges                                                                                                                                  |

| 4.11         | (a) Tank frequency response after inclusion of $L_0$ with a quality factor of (a) 83 and (b) 11                                                                                                                    |

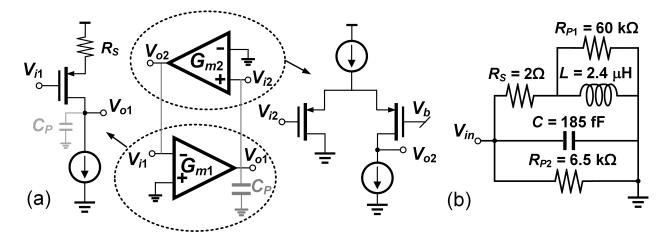

| 4.12         | AI implementation concept: (a) constructing positive and negative transcon-                                                                                                                                        |

|              | ductances (b) approximate model of the actual design                                                                                                                                                               |

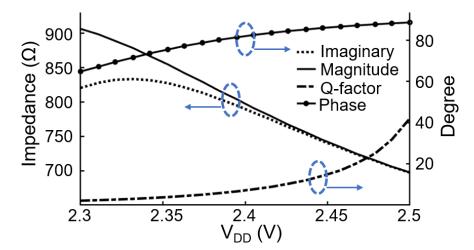

|              | AI input impedance characteristics at 48 MHz across supply                                                                                                                                                         |

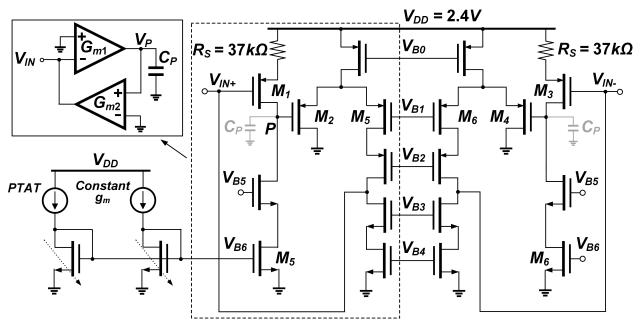

|              | AI circuit schematic                                                                                                                                                                                               |

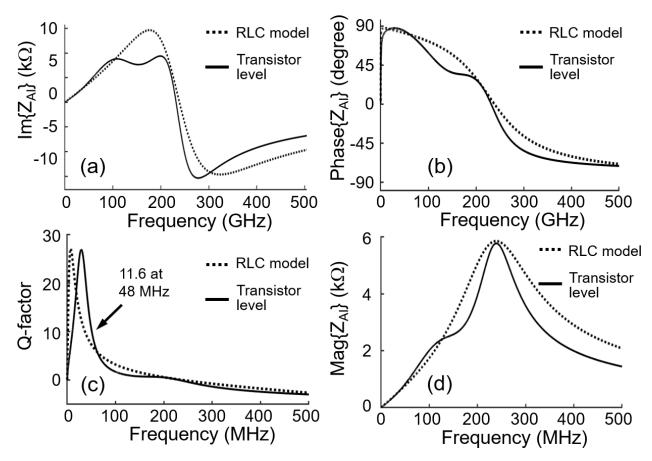

|              | AI reactance vs. frequency and its equivalent circuit model                                                                                                                                                        |

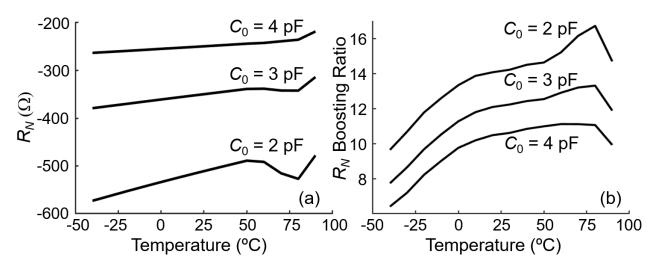

|              | Simulated temperature variations of (a) $R_N$ after addition of the AI and (b) $R_N$ boosting ratio                                                                                                                |

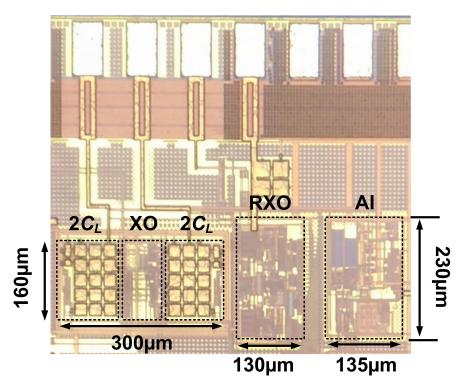

|              | Die micrograph of the prototype                                                                                                                                                                                    |

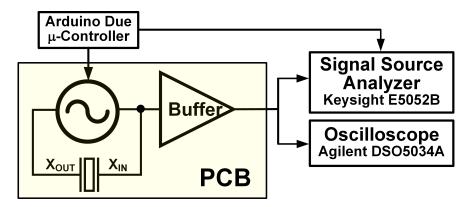

|              | Measurement setup                                                                                                                                                                                                  |

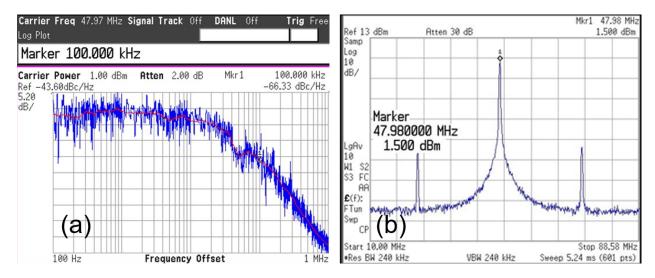

| 4.19         | (a) Measured RXO phase noise and (b) power spectral density                                                                                                                                                        |

| 4.20 | RXO start-up time                                                              | 89 |

|------|--------------------------------------------------------------------------------|----|

| 4.21 | $T_S$ improvement using AI only for a large steady-state oscillation amplitude |    |

|      | of 0.95 V                                                                      | 89 |

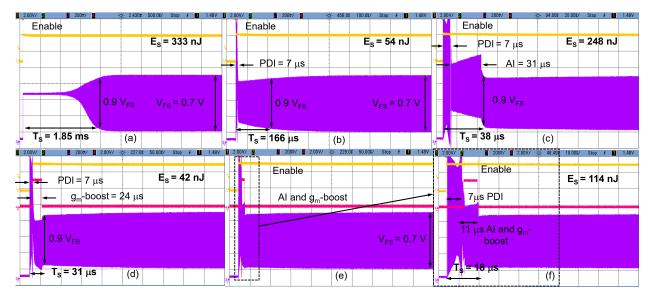

| 4.22 | Start-up behavior of XO with (a) no kick-start technique, (b) PDI only, (c)    |    |

|      | PDI and AI techniques (d) PDI and $g_m$ -boost, (e,f) all techniques combined. | 90 |

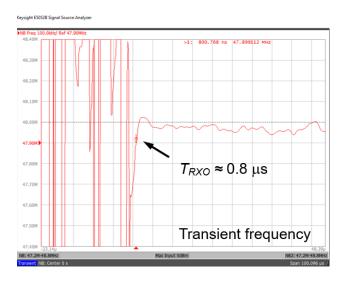

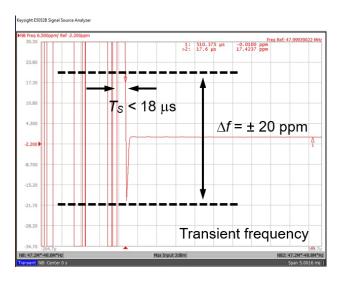

| 4.23 | Settling of XO oscillation frequency                                           | 91 |

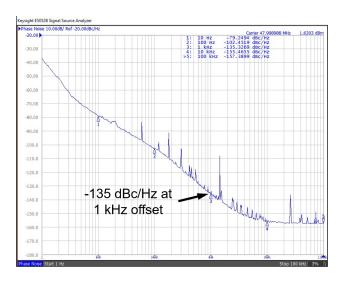

| 4.24 | Measured phase noise                                                           | 91 |

## LIST OF TABLES

|     |                                                   | Page |

|-----|---------------------------------------------------|------|

| 2.1 | Amplifier I device sizes and operating points     | . 14 |

| 2.2 | Amplifier II device sizes and operating points    | . 19 |

|     |                                                   |      |

| 2.4 | Comparison and performance summary of AFEs        | . 29 |

| 3.1 | Measured Transceiver Power Consumption Breakdown  | . 53 |

| 3.2 | Receiver Performance Comparison                   | . 60 |

| 3.3 | Transmitter Performance Comparison                | . 61 |

| 4.1 | Measurement summary and Comparison with prior art | . 92 |

#### ACKNOWLEDGMENTS

I would like to thank my advisor Professor Payam Heydari who always pushed me out of my comfort zone to improve myself and my technical knowledge. Without his technical support, mentorship and financial assistance over the years, this work would not have been possible.

I thank professor Zoran Nenadic and An Do who have supervised my work closely since the beginning of my graduate studies, provided guidance and served in my committee. I was fortunate to be given the opportunity to participate in the multi-disciplinary project which was initiated by collaboration between Nanoscale Communication Integrated Circuits (NCIC) labs lead by professor Heydari and Center for BioMedical Signal Processing and Computation (CBMSPC) lead by Professor Nenadic.

I sincerely thank my friends at NCIC labs and CBMSPC for their support and collaboration in the projects that constitutes this thesis. They are Mao-Cheng Lee for development of the receiver part of the low power transceiver, Omid Malekzadeh-Arasteh and Akshay Mahajan for helping in layout and measurements of ultra low-power amplifier arrays, Haoran Pu for designing the SPI interface circuitry of the crystal oscillator chip, and my colleagues at CBMSPC Dr. Po Wang and Dr. Collin McCrimmon for their assistance in biological measurements.

I also acknowledge National Science Foundation for the financial support under grants #1446908 and #1646275. I thank TowerJazz and MOSIS for providing chip fabrication and Keysight Technologies (especially Dave Huh) for providing measurement equipment.

Permission to use copyrighted material in this manuscript has been granted by Institute of Electrical and Electronics Engineers (IEEE).

#### CURRICULUM VITAE

#### Alireza Karimi Bidhendi

#### **EDUCATION**

Doctor of Philosophy in Electrical Engineering

University of California, Irvine

Master of Science in Electrical Engineering

University of California, Irvine

Bachelor of Science in Electrical Engineering

Sharif University of Technology

2019

Irvine, California

Irvine, California

2013

Sharif University of Technology

Tehran, Iran

#### RESEARCH EXPERIENCE

Graduate Research Assistant

University of California, Irvine

2013–2019

Irvine, California

#### TEACHING EXPERIENCE

Teaching Assistant

University of California, Irvine

2014–2019

Irvine, California

#### PROFESSIONAL EXPERIENCE

Apple Inc.

Apple Inc.

San Diego, California

Engineering Intern

Indie Semiconductor

Engineering Intern

AyDeeKay LLC

Laguna Niquel, California

#### REFEREED JOURNAL PUBLICATIONS

- A. Karimi-Bidhendi, H. Pu, and P. Heydari, "Study and Design of a Fast Start-up Crystal Oscillator Using Precise Dithered Injection and Active Inductance," *IEEE J. Solid-State Circuits*, vol. 54, 2019.

- M. Lee, A. Karimi-Bidhendi, O. Malekzadeh-Arasteh, P. T. Wang, A. H. Do, Z. Nenadic, and P. Heydari., "A CMOS MedRadio Transceiver with Supply-Modulated Power Saving Technique for an Implantable Brain-Machine Interface System," *IEEE J. Solid-State Circuits*, vol. 54, no. 6, pp. 1541-1552, June 2019.

- A. Karimi-Bidhendi, H. Mohammadnezhad, M. M. Green, and P. Heydari, "A Silicon-Based Low-Power Broadband Transimpedance Amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 2, pp. 498-505, Feb. 2018.

- A. Karimi-Bidhendi, O. Malekzadeh-Arasteh, M. Lee, C. M. McCrimmon, P. T. Wang, A. Mahajan, C. Y. Liu, Z. Nenadic, A. H. Do, and P. Heydari, "CMOS Ultralow Power Brain Signal Acquisition Front-Ends: Design and Human Testing," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 5, pp. 1111-1122, Oct. 2017.

- C. McCrimmon, J. L. Fu, M. Wang, L. S. Lopes, P. T. Wang, A. Karimi-Bidhendi, C. Y. Liu, P. Heydari, Z. Nenadic, and A. H. Do, "Performance Assessment of a Custom, Portable and Low-Cost Brain-Computer Interface Platform," *IEEE Trans. Biomed. Eng.*, vol. 64, no. 10, pp. 2313-2320, Oct. 2017.

#### REFEREED CONFERENCE PUBLICATIONS

- J. Lim, P. T. Wang, A. Karimi-Bidhendi, O. Malekzadeh-Arasteh, S. J. Shaw, M. Armacost, H. Gong, C. Y. Liu, P. Heydari, A. H. Do, and Z. Nenadic, "Characterization of stimulation artifact behavior in simultaneous electrocorticography grid stimulation and recording," in *IEEE Eng. Med. Biol. Soc.*, Honolulu, HI, 2018, pp. 4748-4751.

- M. Lee, A. Karimi-Bidhendi, O. Malekzadeh-Arasteh, P. T. Wang, Z. Nenadic, A. H. Do, P. Heydari, "A CMOS Inductorless MedRadio OOK Transceiver With a  $42\mu$ W Event-Driven Supply-Modulated RX and a 14% Efficiency TX for Medical Implants," in *IEEE Custom Integr. Circuits Conf.*, San Diego, CA, 2018.

- P. T. Wang, K. Gandasetiawan, C. M. McCrimmon, A. Karimi-Bidhendi, C. Y. Liu, P. Heydari, Z. Nenadic, and A. H. Do, "Feasibility of an Ultra-Low Power Digital Signal Processor Platform as a Basis for a Fully Implantable Brain-Computer Interface System," in *IEEE Eng. Med. Biol. Soc.*, Orlando, FL, 2016, pp. 4491-4494.

- C. M. McCrimmon, M. Wang, L. S. Lopes, P. T. Wang, A. Karimi-Bidhendi, C. Y. Liu, P.

- Heydari, Z. Nenadic, and A. H. Do, "A Small, Portable, Battery-Powered Brain-Computer Interface System for Motor Rehabilitation," in *IEEE Eng. Med. Biol. Soc.*, Orlando, FL, 2016, pp. 2776-2779.

- C. M. McCrimmon, M. Wang, L. S. Lopes, P. T. Wang, A. Karimi-Bidhendi, C. Y. Liu, P. Heydari, Z. Nenadic, and A. H. Do, "A Portable, Low-Cost BCI for Stroke Rehabilitation," *BCI Meeting*, 2016.

- A. Mahajan, A. Karimi Bidhendi, P. T. Wang, C. M. McCrimmon, C. Y. Liu, Z. Nenadic, A. H. Do, and P. Heydari, "A 64-Channel Ultra-Low Power Bioelectric Signal Acquisition System for Brain-Computer Interface," in *IEEE Biomed. Circuits Syst. Conf.*, Atlanta, GA, 2015, pp.1-4.

- H. Mohammadnezhad, A. Karimi Bidhendi, M. M. Green, and P. Heydari, "A Low-Power BiCMOS 50 Gbps Gm-Boosted Dual-Feedback Transimpedance Amplifier," in *IEEE Bipolar/BiCMOS Circuits Tech. Meeting*, Boston, MA, 2015, pp. 161-164.

#### ABSTRACT OF THE DISSERTATION

Low-Power Integrated Circuits For Biomedical Applications

By

Alireza Karimi Bidhendi

Doctor of Philosophy in Electrical Engineering

University of California, Irvine, 2019

Professor Payam Heydari, Chair

With thousands new cases of spinal cord injury reported everyday, many people suffer from paralysis and loss of sensation in both legs. Beside the healthcare costs, such a state severely deteriorates the patients' quality of life and may even lead to additional medical conditions. Therefore, there is a growing need for cyber-physical systems to restore the walking ability through bypassing the damaged spinal cord. This goal can be achieved by monitoring and processing patient's brain signals to enable brain-directed control of prosthetic legs. Among several existing methods to record brain signals, electrocorticography (ECoG) has gained popularity due to being robust to motion artifacts, having high spatial resolution and signal to noise ratio, being moderately invasive and the possibility of chronic implantation of recording grids with no or minor scar tissue formation. The latest property is of particular importance for the whole system to be a viable fully implantable solution. Furthermore, the implanted system has to operate independently with no or minimal need of external hardware (e.g. a bulky personal computer) to be individually and socially accepted.

To implement a fully implantable system, low-power and miniaturized electronics are needed to reduced heat generation, increase battery life-time and be minimally intrusive. These requirements indicate that many of the system's components should be custom-designed to integrated as much functionality as possible in a given real estate. This thesis presents

silicon tested prototypes of several building blocks for the envisioned system, namely, ultra low-power brain signal acquisition front-ends, a low-power and inductorless MedRadio transceiver, and a fast start-up crystal oscillator. Brain signal acquisition front-ends provide low noise amplification of weak ECoG biosignals. MedRadio transceiver enables communication between the implant and end effectors or base station (e.g. prosthetic legs or desktop computer). Crystal oscillator generates the reference signal for other system's components such as analog to digital converter. Novel techniques to improve important performance parameters (power consumption, low noise operation and interference resilience) have been introduced. Electrical, *in-vitro* and *in-vivo* experimental measurements have verified the functionality and performance of each design.

## Chapter 1

## Introduction

Brain-Computer Interface (BCI) systems have emerged as a multidisciplinary field with vast potentials and applications. BCI systems enable communication between brain and external devices, mainly computers to analyze and process the received time series data for multiple purposes including control of a prosthetic limb [1]. Among these applications, restoring the gait functions in patients suffering from spinal cord injury (SCI) has gained attention recently. This is due to the fact that there is no biological treatments available and the independence, quality of life and financial conditions of those affected are severely degraded due to SCI.

Despite the advances in BCI algorithms and signal processing, implementation of a miniature, portable, aesthetically acceptable system with long battery life remains a challenge. Recent works have proposed implementations using off-the-shelf components to evaluate the feasibility and operation of such systems [2–4]. However, any proposed solution to be clinically viable and widely accepted by the public need to have several important features: It has to be miniature in size, portable, low-power (to elongate battery life time and has low heat generation) and very high degree of accuracy to minimize safety risks.

Integrated circuits revolutionized the electronics and communication precisely because of their miniature scale that has made signal processing and significant computation power possible for consumer usage. This miniaturization also made circuits operate at increasingly higher speeds [8–10], enabling development of complex transceiver architectures [11–21] and wireless networks [5–7].

This work presents design, implementation and experimental results of three building blocks of the BCI system in complementary metal-oxide-semiconductor (CMOS) processes. Each design encompasses novel techniques to reduce power consumption, improve speed and data throughput, and provide low-noise operation. The summary of this thesis is as follows:

In the first chapter, two brain signal acquisition (BSA) front-ends incorporating two CMOS ultra-low power low noise amplifier arrays and serializers operating in MOSFET weak inversion region are presented [22]. To boost the amplifier's gain for a given current budget, cross-coupled-pair active load topology is used in the first stages of these two amplifiers. These two BSA front-ends are fabricated in 130 nm and 180 nm CMOS processes, occupying 5.45 mm² and 0.352 mm² of die areas, respectively (excluding pad rings). The CMOS 130 nm amplifier array is comprised of 64 elements, where each amplifier element consumes 0.216  $\mu$ W from 0.4 V supply, has input-referred noise voltage (IRNoise) of 2.19  $\mu$ V<sub>RMS</sub> corresponding to a power efficiency factor (PEF) of 11.7 and occupies 0.044 mm² of die area. The CMOS 180 nm amplifier array employs 4 elements, where each element consumes 0.69  $\mu$ W from 0.6 V supply with IRNoise of 2.3  $\mu$ V<sub>RMS</sub> (corresponding to a PEF of 31.3) and 0.051 mm² of die area. Non-invasive electroencephalographic (EEG) and invasive electrocorticographic (ECoG) signals were recorded real-time directly on able-bodied human subjects, showing feasibility of using these analog front-ends for future fully implantable brain signal acquisition and brain computer interface systems.

A MedRadio 413–419 MHz inductorless transceiver (TRX) for an implantable brain-machine interface (BMI) in a 180 nm CMOS process is discussed in the second chapter [23]. Occu-

pying 5.29 mm<sup>2</sup> of die area (including pad ring), this on-off-keying (OOK) TRX employs a non-coherent direct-detection receiver (RX), which exhibits a measured in-band noise figure (NF) of 4.9 dB and  $S_{11}$  of -13.5 dB. An event-driven supply modulation (EDSM) technique is introduced to dramatically lower the RX power consumption. Incorporating an adaptive feedback loop, this RX consumes  $42/92~\mu W$  power from 1.8 V supply at  $1/10~\rm kbps$  datarates, achieving  $-79/-74~\rm dBm$  sensitivities for 0.1% bit-error-rate (BER). The TX employs a current-starved ring oscillator with an automatic frequency calibration loop, covering 9% supply-voltage variation and 15–78°C temperature range which guarantees operation within the emission mask. The direct-modulation TX achieves 14% efficiency for a random OOK data sequence at  $-4~\rm dBm$  output power. Wireless testing over a 350 cm distance accounting for bio-signal data transfer, multi-user coexistence, and *in-vitro* phantom measurement results are demonstrated.

The last chapter presents a theoretical study and design of two techniques used to reduce start-up time  $(T_S)$  and energy  $(E_S)$  of Pierce crystal oscillator (XO) [24]. An analytical study of precise injection on a crystal resonator is introduced, and based on this study, a relaxation oscillator with a dithered frequency is designed. Next, a study of negative resistance of XO's active circuitry and a method to boost its value beyond the limit set by crystal static capacitor are presented. A gyrator-C active inductor with high linearity is developed to accelerate the start-up process by boosting the negative resistance. A prototype integrating these techniques is fabricated in a 180 nm CMOS process, and shows a significant improvement compared to prior art. Specifically,  $T_S$  and  $E_S$  are reduced by 102.7× and 2.9×, compared to the XO start-up with no assisting circuitry, to 18  $\mu$ s and 114.5 nJ for a 48 MHz XO across -40–90°C temperature range. The measured steady-state power and phase noise of the XO are 180  $\mu$ W and -135 dBc/Hz at 1 kHz offset frequency.

## Chapter 2

# Ultra Low-Power Brain Signal Acquisition Front-Ends

#### 2.1 Introduction

It is estimated that every year there are ~500,000 new cases of spinal cord injury (SCI) worldwide [25]. This condition substantially decreases independence and quality of life of those affected, and the resulting disability and comorbidities pose a significant economic burden on the individual as well as on society. Since there are no satisfactory means to restore motor function after SCI, novel approaches to address this problem are needed. Bypassing the damaged spinal cord by means of a brain-computer interface (BCI), which enables direct brain control of prostheses, constitutes one such approach. Non-invasive electroencephalogram (EEG)-based BCIs have the capacity to restore basic ambulation after SCI [26], [27], although their applicability is limited by the low information content (i.e., limited bandwidth and low spatial resolution) of EEG signals. Invasive BCIs, on the other hand, have enabled control of multi-degree-of-freedom robotic prostheses [28]. However, they utilize bulky and

power-hungry general-purpose recording hardware, and rely on skull-protruding electronic components. Furthermore, these systems typically employ intracortically implanted microelectrode arrays, which can trigger foreign body responses such as inflammation and scarring, ultimately leading to failure of the system within months to few years [29]. These factors represent a serious obstacle to a widespread adoption of invasive BCI technology.

These problems may be addressed by developing a fully implantable BCI system that uses highly stable electrocorticogram (ECoG) signals [30]. Such a BCI system is envisioned to consist of ECoG electrodes, amplifiers, a processor, and a wireless module to control and communicate with output devices (e.g., prostheses), all implemented in a miniaturized form factor and operating in a low-power regime in order to facilitate permanent implantation. Since ECoG electrodes are placed above the arachnoid layer without breaching the neuronal tissue, ECoG signals have long-term stability [30, 31], while providing the spatiotemporal resolution necessary for high-performance BCI applications [32], [33]. In particular, studies have shown that the ECoG high- $\gamma$  frequency band (70–120 Hz) exhibits spatially localized amplitude modulation that is correlated with individual's physical movements [34], and this feature has been used to decode arm [35] and finger movements [36]. Chronic in vivo recording of ECoG signals has been used for neurological treatment. The Medtronic Activa PC+S system [37, 38], was used in patients having Parkinson disease with ECoG electrode strips implanted over the motor cortex and depth electrodes in the subthalamic nucleus [39]. Chronic recordings from these areas were used to study the association between gamma band oscillations and dyskinesia. The Activa PC+S system was also used for recording signals from ECoG electrode strips over the motor cortex of a patient with amyotrophic lateral sclerosis (ALS) to facilitate BCI-control of a virtual keyboard [40]. Finally, as shown in prior art, a fully implantable system eliminates the need for bulky skull-protruding components, often employed in the state-of-the-art invasive BCIs, as well as bulky recording hardware and external computers.

There has been extensive research on low-power amplifier and amplifier array designs for neural signal sensing applications, which vary substantially in frequency and dynamic range. For example, in [41], the authors present a folded-cascode operational transconductance amplifier (OTA) using current-splitting and current-scaling techniques with a cascaded 6th-order band-pass filter for detecting epileptic fast ripples between 250 and 500 Hz. The stack of 4 transistors and large degeneration resistors in this design increase the required supply voltage to accommodate sufficient output voltage headroom. In [42], a closed-loop neural recording amplifier has been developed that utilizes a T-network in its feedback path in order to achieve high input impedance and common-mode rejection ratio (CMRR) within a small chip area. The authors argued that the T-network in the feedback path is useful when the routing area overhead, crosstalk and input-referred noise (IRNoise) do not dominate the performance [42].

Most of the previously developed neural sensing amplifiers focus on EEG or single-unit recordings. Consequently, their designs are not optimal for use in other recording modalities, such as ECoG. Moreover, a few studies that exist with analog front-end (AFE) designs for ECoG recording lack in vivo experimental validation in humans. For example, [43] presents a 32-channel integrated circuit (IC) for ECoG recording, followed by in vivo measurements in a rat. The power consumption of this system is too high, making it unsuitable for human ECoG signal acquisition, especially in a fully implantable form. In [44], an ECoG/EEG IC has been introduced which records signals in 4 different sub-bands as opposed to simultaneously capturing the complete ECoG spectrum. This IC has been validated by comparing the measurements of a pre-recorded human ECoG signal with those generated by a model of the signal acquisition chain. This approach, however, does not accurately capture the IC's interface with the body (e.g. 60 Hz noise), which may significantly affect the performance. When tested in an awake monkey, the signals simultaneously measured by this IC and those acquired using a commercial system showed only modest correlations in  $\alpha$  (8–12 Hz) and high- $\gamma$  (70–120 Hz) bands. This can be explained by the dominating effects of flicker and

thermal noise at these frequencies. On the other hand, the signals in the  $\beta$  (13–35 Hz) and  $low-\gamma$  (35–70 Hz) bands were only qualitatively compared with no correlation coefficients reported. Recent work [45] reports on an AFE consuming 1.08  $\mu$ W of power per channel, which is achieved by narrowing the AFE bandwidth and filtering out the noise. A potential problem with this approach may lie in the high sensitivity of the designed  $G_mC$  filters to process variation. The proposed AFE has been tested in its ability to reproduce pre-recorded ECoG data and acquire ECoG signals in vivo from an anesthetized monkey. However, human testing and direct comparison of recorded signals to those acquired with a commercial-grade system have not been performed. Finally, the work in [46] presents a 64-channel wireless micro ECoG recording system with the front-end achieving a power-efficiency factor (PEF) that is  $3 \times$  smaller than the state-of-the-art. In vivo measurements from an anesthetized rodent show the power increase with respect to the pre-sedation state in  $\delta$  (1-4 Hz) and  $\theta$ (4-7 Hz) bands, but very little change in BCI-relevant frequency bands. Furthermore, none of the above systems were tested in a hospital environment, which is typically characterized by extremely hostile ambient noise and interference conditions. In summary, while the development of these architectures has been inspired by human BCI applications, their in vivo testing in humans and comparison to conventionally acquired ECoG signals are conspicuously missing.

This paper presents the design, experimental validation, and comparative study of two CMOS ultra-low power (ULP) amplifier array and serialization circuitries that constitute core building blocks of two brain signal acquisition (BSA) front-ends. These BSA front-ends can act as the basis for a future, fully implantable ECoG-based BCI system (Fig. 2.1(a)). The AFE IC will be housed within an enclosure, called the skull unit, to be surgically implanted into the skull [47]. Other building blocks required to develop a complete ECoG-based BCI, e.g., transceiver, power management unit and digital signal processor are intended to be placed in another unit away from the patient's brain. This approach imposes less health hazards for the patient as well as more practical system specifications for a portable, user-

Figure 2.1: Proposed AFE: (a) A cross-sectional view of the envisioned fully implantable BSA circuit, enclosed within a skull unit module. The BSA circuit is connected to a subdurally implanted high-density (HD)-ECoG electrode grid that senses brain signals. (b) Block diagram of the structure showing the brain interface electrodes with their corresponding impedances and BSA comprised of an array of fully differential amplifiers, serializer and buffer.

friendly solution. All circuits in this work are designed to operate in the weak inversion (WI) region to maximize power efficiency and minimize heat dissipation, while maintaining high gain and low noise operation. *In vivo* human measurements and objective validation against a commercial bioamplifier are done in (1) a human subject using non-invasive EEG cap, and (2) a human subject with subdurally implanted high-density ECoG grid.

The paper is organized as follows. Section 2.2 presents the proposed AFE for recording ECoG signals and identifies the criteria and required specifications of the building blocks for designing the system. Sections 2.3 and 2.4 discuss the design and implementation of the two BSA front-ends, BSA I and BSA II, respectively. Section 3.6 illustrates the electrical and neural measurement results of both front-ends. Finally, Section 3.7 presents concluding remarks and potential extensions of this work.

#### 2.2 Proposed System Architecture

Responsible for sensing and amplification of microvolt-level brain signals, the amplifier array IC is a critical building block of a BSA front-end. To be employed as a fully implantable device, the signal acquisition front-end should be small in size and consume micro-watt level of power. The system-level diagram of the proposed AFE is shown in Fig. 2.1(b) [48]. The AFE IC includes fully differential amplifiers, a serializer, and an output buffer all biased in the WI region. The outputs of the array are multiplexed in time to better facilitate input-output cable management by reducing the number of wires. The non-overlapping clock generator within the serializer generates N-phase clock signals, each with 1/N duty cycle. Non-overlapping clock signals ensure that only one amplifier is connected to the output buffer at a time during the channel switchover. This work presents two ULP BSA front-ends, BSA I and BSA II. BSA I provides symmetrical and complementary signal amplification paths to achieve energy-efficient low noise signal conditioning. BSA II is designed to achieve a high CMRR (i.e., better than 70 dB), thereby reducing the detrimental effect of power-line 60 Hz interference on the recorded signal.

Minimizing both noise and power dissipation imposes stringent design trade-off in an AFE for an implantable system, mandating meticulous considerations at every level of the design process. For example, at the device level, this notion implies that transistors should be designed to operate in a region which yields minimum power consumption for a given IRNoise imposed by minimum detectable ECoG signal power.

It is well-known that the MOS transistors in the WI region achieve maximum  $g_m/I_{DS}$ -ratio, resulting in the highest power efficiency at the cost of lower operation maximum bandwidth [49], [50]. Fig. 2.2 demonstrates  $g_m/I_{DS}$  and  $log_{10}(I_{DS})$  variations with respect to  $V_{GS}$  for the two technologies given the same transistor sizes and bias conditions. Referring to Fig. 2.2(a), a higher subthreshold leakage current and a higher slope are observed in the

Figure 2.2: (a) Drain-source current  $(I_{DS})$  vs. gate-source voltage  $(V_{GS})$  for the two technologies. (b)  $g_m/I_{DS}$  vs.  $V_{GS}$  for the two technologies. W/L =  $20\mu$ m/2 $\mu$ m with 10 fingers,  $V_{DS} = 1$ V for both transistors and body temperature of 37 is considered for simulation.

weak-inversion region for the 130nm process compared to the 180nm process. A higher slope corresponds to a larger  $g_m$  for the same bias current. This feature translates to a better power efficiency (Fig. 2.2(b)) and noise performance for transistors designed in this specific 130nm process. It is noteworthy that the  $g_m/I_{DS}$ -plot for the 130 nm CMOS process does not show the expected flat region in the deep subthreshold region. This is because BSIM4 device model was adopted for this process by the foundry. On the other hand, the 180 nm process employed PSP device model, which can predict the device behavior in deep subthreshold region more accurately.

ECoG signals typically have an amplitude of around 50–100  $\mu$ V [51], with  $\beta$  and high- $\gamma$  bands typically providing the most informative features for BCI applications [34]. The IRNoise of the AFE should be kept lower than the noise floor of the ECoG electrodes. Our recorded measurements using a commercial BCI signal acquisition equipment showed that the RMS noise floor, integrated over a frequency range of 8–200 Hz, is typically less than 10  $\mu$ V<sub>RMS</sub>, which is in compliance with the data reported in literature, e.g. [52]. Low noise operation is of particular interest for high- $\gamma$  band, because the ECoG signal power becomes weaker with frequency [53].

The CMRR and power-supply rejection ratios (PSRR) should be large to attenuate the effect of environmental noise sources (e.g., 60 Hz power-line noise). Assuming an IRNoise level of  $2\mu V_{RMS}$  in the presence of common-mode interference with 10 mV<sub>RMS</sub>, a nominal 34 dB attenuation (i.e., 74 dB CMRR) is needed so that the output noise and interference voltage magnitudes are equal. In addition, the amplifier should show a high input impedance to lower the effect of common-mode interference. This attribute is especially important for multi-channel recordings since the impedance mismatch between electrodes  $(Z_{e,1},\ ...,\ Z_{e,N})$ as well as the mismatch between the impedance seen from the common reference input (parallel combination of  $Z_{in,1},...,Z_{in,N}$  in Fig. 2.1) and  $Z_{in,k}$  (1  $\leq k \leq N$ ) reduces the overall CMRR. Subdural electrodes' impedance have been reported (as well as measured) to be about 1 k $\Omega$  [30], thus the input impedance at the frequency of interest should be  $\gg$ 1 M $\Omega$  [54]. Moreover, large DC offset associated with neural recording electrodes should be eliminated so as to minimize distortion or avoid saturation of the amplifier. Furthermore, electrical shielding and DC isolation are needed between the IC and implanted electrodes. Finally, the crosstalk in a multi-channel system should be mitigated to avoid contamination of the overall information recorded from different channels.

## 2.3 BSA I: An Array of 64 Amplifier I Circuits and A Serializer

BSA I incorporates 64 units of Amplifier I and a serializer, as shown in Fig. 2.1(b). Fig. 2.3 shows the general block diagram of the OTA used in the Amplifier I, composed of complementary NMOS-PMOS input stage. Intuitively, the signal is amplified by the transconductance gain of the input transistor pairs and subsequently applied to the current gain stage in each of the top and bottom branches  $(A_{I,N} \text{ and } A_{I,P})$ . Upon flowing through the load impedance  $Z_L$ , the summing current will generate the output voltage. Fig. 2.4(a) shows the top-level

Figure 2.3: Complementary input structure of the OTA used in Amplifier I

topology of Amplifier I employing an OTA with an RC feedback network. The AC-coupled input provides DC rejection between the recording electrodes and the OTA input, thus providing a layer of electrical safety and isolation between the patient's brain and the amplifier. Fig. 2.4(b) depicts the transistor-level schematic of the OTA utilized in Amplifier I, including common-mode feedback (CMFB) circuitry (in gray) [47]. The OTA device sizes and aspect-ratios together with operating points of the individual devices are presented in Table 2.1. NMOS and PMOS transistors' body connections are tied to the ground and supply rails, respectively. The minimum headroom for a single transistor biased in the WI region is  $\sim 4 U_T$  (where  $U_T \approx 26$  mV at room temperature) [55]. As a result, the OTA is biased at 0.4 V supply to mitigate large process variations resulting from WI operation, while achieving low power and low noise. The first stage employs a complementary NMOS-PMOS differential configuration with a complementary active load comprising parallel combination of diode-connected transistors and a cross-coupled pair [47, 56]. Cross-coupled pair and diode-connected transistors are identically sized as shown in Table 2.1, thereby having the same transconductance. The effective output resistance of the input stage is thus increased from

Figure 2.4: (a) Amplifier I comprising a closed-loop amplifier with capacitive feedback and its die microphotograph, and (b) the schematic of the complementary NMOS-PMOS OTA [47]

$\frac{r_{o3}}{1+g_{m3}r_{o3}}||r_{o1}|$  (in the absence of cross-coupled pair load) to  $r_{o1}||r_{o2}||r_{o3}$ , where  $r_{o1}$ ,  $r_{o2}$  and  $r_{o3}$  are the drain resistance of  $M_1$ ,  $M_2$  and  $M_3$ , respectively. The active-load devices are sized in a way that no instability or latch-up happens due to the process variation. The size of output transistors  $M_4$  and  $M_8$  are chosen to exhibit large drain resistance and low current consumption at the output stage.

The capacitance ratio  $C_1/C_2$  ( $C_1 = 20$  pF and  $C_2 = 200$  fF) defines the closed-loop gain with high accuracy so long as the open-loop gain is sufficiently high. High output impedance of the OTA imposes a high impedance load for the feedback and next stage circuits. Pseudoresistors realized by transistors  $M_A$  and  $M_B$  (as in [57]) provide large equivalent resistance R of few  $G\Omega$ , self-bias the input stage of the OTA without consuming any additional power for closing the loop, and set the lower 3-dB cutoff frequency ( $f_L = (2\pi RC_2)^{-1}$ ). Compared to pseudo-resistor used in [58], this implementation provides a wider linear range of operation. Assuming all transistors are identically matched (to simplify the analysis), the IRNoise power spectral density (PSD) of the open-loop OTA ( $\overline{V_{in,OTA}^2}$ ) is calculated to be:

$$\overline{V_{in,OTA}^2(f)} = \frac{4kT\gamma}{g_{m1}} \left( 1 + \frac{2g_{m2}}{g_{m1}} \right) + \frac{K_{p,1/f}}{C_{ox}(WL)_1} \frac{1}{f} \left[ 1 + 2\frac{K_{n,1/f}}{K_{p,1/f}} \frac{(WL)_1}{(WL)_2} \left( \frac{g_{m2}}{g_{m1}} \right)^2 \right]$$

(2.1)

where k is the Boltzmann constant,  $\gamma$ ,  $K_{p,1/f}$  and  $K_{n,1/f}$  are technology-dependent parameters, f is frequency,  $C_{ox}$  is the gate oxide capacitor, and T is the temperature.  $\gamma$ , the excess thermal noise factor, is slightly lower in the WI region than in the strong inversion (SI) [49]. Note that the complementary structure used in this OTA doubles the overall  $G_m$ . Flicker noise and mismatch effects are slightly attenuated by large input transistors and symmetrical circuit layout. In addition, dynamic compensation techniques such as chopper stabilization and autozeroing are commonly used to reduce the effect of amplifier offset and flicker noise [59–63]. However, these techniques require switches with low on-resistance to accommodate highly linear operation for autozeroing techniques and low residual input-referred offset voltage for chopping techniques. Thus, a high-swing on-chip clock needs to be generated at the

Table 2.1: Amplifier I device sizes and operating points

| Devices             | $W/L (\mu m/\mu m)$ | $I_D$ (nA) | $g_m/I_D (V^{-1})$ |

|---------------------|---------------------|------------|--------------------|

| $M_{1a}$ - $M_{1b}$ | 53.5/1.35           | 130        | 34                 |

| $M_{2a}$ - $M_{2b}$ | 50/10               | 65         | 25                 |

| $M_{3a}$ - $M_{3b}$ | 50/10               | 65         | 25                 |

| $M_{4a}$ - $M_{4b}$ | 3.7/32              | 1.5        | 25                 |

| $M_{5a}$ - $M_{5b}$ | 140/1.2             | 138        | 29                 |

| $M_{6a}$ - $M_{6b}$ | 15/30               | 69         | 28                 |

| $M_{7a}$ - $M_{7b}$ | 15/30               | 69         | 28                 |

| $M_{8a}$ - $M_{8b}$ | 0.4/40              | 1.5        | 26                 |

| $M_9$               | 80/0.36             | 89         | 34                 |

| $M_{10}$            | 80/0.36             | 170        | 35                 |

| $M_{11}$            | 120/0.13            | 277        | 25                 |

expense of high power consumption. Therefore, we have not used these compensation techniques in the current design. The IRNoise of Amplifier I in Fig. 2.4(a),  $\overline{V_{in,tot}^2}$ , is calculated to be:

$$\overline{V_{in,tot}^{2}(f)} = \left(4kTR + \overline{V_{in,OTA}^{2}(f)}\right) \left(\frac{f_{L}}{G_{c}f}\right)^{2} + \overline{V_{in,OTA}^{2}(f)} \left(\frac{C_{1} + C_{2} + C_{in}}{C_{1}}\right)^{2}$$

(2.2)

where  $G_c$  is the midband closed-loop gain defined by  $C_1/C_2$  and  $C_{in}$  is the equivalent input capacitance seen from the input of the OTA.

Sizing of the input transistors is critical due to existing trade-off between  $\overline{V_{in,OTA}^2}$  and  $\overline{V_{in,tot}^2}$ . More precisely, large input transistors with low flicker noise will reduce  $\overline{V_{in,OTA}^2}$ . On the other hand, a larger device size leads to larger input capacitance,  $C_{in}$ , which adversely affects the system sensitivity. Another point to consider is that  $C_{in}$  shunts the gate of the input transistor to ground, causing a capacitive voltage division between  $C_1$ ,  $C_2$  and  $C_{in}$ . This, in turn, lowers the differential loop-gain, thereby preventing the closed-loop gain to be accurately defined. Moreover, as  $f_L$  decreases, the thermal noise contribution of the pseudo-resistors to  $\overline{V_{in,tot}^2}$  is reduced, while the flicker noise contribution of the OTA to  $\overline{V_{in,tot}^2}$  is increased.

The serializer in Fig. 2.1(b) is clocked at 64 kHz and is composed of a custom-designed 6-bit synchronous binary counter, a 6-to-64 decoder and 2×64 complementary pass-gate switches for selecting the amplifier channels. A reset signal puts the circuit in an initial state (channel 64) and the clock signal selects the channels sequentially [47].

Section 3.6 presents the measurement results of the BSA I, which was fabricated in a 130nm CMOS process [47].

Figure 2.5: BSA II: (a) overall topology, including 4 Amplifier II circuits and one InAmp (b) InAmp implementation

# 2.4 BSA II: An Array of 4 Amplifier II Circuits, A Serializer, and an Instrumentation Amplifier

The existence of two signal paths in Amplifier I leads to a degradation in CMRR ( $\approx$ 60 dB). To further elaborate, suppose that the only existing mismatch is the one between each of the input pairs in Fig. 2.3 (i.e.,  $\Delta g_{m_N}$  and  $\Delta g_{m_P}$ ). This mismatch directly contributes to the common-mode to differential-mode gain for Amplifier I, which is derived as follows:

$$A_{cm-dm} \approx \frac{\Delta g_{m_N} \times A_{I_P} Z_{out}}{(g_{m_{N_1}} + g_{m_{N_2}}) Z_{S_N}} + \frac{\Delta g_{m_P} \times A_{I_N} Z_{out}}{(g_{m_{P_1}} + g_{m_{P_2}}) Z_{S_P}}$$

(2.3)

where  $Z_{out}$ ,  $Z_{S_N}$  and  $Z_{S_P}$  are output impedances of Amplifier I,  $I_{S_N}$  and  $I_{S_P}$ , respectively. It is inferred from (2.3) that the CMRR of Amplifier I can statistically be degraded by a factor of 2 compared to an amplifier with a single path from the input to the output. A high CMRR is important in brain signal amplifiers due to the presence of a strong 60 Hz power-line noise in the amplification band. If not eliminated, major degradation in the output signal-to-noise

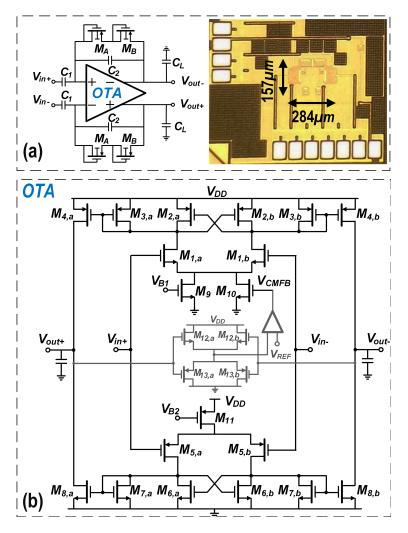

Figure 2.6: (a) OTA schematic used in Amplifier II (b) Op-amp schematic used in InAmp

ratio (SNR) will be seen. To further improve this feature, Fig. 2.5 introduces the block diagram of BSA II, which is composed of an array of 4 Amplifier II circuits, a serializer, and an instrumentation amplifier (InAmp). Similar to Amplifier I, Amplifier II is realized as a fully differential RC feedback circuit incorporating 200 fF feedback and 18 pF input AC-coupled capacitors. Matching accuracy of the feedback capacitor limits the achievable CMRR. For instance, it is readily shown that for closed-loop gain of 100 and 10% mismatch of the feedback capacitor, CMRR is lower than 60 dB. The open-loop OTA within Amplifier II employs PMOS input differential-pair with NMOS cross-coupled active loads, as shown in Fig. 2.6(a). Having one signal path from the input to the output relaxes the mismatch considerations present in complementary signal paths used in the first design.

The IRNoise of the open-loop OTA is calculated to be:

$$\overline{V_{in,OTA}^2(f)} = \frac{8kT\gamma}{g_{m1}} \left( 1 + \frac{2g_{m2}}{g_{m1}} \right) + \frac{2K_{p,1/f}}{C_{ox}(WL)_1} \frac{1}{f} \left[ 1 + 2\frac{K_{n,1/f}}{K_{p,1/f}} \frac{(WL)_1}{(WL)_2} \left( \frac{g_{m2}}{g_{m1}} \right)^2 \right]$$

(2.4)

Assuming a single-pole frequency response, it is readily proven that the noise efficiency factor (NEF [64]) reaches a lower-limit of  $2\sqrt{n\gamma}$  (where n denotes the subthreshold slope factor [55]) for both OTAs used in Amplifiers I and II if no dynamic compensation techniques are employed. The use of the same closed-loop architecture as in Amplifier I indicates that the IRNoise of Amplifier II is also expressed by (2.2).

The InAmp, after the serializer, provides further amplification and buffering to the output. It is commonly known that isolated resistive feedback circuitry ( $R_1$  and  $R_2$ ) provides flexibility in the design of an InAmp and its constituent open-loop op-amps with no concern of loading on preceding circuits [65]. In addition, any variation in  $R_1$  is widely known to only contribute to the differential gain variation and will not increase common-mode to differential-mode gain ( $A_{cm-dm}$ ) [66], [67]. Therefore, the CMRR is not degraded. As for the contribution of the mismatch between the  $R_2$  resistors ( $R_{2\Delta}=R_2+\Delta R$ ) on CMRR, the InAmp's  $A_{cm-dm}$  induced by this mismatch is derived first:

$$A_{cm-dm} = \frac{E_{CM} - 1}{1 + \frac{R_{2\Delta}}{R_1 A_{dm2}} - \frac{R_{2\Delta}}{A_{dm1} R_1} E_{CM} + \frac{1}{A_{dm2}}}$$

(2.5)

where:

$$E_{CM} = \frac{1 + \frac{1}{A_{dm2}} \left(1 + \frac{R_2 + R_{2\Delta}}{R_1}\right)}{1 + \frac{1}{A_{dm1}} \left(1 + \frac{R_2 + R_{2\Delta}}{R_1}\right)}$$

(2.6)

In deriving Eq. (2.5), the open-loop gains of the op-amps,  $A_{dm1}$  and  $A_{dm2}$ , are assumed to be finite, while each op-amp exhibits negligible differential to common-mode gain. The common-mode gain  $A_{cm}$  of the InAmp is almost unity. If followed by a high-CMRR amplification stage, the contribution of  $A_{cm}$  on CMRR will be negligible. On the other hand, to reduce the impact of  $A_{cm-dm}$  on CMRR, the op-amps need to exhibit large open-loop gain. Large open-loop gain significantly reduces the contribution of  $R_2$  mismatch on the CMRR. Ideally, if the op-amps are perfectly matched  $(A_{dm1} = A_{dm2})$ ,  $A_{cm-dm}$  would become zero regardless of  $\Delta R$  value.

Amplifier II and the InAmp are DC-coupled, eliminating the need for large coupling capacitors. Considering a 39-dB gain for the OTA, the expected differential input amplitude of the InAmp is less than 9 mV, which falls within the input common-mode range of InAmp (0 to  $V_{DD} - 2V_{DS,sat}$  where  $V_{DS,sat}$  is the drain-source saturation voltage).

Figs. 2.6(a) and (b) show the transistor-level schematics of the OTA used in Amplifier II