## **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

## **Title**

End-to-end Power Optimization of Circuits for Analog Coherent Optical Links

## **Permalink**

https://escholarship.org/uc/item/83s3n83f

## **Author**

ANDRADE, HECTOR

## **Publication Date**

2022

Peer reviewed|Thesis/dissertation

## University of California Santa Barbara

# End-to-end Power Optimization of Circuits for Analog Coherent Optical Links

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Hector Andrade

## Committee in charge:

Professor Clint L. Schow, Co-Chair Professor James F. Buckwalter, Co-Chair Professor Mark J. W. Rodwell Professor Loai Salem

| The Dissertation of Hector Andrade is approved.   |

|---------------------------------------------------|

|                                                   |

|                                                   |

| Professor Mark J. W. Rodwell                      |

|                                                   |

| Professor Loai Salem                              |

|                                                   |

| Professor James F. Buckwalter, Committee Co-Chair |

|                                                   |

| Professor Clint L. Schow, Committee Co-Chair      |

January 2022

End-to-end Power Optimization of Circuits for Analog Coherent Optical Links

Copyright © 2022

by

Hector Andrade

Para mi papá.

## Acknowledgements

I would like to begin by thanking my two advisors, professors Clint Schow and Jim Buckwalter, who welcomed me to their research groups when I showed interest in staying for the PhD after completing the MS program. I have learned a great deal from them over the past five years, both as people and as academics. No matter how busy, they always made the time to provide guidance whenever necessary and were understanding and empathetic when there were difficulties along the way.

I am also very grateful to professors Mark Rodwell and Loai Salem for being on my committee and for their valuable feedback and advice.

I would like to thank the other PhD students and postdocs at the ECE department that I had the chance to work with and learn from, especially Aaron Maharry, Junqian Liu, Yujie Xia, Luis Valenzuela, Cameron Hill, Takako Hirokawa, Ghazal Movaghar, Navid Hosseinzadeh, Sergio Pinna, Joe Fridlander, and Fabrizio Gambini.

I would also like to acknowledge Val de Veyra, Amanda Miller, and Alethea Butler-Nalin at UCSB and Giovanni Gilardi at Intel for their enormous help during the program.

During these years in Santa Barbara I have had the pleasure of meeting some great people I would also like to thank for their support - Michelle Labrecque, Jeff Haller, Bharat Monga, Heena Yoon, Ravi Rajan, Giulia Collura, and Clint Bockstiegel.

I also want to thank my family. My parents, Héctor and María Esther, have always given me unconditional love and support. My father did not live to see me graduate, but I like to think he would be proud to see me following in his footsteps every step of the way.

Last but not least, I want to thank my fiancé Olga. Without you I simply would not be here today. It is your love and support that have kept me going throughout even the most difficult times.

## Curriculum Vitæ Hector Andrade

#### Education

| 2022 | Ph.D. in Electrical and Computer Engineering (Expected), Univer-                      |

|------|---------------------------------------------------------------------------------------|

|      | sity of California, Santa Barbara.                                                    |

| 2017 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara. |

| 2012 | B.S. in Mechatronics Engineering, Tecnológico de Monterrey, Campus Puebla, México.    |

## **Publications**

- 1. **H. Andrade**, T. Hirokawa, A. Maharry, A. Rylyakov, C. L. Schow, and J. F. Buckwalter, "Monolithically-Integrated 50 Gbps 2pJ/bit Photoreceiver with Cherry-Hooper TIA in 250nm BiCMOS Technology," in Optical Fiber Communication Conference (OFC) 2019, OSA Technical Digest (Optica Publishing Group, 2019), paper M3A.5.

- 2. **H. Andrade**, A. Maharry, T. Hirokawa, L. Valenzuela, S. Pinna, S. Simon, C. L. Schow, and J. F. Buckwalter, "Analysis and Monolithic Implementation of Differential Transimpedance Amplifiers," J. Lightwave Technol. 38, 4409-4418 (2020)

- 3. **H. Andrade**, Y. Xia, A. Maharry, L. Valenzuela, J. F. Buckwalter and C. L. Schow, "50 GBaud QPSK 0.98 pJ/bit Receiver in 45 nm CMOS and 90 nm Silicon Photonics," 2021 European Conference on Optical Communication (ECOC), 2021, pp. 1-4, doi: 10.1109/ECOC52684.2021.9606026.

- 4. **H. Andrade**, A. Maharry, T. Hirokawa, L. A. Valenzuela, S. Simon, C. L. Schow, J. F. Buckwalter, "Comparison of three monolithically integrated TIA topologies for 50 Gb/s OOK and PAM4," Proc. SPIE 11286, Optical Interconnects XX, 112860W (28 February 2020); https://doi.org/10.1117/12.2548762

- 5. **H. Andrade**, A. Maharry, L. A. Valenzuela, N. Hosseinzadeh, C. L. Schow, J. F. Buckwalter, "An 8.2-pJ/bit, 56 Gb/s Traveling-wave Modulator Driver with Large Reverse Terminations," BCICTS 2021.;

- 6. **H. Andrade**, J. Liu, A. Maharry, T. Hirokawa, J. F. Buckwalter, C. L. Schow, "Optical transmitter equalization with mismatched terminations in a Mach-Zehnder modulator", Patent Pending.

- 7. **H. Andrade**, A. Maharry, L. Coldren, J. F. Buckwalter, C. L. Schow, "Wavelength-multiplexed analog coherent optical receiver", Patent Pending.

- 8. T. Hirokawa, S. Pinna, N. Hosseinzadeh, A. Maharry, **H. Andrade**, J. Liu, T. Meissner, S. Misak, G. Movaghar, L. Valenzuela, Y. Xia, S. Bhat, F. Gambini,

- J. Klamkin, A. A. M. Saleh, L. Coldren, J.F. Buckwalter, C. L. Schow, "Analog Coherent Detection for Energy Efficient Intra-Data Center Links at 200 Gbps Per Wavelength," in Journal of Lightwave Technology, vol. 39, no. 2, pp. 520-531, 15 Jan.15, 2021, doi: 10.1109/JLT.2020.3029788.

- 9. L. A. Valenzuela, A. Maharry, **H. Andrade**, C. L. Schow and J. F. Buckwalter, "A 108-Gbps, 162-mW Cherry-Hooper Transimpedance Amplifier," 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2020, pp. 1-4, doi: 10.1109/BCICTS48439.2020.9392928.

- L. A. Valenzuela, H. Andrade, N. Hosseinzadeh, A. Maharry, C. L. Schow and J. F. Buckwalter, "A 2.85 pJ/bit, 52-Gbps NRZ VCSEL Driver with Two-Tap Feedforward Equalization," 2020 IEEE/MTT-S International Microwave Symposium (IMS), 2020, pp. 209-212, doi: 10.1109/IMS30576.2020.9223818.

- 11. A. Maharry, **H. Andrade**, T. Hirokawa, J. F. Buckwalter and C. L. Schow, "A Novel Architecture for a Two-Tap Feed-Forward Optical or Electrical Domain Equalizer using a Differential Element," 2019 IEEE Photonics Conference (IPC), 2019, pp. 1-2, doi: 10.1109/IPCon.2019.8908499.

- 12. A. Maharry, L. A. Valenzuela, **H. Andrade**, I. Kalifa, I. Cestier, M. Galanty, B. Atias, A. Sandomirsky, E. Mentovich, L. Coldren, J. F. Buckwalter, C. L. Schow, "A 50 Gbps 9.5 pJ/bit VCSEL-based Optical Link," 2021 IEEE Photonics Conference (IPC), 2021, pp. 1-2, doi: 10.1109/IPC48725.2021.9592905.

- 13. L. A. Valenzuela, A. Maharry, **H. Andrade**, C. L. Schow and J. F. Buckwalter, "Energy Optimization for Optical Receivers Based on a Cherry-Hooper Emitter Follower Transimpedance Amplifier Front-end in 130-nm SiGe HBT Technology," in Journal of Lightwave Technology, vol. 39, no. 23, pp. 7393-7405, Dec.1, 2021, doi: 10.1109/JLT.2021.3115403.

#### Abstract

End-to-end Power Optimization of Circuits for Analog Coherent Optical Links

by

#### Hector Andrade

Data centers today account for about 2.5 % of the total electricity usage in the United States. The portion of that power that is consumed by the internal network is increasing dramatically, as server-to-server traffic grows over 23 \% every year. As a result, there is great demand for scalable power-efficient intra data center (IDC) optical communication links. IDC links today are based on intensity-modulation direct-detection modulation formats (IMDD). Thus far, the scaling of IMDD links has been achieved by increasing the number of signal amplitude levels, by moving to higher baud rates, and by adding multiple wavelengths or fibers. However, each of these scaling paths is severely constrained. Whereas IMDD systems only utilize the intensity of signal, coherent detection (CD) also leverages the two polarizations and two quadratures of the fiber optic channel, and thus is more scalable. CD also improves sensitivity by up to 20 dB by mixing the received signal with a strong local oscillator. CD has been employed in long-haul links for many years, yet these systems rely on power-hungry high-speed analog-to-digital converters (ADC) and digital signal processing (DSP) and thus may be unsuitable for IDC links. A compelling alternative to DSP-based CD is analog coherent detection (ACD), in which polarization demultiplexing, carrier recovery, and phase demodulation are performed using analog circuits.

This work focuses on the co-design of analog circuits and opto-electric devices that enable low-power ACD-based IDC links. First, a discussion of a proposed next-generation ACD IDC link architecture is outlined as motivation for the low-power circuit designs. Three monolithic 50 Gb/s opto-electric receiver topologies in SiGe BiCMOS technology are analyzed and compared. Then, a 100 Gb/s QPSK hybrid receiver in 45 nm CMOS is described. The co-design of a driver 56 Gb/s and traveling-wave Mach-Zehnder modulator (TW-MZM) is also presented. Finally, the thesis describes a TW-MZM equalization technique based on a tunable termination mismatch.

# Contents

| $\mathbf{C}$ | urric                | ulum Vitae                                                                               | vi        |

|--------------|----------------------|------------------------------------------------------------------------------------------|-----------|

| $\mathbf{A}$ | bstra                | act                                                                                      | viii      |

| 1            | Inti                 | roduction                                                                                | 1         |

|              | 1.1                  | Intra-data Center Link Scaling Challenges                                                | 2         |

|              | 1.2                  | Optical Switching in Future Data Centers                                                 | 3         |

|              | 1.3                  | Analog Coherent Link Implementation                                                      | 6         |

|              | 1.4                  | Overview                                                                                 | 8         |

| 2            | Tra                  | nsimpedance Amplifiers in Monolithic Electronic/Photonic 250 nm                          |           |

|              | $\operatorname{SiG}$ | e BiCMOS                                                                                 | 9         |

|              | 2.1                  | Introduction                                                                             | 9         |

|              | 2.2                  | Monolithic Integration and Transimpedance Limit                                          | 11        |

|              | 2.3                  | TIA Topology Comparison                                                                  | 14        |

|              | 2.4                  | TIA Circuit Design                                                                       | 18        |

|              | 2.5                  | PAM4 Simulations                                                                         | 30        |

|              | 2.6                  | Experimental Results                                                                     | 33        |

|              | 2.7                  | Conclusion                                                                               | 40        |

| 3            | 50                   | GBaud QPSK $0.98~\mathrm{pJ/bit}$ Receiver in $45~\mathrm{nm}$ CMOS and $90~\mathrm{nm}$ |           |

|              | Sili                 | con Photonics                                                                            | <b>44</b> |

|              | 3.1                  | Introduction                                                                             | 44        |

|              | 3.2                  | Coherent Receiver Data Path                                                              | 45        |

|              | 3.3                  | Costas Loop Phase-Frequency Detector and Loop Filter                                     | 55        |

|              | 3.4                  | Conclusions                                                                              | 60        |

| 4            | An                   | 8.2-pJ/bit, 56 Gb/s Traveling-wave Modulator Driver with Large                           |           |

|              | Rev                  | verse Terminations                                                                       | 63        |

|              | 4.1                  | Introduction                                                                             | 63        |

|              | 4.2                  | Circuit Topology and Driver-Modulator Co-design                                          | 65        |

| 5  | Optical transmitter equalization with mismatched terminations |                                                    |  |            |

|----|---------------------------------------------------------------|----------------------------------------------------|--|------------|

|    | silic                                                         | on photonic modulator                              |  | <b>7</b> 8 |

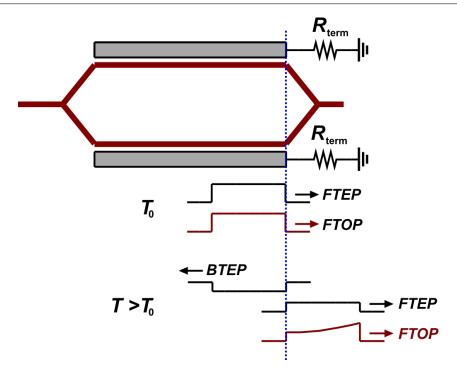

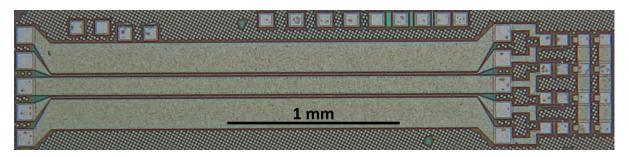

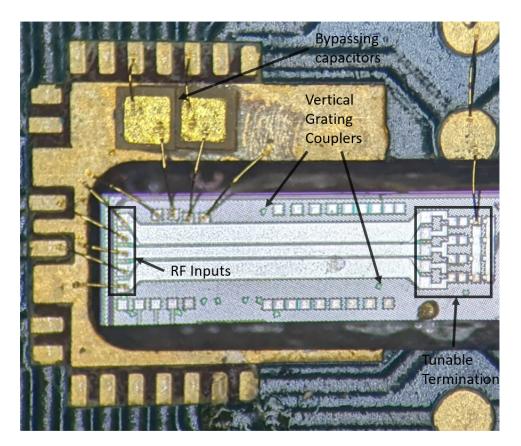

|    | 5.1                                                           | Introduction                                       |  | 78         |

|    | 5.2                                                           | Circuit Schematic and Simulations                  |  | 83         |

|    | 5.3                                                           | TDR Measurements                                   |  | 85         |

|    | 5.4                                                           | Frequency Response Measurements                    |  | 87         |

|    | 5.5                                                           | Time Domain Measurements and Mismatch Optimization |  | 90         |

|    | 5.6                                                           | Conclusion                                         |  | 93         |

| 6  | Summary and Outlook                                           |                                                    |  |            |

|    |                                                               | Future Work                                        |  | 95         |

| Bi | bliog                                                         | craphy                                             |  | 98         |

# Chapter 1

# Introduction

The past decades have seen an enormous increase in the number of Internet users, which is expected to reach 5.3 billion, or two thirds of the world's population, in 2023 [1]. Data centers have been crucial in enabling the explosive growth of the Internet and have become a key component of the world's infrastructure. In the United States, data centers currently consume 73 TWh of power per year. This accounts for 2.5% of total electricity usage and historically has doubled about every 8 years [2]. The portion of data center power that is consumed by the internal network is increasing dramatically, as server-to-server traffic grows over 23% every year [3].

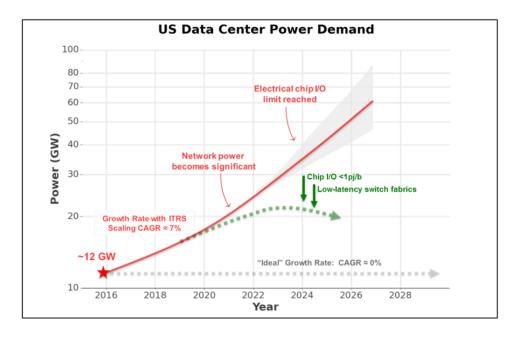

Fig. 1.1 shows the US Department of Energy's Advanced Research Projects Agency – Energy (ARPA-E) data center power consumption forecast. The red curve denotes current power trends, accounting for improvements in computing efficiency due to Moore's Law, as the internal network data center power becomes more significant and electrical I/O power scales with data rates. The green curve depicts how the power consumption trend can be suppressed while meeting internet traffic demands by enabling optical I/O and optical switching. The latter has the potential to transform entire data center networks, leading to drastic improvements in power efficiency. However, to enable optical

switching it is necessary to have sufficient unallocated link budget to accommodate the added losses in the fiber channel. This is not feasible in the intra-data center (IDC) links that are deployed today, which already operate with a very restricted loss budget. As IDC link data rates continue to increase, the unallocated link budgets are not expected to grow. IDC links today are based on intensity-modulation direct-detection (IMDD) modulation formats. Scaling IMDD-based links to meet the future demands is already proving to be difficult. Instead, we propose a paradigm shift towards links based on analog-coherent detection, which can scale to higher data rates while potentially enabling optical switching by increasing the unallocated budget [4].

Figure 1.1: Aggregated power consumption of US datacenters as a function of time.

# 1.1 Intra-data Center Link Scaling Challenges

IDC links today are based on IMDD formats. Thus far, the scaling of IMDD links has been achieved by increasing the number of signal amplitude levels, by moving to higher

baud rates, and by adding multiple wavelengths or fibers [5]. However, each of these scaling paths is severely constrained. IMDD IDC links operate with a tight loss budget. Therefore, the sensitivity penalty that results from increasing the number of signal amplitude levels places a bound on scaling to higher order IMDD formats. Progressing to higher baud rates has become increasingly challenging as increases in data rates outpace the bandwidth improvements of electronic and photonic devices available in commercial semiconductor processes. It is prohibitively expensive to increment the number of fibers per link, since that requires continuous recabling of the data center. Chromatic dispersion sets a limit on the optical transmission bandwidth. As a result, increasing the number of multiplexed wavelengths reduces the spacing between channels. This imposes stricter limits on the wavelength stability of the lasers, which are uncooled due to power density constraints. Whereas IMDD systems only utilize one of the intensity of signal, coherent detection (CD) also leverages the two polarizations and two quadratures of the fiber optic channel, and thus is more scalable. CD also improves sensitivity by up to 20 dB by mixing the received signal with a strong local oscillator, which can directly increase the unallocated link budget. CD has been employed in long-haul links for many years, yet these systems rely on power-hungry high-speed analog-to-digital converters (ADC) and digital signal processing (DSP) and thus may be unsuitable for IDC links. A compelling alternative to DSP-based CD is analog coherent detection (ACD), in which polarization demultiplexing, carrier recovery, and phase demodulation are performed using analog circuits. Power-efficient ACD links can scale to meet future generation data center demands while also enabling optical switching by increasing the unallocated link budget.

# 1.2 Optical Switching in Future Data Centers

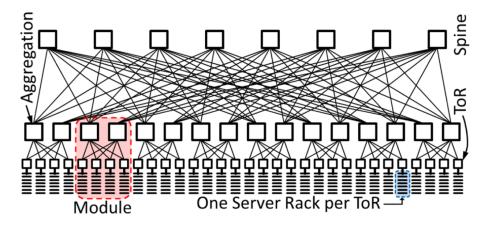

Fig. 1.2 shows a simplified version of a conventional three-level data center fat-tree

topology network [6]. At the bottom of the hierarchy there are servers mounted on vertical racks, which are interconnected using top-of-rack (ToR) switches. The ToR switches are

Figure 1.2: Conventional, three-level, folded-Clos (fat-tree) data center utilizing large spine and aggregation switches of the same size and smaller ToR switches [6].

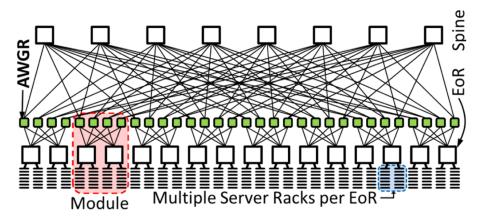

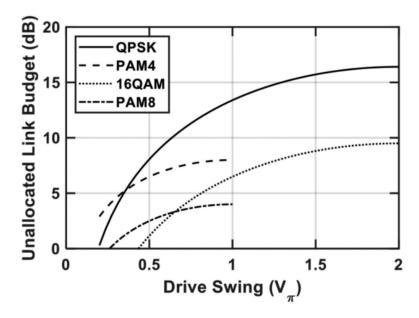

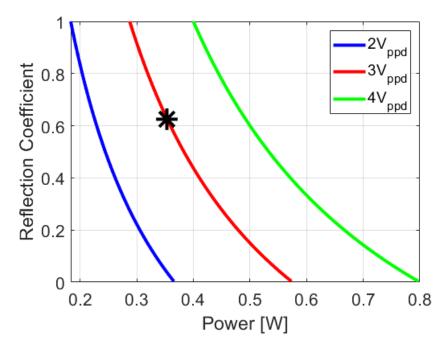

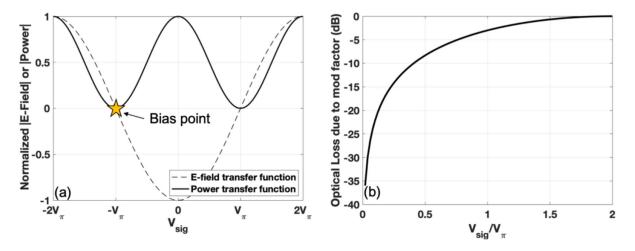

interconnected via aggregate switches, and the aggregate switches are then connected using spine switches at the top of the network hierarchy. In modern data centers, optical IMDD links are used to connect ToR, aggregate, and spine switches. The electro-optical (EO) and opto-electric (OE) conversion required for each optical link requires significant amounts of power. Optical switching can eliminate the need for power-hungry EO-OE conversion at every node, and can have profound implications for the data center as a whole by enabling flatter, more power efficient networks. Fig. 1.3 depicts a novel data center network that employs optical routing in order to reduce the electrical switching levels from three to two [6]. In this design, arrayed waveguide grating routers (AWGRs) are inserted between the two electronic switching levels, resulting in a 50% reduction in the total number of required transceivers compared to a modern conventional data center network. In order to accommodate the optical AWGRs losses, it is necessary to increase the link loss budget. Following the analysis approach described in [7], Fig. 1.4 shows the achievable link budgets offered by candidate link architectures assuming the same laser powers, MZM modulators, and target BER of 10<sup>-5</sup>. Our proposed ACD QPSK

Figure 1.3: Novel data center architecture utilizing two levels of large (spine and EoR) electronic switches of the same size, interconnected with WDM fibers, with an added layer of AWGRs (small, shaded boxes) [6].

implementation can enable optical routing by supporting link budgets of 13 dB with a wall-plug power efficiency of 5 pJ/bit [4].

Figure 1.4: Comparison of unallocated link margin in coherent and IMDD links, assuming MZM drive, and a target BER of 10<sup>-5</sup>. The QPSK curve assumes analog coherent link performance as described in [4].

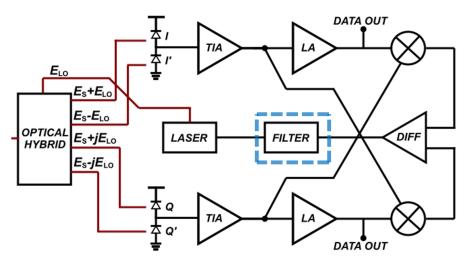

# 1.3 Analog Coherent Link Implementation

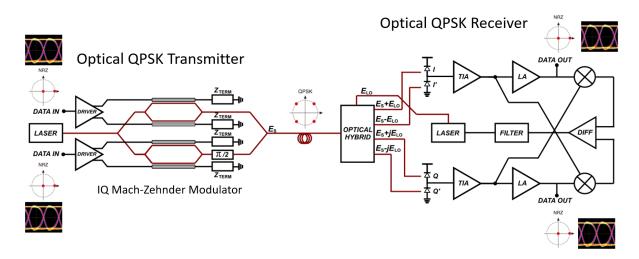

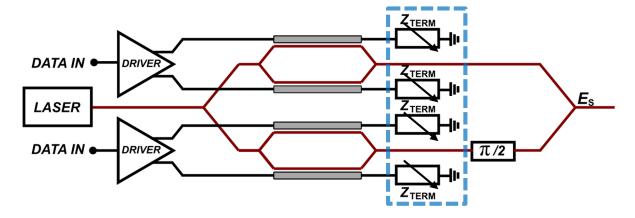

Figure 1.5: Proposed implementation of an analog coherent QPSK optical link.

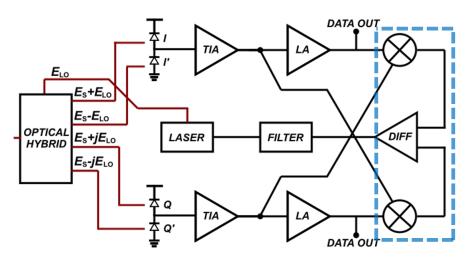

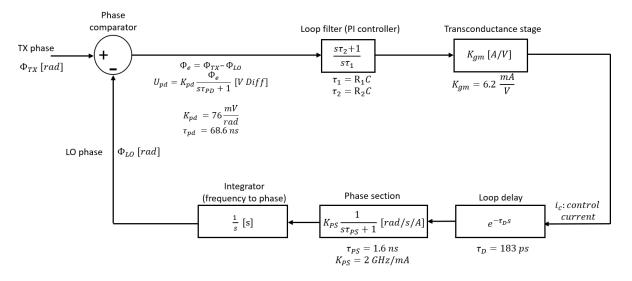

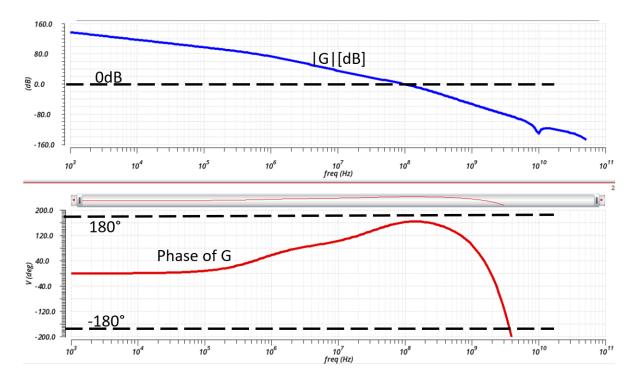

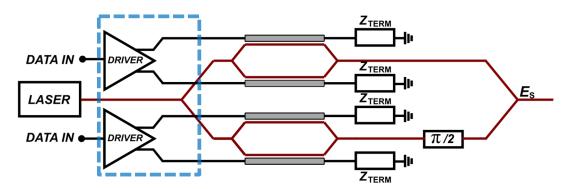

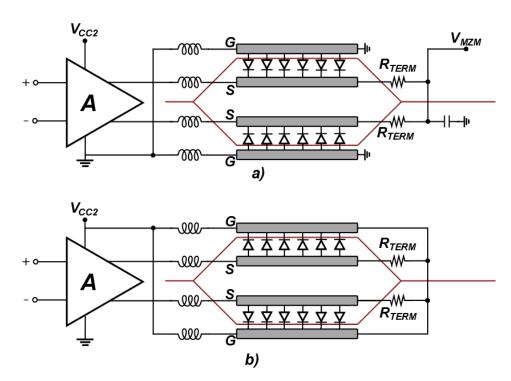

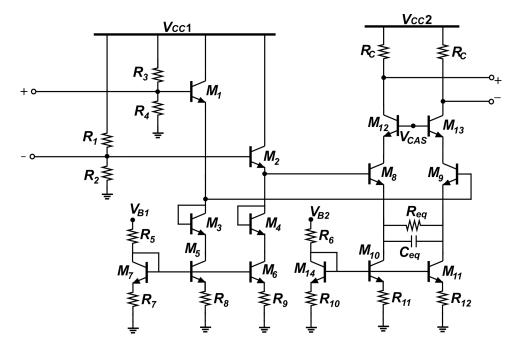

Our proposed link implementation, as described in [4], is an O-band analog coherent wavelength-multiplexed 200 Gb/s/ $\lambda$  DP-QPSK link with an OPLL-based receiver. The transmitter consists of a IQ modulator for each polarization, each of which contains two nested traveling wave Mach-Zehnder modulators (TW-MZMs) that are out of phase by  $\pi/2$ . The TW-MZMs are null-biased to produce a phase inversion at each bit transition. Each wavelength utilizes a separate O-band laser. The nested TW-MZMs are each modulated using differential limited drivers, each of which produces a 56 Gb/s on-off keying (OOK) signal. A polarization splitter rotator (PSR) at the output of one of the two QPSK modulators rotates the TE component to TM to generate the DP-QPSK signal, which propagates across up to 2 km of single-mode fiber. The link has an unallocated budget of 13 dB. The signal is then coupled to a QPSK receiver that employs a Costas Loop for carrier recovery and phase demodulation [8]. Costas-loop based optical phase-locked loops (OPLL) have been previously demonstrated at up to 40 Gb/s [9]. At the receiver, a polarization controller recovers the original transmitted state of polarization. Then a PSR is used to rotate the TM component to TE so it can propagate along the

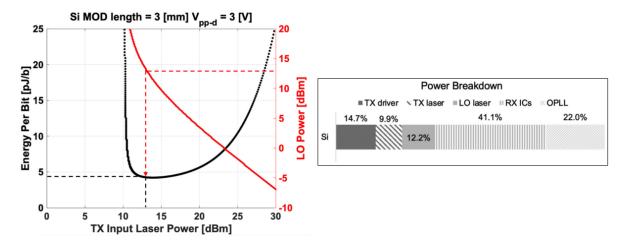

Figure 1.6: Calculated link power efficiency in pJ/bit vs transmitter input laser power for the link implementation described in [4]. The power breakdown corresponds to the optimum power efficiency point. The transmitter and receiver circuits account for about 80 % of the total power.

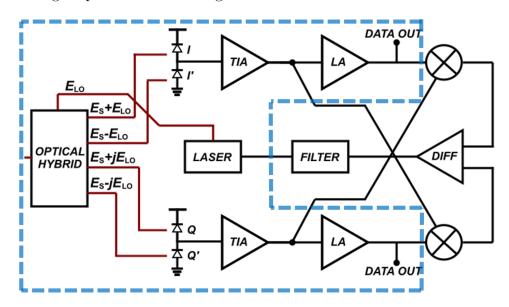

waveguides on the receiver. Each QPSK signal is then routed to an optical 90-degree hybrid. The other input of the hybrid is a local oscillator tunable laser. The hybrid generates the four signals corresponding to the desired vectorial additions of the two input optical fields, which are routed to two pairs of photodiodes (PD), one for the inphase (I) channel and the other for the quadrature channel (Q). Balanced or differential PDs convert the I and Q optical signals into photocurrent. The PDs are connected to TIAs, which convert the photocurrent into a voltage signal. Limiting amplifiers are then used to amplify and limit the signal. A phase-frequency detector (PFD) is implemented by mixing the I and Q channels and subtracting the output signal via a differential to single-ended amplifier. At the output of the amplifier is the PFD error signal, which in the phase-locked state is proportional to the phase error between the local oscillator and the carrier of the received signal. The PFD output signal is then filtered by a loop filter, which typically is a proportional-integral (PI) controller. The loop filter output is connected to a phase section of the local oscillator laser, which functions as a current-controlled oscillator. This closes the phase-locked loop. The proposed implementation

for one of the multiplexed wavelengths for each of the two polarizations is shown in Fig. 1.5.

It has been calculated [4] that the transmitter and receiver electronics consume the majority of the total link power. Fig. 1.6 contains a plot of the calculated link power efficiency in pJ/bit as a function of the transmitter input laser power for a specified bit-error rate of 1<sup>-5</sup>. The power breakdown, which corresponds to the optimum power efficiency point, indicates that the circuits account for about 80% of the total power.

## 1.4 Overview

In our proposed ACD link implementation, the majority of the power is consumed by the transmitter and receiver circuits. This work focuses on the co-design of analog circuits and opto-electric devices that enable low-power ACD-based IDC links.

In chapter 2, three monolithic 50 Gb/s opto-electric receiver topologies in SiGe BiC-MOS technology are analyzed and compared. Then, chapter 3 describes a 100 Gb/s QPSK hybrid receiver in 45 nm CMOS. Chapter 4 presents the co-design of a TW-MZM 56 Gb/s driver implemented in 130 nm SiGe BiCMOS. Finally, in chapter 5, a TW-MZM equalization technique based on a tunable termination mismatch fabricated in a monolithic 90 nm silicon photonics process is demonstrated.

# Chapter 2

# Transimpedance Amplifiers in Monolithic Electronic/Photonic 250 nm SiGe BiCMOS

# 2.1 Introduction

The optical interconnect industry is in the process of moving towards 400G Ethernet with current standards supporting 4 streaming channels at 53.125 GBd PAM-4 [10, 11]. However, PAM-4 adds linearity requirements on the TIA circuitry relative to NRZ signaling and has reduced sensitivity resulting in limited link power margin. For low-power applications, such as analog (DSP-free) optical coherent links that employ DP-QPSK modulation [5], there is demand for high sensitivity TIAs that operate above 50 Gb/s. Fig. 2.1 shows the TIA within an analog optical QPSK receiver. The increasing bandwidth (BW) and sensitivity requirements set stringent design tolerances on the receiver packaging parasitics that result from hybrid optoelectronic integration. Monolithic optoelectronic (O/E) integration drastically reduces parasitics since wirebonds and

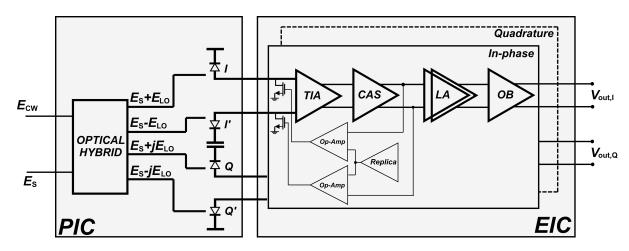

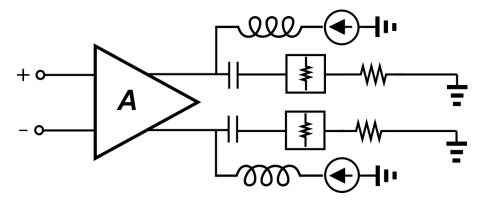

Figure 2.1: TIA within an analog optical coherent QPSK receiver.

bond pads are replaced with back-end-of-line interconnects [12]. The reduction in the wiring capacitance improves the achievable transimpedance for a given transistor performance. Prior high-rate monolithically integrated TIAs have been demonstrated based on SiGe processes. In [13], 25 Gb/s transmission was achieved at a power efficiency of 1.5 pJ/bit, and a 90 Gb/s AC-coupled receiver was shown in [14]. The Cherry-Hooper with emitter-follower (CHEF) topology, which we employ in our receivers, has been previously utilized in an receiver operating at over 50 Gb/s [15]. In this chapter we report three monolithically-integrated optical receiver designs that achieve up to 40 Gb/s at BER =  $10^{-12}$  without transmitter equalization and 50 Gb/s at BER =  $10^{-10}$  with transmitter equalization at a power efficiency as low as 1.1 pJ/bit. In Section 2.2, the advantage of monolithic integration is examined in the context of the transimpedance limit. A comparison of the balanced differential, unbalanced differential, and AC-coupled TIA topologies is presented in Section 2.3. Section 2.4 details the core TIA circuit design and comparison of noise performance in each of the three designs. The experimental results are discussed in Section 2.5 and the chapter is concluded in section 2.6.

# 2.2 Monolithic Integration and Transimpedance Limit

The transimpedance is given by:

$$R_T = \frac{A}{A+1} R_f \approx R_f \tag{2.1}$$

where A is the open-loop gain of the amplifier. The approximate expression is valid when A >> 1. The transimpedance limit describes the maximum transimpedance,  $R_T$ , that a TIA can attain for a given BW and device technology as characterized by the unity current gain transition frequency  $f_T$  [16, 17].

$$R_{T,max} \approx \frac{f_T}{2\pi C_{in} f_{3dB}^2} \tag{2.2}$$

where  $f_{3dB}$  is the desired 3-dB BW, and  $C_{in}$  is the total input capacitance. This expression is obtained by relating the BW to the open-loop gain by the approximation  $A \approx f_T/f_{3dB}$  and assuming the photodiode (PD) series resistance is small. Given constraints on the acceptable BW and device technology, the input capacitance of the TIA directly impacts how much transimpedance is achieved with a single gain stage. When transimpedance is limited to lower values, more gain stages are required at the expense of power consumption and noise.

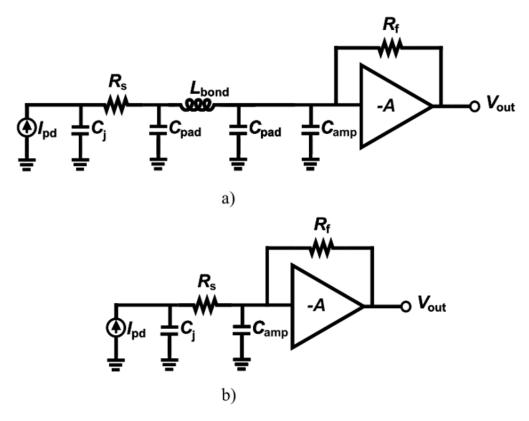

A hybrid approach to integration incorporates bond pads to connect a PD chip to the TIA (Fig. 2.2 (a)). Ignoring series inductance, e.g. wirebonds, for illustration purposes,  $C_{in} = C_j + 2C_{pad} + C_{amp}$ , where  $C_j$  is the PD junction capacitance,  $C_{pad}$  is the bond pad capacitance, and  $C_{amp}$  is the capacitance due to the amplifier. In a monolithic receiver (Fig. 2.2 (b)), the bond pads are eliminated and  $C_{in} = C_j + C_{amp}$ . Additionally, ESD protection devices are not required in the monolithic approach, which results in a further reduction of  $C_{in}$ . The reduced  $C_{in}$  of the monolithic approach should improve the  $R_T$ .

Figure 2.2: Shunt-feedback TIA with PD model a) with packaging parasitics (hybrid integration) and b) without packaging parasitics (monolithic integration).

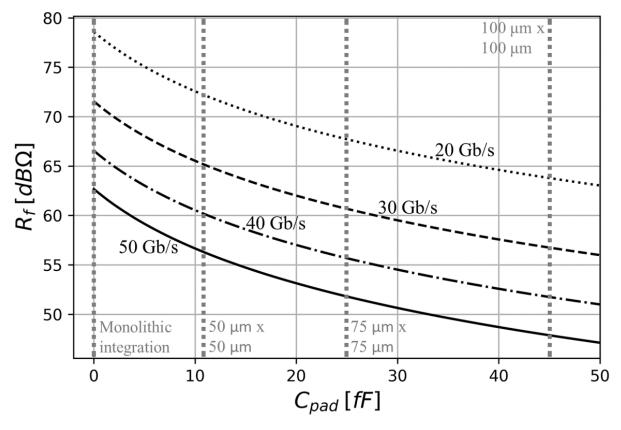

To understand the trade-off in transimpedance limit from monolithic integration of the PD, Fig. 2.3 shows the transimpedance limit for various data rates with  $C_j = 10$  fF,  $C_{amp} = 10$  fF, and  $f_T = 190$  GHz as a function of the bond pad capacitance. The 3-dB BW is assumed to be 2/3 of the bitrate. The resistance, which is plotted in dB $\Omega$ , is given by  $R(dB\Omega) = 20log_{10}(R)$ . The bond pad capacitance scales with 4.5 pF/mm<sup>2</sup> to account for variation in the bond pad area. The dotted vertical lines indicate common dimensions of square bond pads. The detrimental effect of the bond pad capacitance is significant even for small bond pads.

In the case of the monolithic receiver at 50 Gb/s, an  $R_f$  of 62.5 dB $\Omega$  can be achieved, while in a hybrid receiver it drops below 57 dB $\Omega$  for 50 µm x 50 µm bond pads. A bond pad of these dimensions can be difficult to bond reliably and 75 µm x 75 µm bond pads

Figure 2.3: Transimpedance limit versus bond pad capacitance at various data rates. The dotted vertical lines indicate the dimensions of a square bond pad.

or greater may be required for volume manufacturing. This would result in a  $R_T$  of 52 dB $\Omega$ , which constitutes a reduction of over 70 % as compared to monolithic. It can be observed that this reduction in percentage is equal for all data rates.

The derivation of the transimpedance limit does not account for the bandwidth extension that is possible with a series inductance between the PD and TIA. Hybrid integration can introduce a bond wire  $(L_{bond})$  to provide this bandwidth extension [18] with respect to the known bond pad and photodiode capacitance. However, the required inductance for bandwidth extension at 50 Gb/s for bond pads below 40 fF is greater than 1 nH. For monolithic integration the 3 nH of inductance is required, which is likely too large to be feasibly implemented as an on-chip inductor.

# 2.3 TIA Topology Comparison

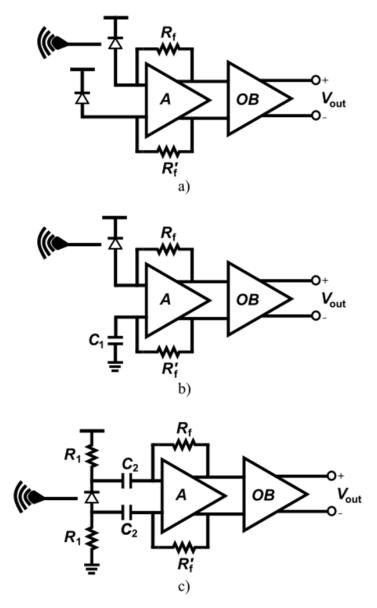

While the transimpedance limit indicates the trade-off between a transistor and photodetector, it does not lend to conclusions regarding the sensitivity, overload current, or voltage offset metrics relevant in modern optical communications. Two sources contribute to DC voltage offset at the output of a differential TIA. The first is the input DC current difference between the two differential inputs and is inherent to connections to single-ended photodiodes. A clear example is the unbalanced differential TIA, in which the photodiode is connected to only one of the two TIA inputs, and thus has an unbalanced input DC current. We will refer to the elimination of its resulting offset as DC level restoration (DCLR). The second source is the random, built-in voltage offset that is caused by process variations during semiconductor fabrication and is present in all TIA variants. Its elimination is referred to as DC offset compensation (DCOC). Both DCLR and DCOC may be implemented with automatic control loops [19]. Here, we analyze three common TIA topologies that utilize differential amplifiers to gain insight into their design trade-offs. The three variants are shown in Fig. 2.4 consisting of balanced, unbalanced, and AC-coupled architectures.

In the balanced variant (2.4 (a)), matched PDs are connected to each of the differential inputs. This architecture is commonly used with a single PD where the other input is connected to an on-chip capacitor designed to match the PD capacitance. However, an advantage of monolithic technologies is that it is convenient to utilize an actual dark PD, which improves matching. This topology is employed in applications such as coherent systems where only balanced detection is possible after 90-degree hybrids. In IMDD systems one PD receives the signal while the other PD is left dark. This variant requires DCLR to cancel the effect of the DC current imbalance in addition to DCOC. Both can be achieved by inputting a DC optical signal to the otherwise dark photodiode. One

Figure 2.4: Block-level schematic of the a) balanced, b) unbalanced, and c) AC-coupled differential TIA variants.

advantage of this topology is that any power supply or substrate noise will couple equally to both inputs and is expected to be rejected as a common-mode signal [19].

In the unbalanced, or pseudodifferential, variant (2.4 (b)), the dark PD is replaced with capacitor  $C_1$ , which in our implementation is a 1.2 nF off-chip capacitor that provides an AC ground at the input. This eliminates the noise contribution of  $R'_f$  down to the

cutoff frequency determined by  $C_1$  and the input resistance  $R_{in}$ , which is given by  $R_{in} \approx R_f/A$  for A >> 1. However, the input impedances are no longer balanced, and thus immunity to noise from the power supply and the substrate is poor. Additionally, the input capacitor must be large at the expense of silicon die area or off-chip assembly. An external current source can be connected to the capacitor input, since both DCOC and DCLR are required.

In the AC-coupled variant (2.4 (c)), each PD terminal is connected to one of the  $R_1$  resistors (2 k $\Omega$ ) and capacitors  $C_2$ . In our implementation these capacitors are realized as 4 pF on-chip metal-insulator-metal (MIM) capacitors.  $R_1$  and  $C_2$  set the low-frequency cutoff frequency of the receiver. DCOC is required but DCLR is not, because there is no DC current at any of the TIA inputs.

Both unbalanced and AC-coupled variants can be employed in IMDD systems such as VCSEL-based optical interconnects [20].

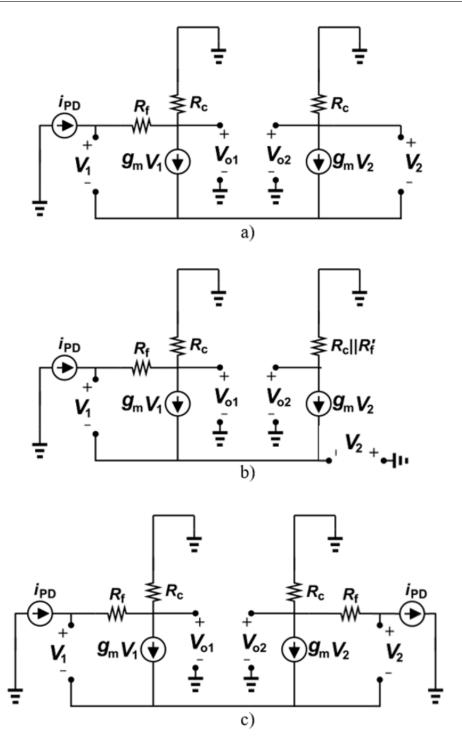

The midband gain of each TIA variant is investigated with the small-signal model transfer functions assuming an emitter-coupled differential pair amplifier. The schematics, assuming a large  $r_{\pi}$ , are shown in Fig. 2.5. Since the purpose of the model is to obtain the midband gain, the large capacitor of the unbalanced variant is assumed to be grounded and the junction capacitance of the dark PD of the balanced variant is considered to be an open circuit. The  $R_1$  of the AC-coupled variant produces a low-pass response with  $C_j$  and thus must be small enough to not limit the overall receiver BW. However, it must be large enough that the  $R_1$ ,  $R_{in}$  current division does not significantly reduce the midband gain. The transimpedance gain of the balanced receiver is

$$R_{T,BAL} = \frac{V_{o1}}{i_{PD}} = \frac{R_C(2 + g_m(R_C - R_f))}{2 + 2g_mR_C} \approx -\frac{R_f}{2}$$

(2.3)

Figure 2.5: Small signal model assuming  $r_{\pi} >> 1$  of the a) balanced, b) unbalanced, and c) AC-coupled variants.

for the unbalanced receiver it is

$$R_{T,UNBAL} = \frac{V_{o1}}{i_{PD}} = \frac{R_C(2 - g_m R_f)}{2 + g_m R_C} \approx -R_f$$

(2.4)

and for the AC-coupled receiver it is

$$R_{T,AC} = \frac{V_{o1}}{i_{PD}} = \frac{R_C(1 - g_m R_f)}{1 + g_m R_C} \approx -R_f$$

(2.5)

The approximate expressions are valid when  $g_m R_C >> 1$  and  $R_f >> R_C$ , which is conventionally true. For TIAs that utilize high amplifier gain, the transimpedance of the unbalanced configuration is expected to be close to twice that of the balanced one. Likewise, the transimpedance of the AC-coupled variant is also approximately twice as large since both PD terminals are connected to the TIA. This doubles the input differential current.

We will inspect the details of these implementations and the noise characteristics of the different circuits in the following section.

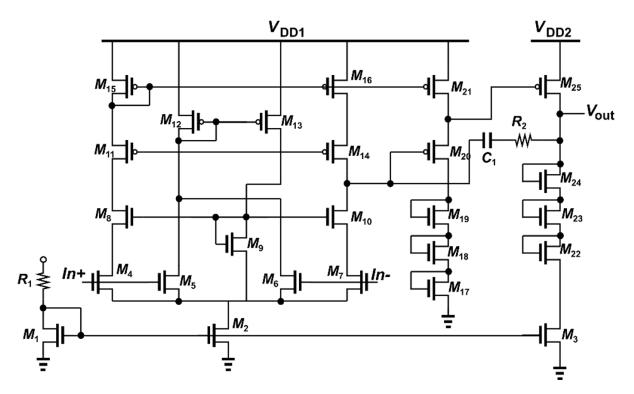

## 2.4 TIA Circuit Design

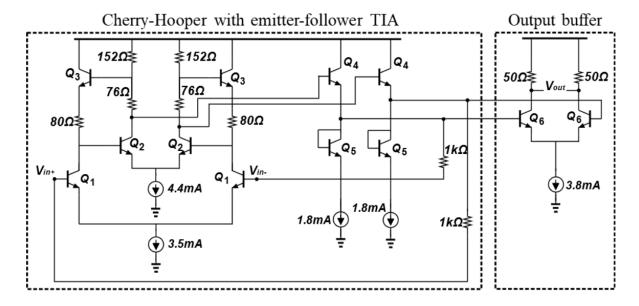

All three TIA variants were realized with the same core circuit and were nominally biased at the same DC operating points shown in Fig. 2.6. It consists of a shunt-feedback TIA and a 50  $\Omega$  differential output buffer. The voltage amplifier has a Cherry- Hooper with emitter-follower (CHEF) feedback topology and emitter follower buffers at the output. The design of the CHEF amplifier utilizes feedback between cascaded common-emitter amplifiers to extend the bandwidth provided that the inverse transconductance of the second stage is much smaller than the value of the feedback resistance between the stages. Emitter-followers are added to drive the load capacitance. The resistor values of

Figure 2.6: Receiver core schematic, common to all three variants.

$R_f$  (1k  $\Omega$ ),  $R_1$  (152  $\Omega$ ),  $R_2$  (76  $\Omega$ ), and  $R_3$  (80  $\Omega$ ) are chosen to produce a Bessel response where the group-delay is maximally flat [21].

A Ge PD is incorporated into the SiGe process and has a reported bandwidth of 70 GHz, a responsivity at 1550 nm of 0.9 A/W, series resistance of 35  $\Omega$ , and junction capacitance of 10 fF [22]. Therefore, we anticipate that the circuit response is the limiting factor for the overall 3-dB bandwidth.

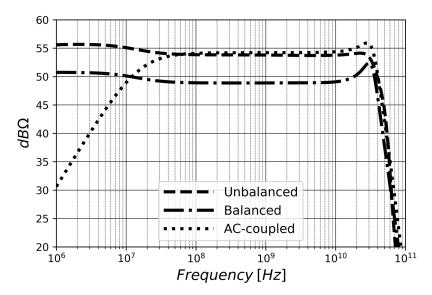

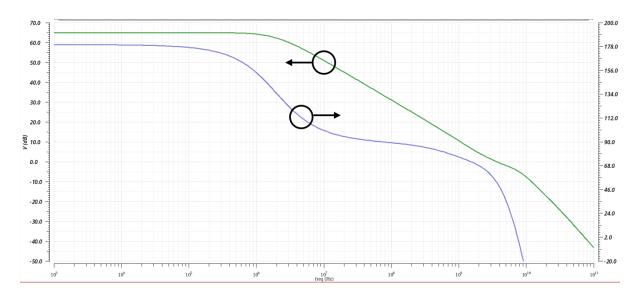

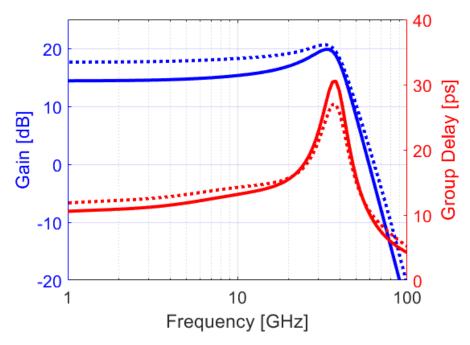

## 2.4.1 Frequency response

Fig. 2.7 plots the single-ended small-signal transimpedance gain of the three receiver variants including output inductance (150 pH) and capacitance (40 fF) that result from packaging parasitics and an RC PD model to verify the midband transimpedance gain prediction. This simulation does not account for post-layout parasitics. While there is a difference of approximately 5 dB between the balanced and unbalanced variants, the -3 dB electrical bandwidths are similar (40.3 GHz, 37.6 GHz, and 38.6 GHz for

Figure 2.7: Simulated transimpedance gain of the three receiver variants. Output wirebond inductances ( $L=150~\mathrm{pH}$ ) and bond pad capacitances ( $C=40~\mathrm{fF}$ ) are considered.

the balanced, unbalanced, and AC-coupled variants, respectively). The midband gain difference is approximately equal to what was predicted in section 2.3. The DC-cutoff of the AC-coupled receiver is 20 MHz, which is viable for use in 8b10b encoded links but is not suitable for 64b/66b encoding. The DC-cutoff frequency is limited by chip area and MIM parasitics. And for large capacitors, self-resonance of the DC-blocking MIM capacitors should also be considered.

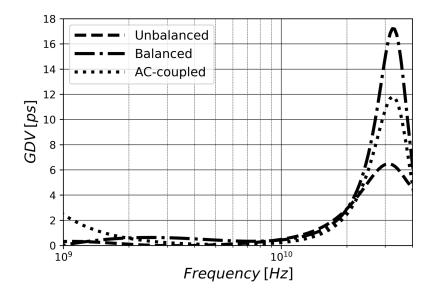

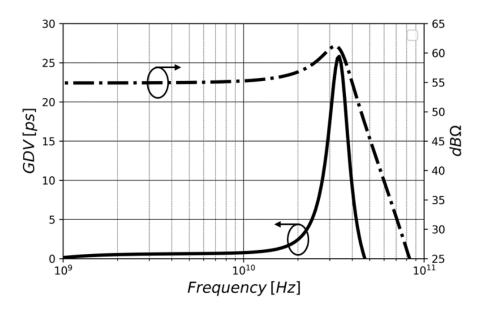

## 2.4.2 Group-Delay Variation

The CHEF amplifier was designed for a flat GDV. However, the addition of the PD and the packaging parasitics, as well as the resistors and capacitors specific to each topology, resulted in an increased GDV. The GDV above 1 GHz, shown in Fig. 2.8, is 6 ps in the unbalanced variant, 12 ps in the AC-coupled variant, and nearly 18 ps (0.9 UI at 50 Gb/s) in the balanced variant. Fig. 2.9 shows the GDV and frequency response of the CHEF TIA assuming an ideal PD with  $C_j = 0$ . The transimpedance has 5 dB of

Figure 2.8: Simulated GDV above 1 GHz of the three TIA variants.

Figure 2.9: CHEF TIA simulated GDV and transimpedance above 1 GHz with an ideal PD  $(C_j = 0)$ .

peaking, which introduces a GDV of over 25 ps. The PD  $C_j$  and the other capacitances introduced in the receiver variants serve to dampen the response and decrease the GDV. Fig. 2.10 shows the normalized frequency response of the three front-end topologies when the CHEF TIA is replaced by an ideal resistor  $R_{in}$ . The BWs are 80, 85, and 130 GHz for

Figure 2.10: Simulated normalized frequency response of the three front-end topologies when the CHEF TIA is replaced by an ideal resistor  $R_{in}$ , which is given by  $R_{in} \approx R_f/A$ .

the unbalanced, AC-coupled, and balanced receivers, respectively. The balanced receiver, which has the highest BW, also has the highest GDV. The unbalanced receiver, with the lowest BW, dampens the TIA response the most, and has the lowest GDV.

## 2.4.3 Sensitivity

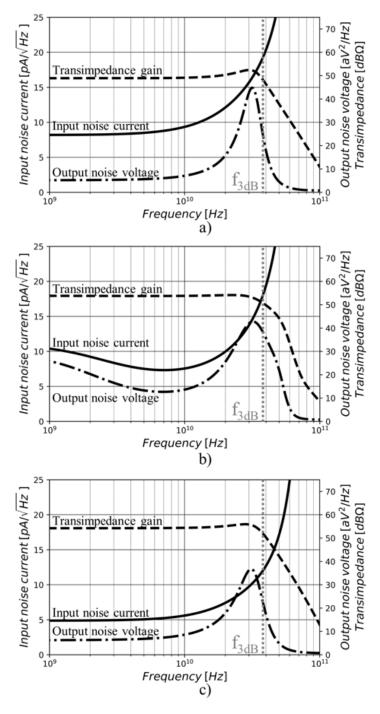

The input-referred current noise and output voltage noise spectral densities are plotted in Fig. 2.11. The input current noise is generally assumed to be approximated by a white noise component and a  $f^2$  region.

$$\frac{I_{n,ckt}^2}{\Delta f} = \alpha_0 + \alpha_2 f^2 \tag{2.6}$$

where  $\alpha_0$  and  $\alpha_2$  are the white noise and violet noise parameters. The white noise parameter is typically due to the TIA feedback resistor thermal noise and the base shot

Figure 2.11: a) Balanced, b) unbalanced, and c) AC-coupled receivers simulated input-referred noise current spectral density, output noise voltage spectral density, and transimpedance.

noise contribution at the input. The violet noise contribution is related to the input device collector shot noise and the base resistance thermal noise. Both have a white spectrum and are transformed into  $f^2$  components as they are referred back to the input and are roughly proportional to  $C_j^2$  [19]. The DC input-referred noise level is lowest for the AC-coupled TIA and is larger for the balanced and unbalanced TIAs. The input referred noise current density in all three cases generally follows the white and violet noise power spectrum.

At low frequency, the dominant noise contributor of the unbalanced TIA is the emitter degeneration resistance of the biasing current mirror. However, it is a negligible fraction of the total integrated output noise voltage. At high frequency, the input noise current spectral density exhibits a  $f^2$  dependence. In all variants the shape of the output voltage noise spectral densities suggests that the  $f^2$  terms dominate the output rms noise, since most of the area under the curve is found after the  $f^2$  terms have begun to dominate. The main noise contributor in all variants is the collector shot noise, which scales with  $f^2$ . The second most-significant contribution in both the balanced and unbalanced receivers is the  $R_f$  thermal white noise. In the AC-coupled receiver, the NPN base resistance is the secondary contributor because its input referred current noise is proportional to  $C_i^2$ , the value of which is effectively doubled with respect to ground when both PD terminals are connected to the differential inputs. Due to the asymmetry of the unbalanced TIA, the contribution of the collector shot noise on the PD-connected terminal is about twice as large as that of the other NPN, and the  $R'_f$  contribution is eliminated. The input-referred peak-to-peak current sensitivities  $(i_{sens})$  for  $BER = 10^{-12}$  are listed in Table 2.1. In the remainder of this chapter,  $i_{sens}$  will only refer to sensitivities for  $BER = 10^{-12}$ .

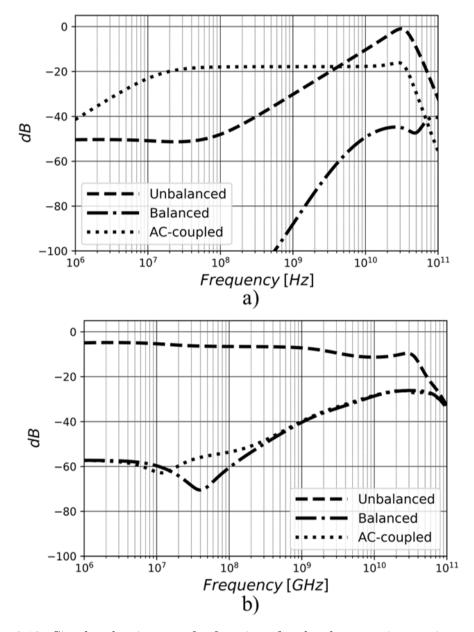

#### 2.4.4 Noise Transfer Functions

The input-referred current sensitivities do not consider the impact of the noise from the power supplies, which can be significant in practical environments with limited capacitive decoupling. Fig. 2.12 shows the transfer functions of the noise from the PD supply and the CHEF TIA voltage supply of the three receiver variants. The PD supply noise transfer functions show that the balanced variant noise gain is over 20 dB lower than the AC-coupled receiver below 40 GHz, and below 60 GHz with respect to the unbalanced variant. This is because the PD supply noise couples to only one of the TIA inputs in both the unbalanced and AC-coupled variants, while it couples to both inputs in the balanced variant and is cancelled out due to common-mode rejection. The CHEF TIA supply noise gain transfer functions of the AC-coupled and balanced variants are nearly identical, and over 10 dB lower than the unbalanced variant for frequencies below 40 GHz. Given that the off-chip capacitor connected to one of the TIA inputs unbalances the differential amplifier of the unbalanced variant, noise from the supply rails are present at the outputs.

The simulated impact of the PD and TIA supply noises on the input-referred sensitivity is investigated by varying their spectral densities while assuming they are white. The supply noise is then integrated and added to the previously calculated circuit noise. It is assumed that they are uncorrelated. The resulting input-referred sensitivity currents and optical modulation amplitudes (OMA) in  $\mu$ W are shown in Fig. 2.13. For PD noise power spectral densities (PSD) below 3 x 10<sup>-14</sup> V<sup>2</sup>/Hz the AC-coupled variant is the most sensitive and for higher PSD, the balanced variant is more sensitive. It can be observed that the unbalanced variant is never more sensitive than the AC-coupled since their slopes are equal once the PD supply noise dominates. Similarly, for TIA supply PSD below 3 x 10<sup>-15</sup> V<sup>2</sup>/Hz the AC-coupled receiver is the most sensitive, and at higher

Figure 2.12: Simulated noise transfer functions for the three receiver variants of the a) PD voltage supply and b) the CHEF TIA voltage supply.

densities the balanced variant performs the best. As expected from the noise transfer functions, as TIA supply noise increases, the unbalanced and AC-coupled tend to have an equal input-referred sensitivity.

Figure 2.13: Simulated input-referred sensitivity and OMA vs a) PD supply and b) TIA VCC supply noise spectral densities, assuming both have white noise spectrums.

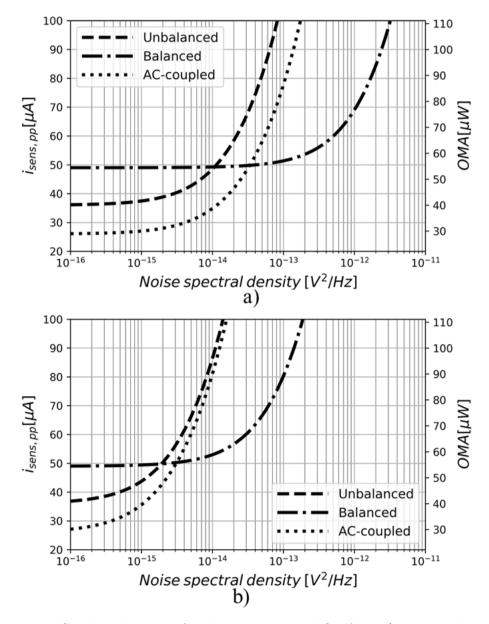

# 2.4.5 Eye-diagram Simulations

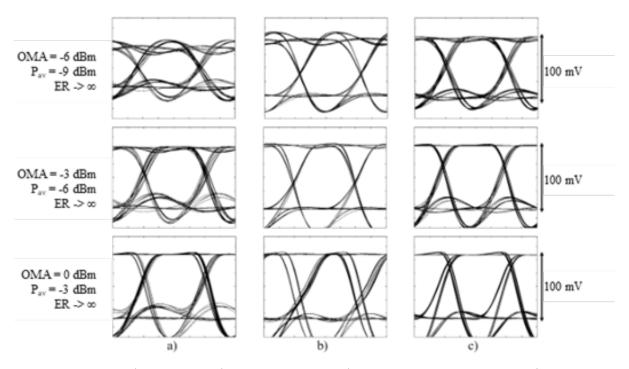

Simulated eye diagrams for an input current of 100  $\mu$ A<sub>pp</sub> are plotted in Fig. 2.14. In all transient simulations, including sections 2.4.6 and 2.4.7, the output DC voltage is eliminated. The greater GDV of the balanced and AC-coupled receivers translates to

Figure 2.14: a) Balanced, b) unbalanced, and c) AC-coupled receiver 50 Gb/s simulated eye-diagrams with PD current of 100  $\mu$ A<sub>pp</sub> at infinite extinction ratio (ER).

jitter in the time domain. The unbalanced receiver, which has the lowest GDV, shows very sharp crossings. Given that the signal is not limited at that current input swing, the midband  $R_T$  difference among the variants results in varying eye amplitudes.

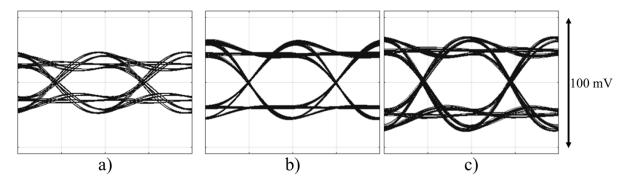

## 2.4.6 Dynamic Range

Transient simulations were done at various average input signal power levels in order to qualitatively compare the dynamic range of the three receiver variants. In general, nonlinear distortion does not limit the BER as a function of signal power because at high enough input power the TIA output becomes limited and thereby compressed. Instead, the increase in nonlinearities that result in a larger GDV are what increase the BER due to increased jitter in the crossings. Fig. 2.15 shows the simulated eye-diagrams for each variant at -6, -3 and 0 dBm of OMA and infinite ER. While the eye distortion is noticeable in all variants, the increase in jitter is more significant in the unbalanced and AC-coupled variants as the signal power increases.

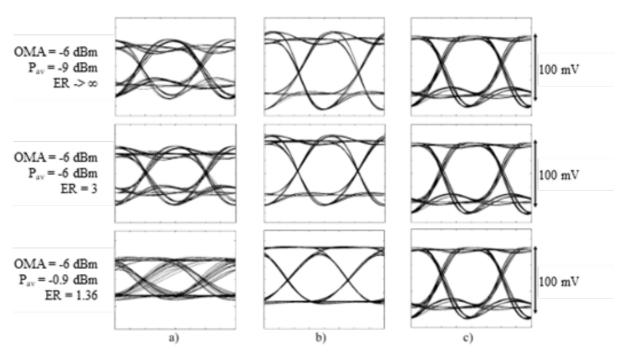

### 2.4.7 DC Phocurrent Overload

The ER of the received signal can vary, e.g. the signal is emphasized at high-frequencies, and the average signal power for a given OMA is usually increased. There-

Figure 2.15: a) Balanced, b) unbalanced, and c) AC-coupled receiver 50 Gb/s simulated eye-diagrams at various input signal power levels with infinite ER.

fore, another important design characteristic is the capacity for the receiver to handle large DC currents even when these are differentially balanced. This is also important in coherent receivers, where the optical signal is mixed with a local oscillator (LO) to increase the signal power. As the LO power increases relative to that of the optical signal, the DC photocurrent for a given current swing also rises [23]. Fig. 2.16 contains output eye-diagrams for the three receivers at varying ERs at a fixed OMA of -6 dBm. This corresponds to 227  $\mu A_{pp}$ . The first and second rows correspond to infinite ER, and ER = 3, respectively. In all the receiver variants, there is no notable difference between the two DC operating points. However, as the ER is reduced to 1.36, which is represented on the third row, the balanced variant shows a significant increase in jitter. An ER of 1.36 is chosen since it results from a LO and signal power ratio of 16 dB, which is feasible in a coherent receiver. The balanced variant shows a slight increase in ISI (intersymbol interference) in comparison with the eye at ER = 3. The AC-coupled variant performance

Figure 2.16: a) Balanced, b) unbalanced, and c) AC-coupled receiver 50 Gb/s simulated eye-diagrams at a fixed OMA and various ERs.

remains unchanged, because no DC current passes into the input of the TIA. However, this simulation uses a small-signal PD model, and thus does not capture the increased drop across the  $R_1$  resistors due to DC photocurrent. This reduces the PD reverse bias voltage and may decrease the BW of the PD.

Table 2.1 contains a summary of the performance characteristics discussed in section 2.4.

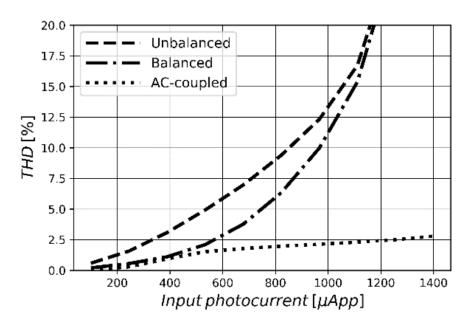

## 2.5 PAM4 Simulations

While NRZ links typically employ limiting TIAs, PAM4 signaling requires the TIA operation to be linear. The optical receivers described in this work do not have limiting amplifiers and are expected to have a sufficiently large linear range for PAM4 operation. The total harmonic distortion (THD) of the three variants is shown in Fig. 2.17. The

|                                                                            | Balanced<br>Differential     | Unbalanced<br>Differential   | AC-coupled               |

|----------------------------------------------------------------------------|------------------------------|------------------------------|--------------------------|

| Midband transimpedance $(R_T)$ [dB $\Omega$ ]                              | 48.9                         | 53.9                         | 54.1                     |

| 3dB BW [GHz]                                                               | 40.3                         | 37.6                         | 38.6                     |

| DC cutoff [MHz]                                                            | 0                            | 0                            | 20                       |

| GDV [ps] <sup>a</sup>                                                      | 17                           | 6                            | 12                       |

| $BER = 10^{-12} \text{ Sensitivity}$ $(i_{sens})[\mu App] / OMA$ $[dBm]^b$ | 49 / -12.7                   | 36 / -14                     | 26 / -15.4               |

| Input-referred current noise density [pA/Hz <sup>1/2</sup> ]               | 17.5                         | 11.6                         | 9.6                      |

| Output DC voltage offset elimination                                       | Requires<br>DCLR and<br>DCOC | Requires<br>DCLR and<br>DCOC | Only<br>requires<br>DCOC |

| Power (PDC) [mW]                                                           | 53.8                         | 53.8                         | 53.8                     |

| Power efficiency at 50<br>Gb/s [pJ/bit]                                    | 1.08                         | 1.08                         | 1.08                     |

<sup>&</sup>lt;sup>a</sup>The GDV is evaluated from 1 GHz to the 3dB BW

Table 2.1: Receiver Variants Performance Comparison

Figure 2.17: THD as a function of input photocurrent swing for the three receiver variants.

<sup>&</sup>lt;sup>b</sup>The photodiode responsivity is 0.9 A/W and infinite ER

input power was swept by varying the peak-to-peak amplitude of a 1 GHz sinusoidal input. The balanced receiver THD is about half that of the unbalanced receiver's up to 800  $\mu$ A<sub>pp</sub>, and they converge above 1.1 mA<sub>pp</sub>. The AC-coupled receiver performs significantly better with a THD below 3% up to 1.4 mA<sub>pp</sub>. This is due to a reduction of the second-order harmonic by approximately 24 dB with respect to the unbalanced receiver.

Fig. 2.18 shows the TIA output PAM4 eye diagrams at 25 Gbaud (50 Gb/s) for the three receiver variants. The decrease in symbol rate from 50 Gbaud OOK to 25 Gbaud

Figure 2.18: Simulated 25 Gbaud PAM4 eye diagrams for the a) balanced, b) unbalanced, and c) AC-coupled receiver variants for a TIA input current of 150  $\mu$ App. This current swing is above the BER = 10-12 sensitivity of all the variants.

PAM4 results in a lower TIA target BW to approximately 20 GHz. To decrease the transimpedance BW, the TIA supply and biases are lowered with respect to those shown

Chapter 2

# 2.6 Experimental Results

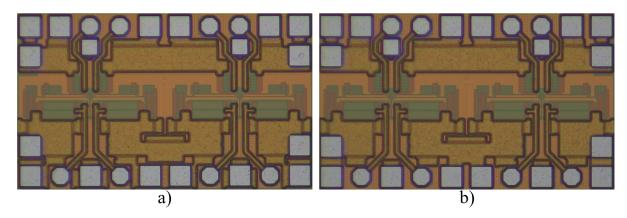

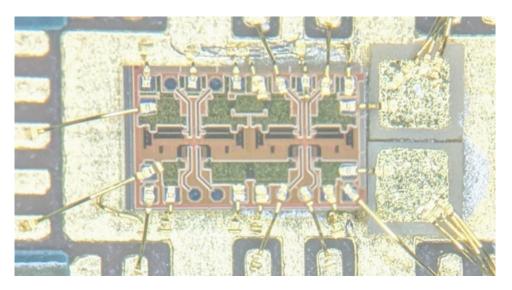

## 2.6.1 Optical Receiver Assembly

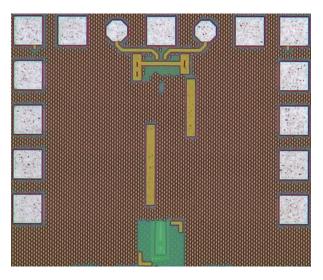

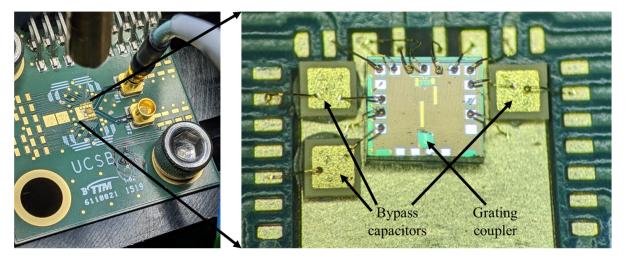

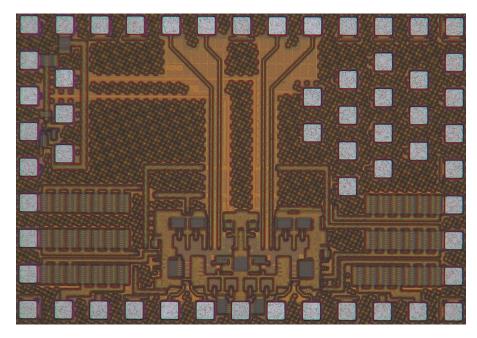

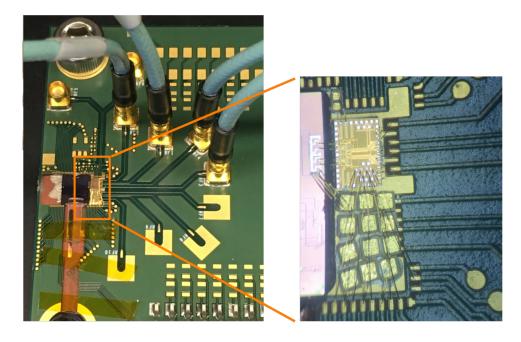

The receivers were implemented on the IHP SG25H4\_EPIC process that combines BiCMOS with silicon photonic devices. The total chip dimensions, limited by the bond pad frame, are less than 1 mm x 1 mm, and the bondpad pitch is 150 µm. The PD and active electronics occupy 130 µm x 120 µm. The AC-coupled receiver variant is shown in Fig. 2.19. The ICs of the other two variants have the same padframe. Each receiver was wire-bonded to custom-built PCBs, as shown in Fig. 2.20. Mini SMP connectors rated for up to 65 GHz were used for the TIA outputs and broadband 1.2 nF capacitors were added to each DC power supply. Additionally, on chip bypassing capacitors provide PD supply low-pass filtering above 240 MHz in the balanced and unbalanced receivers.

#### 2.6.2 Bias conditions

All the variants were designed for the same 3.6V VCC supply and the bias currents detailed in Fig. 2.6. However, it is predicted that the deviation of the Cherry-Hooper resistances due to variations in the fabrication process resulted in a change in the optimal VCC voltage and current of the unbalanced variant's CHEF TIA to 4 V and 10.3

Figure 2.19: Photograph of the AC-coupled variant. The IC area is less than 1 x 1 mm and is bondpad-limited. The bondpad pitch is 150  $\mu$ m. The PD and active electronics occupy 130  $\mu$ m x 120  $\mu$ m. The two octagonal pads are the RF outputs. The balanced and unbalanced variants have the same IC padframe.

Figure 2.20: Optical receiver assembly. The optical fiber probe and RF connectors are shown on the left-hand picture. On the right, the wire bonded assembly is shown. Each of the three receiver variants was assembled as shown.

mA. Similarly, since the bias currents are set by current mirrors that are sensitive to resistor variations, the output buffer bias currents varied from 3.6 to 5 mA, which lead to variations among the output voltage swings. In the balanced and unbalanced variants, the bias across the PD was 4V. In the AC-coupled variant the bias across the two  $R_1$

resistors and the PD was 5.3 V. This corresponds to 4 V across the photodiode for a photocurrent of 325  $\mu$ A, due to the drop across the R1 resistors. The photodiode biases were determined by increasing the voltage until there was no noticeable improvement in sensitivity. In the balanced and unbalanced variants DCLR was implemented off-chip by measuring the PD current and sourcing an equal current to the other differential input.

#### 2.6.3 Measurements

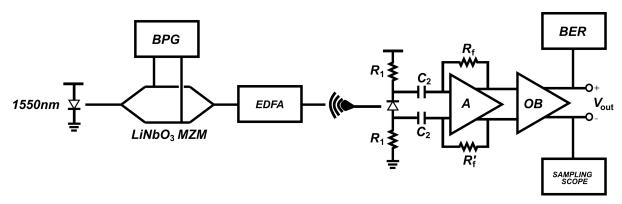

Fig. 2.21 shows setup for eye-diagram and BER measurements. The optical NRZ sig-

Figure 2.21: BER vs power measurement setup for the AC-coupled variant. The setup is the same for the other two variants.

nal is generated by modulating a 1550 nm laser with a LiNbO $_3$  Mach-Zehnder modulator (MZM).

The signal is then amplified and coupled to the DUT and the differential outputs of the TIA are connected to the bit error-rate tester (BER) and a sampling oscilloscope. The bit pattern generator (BPG) contains multiple independent channels with adjustable skew and amplitude, each of which has non-inverted and inverted outputs. The MZM has two differential high-frequency inputs. This allows for two methods of driving it. In the first (without equalization), the MZM inputs are connected to the non-inverted and inverted outputs of a single BPG channel. In the second (with equalization), the MZM inputs are connected to the non-inverted outputs of two separate BPG channels with different amplitudes and a time skew between them to produce a feed forward equalizer (FFE), as described in [24].

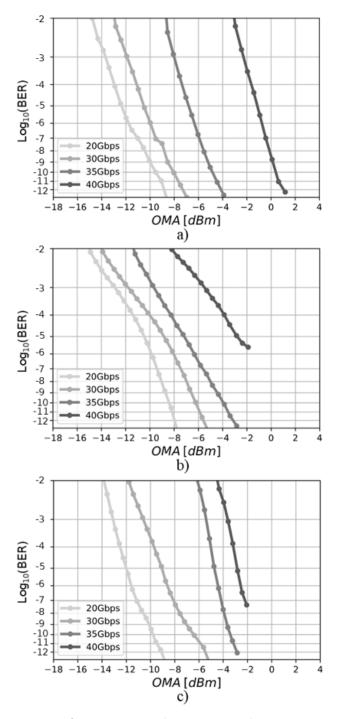

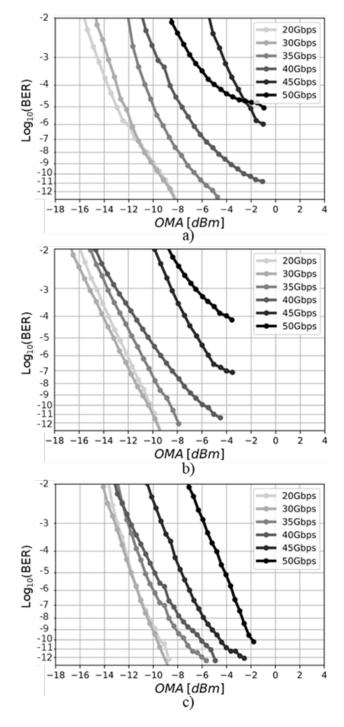

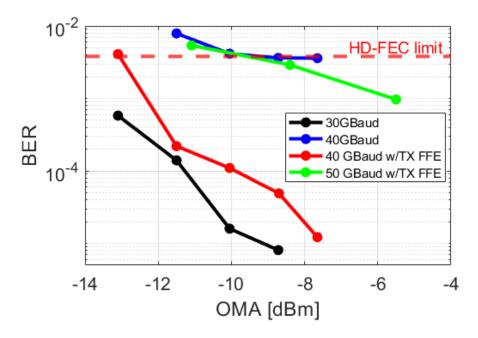

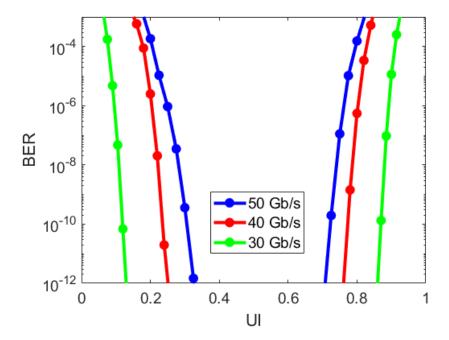

A script was developed to measure BER as a function of OMA which runs two attenuation sweeps for each bitrate. The first sweep is used to find the optimal bit sampling point, and the second to find the BER at varying OMAs at that fixed sampling point. Each BER value was evaluated until at least 5 errors were found or the time corresponding to 5 errors at BER =  $10^{-12}$  passed. In the balanced and unbalanced variants, the photocurrent is measured at each attenuation point and an equal current is fed into the other TIA input to emulate DCLR control loops. A PRBS31 run length was used in the balanced and unbalanced receivers, and for the AC-coupled variant, due to the 20 MHz DC-cutoff, the run length was reduced to PRBS7. For measurements without TX equalization, the MZM was biased at quadrature and the BPG signal amplitude was adjusted to obtain a  $V_{\pi}$  peak-to-peak swing. The data for all three receivers is shown in Fig. 2.22. The ER was measured to be 40, and therefore  $OMA \approx P_{av} + 3dB$ . The measured OMA values for BER =  $10^{-12}$  are -9 dBm, -8 dBm, and -9 dBm, and hence the  $i_{sens}$  are 114  $\mu A_{pp}$ , 143  $\mu A_{pp}$ , 114  $\mu A_{pp}$ , for the balanced, unbalanced and AC-coupled variants, respectively. By referring to Fig. 2.13 and the simulated i<sub>sens</sub> values in Table 2.1, we deduce that the VPD and VCC supply noise contribute significantly to the inputreferred sensitivity in all three cases. The balanced receiver's measured sensitivity is 3.7 dB higher than the simulated one. This difference is 6 dB and 6.4 dB for the unbalanced and AC-coupled receivers, which is consistent with the fact that the balanced variant is the most tolerant to supply noise. At 40 Gb/s only the balanced variant achieves BER < 10<sup>-12</sup>, since the other two variants saturate at -2 dBm of OMA. The overload simulations shown in section 2.4 show that the balanced variant has a slightly better performance at 0 dBm. This may explain its higher dynamic range.

Figure 2.22: BER vs Pav for at various data rates without TX pre-emphasis for the a) balanced, b) unbalanced, and c) AC-coupled receiver variants.

For the BER vs  $P_{av}$  measurements with TX equalization, the MZM bias was set to quadrature, one input (main) amplitude was maintained as in the no TX equalization

configuration, and the amplitude and skew of the other input signal (tap) was adjusted to optimize the BER vs  $P_{av}$  performance. The optimal tap amplitude was found to be half of the main amplitude. This resulted in  $ER \approx 3$ , and so  $OMA \approx P_{av}$ . The optimal skew was found to be 0.5 UI. The same test script was used to obtain the data, which is presented in Fig. 2.23. At 20 Gb/s the BER response is approximately the same as without TX equalization because the power penalty due to ISI is expected to be low. The 30 Gb/s BER curve overlaps with the 20 Gb/s curve. This indicates that the total receiver BW is enhanced and that a minimum ISI sensitivity penalty is achieved. At 35 Gb/s the BER curves shift between 3 and 5 dB towards lower OMAs is observed. The increased BW now makes it possible to measure the BER at 45 and 50 Gb/s. The balanced and unbalanced receivers saturate at lower OMAs in comparison with the unequalized measurements. This agrees with section 2.4.7, where it was shown that these variants are less tolerant to high DC currents. This is because with TX equalization the received Pav for a given OMA is 3 dB higher than without equalization. A BER below  $10^{-10}$  at 50 Gb/s was achieved for the AC-coupled variant.

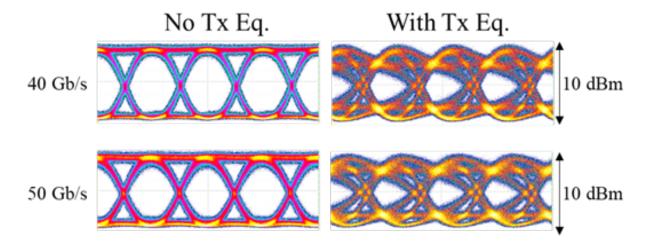

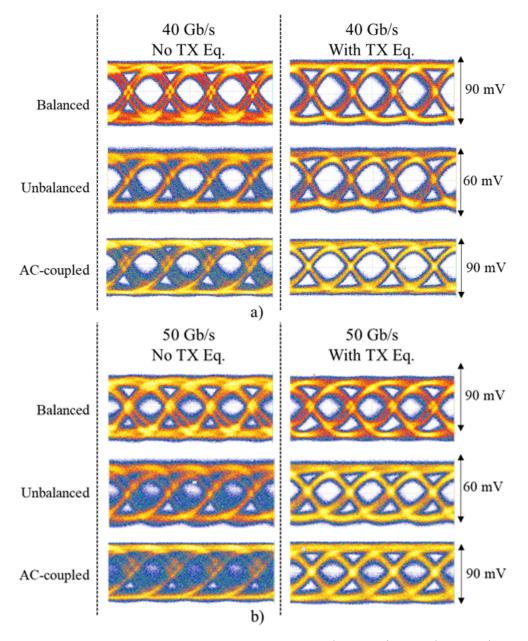

Transmitter (TX) eye-diagrams are shown in Fig. 2.24. At 50 Gb/s without equalization, it can be observed that there is no eye closure at the TX output as the optical link is not limited by the MZM BW, and instead by the packaged optical receiver BW. The TIA output eye-diagrams are taken at a signal power between -5 and -3 dBm and graphed in Fig. 2.25. At 40 Gb/s without TX equalization, the unbalanced and AC-coupled eye-diagrams appear overloaded due to high current swing. At 50 Gb/s without equalization, the balanced variant performs the best while all variants have severe eye closure. At the same data rate with equalization, the eyes are similar as expected from the BER as a function of P<sub>av</sub>. However, as the signal power is increased, the balanced and unbalanced receivers deteriorate before the AC-coupled variant, which can be attributed to a better tolerance to a high DC photocurrent.

Figure 2.23: BER vs Pav for at various data rates with TX pre-emphasis for the a) balanced, b) unbalanced, and c) AC-coupled receiver variants.

Figure 2.24: Measured TX eye-diagrams taken at the output of the MZM using an optical module on the sampling oscilloscope.

The receivers nominally consume 54 mW of power, which corresponds to 1.08 pJ/bit at 50 Gb/s. Simulations show that this figure would increase for a higher required output voltage swing, e.g. to 1.62 pJ/bit for a single-ended output of 150 mV<sub>pp</sub>, since the output stage would require 3 V and a tail current of 6 mA. A comparison of the three receiver variants described in this chapter with state-of-the-art optical receivers is shown in Table 2.2.

## 2.7 Conclusion

A comparison of the three most common optical receiver topologies employing differential TIAs was presented. This analysis considered the tradeoffs in midband RT, BW, GDV, sensitivity, tolerance to supply noise, dynamic range, DC current overload, and output DC voltage cancellation.

Also, the case for the monolithic integration of optical receivers was made by showing the improvement of the transimpedance limit due to the elimination of packaging parasitics. The three receiver variants, which were implemented monolithically in the

Figure 2.25: Measured TIA output eye-diagrams at a) 40 Gb/s and b) 50 Gb/s taken between -5 and -3 dBm of average signal power.

SG25H4\_EPIC IHP BiCMOS process, were packaged and measured. BER vs  $P_{av}$  measurement data was presented, and eye-diagrams were shown.

In summary, the optimal receiver architecture depends on design priorities and the application setting. In our three variants the PD BW is much higher than the required

BW for the target data rate of 50 Gb/s, so the choice of architecture does not determine the total receiver BW. However, the midband transimpedance does depend heavily on the type of frontend. The unbalanced and AC-coupled variants have roughly twice the  $R_T$  as the balanced receiver. This can save power by reducing the amount of limiting amplifier stages required to obtain a specified output voltage swing. The input-referred sensitivity also varies significantly among the different variants. In low-noise environments the AC-coupled variant is more sensitive. However, in an environment where the PD and TIA supplies are noisy the balanced receiver is a better choice. The combined power penalties from ISI and a high input-referred sensitivity may lead to large OMA and DC photocurrents. Therefore, under conditions where the BW requirements are very stringent and/or the environment noise dominates, the dynamic range and DC power handling of the receiver is critical. The balanced receiver performs best at high OMAs, as evinced by the no TX eq. BER measurements. The BER measurements with TX eq. showed that the AC-coupled receiver is superior at high DC photocurrents, which may eliminate the need for DC current sink control. An additional benefit of the ACcoupled variant that results in reduced circuit complexity is that DCLR control is not required, which can save power. The main disadvantage of the AC-coupled variant is the DC-cutoff, which limits the maximum run-length it can tolerate.

| Reference              | Technology           | Integration<br>Level | OE<br>BW<br>(GHz) | Data<br>Rate<br>(Gbaud) | $egin{array}{c} \mathbf{R_T} \\ (\mathbf{dB}\Omega) \end{array}$ | $egin{array}{c} \mathrm{PD} \\ \mathrm{Resp.} \\ \mathrm{(A/W)} \end{array}$ |      | $\begin{array}{ c c }\hline \textbf{IRNCD} \\ (pA/\sqrt{Hz})\end{array}$ | $egin{array}{c} P_{DC} \ (mW) \end{array}$ | Energy<br>efficiency<br>(pJ/bit) |

|------------------------|----------------------|----------------------|-------------------|-------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|------|--------------------------------------------------------------------------|--------------------------------------------|----------------------------------|

| This work <sup>a</sup> | 250nm SiGe<br>BiCMOS | Monolithic           | 37.6              | 50                      | 53.9                                                             | 0.9                                                                          | 3.5  | 17.5                                                                     | 54                                         | 1.08                             |

| This work <sup>b</sup> | 250nm SiGe<br>BiCMOS | Monolithic           | 37.6              | 50                      | 53.9                                                             | 0.9                                                                          | 2.57 | 11.6                                                                     | 54                                         | 1.08                             |

| This work <sup>c</sup> | 250nm SiGe<br>BiCMOS | Monolithic           | 38.6              | 50                      | 54.1                                                             | 0.9                                                                          | 1.86 | 9.6                                                                      | 54                                         | 1.08                             |

| [25]                   | 250nm SiGe<br>BiCMOS | Monolithic           | 34                | 56                      | 66                                                               | 0.7                                                                          | 2.08 | 11.3                                                                     | 205                                        | 3.66                             |

| [26]                   | 250nm SiGe<br>BiCMOS | Monolithic           | 31                | 40                      | 65                                                               | 0.8                                                                          | 5    | 28.1                                                                     | 275                                        | 6.88                             |

| [27]                   | 55nm SiGe<br>BiCMOS  | Hybrid               | N/A               | 56                      | 72.5                                                             | 0.8                                                                          | 2.2  | N/A                                                                      | 170                                        | 3.04                             |

| [28]                   | 130nm SiGe<br>BiCMOS | Hybrid               | 28                | 40                      | 80                                                               | 0.75                                                                         | N/A  | 14                                                                       | 77                                         | 1.93                             |

| [29]                   | 130nm SiGe<br>BiCMOS | Hybrid               | 27                | 34                      | 73                                                               | N/A                                                                          | N/A  | 20                                                                       | 313                                        | 2.30                             |

| [30]                   | 130nm SiGe<br>BiCMOS | Hybrid               | 26                | 32                      | 74                                                               | N/A                                                                          | N/A  | 12.2                                                                     | 218                                        | 4.36                             |

| [31]                   | 40nm CMOS            | Hybrid               | N/A               | 28                      | 68                                                               | N/A                                                                          | 2.56 | N/A                                                                      | 120                                        | 2.14                             |

| [32]                   | 28nm CMOS            | Hybrid               | N/A               | 53                      | 74                                                               | 0.55                                                                         | N/A  | N/A                                                                      | 34.6                                       | 0.65                             |

| [33]                   | 40nm CMOS            | Hybrid               | N/A               | 25                      | 96                                                               | N/A                                                                          | 2.41 | N/A                                                                      | 254                                        | 10.16                            |

| [34]                   | 14nm Fin-<br>FET     | Hybrid               | N/A               | 32                      | 76.9                                                             | 0.52                                                                         | 0.83 | N/A                                                                      | 45                                         | 1.4                              |

Table 2.2: Performance Comparison with State-of-the-Art Optical Receivers

<sup>a</sup>Balanced variant. <sup>b</sup>Unbalanced variant. <sup>c</sup>AC-coupled variant. The noise current values corresponding to this work are from simulations.

# Chapter 3

# 50 GBaud QPSK 0.98 pJ/bit

# Receiver in 45 nm CMOS and 90 nm

# Silicon Photonics

# 3.1 Introduction

There is currently an increasing demand for scalable power-efficient intra-datacenter links. O-band coherent detection has important benefits for use in <2 km optical interconnects. Coherent detection results in higher link margin than the IMDD schemes in use today. This increase in link margin allows for more power efficient network architectures, such as those that utilize optical switching[35]. A key advantage of O-band is that the chromatic dispersion minimum of commercial single-mode fiber is located near 1310 nm, which relaxes DSP requirements.

The energy efficiency of coherent links to be used within the data center will depend heavily on the receiver electronics. Recently, a 56 GBaud monolithic O-band SiGe BiCMOS receiver with a power consumption of 485 mW has been reported[36]. Other

relevant work includes a 34 GBaud DP-QPSK receiver consisting of a SiGe BiCMOS EIC and a SiP PIC with a power consumption of 313 mW per channel[29]. It has been estimated that the front-end transimpedance amplifier (TIA) and limiting amplifiers (LA) implemented in a SiGe BiCMOS, with an assumed combined power consumption of 410 mW, account for >40% of the total power in analog coherent intra-datacenter links that employ silicon photonics. This figure increases to >50% when indium-phosphide optics are utilized[4]. CMOS-based receiver electronics consume significantly less power than those implemented in SiGe BiCMOS, and thus can be a suitable alternative. The recent release of the GlobalFoundries (GF) 45CLO fabrication process demonstrates an industry trend towards monolithic integration of silicon photonics devices with CMOS transistors targeting low-cost, mass-production, and high performance optical transceivers[37], for which low-power receiver topologies will be required.

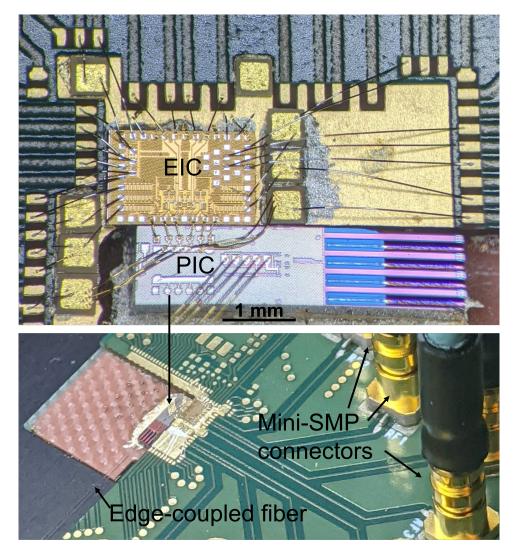

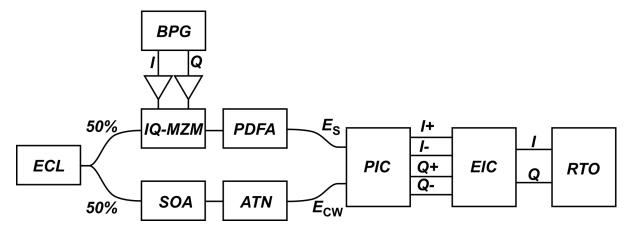

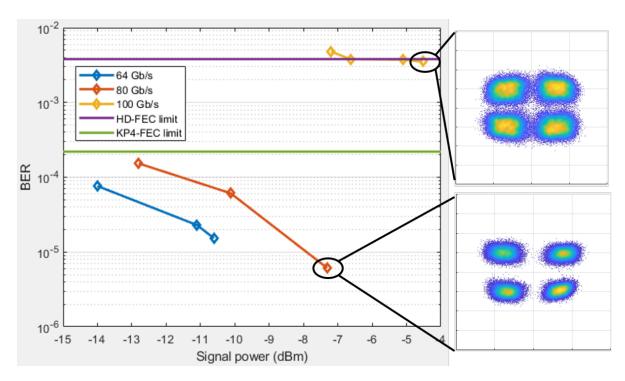

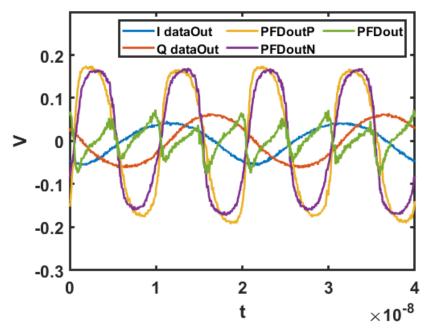

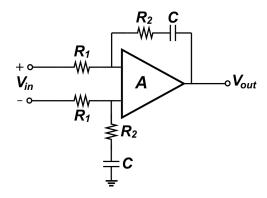

In this chapter, we first present a single-polarization O-band QPSK receiver consisting of an electronic integrated circuit (EIC) fabricated in the GF 45RFSOI 45 nm CMOS process and a photonic integrated circuit (PIC) fabricated in the GF 9WG process. Experimental results demonstrate the operation of the receiver at up to 50 GBaud. We then describe the phase-frequency detector (PFD) and loop-filter OpAmp to be used in a QPSK Costas Loop analog optical coherent receiver.

# 3.2 Coherent Receiver Data Path

# 3.2.1 Receiver Design

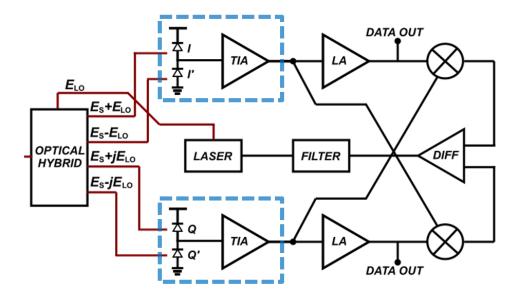

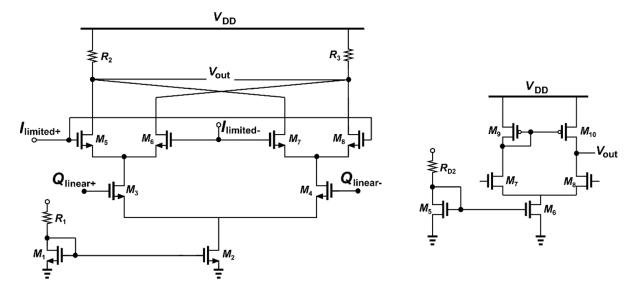

Fig. 3.1 shows a block diagram of the data path of an optical QPSK Costas loop receiver designed for analog coherent intra-datacenter links[35]. The focus of this section, denoted by the dashed area, is the design and characterization of the electronics in the

QPSK data signal path and their integration with the PIC.

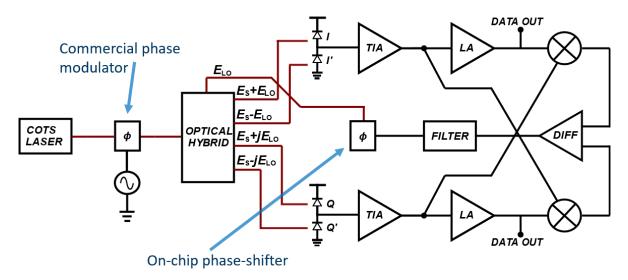

Figure 3.1: Optical QPSK Costas-loop OPLL. The dashed area denotes the work presented in section 3.2.

Figure 3.2: Optical receiver block diagram. The PIC consists of an optical hybrid and 4 photodiodes. The photodiode anodes are connected via wirebonds to the TIA inputs of the EIC.

A block diagram of the PIC and the EIC is shown in Fig. 3.2. The optical hybrid receives a CW laser signal ( $E_{LO}$ ) and a QPSK modulated signal ( $E_{S}$ ) and generates the four signals corresponding to the desired vectorial additions of the two input optical fields, which are routed to two pairs of photodiodes (PD), one for the in-phase (I) channel and

the other for the quadrature channel (Q). The electronics consist of a TIA, a cascode amplifier (CAS), a cascade of LAs, and an output buffer (OB). A slow loop based on a replica TIA and Op-Amps is used for DC-offset compensation (DCOC) and to sink any excess DC photocurrent.

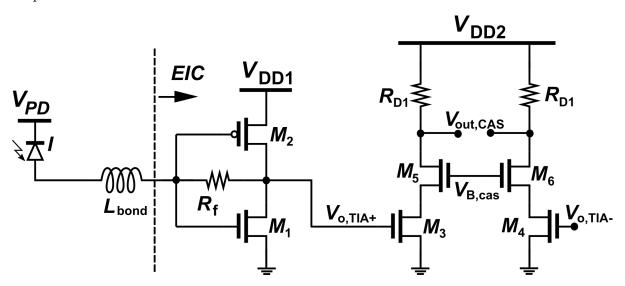

Fig. 3.3 shows the schematic of the receiver TIA and cascode amplifiers. Connected to each PD there is an inverter shunt-feedback TIA. The inverter topology combines both NMOS and PMOS transconductances, resulting in high gain at low power consumption[38, 39] and the pseudodifferential configuration saves power by minimizing the voltage headroom. At the TIA output, a cascode amplifier is used to raise the common-mode voltage to the required value for the subsequent source-coupled limiting amplifiers.

Figure 3.3: Schematic of the receiver TIA and cascode amplifiers.

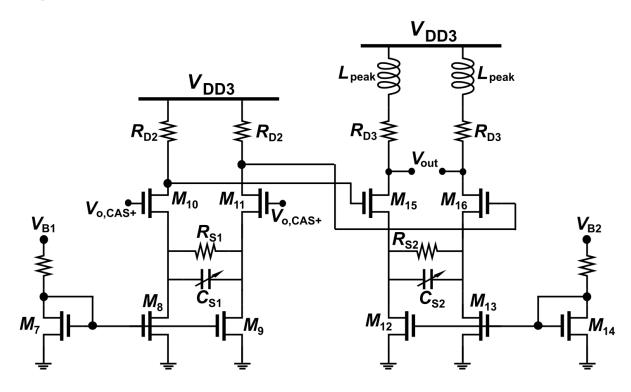

Source-coupled amplifiers were utilized for the LA and OB stages to provide common-mode rejection. The LA chain consists of six cascaded amplifiers of increasing transistor widths to minimize the loading between stages. The schematic of the LA and OB stages, depicted in Fig. 3.4, shows only one of the LA stages.  $R_S$  and varactor  $C_S$  provide tunable equalization. The 50  $\Omega$  OB has shunt inductive peaking to compensate for the

output channel loss.

Figure 3.4: Schematic of the source-coupled limiting amplifiers and output buffer.

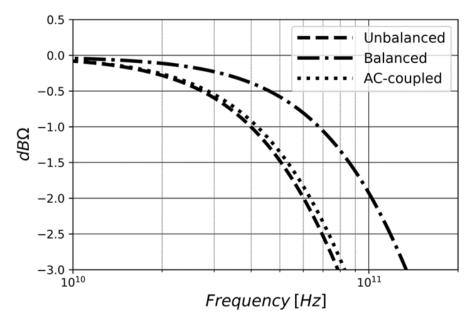

The simulated post-layout 3 dB BW assuming a 40 GHz PD BW, and including wire-bonds and bondpad capacitances, is 23 GHz. The simulated midband transimpedance is  $55 \text{ dB}\Omega$ .

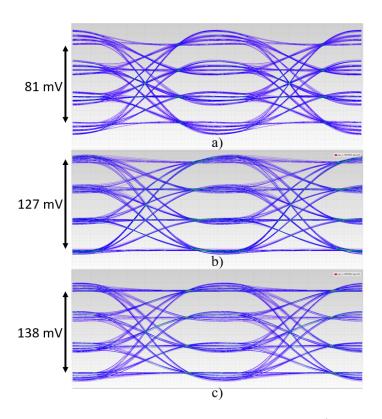

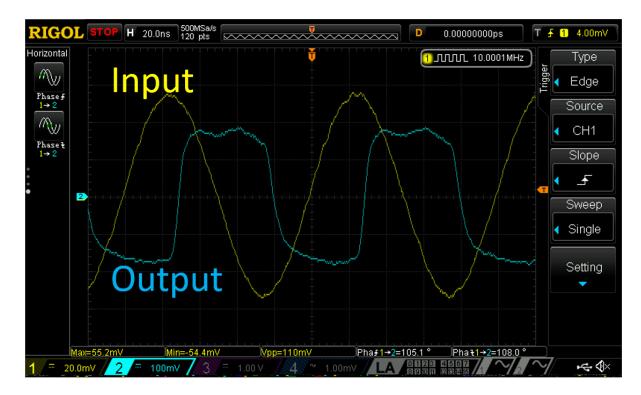

## 3.2.2 Experimental results

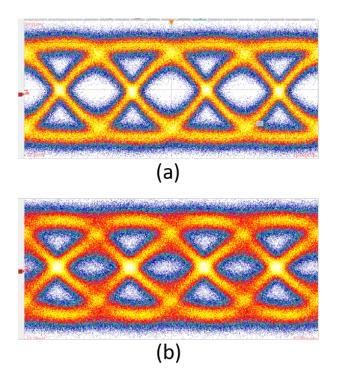

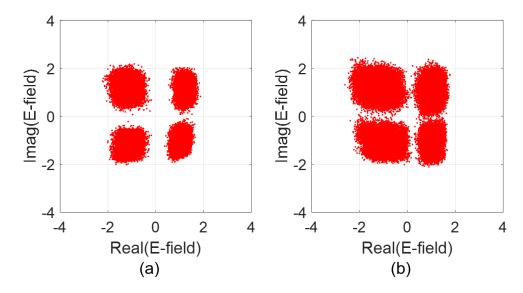

The measured power consumption of the EIC including the OB is 98 mW, or 0.98 pJ/bit for 50 GBaud QPSK transmission. If the OB is omitted, in case a 50  $\Omega$  output is not required, the power is reduced to 77 mW, or 0.77 pJ/bit. The measured output noise of the EIC is 3 mV rms, the midband transimpedance is 477  $\Omega$ , and the calculated input-referred noise is 6.3  $\mu$ A rms. The EIC was initially measured electrically by driving it with a bit-pattern generator (BPG) at a voltage swing equivalent to 136  $\mu$ App. The

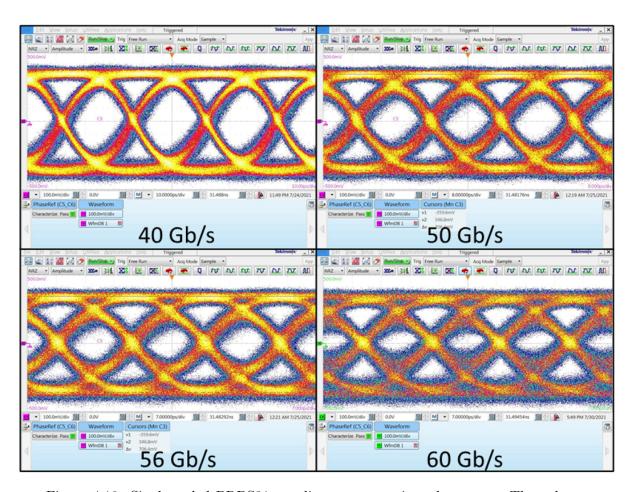

resulting eye diagrams with a voltage swing of 65 mVpp at 40 Gbps and 50 Gbps are shown in Fig. 3.5.

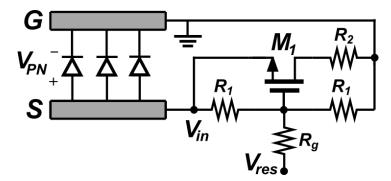

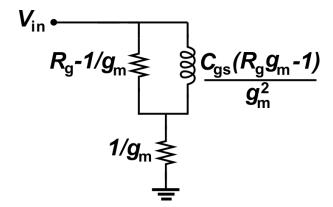

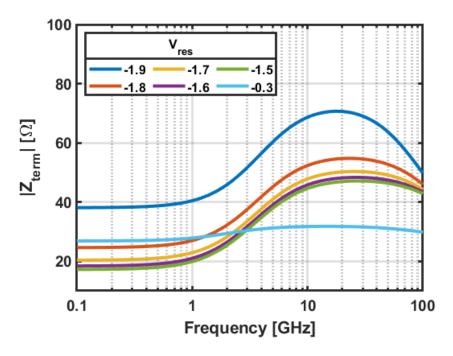

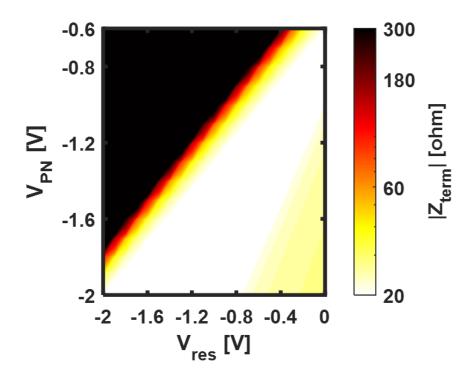

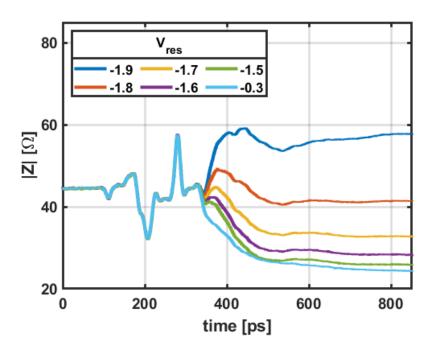

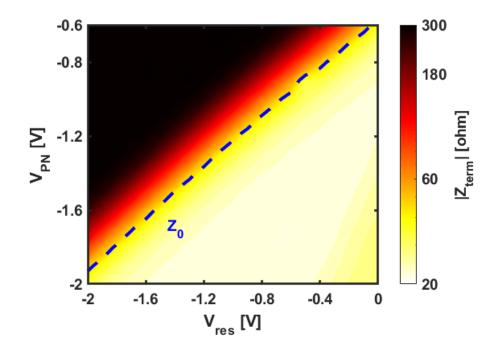

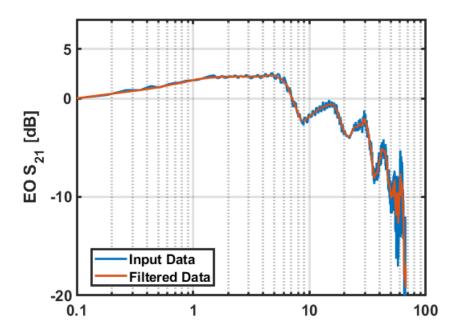

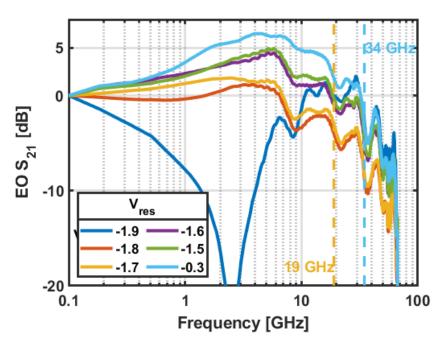

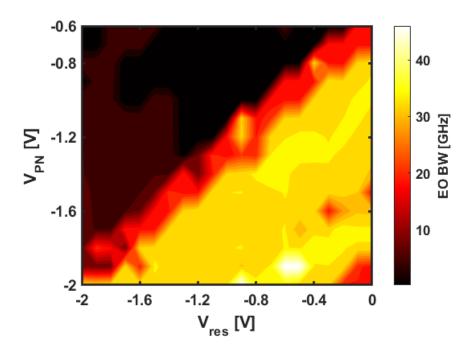

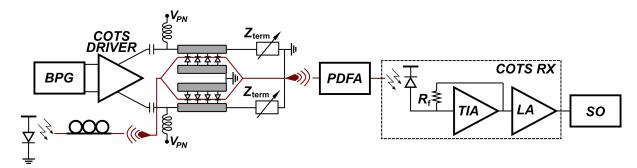

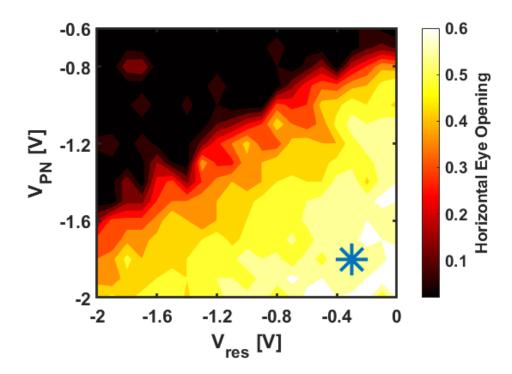

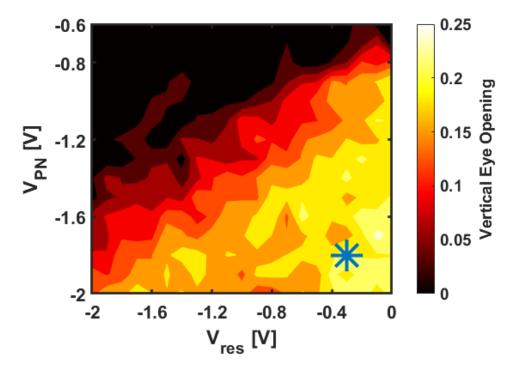

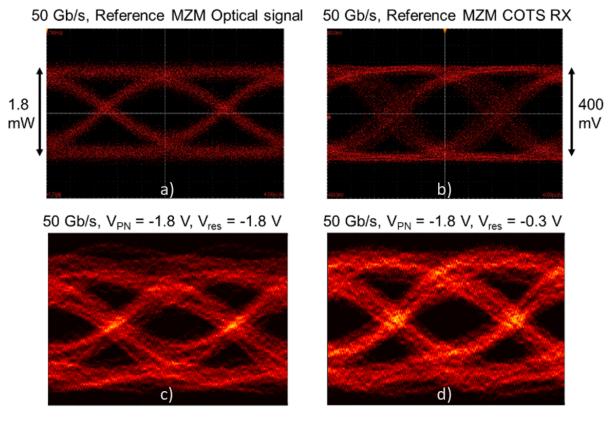

Figure 3.5: Electrical single-ended eye-diagrams at (a) 40 Gbps and (b) 50 Gbps with an input voltage swing equivalent to 136  $\mu$ App. The output voltage swing is 65 mVpp.