## **UC Santa Barbara**

### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Operating Flux-Tunable Superconducting Qubits with High Fidelity

#### **Permalink**

https://escholarship.org/uc/item/83k9v3hx

#### **Author**

Foxen, Brooks Riley

#### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

### UNIVERSITY of CALIFORNIA Santa Barbara

### Operating Flux-Tunable Superconducting Qubits with High Fidelity

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Physics

by

Brooks Riley Foxen

Committee in charge:

Professor John Martinis, Chair

Professor Mark Sherwin

Professor Matthew Fisher

December 2019

|           | The dissertation of Brooks Riley Foxen is approved:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | same of the s |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Professor | Mark Sherwin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Professor | Matthew Fisher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Professor | r John Martinis, Chair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

December 2019

Copyright © 2019 by Brooks Riley Foxen To my parents, Michele and Aaron Campbell, to my partner, Anya Foxen, and to my pets, Abby and Baggins

## Acknowledgements

This work would not have been possible without John Martinis—thank you for building such an incredible lab as well as the teaching and resources necessary for me to complete this work! Similarly, I am indebted to all the members of the UCSB Martinis group and many of the more recent Google additions. Thank you all for your kindness, helpfulness, and for building and sharing the infrastructure this work is build upon.

Pedram, your brought me into this lab on the majorana project and you saw me out with the fSim project. Your love of physics is truly inspiring. It is a joy to see you thrilled by data, day after day, and an even greater joy to (now) often see you promptly pack up at the end of the day to go for a jog, leaving the office at a reasonable time (even if you still return for the night shift). Your dedication and love of physics reminds me how lucky I am to be a part of this group.

Josh, it was a pleasure working with you on the bump bond project, and I would not have made it through the tunable resonator experiment without you. Your friendship and all the runs/bike rides helped keep me going in those middle years, and I am truly thankful for your constant kindness and prospective. Thank you for coming to visit me over in Broida!

Charles, thank you for taking the time to bring me up to speed and mentoring me through out the fSim gate project. It was great learning from you and made an awesome final project.

Jimmy and Andrew, class of 2012 forever! I have asked you both for help more times than I can count over the past seven years. Thank you both for always being generous with your time and for your willingness to teach!

Mom and dad, thank you for the many years of love, support, and encouragement it took to get me here, I could not have done it without you.

Anya, I am so thankful that we had each other through these past several years and I look forward to many more to come!

Abby, thank you for being a good dog and loving me even when graduate school yielded fewer walks than you expected.

Baggins than you for channeling my anxieties... maybe that helped.

### Curriculum Vitæ

#### Brooks Riley Foxen

#### Education

(Ph.D. year) Ph.D., Physics, University of California, Santa Barbara

2007 B.S., Physics, University of Texas, Austin

2004, Grapevine High School, Grapevine

#### **Professional Experience**

2008 Applications Engineer, National Instruments2010 Product Support Engineer, National Instruments

#### First author publications

"High speed flux sampling for tunable superconducting qubits with an embedded cryogenic transducer", B. Foxen, J.Y. Mutus, E. Lucero, E. Jeffrey, D. Sank, R. Barends, K. Arya, B. Burkett, Yu Chen, Zijun Chen, B. Chiaro, A. Dunsworth, A. Fowler, C. Gidney, M. Giustina, R. Graff, T. Huang, J. Kelly, P. Klimov, A. Megrant, O. Naaman, M. Neeley, C. Neill, C. Quintana, P. Roushan, A. Vainsencher, J. Wenner, T.C. White, and John M. Martinis submitted August 2018

"Qubit compatible superconducting interconnects", B. Foxen, J.Y. Mutus, E. Lucero, R. Graff, A. Megrant, Yu Chen, C. Quintana, B. Burkett, J. Kelly, E. Jeffrey, Yan Yang, Anthony Yu, K. Arya, R. Barends, Zijun Chen, B. Chiaro, A. Dunsworth, A. Fowler, C. Gidney, M. Giustina, T. Huang, P. Klimov, M. Neeley, C. Neill, P. Roushan, D. Sank, A. Vainsencher, J. Wenner, T.C. White, John M. Martinis *Quantum Science and Technology* vol 3, 1 (2017)

### Abstract

#### Operating Flux-Tunable Superconducting Qubits with High Fidelity

by

#### Brooks Riley Foxen

The experimental challenge of today's quantum computing engineers is to choose a physical qubit system and whittle away at the multifaceted orders of magnitude improvement needed to build a practical quantum computer. In the first part of this thesis I will provide a general introduction to superconducting qubits and the isolated cryogenic environment in which they operate with an eye towards both the particular design requirements and the challenges we face in accommodating many more qubits in the future. Next, I will present a series of three experiments specifically oriented towards system-level improvements for flux-tunable superconducting qubits. In the first experiment, we develop a new metrology tool to characterize the on-chip settling of magnetic flux waveforms. We then used this technique to develop a new PCB-based packaging solution thereby increasing our package-to-chip wiring limit by at least a factor of ten enabling control of 10x more qubits on a single chip. In the second experiment, we provide a fabrication process for superconducting interconnects which allow for the three dimensional integration of our qubits and a direct factor of 2 improvement in qubit connectivity moving from linear chains to two dimensional grids of qubits enabling  $n^2$  more complex circuits. Finally we implement a hardware-efficient 2-qubit fermionic simulation gateset, proposed to study quantum chemistry, using DC flux control on an adjustable coupling gmon transmon device. This first realization of the complete fSim gateset, of which CZ is a member, yielded nearly a 2x improvement over the best reported Pauli error for a CZ for a solid state system to date, 0.41%, and implements an arbitrary photon conserving and low leakage two qubit unitary operation with a factor of 4 times higher fidelity than a minimally universal gateset using single qubit rotations with only a CZ enabling 4-8x more coherent fSim operations. In total, these improvements have increased the computational complexity of our quantum processor by a factor of 400-800 on the road towards building a practical quantum computer.

# Contents

| 1 | Sup | perconducting qubits                                 |  |   | 1  |

|---|-----|------------------------------------------------------|--|---|----|

|   | 1.1 | Introduction                                         |  |   | 1  |

|   | 1.2 | What is a quantum computer?                          |  |   | 3  |

|   | 1.3 | Superconducting qubits                               |  |   | 6  |

|   | 1.4 | Thesis overview                                      |  |   | 8  |

| 2 | Sup | perconducting Circuits                               |  |   | 10 |

|   | 2.1 | LC oscillator                                        |  |   | 11 |

|   | 2.2 | Josephson junctions                                  |  |   | 15 |

|   | 2.3 | SQUID                                                |  |   | 19 |

|   | 2.4 | Transmon qubits                                      |  |   | 23 |

|   | 2.5 | Used in this thesis                                  |  |   | 28 |

| 3 | Qul | bit system design                                    |  |   | 32 |

|   | 3.1 | Cryogenics                                           |  |   | 34 |

|   |     | 3.1.1 How cold is cold enough?                       |  |   | 37 |

|   | 3.2 | Electronics                                          |  |   | 40 |

|   |     | 3.2.1 Microwave control                              |  |   | 42 |

|   |     | 3.2.2 Frequency control                              |  |   | 47 |

|   | 3.3 | Packaging                                            |  |   | 51 |

|   |     | 3.3.1 Coplanar waveguide resonators as qubit proxies |  |   | 54 |

|   |     | 3.3.2 Coherence check                                |  |   | 57 |

|   |     | 3.3.3 Blackbody radiation                            |  |   | 61 |

|   |     | 3.3.4 Magnetic field shielding                       |  |   | 65 |

|   |     | 3.3.5 Flux bias settling                             |  |   | 67 |

|   |     | 3.3.6 Wire bonding                                   |  |   | 69 |

| 4 | Hig | gh speed on-chip flux measurement                    |  |   | 78 |

| - | 4.1 | Introduction                                         |  | _ | 79 |

|   | 4.2 | Theory of operation                                  |  |   | 81 |

|   | 4.3 | Measurement setup and transducer calibration         |  |   | 85 |

|   | 4.4 | Step response                                        |  |   | 89 |

|   | 4.5 | Package design and device layout                     |  |   | 91 |

|              | 4.6            | Conclusions                                                | 95                |

|--------------|----------------|------------------------------------------------------------|-------------------|

| 5            | <b>Sup</b> 5.1 | erconducting interconnects Introduction                    | <b>97</b><br>98   |

|              | 5.2            | Device fabrication and layout                              |                   |

|              | 5.3            | Electrical characterization                                |                   |

|              | 5.4            | Mechanical characterization                                |                   |

|              | 5.5            | Conclusions                                                |                   |

| 6            | Con            | tinuous Set of Two-qubit Gates                             | 111               |

|              | 6.1            | Introduction                                               | 112               |

|              | 6.2            | Strong coupling with gmon qubits                           | 114               |

|              | 6.3            | Coupled Transmon physics and the fSim gate set             | 116               |

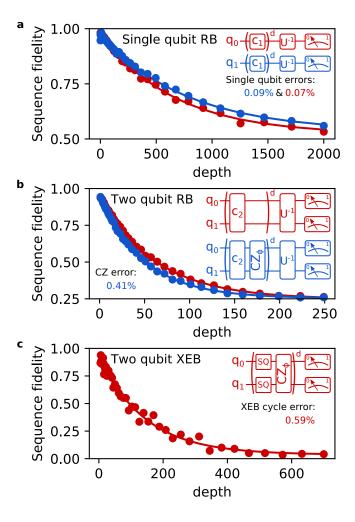

|              | 6.4            | Benchmarking iSWAP-like and CPHASE gates                   |                   |

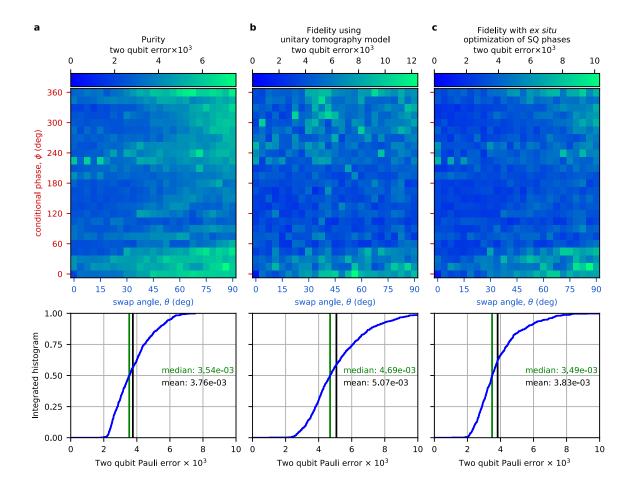

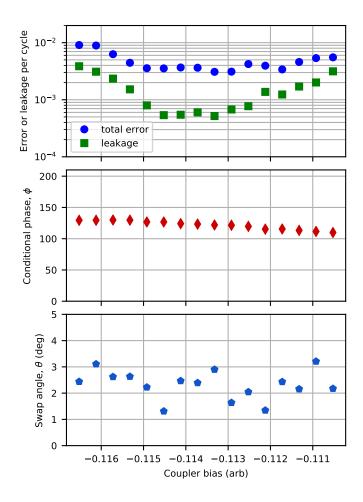

|              | 6.5            | Benchmarking fSim gates                                    | 121               |

|              | 6.6            | Conclusions                                                | 123               |

| $\mathbf{A}$ | Fast           | Flux Measurement Appendices                                | <b>12</b> 4       |

|              | A.1            | Measuring microwave reflections with the tunable resonator | 124               |

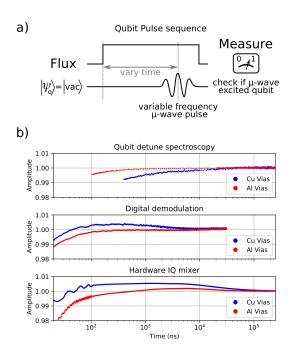

|              | A.2            | Qubit detuning spectroscopy                                | 130               |

|              |                | A.2.1 Device comparison                                    | 133               |

| В            |                | erconducting Interconnect Appendices                       | 135               |

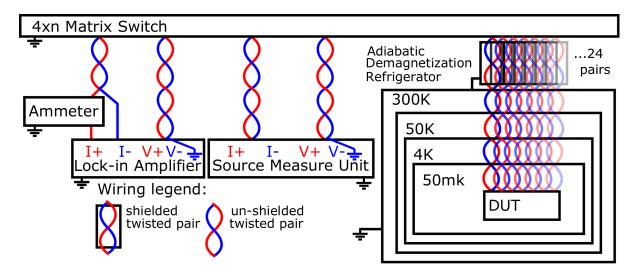

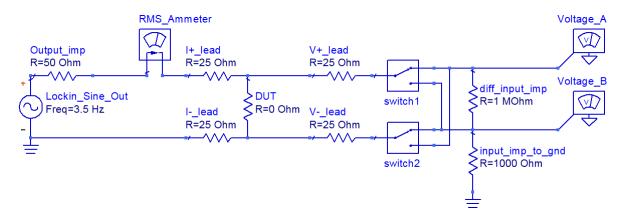

|              | B.1            | Electrical characterization measurement setup              |                   |

|              | B.2            |                                                            |                   |

|              | B.3            | Ion mill parameters                                        | 145               |

| $\mathbf{C}$ |                | n Gate Appendices                                          | 147               |

|              | C.1            | fSim control model                                         |                   |

|              | C.2            | fSim gate numerics                                         |                   |

|              | C.3            | Gate characterization                                      |                   |

|              |                | C.3.1 Computing and reporting Pauli error rates            |                   |

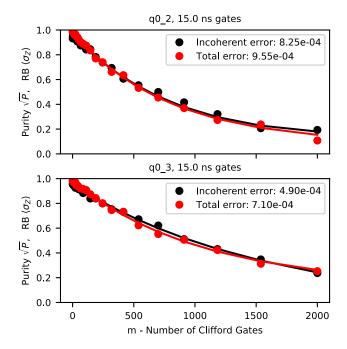

|              |                | C.3.2 Single-qubit coherence and gates                     |                   |

|              |                | C.3.3 Unitary tomography                                   |                   |

|              |                | C.3.4 Cross-entropy error benchmarking                     |                   |

|              |                | C.3.5 RB vs XEB                                            |                   |

|              |                | C.3.6 Error budgeting                                      |                   |

|              |                | C.3.7 Unitary overlap                                      |                   |

|              | C.4            | Control pulse calibration                                  | 167               |

|              |                |                                                            |                   |

|              |                | C.4.1 Electronics calibration                              | 169               |

|              |                | C.4.1 Electronics calibration                              | 169<br>171        |

|              | C.5            | C.4.1 Electronics calibration                              | 169<br>171<br>175 |

Bibliography 181

## Chapter 1

# Superconducting qubits

## 1.1 Introduction

Quantum computers present a potentially revolutionary computational technology. We expect that, once developed, quantum computers will be able to perform some types of computations that are intractable on both existing and even any future classical supercomputers. The precise nature of these applications is somewhat unknown due to the difficultly of proving that solutions are optimal for a given computational problem. Never the less, there are limited examples of a provable speedup for quantum algorithms [1, 2, 3, 4], and many more grey areas where promising quantum algorithms exceed the best known classical algorithm for suspected hard classical problems. Feynman is often credited with formalizing the idea of building a quantum computer in 1982 due to the difficulty of simulating quantum mechanics on classical computers [5]. And today, still, some of the most exciting potential near-term applications involve just that—simulating

quantum dynamics to advance research into materials, energy, and beyond.

Over the past five years, interest in quantum computing has surged. In 2014, superconducting qubits demonstrated performance near the threshold necessary for error correction which indicated that some level of brute-force scaling might be productive [6]. A November 2018 industry report from the Boston Consulting Group identified more than \$700 million in private funding for quantum computing startups and nearly \$6 billion in funding from government led initiatives across the globe since 2012 [7]. Expanding on this report in 2019, they explored the potential commercial value of quantum computing [8]. They broadly consider three types of quantum computers with increasing increasing complexity and computational ability that roughly align with the expected scientific development path. In the near term, they suppose that Noisy Intermediate Scale Quantum (NISQ, [9]) computers may begin to be able to solve materials simulations using error mitigation techniques—they estimate problems of this sort may be worth \$2 to \$5 Billion USD annually. With the addition of some level of error correction, when quantum computers have begun to realize some large scale quantum advantage, BCG estimates the addressable computational value at \$25 to \$50 Billion USD annually. Finally, they assess the value of full-scale fault tolerant quantum computation to be in the range of \$450 to \$850 Billion USD annually! In October 2019 quantum supremacy was achieve with a 53 qubit device performing a well defined computation in 200 seconds that would take 10,000 years on the largest supercomputer in the world, an achievement likely to spark further interest an investment into quantum computing [10].

However, many technical challenges remain before the commercial value of quantum computation may be realized. Current estimates indicate that 10<sup>6</sup> to 10<sup>8</sup> qubits will be necessary to build a moderately sized error corrected quantum computer. Even if we were to ignore the many unsolved challenges in scaling up, the cost of the existing qubit infrastructure, likely \$10,000 to \$25,000 per qubit, is prohibitive. For these reasons, quantum computing researchers must continue to pursue improvements in the quality of the physical qubits and gates to reduce the overall number necessary to achieve error correction and reductions in the cost of the corresponding infrastructure.

## 1.2 What is a quantum computer?

The goal of quantum computing is to harness quantum mechanics to perform computational tasks. The details of how and why that is desirable are subtle, but we can start by considering the instructive, self-referential use case. Quantum mechanics is widely accepted as the most successful quantitative theory ever produced. As such, being able to simulate quantum mechanics in a computer is quite desirable when it comes to understanding chemistry and materials problems. Arbitrarily sized simulations of quantum mechanics might allow for the design of materials like high temperature superconductors, chemical reaction catalysts, more efficient batteries and solar cells, or even help identify candidate drugs [11, 12, 13]. The trouble is that simulating quantum particles requires an exponential overhead of classical resources. That is, simulating n quantum particles requires, in general, storing and computing the evolution of  $2^n$  amplitudes on a classical

computer (that is assuming no a priori knowledge of the system that allows some of these amplitudes to be neglected). While this is easy enough for small n, by the time you reach n = 57, it requires roughly an exabyte ( $10^{18}$  bytes) of storage—more storage than any single supercomputer today. Regardless of the available classical computational resources, with this exponential scaling, there surely exists some such n where one may start to wonder if it might be easier to just control a relatively small number of quantum particles directly. And in this way, one may stumble in to a desire for a quantum computer...

The most basic element of a quantum computer is a quantum bit, or qubit, for those in the know. The designation "qubit" refers to the information content of a quantum system with two states, and not any particular physical implementation of a qubit. While a classical system with two states exists in either one or the other (0 or 1), a qubit may exist in a superposition of both states simultaneously  $|\Psi\rangle = \alpha|0\rangle + \beta|1\rangle$ , where  $\alpha$  and  $\beta$  are complex numbers. The vector  $|\Psi\rangle$  is the quantum mechanical wavefunction, the square of which indicates the probability of finding the qubit in either the  $|0\rangle$  state (probability  $|\alpha|^2$ ) or the  $|1\rangle$  state (probability  $|\beta|^2$ ) if the state of the qubit is measured. Normalization, or the requirement that we find the qubit in either state during measurement, requires that  $|\alpha|^2 + |\beta|^2 = 1$ . After normalization, we may consolidate the remaining three degrees of freedom into one amplitude and two phases,  $|\Psi\rangle = e^{i\phi_g}(\cos\theta/2|0\rangle + e^{i\phi}\sin\theta/2|0\rangle$ ). The global phase,  $\phi_g$ , is inconsequential for a single qubit, further simplifying the state to,

$$|\Psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\phi}\sin\frac{\theta}{2}|1\rangle$$

(1.1)

This representation of an arbitrary qubit superposition may be connected to the Bloch Sphere, where the state  $|\Psi\rangle$  is represented as a point on a sphere where  $\theta$  and  $\phi$  denoted by the azimuthal and equatorial angles [14].

To expand the complexity of this system, a second qubit may be added. An arbitrary wavefunction for 2 qubits will involve four basis states,

$$|\Psi\rangle = \alpha|00\rangle + \beta|01\rangle + \delta|10\rangle + \gamma|11\rangle \tag{1.2}$$

After constraints, it takes  $2^n$  complex amplitudes to describe the wavefunction of an n-qubit system. This is still a bit abstract as most physical quantum systems, like atoms, have many more than just two possible states. Fortunately, with a general enough set of gate operations, a system of qubits may be assembled into a universal quantum computer [15, 16, 17].

So, the task of building a computer consists of choosing a physical system that may be restricted to, and controlled within, a finite number of (at least two) states. Most often this means just two states since controlling the evolution of a three or more level system is likely more difficult than just two levels. Some systems are inherently two-level, like the spin of an electron, or the polarization of a photon. Other systems, like the orbital structure of atoms or the resonant circuits used in superconducting qubits have more than two levels and care must be taken to evolve the state within only the desired subspace of states. After identifying a physical qubit implementation, the task

of building a quantum computer, as outlined by DiVincenzo, is to perform sufficient single and two qubit operations to implement a universal gate set, state preparation, and measurement all in a scalable architecture [18]. The devil, of course, lies in the details, a few of which are considered in this thesis; primarily, the quality and choice of two qubit gates (Chapter 6) and general system scalability concerns for flux tunable superconducting qubits (Chapters 3, 4, and 5).

## 1.3 Superconducting qubits

Superconducting qubits are non-linear electrical resonators—we fabricate ours using aluminum on sapphire, or more recently silicon. When a qubit is excited by placing a photon of energy into the resonator, the excitation produces currents which oscillate back and forth in the circuit. Superconductivity reduces the resistive losses of the currents flowing in the metal, but it is impossible to completely isolate the resonator circuit. The oscillating currents may have some weak interaction with lossy residues from fabrication, lattice imperfections in the substrate, or even a direct coupling to other qubits or resonators intentionally built into the system. Due to these interactions, eventually the energy will leak out of the resonator. This limits the qubit coherence, but also provides a straight forward method of initializing the state of the qubit—just wait long enough and photons will leak out of the qubit (assuming that the qubit's temperature is cold enough that it is not excited thermally). We excite the qubits with an electronic microwave frequency pulse, and, for frequency tunable qubits, we can control the frequency by applying a

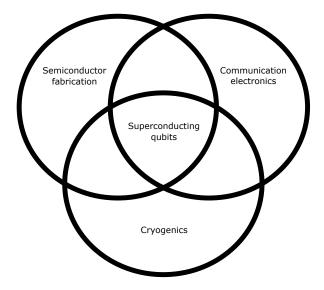

Figure 1.1: Superconducting qubits are an attractive candidate for building a quantum computer because the core technologies they rely on have already been scaled enormously on an individual basis.

magnetic field to the qubit, which we modulate with a control current. To measure the state of the qubit, we couple a linear resonator to each qubit such that the frequency of the linear resonator is dependent on the presence or absence of a photon in the qubit. We then perform a reflective microwave measurement, driving the linear resonator at an appropriate frequency, to distinguish the 0 and 1 photon states.

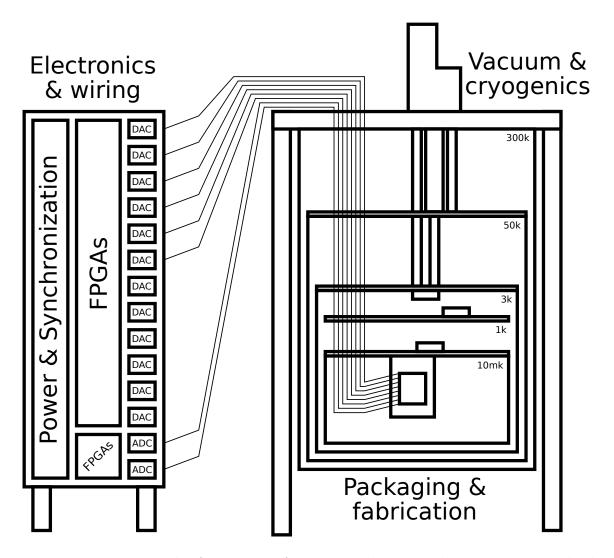

Superconducting qubits are an attractive candidate system for building a quantum computer because they have been developed on the periphery of advanced technologies that have been scaled enormously on an individual basis (Figure 1.1). Their aluminum-on-silicon fabrication is largely based on semiconductor fabrication techniques developed for CMOS aluminum on silicon fabrication that has received trillions of dollars in funding

over many decades and now routinely produces processors with several billion transistors and memory storage devices with tens of trillions of transistors each [19, 20]. The control and readout of superconducting qubits require high frequency electronics, but fortunately, qubits may be designed to operate in standard telecommunication bandwidths thus benefiting from the corresponding development of high quality and low(er) cost microwave components and design practices. Millikelvin temperature are perhaps the most exotic requirement for operating superconducting qubits, but these low temperatures are readily attainable. We are able to purchase off-the-shelf systems capable of handling the cooling needs of a couple hundred cables and a dozen qubit readout amplifiers thus far supporting as many as 72 qubits or 54 qubits and 88 couplers [10, 21]. While many design challenges remain, it is worth noting that particle physicists have already commissioned and built very large cryogenic cooling systems. The largest such cooling system, at the Large Hadron Collider, has a cooling capacity of 144 kW at 4.5 K and 20 kW of cooling power at 1.8 K, nearly 300,000x more cooling power than our existing cryostat [22, 23, 24].

## 1.4 Thesis overview

As I mentioned earlier, most of this thesis focuses on concerns related to the scalability of frequency tunable superconducting qubits. In Chapter 2 we will first review the superconducting circuits used in this thesis. In Chapter 3, we will explore some of the general experimental infrastructure requirements for superconducting qubit processors ranging from cryogenics, to the control electronics, and packaging. While fixed

frequency qubits require only low-current microwave control signals on-chip, frequency tunable qubits which offer more control, require several hundred MHz base band control waveforms with 1-2 mA of current. In Chapter 4 we develop a metrology tool for sampling on-chip flux waveforms using a frequency tunable resonator that allowed us to develop a near-term-scalable PCB based chip mount and directly model the complex DC to MHz flux bias transfer function on a superconducting chip. In Chapter 5 we develop and characterize superconducting interconnects used to assemble flip chip hybrid qubit devices, compatible with the mA flux bias currents. Finally, in Chapter 6 we use flux bias control of both gmon qubits and their couplers to implement a continuous set of two qubit gates with an average error for an arbitrary excitation-preserving 2-qubit unitary less than the previously reported best  $CZ_{\phi}$ .

## Chapter 2

# **Superconducting Circuits**

In this chapter we will briefly review the theory of some relevant superconducting circuits. Typical quantum processor consists of a relatively small number of components since we deal with only reactive circuit elements due to the extremely small cooling power available at mK temperatures. This means circuit design is limited to distributed inductors or capacitors formed by various transmission lines of varied geometries, lumped element parallel plate capacitors, the lumped non-linear inductance offered by Josephson junctions, or the flux-controllable non-linear inductance of a SQUID. Without Josephson junctions to provide a non-linear circuit element, superconducting quantum computing would not be possible as all circuits would produce linearly spaced energy levels that cannot be addressed independently.

With any introduction of superconducting qubits, it is difficult to avoid describing the quantum harmonic oscillator both because superconducting qubits are electrical anharmonic oscillators and because the harmonic oscillator is one of the few analytically solvable problems in quantum mechanics. The values of the inductance and capacitance of the oscillator circuit may be adjusted to trade one noise sensitivity for another. Transmon qubits have gained favor because they are insensitive to charge noise that seems to be unavoidable with existing fabrication techniques. Here we will introduce frequency tunable transmon qubits in four steps by first describing a superconducting harmonic oscillator circuit, then a Josephson junction followed by a SQUID which allows for a flux tunable circuit element, and finally frequency tunable transmons. Each of these circuits plays an important role in the design of superconducting quantum processors, and with the exception of a single Josephson junction, are later used in the experiments described in this thesis.

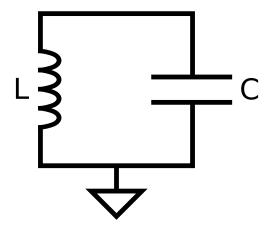

## 2.1 LC oscillator

Here we follow the Lagrangian formalism to derive the energy level structure of the quantum harmonic oscillator. In Figure 2.1 we have a parallel LC circuit, and we begin by writing down the kinetic and potential energies of the inductor and capacitor using the charge, Q, as our position coordinate,

$$U = \frac{Q^2}{2C} \tag{2.1}$$

$$T = \frac{L\dot{Q}^2}{2}. (2.2)$$

Figure 2.1: Simple LC oscillator composed of an inductor in parallel with a capacitor.

Combining these, we write down the Lagrangian of the circuit,

$$\mathcal{L} = T - U = \frac{L\dot{Q}^2}{2} - \frac{Q^2}{2C}.$$

(2.3)

We then apply the Euler-Lagrange formula,

$$\frac{\partial \mathcal{L}}{\partial q_j} - \frac{d}{dt} \left( \frac{\partial \mathcal{L}}{\partial \dot{q}_j} \right) = 0. \tag{2.4}$$

Using our charge coordinate  $Q = q_j$ , we obtain,

$$\frac{\partial \mathcal{L}}{\partial Q} - \frac{d}{dt} \left( \frac{\partial \mathcal{L}}{\partial \dot{Q}} \right) = 0$$

$$\frac{Q}{C} - \frac{d}{dt} (L\dot{Q}) = 0$$

$$\frac{Q}{C} - L\ddot{Q} = 0$$

$$\frac{Q}{C} - L\ddot{Q} = 0$$

$$Q\omega^2 - \ddot{Q} = 0$$

(2.5)

where  $\omega$  is the resonance frequency,  $1/\sqrt{LC}$ . We can then produce the conjugate coordinate to Q by computing  $p_x = \partial \mathcal{L}/\partial \dot{q}_j$ , or, in our case:

$$p_x = \frac{\partial \mathcal{L}}{\partial \dot{Q}} = L\dot{Q} = \Phi. \tag{2.6}$$

where  $\Phi$  is the flux through the inductor. Since Q and  $\Phi$  are canonically conjugate coordinates, they obey the canonical commutation relation  $[\Phi, Q] = i\hbar$ . We then perform a Legendre transformation to convert the Lagrangian into a Hamiltonian:

$$H = p_{j} \cdot \dot{q} - \mathcal{L}$$

$$H = \dot{Q}\Phi - \frac{L\dot{Q}^{2}}{2} + \frac{Q^{2}}{2C}$$

$$H = \dot{Q}\Phi - \frac{\dot{Q}\Phi}{2} + \frac{Q^{2}}{2C}$$

$$H = \frac{\Phi^{2}}{2L} + \frac{Q^{2}}{2C}$$

(2.7)

Now we have the familiar harmonic oscillator Hamiltonian which can be rewritten in terms of raising and lowering operators, a and  $a^{\dagger}$ , as

$$H = \hbar\omega \left( a^{\dagger} a + \frac{1}{2} \right) \tag{2.8}$$

where,

$$a^{\dagger} = \sqrt{\frac{1}{2\hbar Z}} (\Phi - iZQ) \tag{2.10}$$

$$a = \sqrt{\frac{1}{2\hbar Z}}(\Phi + iZQ) \tag{2.11}$$

and  $Z = \sqrt{L/C}$  is the circuit impedance. Similarly, Q and  $\Phi$  may be rewritten in terms of a and  $a^{\dagger}$ ,

$$Q = i\sqrt{\frac{\hbar}{2Z}}(a^{\dagger} - a) = iQ_{zpf}(a - a^{\dagger})$$

(2.12)

$$\Phi = \sqrt{\frac{\hbar Z}{2}} (a^{\dagger} + a) = \Phi_{zpf} (a + a^{\dagger})$$

(2.13)

Where  $Q_{zpf} = \sqrt{\langle 0|Q^2|0\rangle} = \sqrt{\hbar/2Z}$  is the zero point fluctuation of the charge operator, and  $\Phi_{zpf} = \sqrt{\hbar Z/2}$  is the zero point fluctuation of the flux operator.

The harmonic oscillator energy levels are all evenly spaced by an energy,  $\hbar\omega$ . As such, the harmonic oscillator is not a suitable qubit circuit—it is impossible to confine the system to any two levels. Any attempt to excite a single energy level will immediately populate a coherent state involving many energy levels [25]. Alas, this effort is not in vain. Linear harmonic oscillators may be fabricated with discrete inductors and capacitors or as

distributed transmission line stubs using either shorted or open termination to form  $\lambda/4$  or  $\lambda/2$  resonators. Such transmission line resonators form useful ancillary qubit readout circuitry [26, 27, 28] for dispersive measurement. These resonators also require only a single layer of lithography to fabricate and they may be characterized with a standard Vector Network Analyzer. Distributed transmission line resonators are sensitive to many of the same loss mechanisms as transmon qubits, so they may often be used as proxies for qubit performance subject to new fabrication techniques, packaging, etc, as we do in Chapter 3. Additionally, since actual superconducting qubit circuits are just non-linear resonators, we will pick this derivation back up in Section 2.4.

## 2.2 Josephson junctions

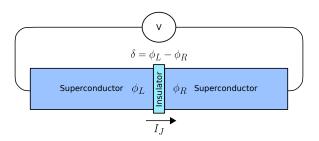

While the LC oscillator discussed above is useful for building ancillary qubit circuitry and for general materials characterization, the equal spacing of energy make it impossible to operate a linear LC oscillator as a qubit. In order to make a quantum circuit with addressable energy levels tat can be used as a qubit, we need a non-linear superconducting circuit element. Fortunately, such an element exists: the Josephson junction (JJ). Figure 2.2 depicts a JJ constructed by placing a weak link between two superconducting islands. In our case, this weak link is a thin, insulating, oxide barrier, but JJs may be formed by sandwiching a normal metal, insulator, or even just a superconductor with a lower critical current between two robust superconductors.

In this section, we follow the classic Feynman lectures [29] to derive the current-

phase and voltage-phase relations for a JJ [30]. We can begin by defining  $\Psi_L$  and  $\Psi_R$  as the wave functions of the superconducting state in the left and right superconductors. The dynamics of these wavefunctions are determined by coupled Schrödinger equations

$$i\hbar \frac{d\Psi_L}{dt} = U_L \Psi_L + K \Psi_R$$

$$i\hbar \frac{d\Psi_R}{dt} = U_R \Psi_R + K \Psi_L$$

(2.14)

where K is a constant representing the coupling across the JJ barrier, and  $U_L$  and  $U_R$  are the lowest energy states on either side. In the absence of an applied voltage,  $U_L$  and  $U_R$  would be equal, but here we consider the case of an applied voltage  $V = U_L - U_R$ , defined such that the voltage on either size is  $\pm V/2$ .

$$i\hbar \frac{d\Psi_L}{dt} = \frac{qV}{2}\Psi_L + K\Psi_R$$

$$i\hbar \frac{d\Psi_R}{dt} = -\frac{qV}{2}\Psi_R + K\Psi_L$$

(2.15)

Figure 2.2: A Josephson junction consisting of two superconducting islands separated by a thin insulating barrier.

To solve these equations we make the ansatz,

$$\Psi_L = \sqrt{\rho_L} e^{i\phi_L}$$

$$\Psi_R = \sqrt{\rho_R} e^{i\phi_R}$$

(2.16)

where  $\Psi_L$  and  $\Psi_R$  are the wavefunctions of the electrons on the left and right superconducting islands,  $\rho_L$  and  $\rho_R$  are the electron densities, and  $\phi_L$  and  $\phi_R$  are the superconducting phases. We then substitute equations 2.16 into equations 2.14 and equate the real and imaginary parts of each obtaining the system of four equations:

$$\dot{\rho_L} = +\frac{2}{\hbar} K \sqrt{\rho_L \rho_R} \sin(\phi_R - \phi_L)$$

$$\dot{\rho_R} = -\frac{2}{\hbar} K \sqrt{\rho_L \rho_R} \sin(\phi_R - \phi_L)$$

(2.17)

$$\dot{\phi_L} = +\frac{K}{\hbar} \sqrt{\frac{\rho_R}{\rho_L}} \cos(\phi_R - \phi_L) - \frac{qV}{2\hbar}$$

$$\dot{\phi_R} = +\frac{K}{\hbar} \sqrt{\frac{\rho_L}{\rho_R}} \cos(\phi_R - \phi_L) + \frac{qV}{2\hbar}$$

(2.18)

The first two equations (2.17) are just a statement of charge conservation indicating that the change in electron density on the left and right islands are equal and opposite  $(\dot{\rho}_L = -\dot{\rho}_R)$ . This makes sense for a tunneling current,  $I_J$ , moving electrons from one island to the other. The magnitude of  $I_J$ ,  $|\dot{\rho}_L|$ , may be simplified to the standard current-phase relation,

$$I_{J} = \frac{2K}{\hbar} \sqrt{\rho_{L} \rho_{R}} \sin \delta$$

$$I_{J} = I_{0} \sin \delta$$

(2.19)

where  $\delta = \phi_R - \phi_L$  is the difference in the superconducting phase on either side of the barrier and  $I_0$  is the maximum tunneling current, characteristic of the junction. Electrostatic forces keep the electron density fairly uniform, so  $\rho_L$  and  $\rho_R$  are both approximately equal to the normal electron density,  $\rho_0$ , which means  $I_0 \approx 2K\rho_0/\hbar$ . We can then take the difference of the second two equations (2.18) to obtain the voltage-phase relationship,

$$\dot{\phi}_{R} - \dot{\phi}_{L} = \frac{qV}{\hbar}$$

$$\dot{\delta} = \frac{qV}{\hbar}$$

$$\Longrightarrow V = \frac{\hbar}{2e} \frac{\partial \delta}{\partial t}$$

$$V = \frac{\Phi_{0}}{2\pi} \frac{\partial \delta}{\partial t}$$

$$(2.20)$$

where q=2e is the total charge of a cooper pair, and  $\Phi_0=h/2e$  is the magnetic flux quantum. Equations 2.19 and 2.20 are the standard Josephson Junction current-phase and voltage-phase relations. If we take the time derivative of equation 2.19 and solve for  $\partial \delta/\partial t$ , we obtain:

$$\frac{\partial I_J}{\partial t} = I_0 \cos(\delta) \frac{\partial \delta}{\partial t}

\frac{\partial \delta}{\partial t} = \frac{\partial I_J}{\partial t} \frac{1}{I_0 \cos(\delta)}$$

(2.21)

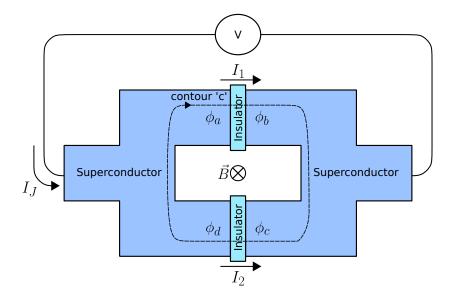

Figure 2.3: A superconducting quantum interference device (SQUID) composed of two Josephson junctions.

which we can then substitute into 2.20 to obtain the expression,

$$V = \underbrace{\frac{\Phi_0}{2\pi} \frac{1}{I_0 \cos(\delta)}}_{=L_L} \underbrace{\frac{\partial I_J}{\partial t}}$$

(2.22)

The voltage in equation 2.22 takes the form of an inductance where the Voltage is proportional to the change in current giving us an expression for the so-called Josephson inductance  $L_j = \Phi_0/2\pi I_0 \cos(\delta)$ .

## 2.3 SQUID

Before we explore how a single Josephson junctions may be used to create a qubit, we will first consider a circuit with two JJs which is the core of the magnetic-flux-tunable

circuits used in this thesis. Figure 2.3 provides a schematic drawing of a Superconducting QUantum Interference Device, or SQUID. A SQUID is composed of two Josephson junctions joined into a loop by two superconducting electrodes. If we assume that both junctions have the same critical current<sup>1</sup>,  $I_c$ , then,

$$I_1 = I_c \sin(\delta_1)$$

$$I_2 = I_c \sin(\delta_2)$$

(2.23)

where  $\delta_1$  and  $\delta_2$  are the phase differences across the first and second junctions. Summing these currents, we obtain an expression for the total current through the SQUID,

$$I_{J} = I_{1} + I_{2}$$

$$I_{J} = I_{c}(\sin(\delta_{1}) + \sin(\delta_{2}))$$

$$I_{J} = 2I_{c}\cos\left(\frac{\delta_{1} - \delta_{2}}{2}\right)\sin\left(\frac{\delta_{1} + \delta_{2}}{2}\right)$$

(2.24)

We can then consider the difference in the superconducting phase along the closed contour c going around the loop clockwise starting at the 11 o'clock position.

$$\oint_{c} \nabla \phi \cdot d\vec{\ell} = 2\pi n$$

$$= (\phi_{b} - \phi_{a}) + (\phi_{c} - \phi_{b}) + (\phi_{d} - \phi_{c}) + (\phi_{a} - \phi_{d})$$

(2.25)

Where we know the integral of the phase for a closed loop must be  $2\pi$ -periodic (e.g.  $= 2\pi n$  for integer values of n, since the wavefuction  $\Phi = |\rho|e^{i\phi}$  must be single valued).

<sup>&</sup>lt;sup>1</sup>While all the qubits used in this thesis are nominally symmetric, it is worth mentioning that asymmetric SQUIDs have been suggested as a way to trade some frequency tunability for a reduced flux sensitivity and consequently improved dephasing [31].

We can then write the phase differences across the junction as gauge invariant phases,

$$(\phi_b - \phi_a) = -\delta_1 - \frac{2\pi}{\Phi_0} \int_a^b \vec{A} \cdot d\vec{\ell}$$

$$(\phi_d - \phi_c) = \delta_2 - \frac{2\pi}{\Phi_0} \int_c^d \vec{A} \cdot d\vec{\ell}$$

(2.26)

and for the phase differences within the superconductor we can use the supercurrent equations,

$$(\phi_c - \phi_b) = \int_b^c \nabla \phi \cdot d\vec{\ell} = -\Lambda \int_b^c \vec{J} \cdot d\vec{\ell} - \frac{2\pi}{\Phi_0} \int_b^c \vec{A} \cdot d\vec{\ell}$$

$$(\phi_a - \phi_d) = \int_d^a \nabla \phi \cdot d\vec{\ell} = -\Lambda \int_d^a \vec{J} \cdot d\vec{\ell} - \frac{2\pi}{\Phi_0} \int_d^a \vec{A} \cdot d\vec{\ell}$$

(2.27)

where  $\Lambda = \frac{m}{nq^2}$ . Then, combining equations 2.26 and 2.27 into equation 2.25, we have

$$2\pi n = -\delta_{1} - \frac{2\pi}{\Phi_{0}} \int_{a}^{b} \vec{A} \cdot d\vec{\ell} + \delta_{2} - \frac{2\pi}{\Phi_{0}} \int_{c}^{d} \vec{A} \cdot d\vec{\ell}$$

$$-\Lambda \int_{b}^{c} \vec{J} \cdot d\vec{\ell} - \frac{2\pi}{\Phi_{0}} \int_{b}^{c} \vec{A} \cdot d\vec{\ell} - \Lambda \int_{d}^{a} \vec{J} \cdot d\vec{\ell} - \frac{2\pi}{\Phi_{0}} \int_{d}^{a} \vec{A} \cdot d\vec{\ell},$$

(2.28)

and collecting the  $\int \vec{A} \cdot d\vec{\ell}$  terms, this simplifies to

$$\delta_{2} - \delta_{1} = 2\pi n + \underbrace{\frac{2\pi}{\Phi_{0}} \oint_{c} \vec{A} \cdot d\vec{\ell}}_{\equiv \Phi \, through \, SQUID} + \Lambda \int_{b}^{c} \vec{J} \cdot d\vec{\ell} + \Lambda \int_{d}^{a} \vec{J} \cdot d\vec{\ell}, \qquad (2.29)$$

by assuming we can take the contour, c, to be deep inside the superconductor where  $\vec{J} = 0$  this reduces to,

$$(\delta_2 - \delta_1) = 2\pi n + \frac{2\pi}{\Phi_0} \Phi \tag{2.30}$$

where  $\Phi$  is the magnetic flux through the SQUID loop. This flux quantization means we can control the effective critical current of the SQUID with an applied flux. Substituting equation 2.30 into equation 2.24,

$$I_{J} = 2I_{c}\cos\left(\frac{2\pi n}{2} + \frac{\pi\Phi}{\Phi_{0}}\right)\sin\left(\frac{2\pi n}{2} + \frac{2\pi n}{2\Phi_{0}}\Phi + \frac{2\delta_{1}}{2}\right)$$

$$I_{J} = \underbrace{2I_{c}\cos\left(\frac{\pi\Phi}{\Phi_{0}}\right)}_{effective I_{c}}\sin\left(\delta_{1} + \frac{\pi\Phi}{\Phi_{0}}\right)$$

$$(2.31)$$

Comparing the SQUID current phase relation (2.31) with that of the single junction (2.19) we see that the behavior of a SQUID is just like that of a single junction with an effective critical current that may be adjusted from some maximum value for integer values of trapped flux down to zero at half-integer flux quanta with an externally applied magnetic flux<sup>2</sup>. In the next section we will see how to use such an element to form a qubit.

<sup>&</sup>lt;sup>2</sup>Note, if the two junctions have different critical currents, the tunable range is only over the range  $|I_{j1} - I_{j2}|$  to  $|I_{j1} + I_{j2}|$

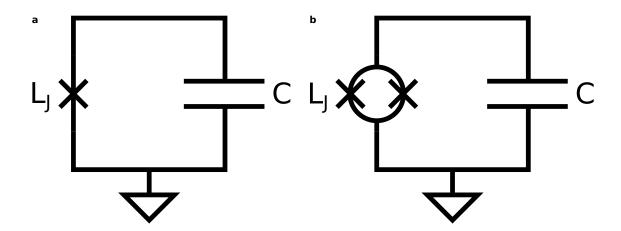

Figure 2.4: Transmon circuits. **a**, Fixed frequency transmon qubit and **b**, flux tunable transmon qubit.

## 2.4 Transmon qubits

In order to produce a quantum circuit with addressable energy levels, we can replace the inductance in the oscillator discussed in Section 2.1, with one Josephson junction (Section 2.2), or pair of Josephson junctions forming a SQUID (Section 2.3), as shown in Figure 2.4. As we saw in Section 2.3, a SQUID behaves like a single junction, so the following derivation holds for either circuit if you take  $I_c$  to be the single junction critical current, or the effective, flux-tuned, critical current of the SQUID (equation 2.31). Here, we begin by restating the JJ voltage and current relations.

$$V(t) = \frac{\hbar}{2e} \frac{d\delta}{dt}$$

$$I(t) = I_c \sin(\delta)$$

(2.32)

where  $\delta$  is the difference in the superconducting phase across the junction and  $I_c$  is the

junction critical current, above which the junction exhibits an Ohmic resistance (e.g. a linear resistance where V = IR). We can then integrate the IV product to compute the potential energy of the JJ circuit element

$$U = \int_{0}^{t} I(t)V(t)dt$$

$$= \frac{\hbar I_{c}}{2e} \int \sin(\delta) \frac{\partial \delta}{\partial t} dt$$

$$= \frac{\hbar I_{c}}{2e} \int \sin(\delta) d\delta$$

$$= -\frac{\hbar I_{c}}{2e} \cos(\delta)$$

$$= -\frac{\Phi_{0}I_{c}}{2\pi} \cos(\delta)$$

$$= -E_{j} \cos(\delta)$$

(2.33)

where  $\Phi_0 = h/2e$  is the magnetic flux quantum, and  $E_j = \Phi_0 I_c/2\pi$  is the Josephson energy. Combining this with the capacitive energy we have the circuit Hamiltonian

$$H = \frac{Q^2}{2C} - E_J \cos(\delta) \tag{2.34}$$

We can rewrite the first term using the number operator, n = Q/2e, which counts the number of Cooper pairs on the capacitor, and the charging energy,  $E_c = e^2/2C$ .

$$H = 4E_c n^2 - E_J \cos(\delta) \tag{2.35}$$

where we may expand  $\cos(\delta) = 1 - \delta^2 + \delta^4/24 + O(\delta^6)$ , yielding an approximate harmonic oscillator Hamiltonian (ignoring the offset energy from the constant term),

$$H = 4E_c n^2 + E_J \delta^2 + O(\delta^4)$$

(2.36)

with energy levels given by  $E_n = \sqrt{8E_cE_J}(n+1/2)$ , for integer values of n. In order to determine the qubit non-linearity, we can consider the next term in the expansion,  $E_J\delta^4/24$  as a perturbation. We begin by rewriting  $\delta$  in terms of the ladder operators a and  $a^{\dagger}[32]$ ,

$$\delta = \left(\frac{2E_C}{E_J}\right)^{\frac{1}{4}} (a^{\dagger} + a) \tag{2.37}$$

Then we can compute the effect of the  $\delta^4$  term using perturbation theory,

between the last two lines, we have ignored all terms with an unequal number of raising and lowering operators, as they would not map  $\langle j|$  to  $|j\rangle$ . We then use the fact that  $a^{\dagger}|j\rangle = \sqrt{j+1}|j+1\rangle$  and  $a|j\rangle = \sqrt{j}|j-1\rangle$  to simplify further,

$$\Delta E_{j} = -\frac{E_{C}}{12} (\langle j | a^{\dagger} a^{\dagger} a a | j \rangle + \langle j | a^{\dagger} a a^{\dagger} a | j \rangle + \langle j | a^{\dagger} a a^{\dagger} a | j \rangle + \langle j | a^{\dagger} a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | j \rangle + \langle j | a a^{\dagger} a | a a^{\dagger} a$$

and finally we simplify all the eigenvalues,

$$\Delta E_{j} = -\frac{E_{C}}{12}(j(j-1) + j^{2} + (j+1)j + j(j+1) + (j+1)^{2} + (j+1)(j+2))$$

$$= -\frac{E_{C}}{12}(j^{2} - j + j^{2} + j^{2} + j + j^{2} + j + j^{2} + 2j + 1 + j^{2} + 3j + 2)$$

$$= -\frac{E_{C}}{12}(6j^{2} + 6j + 3)$$

$$= -\frac{E_{C}}{4}(2j^{2} + 2j + 1)$$

(2.40)

So, the  $j^{th}$  energy level is given by,

$$E_J = j\sqrt{8E_J E_C} - \frac{E_C}{4}(2j^2 + 2j + 1)$$

(2.41)

We can take the difference of the lowest two energy levels,

$$E_1 - E_0 = \left(\sqrt{8E_J E_C} - \frac{E_C}{4}(2 + 2 + 1)\right) - \frac{E_C}{4}$$

$$= \sqrt{8E_J E_C} - E_C$$

(2.42)

and similarly for the difference between the  $j^{th}$  and  $(j-1)^{th}$  states,

$$E_{j} - E_{j-1} = \left(j\sqrt{8E_{J}E_{C}} - \frac{E_{C}}{4}(2j^{2} + 2j + 1)\right)$$

$$-\left((j-1)\sqrt{8E_{J}E_{C}} - \frac{E_{C}}{4}(2(j-1)^{2} + 2(j-1) + 1)\right)$$

$$= \sqrt{8E_{J}E_{C}} - \frac{E_{C}}{4}((2j^{2} + 2j + 1) - (2j^{2} - 4j + 2 + 2j - 2 + 1))$$

$$= \sqrt{8E_{J}E_{C}} - \frac{E_{C}}{4}((2j^{2} + 2j + 1) - (2j^{2} - 2j + 1))$$

$$= \sqrt{8E_{J}E_{C}} - \frac{E_{C}}{4}(4j)$$

$$= \sqrt{8E_{J}E_{C}} - jE_{C}$$

$$(2.43)$$

Thus the energy levels of the transmon are addressable with an anharmonicity equal to  $E_C$ . Practically speaking, the anharmonicity is an extremely important parameter in our circuit design as sets a "speed limit" on how fast we can perform single qubit microwave gates equal to  $\tau = h/E_c$ . Beyond this limit, faster gates would require spectral content overlapping with the next energy level resulting in leakage from the qubit subspace to a higher energy level or levels. For this reason, a large  $E_C$  desirable. However, when  $E_C$  is large, the shunt capacitance is small making us sensitive to charge noise—e.g. noise due to charge carriers entering or leaving the capacitor. Charge noise has proven unavoidable with existing fabrication techniques ultimately limiting the coherence of charge qubits. This led to the development of the more successful Transmons qubit which uses a fairly sizable shunt capacitance ( $\approx 80 \, fF$ ) yielding a non-linearity of just 240 MHz. In Chapter 4 we use a very large capacitance to create an approximately harmonic tunable resonator.

### 2.5 Used in this thesis

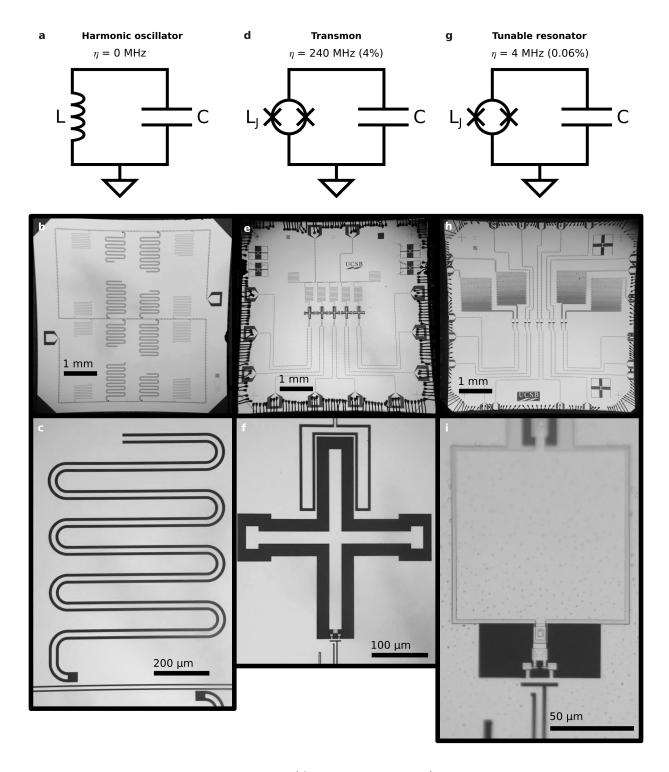

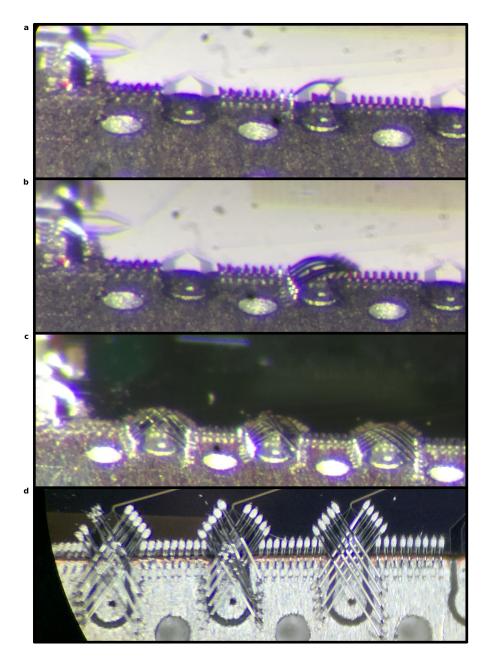

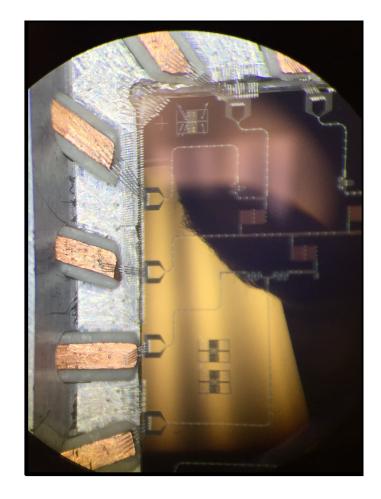

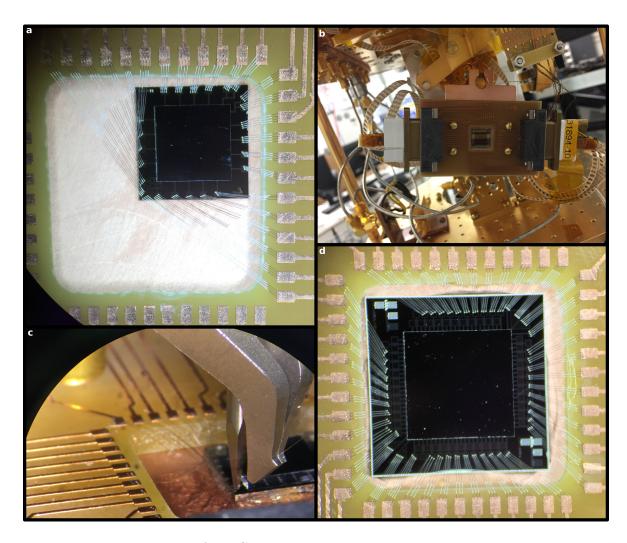

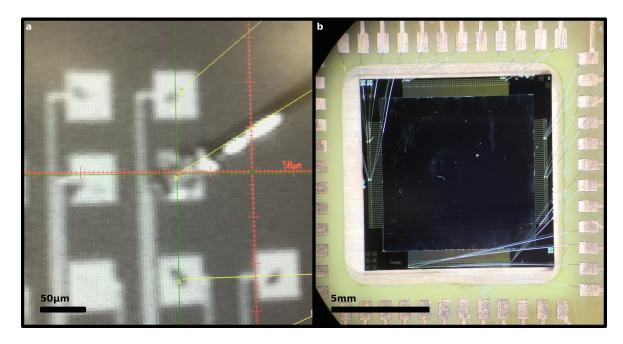

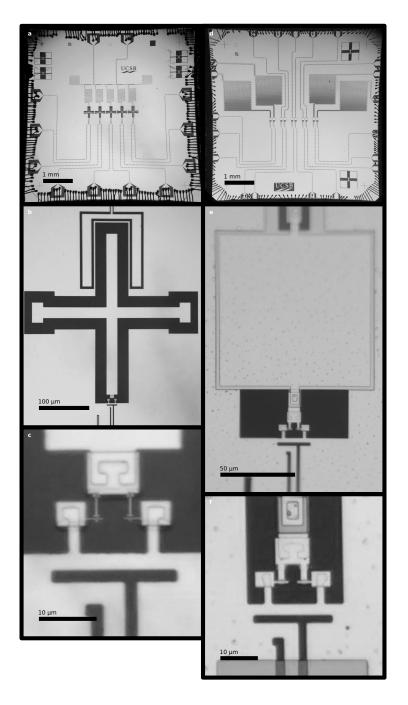

In this chapter we have theoretically explored a linear resonator, a non-linear resonator, and a SQUID, which acts as a flux-tunable non-linear inductance. In the remaining chapters of this thesis we will use a combination of all three of these circuits. Figure 2.5 shows physical realizations a linear harmonic oscillator ( $\mathbf{b}$ , $\mathbf{c}$ ), a frequency tunable transmon qubit ( $\mathbf{e}$ ,  $\mathbf{f}$ ), and a nearly-linear frequency tunable resonator ( $\mathbf{h}$ , $\mathbf{i}$ ). In Chapter 3 we us linear harmonic oscillator circuits formed by  $\lambda/4$  coplanar waveguide resonators as shown in Figure 2.5a and 2.5b. These resonators require just one layer of lithography

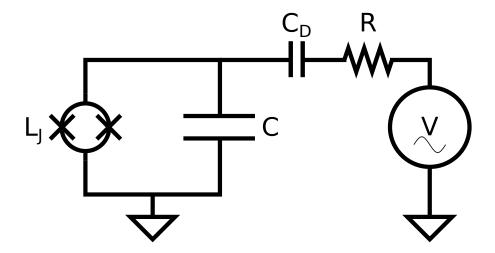

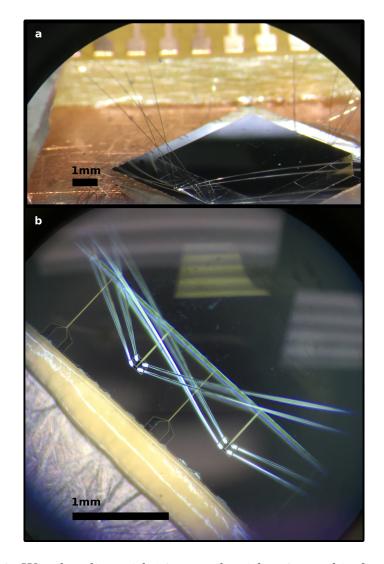

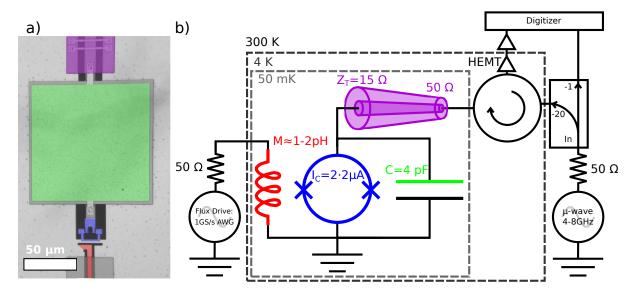

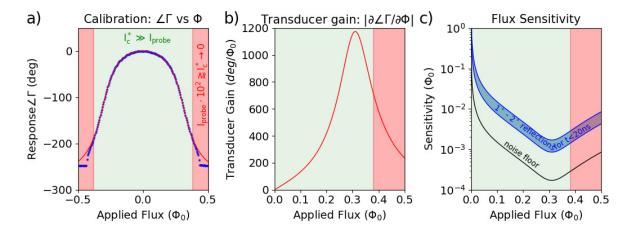

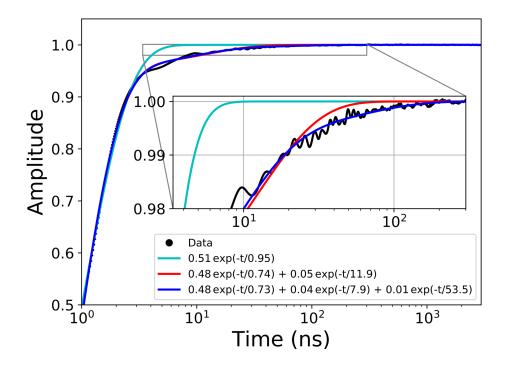

to fabricate, they are sensitive to many of the same loss mechanisms as transmon qubits, and may be characterized with a standard Vector Network Analyzer. In Chapter 4 we use a circuit consisting of a capacitively shunted SQUID that behaves as a frequency tunable resonator (Figures 2.5g, h, and i) to characterize the performance of our flux bias control electronics and wiring. While the layout of the SQUID and flux bias line geometry of the tunable resonator is similar to the transmon, the capacitance, formed by parallel plates, and SQUID critical current are much larger. The large capacitance reduces the non-linearity of the circuit and results in a nearly harmonic energy level spacing while the increased critical current reduces the minimum SQUID inductance resulting in a resonant frequency similar to the qubit. This tunable resonator circuit allows us to characterize the response of our SQUID without having to calibrate or readout qubits offering a more direct measurement of the transfer function of our control electronics as seen by qubits. In Chapters 3 and 6 we use xmon transmon and gmon transmon qubits to check the coherence of a near-term scalable PCB based package and to demonstrate a continuous set of two qubit gates (xmon circuit shown in A.3d and qubit device shown in Figures 2.5e and 2.5f).

Figure 2.5: (Caption next page.)

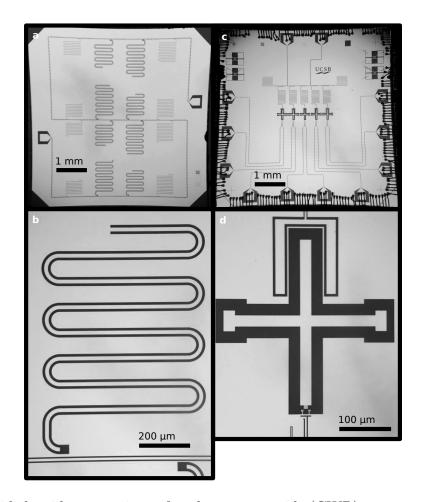

Figure 2.5: (Previous page.) Comparison of three devices used in this thesis. a, Linear harmonic oscillator circuit consisting of an inductance and capacitance. b, Aluminum on sapphire device with sixteen coplanar waveguide resonators on one "S" shaped feed line. c, Zoom in of one coplanar wave guide resonator, where the L and C are both distributed along the length of the transmission line. d, Transmon qubit circuit where the linear inductance has been replaced by two Josephson junctions forming a SQUID which behaved as a non-linear inductance that may be tuned with an external magnet field. e, A five transmon device ("+" signs in the middle), coplanar waveguide resonators for dispersive readout (top center), and control wiring (left, right, and bottom). f, Zoom in of one transmon qubit showing the capacitance formed by the coplanar plus-shaped capacitor and the inductance formed by the SQUID loop at the bottom of the plus. g, Circuit diagram of a tunable nearly linear resonator. This circuit reduces the nonlinearity of the qubit so that it may be driven to higher energy levels with a nearly linear resonant behavior. h, i, Tunable resonator device made to mimic the qubit layout, while the capacitance has been increased with a parallel plate geometry, the SQUID loop and associated control wiring are the same as the qubit design. Rather than dispersive readout, we can directly probe the impedance of this circuit with a reflective microwave phase measurement allow us to measure the time-domain flux response of our flux bias control signals.

# Chapter 3

# Qubit system design

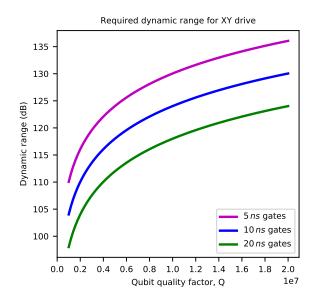

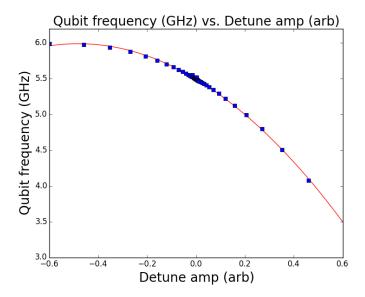

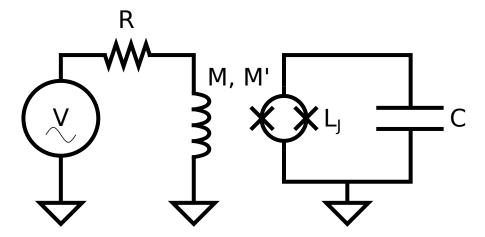

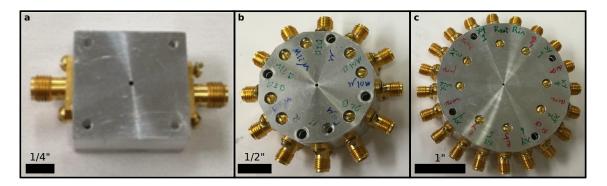

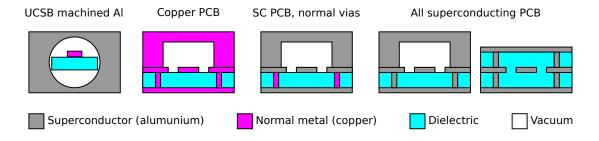

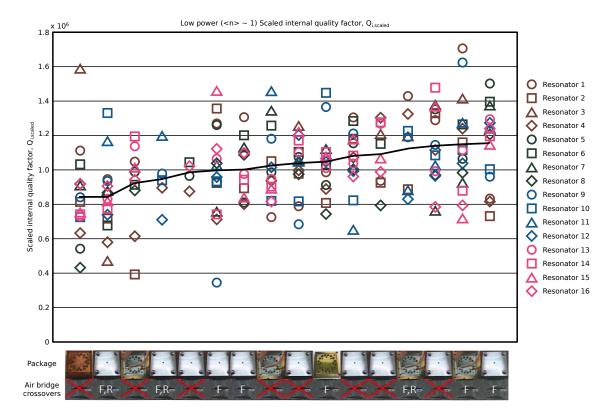

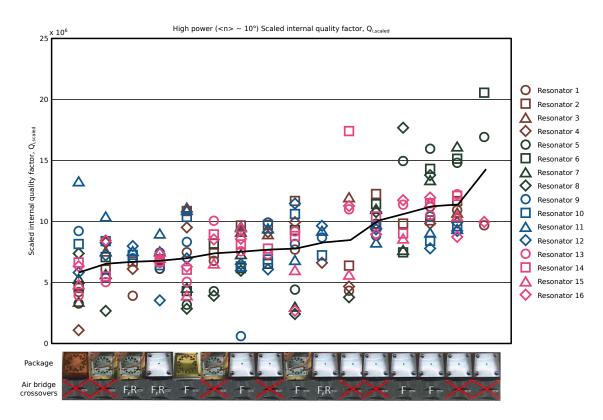

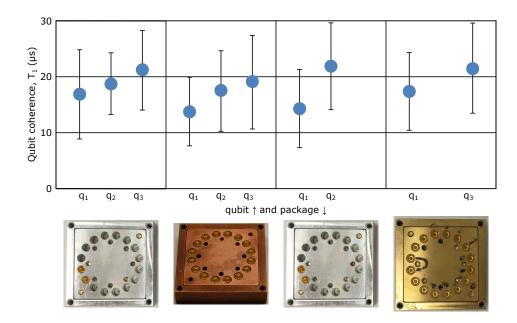

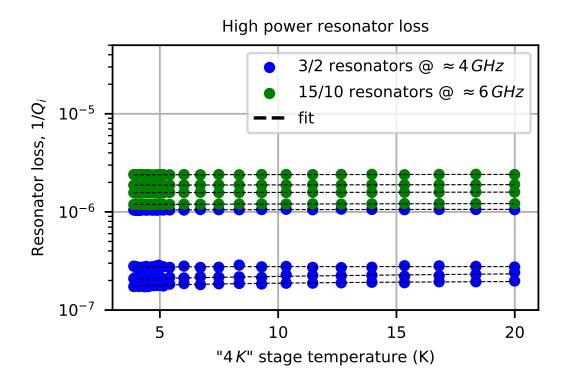

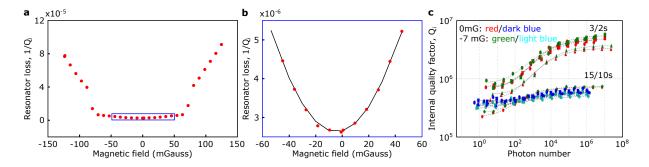

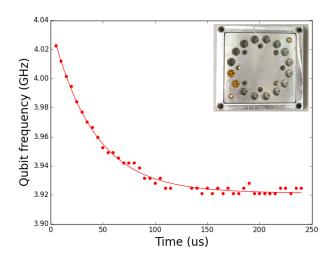

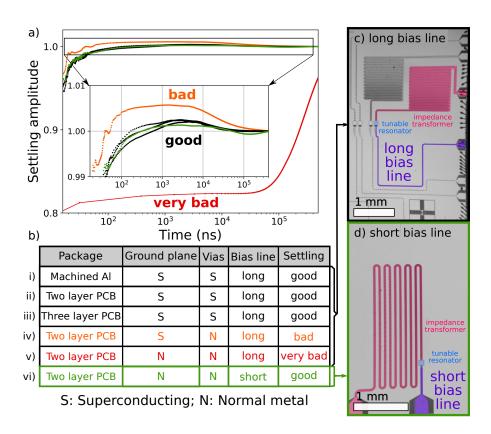

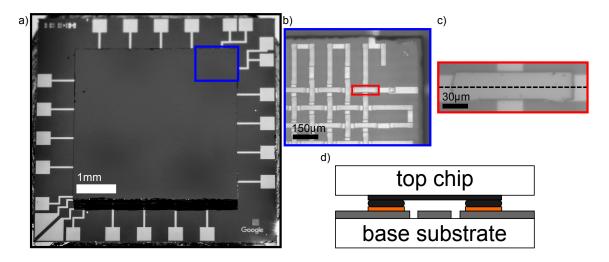

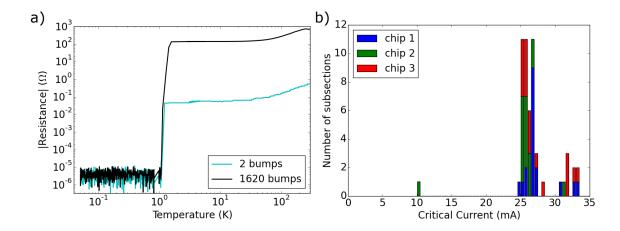

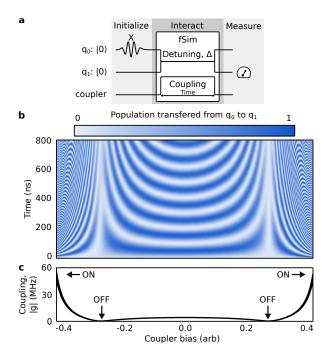

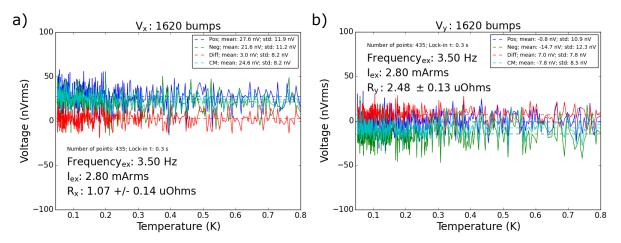

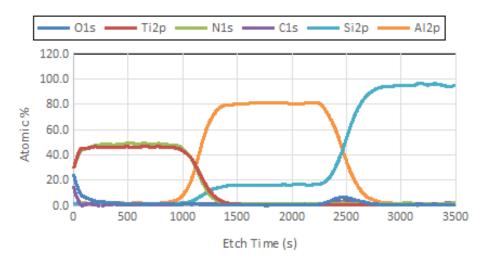

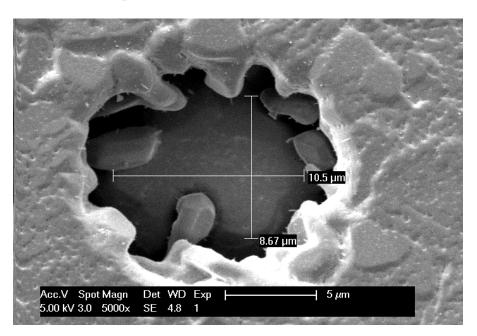

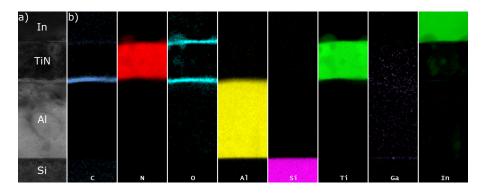

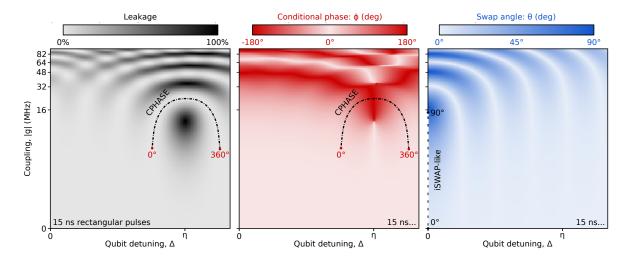

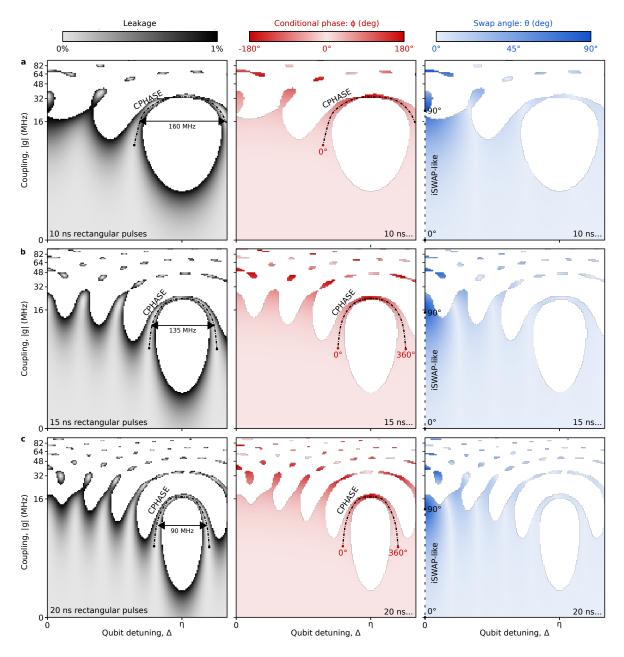

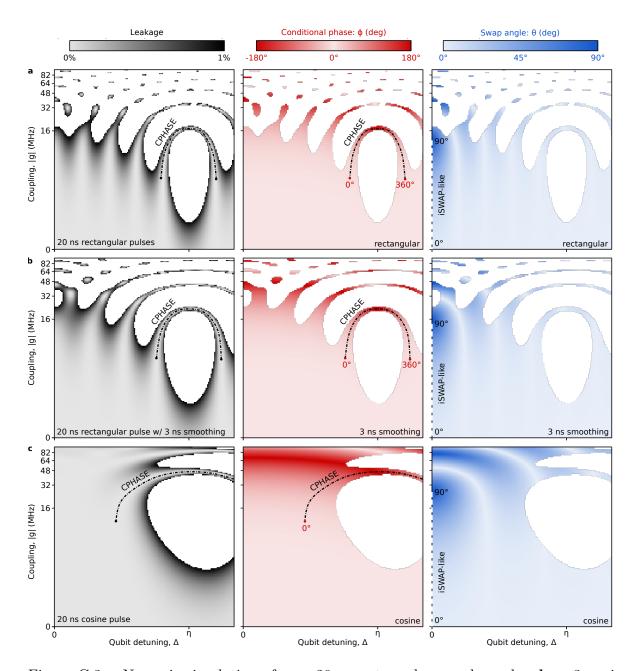

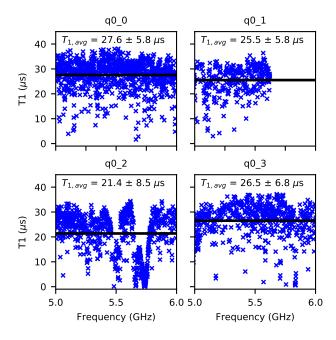

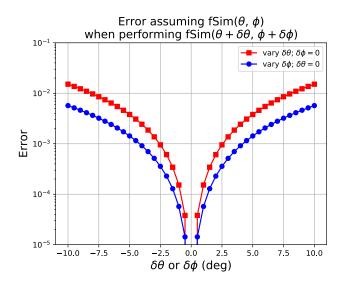

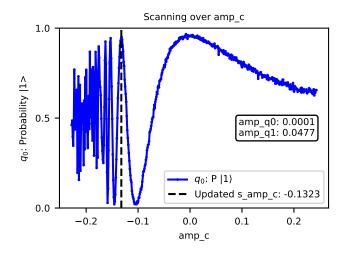

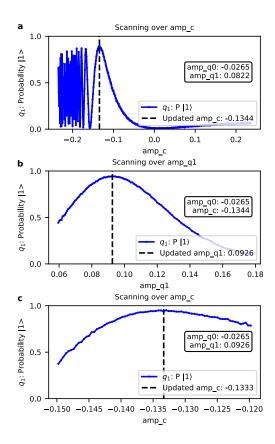

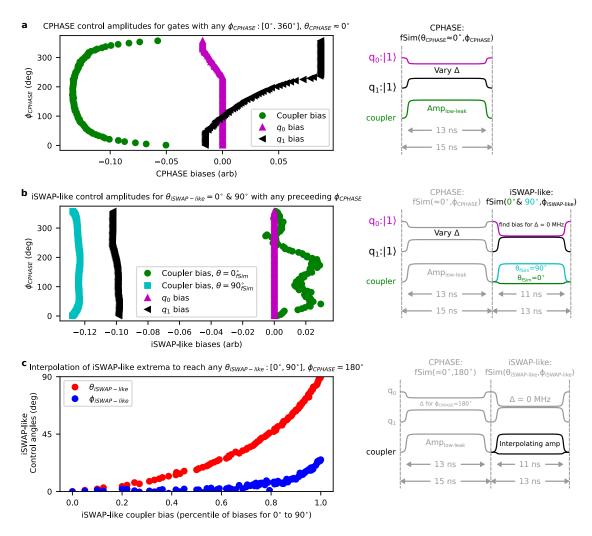

Building a quantum computer is effectively the task of asserting arbitrary control over a system composed of individual quantum mechanical states. This requires two things: