# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

GaN-based Microwave Power Varactors for Wireless Base Station Applications

# Permalink

https://escholarship.org/uc/item/80c223cd

# Author

Lu, Wei

# Publication Date 2013

Peer reviewed|Thesis/dissertation

# **GaN-based Microwave Power Varactors for Wireless Base Station Applications**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Applied Physics)

by

Wei Lu

Committee in charge:

Professor Paul K.L. Yu, Chair Professor Peter M. Asbeck, Co-Chair Professor Prabhakar R. Bandaru Professor Andrew C. Kummel Professor Yu-Hwa Lo

2013

Copyright ©

Wei Lu, 2013

All rights reserved.

The Dissertation of Wei Lu is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Chair

University of California, San Diego

2013

DEDICATION

To my beloved wife Wen Qiao.

### EPIGRAPH

There are no secrets to success. It is the result of preparation, hard work, and learning from failure.

Colin Powell

## TABLE OF CONTENTS

| Signature Page               | iii  |

|------------------------------|------|

| Dedication                   | iv   |

| Epigaph                      | v    |

| Table of Contents            | vi   |

| List of Figures              | ix   |

| List of Tables               | xvi  |

| Acknowledgments              | xvii |

| Vita                         | xxii |

| Abstract of the Dissertation | xxiv |

| Chapte | er 1 Introduction                                       | 1    |

|--------|---------------------------------------------------------|------|

| 1.1    | Introduction to varactors                               | 1    |

| 1.2    | Figure of merit for GaN-based microwave power varactors | 3    |

| 1.3    | Overview of the dissertation                            | 7    |

| 1.4    | References                                              | . 10 |

| Chapte | Per 2Design of GaN-based microwave power varactors      | .11  |

| 2.1    | Design for high breakdown voltage                       | .11  |

| 2.2    | Design for high linearity                               | . 19 |

| 2.3    | Design for high Q                                       | .20  |

| 2.4    | Summary of the designs                                  | .24  |

| 2.5    | References                                              | .25  |

| Chapte | er 3 Ni-InGaN/GaN Schottky diode technology             | .27  |

| 3.1 Theory of InGaN surface layer design                           | 28 |

|--------------------------------------------------------------------|----|

| 3.1.1 Analysis of reverse leakage current in GaN Schottky barriers | 28 |

| 3.1.2 InGaN surface layer design for reduced leakage current       | 34 |

| 3.2 Experimental results and discussions                           | 38 |

| 3.2.1 C-V measurements and analysis                                | 38 |

| 3.2.2 Forward I-V measurements and analysis                        | 40 |

| 3.2.3 Reverse I-V measurements and analysis                        | 44 |

| 3.3 Leakage current reduction using higher pressure GaN buffer     | 48 |

| 3.4 InGaN/GaN material growth and characterization                 | 52 |

| 3.4.1 InGaN/GaN MOCVD growth                                       | 53 |

| 3.4.2 InGaN/GaN material characterization                          | 56 |

| 3.4.2.1 Reported defects in GaN and InGaN materials                | 57 |

| 3.4.2.2 Experimental procedures                                    |    |

| 3.4.2.3 X-ray diffraction measurements                             | 60 |

| 3.4.2.4 Nomarski microscope imaging                                | 61 |

| 3.4.2.5 Surface topography investigation by SEM and AFM            | 62 |

| 3.4.2.6 Etch pit density measurements                              | 64 |

| 3.4.2.7 Discussion of material defect characterization             | 67 |

| 3.4.3 Electrical characteristics of InGaN/GaN Schottky diodes      | 70 |

| 3.4.4 Effects of thermal annealing on Ni-InGaN/GaN Schottky diodes |    |

| 3.5 Application for enhancement-mode HFETs                         | 78 |

| 3.6 Summary of InGaN/GaN technology                                |    |

| 3.7 Reference                                                      |    |

|                                                                    |    |

| Chapter 4 Fabrication procedure                                    | 91 |

| 4.1 Introduction                                                   |    |

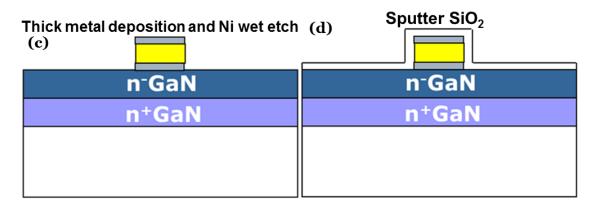

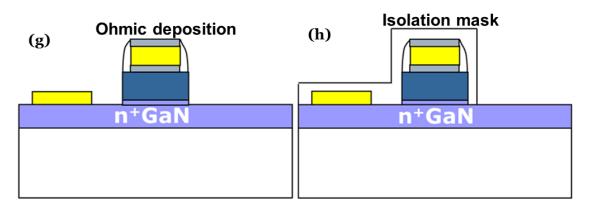

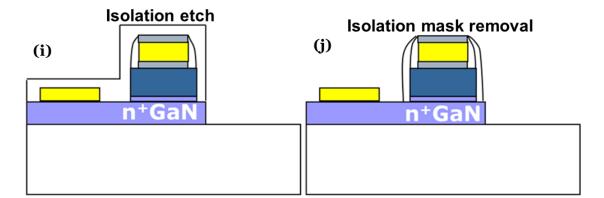

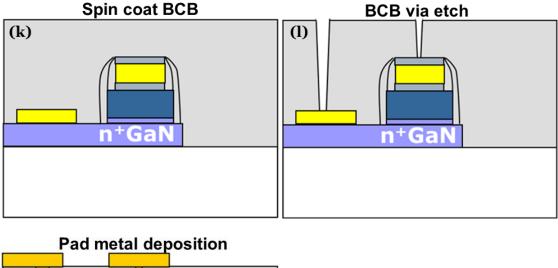

| 4.2 Initial fabrication procedure                                  | 92 |

| 4.3 Preliminary results                                            | 96 |

| 4.3     | .1 I-V measurements                                               | 96  |

|---------|-------------------------------------------------------------------|-----|

| 4.3     | .2 RF measurements                                                |     |

| 4.4     | Sidewall passivation in GaN-based Schottky diodes                 | 107 |

| 4.4     | .1 Simulation of electric field distribution under reverse biases |     |

| 4.4     | .2 Experimental procedure                                         |     |

| 4.4     | .3 Results and discussions                                        |     |

| 4.4     | .4 Summary of sidewall passivation in GaN-based Schottky diodes   | 117 |

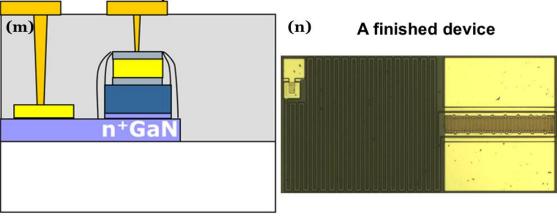

| 4.5     | Improved fabrication procedure                                    | 117 |

| 4.6     | Summary of the fabrication procedure                              |     |

| 4.7     | References                                                        |     |

| Chapter | 5 Experimental results and discussions                            |     |

| 5.1     | High voltage I-V and C-V measurements                             |     |

| 5.2     | S-parameter measurements                                          |     |

| 5.2     | .1 Measurements for the 1-port devices                            |     |

| 5.2     | .2 Measurements for the 2-port devices                            |     |

| 5.3     | Linearity measurements                                            | 146 |

| 5.3     | .1 Two-tone test                                                  |     |

| 5.3     | .2 2-W WCDMA signal input                                         |     |

| 5.4     | Application in the tunable resonant circuit                       |     |

| 5.5     | Summary                                                           |     |

| Chapter | 6 Conclusion and Future Work                                      |     |

| 6.1     | Summary of the thesis                                             |     |

| 6.2     | Comparison of different varactor technologies                     |     |

| 6.3     | Future work                                                       |     |

| 6.4     | References                                                        |     |

| Append  | ix A GaN-based varactor fabrication procedure                     |     |

### LIST OF FIGURES

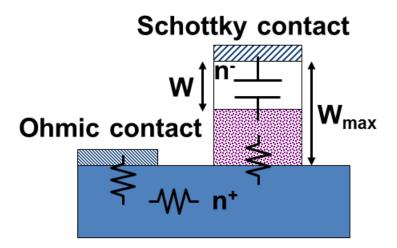

| Figure 1-1  | Schematic structure of Schottky-diode based semiconductor varactor                                                                                                                                                                                             | 4  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

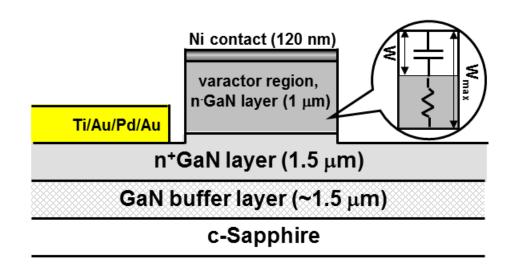

| Figure 2-1  | Schematic diagram of a GaN-based varactor and its layer structure.                                                                                                                                                                                             | 12 |

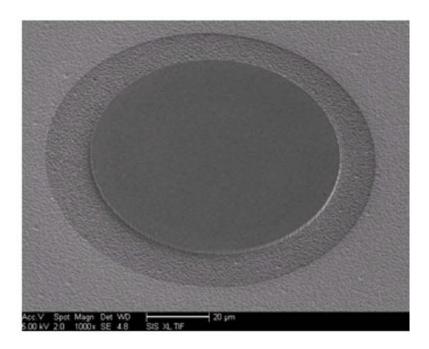

| Figure 2-2  | SEM top view of a fabricated diode with an 80- $\mu$ m diameter                                                                                                                                                                                                | 13 |

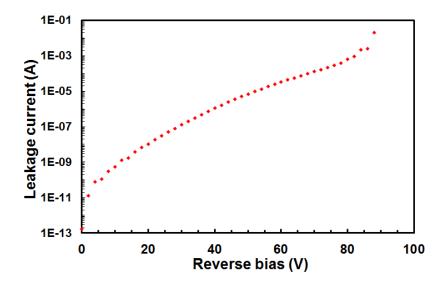

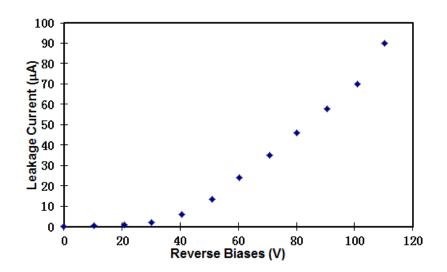

| Figure 2-3  | Reverse leakage current of a device with an area of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                                                         | 14 |

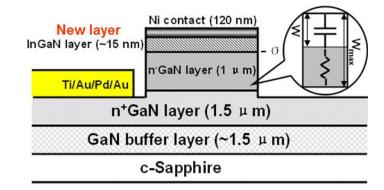

| Figure 2-4  | Schematic diagram of the GaN-based Schottky diode design<br>with thin InGaN surface layer for breakdown voltage<br>enhancement.                                                                                                                                | 16 |

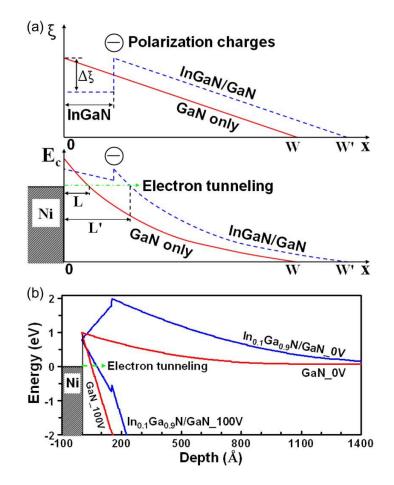

| Figure 2-5  | (a) Schematic diagrams of the (upper) electric field and energy<br>bands under the same reverse bias for the designs with<br>InGaN/GaN and GaN only. (b) Representative energy band<br>diagrams at reverse 0 and 100 V calculated by the 1-D Poisson<br>solver | 16 |

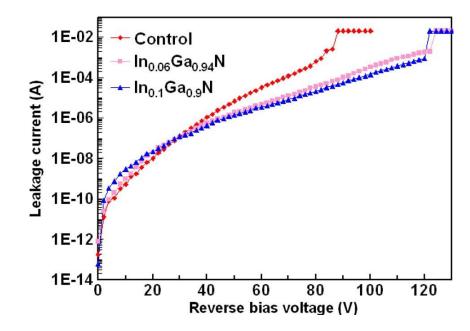

| Figure 2-6  | Reverse IV characteristics for samples with and without InGaN surface layers. Circular diodes have areas of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                 | 18 |

| Figure 2-7  | Simulated CV curves for (a) single diode structure and (b) two<br>anti-parallel diode structure                                                                                                                                                                | 20 |

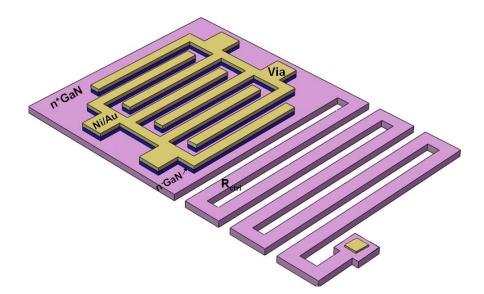

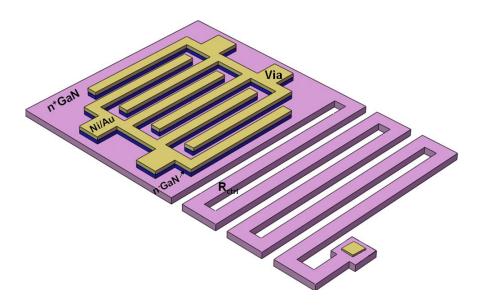

| Figure 2-8  | Schematic diagram of the anti-parallel diode structure with interdigitated strip geometry                                                                                                                                                                      | 21 |

| Figure 2-9  | (a) Schematic diagram of the anti-parallel varactor diode with<br>its corresponding lump components, and (b) the circuit model<br>represented by a distributed resistance and capacitance                                                                      | 22 |

| Figure 2-10 | Simulated values of <i>Q</i> as a function of finger length                                                                                                                                                                                                    | 23 |

| Figure 3-1  | Schematic energy band diagram of a Schottky barrier under reverse bias                                                                                                                                                                                         | 33 |

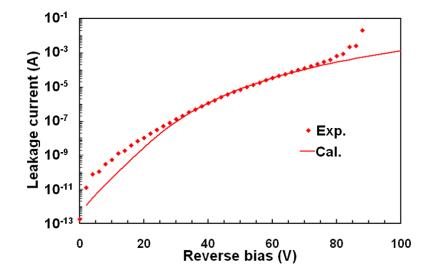

| Figure 3-2  | Experimental and calculated reverse leakage current of a Ni-                                                                                                                                                                                                   |    |

| GaN Schottky diode with an area of $5 \times 10^{-5}$ cm <sup>2</sup> | 34 |

|-----------------------------------------------------------------------|----|

|-----------------------------------------------------------------------|----|

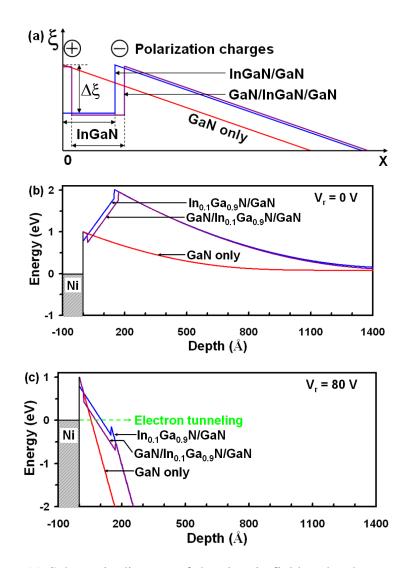

| Figure 3-3  | (a) Schematic diagram of the electric field under the same reverse bias for the designs with InGaN/GaN, GaN/InGaN/GaN and GaN only. (b) Representative energy band diagrams ( $E_c$ only) at $V_r = 0V$ and (c) $V_r = 80$ V by solving the 1-D Poisson equation. | 37 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

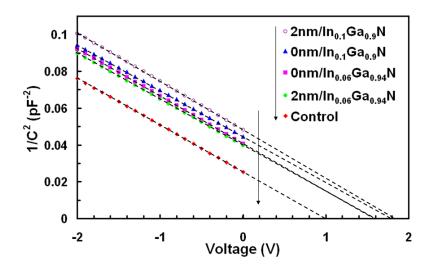

| Figure 3-4  | C-V results of the five samples with area of $7.85 \times 10^{-5}$ cm <sup>2</sup> , measured in the dark at 1 MHz. The colored dots are measurement data and the dash lines are fitting curves                                                                   | 39 |

| Figure 3-5  | Schematic energy band diagram of an InGaN/GaN Schottky barrier under forward bias                                                                                                                                                                                 | 42 |

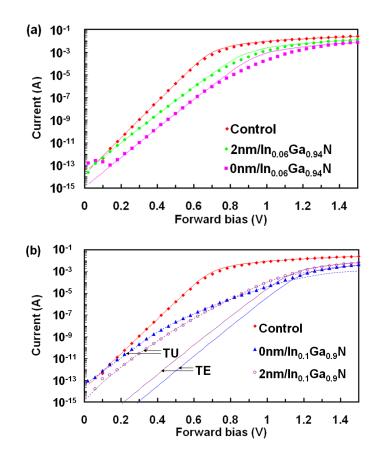

| Figure 3-6  | Forward I-V curves of the five samples with areas of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                                                           | 43 |

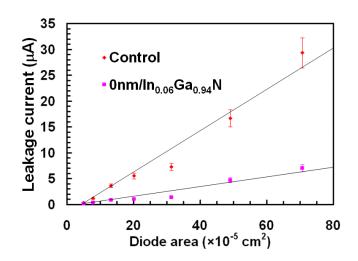

| Figure 3-7  | Currents at reverse bias 50 V as a function of diode area for the control and $0$ nm/In <sub>0.06</sub> Ga <sub>0.94</sub> N samples                                                                                                                              | 45 |

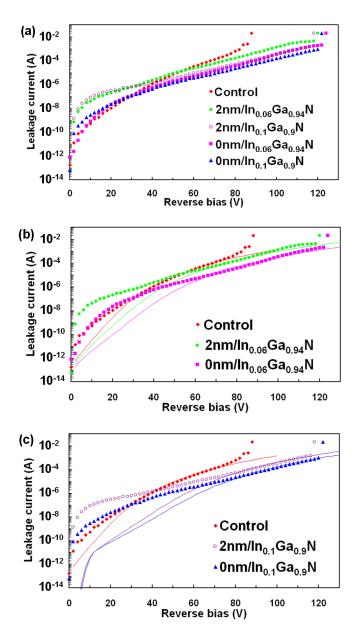

| Figure 3-8  | Reverse I-V curves of the five samples with area of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                                                            | 47 |

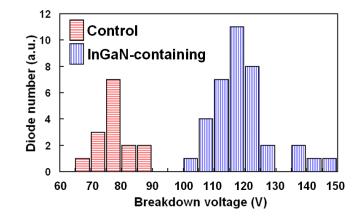

| Figure 3-9  | The histogram of the breakdown voltages for the control and InGaN-containing diodes                                                                                                                                                                               | 48 |

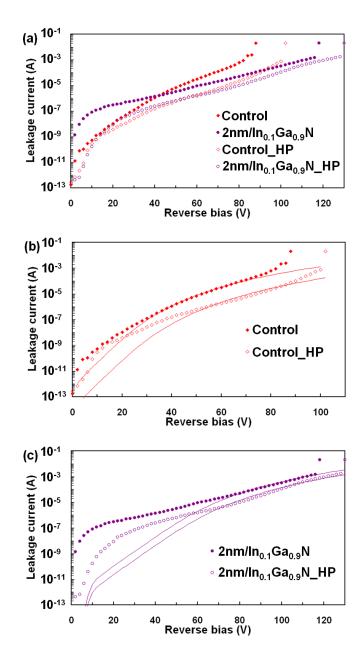

| Figure 3-10 | Reverse I-V curves of the samples using HP and LP GaN buffer layers with area of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                               | 50 |

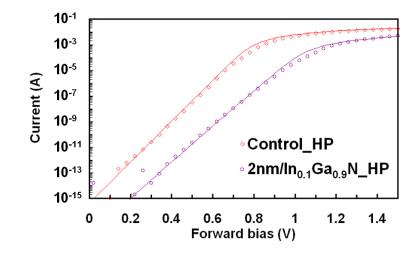

| Figure 3-11 | Forward <i>I-V</i> curves of the Control_HP and $2nm/In_{0.1}Ga_{0.9}N_HP$ samples with area of $5 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                | 52 |

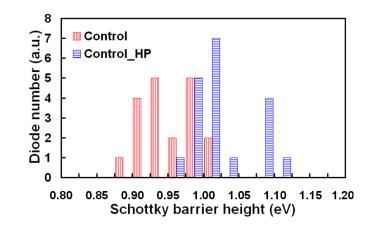

| Figure 3-12 | The histogram of SBHs extracted from the experimental forward I-V curves of the Control and Control_HP samples                                                                                                                                                    | 52 |

| Figure 3-13 | Thomas Swan close-coupled showerhead (CCS) 3×2"<br>MOCVD system                                                                                                                                                                                                   | 54 |

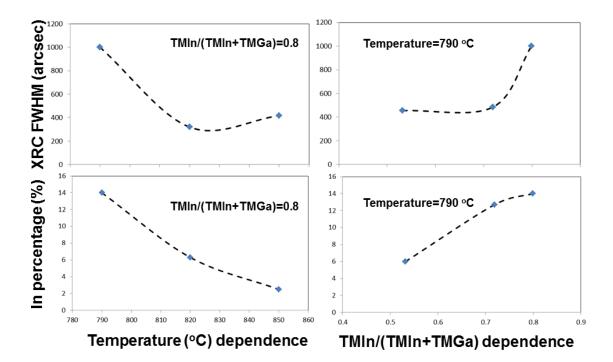

| Figure 3-14 | The indium percentage and FWHMs of (0002) X-ray rocking curve (XRC) of thick InGaN films for different growth temperatures and molar flow ratios of TMIn/(TMIn+TMGa) during growth.                                                                               | 55 |

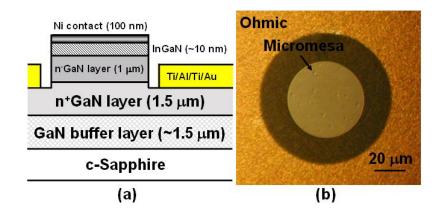

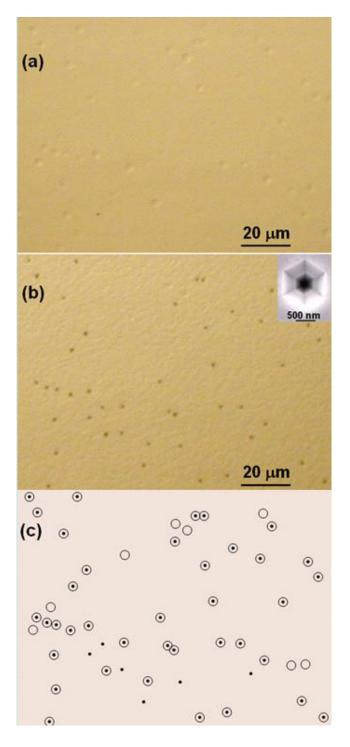

| Figure 3-15 | a) Schematic cross section of the InGaN/GaN Schottky diode<br>and (b) the Nomarski optical microscopy top view of a real<br>diode with surface micromesas                                                     | 59 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

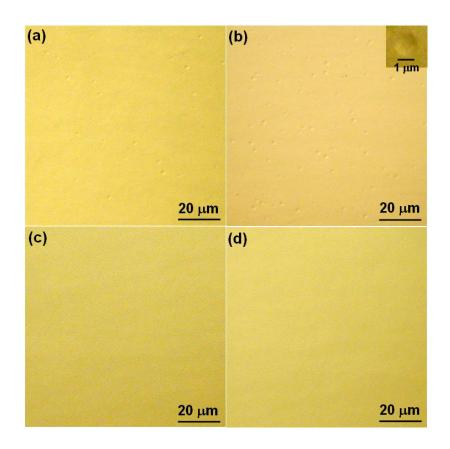

| Figure 3-16 | Nomarski optical microscopy images of (a) HP_InGaN/GaN, (b) LP_InGaN/GaN, (c) HP_GaN and (d) LP_GaN                                                                                                           | 62 |

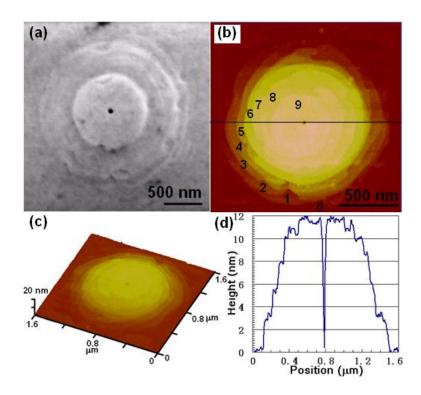

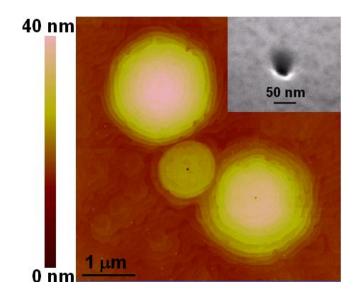

| Figure 3-17 | Representative SEM and AFM (tapping mode) micrographs of the surface micromesas.                                                                                                                              | 63 |

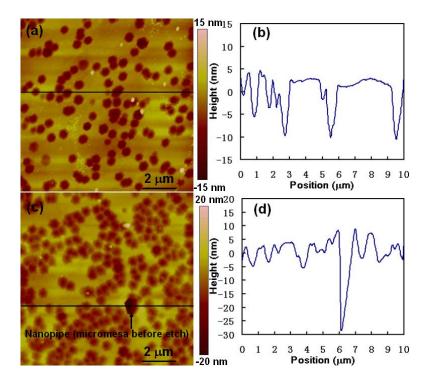

| Figure 3-18 | $10 \times 10 \ \mu m^2$ AFM images of (a) HP_InGaN/GaN, (b) surface profile along the line in (a), (c) LP_InGaN/GaN, and (d) surface profile along the line in (c) after H <sub>3</sub> PO <sub>4</sub> etch | 64 |

| Figure 3-19 | Surface micromesa mapping by Nomarski optical microscopy                                                                                                                                                      | 66 |

| Figure 3-20 | An AFM (tapping mode) micrograph of surface micromesas with and without nanopipes at the center                                                                                                               | 69 |

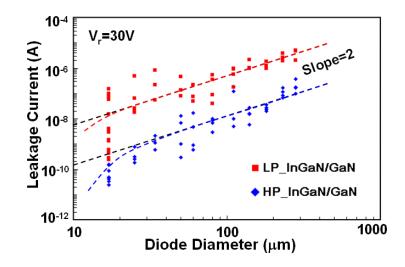

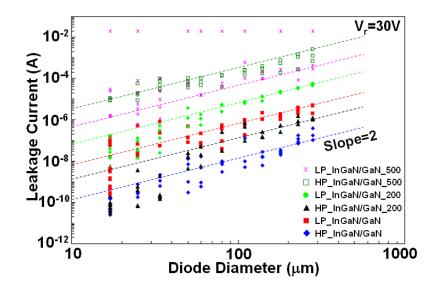

| Figure 3-21 | Leakage current at a reverse bias of 30 V versus diode diameter for LP_InGaN/GaN and HP_InGaN/GaN Schottky diodes.                                                                                            | 71 |

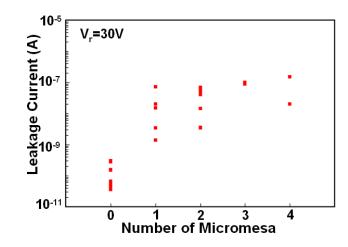

| Figure 3-22 | Leakage current at a reverse bias of 30 V versus micromesa<br>number on the smallest (17-µm diameter) LP_InGaN/GaN and<br>HP_InGaN/GaN Schottky diodes                                                        | 73 |

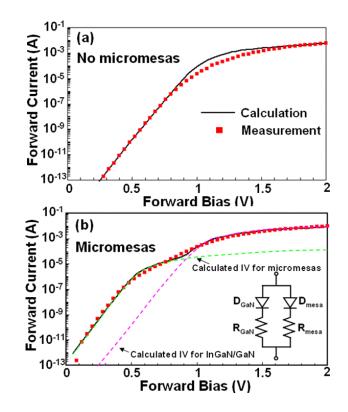

| Figure 3-23 | Representative forward IV curves for the smallest (17-µm diameter) Ni-InGaN/GaN Schottky barriers (a) without surface micromesas and (b) with surface micromesas                                              | 73 |

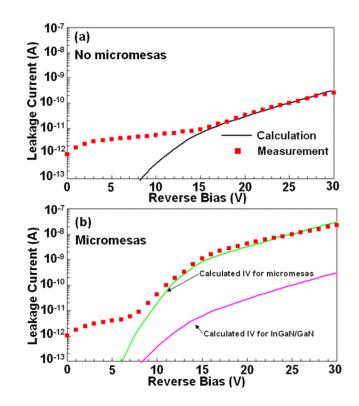

| Figure 3-24 | Representative reverse-bias IV curves for the smallest (17-µm diameter) Ni-InGaN/GaN Schottky barriers (a) without surface micromesas and (b) with surface micromesas                                         | 75 |

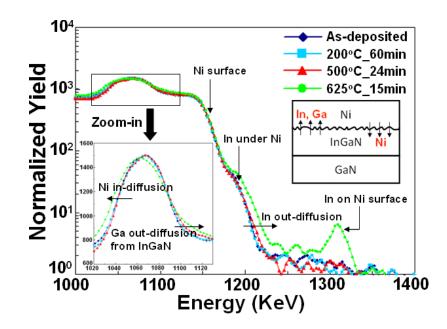

| Figure 3-25 | RBS spectra of as-deposited, annealed at 200 °C for 60 minutes, 500 °C for 24 minutes and 625 °C for 15 minutes Ni-InGaN/GaN samples.                                                                         | 76 |

| Figure 3-26 | Leakage current at a reverse bias of 30 V versus diode diameter for LP_InGaN/GaN and HP_InGaN/GaN Schottky diodes before and after annealing at different temperatures                                        | 78 |

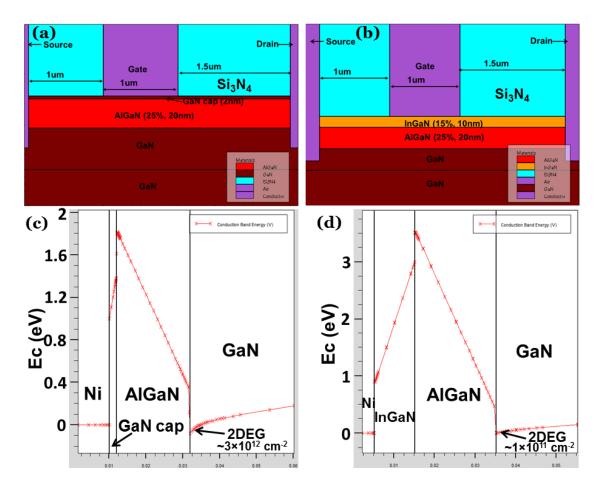

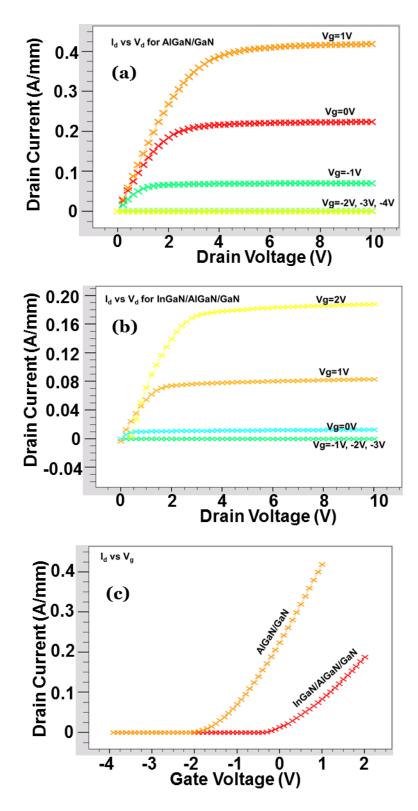

| Figure 3-27 | Simulated AlGaN/GaN and InGaN/AlGaN/GaN HEMT structures and the corresponding energy band diagrams                                                                                                                                         | 80  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3-28 | Simulated I-V characteristics for AlGaN/GaN and InGaN/AlGaN/GaN HEMTs                                                                                                                                                                      | 82  |

| Figure 4-1  | Schematic diagram of the anti-parallel diode structure with interdigitated strip geometry                                                                                                                                                  | 92  |

| Figure 4-2  | Schematic diagrams of the initial GaN-based varactor fabrication procedure                                                                                                                                                                 | 95  |

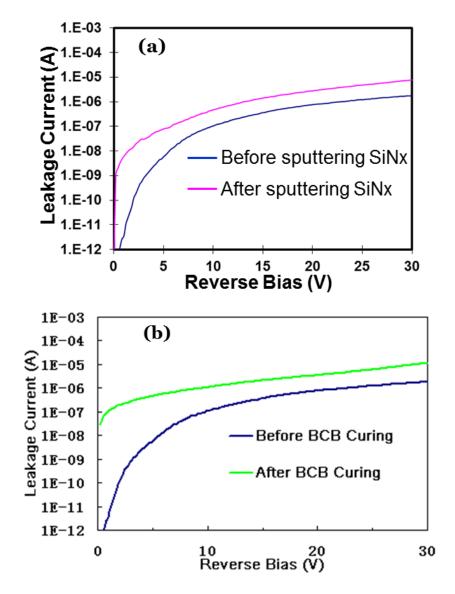

| Figure 4-3  | Reverse leakage current tracking after critical fabrication steps.<br>(a) Before and after sputtering $SiN_x$ and (b) before and after BCB curing                                                                                          | 97  |

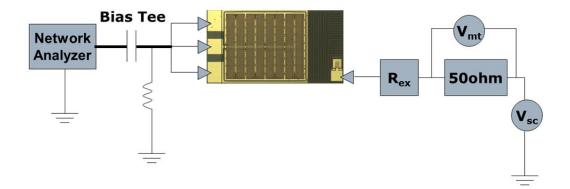

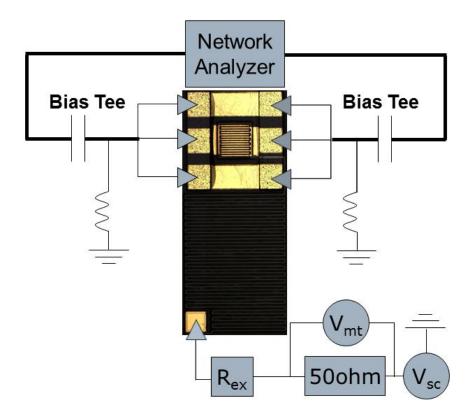

| Figure 4-4  | Measurement setup for S11                                                                                                                                                                                                                  | 98  |

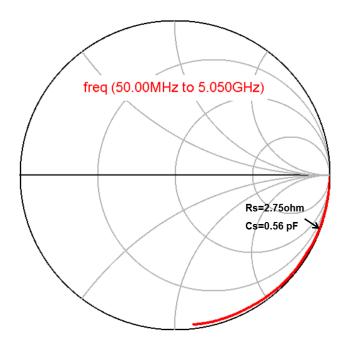

| Figure 4-5  | S11 measured from a device at reverse bias of 40 V from 50 MHz to 5.05 GHz shown in a Smith Chart                                                                                                                                          | 100 |

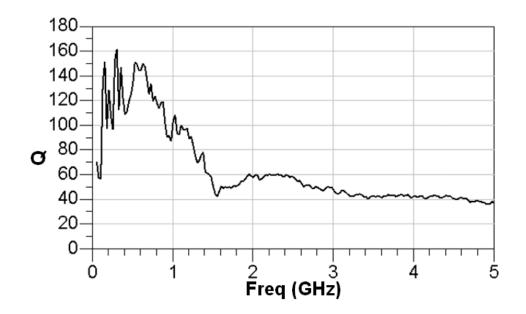

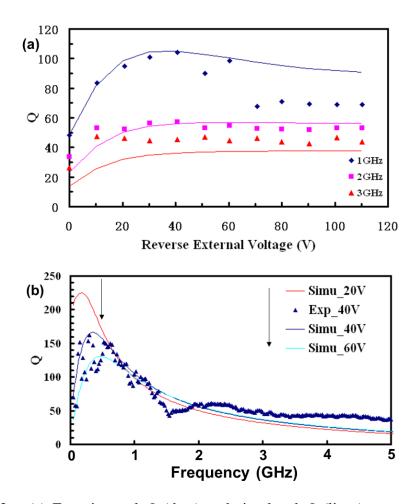

| Figure 4-6  | Q factor versus frequency at a reverse external bias of 40 V for an anti-parallel varactor diode                                                                                                                                           | 100 |

| Figure 4-7  | Reverse I-V characteristics of an anti-parallel varactor diode                                                                                                                                                                             | 101 |

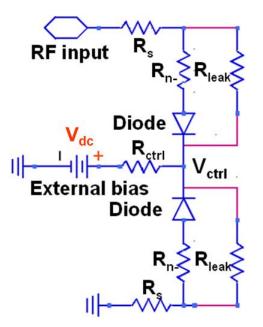

| Figure 4-8  | Equivalent circuit model for the anti-parallel varactors with considering $R_{leak}$ for the reverse leakage current                                                                                                                       | 102 |

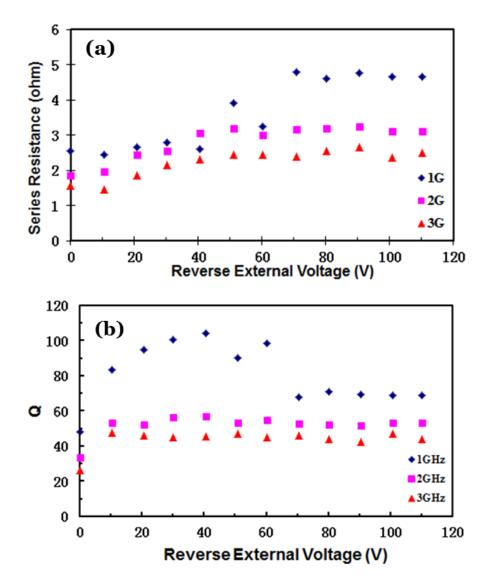

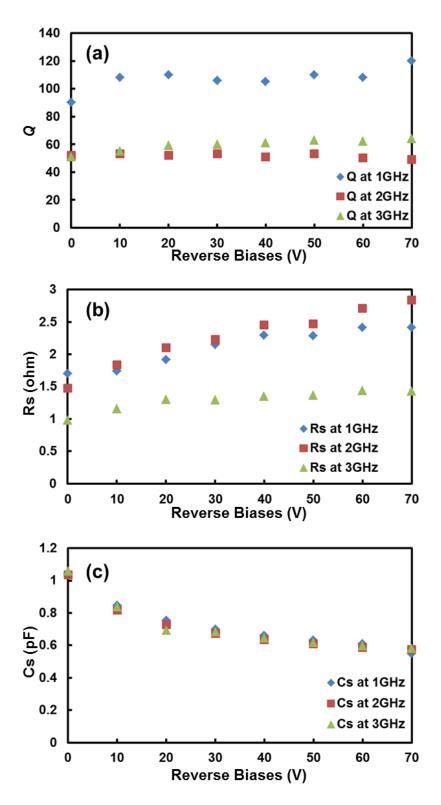

| Figure 4-9  | Extracted series resistance (a) and $Q$ (b) versus reverse external biases for 1GHz, 2GHz and 3GHz                                                                                                                                         | 103 |

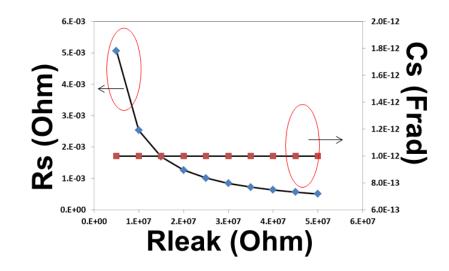

| Figure 4-10 | Relations between series resistance and $R_{leak}$ , and series capacitance and $R_{leak}$ .                                                                                                                                               | 104 |

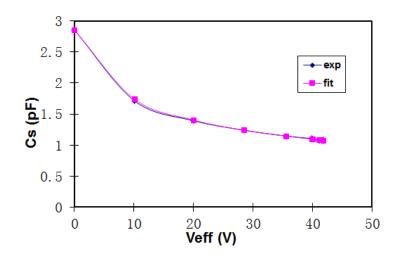

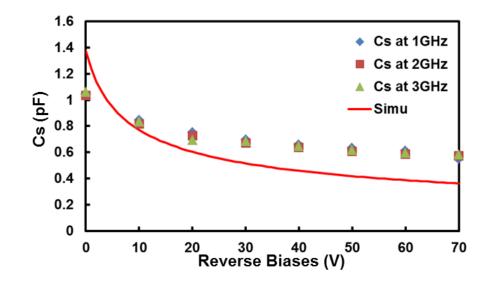

| Figure 4-11 | Experimental and simulated C-V curves for one of the diode in the two back-to-back diodes                                                                                                                                                  | 104 |

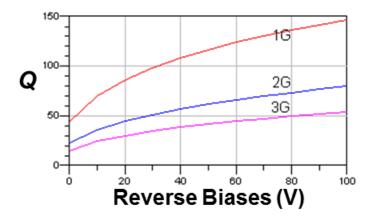

| Figure 4-12 | (a) Experimental $Q$ (dots) and simulated $Q$ (lines) versus the reverse external bias at $f = 1$ GHz, 2 GHz and 3 GHz; (b) experimental $Q$ (dots) and simulated $Q$ (at reverse external biases of 20 V, 40 V and 60 V) versus frequency | 106 |

| Figure 4-13 | Simulated $Q$ versus reverse biases assuming the reverse leakage is low at high biases                                                                                                                                                                                                                                  | 106 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

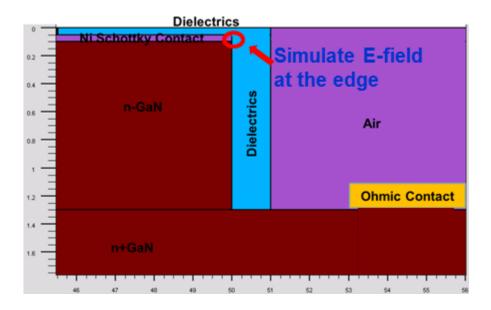

| Figure 4-14 | Simulated GaN Schottky diode structure with sidewall passivation in Silvaco ATLAS 2-D simulator for electric field distribution under reverse biases                                                                                                                                                                    | 109 |

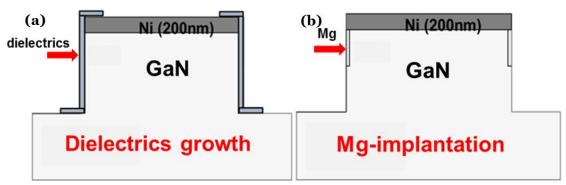

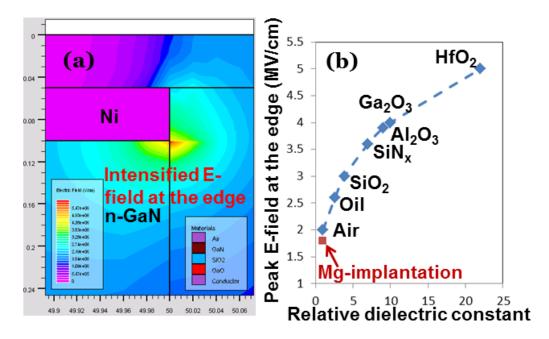

| Figure 4-15 | Sidewall passivation by (a) growing dielectrics along the sidewall and (b) $Mg^+$ implantation through the sidewall                                                                                                                                                                                                     | 109 |

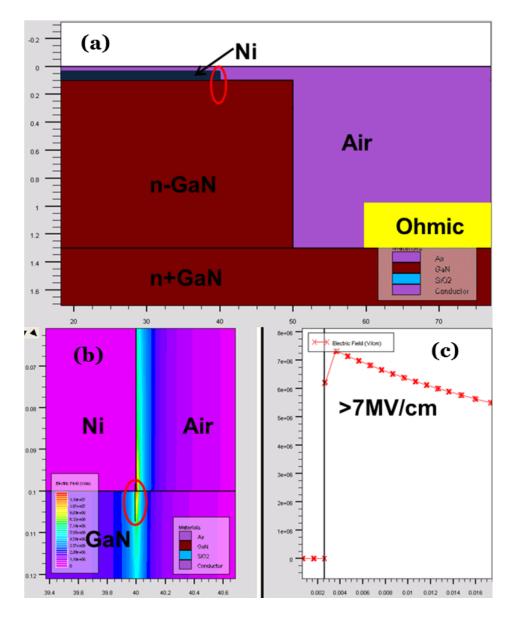

| Figure 4-16 | (a) Electric field distribution under a reverse bias of 85 V and<br>(b) peak electric field at the edge of Ni-GaN Schottky<br>junctions for different passivation materials along the GaN<br>sidewalls.                                                                                                                 | 110 |

| Figure 4-17 | Electric field distribution for a device with a non-self-aligned gate process.                                                                                                                                                                                                                                          | 111 |

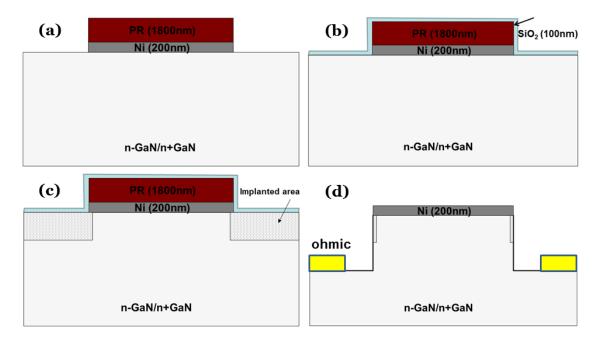

| Figure 4-18 | Fabrication procedure for sidewall passivation by $Mg^+$ implantation.                                                                                                                                                                                                                                                  | 114 |

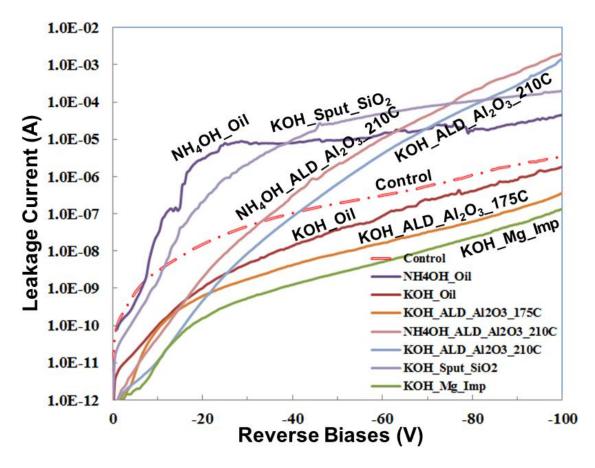

| Figure 4-19 | Reverse leakage current for samples fabricated with different sidewall processing procedures. The diode area is $2.8 \times 10^{-5}$ cm <sup>2</sup>                                                                                                                                                                    | 116 |

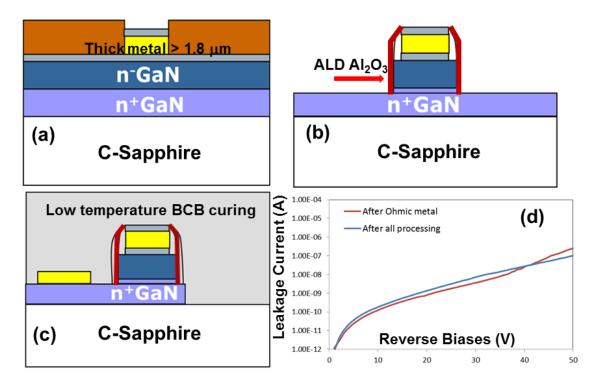

| Figure 4-20 | Improved fabrication procedure and the resultant reverse I-V characteristics                                                                                                                                                                                                                                            | 119 |

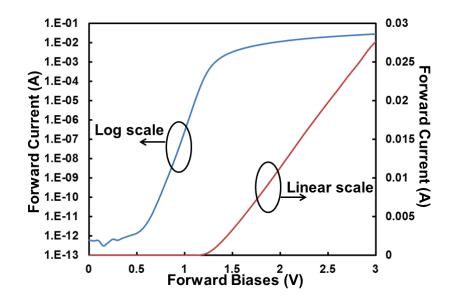

| Figure 5-1  | Forward I-V characteristics for a 60-µm-diameter circular diode in the sample                                                                                                                                                                                                                                           | 123 |

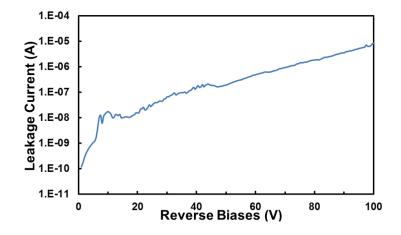

| Figure 5-2  | Reverse I-V characteristics for a 60-µm-diameter circular diode in the sample.                                                                                                                                                                                                                                          | 123 |

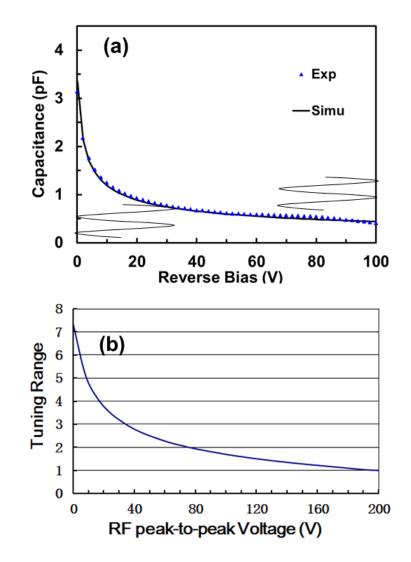

| Figure 5-3  | (a) High voltage C-V characteristics for a circular diode with an area of $5 \times 10^{-5}$ cm <sup>2</sup> at $f = 1$ MHz and (b) the corresponding tuning ratio vs RF peak-to-peak voltage for the anti-parallel diode varactor, based on the considerations of not causing reverse breakdown or forward conduction. | 125 |

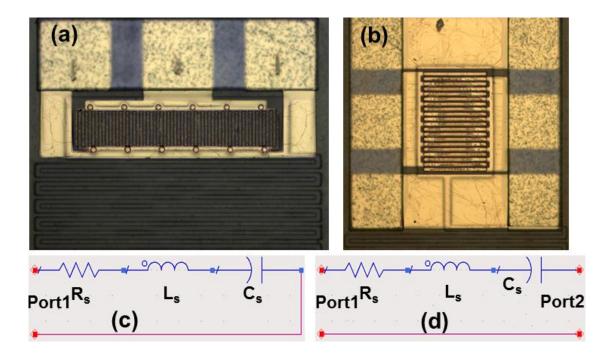

| Figure 5-4  | (a) An optical microscopy image of a device for 1-port<br>measurements, (b) an optical microscopy image of a device for<br>2-port measurements, (c) the equivalent series LRC network<br>for the 1-port device and (d) the equivalent series LRC                                                                        |     |

|             | network for the 2-port device                                                                                                                                | 127 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

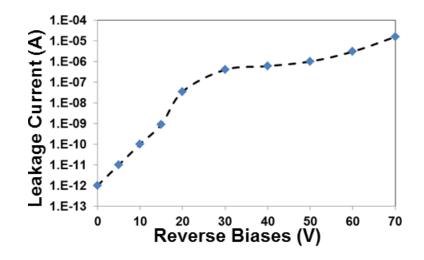

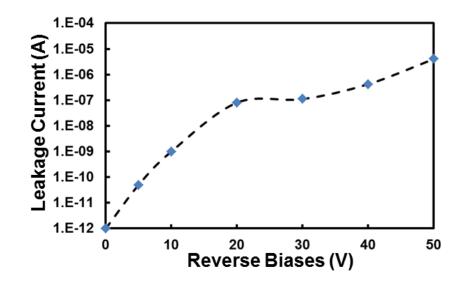

| Figure 5-5  | Reverse I-V curve for a 1-port anti-parallel diode varactor. The dots are the measurement data points                                                        | 129 |

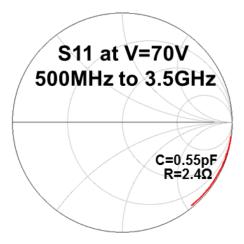

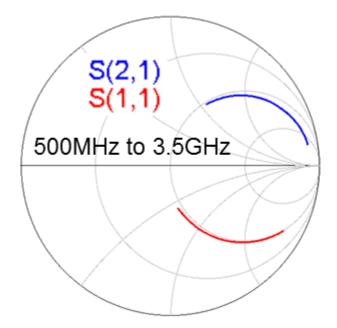

| Figure 5-6  | S11 from 500 MHz to 3.5 GHz for a 1-port device at a reverse bias of 70 V.                                                                                   | 129 |

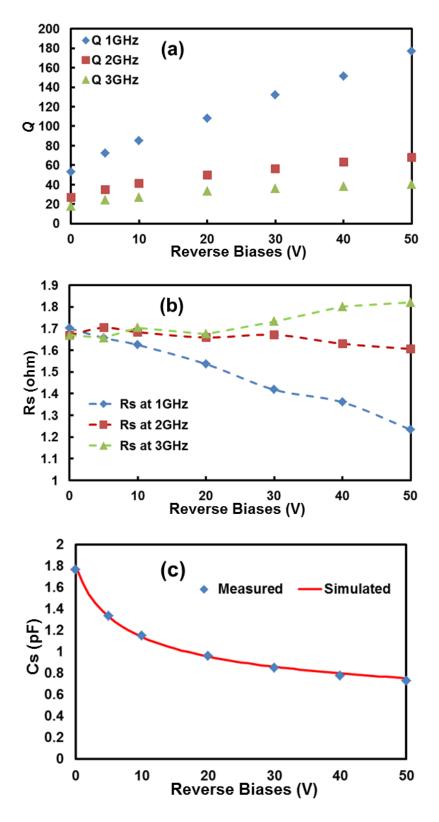

| Figure 5-7  | The relations of (a) $Q$ versus reverse bias, (b) $R_s$ versus reverse bias and (c) $C_s$ versus reverse bias at 1 GHz, 2 GHz and 3 GHz for a 1-port device. | 131 |

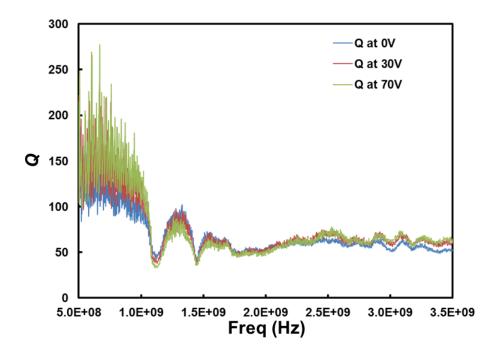

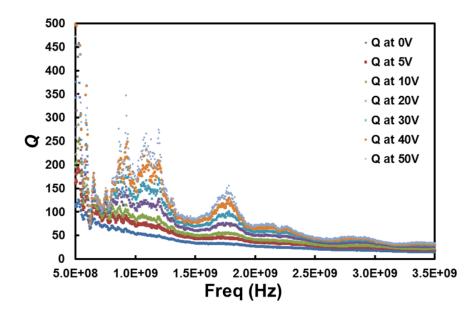

| Figure 5-8  | The relation of $Q$ versus frequency at different reverse biases for a 1-port device                                                                         | 132 |

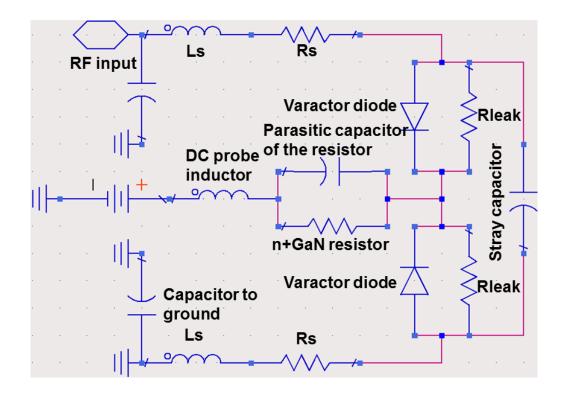

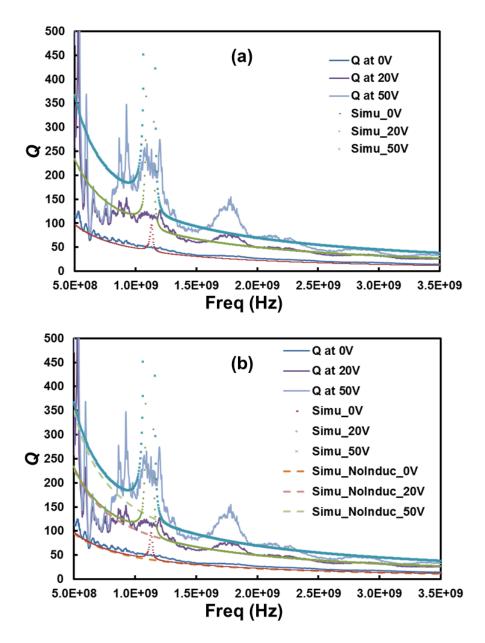

| Figure 5-9  | Equivalent circuit model considering the parasitics from the 1-<br>port device and the measurement setup                                                     | 133 |

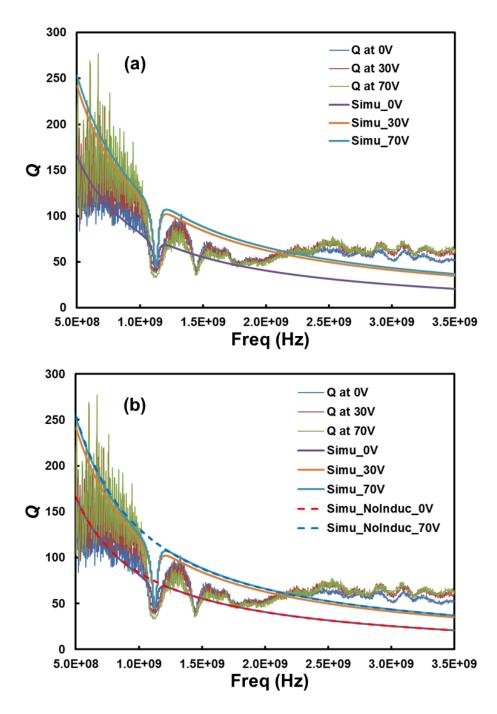

| Figure 5-10 | Experimental and simulated $Q$ versus frequency curves at different reverse biases for a 1-port device.                                                      | 135 |

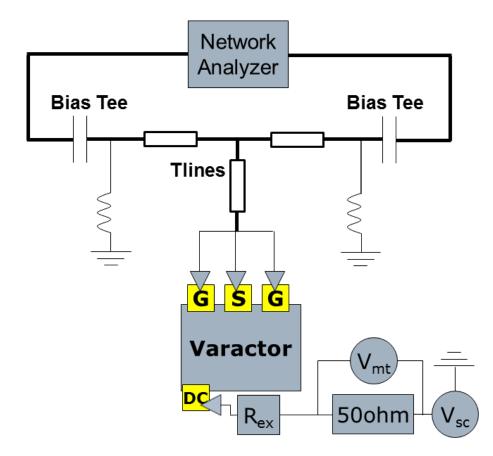

| Figure 5-11 | Schematic diagram for the 2-port measurements                                                                                                                | 136 |

| Figure 5-12 | Reverse I-V curve for a 2-port anti-parallel diode varactor. The dots are the measurement data points                                                        | 137 |

| Figure 5-13 | The representative S-parameters for the varactor 2-port measurements                                                                                         | 138 |

| Figure 5-14 | The relations of (a) $Q$ versus reverse bias, (b) $R_s$ versus reverse bias and (c) $C_s$ versus reverse bias at 1 GHz, 2 GHz and 3 GHz for a 2-port device  | 140 |

| Figure 5-15 | The experimental and simulated C <sub>s</sub> versus reverse bias curves for a 1-port device.                                                                | 141 |

| Figure 5-16 | The relation between $Q$ and frequency at different reverse biases for a 2-port device.                                                                      | 142 |

| Figure 5-17 | Experimental and simulated $Q$ versus frequency curves at different reverse biases for a 2-port device                                                       | 143 |

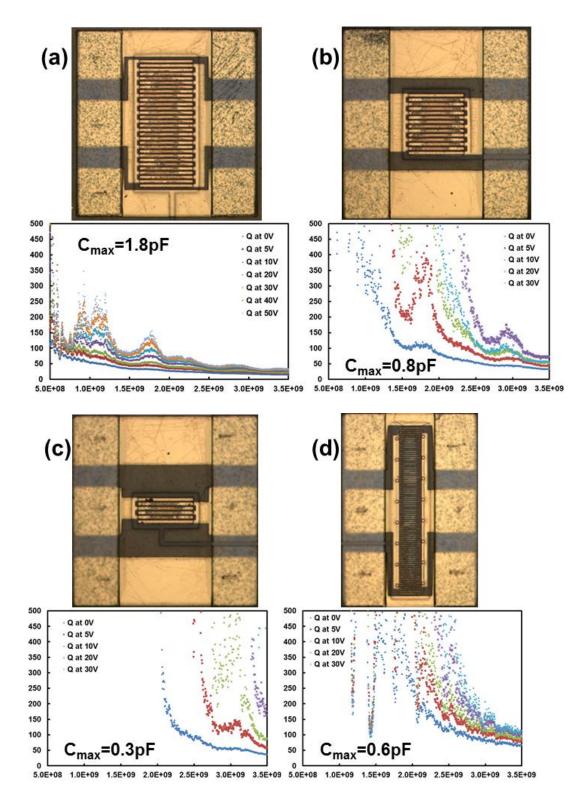

| Figure 5-18 | Optical microscopy images and the corresponding experimental Q versus frequency curves for the 2-port devices                                                |     |

|             | with different areas and structures                                                                                                                                       | 145 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

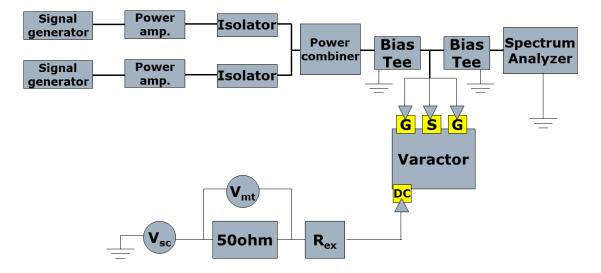

| Figure 5-19 | Measurement setup for the two-tone test                                                                                                                                   | 147 |

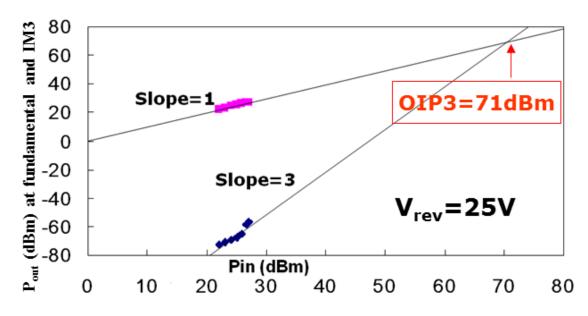

| Figure 5-20 | Output power at fundamental and IM3 frequencies versus the input power for an anti-parallel diode varactor (1-port) at a control reverse bias of 25 V                     | 148 |

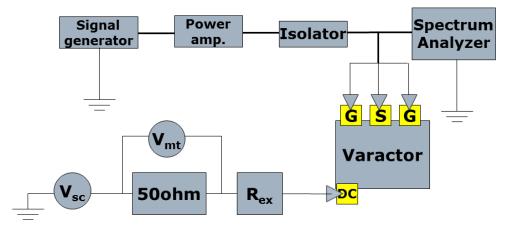

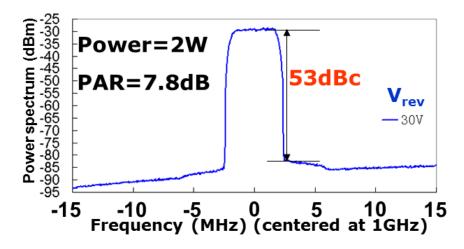

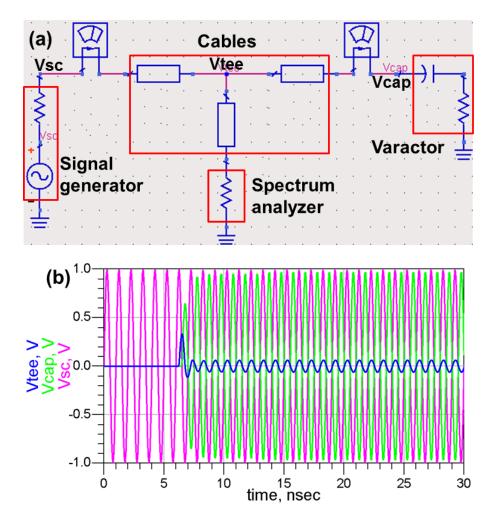

| Figure 5-21 | Measurement setup for the WCDMA signal input experiment                                                                                                                   | 150 |

| Figure 5-22 | Adjacent channel leakage ratio (ACLR) for a small 1-port device with a 2-W (12-W peak power) WCDMA signal input                                                           | 151 |

| Figure 5-23 | (a) Equivalent circuit model of the measurement system for the WCDMA signal input experiment, and (b) simulated instantaneous RF voltage at different nodes               | 152 |

| Figure 5-24 | Measurement setup of the tunable resonant circuit using the varactor and transmission lines                                                                               | 153 |

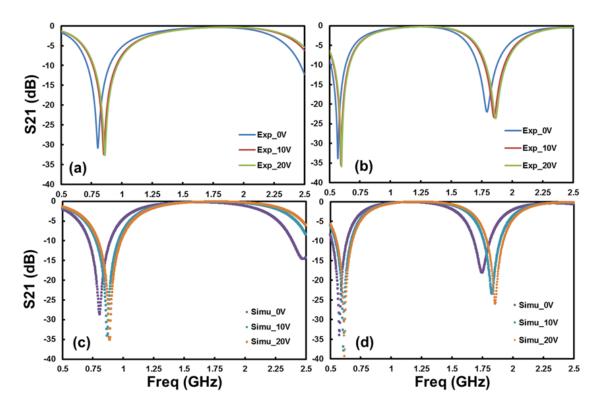

| Figure 5-25 | (a), (b) Experimental and (c), (d) the corresponding simulated S21 curves from 0.5 GHz to 2.5 GHz, for the tunable resonant circuit using varactor and transmission lines | 154 |

### LIST OF TABLES

| Table 1-1 | Comparison of properties and varactor figure of merit for<br>various semiconductors                                                                                                        | 7   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2-1 | Sample layer structures and labels                                                                                                                                                         | 17  |

| Table 3-1 | Sample labels and key growth details used in this study                                                                                                                                    | 35  |

| Table 3-2 | Values of the parameters used for all calculations (including forward and reverse I-V curves) in this work                                                                                 | 44  |

| Table 3-3 | Sample labels and key growth details used in this work                                                                                                                                     | 60  |

| Table 3-4 | FWHM of symmetric (0002) and asymmetric (10-12) XRCs, surface micromesa density estimated under Nomarski optical microscopy and nanopipe and TD densities estimated by EPD in all samples. | 61  |

| Table 4-1 | Samples treated with different sidewall cleaning and passivation methods                                                                                                                   | 115 |

| Table 5-1 | Measured and simulated OIP3 for the anti-parallel diode varactor with different n factors                                                                                                  | 149 |

| Table 6-1 | The performance parameters of different varactor technologies.                                                                                                                             | 161 |

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my dissertation advisor, Professor Paul Yu, who provided enlightening guidance and tremendous support throughout my research and life in the last six years at UCSD. He brought me to the world of MOCVD and Gallium Nitride, in which I found my interests. I am deeply indebted to my co-advisor, Professor Peter Asbeck, whose incisive and insightful advices always led me to the right directions. I am most impressed by his solid and comprehensive knowledge as well as his great patience during his discussions with students.

I would like to acknowledge Professor S. S. Lau, who was my teacher of ECE 136L and offered me a TAship for ECE 136L later on. He is not only my teacher of academics but also a good mentor of personality. I am very grateful to Prof. Tohru Nakamura, who is a professor in Hosei University. He provided lots of valuable comments to my thesis research and co-authored several papers during his visit at UCSD. I would like to thank Prof. Yu-Hwa Lo, who was my teacher of ECE 230A and ECE 236B as well as my thesis committee member. Also I am grateful for his excellent guidance to my wife's thesis research. I would like to thank Prof. Prabhakar R. Bandaru and Prof. Andrew C. Kummel for serving as my thesis committee members.

I would like to express my special thanks to my previous advisor Professor Yan Huimin at Zhejiang University, who always advise me selflessly not only in the research but also in my life. I would like to thank many other professors who taught me in classes and offered me all kinds of help at UCSD, including Prof. Yuan Taur, Prof. Jie Xiang, Prof. Deli Wang, Prof. Zhaowei Liu, Prof. Gabriel M. Rebeiz, etc.

I am most thankful for Mr. David Aplin and Arthur Clawson for their work training and helping me to keep the MOCVDs running smoothly and very thorough and practical discussions on crystal growth. I would like to thank Dr. Lingquan (Dennis) Wang for his great guidance and help on several projects and paper writing. He is not only my good friend but also a good teacher of mine. I would like to thank Dr. Winnie Chen for her excellent training skills to help me become an experimental researcher.

I would also like to thank those who were labmates and great coworkers, including Dr. Xiaobo Xie, Dr. Justin Bickford, Jeff Bloch, Dr. Meredith Draa, Dingbo Chen, Siyuan Gu, Hayg Dabag, Johana Yan, Dr. Paul Theilmann, Kangmu Lee, Wenyi Rai, Daniel Estrada, Conway Wang and Jianzhi Wu. Many thanks to friends and collaborators, including Dr. Peng Chen, Dr. Arthur Zhang, Dr. Hua Li, DanYong Lu, Feifei Wei, Muchuan Yang, Ke Sun, Yi Jing, Yuchun Zhou, Yanjin Kuang, and many of whom graciously lent me their time and lab equipment.

I would like to acknowledge the staffs at Nano3, Dr. Bernd Fruhberger, Larry Grissom, Ryan Anderson, Xuekun Lu, Sean Parks, Ahmet Erten, and Dr. Maribel Montero for their help in the cleanroom whenever needed. I would also like to thank all of the staffs at ECE, especially Cheryle Wills, Shana Slebioda, etc.

My deepest thanks go to my family. I am grateful to my parents whose selfless love and sacrifice are always the power for success. I am so indebted to my wife who is a great source of intelligence in our family and encourages me all the time when I encountered difficulties. All of the achievements I made she has a share. I owe lots of care to my son at his early ages. To all my family, I owe the greatest thanks for being the indispensable support of my growth.

Finally I would like to acknowledge the financial sponsors of my Ph.D research projects, including the FutureWei Technologies Inc., the University of California at San Diego Center for Wireless Communications, the National Science Foundation grant of NSF-ECCS-901113, the National Science Foundation under the program NIRT0506902, the UC Discovery Grant Program, the Army Research Office sponsored DURIP and the Department of Energy under the EERE-PMC program DE-FG36-08GO18016.

Section 1.1, 2.2 and 2.3, are a rearrangement of the project proposal "High Power Varactor Development for Adaptive Basestations," Peter M. Asbeck. The dissertation author was the primary researcher of this project. Section 1.2 and 2.1, are a rearrangement of the paper "InGaN/GaN Schottky Diodes With Enhanced Voltage Handling Capability for Varactor Applications," Wei Lu, Lingquan Wang, Siyuan Gu, David P. R. Aplin, Daniel M. Estrada, Paul K. L. Yu, and Peter M. Asbeck, IEEE Electron Device Letters, vol. 31, no. 10, pp. 1119–1121, Oct. 2010. The dissertation author was the primary author of the paper.

Section 3.1, 3.2 and 3.3, are a rearrangement of the paper "Analysis of Reverse Leakage Current and Breakdown Voltage in GaN and InGaN/GaN Schottky Barriers," Wei Lu, Lingquan Wang, Siyuan Gu, David P. R. Aplin, Daniel M. Estrada, Paul K. L. Yu, and Peter M. Asbeck, IEEE Trans. Electron Devices, vol. 58, no. 7, pp. 1986– 1994, Jul. 2011. The dissertation author was the primary author of the paper.

Section 3.4, is a rearrangement of the paper "Effects of surface micromesas on reverse leakage current in InGaN/GaN Schottky barriers," Wei Lu, Tomoaki Nishimura, Lingquan Wang, Tohru Nakamura, Paul K. L. Yu, and Peter M. Asbeck, J. Appl. Phys., vol. 112, pp.044505, Aug. 2012. The dissertation author was the primary author of the paper.

Section 4.3, is a rearrangement of the paper "InGaN/GaN Microwave Varactors with High *Q*, High-Breakdown Voltage and High Linearity," Wei Lu, Lingquan (Dennis) Wang, Siyuan Gu, David P. R. Aplin, Paul K. L. Yu, and Peter M. Asbeck, in Semiconductor Device Research Symposium (ISDRS), 2011 International,

IEEE, College Park, MD, 7-9 Dec., 2011. The dissertation author was the primary author of the paper.

#### VITA

| 2005 | B. S., Optical and Electrical Engineering         |

|------|---------------------------------------------------|

|      | Zhejiang University, Hangzhou, China              |

| 2007 | Completion of Graduate Study, Optical Engineering |

|      | Zhejiang University, Hangzhou, China              |

| 2011 | M. S., Electrical Engineering (Applied Physics)   |

|      | University of California, San Diego, USA          |

| 2013 | Ph. D., Electrical Engineering (Applied Physics)  |

|      | University of California, San Diego, USA          |

#### PUBLICATIONS

- <u>W. Lu</u>, L. Wang, S. Gu, D. P. R. Aplin, D. M. Estrada, P. K. L. Yu, and P. M. Asbeck, "InGaN/GaN Schottky Diodes with Enhanced Voltage Handling Capability for Varactor Applications," *IEEE Electron Device Lett.*, vol. 31, no. 10, pp. 1119–1121, Oct. 2010.

- <u>W. Lu</u>, L. Wang, S. Gu, D. P. R. Aplin, D. M. Estrada, P. K. L. Yu, and P. M. Asbeck, "Analysis of Reverse Leakage Current and Breakdown Voltage in GaN and InGaN/GaN Schottky Barriers," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 1986–1994, Jul. 2011.

- <u>W. Lu</u>, L. Wang, S. Gu, D. P. R. Aplin, P. K. L. Yu, and P. M. Asbeck, "InGaN/GaN Microwave Varactors with High *Q*, High-breakdown Voltage and High Linearity," in *Semiconductor Device Research Symposium (ISDRS), 2011 International*, IEEE, College Park, MD, 7-9 Dec., 2011.

- <u>W. Lu</u>, T. Nishimura, L. Wang, T. Nakamura, P. K. L. Yu, and P. M. Asbeck, "Effects of Surface Micromesas on Reverse Leakage Current in InGaN/GaN Schottky Barriers," *J. Appl. Phys.*, vol. 112, pp.044505, Aug. 2012.

- S. Gu, H. Katayose, K. Nomoto, T. Nakamura, A. Ohoka, K. Lee, W. Lu, and P.

M. Asbeck, "High Transconductance Ion-Implanted GaN MISFETs Using Atomic Layer Deposited High-k Dielectrics," *Phys. Status Solidi C*, 2013.

- <u>W. Lu</u>, L. Wang, S. Gu, P. M. Asbeck, and P. K. L. Yu, "Critical Design Considerations for GaN-based Microwave Power Varactors," in *Electronic Devices and Solid State Circuits (EDSSC), 2012 International*, IEEE, Bangkok, Thailand, 3-5 Dec., 2012.

- <u>W. Lu</u>, D. Aplin, A. R. Clawson, and P. K. L. Yu, "Effects of the Gas Ambient in Thermal Activation of Mg-doped p-GaN on Hall Effect and Photoluminescence," *Journal of Vacuum Science and Technology A*, vol. 31, 011502, Jan. 2013.

#### FIELD OF STUDY

Major Field: Electrical Engineering

Focused Field: Applied Physics

#### ABSTRACT OF THE DISSERTATION

GaN-based Microwave Power Varactors for Wireless Base Station Applications

by

Wei Lu

#### Doctor of Philosophy in Electrical Engineering (Applied Physics)

University of California, San Diego, 2013

Professor Paul K. L. Yu, Chair Professor Peter M. Asbeck, Co-Chair

With the development of wireless communication systems, the demand for providing tunability in the wireless communication circuits becomes more and more intense. Among the technologies, semiconductor varactor is the critical component that is capable of implementing tunable and adaptive characteristics, particularly for the frond-end components of the wireless communication systems. For base station applications, high voltage handling capability, typically of 100 V or greater, high

quality factor (Q), typically of above 100 at operation frequency, and high linearity, OIP3 > 65 dBm, are required. This work will mainly discuss in detail the design, fabrication and characterization to achieve the high-voltage high-Q and high-linearity microwave power varactors for wireless base station applications. Some preliminary varactor applications in the test tunable circuits will be demonstrated too.

In this dissertation, we first introduce the physics of the semiconductor varactors and the motivation for choosing GaN as the candidate material for this microwave power varactor. Then we elucidate the critical design considerations for achieving high breakdown voltage, high quality factor and high linearity. The novel Schottky barrier engineered design using a thin InGaN surface layer on top of GaN to enhance the breakdown voltage of GaN-based Schottky diodes is therefore introduced. We then show the theoretical and experimental studies on the suppression mechanisms for electron tunneling in the InGaN/GaN Schottky barriers. The detailed material characterization for the InGaN/GaN material system and its application for the enhancement-mode HEMTs are also presented. Next, we discuss the initial device fabrication procedure and the improving methods based on the initial DC and RF measurement results. Thereafter, we report the detailed characterizations of the fabricated devices including the high-voltage I-V and C-V, S-parameters for 1-port and 2-port devices, linearity and application in the tunable resonant circuits. Finally, we summarize the dissertation and outline the future work.

In this work, we achieved a high-performance GaN-based microwave power varactors with breakdown voltage > 100 V, quality factor > 100 and OIP3 > 71 dBm. It meets the initial goal of this project as well as the specifications in some practical

XXV

applications. To the best of our knowledge, this combination of breakdown voltage, Q and OIP3 represents remarkable advancement from any other reported varactors.

# Chapter 1

# Introduction

#### **1.1 Introduction to varactors**

Future generations of wireless base station systems need to respond to a wide variety of requirements concerning carrier frequency, output power, modulation bandwidth and peak-to-average ratio. To meet these requirements, the base stations need to be much more adaptive than they are at present. It is envisioned that the carrier frequency should be able to be controllably varied over a wide spectral range, to make use of different channels and different bands. The characteristics of the amplifiers should also be controllably variable in order to adapt to different environments and different specifications, such as output power level, antenna condition, and linearity specifications. Such adaptation requirements can provide new levels of performance to base stations utilizing the architecture currently in use; and even greater benefits can be obtained with future architectures based on software defined radio concepts, where a single RF front-end, under software control, can meet the requirements for all bands and signaling formats. Cognitive radio is a further development of this idea, in which "white spaces" in the RF spectrum are identified and utilized for opportunistic transmissions. To permit this adaptability while maintaining satisfactory performance of high RX (receive) input sensitivity and high TX (transmit) output efficiency, very high performance tunable microwave filters and matching networks are required. In turn, new enabling components are needed in order to provide this tunability. One of the most promising avenues is to develop tunable capacitors (or varactors). For base station applications, however, the varactors must be able to handle very high voltage levels (peak RF voltages above 100 V), have very high Q (greater than 100), and have very high linearity. This combination of specifications has not been obtainable to date with available technologies - which include semiconductor varactors, MEMS, and ferroelectric-/piezoelectric- based [1] systems.

The key objective of this research is to develop varactor diodes capable of providing high Q in high power operation and to demonstrate them in adaptive microwave circuits. Comparing with MEMS, or ferroelectric-/piezoelectric-based varactor technology, semiconductor Schottky diode varactors provide faster tuning and higher reliability. Semiconductor varactors have traditionally been implemented with Si or GaAs-based diodes, for which the depletion region thickness (depletion capacitance) can be varied with applied voltage. The resultant devices, however, typically do not have sufficient voltage handling capability for the output of a power amplifier, or, if they are designed particularly for high voltage operation, then their Q values at microwave frequencies are too low, so that they cause significant loss of output power and efficiency. The linearity of the varactors is also a critical concern. SiC power varactors have been recently developed and reported [2]. This research

explores varactors based on GaN materials, which have dramatic new opportunities for improved performance in high-power microwave applications; the relevant figure of merit (see next section) for GaN is  $40 \times$  larger than that of Si for this application. The new varactors are an enabling technology for wireless base stations, since for the first time, the varactors will be able to operate at the power levels required in the base station front-ends.

#### **1.2** Figure of merit for GaN-based microwave power varactors

Microwave varactors provide the ability to tune the impedance matching of microwave components, and varying the operating frequency of amplifiers, oscillators and filters. They are important elements for the implementation of tunable and adaptive microwave systems and can assist in enabling efficient multi-band and software-defined radios. Critical considerations for the application of microwave varactors are: the maximum to minimum capacitance ratio (*r*), the maximum voltage handling capability ( $V_{max}$ ), and the microwave loss (as represented by the *Q* value, defined below). In order to apply varactors to the tuning of microwave power amplifiers, it is typically necessary to have large capacitance ratios (*r*>2~3), high voltage handling capability ( $V_{max} > 25V$  and up to 200V), and high *Q* values (*Q*>200). The proposed study is based on our observation that GaN has significant material

advantages for the implementation of varactor diodes. A figure-of-merit is derived below, and shown to be larger for GaN than for Si by a factor of more than 40.

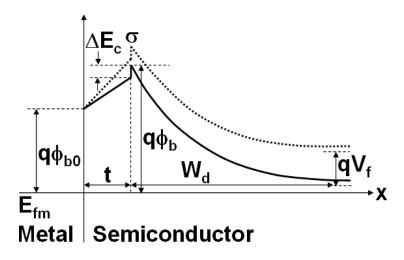

A schematic diagram of a Schottky-diode based varactor is shown in Fig. 1. Under external bias control, the width of the depletion region is varied in the n<sup>-</sup> varactor region. Underlying this region, an n<sup>+</sup> layer serves to provide contact to the backside. The Q value of the varactor under a given operating condition is the ratio of capacitive reactance to series resistance, and can be calculated by  $1/(2\pi/RC)$ , where C is the capacitance, and R is the resistance at the operating condition (when the overall impedance is considered as a simple series RC network). Both R and C vary as the depletion capacitance is changed with the control voltage. The worst case Q is  $Q_{min}$ , which occurs generally when C reaches its maximum value. We will consider  $Q_{min}$  in the following.

Figure 1-1 Schematic structure of Schottky-diode based semiconductor varactor.

For the varactor, the capacitance C is given by  $A\varepsilon/W$ , where W is the depletion region width at a given voltage bias, A is the junction area and  $\varepsilon$  is the dielectric constant of the semiconductor. Thus  $C_{max}=A\varepsilon/W_{min}$  (which occurs at the lowest control voltages),  $C_{min}=A\varepsilon/W_{max}$  (ignoring stray capacitances), and  $r=W_{max}/W_{min}$ . We will assume in the following that the doping level is constant in the lightly doped n<sup>-</sup> varactor region. The series resistance R comprises various contributions. In the following we neglect series resistance from contacts and n<sup>+</sup> region, and assume that the undepleted portion of the "lightly doped" varactor region dominates the resistance. The width of this undepleted region (and hence the resistance) varies with the control voltage. R is then given by  $\rho(W_{max}-W)/A$ , where  $\rho$  is the n<sup>-</sup> material resistivity, constant across the varactor region. Therefore,

$$Q_{min}^{-1} = \frac{2\pi f \varepsilon \rho (W_{max} - W_{min})}{W_{min}} = 2\pi f \varepsilon \rho (r - 1)$$

Eq. 1-1

The resistivity in the undepleted varactor region,  $\rho$ , is given by  $1/(n\mu q)$ , where *n* is the carrier density,  $\mu$  the carrier mobility and *q* the charge of the electron. The carrier density (and the corresponding doping density N<sub>d</sub>) is limited by the need to keep the maximum electric field, E<sub>max</sub>, below the critical breakdown electric field, E<sub>bk</sub>, when the varactor region is fully depleted. Using the constant N<sub>d</sub> (constant *n*) design, this constraint is given by

$$E_{max} = \frac{qN_d W_{max}}{\varepsilon} < E_{bk}$$

The maximum voltage supported under these conditions is  $V_{max} = E_{max}W_{max}/2$ . It follows that  $N_d < \varepsilon E_{bk}^2/(2qV_{max})$ , and from the above it follows that

$$Q_{min} < \frac{\mu E_{bk}^2}{[4\pi (r-1)fV_{max}]}$$

Eq. 1-3

The factor  $\mu E_{bk}^2$  constitutes a material figure of merit that indicates the potential of a given material for attaining high Q varactors, while the factor  $1/[4\pi(r-1)fV_{max}]$  corresponds to varactor design parameters, independent of material. The equation illustrates that attaining high Q is particularly challenging for circuits in which the voltage level is high (as needed in high power amplifiers). It is of interest to compare the varactor figure-of-merit for different semiconductor material technologies. Table 1-1 below shows values appropriate to Si, GaAs, InP and GaN [3]. Values of  $Q_{min}$  are also calculated for a representative scenario (f=1 GHz, r=3,  $V_{max}=100$  V). The figure-of-merit obtained for GaN is the highest in the table, higher than that of Si by a factor of more than  $40 \times$ . This suggests that for microwave power amplifiers, designs based on GaN will be attractive.

Eq. 1-2

| Properties and $Q_{\min}$                 | Si   | GaAs | InP  | GaN  |

|-------------------------------------------|------|------|------|------|

| $\mu$ (cm <sup>2</sup> /Vsec)             | 1200 | 4000 | 3500 | 500  |

| $E_{bk}$ (MV/cm)                          | 0.25 | 0.35 | 0.40 | 2.5  |

| $\mu E_{bk}^{2}$ (10 <sup>12</sup> V/sec) | 75   | 490  | 560  | 3125 |

| $Q_{min}$                                 | 30   | 195  | 223  | 1240 |

Table 1-1 Comparison of properties and varactor figure of merit for various semiconductors. The calculated  $Q_{\min}$  is shown for the materials for the condition f=1 GHz, r=3 and  $V_{\max}=100$  V.

Table 1-1 provides an upper bound to the  $Q_{\min}$  that can be expected for a given material. In actual implementation, the series resistance will incorporate also portions corresponding to the n<sup>+</sup> regions, bond-wires and interconnects, and potentially from the ohmic contact regions.

## **1.3** Overview of the dissertation

This dissertation explores a technology to achieve high-voltage, high-Q and high-linearity microwave varactors in order to provide tunable and adaptive characteristics to the wireless base station systems. GaN with its high electron mobility and high breakdown electric field is used as the candidate material for this technology. In Chapter 1, the needs of microwave power varactors in the wireless base station applications are illustrated. The criteria for choosing the candidate semiconductor materials are also discussed. Chapter 2 details the design considerations for achieving high breakdown voltage, high Q and high linearity. Epitaxial layer structure is designed to achieve the required breakdown voltage and Q. Optimized interdigitated and anti-parallel-diode device structures are used to improve the Q and linearity, respectively. Chapter 3 describes the invention of thin InGaN surface layer on top of GaN to enhance the Schottky barrier height and increase the breakdown voltage of the GaN-based Schottky diodes. InGaN/GaN material MOCVD growth, material characterization, thermal effects on Ni-InGaN/GaN Schottky junctions and its application in the enhancement-mode HEMTs are also presented. Chapter 4 discusses the fabrication procedure and preliminary DC and RF results of the microwave power varactors. Simulated and experimental results for various sidewall passivation methods to reduce reverse leakage current and maintain low leakage current during device fabrication are also reported. Chapter 5 demonstrates the final experimental DC and RF results and the corresponding simulations of the GaNbase microwave power varactors. Varactors with breakdown voltage of > 100 V, Q > 100 and OIP3 > 71 dBm (ACLR < -53 dBc) are achieved. Demonstration of the real application for the GaN-based microwave power varactors are also carried out by using the varactors in a tunable resonance circuit. Finally, Chapter 6 summarizes the entire dissertation and outlines the future work.

Section 1.1, is part of the project proposal "High Power Varactor Development for Adaptive Basestations", Peter M. Asbeck. The dissertation author was the primary researcher of this project. Section 1.2, is part of the paper "InGaN/GaN Schottky Diodes With Enhanced Voltage Handling Capability for Varactor Applications", Wei Lu, Lingquan Wang, Siyuan Gu, David P. R. Aplin, Daniel M. Estrada, Paul K. L. Yu, and Peter M. Asbeck, IEEE Electron Device Letters, vol. 31, no. 10, pp. 1119–1121, Oct. 2010. The dissertation author was the primary author of the paper.

### 1.4 References

- [1] P. Padmini, T. R. Taylor, M. J. Lefevre, A.S. Nagra, R. A. York and J. S. Speck, "Realization of high tunability barium strontium titanate thin films by RF magnetron sputtering," Applied Physics Letters, vol. 75, issue 20, pp. 3186-3188, Nov. 1999.

- [2] C. M. Andersson, N. Ejebjörk, A. Henry, S. Andersson, E. Janzén, H. Zirath, and N. Rorsman, "A SiC varactor with large effective tuning range for microwave power applications," IEEE Electron Device Lett., vol. 32, no. 6, pp. 788–790, Jun. 2011.

- [3] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd Edition. Hoboken, NJ: Wiley, 2007.

### Chapter 2

# Design of GaN-based microwave power varactors

GaN-based varactors have been previously reported mainly fabricated with a GaN HFET process [1]-[3]. In this chapter, we discuss the design of the GaN varactors with vertical geometry as shown before in Figure 1-1 and illustrate that a higher voltage handling capability may be obtained with a suitable InGaN surface layer design. Designs and simulations for optimizing the device layout to achieve high Q and high linearity will be also presented.

### 2.1 Design for high breakdown voltage

Figure 2-1 schematically shows the structure of a GaN varactor with vertical geometry. In order to achieve a breakdown voltage of larger than 100 V, the varactor region (n<sup>-</sup> GaN) thickness is designed to be  $t = 2V_{max}/E_{bk} = 1 \mu m$ , where  $V_{max} = 100 V$

and  $E_{bk}$  is conservatively assumed to be 2 MV/cm. The doping concentration of the n<sup>-</sup> GaN is estimated from 1-D Poisson equation:  $N_d = \epsilon E_{bk}/(qt) = 1 \times 10^{17}$  cm<sup>-3</sup>. The thickness and doping level of the underlying n<sup>+</sup> GaN region should be thick and high enough, but without deteriorating the material quality, to minimize the series resistance coming from this layer. In this design, they are chosen to be ~1.5 µm and  $5 \times 10^{18}$  cm<sup>-3</sup>, respectively. The material is grown on c-Sapphire substrates using metal organic chemical vapor deposition (MOCVD). Ni is used as the Schottky contact to ensure a high Schottky barrier height and Ti/Au/Pd/Au (Au is atop) metal stack is used as the ohmic contact.

Figure 2-1 Schematic diagram of a GaN-based varactor and its layer structure.

Then devices are fabricated and measured to verify the breakdown characteristics of the designed GaN Schottky diodes. The fabrication procedure is as follows: a 120-nm-thick Ni Schottky contact was deposited immediately after the sample MOCVD growth and NH<sub>4</sub>OH surface cleaning to minimize the interface

oxidation or contamination [4]. The Ni film was then patterned, and circular mesa diodes with diameters in the range of 80–300  $\mu$ m were formed using BCl<sub>3</sub>/Cl<sub>2</sub> in a Trion reactive-ion-etching/inductively-coupled plasma dry-etch system, which was followed by an ~90 °C KOH (0.1 mol/L) treatment to reduce the dry-etch residuals. A Ti/Al/Pd/Au (20 nm/80 nm/50 nm/100 nm) metal stack was used to form ohmic contacts to n<sup>+</sup> GaN. A scanning-electron microscopy (SEM) top view of the fabricated device is shown in Figure 2-2.

Figure 2-2 SEM top view of a fabricated diode with an 80-µm diameter.

The current-voltage (I-V) characteristics of these diodes were measured with an Agilent B1500 semiconductor device analyzer. The reverse I-V curve of a diode with an area of  $5 \times 10^{-5}$  cm<sup>2</sup> is shown in Figure 2-3. However, the breakdown voltage is lower and the reverse leakage current is higher than the expected values. The leakage current under a high reverse bias has been attributed to the direct tunneling of electrons through the Schottky barrier [5], [6]. For a proper operation and low-power loss of the GaN varactors, the leakage current of the Schottky diode must be adequately low even at high operating voltages. Therefore an improved design is needed to suppress the electron tunneling.

Figure 2-3 Reverse leakage current of a device with an area of  $5 \times 10^{-5}$  cm<sup>2</sup>.

It is known that large polarization-charge densities present at III-nitride semiconductor heterojunction interfaces significantly affect the electric-field distributions in the semiconductors [7], providing opportunities for Schottky-barrier engineering. To suppress the tunneling current under a high reverse bias, we designed an InGaN surface layer to engineer the tunneling barrier by utilizing the polarization charges at the InGaN/GaN interface. The new design and its corresponding electric field and energy band diagrams are shown in Figure 2-4 and 2-5, respectively. As

shown in Figure 2-5(a), in comparison to the design with GaN only, the surface electric field is reduced for the InGaN surface layer design, which leads to an increased electron tunneling distance. The significant reduction ( $\sim 50\%$  at a 100-V reverse bias) of the surface electric field is primarily due to the presence of the negative polarization charges at the InGaN/GaN interface, although the slightly increased dielectric constant of the InGaN also favors the surface field reduction. The suppression of the leakage current is thus achieved because the tunneling probability sharply decreases with the increase of the tunneling distance. The indium concentration and the thickness of the InGaN layer are designed to be 10% and 15 nm, respectively, based on the considerations of obtaining high-quality InGaN layers and resultant energy barrier shape. Figure 2-5(b) shows the corresponding energy band diagram at reverse 0 and 100 V by solving a 1-D Poisson equation. In this computation, a 4.9  $\times$  10<sup>12</sup> cm<sup>-2</sup> sheet polarization charge density and a 0.21-eV conduction band energy discontinuity [8] at the In<sub>0.1</sub>Ga<sub>0.9</sub>N/GaN interface were assumed. The Schottky barrier height of  $In_{0.1}Ga_{0.9}N$  was also assumed to be 0.21 eV lower than that of the GaN. As seen, at reverse 100 V, the tunneling distance for the InGaN/GaN design is  $\sim 2$  times larger than the design with GaN only.

Figure 2-4 Schematic diagram of the GaN-based Schottky diode design with thin InGaN surface layer for breakdown voltage enhancement.

Figure 2-5 (a) Schematic diagrams of the (upper) electric field and energy bands under the same reverse bias for the designs with InGaN/GaN and GaN only. W and W': Depletion width. L and L': Electron tunneling distance.  $\Delta \xi$ : Surface electric field reduction. (b) Representative energy band diagrams at reverse 0 and 100 V calculated by the 1-D Poisson solver [9].

The samples with and without InGaN surface layer design were grown using a Thomas Swan Close Coupled Showerhead  $3\times 2$  MOCVD system. For comparison purposes, three samples have been grown, with layer information and labels shown in Table 2-1. The Schottky diodes were then fabricated followed the same procedure stated above. The measured reverse IV characteristics are shown in Figure 2-6.

Table 2-1Sample layer structures and labels.

| Sample labels | Control                                                          | In <sub>0.06</sub> Ga <sub>0.94</sub> N | In <sub>0.1</sub> Ga <sub>0.9</sub> N |  |  |  |

|---------------|------------------------------------------------------------------|-----------------------------------------|---------------------------------------|--|--|--|

| InGaN layer   | N.A.                                                             | 6 % indium, ~15 nm                      | 10 % indium, ~15 nm                   |  |  |  |

|               | n GaN (n~1×10 <sup>17</sup> cm <sup>-3</sup> , 1 $\mu$ m)        |                                         |                                       |  |  |  |

| Common        | $n^+$ GaN ( $n \sim 5 \times 10^{18}$ cm <sup>-3</sup> , 1.5 µm) |                                         |                                       |  |  |  |

| layers        | undoped GaN buffer (~1.5 μm)                                     |                                         |                                       |  |  |  |

|               | c-sapphire substrate                                             |                                         |                                       |  |  |  |

Figure 2-6 Reverse IV characteristics for samples with and without InGaN surface layers. Circular diodes have areas of  $5 \times 10^{-5}$  cm<sup>2</sup>.

It is obvious that the inclusion of the InGaN surface layer significantly improves the breakdown voltage by up to ~40 V, in comparison with the control sample. Such improvement is consistently observed, for all of our InGaN-containing samples, as a result of the reduced surface electric field, as shown in Figure 2-5(a). These results validated the approach of implementing a thin InGaN surface layer on top of GaN is effective in achieving the GaN-based high-voltage microwave varactors. The detailed analysis including forward and reverse I-V, capacitance-voltage (C-V), material and thermal characteristics of the Ni-InGaN/GaN Schottky diodes will be discussed chapter 3.

### 2.2 Design for high linearity

In order to maintain adequate linearity in the amplifier, the effective varactor capacitance should not vary with the RF signal level. However, a single Schottky diode varactor has poor linearity due to the square root dependence of the capacitance on the applied voltage:  $C \sim V^{1/2}$ , for a uniformly doped junction. A well-established strategy to improve the linearity of diode-based varactors is to employ an anti-parallel (back-to-back) diode topology [10], in the geometry shown in Figure 2-7(b). In this circuit, the DC control voltage is applied to both diodes equally. The RF voltage swing, however, adds to the instantaneous voltage of each diode with opposite sign (such that the capacitance of one of the diodes is increased, while the other is decreased). The net capacitance under the application of DC voltage and RF voltage can be readily calculated; representative results for both two diode topologies are shown in Figure 2-7 for simple diodes with uniform n<sup>-</sup> doping. It is seen that by using the anti-parallel diode topology, the RF signal induced capacitance variation is minimized. The linearity of the varactor diode is thus significantly improved. An optimal choice of semiconductor doping profile can improve linearity further [10].

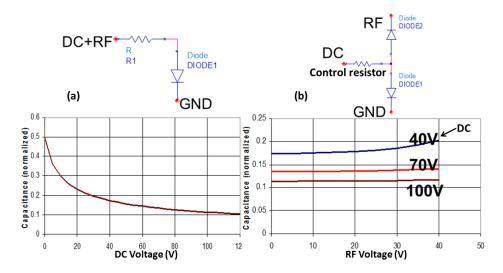

Figure 2-7 Simulated C-V curves for (a) single diode structure and (b) two antiparallel diode structure.

In this design, a center resistor, also called "control resistor" is needed to maintain a high Q factor. The impedance of the control resistor should be high enough to prevent the loss of the RF signal through the DC path (maintaining high Q factor), but not cause too much voltage drop through the DC path (maintaining tuning characteristics). In our design, the resistance of the control resistor  $R_{ctrl}$  is typically >  $10 \times |1/j\omega C|$ , where  $\omega$  is the operation frequency and C is the capacitance of the anti-parallel varactor. More design considerations on improving the Q will be discussed in the following section.

### **2.3** Design for high Q

In order to achieve high Q, the series resistance of the structure needs to be minimized. The component of resistance associated with the undepleted n<sup>-</sup> region is decreased by doping the n<sup>-</sup> region as high as is feasible, as discussed in section 1.2. The component of resistance associated with the n<sup>+</sup> backside contact is decreased by increasing the doping and thickness of the n<sup>+</sup> layer, and by decreasing the separation of the varactor regions. As a result of these considerations, an interdigitated stripe geometry is adopted, as shown schematically in Figure 2-8. The dimensions of the stripes are made as small as possible, consistent with the lithography and etch techniques available. The serpentine resistor made by n<sup>+</sup> GaN is the control resistor for blocking RF signals in the DC path. The design constraint of the R<sub>etrl</sub> is described in the previous section.

Figure 2-8 Schematic diagram of the anti-parallel diode structure with interdigitated strip geometry.

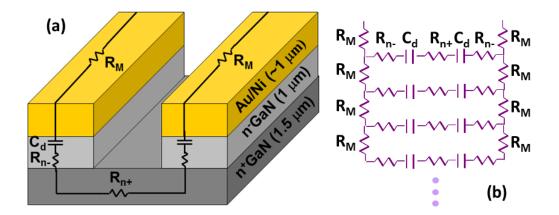

The series resistance expected from the  $n^+$  regions under the diodes is the principal parasitic; by contrast, the resistance from the undepleted  $n^-$  GaN region is usually very small. Bondwires add additional series resistance, exacerbated by skin effect as the frequency increases. An additional concern of significance for Q is the series resistance of the stripe (interdigitated) Schottky metal contacts. The distributed resistance of these metals can add appreciably to the overall resistance if the fingers are too long. In order to find out the optimal geometry of the interdigitated structure for the purpose of achieving high Q, a transmission line method considering the corresponding lump components is used to estimate the overall contribution from different regions of the structure. Fig. 2-9(a) shows the schematic diagram of an interdigitated diode structure with its corresponding lump components. The transmission-line circuit model was represented by a distributed resistance and capacitance as shown in Figure 2-9(b).

Figure 2-9 (a) Schematic diagram of the anti-parallel varactor diode with its corresponding lump components, and (b) the circuit model represented by a distributed resistance and capacitance.

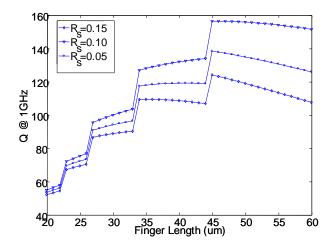

The calculation result shows that the overall Q is a function of finger length, with maximum values that differed according to the metal sheet resistance used, as detailed in Figure 2-10. A maximum Q value is achieved for a finger length of ~ 50 µm under the assumption of 2.5-µm finger width and spacing and 1-µm metal stripe thickness. Too long or too short metal length will result in a lower Q.

Figure 2-10 Simulated values of Q as a function of finger length.

Another lump component that is not considered in this model is the  $R_{leak}$  in parallel with the series  $R_{n-}$  and  $C_d$ , which represents the leakage path of the Schottky barrier. A small value of  $R_{leak}$  (corresponding to a leaky junction) will cause an increase of the series resistance so that the *Q* drops. The detailed analysis of reverse leakage current will be discussed in chapter 4.

### 2.4 Summary of the designs

This chapter covered the designs for achieving high-breakdown voltage, high-Q and high-linearity GaN-based microwave Schottky varactor diodes. A thin InGaN surface layer design is invented to increase breakdown voltage of the GaN-based Schottky diodes by ~40 V, from ~80 V to above 120 V. The anti-parallel diode topology will be adopted to improve the linearity performance of varactors. Interdigitated structure with small and optimized finger dimensions (upon the lithograph and processing techniques) and thick metal stripe will be used to maximize the Q.

Section 2.1, is a rearrangement of the paper "InGaN/GaN Schottky Diodes With Enhanced Voltage Handling Capability for Varactor Applications", Wei Lu, Lingquan Wang, Siyuan Gu, David P. R. Aplin, Daniel M. Estrada, Paul K. L. Yu, and Peter M. Asbeck, IEEE Electron Device Letters, vol. 31, no. 10, pp. 1119–1121, Oct. 2010. The dissertation author was the primary author of the paper.

Section 2.2 and 2.3, are a rearrangement of the project proposal "High Power Varactor Development for Adaptive Basestations", Peter M. Asbeck. The dissertation author was the primary researcher of this project.

### 2.5 References

- [1] M. Saglam, K. Mutamba, A. Megej, C. Sydlo, H. L. Hartnagel, and I. Daumiller, "Influence of polarization charges in Al<sub>0.4</sub>Ga<sub>0.6</sub>N/GaN barrier varactors," Appl. Phys. Lett., vol. 82, no. 2, pp. 227–229, Jan. 2003.

- [2] C. S. Chu, Y. G. Zhou, K. J. Chen, and K. M. Lau, "Q-factor characterization of RF GaN-based metal-semiconductor-metal planar interdigitated varactor," IEEE Electron Device Lett., vol. 26, no. 7, pp. 432–434, Jul. 2005.

- [3] M. Marso, A. Fox, G. Heidelberger, P. Kordos, and H. Luth, "Comparison of AlGaN/GaN MSM varactor diodes based on HFET and MOSHFET layer structures," IEEE Electron Device Lett., vol. 27, no. 12, pp. 945–947, Dec. 2006.

- [4] I. J. Lee, C. Yu, H. J. Shin, J. Y. Kim, Y. P. Lee, T. B. Hur, and H. K. Kim, " Oxidation study of polycrystalline InN film using in situ X-ray scattering and X-ray photoemission spectroscopy," Thin Solid Films, vol. 515, no. 11, pp. 4691–4695, Apr. 2006.

- [5] F. A. Padovani and R. Stratton, "Field and thermionic-field emission in Schottky barriers," Solid State Electron., vol. 9, no. 7, pp. 695–707, Jul. 1966.

- [6] T. Hashizume, J. Kotani, and H. Hasegawa, "Leakage mechanism in GaN and AlGaN Schottky interfaces," Appl. Phys. Lett., vol. 84, no. 24, pp. 4884–4886, Jun. 2004.

- [7] O. Ambacher, J. Majewski, C. Miskys, A. Link, M. Hermann, M. Eickhoff, M. Stutzmann, F. Bernardini, V. Fiorentini, V. Tilak, B. Schaff, and L. F. Eastman, "Pyroelectric properties of Al(In)GaN/GaN hetero- and quantum well structures," J. Phys.: Condens. Matter, vol. 14, no. 13, pp. 3399–3434, Apr. 2002.

- [8] H. Zhang, E. J. Miller, E. T. Yu, C. Poblenz, and J. S. Speck, "Measurement of polarization charge and conduction-band offset at  $In_xGa_{1-x}N/GaN$  heterojunction interfaces," Appl. Phys. Lett., vol. 84, no. 23, pp. 4644–4646, Jun. 2004.

- [9] Gregory Snider, "1-D Poisson solver," http://www3.nd.edu/~gsnider/

[10] K. Buisman, L. C. N. de Vreede, L. E. Larson, M. Spirito, A. Akhnoukh, T. L. M. Scholtes, and L. K. Nanver, "Distortion-free varactor diode topologies for RF adaptivity," in Proc. IEEE MTTS Int. Microwave Symp., Long Beach, CA, pp. 157–160, Jun. 2005.

## Chapter 3

# Ni-InGaN/GaN Schottky diode technology

III-nitride-based Schottky diodes have achieved many applications, such as ultraviolet photodetectors [1], gas sensors [2], high-voltage rectifiers [3], and varactors [4]. One key factor to improve the performance of these devices is to minimize reverse leakage current, particularly under high reverse voltages. For microwave power varactors, excess leakage current can cause Q degradation, device heating and reliability issue. Many prior efforts have been reported to reduce the leakage current in GaN-based Schottky barriers, such as electrochemical surface treatment [5], SiO<sub>2</sub> dielectric surface passivation [6], capping with low-temperature GaN layers [7], and oppositely doped surface layers to increase the Schottky-barrier height (SBH) [8]. However, these studies do not discuss in detail the leakage-current-suppression mechanisms particularly under high reverse voltages, which is important in highpower applications. In this chapter, we present a detailed study of the reverse-leakagecurrent mechanisms in MOCVD-grown GaN Schottky barrier diodes as well as the leakage-suppression mechanism using InGaN/GaN Schottky barriers. We also report that the leakage current can be further significantly suppressed by using a highpressure (HP, near atmospheric pressure) MOCVD growth technique [9] for the GaN buffer layers (i.e., an HP GaN buffer). Additionally, extensive InGaN/GaN material characterization using Nomarski optical microscopy, scanning electron microscopy, and atomic force microscopy are performed to correlate between the material defects and the excess reverse leakage current in Ni-InGaN/GaN Schottky barrier diodes. The application of InGaN/GaN design in the enhancement-mode GaN-based high electron mobility transistors (HEMTs) is also introduced.

### **3.1** Theory of InGaN surface layer design

Based on the introduction of the InGaN surface layer design for enhancing the breakdown voltages of the GaN-based Schottky diode varactors, furthermore analytical studies on the reverse leakage current and leakage current suppression mechanisms in the GaN-based Schottky diodes will be discussed in this section.

### 3.1.1 Analysis of reverse leakage current in GaN Schottky barriers

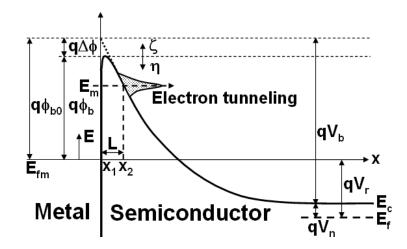

The reverse leakage current of the Schottky barrier has been attributed to the electron tunneling directly through the Schottky barrier [10], [11]. In order to suppress the leakage current, it is necessary to re-examine the leakage current mechanisms in

GaN Schottky barriers. Figure 3-1 shows a schematic energy band diagram of a Schottky barrier under reverse bias. According to conventional analysis [12], for reverse biases greater than 3kT/q the current density J<sub>r</sub> from semiconductor to metal through the Schottky barrier can be expressed by the following:

$$J_{r} = \frac{A^{*}T}{k} \exp\left[-\frac{q\phi_{b}}{kT}\right] \times \int_{0}^{\infty} P(\zeta) \exp\left(-\frac{\zeta}{kT}\right) d\zeta$$

$$+ \frac{A^{*}T}{k} \times \int_{0}^{q(V_{b} - \Delta\phi)} F_{m} P(\eta) [1 - F_{s}(V_{r})] d\eta$$

$$= J_{A} + J_{B}$$

Eq. 3-1

where  $A^*$  is the effective Richardson constant, *T* is the temperature in Kelvin, *k* is the Boltzmann constant, *q* is the charge of an electron,  $q\phi_b$  is the effective barrier height,  $V_b$  is the built-in potential at reverse bias  $V_r$  ignoring image force lowering,  $q\Delta\phi$  is the image force lowering of the barrier height,  $F_m$  and  $F_s$  are the Fermi-Dirac distribution functions of electrons in the metal and semiconductor, respectively,  $\zeta$  and  $\eta$  are the energy of the electrons above and below the top of the effective barrier, respectively, and  $P(\zeta)$  and  $P(\eta)$  are the tunneling probabilities of the electrons above and below the top of the electrons above and below the use of the electrons above and below the top of the effective barrier, respectively. Assuming  $P(\zeta) = 1$  and  $P(\eta)$  calculations using the Wentzel-Kramers-Brillouin (WKB) approximation [13], we find

$$P(E) = \exp\left[-2\frac{\sqrt{2m^*}}{\hbar}\int_{x1}^{x2}\sqrt{q\phi(x) - E}dx\right]$$

30