## **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Thin Film Encapsulation Methods for Large Area MEMS Packaging

#### **Permalink**

https://escholarship.org/uc/item/7jz7j897

#### **Author**

Mahajerin, Armon

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

### Thin Film Encapsulation Methods for Large Area MEMS Packaging

By

### Armon Mahajerin

A dissertation submitted in partial satisfaction of the requirements in the degree of

Doctor of Philosophy

in

Engineering – Mechanical Engineering and the Designated Emphasis

in

Nanoscale Science & Engineering

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Liwei Lin, Chair Professor Dorian Liepmann Professor Tsu-Jae King Liu

Spring 2012

## Thin Film Encapsulation Methods for Large Area MEMS Packaging

Copyright 2012

by

Armon Mahajerin

#### Abstract

Thin Film Encapsulation Methods for Large Area MEMS Packaging

by

### Armon Mahajerin

Doctor of Philosophy in Engineering – Mechanical Engineering and the Designated Emphasis in Nanoscale Science and Engineering

University of California, Berkeley

Professor Liwei Lin, Chair

The past thirty years have seen rapid growth in products and technologies based on microelectromechanical systems (MEMS). However, one of the limiting factors in commercializing MEMS devices is packaging, which can be the most costly step in the manufacturing process. A MEMS package must protect the movable parts of the device while allowing it to interact with its surroundings. In addition, the miniaturization of sensors and actuators has made it possible to integrate MEMS fabrication with that of integrated circuit (IC) processing. Due to the varying requirements for different applications, a universal standard for packaging MEMS has been elusive. However, a growing trend has been the shift away from bonding a separate sealing substrate to the device substrate and toward thin film encapsulation. The latter method has the potential to reduce costs and materials usage while increasing device throughput and yield.

Two thin film encapsulation methods for creating large area packaged cavities on top of silicon substrates have been developed based on porous membrane structures. The first approach uses thin polysilicon as a permeable membrane. The polysilicon is deposited on top of a doped oxide using low pressure chemical vapor deposition (LPCVD) to a thickness less than 300 nm. High temperature annealing drives the dopant atoms from the oxide into the polysilicon film, creating gaps within the film through which hydrofluoric acid (HF) vapor penetrates and etches the buried oxide. In addition, a process of rapidly depositing oxides greater than 10  $\mu$ m thick without cracking due to residual stress has also been demonstrated. This is accomplished by using plasma enhanced chemical vapor deposition (PECVD) steps of 2.5  $\mu$ m thickness with interceding rapid thermal annealing (RTA). The permeable polysilicon membrane technology provides the foundation for wafer-level encapsulation of MEMS devices inside the cavities by depositing a thick structural layer either under vacuum or at arbitrary pressure environments.

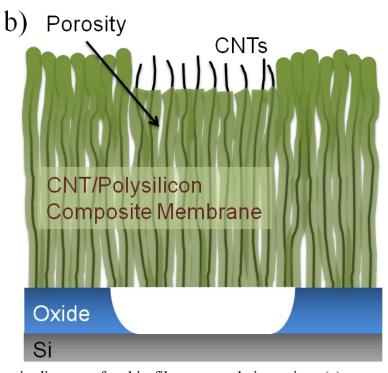

The thin permeable polysilicon technique then evolves into a broader encapsulation method in which a semi-permeable film is constructed from carbon nanotubes (CNTs) and polysilicon. The dense forest of CNTs may be grown to a height from  $10~\mu m$  to hundreds of  $\mu m$

as the structural foundation for the encapsulation layer. Conformally coating the CNTs with polysilicon by LPCVD generates natural pores within the thick membrane. HF vapor penetrates the semi-permeable film to selectively etch the bottom oxide layer, after which another polysilicon deposition seals the film, rendering it impermeable. The etching behavior has been characterized as a function of the CNT height and exposure time to HF vapor. The CNT/polysilicon thickness for a given vacuum-sealed cavity area has also been designed using finite element analysis (FEA). Furthermore, large sealing areas of more than 1x1 mm² have been successfully demonstrated. As such, this wafer-level encapsulation technology could find potential packaging applications of MEMS devices, including large area gyroscope structures.

"I'll be honest.

We're throwing science at the walls here to see what sticks.

No idea what it'll do."

- Cave Johnson

For Tatar

## **Contents**

| L  | ist of Figu | ires                                          | v  |

|----|-------------|-----------------------------------------------|----|

| L  | ist of Tab  | les                                           | X  |

| 1. | Introdu     | action                                        | 1  |

|    | 1.1 Mi      | croelectromechanical Systems                  | 1  |

|    | 1.2 MI      | EMS Fabrication                               | 2  |

|    | 1.3 Pag     | ckaging                                       | 5  |

|    | 1.4 Dis     | ssertation Overview                           | 6  |

| 2. | MEMS        | Packaging Overview                            | 8  |

|    | 2.1 Ba      | ckground                                      | 8  |

|    | 2.1.1       | Packaging Considerations                      | 8  |

|    | 2.1.2       | Challenges of Packaging MEMS                  | 9  |

|    | 2.2 Wa      | afer Level Packaging                          | 14 |

|    | 2.2.1       | Overview of Wafer Level Processes             | 14 |

|    | 2.2.2       | Interfacial Bonding                           | 14 |

|    | 2.2.3       | Thin Films                                    | 20 |

|    | 2.2.4       | Electrical Feedthrough                        | 26 |

|    | 2.3 Su      | mmary                                         | 27 |

| 3. | Thin Fi     | ilm Encapsulation Using Permeable Polysilicon | 29 |

|    | 3.1 Pro     | oject Background                              | 29 |

|    | 3.1.1       | Motivation                                    | 29 |

|    | 3.1.2       | Device Overview                               | 29 |

|    | 3.1.3       | Initial Fabrication Process.                  | 32 |

|    | 3.2 Mo      | odeling and Design                            | 34 |

|    | 3.2.1       | Theory of Membrane Behavior                   | 34 |

|    | 3 2 2       | Polysilicon Membrane                          | 35 |

| 3.2.3      | Thick TEOS as Membrane                                          | 41 |

|------------|-----------------------------------------------------------------|----|

| 3.2.4      | Mask Design                                                     | 43 |

| 3.3 As     | sessing Permeability of Polysilicon                             | 45 |

| 3.3.1      | Preliminary Studies                                             | 45 |

| 3.3.2      | Modified Fabrication Process Using TEOS Cap                     | 49 |

| 3.4 Ch     | aracterizing Etching Behavior                                   | 50 |

| 3.4.1      | HF Vapor Penetration                                            | 50 |

| 3.4.2      | Using a Silicon Nitride Hard Mask                               | 52 |

| 3.5 De     | position of Thick TEOS Films                                    | 55 |

| 3.5.1      | Issue with TEOS Cracking                                        | 55 |

| 3.5.2      | Rapid Thermal Annealing                                         | 56 |

| 3.5.3      | Results of TEOS + RTA                                           | 58 |

| 3.6 Su     | mmary                                                           | 60 |

| 4. Large A | Area Encapsulation Using Carbon Nanotube/Polysilicon Composites | 61 |

| 4.1 Ov     | erview                                                          | 61 |

| 4.1.1      | Motivation                                                      | 61 |

| 4.1.2      | Carbon Nanotube Background                                      | 61 |

| 4.1.3      | Carbon Nanotube Growth                                          | 63 |

| 4.1.4      | Proposed CNT/Polysilicon Composite                              | 65 |

| 4.2 Pre    | eliminary Results                                               | 66 |

| 4.2.1      | Fabrication Process                                             | 66 |

| 4.2.2      | CNT Growth and Polysilicon Deposition                           | 68 |

| 4.2.3      | Permeability of Composite Film                                  | 71 |

| 4.3 Mo     | odeling Deflection of the Composite Film                        | 75 |

| 4.3.1      | Reasoning for Measuring Deflection                              | 75 |

| 4.3.2      | Theory for Plate Deflection                                     | 77 |

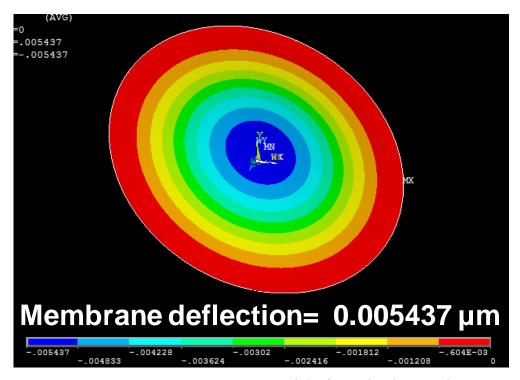

| 4.3.3      | Membrane Deflection Calculations and FEA                        | 79 |

| 4.3.4      | Design Methodology                                              | 83 |

| 4.4 Pro    | ocess Characterization                                          | 84 |

|            |                                                                 |    |

| 4.4    | 1.2    | Encapsulation and Deflection Under Vacuum | 87 |

|--------|--------|-------------------------------------------|----|

| 4.5    | Sun    | nmary                                     | 89 |

| 5. Co  | onclus | ions and Future Work                      | 91 |

| 5.1    | Cor    | nclusions                                 | 91 |

| 5.2    | Fut    | ure Work                                  | 93 |

| 5.2    | 2.1    | Redesign of Composite Membrane            | 93 |

| 5.2    | 2.2    | Characterizing Sealing Conditions         | 94 |

| 5.2    | 2.3    | Process Flow for Integrated MEMS Device   | 95 |

| Refere | nces   |                                           | 98 |

# List of Figures

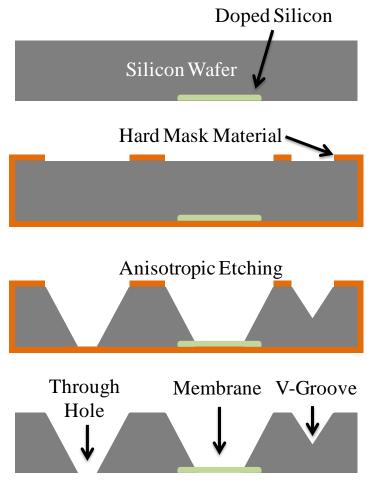

| Figure 1.1. Bulk micromachining using anisotropic etching                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

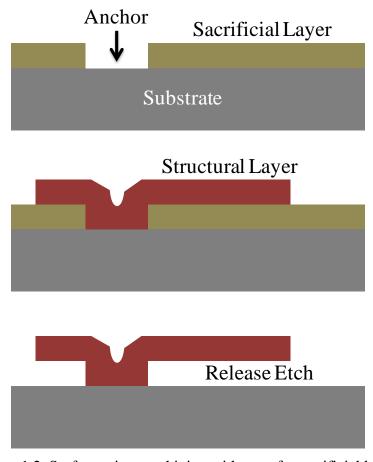

| Figure 1.2. Surface micromachining with use of a sacrificial layer                                                                                                                                                                                                                                  |

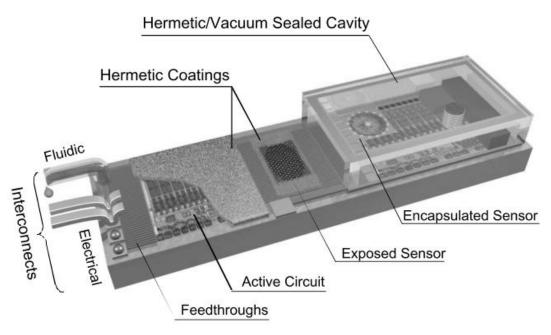

| Figure 1.3. Sample MEMS package with multiple interfaces. [17]                                                                                                                                                                                                                                      |

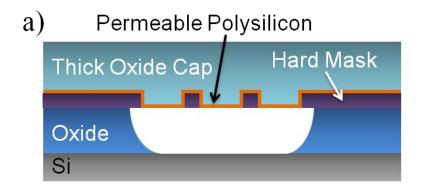

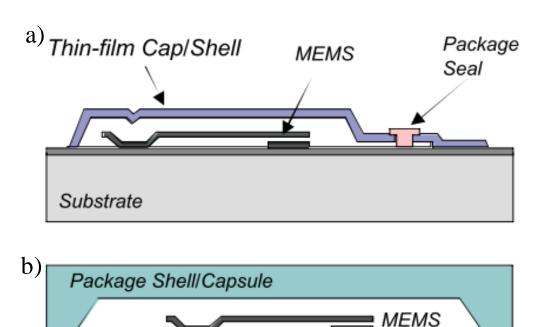

| Figure 1.4. Schematic diagrams for thin film encapsulation using: (a) permeable polysilicon, and (b) composites of carbon nanotubes and polysilicon                                                                                                                                                 |

| Figure 2.1. Comparison of die level and wafer level packaging                                                                                                                                                                                                                                       |

| Figure 2.2. Schematics of (a) an IC package and (b) a MEMS pressure sensor package. [21] 10                                                                                                                                                                                                         |

| Figure 2.3. Stiction of MEMS structures to silicon substrate after release                                                                                                                                                                                                                          |

| Figure 2.4. Effect of mismatch of coefficient of thermal expansion (CTE) on film stress 12                                                                                                                                                                                                          |

| Figure 2.5. Cross section of an interfacial capsule or shell bonded to a substrate. [17]                                                                                                                                                                                                            |

| Figure 2.6. Anodic bonding schematic showing (a) procedure with top tool functioning as a cathode and the chuck as an anode, and (b) ion drift in the Pyrex glass as a result of the electric field, forming a depletion zone at the interface to which O ions drift                                |

| Figure 2.7. Schematic diagram of Au-Si eutectic bonding for packaging a silicon cap wafer to a MEMS device wafer, (a) before bonding and (b) after bonding. [62]                                                                                                                                    |

| Figure 2.8. Schematic of localized bonding using on-chip resistors. [17]                                                                                                                                                                                                                            |

| Figure 2.9. SEM photograph of an encapsulated microresonator under a glass cap. [84] 19                                                                                                                                                                                                             |

| Figure 2.10. Schematic diagram of thermo-compressive Au-Au diffusion bonding. [85] 20                                                                                                                                                                                                               |

| Figure 2.11. Comparison of MEMS device packages sealed by using (a) a thin film membrane or (b) a bonded capsule. [17]                                                                                                                                                                              |

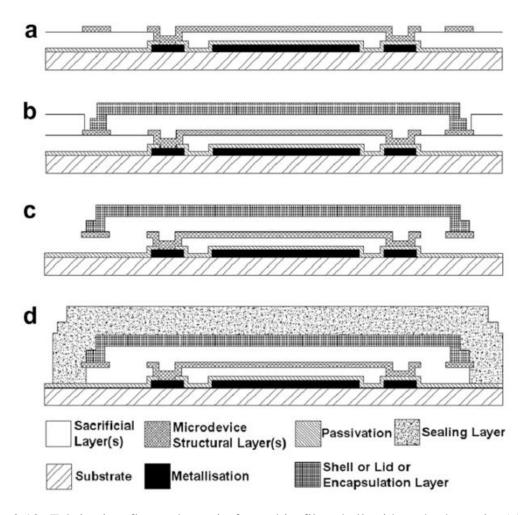

| Figure 2.12. Fabrication flow schematic for a thin film shell with etch channels: (a) device and etch channel formation; (b) second sacrificial layer deposition and encapsulation layer patterning; (c) simultaneous removal of both sacrificial layers; (d) sealing of encapsulation shell. [102] |

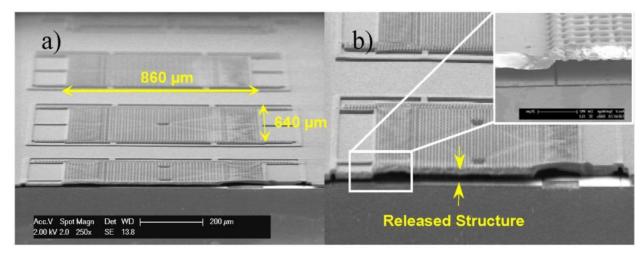

| Figure 2.13. Image of thin film encapsulated accelerometers: (a) released structure; (b) detailed cross-sectional view. [107]                                                                                                                                                                       |

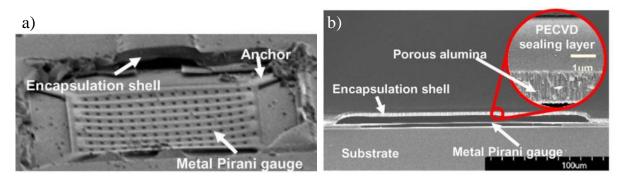

| Figure 2.14. Monolithically encapsulated Pirani gauge using porous alumina: (a) SEM photograph of the device under a broken shell; (b) cross-sectional view of the cavity. [116] 24                                                                                                                 |

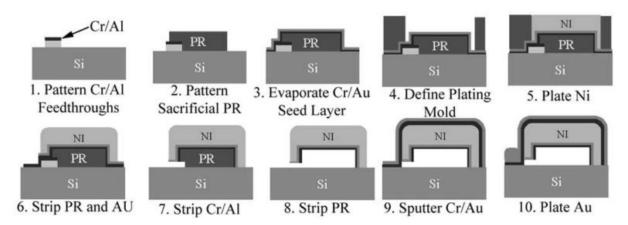

| Figure 2.15. Fabrication process for creating electroplated nickel vacuum packages. [117] 25                                                                                                                                                                                                        |

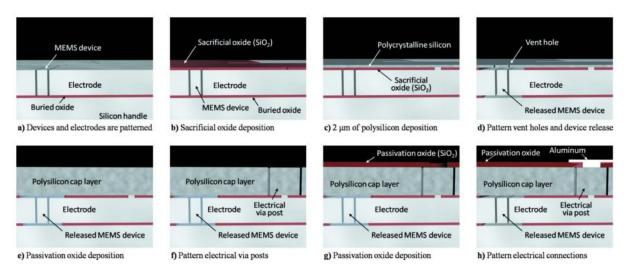

| Figure 2.16. Schematic of fabrication process for epitaxial polysilicon encapsulation, [122] 25                                                                                                                                                                                                     |

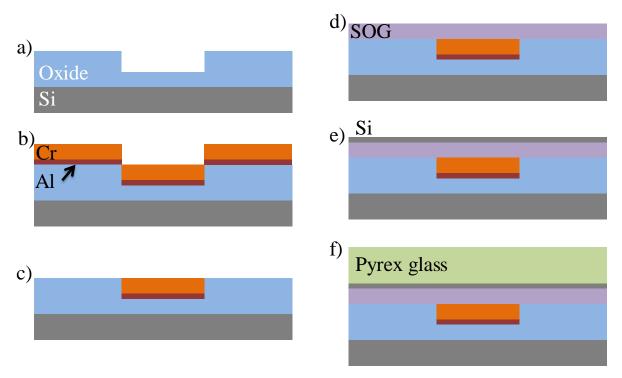

| Figure 2.17. Lateral feedthrough process flow for anodic bonding: (a) pattern oxide; (b) deposit metal; (c) lift-off; (d) SOG coating; (e) Si sputtering; (f) Pyrex cap anodic bonding                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

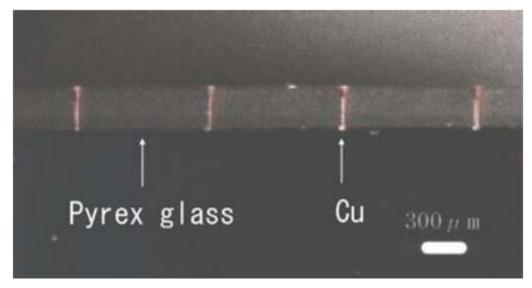

| Figure 2.18. Vertical electrical feedthrough with filled via holes in a Pyrex wafer. [128] 27                                                                                                                                                                                                                                                                                                                                       |

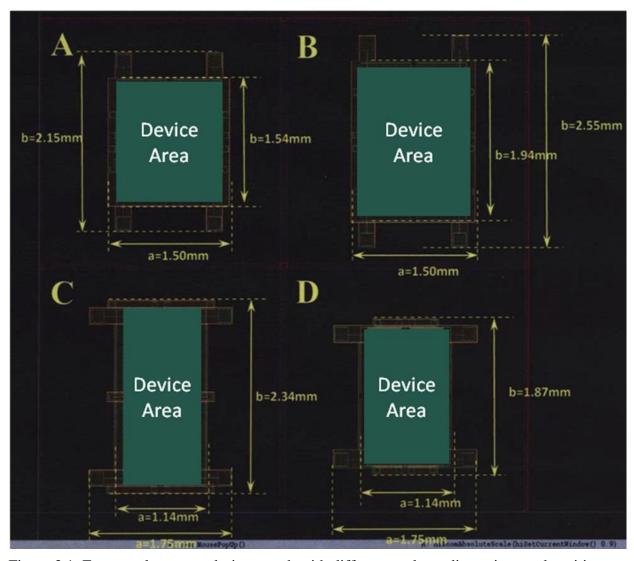

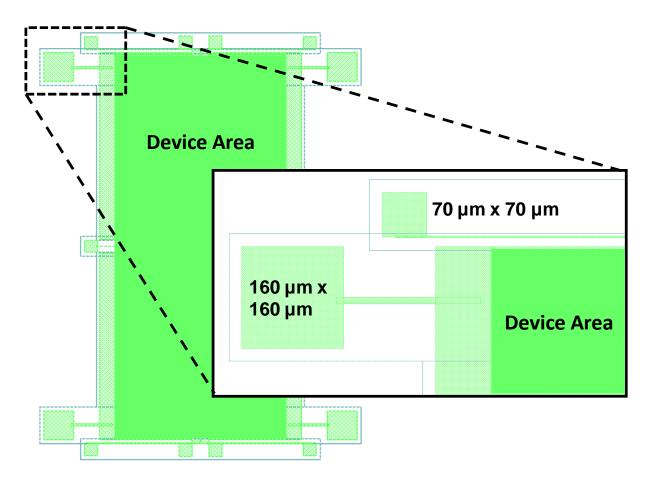

| Figure 3.1. Four accelerometer designs, each with different package dimensions and positions of the bonding pads                                                                                                                                                                                                                                                                                                                    |

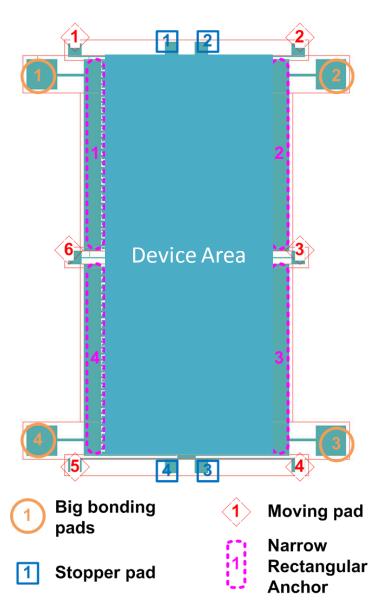

| Figure 3.2. Overview of device structural components                                                                                                                                                                                                                                                                                                                                                                                |

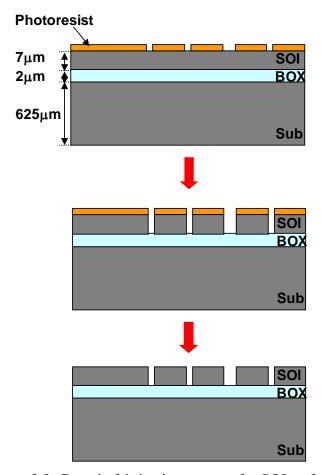

| Figure 3.3. Generic fabrication process for SOI wafers                                                                                                                                                                                                                                                                                                                                                                              |

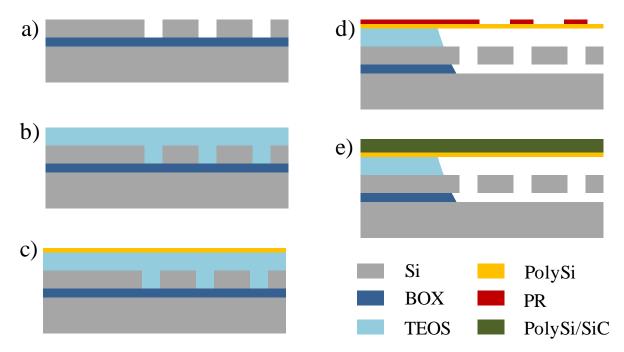

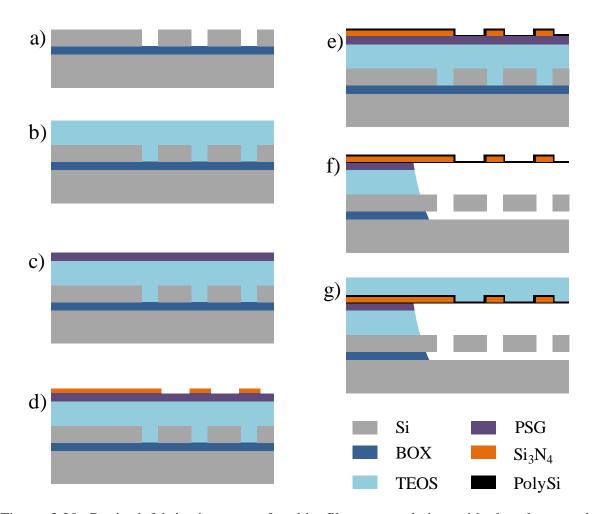

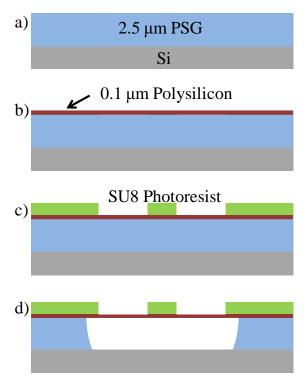

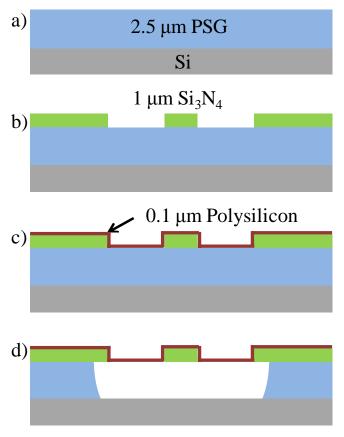

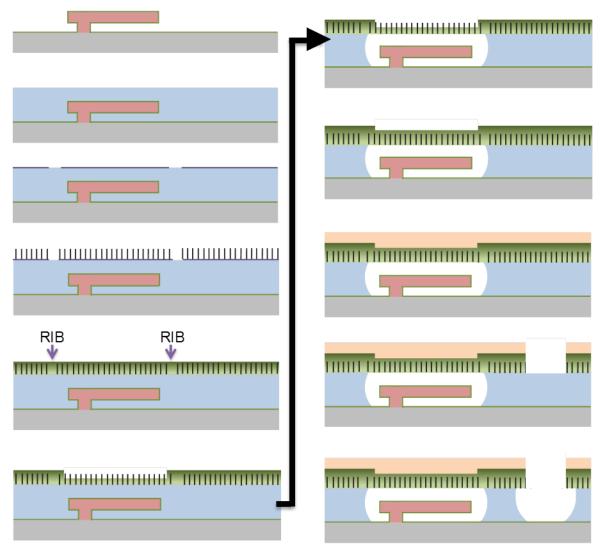

| Figure 3.4. Preliminary fabrication process for thin film encapsulation using thin polysilicon. (a) Begin with patterned SOI wafer; (b) deposit thick TEOS sacrificial layer via PECVD; (c) LPCVD thin polysilicon; (d) pattern photoresist to create etch windows and expose wafer to HF for removing underlying oxide; (e) seal cavity and strengthen membrane against deflection with additional polysilicon or silicon carbide. |

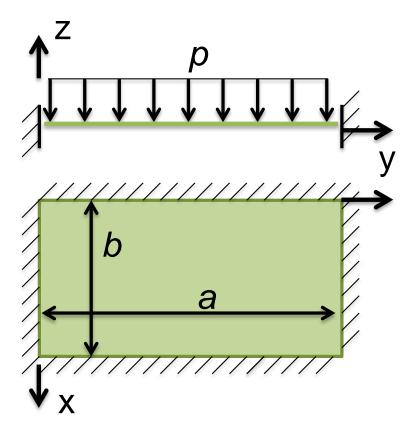

| Figure 3.5. Rectangular plate fixed along all edges under uniformly distributed load 34                                                                                                                                                                                                                                                                                                                                             |

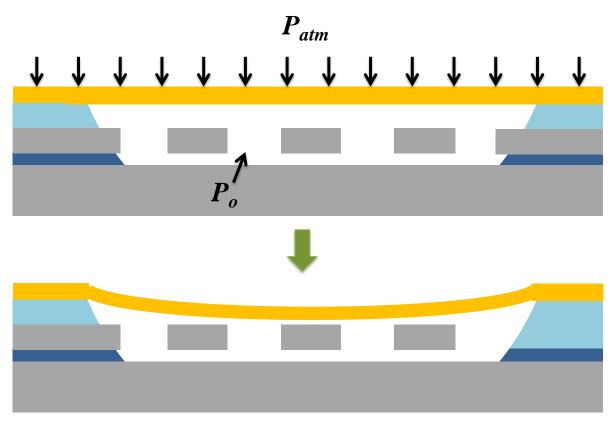

| Figure 3.6. Schematic of pressure load causing thin membranes to deform                                                                                                                                                                                                                                                                                                                                                             |

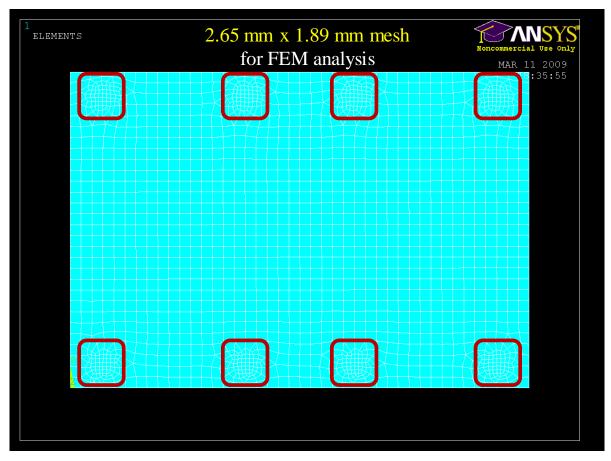

| Figure 3.7. FEA mesh area and pillar supports for generic thin polysilicon film                                                                                                                                                                                                                                                                                                                                                     |

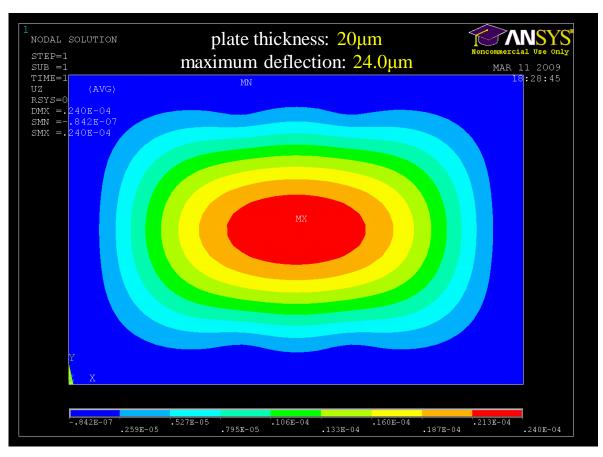

| Figure 3.8. Two-dimensional plot of maximum deflection for a 20 µm thick polysilicon membrane under vacuum load                                                                                                                                                                                                                                                                                                                     |

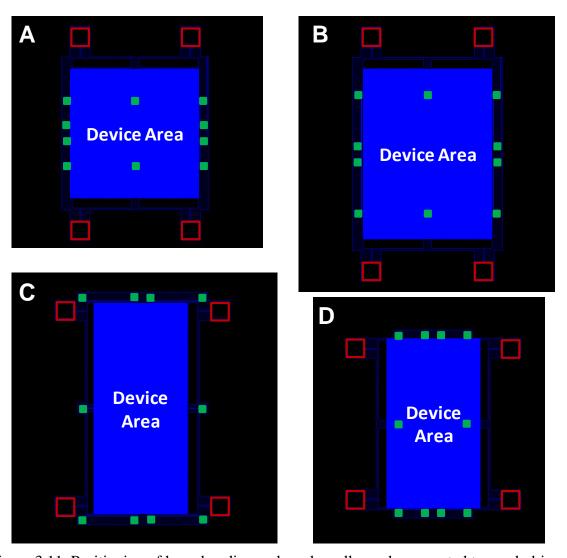

| Figure 3.9. Large area bonding pads on MEMS devices used as support pillars at each corner for thin membranes; smaller pads also may be treated as pillars to support polysilicon film                                                                                                                                                                                                                                              |

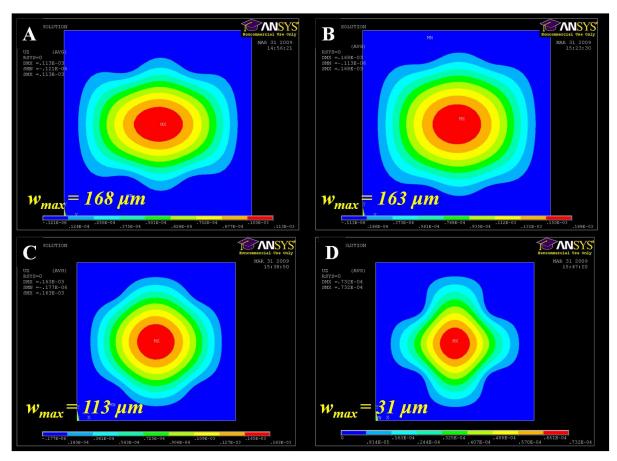

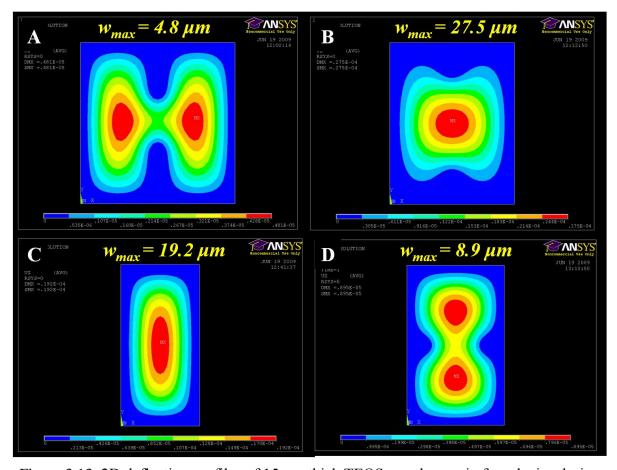

| Figure 3.10. 2D models in <i>ANSYS</i> for each membrane configuration based on support pad positions, showing maximum deflection under vacuum load at the center of each film                                                                                                                                                                                                                                                      |

| Figure 3.11. Positioning of large bonding pads and smaller pads connected to comb drives 41                                                                                                                                                                                                                                                                                                                                         |

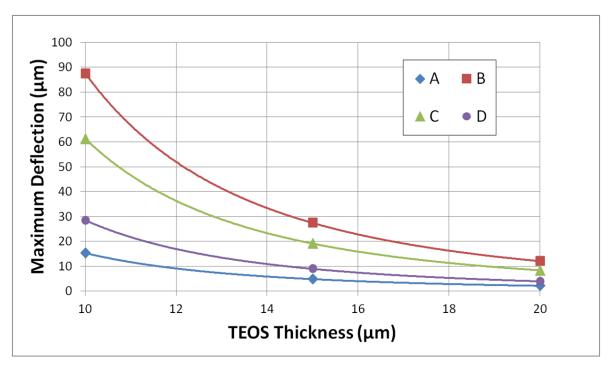

| Figure 3.12. Maximum film deflection vs. TEOS thickness for four different configurations $42$                                                                                                                                                                                                                                                                                                                                      |

| Figure 3.13. 2D deflection profiles of 15 $\mu m$ thick TEOS membranes in four device designs 43                                                                                                                                                                                                                                                                                                                                    |

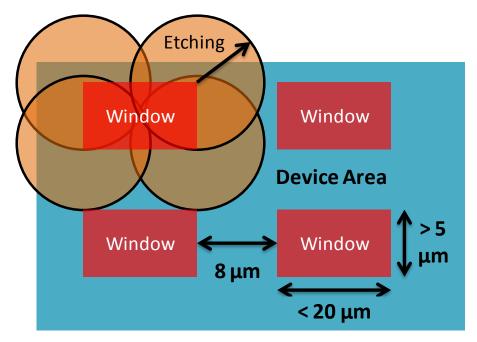

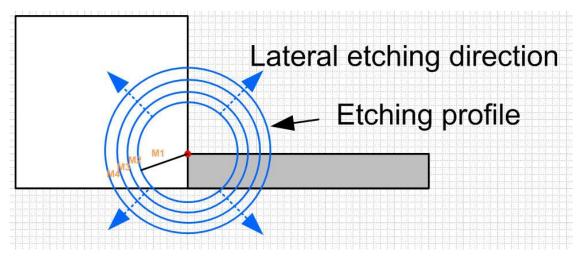

| Figure 3.14. Lateral undercut required for release of movable fingers (not to scale)                                                                                                                                                                                                                                                                                                                                                |

| Figure 3.15. Lateral undercut of bonding pad pillars (not to scale)                                                                                                                                                                                                                                                                                                                                                                 |

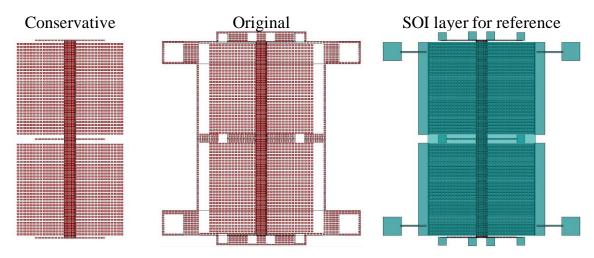

| Figure 3.16. Comparison of "conservative" and "original" etch mask layouts                                                                                                                                                                                                                                                                                                                                                          |

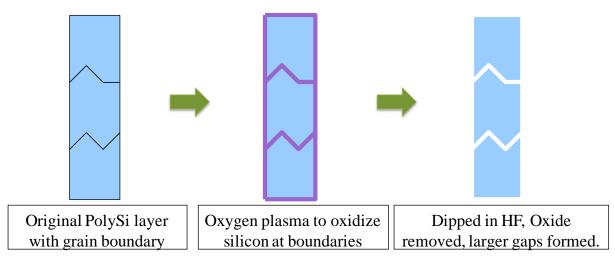

| Figure 3.17. Using oxygen plasma to generate gaps at polysilicon grain boundaries 46                                                                                                                                                                                                                                                                                                                                                |

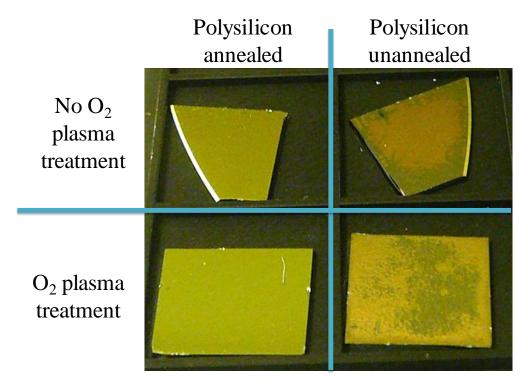

| Figure 3.18. Results of annealing and oxygen plasma treatment of polysilicon films 47                                                                                                                                                                                                                                                                                                                                               |

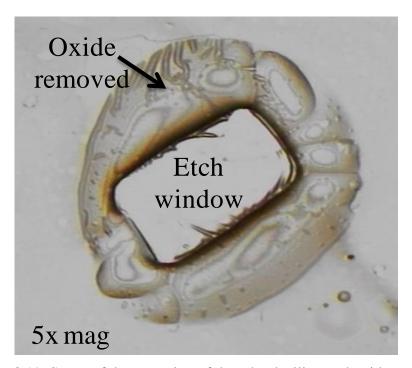

| Figure 3.19. Successful penetration of doped polysilion and oxide etching                                                                                                                                                                                                                                                                                                                                                           |

| Figure 3.20. Revised fabrication steps for thin film encapsulation with doped permeable polysilicon. (a) Begin with patterned SOI wafers; (b) deposit thick TEOS sacrificial layer via PECVD; (c) deposit PSG via LPCVD followed by high temperature densification; (d) LPCVD                                                                                                                                                       |

| and patterning of silicon nitride for hard mask; (e) LPCVD of polysilicon followed by dopant drive in annealing step; (f) HF vapor etching; (g) additional TEOS reinforcement                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

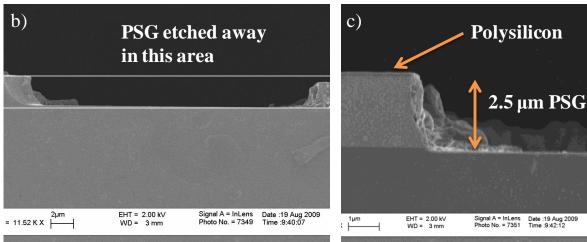

| Figure 3.21. Simplified fabrication process testing HF vapor penetration. (a) LPCVD deposition of PSG followed by densification; (b) LPCVD of polysilicon followed by dopant anneal; (c) spinning and patterning of SU8 photoresist for etch mask; (d) oxide removal by HF vapor penetration of permeable polysilicon                                                                                                                 |

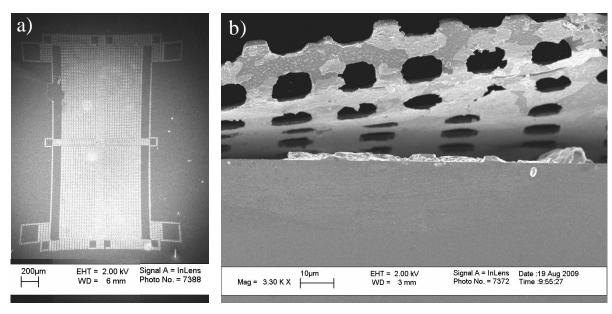

| Figure 3.22. SEM photographs of: (a) top view of patterned SU8 photoresist mask; and (b) cross-sectional view of etch holes in suspended SU8 layer                                                                                                                                                                                                                                                                                    |

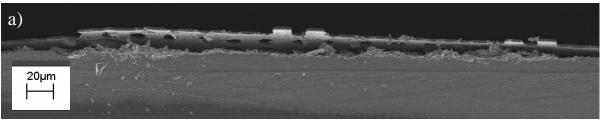

| Figure 3.23. SEM photographs showing: (a) suspended SU8 layer above etched cavity; and (b) PSG removed in select areas on substrate; and (c) thin polysilicon on top of PSG layer                                                                                                                                                                                                                                                     |

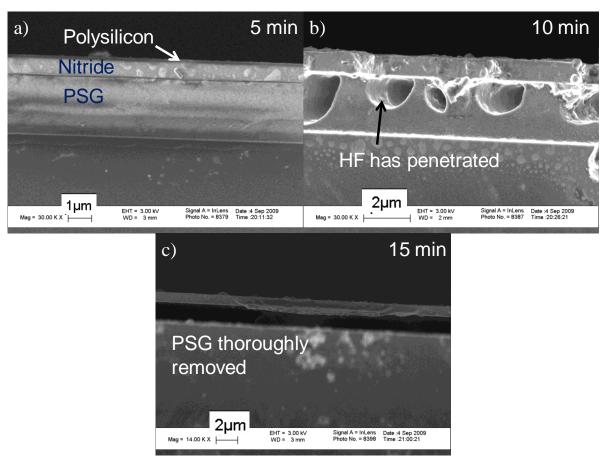

| Figure 3.24. Modified fabrication process testing nitride as a hard mask. (a) LPCVD deposition of PSG followed by densification; (b) LPCVD of silicon nitride; (c) LPCVD of polysilicon followed by annealing of dopant; (d) oxide removal by HF vapor penetration of permeable polysilicon                                                                                                                                           |

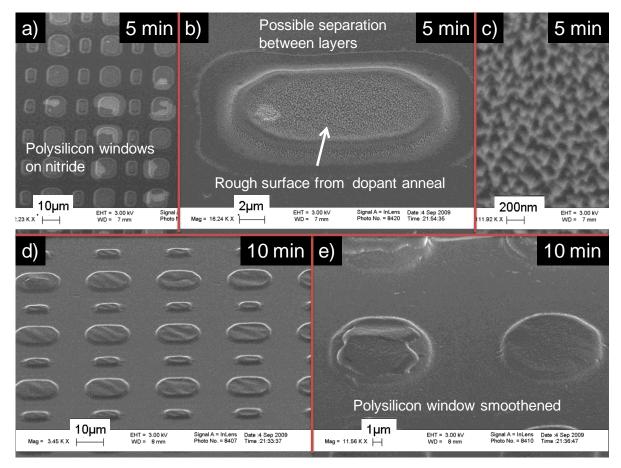

| Figure 3.25. Cross-sectional profiles of fabricated chips after HF vapor exposure times of: (a) 5 minutes; (b) 10 minutes; and (c) 15 minutes, showing the natural progression of HF penetration and removal of buried oxide underneath the nitride mask                                                                                                                                                                              |

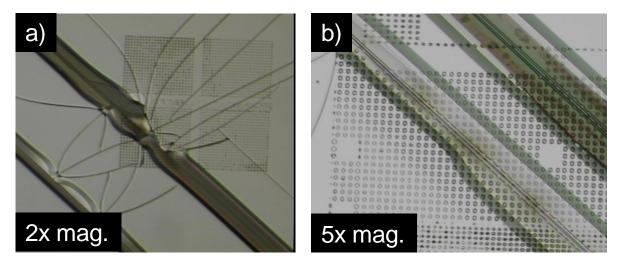

| Figure 3.26. Polysilicon etch windows on top of nitride hard mask: (a) after 5 min HF vapor; (b) roughness of polysilicon window can be seen; (c) close-up of poly roughness from doping; (d) after 10 min HF vapor; (e) close-up photo of polysilicon windows                                                                                                                                                                        |

| Figure 3.27. TEOS cracking on fabricated chips at (a) 2x and (b) 5x magnification                                                                                                                                                                                                                                                                                                                                                     |

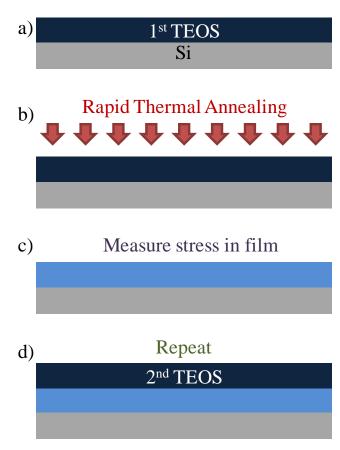

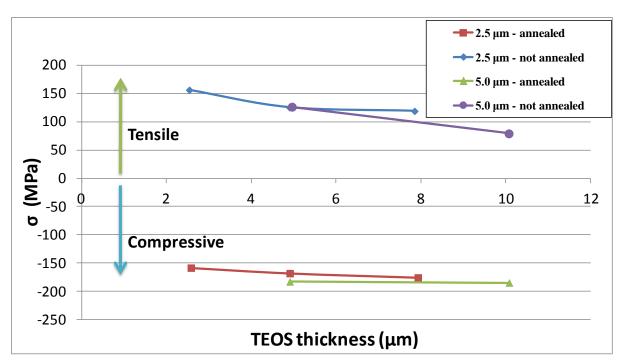

| Figure 3.28. Thick TEOS deposition with rapid thermal annealing: (a) deposit 1 <sup>st</sup> TEOS layer via PECVD; (b) clean wafer and perform RTA; (c) measure stress in deposited film with laser interferometer; (d) repeat until desired TEOS thickness is reached                                                                                                                                                                |

| Figure 3.29. Stress in deposited TEOS films vs. overall thickness                                                                                                                                                                                                                                                                                                                                                                     |

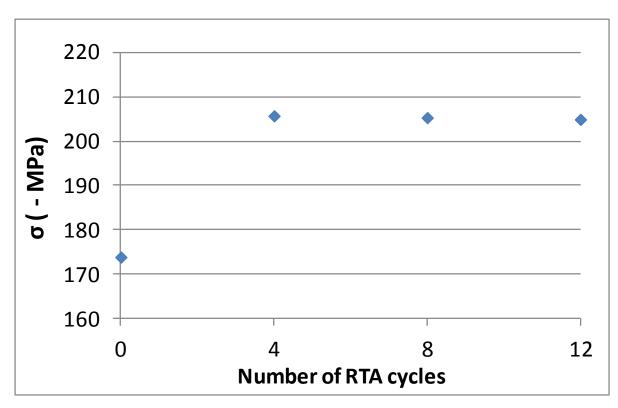

| Figure 3.30. Film stress of 10 µm TEOS after multiple rapid thermal anneals                                                                                                                                                                                                                                                                                                                                                           |

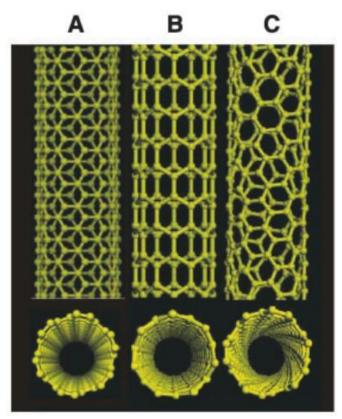

| Figure 4.1. Three different SWNT structures: (a) armchair; (b) zigzag; (c) chiral. [170] 62                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.2. Experimental setup for CNT growth on sample chips                                                                                                                                                                                                                                                                                                                                                                         |

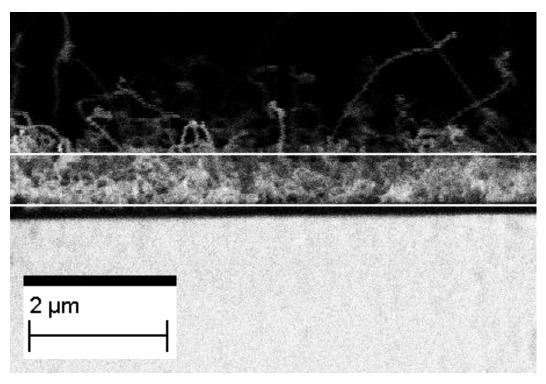

| Figure 4.3. Carbon nanofiber growth resulting from thick Fe catalyst                                                                                                                                                                                                                                                                                                                                                                  |

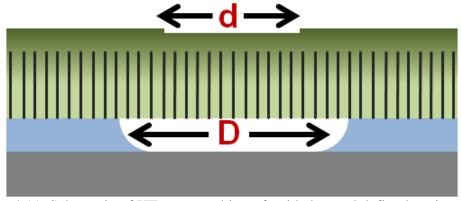

| Figure 4.4. Conceptual illustration of a semipermeable encapsulation membrane using a CNT/polysilicon composite                                                                                                                                                                                                                                                                                                                       |

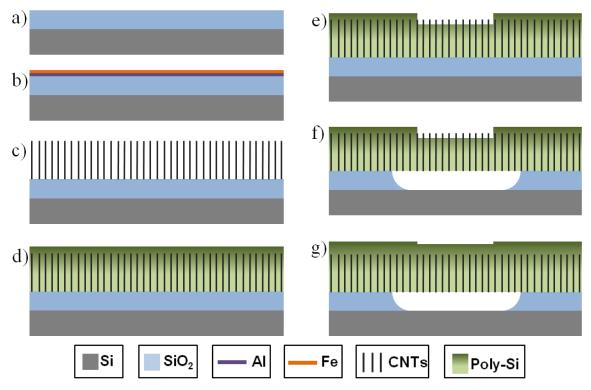

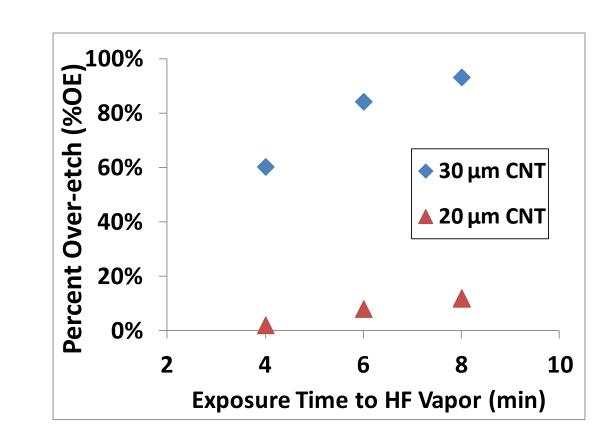

| Figure 4.5. Fabrication process for CNT/polysilicon composite: (a) LPCVD of low-temperature oxide or PECVD of TEOS oxide; (b) evaporation of metal Al and Fe films; (c) CNT growth via CVD; (d) first polysilicon LPCVD to conformally coat CNTs; (e) pattern top surface of polysilicon and plasma etch select area to open membrane pores (f) HF vapor penetration and oxide removal; (g) second polysilicon LPCVD to seal the film |

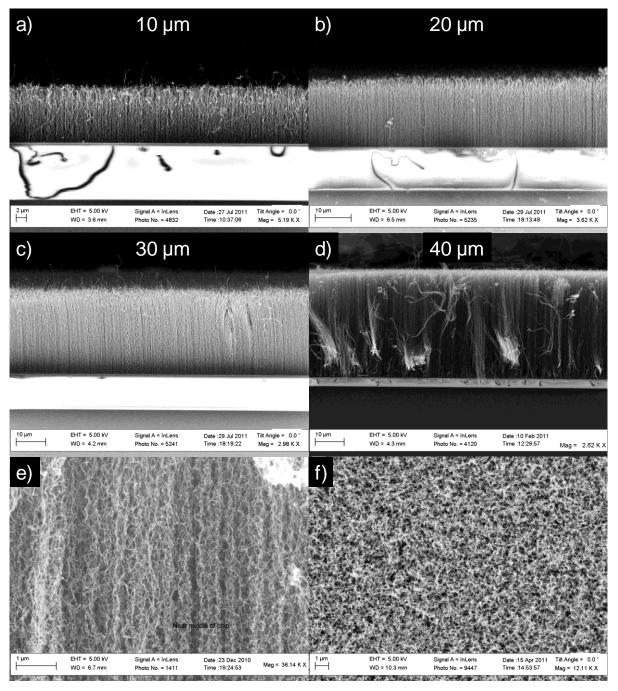

| Figure 4.6. CNT growth results for forest heights of: (a) 10 $\mu$ m, (b) 20 $\mu$ m, (c) 30 $\mu$ m, and (d) 40 $\mu$ m; (e) close up of CNT forest; (f) top view of CNT forest                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

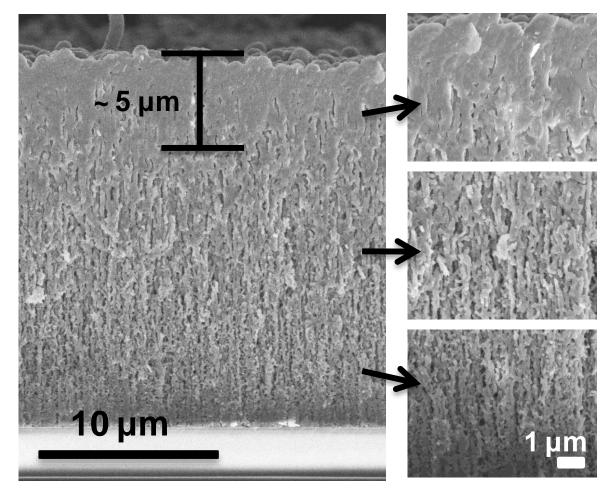

| Figure 4.7. Polysilicon deposition onto CNT forests, showing thickness variation from top to bottom as well as the natural seal of the top 5 $\mu$ m of the membrane                                                                                          |

| Figure 4.8. Profile of defined etch window after 4 min plasma etching of polysilicon: (a) cross-sectional view; (b) top view                                                                                                                                  |

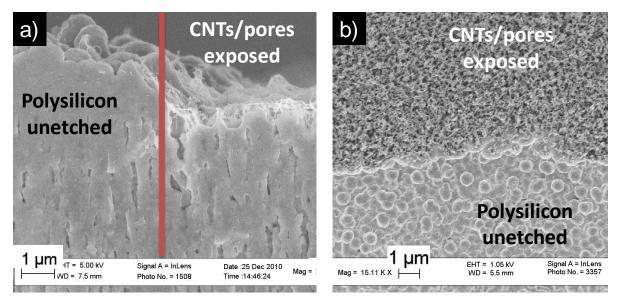

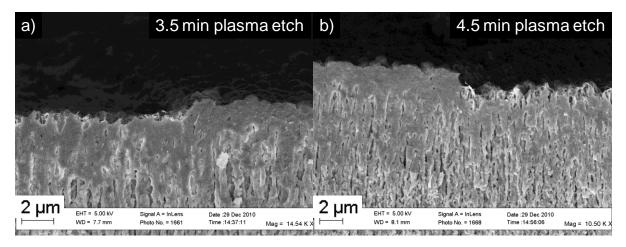

| Figure 4.9. Polysilicon removal after (a) 3.5 min and (b) 4.5 min plasma etching                                                                                                                                                                              |

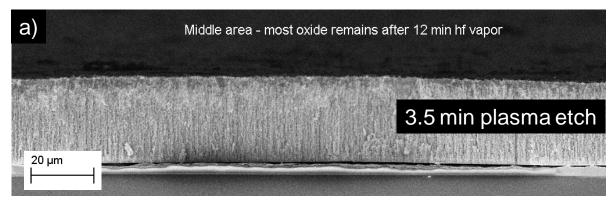

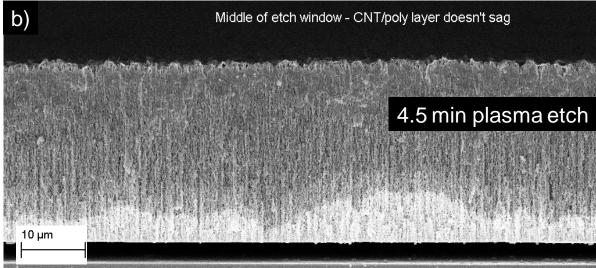

| Figure 4.10. HF vapor penetration after 12 minutes on membranes with windows opened by (a) 3.5 min and (b) 4.5 min plasma etches                                                                                                                              |

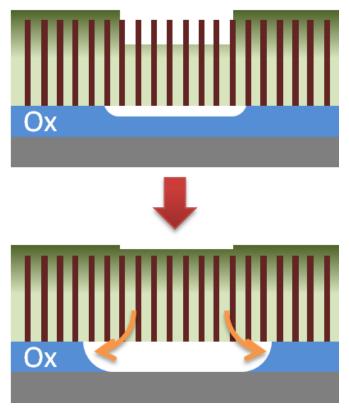

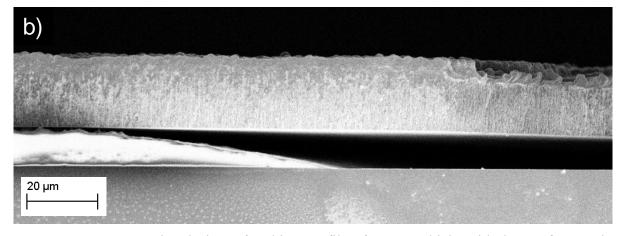

| Figure 4.11. Schematic of HF vapor etching of oxide beyond defined cavity width                                                                                                                                                                               |

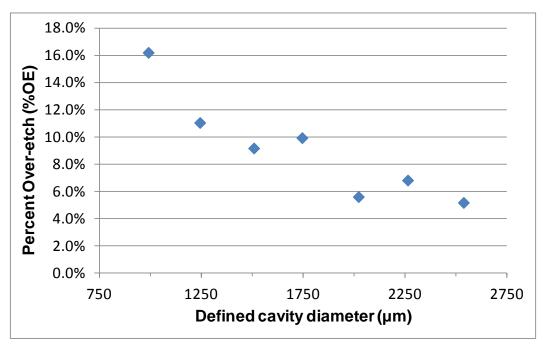

| Figure 4.12. Lateral HF vapor penetration through composite membrane which produces oxide over-etching.                                                                                                                                                       |

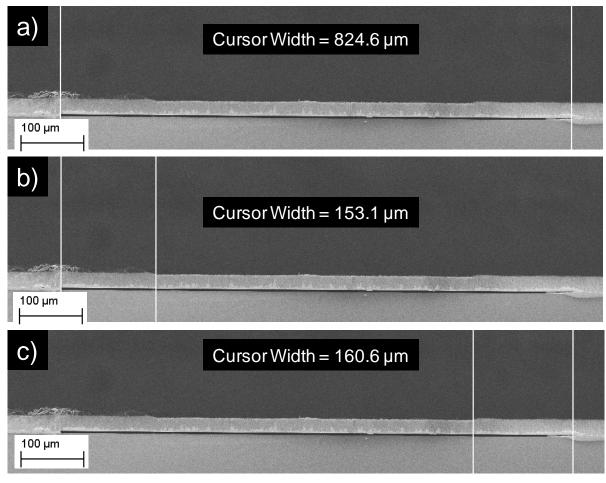

| Figure 4.13. HF vapor undercut for 30 $\mu$ m sample exposed to 4 min HF vapor: (a) total cavity width of 825 $\mu$ m; (b) left side undercut of 153 $\mu$ m; (c) right side undercut of 161 $\mu$ m                                                          |

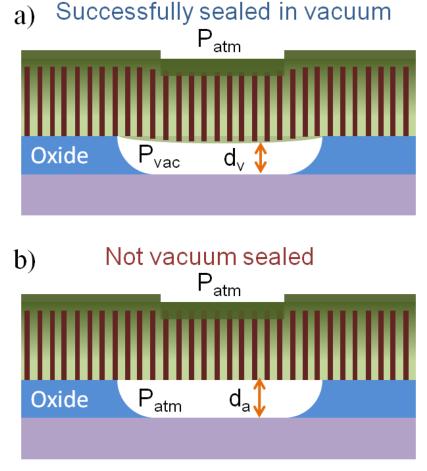

| Figure 4.14. Illustration of plate separation for (a) sealed cavity and (b) unsealed cavity 76                                                                                                                                                                |

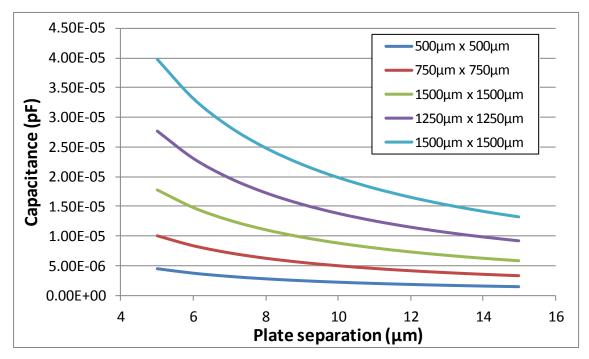

| Figure 4.15. Theoretical capacitance for different cavity sizes as a function of plate separation or oxide thickness                                                                                                                                          |

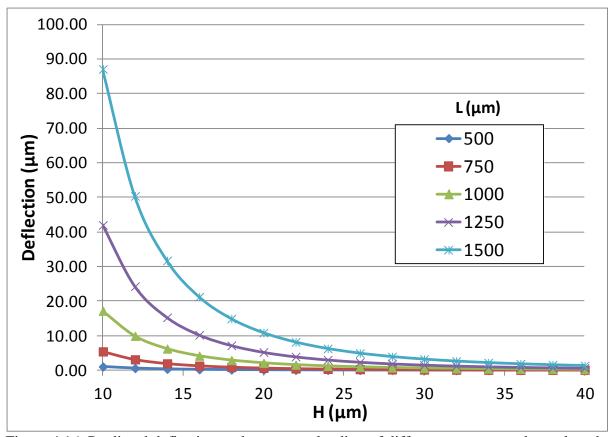

| Figure 4.16. Predicted deflection under vacuum loading of different square membrane lengths (different colors) with respect to CNT/polysilicon composite film thickness                                                                                       |

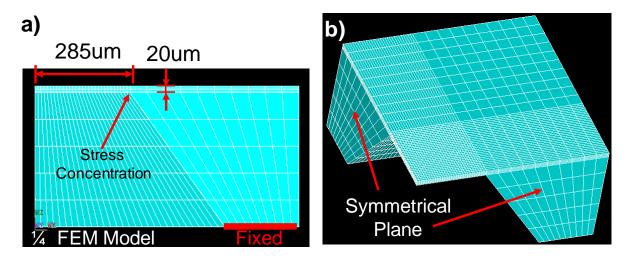

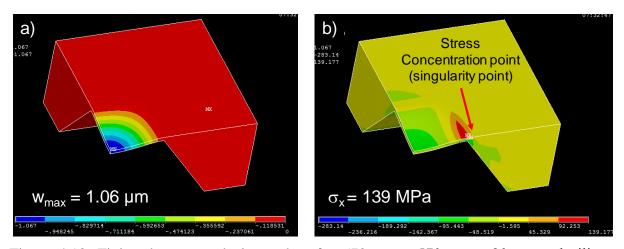

| Figure 4.17. Finite element $\frac{1}{4}$ model of a suspended polysilicon membrane: (a) 285 $\mu$ m from edge to center and 20 $\mu$ m thickness; (b) symmetrical planes surrounding film                                                                    |

| Figure 4.18. Finite element analysis results of a 570 $\mu$ m x 570 $\mu$ m x 20 $\mu$ m polysilicon membrane: (a) maximum deflection of 1.06 $\mu$ m, and (b) maximum surface stress of 139 MPa. 81                                                          |

| Figure 4.19. FEA result of deflection under self-weight for a circular membrane 1000 $\mu m$ in diameter and 20 $\mu m$ in thickness                                                                                                                          |

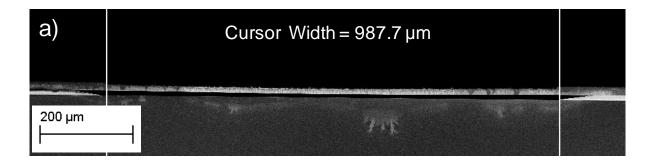

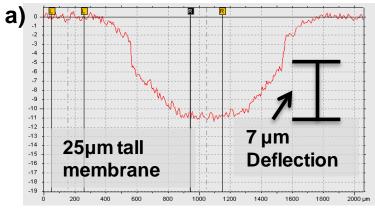

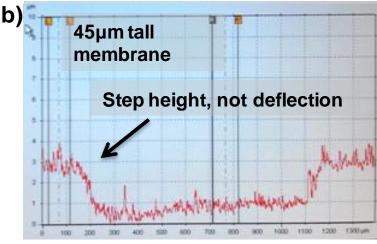

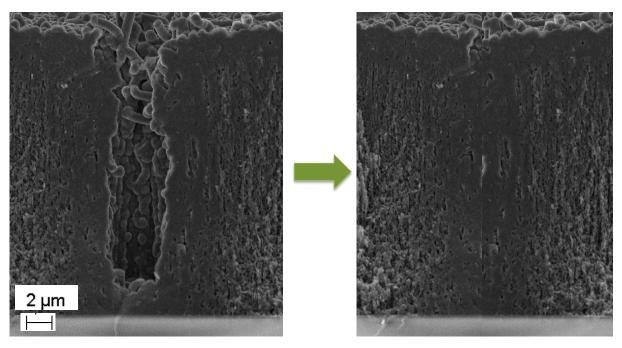

| Figure 4.20. Cross-sectional view of etching profile of 7.8 µm thick oxide layer after 8 min HF vapor for a 20 µm tall encapsulation membrane: (a) suspended membrane with minimal lateral undercut; (b) close-up of oxide profile after etching by HF vapor. |

| Figure 4.21. Comparison of oxide over-etch for 20 $\mu m$ and 30 $\mu m$ thick encapsulation membranes as a function of HF vapor exposure time                                                                                                                |

| Figure 4.22. Oxide over-etch for 25 µm thick membranes as a function of defined cavity diameter for circular etch windows                                                                                                                                     |

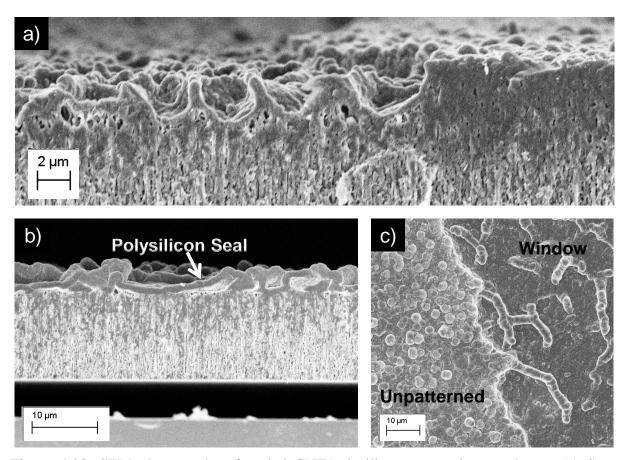

| Figure 4.23. SEM photographs of sealed CNT/polysilicon composite membrane. (a) Step height at edge of patterned window; (b) membrane suspended over cavity; (c) top view showing sealing over patterned and unpatterned areas on membrane                     |

| Figure 4.24. Surface profile measurements of film deflection after encapsulation over 1000 $\mu m$ wide cavities for (a) 25 $\mu m$ tall membrane, and (b) 45 $\mu m$ tall membrane |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.1. Schematic of reduced over-etch by patterning ribs into composite membrane 93                                                                                            |

| Figure 5.2. Hypothetical gap filling between CNT forests by polysilicon                                                                                                             |

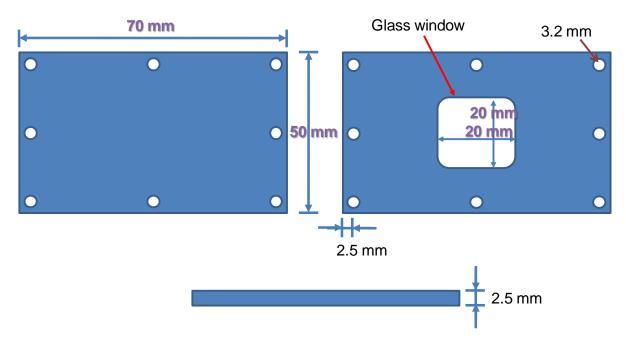

| Figure 5.3. Sample design for a small vacuum test chamber used in conjunction with a laser interferometer or laser displacement meter                                               |

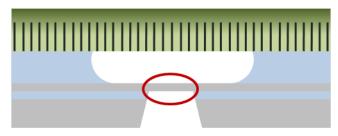

| Figure 5.4. Backside membrane of silicon or silicon nitride used to characterize internal cavity pressure based on measured deflection                                              |

| Figure 5.5. General process for encapsulating a simple MEMS device and opening electrical contacts without breaking vacuum                                                          |

## List of Tables

| Table 2.1. Summary of packaging parameters, challenges, and solutions for MEMS                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1. Summary of four device designs and relevant dimensions                                                                                   |

| Table 3.2. Maximum deflection for differing polysilicon films spanning large area of 2.65 mm x 1.89 mm                                              |

| Table 3.3. Maximum deflection for each device with 15 μm thick polysilicon membrane 40                                                              |

| Table 3.4. Results of using 0.1 μm polysilicon as permeable layer                                                                                   |

| Table 3.5. Rapid thermal anneal process for TEOS films                                                                                              |

| Table 3.6. Summary of results for TEOS deposition with RTA                                                                                          |

| Table 4.1. CNT growth process                                                                                                                       |

| Table 4.2. Summary of oxide over-etch compared to HF vapor exposure time for 30 μm thick membranes                                                  |

| Table 4.3. Comparison of maximum deflection and surface stress values obtained by hand or by FEA for a 570 μm x 570 μm x 20 μm polysilicon membrane |

| Table 4.4. Upper bounds for square and circular cavity sizes as a function of CNT height for 7.5 μm maximum deflection                              |

| Table 4.5. Summary of oxide over-etch compared to HF vapor exposure time for 20 µm thick membranes                                                  |

| Table 5.1. Comparison of thin film encapsulation approaches                                                                                         |

### Acknowledgements

The past six years of my life have been engaging, challenging, eye-opening, and ultimately rewarding. I have many people to thank and hope I do not forget anyone.

First and foremost I owe much to my advisor, Professor Liwei Lin, who welcomed me to Berkeley and has supported me in many ways throughout my graduate school career. His encouragement to explore new ideas and not be afraid to take risks has helped me to grow as a student, researcher, and scholar. I thank him deeply for his patience, guidance, and wisdom.

I also thank Professor Dorian Liepmann and Professor Tsu-Jae King Liu for serving on my dissertation committee. Their time, feedback, and support have meant a great deal to me. Professor Liepmann also served as the chair of my qualifying exam committee.

Countless other professors at Berkeley have also stimulated my interests in various exciting fields and helped guide my learning and research. Most notable are Professor Albert Pisano, Professor Samuel Mao, Professor Costas Grigoropoulos, Professor Junqiao Wu, Professor Vivek Subramanian, and Professor Luke Lee. In addition, I would like to acknowledge Professor John Lloyd and Professor Craig Somerton of Michigan State University for inspiring me and assisting my path to attend graduate school.

A great deal of the graduate school experience is dependent upon one's peers. Within the Lin Lab family, I give thanks to Brian Sosnowchik, Adrienne Higa, Ryan Sochol, Heather Chiamori, and Kedar Shah for the many hours of random pranks and goofiness amidst the long hours pondering research challenges on the whiteboard in 1113 Etcheverry. In addition, Yingqi Jiang and Qin Zhou have provided immeasurable assistance and discussion throughout the past few years. Their knowledge and kindness have been a blessing. Kevin Limkrailassiri contributed significantly to the work in Chapter 3 and deserves recognition. Hsieh Shen Hsieh also provided some assistance in the latter stages of my work. Everyone in the Lin Lab comes to depend on another person at one point or another, so to the rest of the past and present labmates I give heartfelt thanks for the memories and support. Outside of the Lin Lab, special thanks go to David Myers from the Pisano Lab for being another source of aid and guidance.

I would also like to give thanks to the Berkeley Sensor and Actuator Center (BSAC). I'm really grateful to have had the opportunity to work under this collaborative, interdisciplinary research group. My advisor and the other co-directors have given researchers a chance to share our ideas with fellow researchers as well as industry members. The efforts of John Huggins, Richard Lossing, Kim Ly, Alain Kesseru, and others make everything in BSAC possible, from the Tuesday lunches to the biannual research reviews. Moreover, thank you to the staff of the Marvell Nanofabrication Laboratory for making much of our research efforts possible.

My Berkeley experience would not have been complete without the friendship and support of my peers. From studying for classes in the early years to discussing movies and politics as a respite from research, my interactions with everyone have positively shaped me and my time here. In no particular order: Daniel Peters, Chris Zueger, Sara Beaini, Hector Mendoza, Kenneth Armijo, Kim Ly, Rich Winslow, John Edmiston, Lindsay Miller, Coleman Kronawitter,

Sonia Fereres, and Amanda Dodd. I'm probably forgetting many other people, as it's been quite the long journey, but certainly it's been a pleasure to spend time with everyone. The entity of Berkeley itself, including the university and the town, has exposed me to great people, cultures, ideas, and experiences.

Lastly, I thank my family for being so supportive and helping me through these past few years. Their love and encouragement have been my fuel to make it through the Ph.D. My brothers, Arash and Ali, have been there for me every step of the way. Arash has provided that listening ear in crucial moments with a dose of rationality when I needed it, and I owe him for being available at all times. Ali and my sister-in-law Sonya have sent me all kinds of goodies and homemade treats to remind me of home and keep my spirits up. The pictures and videos of my beautiful niece and nephew, Sophia and Ethan, always provided the perfect balance to work and put a smile on my face every day. Watching them grow up has been very enjoyable.

The older I grow the more I realize how special my parents are. My father has been there to help me as a loving, caring parent as well as a fellow mechanical engineer. His wisdom and insight into the Ph.D. process have been immeasurable, and the random jokes were always great as well. Words cannot express what my mother's love and support mean to me. The strength and confidence she has given me have been nothing short of vital. My mother is a truly remarkable person, and I owe her more than the world has to offer.

## **Chapter 1**

## Introduction

## 1.1 Microelectromechanical Systems

Microelectromechanical systems (MEMS) devices have been researched extensively and developed for a wide variety of applications since the late twentieth century. Essentially, MEMS are small integrated devices or systems which combine electrical and mechanical components. They range in size from the sub-micrometer level to the millimeter level and are fabricated utilizing the technologies developed for the integrated circuit (IC) industry. MEMS may add mechanical elements such as beams, gears, diaphragms, and springs to existing devices. Some examples of MEMS applications include accelerometers, inertial sensors, microengines, miniature robots, micromirrors, inkjet-printer cartridges, micro actuators, optical scanners, fluidic pumps, transistors, and chemical, pressure, or flow sensors. The function of these systems is to sense, control, and activate mechanical processes on the micro scale which integrate and combine to perform macro scale tasks.

MEMS offer a wide variety of advantages related to the scaling down of devices or systems. For example, by scaling MEMS materials to densities that approach the defect density of the material, devices may be produced with a very low total number of defects. As a result some MEMS devices, such as cantilevers whose design is relatively simple, may have better reliability than their macroscopic versions [1]. At the same time assumptions of homogeneity for bulk materials may become unreliable when modeling devices on similar scales as that of individual grains or other microscopic fluctuations in material properties. Nevertheless, the flexibility of microfabrication permits the properties of thin film materials to be controlled with high precision [2], [3].

Other scaling advantages of MEMS are evident in fluidic systems, where flow through microchannels is almost entirely dominated by laminar flow conditions rather than turbulent and chaotic flows prevalent in most macroscopic systems. Furthermore, in chemical or biological systems, it's quite advantageous to reduce the required sample size for a smaller device while keeping the detectable concentration fixed. It's also noted that many systems interfacing with biology are multidisciplinary in nature, requiring fluidic, electronic, and/or mechanical components. In addition, rapid removal of heat from a microscale object may be realized since heat can typically conduct in all directions. At the same time it is possible to fabricate structures which only allow heat transfer along certain directions for good thermal isolation.

The overall importance of MEMS lies in their ability to interface the digital electronic world with the analog physical world [4]. Due to a wide variety of nonelectrical signals that exist in the physical world, different transduction mechanisms are required to transducer physical signals into electrical signals (via sensors). These signals are then processed by IC-enabled electronic systems and from electric signals into physical signals (via actuators) [5]. Transduction mechanisms may be linked in series, such as from thermal to mechanical to optical to electrical. In other cases the sensing and actuating mechanisms may be combined with electronics to form complete microsystems. Overall, the most successful MEMS products utilize advantageous scaling properties, batch fabrication, and circuit integration.

### 1.2 MEMS Fabrication

In the early 1980s the term micromachining became a popular designation of fabricating micromechanical parts, such as pressure-sensor diaphragms or accelerometer suspension beams, for Si microsensors [6]. These micromechanical parts were fabricated by selectively etching areas of the Si substrate to form desired geometries. This etching was accomplished using both isotropic and anisotropic techniques, where the former etches material at the same rate in different directions through a given material and the latter does not. These etching processes formed the basis for bulk micromachining (BMM) processing [7]. BMM has remained a useful technique for fabricating micromechanical structures, but the need for flexibility in device design and improvements in performance has driven the development of new concepts and methods of micromachining.

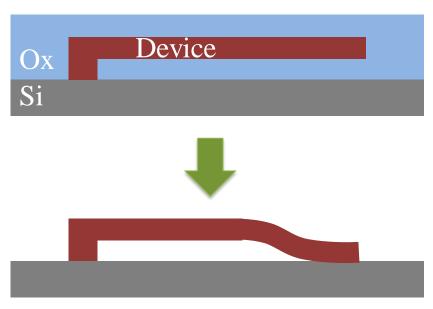

In 1965 researchers developed a technique of creating microstructures using a sacrificial layer technique [8]. In this method a layer of material is deposited between structural layers for mechanical separation and isolation. When this layer is removed during a release etch, the structural layers of the device are given freedom of movement relative to the substrate. The application of sacrificial layer techniques to micromachining inspired the growth of surface micromachining (SMM), in which the Si substrate serves as a mechanical support upon which various micromechanical elements are deposited, patterned, and etched in sequence. Both BMM and SMM techniques are illustrated below in Figure 1.1 and Figure 1.2, respectively.

Figure 1.1. Bulk micromachining using anisotropic etching.

Figure 1.2. Surface micromachining with use of a sacrificial layer.

It is noted that in both types of micromachining the process of photolithography is critical for patterning each layer. Photolithography uses a photosensitive polymer called a photoresist to coat the top surface of the substrate. It is then exposed to ultraviolet (UV) light in specific areas with use of a photomask which contains transparent and opaque regions matching the desired pattern to be created on the film. The regions of photoresist exposed to UV light are chemically altered, and the substrate is placed into a developer solution. Either the exposed regions are removed (positive resist) or the unexposed regions are removed (negative resist). The patterned photoresist may then be used as a mask for subsequent deposition or etch processes, and when the photoresist is removed the micromachined structures are left behind.

MEMS fabrication processes have expanded largely since the 1980s, during which the idea arose that the miniaturization challenge was not difficult [9]. In 1984 the first polysilicon surface micromachining process was developed and used to produce MEMS with integrated circuits [10]. Just a few years later researchers created the first electrostatically controlled micromotors using rotating bearing surfaces [11], [12]. Both of these technologies have served as a basis for many MEMS products. In addition, the development of microhinges in

1991 extended surface micromachining of polysilicon such that large structure could be assembled out of plane relative to the substrate [13]. This third dimensional aspect led to an incredible increase in the number of devices, technologies, and applications in the field of MEMS.

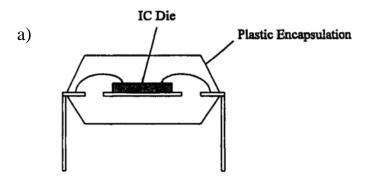

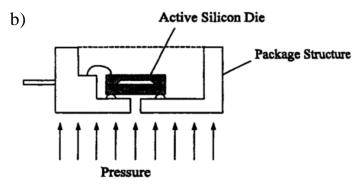

### 1.3 Packaging

Packaging is highly critical for the practical realization of MEMS devices, often being the most costly step in the manufacturing process [14]. Packaging is also important for yield and reliability [15]. Both the encapsulation of the moving, working parts of the device and the electrical interconnection must be integrated into the fabrication method for the MEMS devices. The MEMS device must essentially be sealed within a protective cap. In addition, there may be specific performance-related packaging requirements. MEMS devices such as pressure sensors or chemical/fluidic sensors need to be exposed to the environment to function. On the other hand, accelerometers, gyroscopes, and oscillators may need to be hermetically sealed, sometimes with an anti-stiction agent and/or buffer gas [16]. Overall, the delicate, specific, and varied nature of MEMS devices can complicate the integration of packaging steps and drive up manufacturing costs. Due to the widely varying conditions and specifications for MEMS packaging, no single universal packaging method exists. A sample of a fully fabricated MEMS package is seen in Figure 1.3.

Figure 1.3. Sample MEMS package with multiple interfaces. [17]

### 1.4 Dissertation Overview

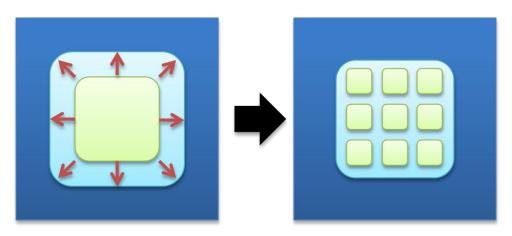

The motivation for this work lies in the pursuit of a broadly applicable MEMS packaging scheme for large area devices using a streamlined fabrication process. First the necessary background, criteria, and design considerations for MEMS packaging are discussed in Chapter 2. Two approaches to wafer level packaging, interfacial bonding (bulk micromachining) and thin film encapsulation (surface micromachining) are evaluated in the context of simplified fabrication and cost effectiveness. Chapters 3 and 4 test and present the potential of two different thin film encapsulation technologies, seen below in Figure 1.4

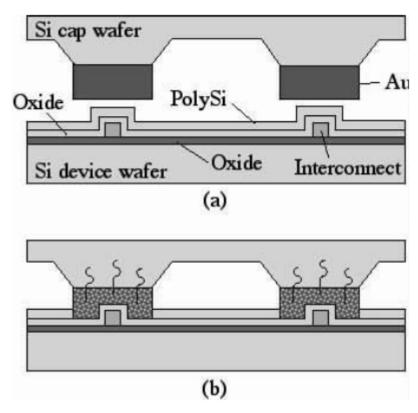

Figure 1.4. Schematic diagrams for thin film encapsulation using: (a) permeable polysilicon, and (b) composites of carbon nanotubes and polysilicon.

In Chapter 3 a thin film encapsulation method using permeable polysilicon for MEMS devices is presented, as seen in Figure 1.4(a). The necessary process parameters to render the thin polysilicon film permeable are developed. Furthermore, the encapsulation membrane is modeled to determine the necessary thickness of the sealing layer to sustain the package against atmospheric pressure loading. This requires supplemental material deposited on top of the permeable membrane. Therefore, a process of incremental thick oxide deposition and thermal annealing is optimized to hasten both the seal of the membrane and necessary filling of sacrificial oxide beneath the thin film package.

This process evolves in Chapter 4 into using polysilicon as a filler material in a composite membrane formed by carbon nanotubes (CNTs), shown in Figure 1.4(b). The CNTs serve as a skeletal framework for the membrane, which contains a natural permeability due to its porosity. This structure is used to expand beyond thickness limitations of typical thin film approaches while offering the advantages in packaging via surface micromachining. The CNT/polysilicon composite membrane is modeled for deflection under load to assist with designing thickness for any given area. In addition, the permeability and etching behavior of the sacrificial underlayer are characterized.

Chapter 5 summarizes the work in this dissertation and suggests future directions to further assess the viability of the CNT/polysilicon composite membrane and implement it into practical applications.

## Chapter 2

## MEMS Packaging Overview

### 2.1 Background

### 2.1.1 Packaging Considerations

Broadly speaking the main functions of MEMS packaging are as follows:

- 1. *Mechanical sustentation* the packaging material should sustain and protect the internal MEMS devices from the working environment. This may include protection against shock due to impact. Material selection plays a very important role, and in some cases glass or ceramic packages are attractive for their insulating and hermetic properties [18]. Moreover, the coefficient of thermal expansion (CTE) plays a significant factor in selecting packaging materials to minimize mechanical thermal stress at the interface between the MEMS die and the package substrate.

- 2. Protection from environment embedded MEMS devices on a die should be electrically isolated or passivated from electrolytes and moisture. This is extremely important because moisture, which may come from humidity in the environment, can cause corrosion of the device and hamper performance. Metal interconnects also are susceptible to becoming disconnected due to environmental factors.

- 3. *Electrical connection* –MEMS devices require electrical connections to the outside world, and this is a significant consideration for designing the packaging process steps. One benefit is that the signal path within the MEMS device is typically short and electrical noise may be unlikely or less impactful.

- 4. Thermal budgets One of the greatest limitations in packaging is the temperature of the process steps. In addition to the above mentioned CTE and its effect on inducing stress at the die/package interface, many IC devices have a thermal budget based on the allowed dopant diffusion. Repeated high temperature steps may destroy the diffusion profile for CMOS devices, especially, aluminum can begin to spike into devices at temperatures as low as 400°C [19].

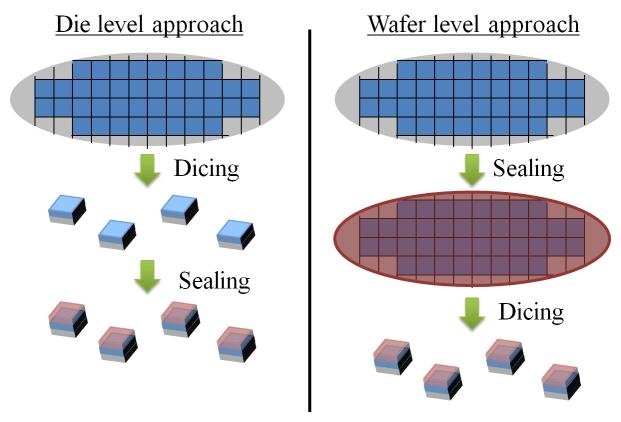

The two general approaches to packaging MEMS are at the die level and the wafer level. In the die level approach chips are fully fabricated, diced, then sealed or packaged individually. On the other hand, wafer level packaging consolidates the sealing and testing

processes for all chips on the wafer prior to dicing. Figure 2.1 illustrates this below. Prior to comparing die and wafer level sealing directly, the key challenges of MEMS packaging will be discussed in the next section.

Figure 2.1. Comparison of die level and wafer level packaging.

### 2.1.2 Challenges of Packaging MEMS

As mentioned above, a variety of issues arise when designing a packaging scheme for MEMS devices. One of the key distinctions between packaging for ICs and MEMS is that ICs have more well-defined requirements: physical support for the chip, an electrical interface, and heat dissipation [20]. On the other hand, MEMS devices interact with a range of environments, such as underneath automobile hoods or in strong acids or organic solutions. This distinction is shown below in Figure 2.2. The overall challenge in MEMS packaging is ensuring that the chip, package, and environment all function together.

Figure 2.2. Schematics of (a) an IC package and (b) a MEMS pressure sensor package. [21]

One of the key steps in device fabrication is the release of the MEMS structure. For example, a polysilicon feature may be fabricated on a silicon wafer while protected from sacrificial oxide. The oxide serves to support the device features and prevent them from being damaged in the fabrication process. Eventually the oxide must be etched away to release the MEMS structure, such as with an HF etch which exhibits selectivity for SiO<sub>2</sub> and Si [22–24]. A serious concern is when to perform this step. It is more simple and economical to HF etch oxide as a batch process in wafer form, but this may lead to contamination risks and damage during subsequent dicing. On the other hand, releasing MEMS after dicing is much more costly and difficult in the handling of the individual dies.

In either case one of the major risks with device release is stiction, seen below in Figure 2.3. This occurs from the capillary action of the evaporating rinse solution in the small crevices between components like cantilevers and the substrate [25–27]. Stiction can render the MEMS device useless, so preventative measures are sometimes taken. This may include freeze or supercritical CO<sub>2</sub> drying, which removes the liquid surface tension from the device and substrate surfaces to minimize adhesive forces [28]. However, this may not prevent stiction throughout the lifetime of the device.

Figure 2.3. Stiction of MEMS structures to silicon substrate after release.

One longer-term solution for stiction is to include the use of non-stick coatings on the device surfaces, typically organically based [29], [30]. Another strategy is to minimize the contact area between the device and substrate. This may be accomplished by either roughening the device surfaces or by introducing dimples onto regions of the device where stiction may be a problem [31].

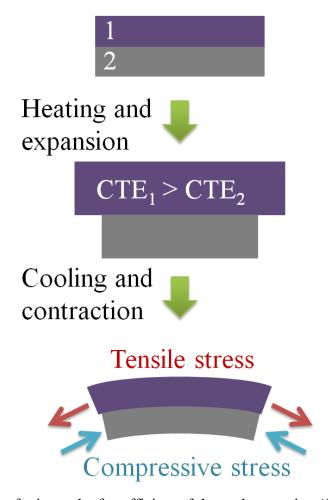

Another fabrication related issue is residual stress within the micromachined structures, especially thin film polysilicon [32], [33]. Excessive tensile stress can lead to film cracking, while compressive stress can cause films to buckle. High temperature annealing at around 1000°C will alleviate the stress in polysilicon, and if the polysilicon is deposited amorphously then annealed it will form a polycrystalline structure [34]. Another source of stress may come from the die attach material between the MEMS die and packaging substrate [35]. This depends on the aforementioned CTE mismatch between the package and the chip. Figure 2.4 below illustrates how differing CTE values for two materials may cause tensile or compressive stress in each respective film.

Figure 2.4. Effect of mismatch of coefficient of thermal expansion (CTE) on film stress.

When selecting the materials for packaging it is critical to consider the CTE mismatch. Residual stress in the package may cause misalignment, device deformation, changes in the resonant frequency of RF MEMS, and even device breakage. One type of packaging, using hard solders like AuSn or AuSi, can cause excessive stress in the film [36], [37]. Later discussion will address soldering issues in more detail. Furthermore, over time creep may settle in and change the stress state of the chip, which is just as problematic as having high stress [38], [39].

If adhesives such as epoxies or cyanate esters are used, the die attach compounds may outgas as they cure [35]. The organic vapors and water deposit on the MEMS devices, in crevices, and on bond pads. This can lead to stiction and/or cause corrosion. Recommended solutions include the use of very low outgassing die attach materials and the removal of outgassing vapors during the curing stage. One method is to use "particle getters", which chemically attract active gases or particles in a vacuum environment with the role of

maintaining and even improving vacuum [40], [41]. This may prolong the operational lifetime of sealed MEMS packages.

As mentioned above another consideration is dicing the wafer into individual chips. This process usually involves a diamond saw and requires coolant to flow over the surface of the wafer. The coolant may combine with silicon and diamond particles to contaminate the devices [42], [43]. One way around this is to cleave the wafers with a laser, but this process may result in thermal damage to the chips [44].

One difference between the assembly of MEMS and IC dies is that MEMS dice typically require special handling. This is due to the delicate surface features of the MEMS structures, and unlike IC dies they may not be moved using vacuum pick-up heads. Instead, MEMS dice must be picked up and handled by the edges by fixtures such as fingers or clamps. This is more difficult than handling dies by an entire surface due to the reduced area and increased dexterity requirements of pick and place equipment [45].

Wafer level encapsulation, on the other hand, eliminates the need for special die handling fixtures. Since a capping wafer is bonded to the top of a device wafer and when diced, each MEMS chip has a protective lid attached to it already. In addition, these wafers may be bonded in a vacuum to produce a permanent vacuum or low pressure environment inside each device chip. Various types of wafer level packaging are discussed in the following section. Finally, Table 2.1 below summarizes MEMS packaging issues and recommended solutions in this section.

Table 2.1. Summary of packaging parameters, challenges, and solutions for MEMS.

| Packaging<br>Parameters | Challenge                                                   | Solutions                                                                                                 |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Release and stiction    | Stiction of devices                                         | Freeze drying, CO <sub>2</sub> drying, roughening of contact surfaces, non-stick coatings                 |

| Stress                  | Performance degradation, resonant frequency shifts, failure | Low modulus die attach, annealing, minimize CTE mismatch                                                  |

| Outgassing              | Stiction, corrosion                                         | Low outgassing epoxies, low modulus solders, removal of outgassing vapors                                 |

| Dicing                  | Contamination risks                                         | Release devices after dicing, flush chip<br>surface to remove contaminants, wafer<br>cleaving with lasers |

| Die handling            | Device failure, top die face sensitive to contact/exposure  | Edge-holding fixtures, wafer level encapsulation                                                          |

### 2.2 Wafer Level Packaging

### 2.2.1 Overview of Wafer Level Processes

In the context of the previously addressed issues for MEMS devices, wafer level encapsulation presents a variety of appealing characteristics for large volume MEMS fabrication. Most importantly, there are substantially potential lower costs and higher volume throughput in wafer level packaging relative to the component or die level approach [46]. In addition, wafer level packaging enables device testing during batch fabrication. This may save costs and time compared to packaging individual dies because in the latter approach the testing only occurs after all devices have been fully diced and sealed.

Sealing the MEMS within their cavities earlier in the fabrication process protects them mechanically. Moreover, this wafer level packaging limits contamination during fabrication steps such as dicing, since there is a seal ring surrounding each die that will enclose it from byproducts of that or any other process. Batch encapsulation may also eliminate the need for extra packaging equipment. For example, wafer level packaged pressure sensors could be calibrated via reference pressure chambers.

The ability to miniaturize low cost microsensor applications and integrate them with other systems is another driving force behind the industry shift towards wafer level packaging [47]. Yet, a definitive industry-wide standard remains elusive due to the wide variety of applications for MEMS devices, from implantable biological sensors to RF wireless communications. Before delving further it is necessary to examine different types of wafer level packaging, as follows in the next sections.

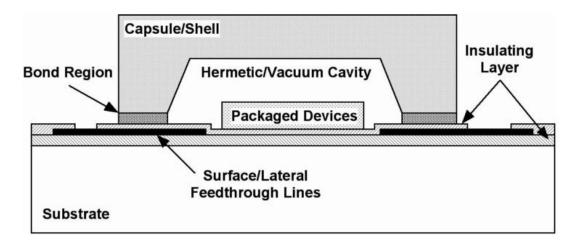

### 2.2.2 Interfacial Bonding

This method essentially involves using an external lid as a physical shell or capsule that may be placed over sensitive parts of the MEMS device, as seen below in Figure 2.5. There are three essential aspects of the entire package: the capsule, feedthroughs for signal transfer, and the bonding interface between the sealing layer and the device substrate. The capsule may be fabricated from a variety of materials, such as metals, glass/ceramics, silicon, or other semiconductor materials [48]. As discussed before, the capsule must be bonded to the device substrate prior to dicing in order to minimize handling costs and protect the MEMS components from subsequent process steps.

Figure 2.5. Cross section of an interfacial capsule or shell bonded to a substrate. [17]

During the bonding process high temperatures should be avoided to prevent damage to both the MEMS components and the interconnection. Moreover, the surface of the MEMS substrate should be planar enough so that the bond interface between the two substrates may be atomically close. As a result bonding silicon to silicon is not a good option because temperatures may exceed 1000°C in the standar silicon-to-silicon fusion bonding process [49].

Whatever the chosen capsule material may be, such as glass or solder, the primary goal is a permanent seal which will provide a long-term, stable hermetic or vacuum environment for the MEMS device. Most of these packages tend to be resistant to permeation by various gases or other environmental conditions like moisture [48]. Finally, it is sometimes easier to fabricate the signal feedthrough on the capsule substrate instead of the device substrate, since the surface of the MEMS chip may either be delicate, nonplanar, or otherwise constricted.

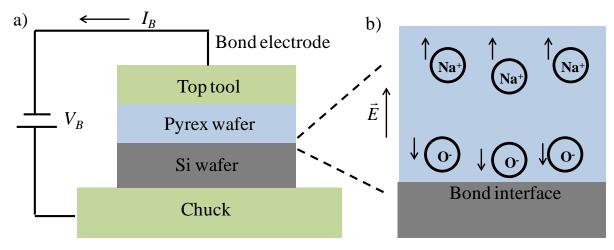

One of the more widely used bonding methods in MEMS is that between a glass capsule (usually Pyrex 7740) and a silicon substrate in a process called anodic, or electrostatic, bonding [50–52]. Figure 2.6 illustrates the anodic bonding setup and mechanism of ion drift that causes chemical bonds to form at the interface.

Figure 2.6. Anodic bonding schematic showing (a) procedure with top tool functioning as a cathode and the chuck as an anode, and (b) ion drift in the Pyrex glass as a result of the electric field, forming a depletion zone at the interface to which O ions drift.

In this process the two substrates come into intimate contact, are heated to roughly 400°C, and then experience a voltage from 800-1500V across the interface. This generates a large electrostatic attractive force to promote a chemical bond between the substrates. Specifically, Si and O<sub>2</sub> atoms form a Si-O bond that is stronger than both an Si-Si bond and glass [53]. After the bond forms the package cools to room temperature. One of the reasons Pyrex 7740 glass is a standard capsule material for anodic bonding to silicon is that the CTE mismatch is very low from room temperature to 400°C [54].

There are other advantages to using glass a capsule, the most apparent one being transparency. This allows such packages to be used for Micro-Opto-Electromechanical Systems (MOEMS) and biomedical applications in which a radio frequency signal must be transmitted to the embedded device [55–59]. Furthermore, Pyrex 7740 is biocompatible and resistant to corrosive environments such as salt water or humidity. Since glass wafer technology is well established, material costs can be kept low.

Other methods of interfacial bonding include silicon-gold eutectic bonding, glass frit bonding, fusion bonding, and evaporated glass bonding [60–64]. Wafer bonding with solder or eutectics is one of the more common approaches. A solder forms in the bond area between the package and device substrates. After the substrates are brought together, the temperature is raised to produce solder reflow which forms the bond. This heating may be localized with induction heating using magnetic coils, such that the MEMS device temperature may remain less than 125°C [65]. However, solder materials may contain impurities which cause them to outgas during the reflow process, creating problems for vacuum packaging [66], [67].

Eutectic soldering, on the other hand, employs the use of a metal such as gold to form a bond between the device and package substrates [68], [69]. The silicon-gold eutectic is attractive because it forms at a temperature of roughly 360°C. Outgassing is not a problem

because the mixture forms from simply raising the temperature and the starting materials are pure, unlike solder. The low temperature is sufficient for most MEMS applications. Figure 2.7 below shows the mechanism and experimental setup for eutectic bonding using gold to a silicon capsule.

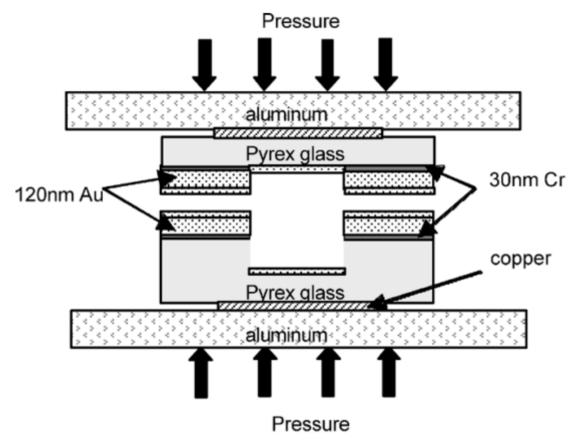

Figure 2.7. Schematic diagram of Au-Si eutectic bonding for packaging a silicon cap wafer to a MEMS device wafer, (a) before bonding and (b) after bonding. [62]

The eutectic may be used to bond two wafers or for hermetic and vacuum packaging. Usually the gold is deposited onto the sealing substrate, and the silicon is provided from the bulk of the device substrate or a thin film deposited on one or both of the wafers. Once the two materials are brought into contact and heated above the eutectic temperature, the liquid mixture forms by silicon diffusing into the gold. Once cooled a strong diffusional bond forms at the interface [70].

One of the issues with Si-Au eutectic bonding is the lack of uniformity and reproducibility. There are various reasons for this, including non-uniform eutectic flow, void formation, insufficient eutectic material between wafers that causes non-uniform bonding, oxidation of bond surfaces, and poor surface contact or adhesion [71]. The quality of the Au-Si bond may be improved by conducting the process in a vacuum or inert gas ambient to avoid oxidation at high temperature. In addition, the bonding surface should be clean and

smooth. During bonding a contact force should be applied to the wafers, and cooling should occur as quickly as possible. To ensure sufficient coverage of the Au-Si eutectic on the interface, the eutectic material should be several µm thick so that it covers nonplanar surfaces. Lastly, the wafers may be baked to minimize outgassing [72].

While Au-Si eutectic bonding has a process temperature less than 400°C when using a silicon cap, the temperature must be raised if another material such as glass frit is used [73], [74]. Temperatures of 700°C and above begin to exceed the allowable range for various MEMS devices as well as ICs. Furthermore, some MEMS devices incorporate polymers or biological coatings which cannot withstand temperatures much greater than 100°C [75].

As mentioned for soldering, localized heating is useful to avoid damaging the MEMS device with high bonding temperatures. Several techniques have been developed, such as microwave heating, laser heating, localized CVD deposition, resistive heating, ultrasonic bonding, and RF heating [76–83]. An example of localized heating using on-chip resistors is seen below in Figure 2.8.

Figure 2.8. Schematic of localized bonding using on-chip resistors. [17]

The resistive heater may be used with common materials such as aluminum or polysilicon. In addition, it may be patterned onto either the sealing substrate or the device substrate. Silicon has a good thermal conductivity of 149 W/m-K, enabling heat from the resistive heater to be confined and localized to the bonding area. Sensitive regions of the device substrate may be maintained at room temperature or slightly above by using a heat sink. For example, the temperature can vary from over 700°C to 50°C over a length of 100µm or less [17]. However, the entire package may be baked at an elevated temperature to allow for outgassing of any residual materials on either the package surface or the device substrate.

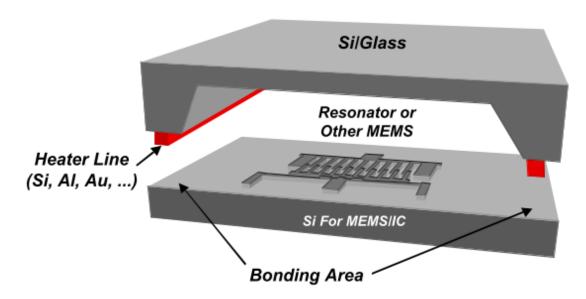

Additional protective layers such as Ti/Pt may be implemented on the inside of the glass cap to prevent future outgassing and also function as a getter, which absorbs residual outgassing within the package [84]. Figure 2.9 shows an example of a microresonator which has been encapsulated using localized bonding between aluminum and the glass cap.

Figure 2.9. SEM photograph of an encapsulated microresonator under a glass cap. [84]

Overall, localized heating for bonding is very attractive for highly sensitive MEMS devices. A variety of materials may be used in the bonding region. They will conform to the topology of the substrate which may often be nonplanar due to the implementation of electrical feedthroughs which carry signals between the sealed device and the outside environment.

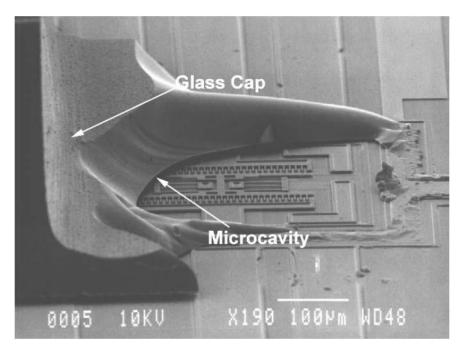

Lesser used interfacial techniques invoke metal-metal bonds. One such process uses Au-Au thermo-compression bonding to form microfluidic channels in a Pyrex substrate [85]. Thermo-compression is the application of heating and pressure to melt the interfacial metal and form the bond between the substrates. Aluminum plates provide both the pressure and necessary conduction of heat to the Pyrex substrates, as seen in Figure 2.10.

Figure 2.10. Schematic diagram of thermo-compressive Au-Au diffusion bonding. [85]

Similar bonding may be performed with Al-Al and Cu-Cu interfaces [86], [87]. This bonding scheme allows for hermetic sealing and electrical interconnection simultaneously. Atom beams may also be used in vacuum to generate reproducible Au-Au bonding at low temperatures as well [88]. In the case that hermetic sealing is not required, MEMS devices may be protected by bonding a lid wafer with adhesive polymer films [89–93].

#### 2.2.3 Thin Films