## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Algorithm-Hardware Optimization of Deep Neural Networks for Edge Applications

#### **Permalink**

https://escholarship.org/uc/item/7hx3z4n4

#### **Author**

Akhlaghi, Vahideh

## **Publication Date**

2020

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

## Algorithm-Hardware Optimization of Deep Neural Networks for Edge Applications

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Vahideh Akhlaghi

### Committee in charge:

Professor Rajesh K. Gupta, Chair Professor Hadi Esmaeilzadeh, Co-Chair Professor Gert Cauwenberghs Professor Sicun Gao Professor Ryan Kastner

2020

Copyright

Vahideh Akhlaghi, 2020

All rights reserved.

| The dissertation of Vahideh Akhlaghi is approved, and it is |

|-------------------------------------------------------------|

| acceptable in quality and form for publication on microfilm |

| and electronically:                                         |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

| Co-Chair                                                    |

|                                                             |

| Chair                                                       |

University of California San Diego

2020

## **DEDICATION**

To my dearest family and my loving husband

## **EPIGRAPH**

Be the peace you wish to see in the world!

—Martin Luther King, Jr.

## TABLE OF CONTENTS

| Signature Pa    | ige .                    | iii                                                                                                                                                              |

|-----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .    |                          | iv                                                                                                                                                               |

| Epigraph        |                          |                                                                                                                                                                  |

| Table of Con    | ntents                   |                                                                                                                                                                  |

| List of Figur   | es                       | ix                                                                                                                                                               |

| List of Table   | es                       | xii                                                                                                                                                              |

| Acknowledg      | ements                   |                                                                                                                                                                  |

| Vita            |                          |                                                                                                                                                                  |

| Abstract of the | he Diss                  | ertation                                                                                                                                                         |

| Chapter 1       | Intro<br>1.1<br>1.2      | duction1Background and Problem Definition2Related Works51.2.1 Algorithmic Optimization51.2.2 Hardware Optimization11Dissertation Contribution and Organization13 |

| Chapter 2       | 2.1<br>2.2<br>2.3<br>2.4 | Introduction                                                                                                                                                     |

|                 | 2.6                      | ReBF: Resistive Bloom Filter                                                                                                                                     |

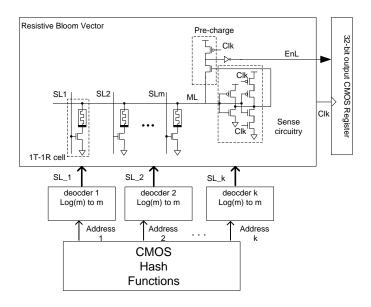

|           |      | 2.6.1 ReBF Architecture                                          |

|-----------|------|------------------------------------------------------------------|

|           |      | 2.6.2 Scalability of ReBF                                        |

|           | 2.7  | Experimental Results                                             |

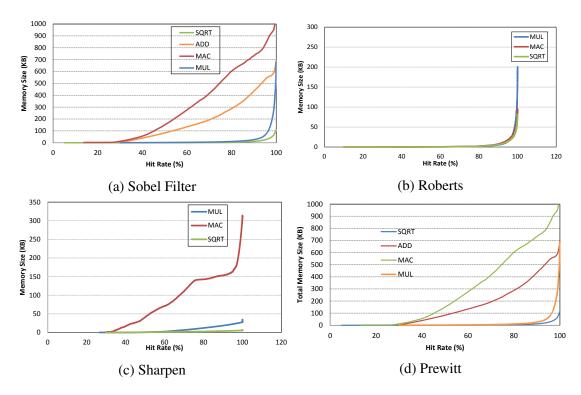

|           |      | 2.7.1 Evaluation of Function Approximation on Image Processing   |

|           |      | Applications                                                     |

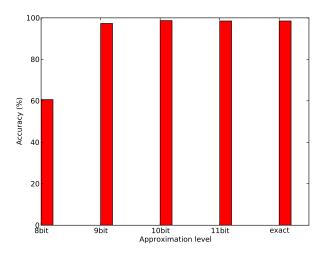

|           |      | 2.7.2 Evaluation of Function Approximation on CNNs 40            |

|           | 2.8  | Summary of the Chapter                                           |

| Chapter 3 | Dyn  | amic Network Pruning                                             |

|           | 3.1  | Introduction                                                     |

|           | 3.2  | Related Work                                                     |

|           | 3.3  | SnaPEA Hardware-Software Solution                                |

|           |      | 3.3.1 SnaPEA Software Workflow                                   |

|           |      | 3.3.2 SnaPEA Hardware Architecture                               |

|           | 3.4  | Computation Reduction in SnaPEA                                  |

|           | 3.5  | SnaPEA Software Optimization                                     |

|           | 3.3  | 3.5.1 Speculation Parameters                                     |

|           |      | 3.5.2 Problem Formulation                                        |

|           |      | 3.5.3 Finding the Speculation Parameters                         |

|           | 3.6  | C 1                                                              |

|           | 3.7  | e                                                                |

|           | 3.7  |                                                                  |

|           |      | 3.7.1 Methodology                                                |

|           | 2.0  | 3.7.2 Experimental Results                                       |

|           | 3.8  | Summary of the Chapter                                           |

| Chapter 4 | Plat | form-Aware Algorithm-Hardware Approximation                      |

|           | 4.1  | Introduction                                                     |

|           | 4.2  | Related Work                                                     |

|           | 4.3  | Overview of the Framework                                        |

|           |      | 4.3.1 Parameterized Error Injection                              |

|           |      | 4.3.2 Model and Hardware Related Constraints                     |

|           |      | 4.3.3 Problem Formulation                                        |

|           |      | 4.3.4 Learning Optimal Algorithm-Hardware Level Approximation    |

|           |      | and Architecture Design                                          |

|           | 4.4  | Optimal Algorithm-Hardware Approximation for FPGA-based CNN      |

|           |      | accelerators                                                     |

|           |      | 4.4.1 Injecting Quantization and DRAM Voltage Scaling Error into |

|           |      | CNNs                                                             |

|           |      | 4.4.2 Constraints on Model Accuracy and FPGA Resource Budget 90  |

|           |      | ·                                                                |

|           |      | 4.4.3 Problem Formulation                                        |

|           | 4 ~  | 4.4.4 Optimal Quantization and DRAM Voltage                      |

|           | 4.5  | Experimental Evaluation                                          |

|           |      | 4.5.1    | Optimal Hardware Approximation for the Weight Updates in | 99  |

|-----------|------|----------|----------------------------------------------------------|-----|

|           |      | 4.5.2    | Linear Regression and SVM                                | 105 |

|           |      | 4.5.2    | Optimal Algorithm-Hardware Approximation                 |     |

|           | 16   |          | Optimal FPGA-Aware Algorithm-Hardware Approximation      | 120 |

|           | 4.6  | Summ     | ary of the Chapter                                       | 125 |

| Chapter 5 | Para | ımeter A | approximation                                            | 127 |

|           | 5.1  | Introd   | uction                                                   | 128 |

|           | 5.2  | Relate   | d Works                                                  | 131 |

|           | 5.3  | Prelim   | inaries                                                  | 134 |

|           |      | 5.3.1    | Convolutional Neural Network (CNN)                       | 134 |

|           |      | 5.3.2    | Slices                                                   | 135 |

|           |      | 5.3.3    | Code Vectors                                             | 135 |

|           | 5.4  | Convo    | lutional Slice Generator                                 | 135 |

|           |      | 5.4.1    | The CSG Network                                          | 136 |

|           |      | 5.4.2    | Training the CSG-Augmented Network                       | 136 |

|           |      | 5.4.3    | Cardinality of the Code Vector Space                     | 137 |

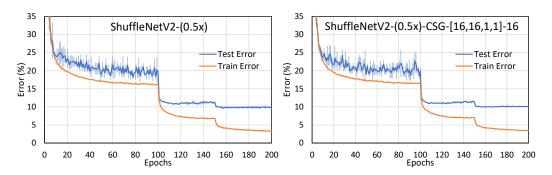

|           |      | 5.4.4    | Training Convergence                                     | 139 |

|           | 5.5  |          | zed Slice Generator (BSG)                                | 141 |

|           |      | 5.5.1    | Binarization                                             | 141 |

|           |      | 5.5.2    | Permutation                                              | 141 |

|           |      | 5.5.3    | Bit-Level Manipulation                                   | 142 |

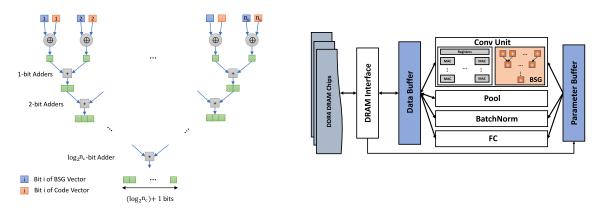

|           | 5.6  |          | erator Architecture for BSG-Augmented CNNs               | 143 |

|           |      | 5.6.1    | Hardware Implementation of BSG                           | 143 |

|           |      | 5.6.2    | BSG-based Architectural Modification of Accelerators     | 143 |

|           | 5.7  |          | iments                                                   | 146 |

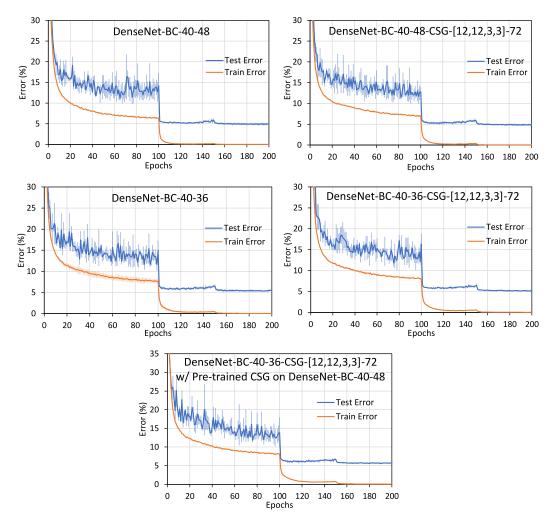

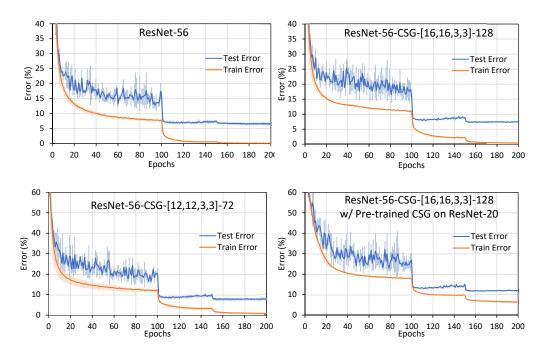

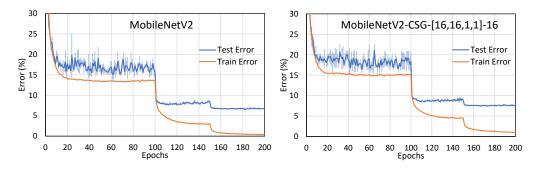

|           | ٥.,  | 5.7.1    | CSG on CIFAR-10 Dataset                                  | 148 |

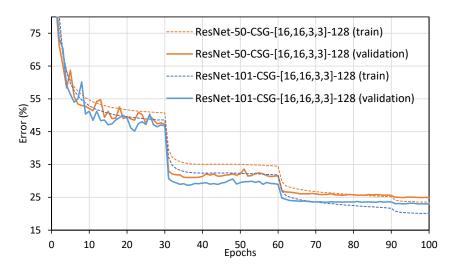

|           |      | 5.7.2    | CSG on ImageNet-1000 (ILSVRC2012) Dataset                | 150 |

|           |      | 5.7.3    | Training the CSG alongside the CNN                       | 151 |

|           |      | 5.7.4    | Using Pre-Trained CSG                                    | 152 |

|           |      | 5.7.5    | CSG for Semantic Segmentation Tasks                      | 152 |

|           |      | 5.7.6    | Comparison of CSG with Related Methods                   | 153 |

|           |      | 5.7.7    | BSG for Improved Inference on FPGA                       | 155 |

|           | 5.8  |          | ary of the Chapter                                       | 161 |

| ~         |      |          |                                                          |     |

| Chapter 6 | Con  | clusion  |                                                          | 163 |

## LIST OF FIGURES

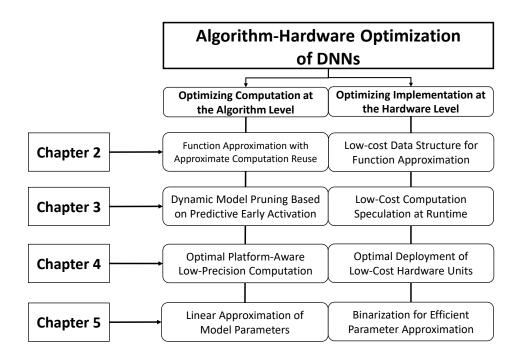

| Figure 1.1:  | The organization of this dissertation                                                 | 13 |

|--------------|---------------------------------------------------------------------------------------|----|

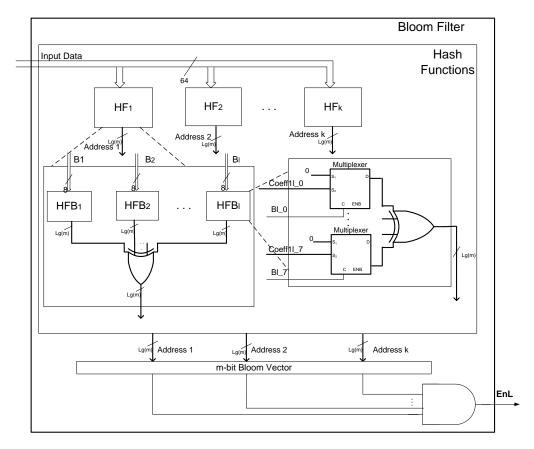

| Figure 2.1:  | The hardware architecture of Bloom filter                                             | 22 |

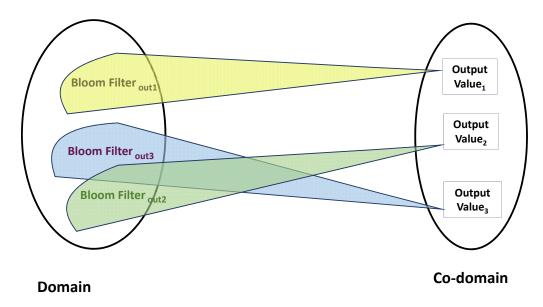

| Figure 2.2:  | Function approximation using Bloom filters                                            | 23 |

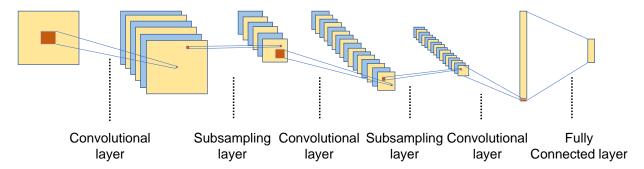

| Figure 2.3:  | An illustration of a convolutional neural network                                     | 29 |

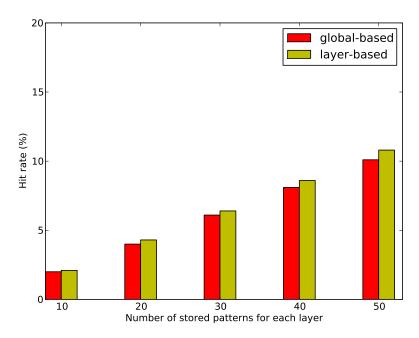

| Figure 2.4:  | The hit rate of exact pattern matching                                                | 30 |

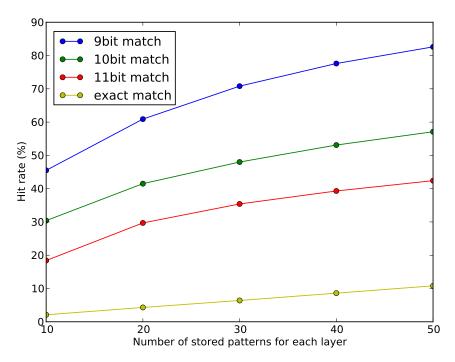

| Figure 2.5:  | The hit rate of approximate pattern matching                                          | 31 |

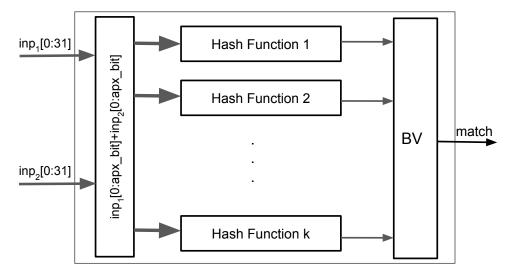

| Figure 2.6:  | The implementation of approximate pattern matching                                    | 32 |

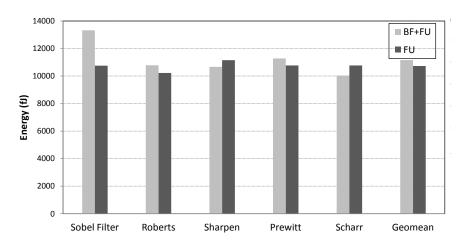

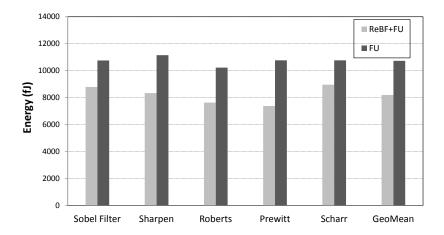

| Figure 2.7:  | Energy consumption comparison of the proposed architecture using CMOS                 |    |

|              | BFs and conventional FU                                                               | 34 |

| Figure 2.8:  | 1T-1R implementation of ReBF                                                          | 35 |

| Figure 2.9:  | Total memory size vs frequency of computational reuse (hit rate)                      | 36 |

| Figure 2.10: | Energy comparison of the proposed architecture using ReBFs and conven-                |    |

|              | tional FUs                                                                            | 39 |

| Figure 2.11: | Neural network accuracy loss due to approximate pattern matching                      | 41 |

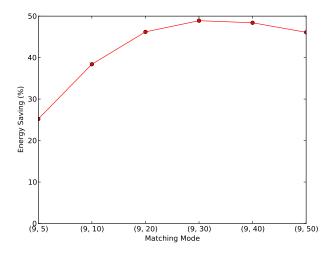

| Figure 2.12: | Energy Savings under different matching mode                                          | 42 |

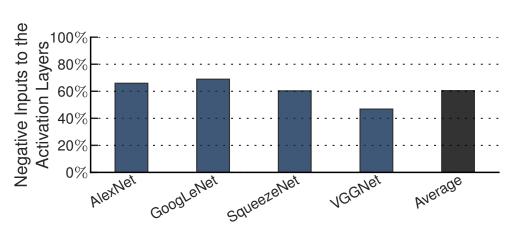

| Figure 3.1:  | Fraction of activation input values that are negative                                 | 47 |

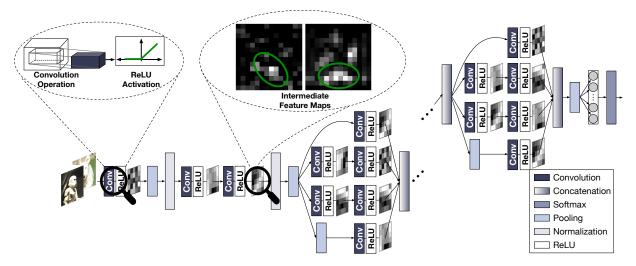

| Figure 3.2:  | GoogLeNet [SLJ <sup>+</sup> 15], in which the intermediate feature maps for two input |    |

|              | images are magnified. The ellipses on the intermediate feature maps highlight         |    |

|              | the varying spatial distribution of non-zero values for distinct input images.        | 48 |

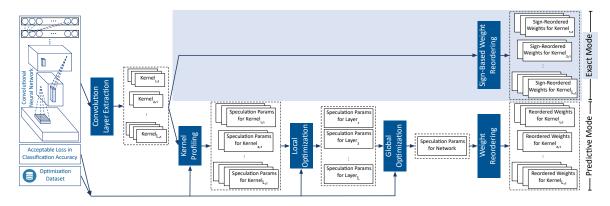

| Figure 3.3:  | Software workflow for SnaPEA                                                          | 52 |

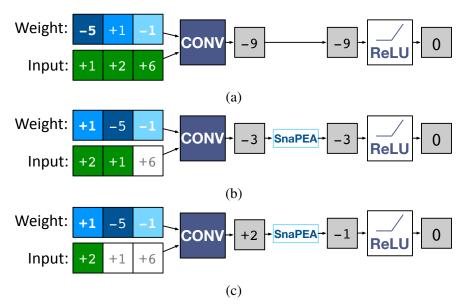

| Figure 3.4:  | A 1×3 convolution in (a) unaltered (b) exact, and (c) predictive modes. In            |    |

|              | the latter two, the weights and their corresponding inputs are reordered. The         |    |

|              | white boxes highlight the operations that are cut                                     | 55 |

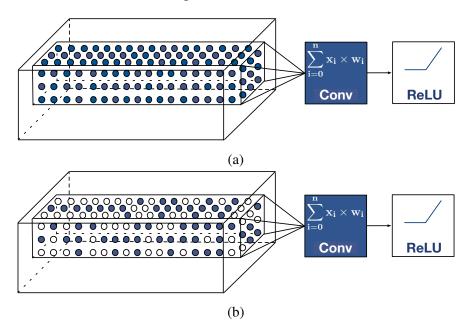

| Figure 3.5:  | (a) The unaltered 3D convolution where all the MAC operations (bubbles)               |    |

|              | are carried out. (b) The same convolution with SnaPEA, where a significant            |    |

|              | number of operations are eliminated, delineated by the white bubbles                  | 56 |

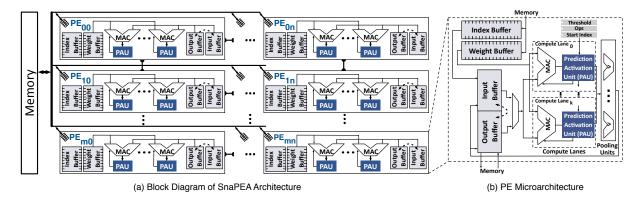

| Figure 3.6:  | (a) The overall structure of the SnaPEA architecture and its multilevel mem-          |    |

|              | ory hierarchy. (b) The micro-architecture of each PE. The weights are shared          |    |

|              | across the compute lanes                                                              | 64 |

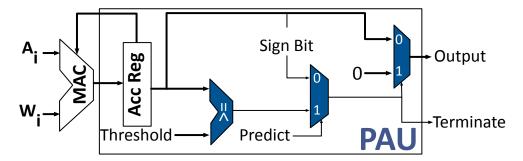

| Figure 3.7:  | Prediction Activation Unit (PAU). The Predict signal determines the PAU               |    |

|              | operation mode (exact or predictive). The Terminate signal, once asserted,            |    |

|              | terminates the computation early                                                      | 67 |

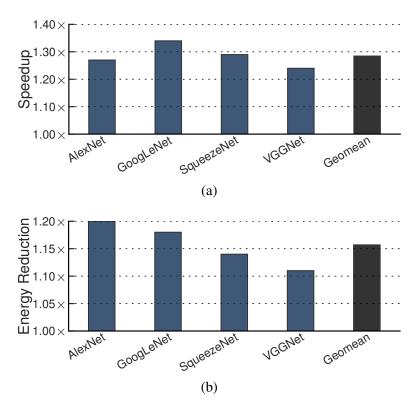

| Figure 3.8:  | Overall (a) speedup and (b) energy reduction with exact mode                          | 72 |

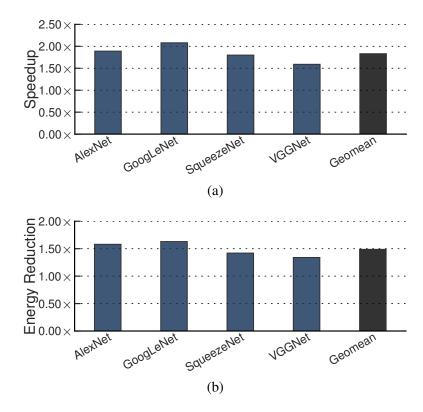

| Figure 3.9:  | Overall (a) speedup and (b) energy reduction with SnaPEA over EYERISS                 |    |

|              | [CES16] in the predictive mode. The acceptable classification accuracy drop           |    |

|              | is maintained within $\leq$ 3% range of its baseline value                            | 73 |

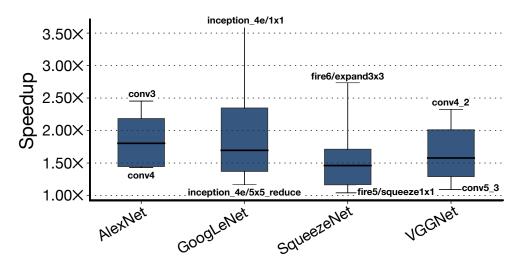

| Figure 3.10: | Speedup of convolutional layers in each network for the predictive mode               |    |

|              | when the degradation in classification accuracy is set to $\leq 3\%$                  | 74 |

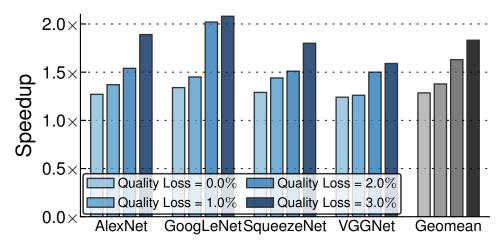

| Figure 3.11: | Speedup for different levels of loss in the CNN classification accuracy               | 75 |

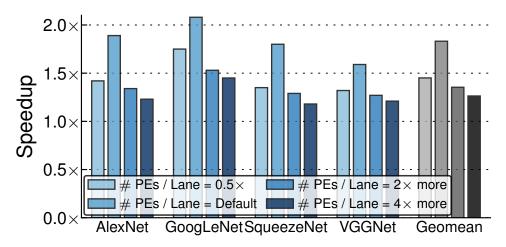

| Figure 3.12: | Sensitivity of speedup with SnaPEA over EYERISS to the number of compute lanes per each PEs. The number of compute lanes per each PEs is altered by different factors (acceptable classification accuracy drop $\leq 3\%$ )                                | 77         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

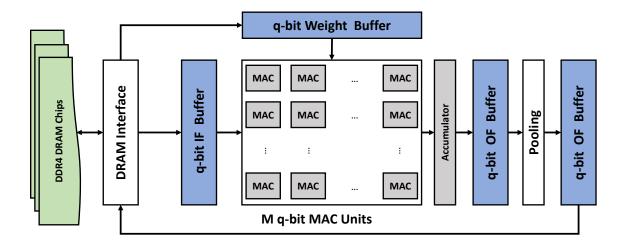

| Figure 4.1:  | Overview of FPGA-based accelerator architecture with uniform quantization and DRAM voltage for all layers.                                                                                                                                                 | 93         |

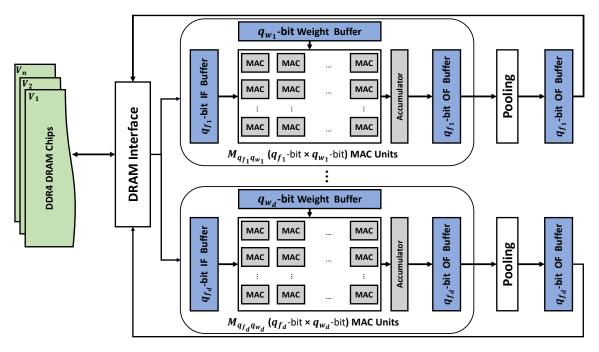

| Figure 4.2:  | CNN accelerator architecture to support non-uniform quantization and approximate main memory error                                                                                                                                                         | 94         |

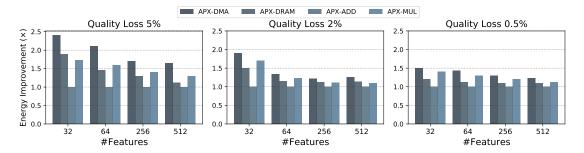

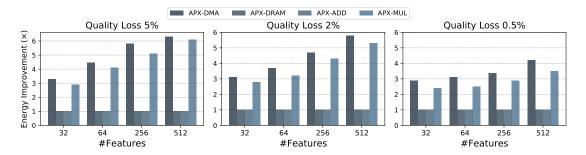

| Figure 4.3:  | Energy consumption improvement of different approximate systems compared to the baseline in executing Linear Regression training algorithm with different number of features under different quality constraints                                           | 101        |

| Figure 4.4:  | Energy consumption improvement of different approximate systems compared to the baseline in executing SVM training algorithm with different number of features under different quality constraints                                                         | 102        |

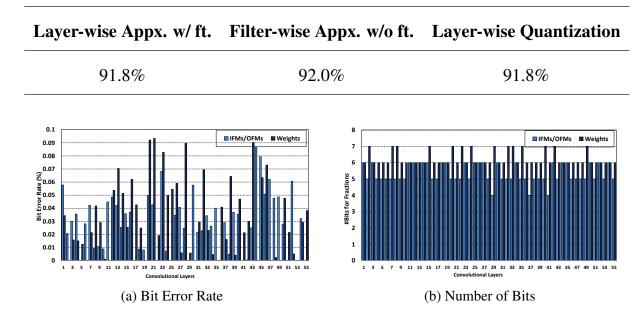

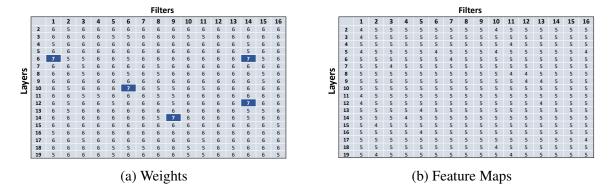

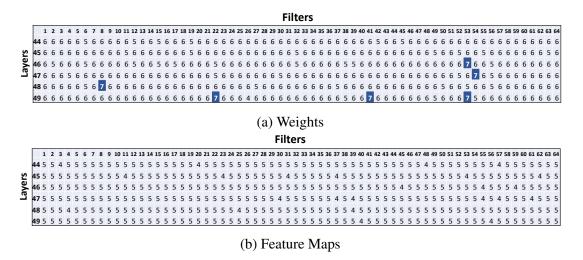

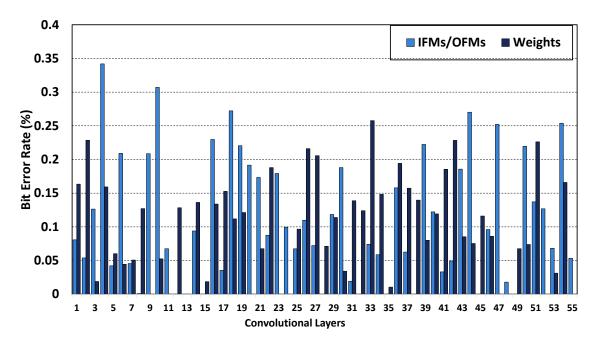

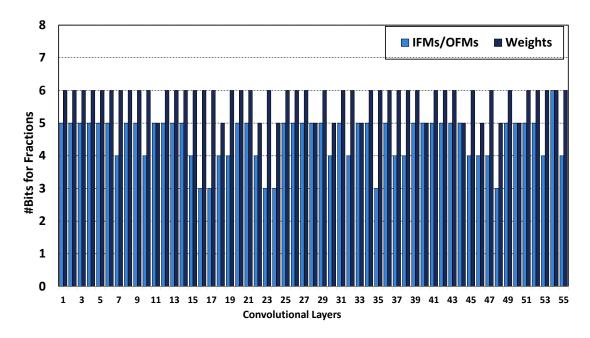

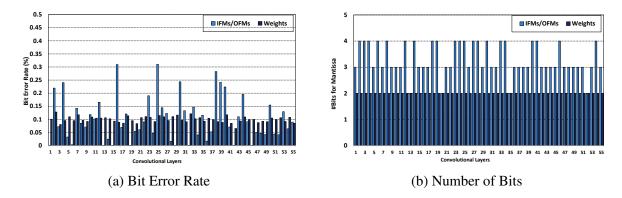

| Figure 4.5:  | The learned Bit error rate and the number of bits of feature maps and weights in ResNet-56 without fine-tuning the original network parameters                                                                                                             | 110        |

| Figure 4.6:  | The learned bit error rate and the number of bits of IFMs/OFMs and weights in ResNet-56 with fine-tuning the original network parameters                                                                                                                   | 111        |

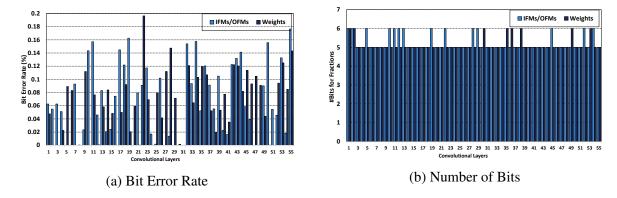

| Figure 4.7:  | The learned bit error rate and the number of bits of feature maps and weights in ResNet-110 without fine-tuning the original network parameters                                                                                                            | 112        |

| Figure 4.8:  | The learned number of bits for the fractional part of quantized feature maps and weights in different filters of layers 2-19 of ResNet-56 without fine-                                                                                                    |            |

| Figure 4.9:  | tuning the original network parameters                                                                                                                                                                                                                     | 113<br>114 |

| Figure 4.10: | The learned bit error rate of feature maps and weights in different layers of ResNet-56 without fine-tuning of the original model parameters with                                                                                                          |            |

| Figure 4.11: | filter-wise approximation setting                                                                                                                                                                                                                          | 115        |

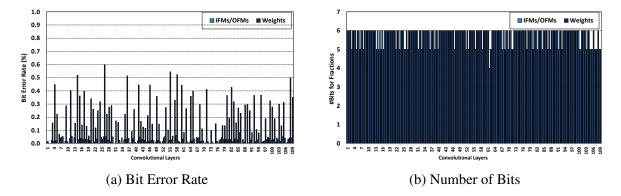

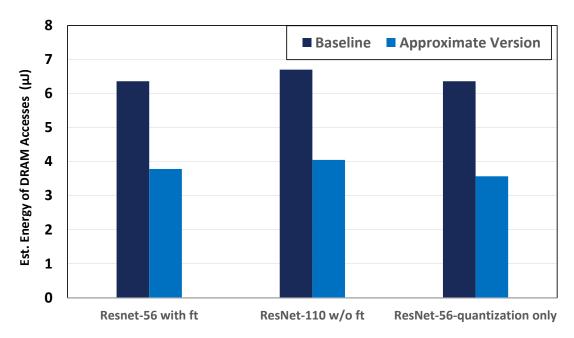

| Figure 4.12: | error is quantization with layer-wise approximation setting Estimated energy $(\mu J)$ of DRAM accesses for various models under various                                                                                                                   | 118        |

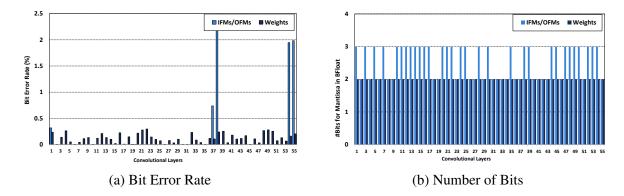

| Figure 4.13: | configurations. Nominal baseline voltage for DRAM is 1.5V Bit error rate and the number of bits for the mantissa of feature maps (IFMs/OFMs) and weights represented in BFloat format in ResNet-56 learned                                                 | 119        |

| Figure 4.14: | by platform-aware algorithm-hardware approximation process Bit error rate and the number of bits for the mantissa of feature maps and weights represented in BFloat format in ResNet-56 learned by platform-aware algorithm-hardware approximation process | 123<br>124 |

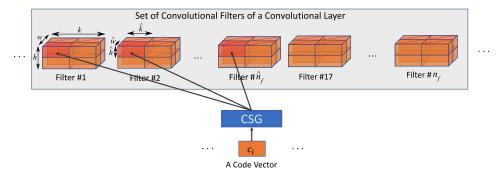

| Figure 5.1:  | Generation of a regular-shaped but approximate set of filters from the concatenation of slices through Convolutional Slice Generator                                                                                                                       | 130        |

| Figure 5.2: | a) The hardware implementation of BSG and b) the BSG-augmented acceler-   |     |

|-------------|---------------------------------------------------------------------------|-----|

|             | ator architecture                                                         | 145 |

| Figure 5.3: | Training and test error for DenseNet-BC-40-48, DenseNet-BC-40-36 and      |     |

|             | their CSG-augmented versions on CIFAR-10 dataset                          | 147 |

| Figure 5.4: | Training and test error for the ResNet-56 and its CSG-augmented versions. | 150 |

| Figure 5.5: | Training and test error for MobileNet V2 (CIFAR version) and its CSG-     |     |

|             | augmented version                                                         | 151 |

| Figure 5.6: | Training and test error for ShuffleNet V2 (0.5x) (CIFAR Version) and its  |     |

|             | CSG-augmented version                                                     | 151 |

| Figure 5.7: | Train and validation errors of ResNet-50-CSG-[16,16,3,3]-128, and ResNet- |     |

|             | 101-CSG-[16,16,3,3]-128 on ImageNet dataset                               | 153 |

## LIST OF TABLES

| Table 1.1: | Various CNN models for ImageNet-1K dataset and their number of parameters, MAC operations for classifying a single input image, and their Top-1 and Top-5 classification accuracies | 4   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1: | Maximum Acceptable Error Rate and Output PSNR                                                                                                                                       | 27  |

| Table 2.2: | Energy consumption Comparison of resistive Bloom vector in ReBF and CMOS Bloom vector                                                                                               | 38  |

| Table 2.3: | Optimum ReBF configuration for different applications                                                                                                                               | 38  |

| Table 2.4: | Total energy consumption (fJ) of CMOS components in ReBF, Hash functions, output registers, and decoder for FUs in different applications                                           | 39  |

| Table 2.5: | Energy savings and neural network accuracy across different BF settings                                                                                                             | 42  |

| Table 3.1: | Workloads, their released year, model size, number of convolution and fully-connected layers, and baseline classification accuracy                                                  | 69  |

| Table 3.2: | SnaPEA and EYERISS design parameters and area breakdown                                                                                                                             | 69  |

| Table 3.3: | Absolute and relative energy comparison for different components of SnaPEA architecture along with off-chip memory access energy cost                                               | 71  |

| Table 3.4: | The percentage of convolution layers operating in the predictive mode, and their average speedup and energy reduction when classification accuracy drop                             | , 1 |

|            | is set to $\leq 3\%$                                                                                                                                                                | 76  |

| Table 3.5: | True negative and false negative rate in predictive mode when classification accuracy drop is set to $\leq 3\%$                                                                     | 76  |

| Table 4.1: | Energy-error of approximate units extracted from [LPMZ11, AKAKP17, VKAKP17]                                                                                                         | 101 |

| Table 4.2: | Number of error parameters, adders and multipliers, and the quality loss on the validation dataset for Linear Regression and Support Vector Machine learning                        | 400 |

| Table 4.3: | algorithms with different number of input features                                                                                                                                  | 103 |

| 14016 4.5. | Energy consumption of adders, multipliers and refreshing DRAM of Linear Regression in the exact and approximate modes with quality loss of 5%                                       | 105 |

| Table 4.4: | CNN model size, original model accuracy, and accuracy of the models with                                                                                                            | 105 |

|            | the approximate configurations at layer-wise granularity without fine-tuning                                                                                                        |     |

|            | the original model parameters                                                                                                                                                       | 108 |

| Table 4.5: | Accuracy obtained for ResNet-56 in various settings: layer-wise approximation with fine-tuning, filter-wise approximation without fine-tuning, and                                  |     |

|            | layer-wise approximation quantization only                                                                                                                                          | 110 |

| Table 4.6: | Error model (percentage of beats that are erroneous) in approximate DRAM                                                                                                            |     |

|            | units under various voltage levels obtained from [CYG <sup>+</sup> 17]                                                                                                              | 117 |

| Table 4.7: | The estimated coefficients $\alpha$ and $\beta$ in Problem 4.2. to model the required number of LUTs and FFs for different number of MAC units based on the                         |     |

|            | required resources for 16 MACs                                                                                                                                                      | 122 |

| Table 4.8: | On-chip energy consumption, energy improvement of DRAM accesses and resource utilization on a Xilinx Zynq-7000 series FPGA for original ResNet-56 and platform-aware quantization and approximate DRAM settings | 125 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5.1: | Training results of CSG on CIFAR-10 dataset with similar hyperparameters as original models                                                                                                                     | 148 |

| Table 5.2: | Training results of CSG on ImageNet-1000 (ILSVRC2012) dataset                                                                                                                                                   | 152 |

| Table 5.3: | Results of CSG for semantic segmentation on Pascal VOC 2012 validation                                                                                                                                          | 152 |

| 14010 5.51 | dataset                                                                                                                                                                                                         | 154 |

| Table 5.4: | Comparison of various compression techniques with CSG method on CIFAR-                                                                                                                                          |     |

|            | 10 dataset                                                                                                                                                                                                      | 155 |

| Table 5.5: | Accuracy and the model size of ResNet-56 and its BSG augmented version                                                                                                                                          |     |

|            | for different sizes of code vectors $(n_c)$                                                                                                                                                                     | 157 |

| Table 5.6: | Latency, on-chip energy consumption, energy improvement of DRAM ac-                                                                                                                                             |     |

|            | cesses and resource utilization on a Xilinx Zynq-7000 series FPGA for BSG-                                                                                                                                      |     |

|            | augmented ResNet-56 compared to the original model                                                                                                                                                              | 158 |

| Table 5.7: | Accuracy and the model size of MobileNetV2 and its BSG augmented version                                                                                                                                        |     |

|            | for different sizes of code vectors                                                                                                                                                                             | 159 |

| Table 5.8: | Latency, on-chip energy consumption, energy improvement of DRAM ac-                                                                                                                                             |     |

|            | cesses and resource utilization on a Xilinx Zynq-7000 series FPGA for BSG-                                                                                                                                      |     |

|            | augmented MobileNetV2 compared to the original model                                                                                                                                                            | 160 |

#### **ACKNOWLEDGEMENTS**

This dissertation would not have been possible without the encouragement, guidance and support from many people throughout my academic study.

First and foremost, I would like to express my greatest appreciation to my Ph.D. advisor, Professor Rajesh K. Gupta, for providing me an opportunity to join University of California San Diego and his research group, where I could follow a new path for research and enjoy the beautiful city of San Diego. His great leadership and vision enabled me to choose an exciting research area and explore it enthusiastically during my PhD program. His expertise, guidance and continuous support helped me shape my Ph.D. dissertation as well as my future path.

I am deeply grateful to my co-advisor, Professor Hadi Esmaeilzadeh, for sharing his knowledge in computer architecture and providing opportunities to explore practical aspects of my research area that significantly helped broaden my perspective. I would also like to thank Professor Sicun Gao, one of my committee members, whose expertise in optimized automation notably aided in the introduction of a new way for systematic hardware design. I would like to thank my other committee members, Professor Gert Cauwenberghs and Professor Ryan Kastner, for their feedback and suggestions, without which, I would not have expanded my research from different perspectives. Moreover, I am thankful to Professor Massimo Franceschetti and Professor Hao Su, who kindly accepted to collaborate and shared their valuable ideas and feedback.

In addition to professors at UCSD, I am greatly thankful to Professor Zainalabedin Navabi and Professor Ali Afzali-Kusha, who not only taught me research skills and fundamental concepts in digital systems while studying for my Bachelor's and Master's degrees at University of Tehran, their efforts to instill confidence in their students including me to think big and pursue their own ideas were also commendable.

I was highly fortunate to be surrounded by past and current members of the Microelectronic Embedded Systems Laboratory (MESL) at UCSD, whose guidance, friendship, sense of humor, and support made my Ph.D. program at UCSD enjoyable and unforgettable. I would like

to thank my colleagues in the MESL, Abbas Rahimi, Atieh Lotfi, Xun Jiao, Jeng-Hau Lin, Dezhi Hong, Francesco Fraternali, Dhiman Sengupta, Sean Hamilton, Jason Koh, Omid Assare, Manish Gupta, Zhou Fang, Ranak Roy Chowdhury, Muhammad Adnan, Bharathan Balaj and many more who made me feel here home and my path brighter and easier.

Last but not least, I owe my deepest gratitude to my parents, Masoumeh Koosha and Seyfollah Akhlaghi, for their unconditional love, dedication, wisdom, their belief in me and more importantly for respecting my choice to study abroad. I would have not been able to stand at this point in my life without their help, love, patience and support. I am also greatly indebted to my sisters, Saeedeh Akhlaghi and Sepideh Akhlaghi, for always being there in the time of need with love and for encouraging me to move forward. I would also like to extend my deepest gratitude to my husband, Hamed Omidvar, who not only helped strengthen my dissertation through sharing his mathematical insights and fundamental ideas, he has also supported me during challenging times. His trust in me and his love for me have been helping me grow.

The material in this dissertation is based on the following publications.

Chapter 2 contains re-organized reprints of Vahideh Akhlaghi, Abbas Rahimi, and Rajesh Gupta, "Resistive Bloom Filters: from Approximate Membership to Approximate Computing with Bounded Errors", *In IEEE Design, Automation, and Test in Europe (DATE)*, 2016, of which the dissertation author is the primary author, and Xun Jiao, Vahideh Akhlaghi, Yu Jiang, and Rajesh Gupta, "Energy-Efficient Neural Networks using Approximate Computation Reuse", *In IEEE Design, Automation, and Test in Europe (DATE)*, 2018, of which the dissertation author is the co-author and primary investigator.

Chapter 3, in full, is a reprint of the material appeared in Vahideh Akhlaghi, Amir Yazdanbakhsh, Kambiz Samadi, Rajesh Gupta, and Hadi Esmaeilzadeh, "Snapea: Predictive Early Activation for Reducing Computation in Deep Convolutional Neural Networks", *In ACM/IEEE International Symposium on Computer Architecture (ISCA)*, 2018. This dissertation author is the primary author of the paper.

Chapter 4, partly contains the materials of Vahideh Akhlaghi, Sicun Gao, and Rajesh Gupta, "LEMAX: learning-based Energy Consumption Minimization in Approximate Computing with Quality Guarantee", *In ACM/IEEE Design Automation Conference (DAC)*, 2018. In addition, this chapter contains the unpublished materials co-authored by Vahideh Akhlaghi, Dezhi Hong, Sicun Gao, Hadi Esmaeilzadeh and Rajesh K. Gupta. This dissertation author is the primary author of the mentioned materials.

Chapter 5 contains the materials of Hamed Omidvar, Vahideh Akhlaghi, Hao Su, Massimo Francescheti, and Rajesh K. Gupta, "Associative Convolutional Layers", *submitted for publication in International Conference on Artificial Intelligence and Statistics (AISTATS)*, 2021, of which this dissertation author is the co-author and the primary investigator and Vahideh Akhlaghi, Hamed Omidvar, Massimo Francescheti, and Rajesh K. Gupta, "Parameter Approximation of CNNs for Improved Inference on FPGA", *submitted for publication in Design Automation Conference (DAC)*, 2021, of which this dissertation author is the primary author.

Finally, I would like to thank all my co-authors and collaborators (Abbas Rahimi, Xun Jiao, Yu Jiang, Amir Yazdanbakhsh, Kambiz Samadi, Dezhi Hong, Hamed Omidvar, Massimo Franceschetti, Hao Su, Sicun Gao, Hadi Esmaeilzadeh and Rajesh K. Gupta) who kindly approved the inclusion of the aforementioned publications in my dissertation.

#### **VITA**

| 2007 | B. S. in Computer Engineering (Hardware Engineering),<br>University of Tehran            |

|------|------------------------------------------------------------------------------------------|

| 2011 | M. S. in Computer Engineering (Computer Architecture), University of Tehran              |

| 2020 | Ph. D. in Computer Science (Computer Engineering),<br>University of California San Diego |

#### **PUBLICATIONS**

Vahideh Akhlaghi, Hamed Omidvar, Massimo Francescheti, and Rajesh K. Gupta, "Parameter Approximation of CNNs for Improved Inference on FPGA", *submitted for publication in Design Automation Conference (DAC)*, 2021.

Hamed Omidvar, Vahideh Akhlaghi, Hao Su, Massimo Francescheti, and Rajesh K. Gupta, "Associative Convolutional Layers", *submitted for publication in International Conference on Artificial Intelligence and Statistics (AISTATS)*, 2021.

Vahideh Akhlaghi, Sicun Gao, and Rajesh Gupta, "LEMAX: learning-based Energy Consumption Minimization in Approximate Computing with Quality Guarantee", in *Proceedings of ACM/IEEE Design Automation Conference (DAC)*, 2018.

Vahideh Akhlaghi\*, Amir Yazdanbakhsh\*, Kambiz Samadi, Rajesh Gupta, and Hadi Esmaeilzadeh, "Snapea: Predictive Early Activation for Reducing Computation in Deep Convolutional Neural Networks", *in Proceedings of ACM/IEEE International Symposium on Computer Architecture (ISCA)*, 2018. (\*equal contributions)

Xun Jiao, Vahideh Akhlaghi, Yu Jiang, and Rajesh Gupta, "Energy-Efficient Neural Networks using Approximate Computation Reuse", *in Proceedings of IEEE Design, Automation, and Test in Europe (DATE)*, 2018.

Vahideh Akhlaghi, Abbas Rahimi, and Rajesh Gupta, "Resistive Bloom Filters: from Approximate Membership to Approximate Computing with Bounded Errors", *in Proceedings of IEEE Design, Automation, and Test in Europe (DATE)*, 2016.

#### ABSTRACT OF THE DISSERTATION

#### **Algorithm-Hardware Optimization of Deep Neural Networks for Edge Applications**

by

#### Vahideh Akhlaghi

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2020

Professor Rajesh K. Gupta, Chair Professor Hadi Esmaeilzadeh, Co-Chair

Deep Neural Network (DNN) models are now commonly used to automate and optimize complicated tasks in various fields. For improved performance, models increasingly use more processing layers and are frequently over-parameterized. Together these lead to tremendous increases in their compute and memory demands. While these demands can be met in large-scale and accelerated computing environments, they are simply out of reach for the embedded devices seen at the edge of a network and near edge devices such as smart phones and etc. Yet, the demand for moving these (recognition, decision) tasks to edge devices continues to grow for increased localized processing to meet privacy, real-time data processing and decision making

needs. Thus, DNNs continue to move towards the edges of the networks at 'edge' or 'near-edge' devices, even though a limited off-chip storage and on-chip memory and logic on the edge devices prohibit the deployment and efficient computation of large yet highly-accurate models.

Existing solutions to alleviate such issues improve either the underlying algorithm of these models to reduce their size and computational complexity or the underlying computing architectures to provide efficient computing platforms for these algorithms. While these attempts improve computational efficiency of these models, significant reductions are only possible through optimization of both the algorithms and the hardware for DNNs.

In this dissertation, we focus on improving the computation cost of DNN models by taking into account the algorithmic optimization opportunities in the models along with hardware level optimization opportunities and limitations. The techniques proposed in this dissertation lie in two categories: optimal reduction of computation precision and optimal elimination of inessential computation and memory demands. Low precision but low-cost implementation of highly frequent computation through low-cost probabilistic data structures is one of the proposed techniques to reduce the computation cost of DNNs. To eliminate excessive computation that has no more than minimal impact on the accuracy of these models, we propose a software-hardware approach that detects and predicts the outputs of the costly layers with fewer operations. Further, through the design of a machine learning based optimization framework, it has been shown that optimal platform-aware precision reduction at both algorithmic and hardware levels minimizes the computation cost while achieving acceptable accuracy. Finally, inspired by parameter redundancy in over-parameterized models and the limitations of the hardware, reducing the number of parameters of the models through a linear approximation of the parameters from a lower dimensional space is the last approach proposed in this dissertation. We show how a collection of these measures improve deployment of sophisticated DNN models on edge devices.

# **Chapter 1**

## Introduction

Deep Neural Networks (DNNs) have expanded applications in various areas, including but not limited to healthcare, education, cybersecurity, and climatology [LLZ<sup>+</sup>17, HRH<sup>+</sup>19, AKX<sup>+</sup>19, OYSO17, SM19, CZZ19, FMJS19, YBU19]. To continuously fuel performance improvements, the size and computation complexities of DNNs are still increasing rapidly. Yet, complex and powerful algorithms are placing high demands on the computing systems in terms of latency and energy consumption. Furthermore, as implementation of these algorithms on the edge and end devices is becoming commonplace due to extreme importance of data privacy and real-time data processing and decision making, similar concerns are also relevant in this area [MARAM18, LBG<sup>+</sup>15, WBC<sup>+</sup>19]. Therefore, to fully exploit the benefits of these algorithms and increase their applicability, they are required to become less computationally complex and be implemented efficiently in order to be executed with high speed and low energy consumption on both large and small scale devices while providing high accuracy.

There exist several attempts to improve DNN models execution, the majority of which can be categorized in two major directions: lowering the computational complexities of these models algorithms and designing efficient hardware architecture. However, in this dissertation, we show that simultaneous consideration of opportunities in both models algorithms and hardware

designs provides significant improvement and optimizes the state-of-the-art solutions without unacceptable drop in the models accuracies. This dissertation provides a set of algorithm-hardware optimization techniques to accelerate Convolutional Neural Networks (CNNs), as one of the important DNN models that are extensively used in various applications such as image and video recognition, recommender systems, and etc. These techniques can be applied on various DNN models due to their algorithmic similarity. Before explaining the techniques, in this section, we review CNN algorithms, their computation and memory demands, and the existing solutions to improve the computation costs of these algorithms.

## 1.1 Background and Problem Definition

CNN algorithms automatically extract features from a given input image through a set of layers, and depending on the application, the extracted features are being processed and used for decision making, classification, recognition, and etc. To extract the features, CNNs consist of various types of layers such as convolutional layers, batch normalization layers, activation layers, pooling layers and fully connected layers. Compared to other types of layers, the computation and memory demands of convolutional layers are relatively high (i.e., it accounts for more than 90% of total computation and memory demand of the whole model [CES16, GPY<sup>+</sup>17, SPM<sup>+</sup>16].)

A convolutional layer is composed of a number of filters that are convolved with the input of the layer called input feature maps with several dot-product operations and generate the output called output feature maps. Equation 1.1 shows the mathematical formulation of a singe pixel in the output feature maps Y generated by a convolutional layer that has F filters and input feature maps of X. The parameters corresponding to filters (i.e., the weights) are shown as a matrix W. In this equation, S is the stride determining the overlap between the regions of the input called receptive fields that each convolution operation is performed on, K the size of kernels in filters, C the number of channels of the input feature maps, and D the number of rows (and columns) of

the output feature maps.

$$Y[f, i, j] = \sum_{c=1}^{C} \sum_{k=1}^{K} \sum_{k=1}^{K} X[c][si+k][sj+k] \times W[f][c][k][k]$$

$$0 \le f < F, \quad 0 \le i, j < D$$

(1.1)

Equation 1.1 indicates several points. First, the main operation in the convolutional layers is multiply-and-add (MAC) operations that is performed in a large quantity depending on values of F, D, C, K. As we can see in the equation, total number of operations to generate all the output feature maps in a single convolutional layer of a CNN with F filters is  $F \times D^2 \times C \times K^2$ , meaning that the current trend of increasing the number of layers and deepening the convolutional layers in CNNs to improve their accuracies results in performing copious number of MAC operations. Second, total number of parameters in a single convolutional layers is  $F \times C \times K^2$ , which similarly indicates that large number of convolutional layers with a large number of filters in current highly accurate CNN models results in tremendous number of parameters to be stored and accessed on computing devices. According to these points, the computation of today's CNN models mainly due to the large number of MAC operations and large sizes of model parameters pushes the limits of computing devices.

Table 1.1 summarizes various CNN models for the classification task on ImageNet-1K [RDS+15] dataset with their corresponding number of parameters, the number of MAC operations that are required to classify a single input image and their Top-1 and Top-5 accuracies. The reported accuracies are obtained from [Tor30]. As we can see in the table, in CNN models with similar architectures increasing the number of parameters and MAC operations leads to increase in their classification accuracies. However, this is not the case across various model architectures. For example, VGG-19 with batch normalization layers (VGG-19-w/BN in the table), although consists of a considerably larger number of parameters and operations compared to ResNet-50, ResNet-101 and ResNeXt architectures, both of its Top-1 and Top-5 accuracies are lower than those models. In addition, comparing ResNeXt-50 (32×4d) and ResNet-50 indicates that only

**Table 1.1:** Various CNN models for ImageNet-1K dataset and their number of parameters, MAC operations for classifying a single input image, and their Top-1 and Top-5 classification accuracies. The reported accuracies are obtained from [Tor30] except those of ResNeXt-101(64×4d) marked by asterisks which are obtained from [XGD<sup>+</sup>17]. In networks with similar structures, increasing the number of parameters and operations will improve the accuracies.

| CNN Models                         | #Parameters | #MAC Operations | Top-1 accuracy | Top-5 accuracy |

|------------------------------------|-------------|-----------------|----------------|----------------|

| VGG-19-w/BN [SZ14]                 | 144M        | 19.6B           | 74.4           | 91.9           |

| MobileNet-V2 [SHZ <sup>+</sup> 18] | 3.4M        | 300M            | 71.9%          | 90.3%          |

| ResNet-18 [HZRS16a]                | 11.1M       | 1.8B            | 69.8%          | 89.1%          |

| ResNet-50 [HZRS16a]                | 25.6M       | 3.8B            | 76.2%          | 92.9%          |

| ResNet-101 [HZRS16a]               | 44.7M       | 7.6B            | 77.4%          | 93.6%          |

| ResNeXt-50(32x4d) [XGD+17]         | 25.6M       | 3.8B            | 77.6%          | 93.7%          |

| ResNeXt-101(64x4d) [XGD+17]        | 79.8M       | 15.2B           | 79.6%*         | 94.7%*         |

re-structuring the original model (ResNet-50) without any additional parameters and operations can result in improving the accuracy. Therefore, in general, Table 1.1 indicates that there are opportunities in the model algorithm itself that can be exploited to improve the model accuracy without the need to add extra parameters and operations.

In addition to opportunities in the model algorithms, another possible direction to improve the model execution cost (i.e., energy consumption and latency) is to optimize hardware design and architecture of underlying computing devices for these algorithms. Existing powerful computing devices with tremendous computing capacities such as Graphics Processing Units (GPUs), although are the main reason behind the advancement of highly accurate DNN models, due to several reasons such as high cost, large energy consumption and area, they are not suitable to be deployed in various range of devices especially in the edge and end devices. Therefore, there is an imperative need to design low energy yet powerful computing devices that can execute the CNN models efficiently without significant degradation of the model accuracy.

According to the mentioned needs and opportunities to improve the computational costs of CNN models without degrading their accuracies to the unacceptable levels, in this dissertation, we introduce a set of techniques, namely algorithm-hardware optimization techniques. These

methods optimize the execution of the CNN models and advance the related state-of-the-art methods by considering the optimization opportunities available both in the model algorithms and their hardware implementations.

## 1.2 Related Works

To improve the computational costs of DNN algorithms, most of the existing techniques mainly focus on optimizing either the computation in DNN models or the underlying computing architectures. Here, we review some of these techniques in each category.

## 1.2.1 Algorithmic Optimization

To optimize the model computation and size, several techniques have been introduced that can be categorized into four groups [CWZZ18]: network pruning, quantization, low rank factorization, and transferred convolutions. Network pruning approaches reduce the network size and computation by removing the unnecessary connections and operations in the DNN models determined based on various metrics. In quantization based approaches, the computation precision is reduced by lowering the bit-width of operations, weights and feature maps. The methods in low-rank factorization category break down the convolutional layers into several smaller layers by factorizing their weight matrices to low-rank ones, which leads to fewer number of parameters and MAC operations. The last category of the methods to optimize DNN algorithms is transferred convolutions in which a fraction of parameters are eliminated and their corresponding feature maps are generated by a specific transformation of the outputs of the remaining parameters. In the rest of this section, several methods in each category will be explained in more details.

#### **Network Pruning**

One of the common techniques to reduce the computation and memory demands of a DNN model is pruning in which unimportant parameters and operations are identified and removed.

One set of approaches to identify unimportant parameters and operations is based on the magnitude of the weights that eliminates the neurons corresponding to the weights with small magnitude. An example of such methods is biased weight decay [HP89] which includes the weight decay term in the weight update process during the backpropagation in order to make the unimportant weights approach zero and be removed automatically. Another method in this category is introduced in [HPTD15b] that prunes the parameters and the related operations of the pre-trained models by removing their small magnitude weights.

Optimal Brain Damage (OBD) [CDS90] and Optimal Brain Surgeon (OBS) [HSW93] are another set of pruning approaches that eliminate the weights according to their impact on the loss function rather than their magnitude. These methods are built upon measuring the changes in the loss function as a result of deleting a weight and removing the weights with small impact on the loss. To measure the impact of weights on the loss function, the Taylor series of the change in the loss function is represented as a function of perturbation of the weights and a set of coefficients that can be obtained by the Hessian matrix at the end of training.

Despite the effectiveness of the mentioned approaches in reducing the model size and computation, due to irregular sparsity which leads to irregular computation patterns, their final impact on the execution costs is not optimal. To avoid this issue, finding structured sparse models in which a set of regular computational blocks in the original model (e.g., a number of filters in a convolutional layer of a CNN model) are removed are another technique in pruning DNN networks proposed in [WWW<sup>+</sup>16]. The technique learns the structured sparse models by adding a group lasso of a set of weights into the loss function and using the regularization technique to make all the weights in a group zero.

#### Quantization

Lowering the numerical precision of computation through lowering the bit-width of parameters and feature maps, namely quantization, is another common effective approach to reduce the computation and memory demands of DNN models. In general, the computation in DNN models is performed in 32-bits floating point format (FP-32), which imposes high computational and memory burden on computing devices due to performing high-cost floating point MAC operations and transferring large sizes of data across the memory hierarchy, especially for large models with a large number of operations. To reduce the cost, quantizing the values of parameters and feature maps to a numerical format with lower bit-width is commonplace; however, due to reduced precision the final accuracy of the quantized models may be degraded in some cases. Here, we review some of the quantization methods available in the literature and their impact on the model accuracies.

Representing the values in fixed point format with less than 32 bits during the inference phase is one of the common quantization method, which requires significantly lower cost computation compared to computation in 32-bit floating point format. [GMG16] uses dynamic fixed point values in which the model parameters and feature maps are quantized to different bit-width due to the different ranges of their values. To recover the resulting accuracy degradation due to quantization, the under-studied models are fine-tuned (with the floating point format in back-propagation stage) until the final accuracy drop remains within 1%. Quantizing the values to integer format is another approach that is studied in [JKC+18], which quantizes the network parameters and feature maps to 8-bits integer values during the inference while during training the models, in the backpropagation pass floating point format is used and in the forward pass, the impact of quantization is computed. This method, although reduces the computation overhead, it drops the accuracy significantly (2% accuracy drop for ResNet models on ImageNet-1K are reported.)

Although quantization is more common in the inference phase of DNN algorithms, there exists some work that quantize the computed gradients and the model parameters and feature

maps during DNNs' training as well. Binarized Neural Networks (BNNs) [HCS+16] and XNOR-Nets [RORF16] binarize the weights and feature maps, and Quantized Neural Networks (QNNs) [HCS+17] quantizes them to more than 1-bits during both inference and training phases. In addition, in XNOR-Net and QNN, the impact of binarizing/quantizing the gradients on the model accuracy are also studied. The accuracies obtained by all these methods indicates that excessive quantization, especially in training phase, can lead to significant reduction in the model's accuracy. In addition, most of these methods require elaborate modifications to the model and its training and inference phases and hence are not always easy to implement.

#### **Low-Rank Factorization**

Low-rank factorization methods aim to reduce the number of operations and parameters of a DNN by breaking down a matrix multiplication in fully connected layers or convolutional layers into several smaller matrix multiplications that have lower rank, thus lower number of parameters and operations.

To be more specific, let's go back to the operations in a convolutional layer discussed in Section 1.1 with a parameter matrix of W with the dimension of  $F \times C \times K \times K$  and the input feature maps as a matrix X with the dimension of  $C \times D_{in} \times D_{in}$ . In general, the convolution of W and X in the convolutional layer can be formulated as follows:

$$Y_f = W_f * X \quad \forall f \in \{1, 2, ..., F\}$$

(1.2)

where  $W_f$  and  $Y_f$  is the parameters of filter f and its the corresponding output feature maps, respectively. Here, the dimension of  $W_f$  is  $C \times K \times K$ .

In low-rank factorization approaches, the parameter matrix of  $W_f$  corresponding to filter f is broken down into several low-rank matrices called separable filters [RSLF13] in different ways. One way upon which filter decomposition approaches in [TXZ<sup>+</sup>15] and [JVZ14] are built is to

represent the parameter matrix of a filter  $f(W_f)$  as a sum of R matrix multiplications between a set of horizontal and vertical matrices  $H_f$  and V with rank R (i.e.,  $W_f = \sum_{r=1}^{r=R} H_f^r(V_r)^T$ ). The matrix  $H_f$  consists of R horizontal kernels of shape  $1 \times K$  and the matrix V consists of R vertical filters of shape  $C \times K \times 1$ . Therefore, the corresponding convolution in equation 1.2 is broken down into two convolutions according to the following equation:

$$Y_f = W_f * X = \sum_{r=1}^{r=R} H_f^r * (V_r * X)$$

(1.3)

Here, in this method the main challenge is to find the horizontal and vertical matrices to represent the parameters of a convolutional layer. In [TXZ $^+$ 15], such matrices are obtained by computing the Singular Value Decomposition (SVD) of the weight matrix of a layer. To minimize the error of this decomposition, SVD decomposition is added in the forward pass of training a CNN model by breaking down the weights in the forward pass and back-propagating the corresponding error and updating the weights in the backward pass. This method due to computing SVD during training of CNNs results in high training cost; the inference phase, however, due to performing smaller convolutions is more efficient compared to the original model. Another approach to find such breakdown is introduced in [JVZ14], which proposes to learn the H and V matrices by defining a new objective function that reflects the approximation error as a difference between the original weights in a pre-trained model and approximated weights obtained by multiplications of H and V and learns these matrices such that the objective function (i.e., the approximation error) is minimized.

Another way of decomposing filters into the low-rank ones is to break them down into depth-wise and point-wise filters, which is a common method widely used for designing a small network for embedded devices such as MobileNet models [HZC<sup>+</sup>17]. Depth-wise and point-wise separable filters are a decomposition of matrix W with a shape of  $F \times C \times K \times K$  into C separate  $1 \times K \times K$  depth-wise filters, which are convolved with feature maps in each channel of the input

feature maps X separately and F point-wise separable filters with the shape of  $C \times 1 \times 1$ , which are convolved with the results of depth-wise filters.

#### **Transferred Convolutions**

Transferred convolutions are one of the interesting methods that compact a network by allowing high degree of weight sharing inspired by the translation symmetry existing in most of the perception tasks such as the tasks in computer vision [CW16]. Translation symmetry is a property that means data labels and distributions are invariant to shifts. By this property, shifting an image and feeding it to a network generate the same results as feeding the image to the network and shifting the outputs. This characteristic is held in all the layers of a CNN as well as in the first layer. Therefore, the output feature maps of a layer can be constructed by feeding a part of input feature maps to a layer and constructing the rest through a transformation function, which can help to share and reuse the weights to a large extent. More specifically, transferred convolutions compact the parameters of a model and reduce the operations by specifying a set of base filters, computing the corresponding feature maps and constructing the rest of the feature maps by spatial repetition of the feature maps obtained by the base filters.

An example of such approach is CReLU [SSAL16], which reduces the computation and parameters by 2× through constructing half of the feature maps in each convolution layer as the opposite of the other half. Another method to transfer convolutions is called G-CNN introduced in [CW16] that reduces the computation and the size of parameters by rotating a fraction of the feature maps obtained by a set of base filters, which in size is a fraction of the number of parameters in the original model to construct all the feature maps. In these methods, although the size of feature maps remains the same as the original models, the number of MAC operations and parameters are reduced. Depending on the compression ratios, the accuracy of the models is degraded by up to 3% of the original models.

## 1.2.2 Hardware Optimization

The next set of existing solutions to improve the execution cost of DNN algorithms is designing specialized hardware architectures optimized for these algorithms. In these solutions the model computation is not modified and only the hardware is optimized to perform the computation efficiently. Here, in this section, we review some of the main architectures developed in academia and industry with the goal of improving the performance and energy consumption of the DNN models.

Due to high computing capacity of GPUs, especially with the added tensor cores along with CUDA cores, and high degree of parallelization, these computing devices are the main computing platforms for training large neural networks. However, due to their large size, high cost, high energy consumption and inefficient processing of single input, GPUs are a poor fit for inference especially on edge and end devices with limited area, memory and energy budget, where efficient processing of single input matters most. To improve the inference performance and cost, many ASIC or FPGA based specialized architectures are introduced [LCL+15, ZLS+15, XYP+17, AJH+16, CES16, JYP+17, FOP+18].

PuDiannao [LCL<sup>+</sup>15] is one of the ML accelerators that executes various types of ML algorithms and tasks such as classification, regression and clustering. This ASIC accelerator implements a general ML functional unit that supports various computation types used in ML algorithms such as dot-product, sorting, and etc along with various types of on-chip buffers to factor in various locality properties of ML algorithms and maximize reusability of on-chip data.

[ZLS<sup>+</sup>15] introduces an analytical method to optimize resource and bandwidth utilization on an FPGA platform to maximize the performance. It quantitatively analyzes the computation throughput and memory bandwidth for a CNN design with various optimization methods such as loop tiling and chooses the design with maximum performance and lowest resource requirements. In addition, [XYP<sup>+</sup>17] focuses on designing a high-performance FPGA accelerator for CNNs using systolic arrays with a number of PEs. To achieve such design, it proposes an automatic

design space exploration framework that selects the best mapping of operations onto the systolic array to feed proper data to each PE location, the best PE array shape to maximize DSP efficiency, and a proper tiling size to maximize on-chip data reusability.

Cnvlutin [AJH<sup>+</sup>16] is another design that eliminates multiplication of the zero operands by grouping the lanes and allowing them to execute operations independently while skipping zero values multiplications. It also introduces a data storage format that encodes the elimination decision and controls the lanes.

Another ASIC accelerator design is called Eyeriss [CES16], which is a spatial architecture consisting of a global buffer and an array of processing elements (PEs). Each PE is made up of several MAC units and local registers and connected to other PEs with a Network on Chip (NoC). The entire operations of a convolutional layer are parallelized on PEs based on a novel dataflow called Row Stationary (RS). RS dataflow maximizes reusability of both feature maps and weights through sharing a set of filters horizontally and a set of feature maps diagonally across the PEs in the PE array, which leads to reduced data movement across various memory units and energy consumption.

In addition, Google in [JYP<sup>+</sup>17] introduces an ASIC architecture called Tensor Processing Units (TPU), which is hard-wired for parallelizing MAC operations in a matrix-matrix multiplications through a systolic array of 256×256 MAC units. Despite achieving high performance for a batch of dense layers in DNN models, this design suffers from resource under-utilization for processing a single input.

To efficiently serve single requests, Microsoft introduces a new FPGA based architecture called Brainwave [FOP+18], which instead of parallelizing operations in a matrix-matrix multiplication, parallelizes operations in matrix-vector (MV) multiplications and constructs matrix-matrix multiplications through MV multiplications. To parallelize operations in convolutional layers, Brainwave employs a set of tile engines, each performing a native-sized MV multiplications and accumulates the results of all tile engines by a set of accumulators.

In addition to the mentioned 2D architectures, the challenges of designing CNN accelera-

Figure 1.1: The organization of this dissertation

tors in 3D-stacked logic-in-memory computing systems are also studied in the literature and new accelerators such as Neurocube [KKC<sup>+</sup>16] and TETRISS [GPY<sup>+</sup>17] are introduced.

## 1.3 Dissertation Contribution and Organization

As discussed in the previous section, existing solutions to reduce the execution costs of DNN models in the literature mostly focus on optimizing either the underlying algorithms or hardware architectures. Even though the execution cost of these models are improved with the mentioned approaches, sometimes model accuracy is compromised and due to disregarding the other end of the spectrum, maximum benefit is not achieved. Therefore, substantial improvement without unacceptable accuracy degradation is still achievable by considering holistic optimization opportunities. In this dissertation, we explore various approaches for providing such optimizations to CNN accelerators. The organization of this dissertation is summarized in Figure 1.1.

In general, the methods presented in this dissertation are inspired by the fact that due to several reasons such as the algorithmic structures of DNNs, i.e., pooling and activation layers in their algorithms and specific functions at the end of their networks to make final decision based on the underlying task (e.g., softmax for classification), over-parameterization and repeated operations on similar inputs these models are error-tolerant. Therefore, approximate computation of models algorithms with less precise and a decreased number of parameters and operations along with efficient hardware architecture designs to support these approximate computation can lead to lower execution cost while achieving an acceptable accuracy. This dissertation exploits this characteristics and proposes several algorithm-hardware optimization approaches.

First, due to similarity of data and parameters in various CNN models, highly frequent patterns (approximate patterns) can be observed on the inputs (on a part) of inputs of MAC operations in their convolutional layers. Motivated by this observation, we propose an optimization approach at their algorithmic level by which the computed outputs for the matching patterns are reused in order to reduce the number of heavy MAC operations. A proper selection of these patterns (or approximate patterns) can achieve acceptable accuracy while lowering the cost. We optimize the hardware architecture as well for efficient implementation of this computation reuse by exploiting a low-cost data structure to memorize frequent patterns and match approximate patterns. Chapter 2 provides the detailed description of this algorithm-hardware optimization approach.

Second, due to the algorithmic structure of CNN models in which compute-heavy convolutional layers are followed by the activation layers, thus a specific range of their outputs are mapped to a predetermined set of values, a large number of the convolution outputs are not required to be thoroughly computed. Therefore, to reduce the number of MAC operations and memory accesses, we propose to dynamically identify and prune a large number of unnecessary MAC operations by speculating the range of convolutional outputs that are bounded by the activation functions with a fewer number of operations. To support such dynamic pruning at the hardware level, we design a low-cost hardware architecture with a slight modification of the prevailing accelerator

architectures. This technique, called SnaPEA, is explained in more detail in Chapter 3.

Third, tolerance of DNN models to low precision computation and hardware units, non-uniform impact of imprecise computation in various layers/filters on the model output and different architecture designs and resource constraints in different underlying computing platforms are the motivation behind our proposed approach in chapter 4, where we propose platform-aware algorithm-hardware approximation of various layers/filters of a CNN model in order to maximize speedup and energy saving. Due to a large design space, we propose a novel machine learning based optimization framework for automatic and quick exploration and selection of proper approximate version of computation in DNN algorithms and proper approximate hardware configurations to implement various layers/filters by taking the resource constraints of the underlying computing platform into consideration.

As the final approach, in chapter 5, to reduce the model size that helps to improve the inference cost by reducing the off-chip memory accesses and the training cost, especially in distributed and federated learning, by reducing the communication overhead (i.e., to transfer gradients of parameters among devices), we provide a plug-and-play solution that generates the model parameters from a lower dimensional space with a linear transformation. For further parameter reduction, this method mainly exploits the associativity between convolutional layers and generates all the parameters through a set of fewer auxiliary parameters that is shared among all layers. Given the limited energy of edge devices, we further optimize this approach in order to provide low energy inference on edge through representation and reconstruction of models parameters with binary parameters and operations.

Finally, chapter 6 concludes this dissertation.

# Chapter 2

## **Hardware Efficient Function**

# **Approximation**

Current hardware implementations of neural networks exhibit high energy consumption due to the intensive computing workloads. The problem exacerbates, especially, when these models are executed on massively parallel architectures such as GPUs, which bring large-scale computations on a single device at the expense of significant energy consumption. Inspired by highly repetitive patterns on costly operations observed in the computation of these models, we provide an energy efficient implementation of these models through proposing a novel function approximation. We provide an energy efficient yet controllable function approximation using the probabilistic membership provided by Bloom filters (BF). A set of BFs is integrated into the functional units (FU) to store and detect frequent patterns for computational reuse. Depending on the applications, the computation reuse can be expanded through approximate pattern matching that detect frequent patterns on narrow precision data. Our approach has the ability to control the error behavior of a target function, hence the output quality, at the design time with the aid of controllable false positives (FP) available in the structure of the BF.We further lower energy consumption by designing a resistive Bloom filter (ReBF) using memristor array. Our

experimental results show that for Convolutional Neural Networks, the BFs enable 47.5% energy saving of multiplication operations, while incurring only 1% accuracy drop. While the actual savings will vary depending upon the extent of approximation and reuse, this work presents a method for reducing computing workloads and improving energy efficiency.

## 2.1 Introduction

Recent advances in neural networks have achieved impressive performance on various application domains such as medical diagnostics [YJZ<sup>+</sup>06], image classification [KSH12], speech recognition [HDY<sup>+</sup>12], and natural language processing [CWB<sup>+</sup>11]. The continued success of neural networks has led to their implementation on a variety of hardware platforms [CLL<sup>+</sup>14][HAM07][CDS<sup>+</sup>14a]. Energy consumption is an important metric for their implementation in increasingly broad range of computing platforms. Arithmetic operations and memory accesses constitute a significant source of energy consumption in deep learning accelerators. We focus here on reducing the computational workloads in neural networks.

In recent literature, computational workloads have been addressed by using approximations in computations thus creating a tradeoff between accuracy and energy [DLC<sup>+</sup>15][MSS<sup>+</sup>16]. The approximations can be made both in hardware or in software. For instance, approximate computation units have been shown to have better energy efficiency than the exact ones [JLL<sup>+</sup>17]. Neural network computations are dominated by additions and multiplications. Due to their cost and latency, multiplications have been a natural target for optimization in hardware. For instance, in [DLC<sup>+</sup>15], the authors substitute the normal multipliers with inexact multipliers that provide inexact logic but with less hardware cost. Mrazek *et al.* further optimize approximate multiplier design with a uniform structure suitable for hardware implementation [MSS<sup>+</sup>16]. While the adaptability of neural networks in its applications is naturally suited to use approximation, in practice it also requires *retraining* the network to mitigate accuracy loss caused by logic errors

from inexact design. Moreover, once the design has been physically implemented in hardware, it is not possible to reconfigure the design to control the approximation level entirely in hardware.