# **UC Irvine**

## **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Fluxless Tin Bonding Processes with Intermetallic Study and Aluminum Circuit Board Technology

#### **Permalink**

https://escholarship.org/uc/item/7gb953pq

#### **Author**

Hsu, Shou-Jen

#### **Publication Date**

2015

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Fluxless Tin Bonding Processes with Intermetallic Study and Aluminum Circuit Board

Technology

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Engineering

by

Shou-Jen Hsu

Dissertation Committee: Professor Chin C. Lee, Chair Professor Farghalli A. Mohamed Professor James C. Earthman

Chapter 3 © 2014 Springer

Chapter 4 © IEEE

Chapter 5 © 2013 Springer

Chapter 8 © IEEE

All other materials © 2015 Shou-Jen Hsu

# **DEDICATION**

To

my dear family and friends

Without their moral support, unconditional love, and encouragement, this dissertation would have never been possible.

# TABLE OF CONTENTS

|                |                                                                  |                                                      | Page |

|----------------|------------------------------------------------------------------|------------------------------------------------------|------|

| List of Figure | s                                                                |                                                      | vi   |

| List of Tables |                                                                  |                                                      | xi   |

| Acknowledge    | ment                                                             |                                                      | xii  |

| Curriculum V   | itae                                                             |                                                      | xiii |

| Publications   |                                                                  |                                                      | xiv  |

| Abstract of th | e Disse                                                          | rtation                                              | xvi  |

| Chapter 1      | Introd                                                           | uction                                               | 1    |

| 1.1            | Electro                                                          | onic Packaging                                       | 1    |

| 1.2            | The So                                                           | oldering Process                                     | 2    |

| 1.3            | The Fl                                                           | luxing Action                                        | 3    |

| 1.4            | Fluxle                                                           | ess Bonding Technique                                | 5    |

| 1.5            | Disser                                                           | tation Outline                                       | 6    |

| 1.6            | Refere                                                           | ences                                                | 9    |

| Chapter 2      | Experi                                                           | imental Setup and Techniques                         | 12   |

| 2.1            | Materi                                                           | ial Fabrication                                      | 12   |

|                | 2.1.1                                                            | Electron Beam Evaporation                            | 12   |

|                | 2.1.2                                                            | Electroplating                                       | 13   |

| 2.2            | Vacuu                                                            | m Furnace and Bonding Setup                          | 14   |

| 2.3            | Charac                                                           | cterization Techniques                               | 18   |

|                | 2.3.1                                                            | X-Ray Diffraction (XRD)                              | 18   |

|                | 2.3.2                                                            | Scanning Electron Microscope (SEM)/Energy Dispersive |      |

|                |                                                                  | X-ray Spectroscopy (EDX)                             | 19   |

| 2.4            | Refere                                                           | ences                                                | 21   |

| Chapter 3      | ter 3 Fluxless Bonding of Silicon Chips to Aluminum Boards using |                                                      |      |

|                | Electro                                                          | oplated Sn Solder                                    | 22   |

| 3.1       | Introduction                                                        | 22 |  |

|-----------|---------------------------------------------------------------------|----|--|

| 3.2       | Experimental design and procedures                                  |    |  |

| 3.3       | Experimental results and discussion                                 | 27 |  |

|           | 3.3.1 Bonding design I                                              | 27 |  |

|           | 3.3.2 Bonding design II                                             | 34 |  |

|           | 3.3.3 Shear test                                                    | 36 |  |

| 3.4       | Summary                                                             | 39 |  |

| 3.5       | References                                                          | 40 |  |

| Chapter 4 | Fabrication of Insulated Metal Substrate (IMS) based on             |    |  |

|           | Anodization on Aluminum & Fluxless Bonding of Cu to IMS using       |    |  |

|           | Electroplated Tin Solder                                            | 43 |  |

| 4.1       | Introduction                                                        | 43 |  |

| 4.2       | Experimental Design and Procedure                                   | 47 |  |

| 4.3       | Experimental Results and Discussion                                 |    |  |

| 4.4       | Summary                                                             | 60 |  |

| 4.5       | References                                                          | 61 |  |

| Chapter 5 | Fluxless Sn bonding of silicon chips to low carbon steel substrates |    |  |

|           | using nickel under-bump metallurgy                                  | 64 |  |

| 5.1       | Introduction                                                        | 64 |  |

| 5.2       | Experimental Design and Procedure                                   | 65 |  |

| 5.3       | Experimental Results and Discussion                                 | 68 |  |

| 5.4       | Summary                                                             | 77 |  |

| 5.5       | References                                                          | 78 |  |

| Chapter 6 | Fluxless Sn bonding of silicon chips to low carbon steel            |    |  |

|           | substrates without underbump metallurgy                             | 82 |  |

| 6.1       | Introduction                                                        | 82 |  |

| 6.2       | Experimental Design and Procedure                                   | 83 |  |

| 6.3       | Experimental Results and Discussion                                 | 85  |

|-----------|---------------------------------------------------------------------|-----|

| 6.4       | Summary                                                             | 89  |

| 6.5       | References                                                          | 90  |

| Chapter 7 | Growth Kinetics of Intermetallic Compounds between Sn and Fe        |     |

|           | Liquid-Solid Reaction Couples                                       | 92  |

| 7.1       | Introduction                                                        | 92  |

| 7.2       | Experimental Design and Procedure                                   | 93  |

| 7.3       | Experimental Results and Discussion                                 | 94  |

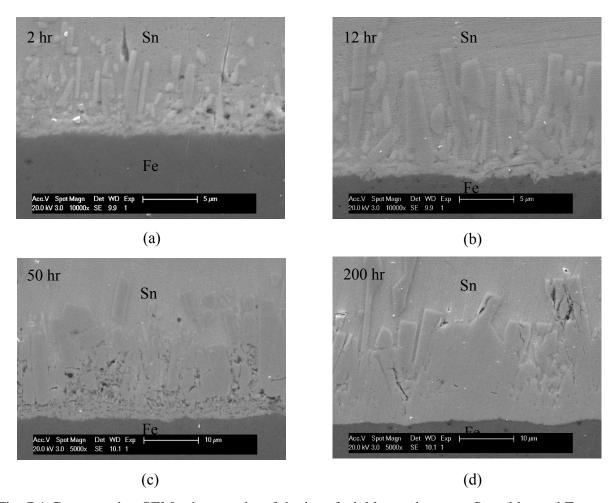

|           | 7.3.1 Microstructural evolution of the intermetallic compound layer | 94  |

|           | 7.3.2 Growth kinetics of the intermetallic compound layer           | 99  |

| 7.4       | Summary                                                             | 105 |

| 7.5       | References                                                          | 106 |

| Chapter 8 | Fluxless Tin Bonding Process with Suppressed Intermetallic          |     |

|           | Growth                                                              | 109 |

| 8.1       | Introduction                                                        | 109 |

| 8.2       | Experimental Design and Procedure                                   | 111 |

| 8.3       | Experimental Results and Discussion                                 | 114 |

| 8.4       | Summary                                                             | 126 |

| 8.5       | References                                                          | 127 |

| Chapter 9 | Summary                                                             | 130 |

## LIST OF FIGURES

|          |                                                                                                                                                                                                                                                                                    | Page |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

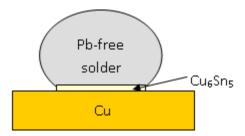

| Fig. 1.1 | A solder joint needs intermetallic formation to be achieved                                                                                                                                                                                                                        | 3    |

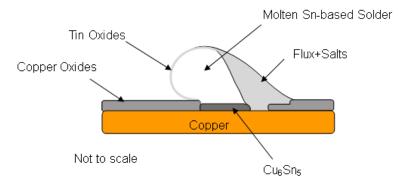

| Fig. 1.2 | Molten flux converts oxide into salts to expose fresh solder and fresh base metal, and to shield them from further oxidation                                                                                                                                                       | 4    |

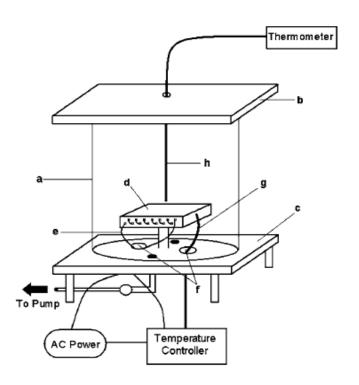

| Fig. 2.1 | Schematic of the vacuum furnace showing key components: (a) quartz cylinder, (b) upper stainless plate, (c) base plate, (d) graphite platform, (e) heating wire, (f) electrical feedthroughs, (g) platform thermocouple, and (h) sample thermocouple                               | 15   |

| Fig. 2.2 | Photo of the graphite heating platform                                                                                                                                                                                                                                             | 16   |

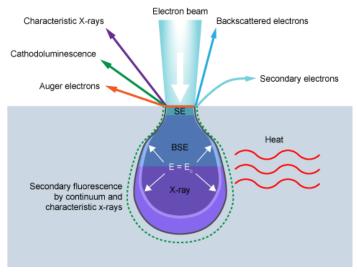

| Fig. 2.3 | The interaction volume and the signals produced by the interaction between the electron beam and specimen                                                                                                                                                                          | 21   |

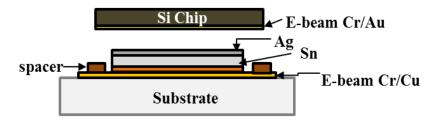

| Fig. 3.1 | Bonding structure and configuration of controlling joint thickness using Cu spacer                                                                                                                                                                                                 | 26   |

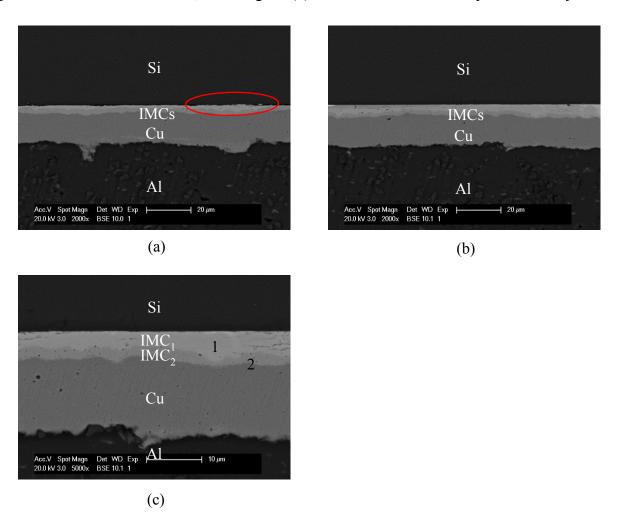

| Fig. 3.2 | Cross-section SEM images of the sample under bonding pressure of 0.6 psi at (a) low magnification ( $1000\times$ ), (b) high magnification ( $5000\times$ ) and (c) low magnification ( $500\times$ ), showing the joint on the edge                                               | 28   |

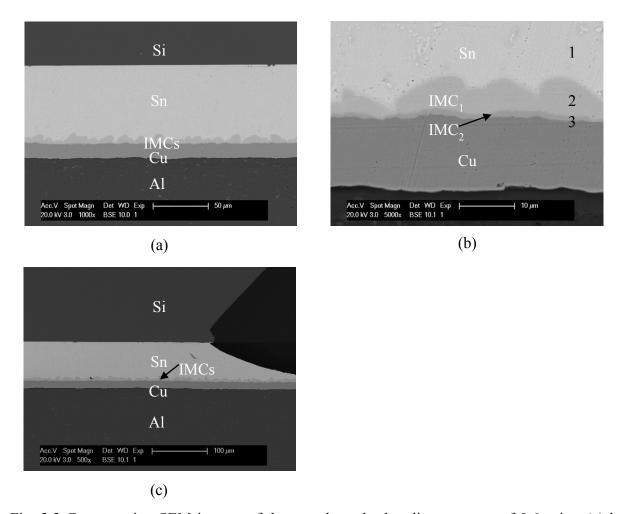

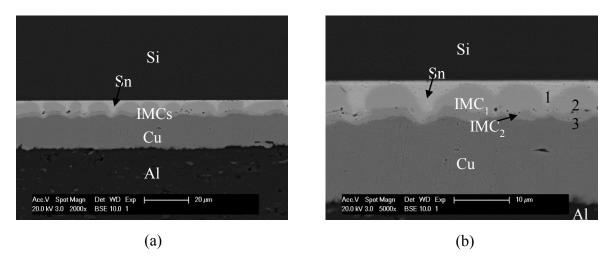

| Fig. 3.3 | Cross-section SEM images of the sample under bonding pressure of 2.5 psi at (a) low magnification ( $2000\times$ ) and (b) high magnification ( $5000\times$ )                                                                                                                     | 30   |

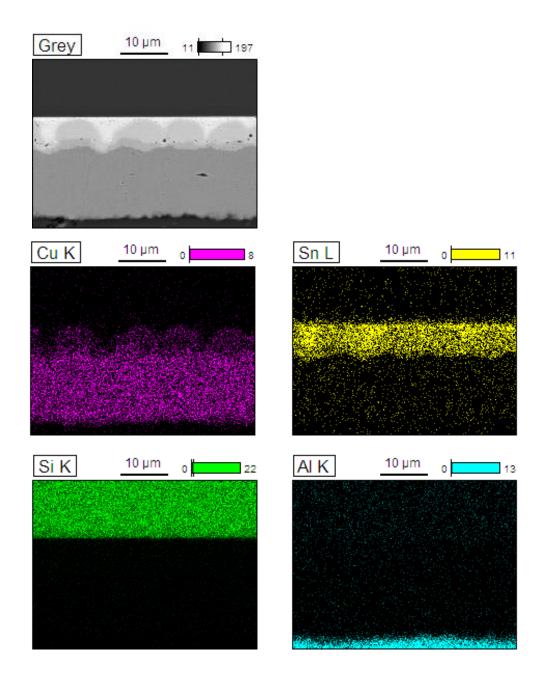

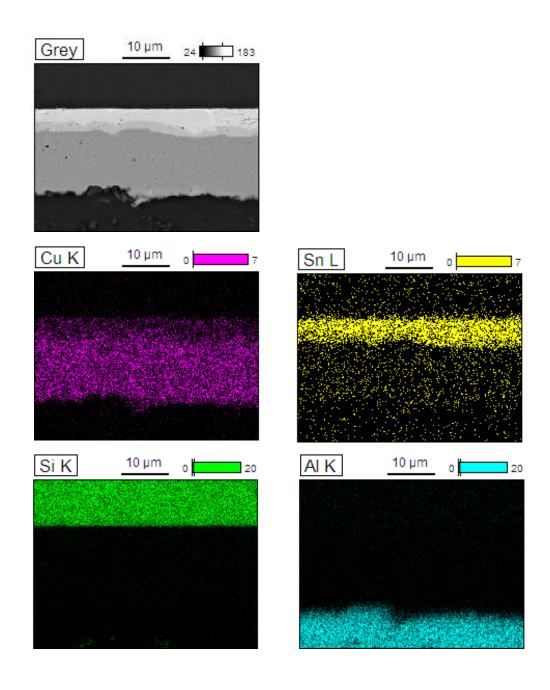

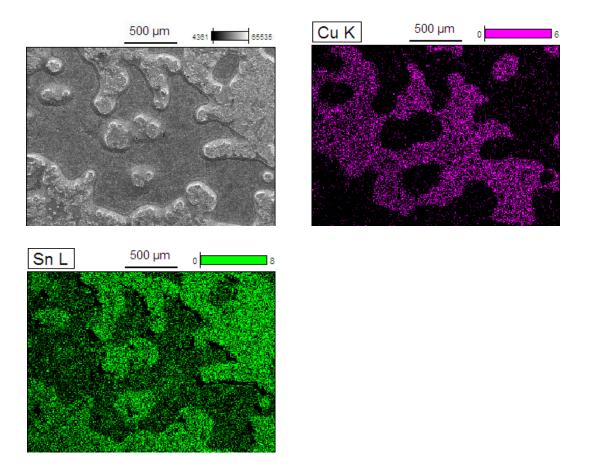

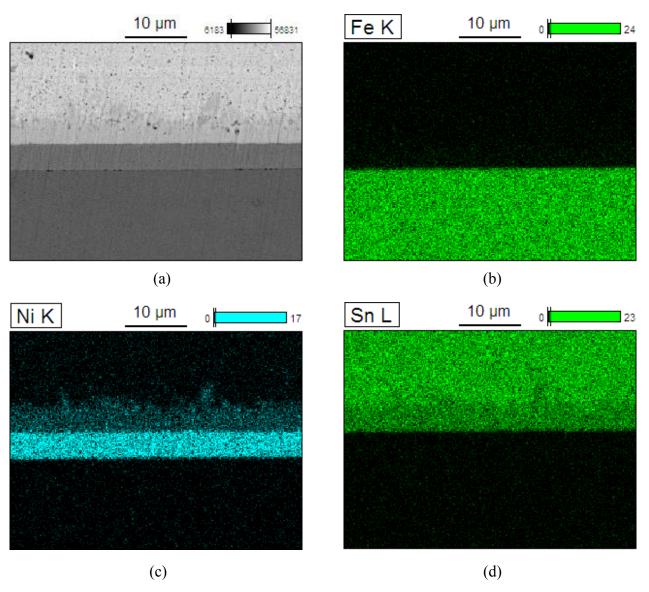

| Fig. 3.4 | EDX element mappings of the sample under bonding pressure of 2.5 psi                                                                                                                                                                                                               | 31   |

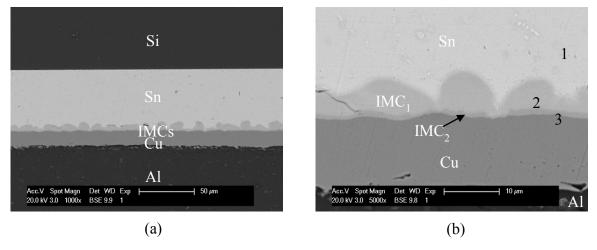

| Fig. 3.5 | Cross-section SEM images of the sample under bonding pressure of 32 psi at (a) low magnification $(2000\times)$ of the partially bonded region, (b) low magnification $(2000\times)$ of the well bonded region and (c) high magnification $(5000\times)$ of the well bonded region | 32   |

| Fig. 3.6 | EDX element mappings of the sample under bonding pressure of 32 psi                                                                                                                                                                                                                | 34   |

| Fig. 3.7 | Cross-section SEM images of the sample made with 50 $\mu m$ Cu spacers at (a) low magnification (1000×) and (b) high magnification (5000×)                                                                                                                                         | 35   |

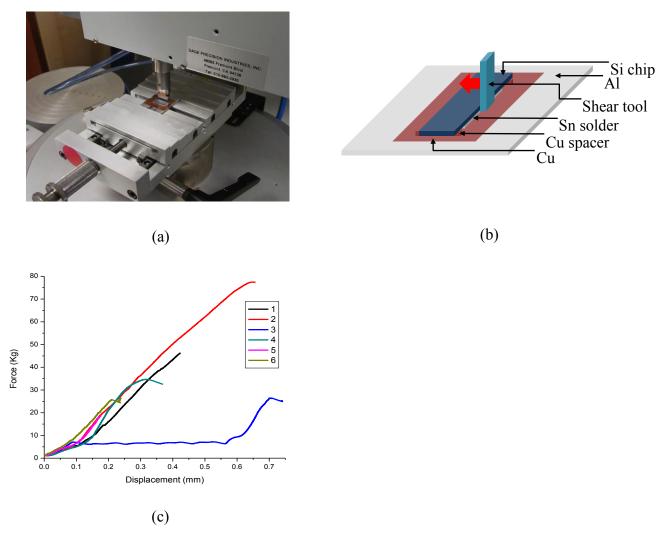

| Fig. 3.8 | Shear test: (a) shear tester, (b) schematic of test geometry, and (c) force versus displacement curves of six samples bonded using 50                                                                                                                                              |      |

|          | um spacer. The displacement is mainly caused by the shear tester.  The tester does not have a sensor to measure the displacement caused by the sample                                                                                                                                                                                                                 | 37 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.9 | An SEM image and EDX mappings on the Al substrate of sample 5 after fracture. On the SEM image, the light regions are Sn and the dark regions are Cu <sub>6</sub> Sn <sub>5</sub> . The joint broke on two interfaces: some regions on the Si/Sn interface and the rest on Sn/Cu <sub>6</sub> Sn <sub>5</sub> interface. The joint did not break inside the Sn solder | 39 |

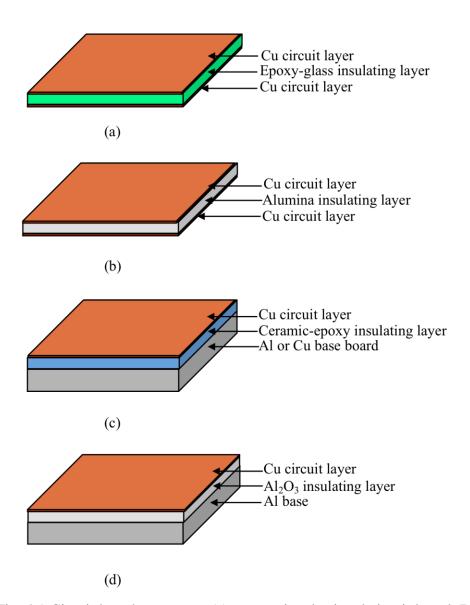

| Fig. 4.1 | Circuit board structures: (a) conventional printed circuit board (PCB), (b) Direct bonded Cu (DBC) board, (c) insulated metal substrate (IMS), and (d) Cu/alumina/Al board of this study                                                                                                                                                                              | 44 |

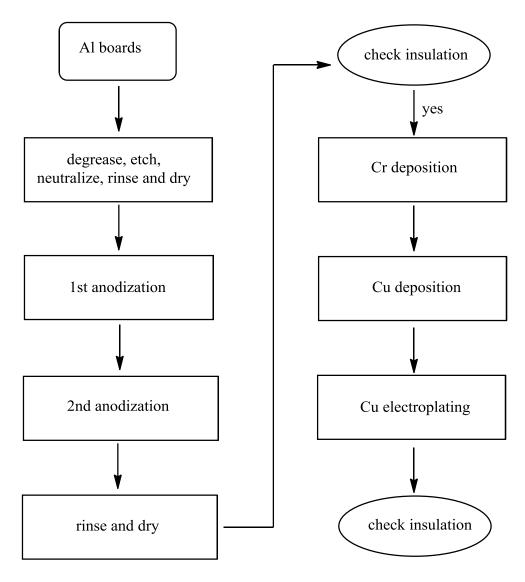

| Fig. 4.2 | Process flow chart of the board fabrication                                                                                                                                                                                                                                                                                                                           | 48 |

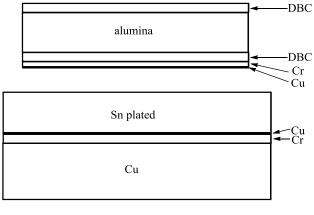

| Fig. 4.3 | Structures used during the development of Al circuit boards                                                                                                                                                                                                                                                                                                           | 50 |

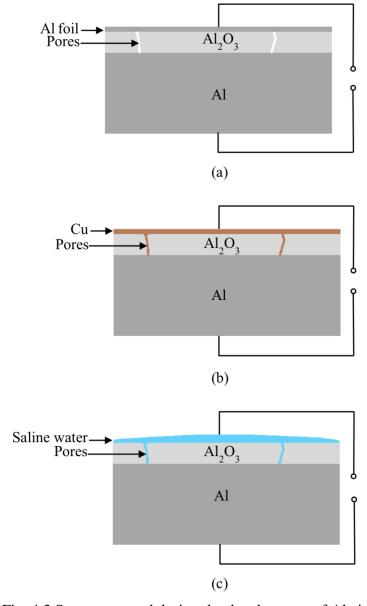

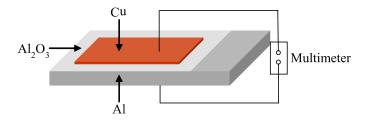

| Fig. 4.4 | Experimental setup to measure the electrical resistance of alumina layer grown on Al base                                                                                                                                                                                                                                                                             | 53 |

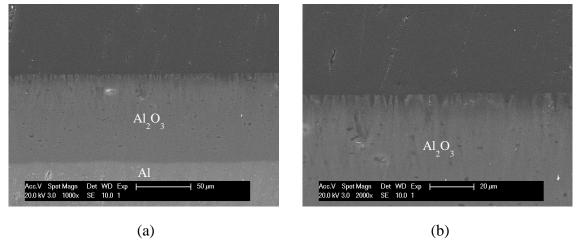

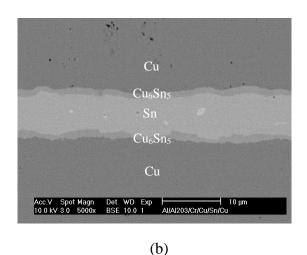

| Fig. 4.5 | Cross-section SEM images of alumina layer after the first anodization step: (a) $1000\times$ magnification, and (b) $2000\times$ magnification. The alumina layer is 80 $\mu$ m thick and pores are clearly seen in (b)                                                                                                                                               | 54 |

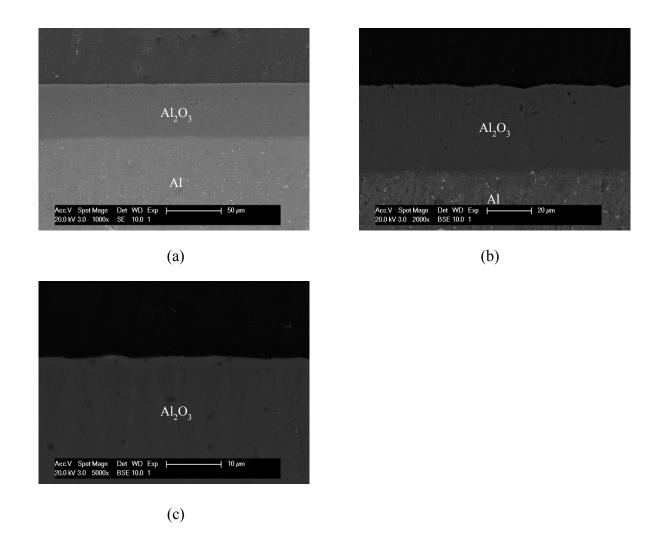

| Fig. 4.6 | Cross-section SEM image of alumina grown using the two-step anodization process: (a) $1000\times$ magnification, (b) $2000\times$ magnification and (c) $5000\times$ magnification. The alumina layer is 50 $\mu$ m thick and free of pores                                                                                                                           | 55 |

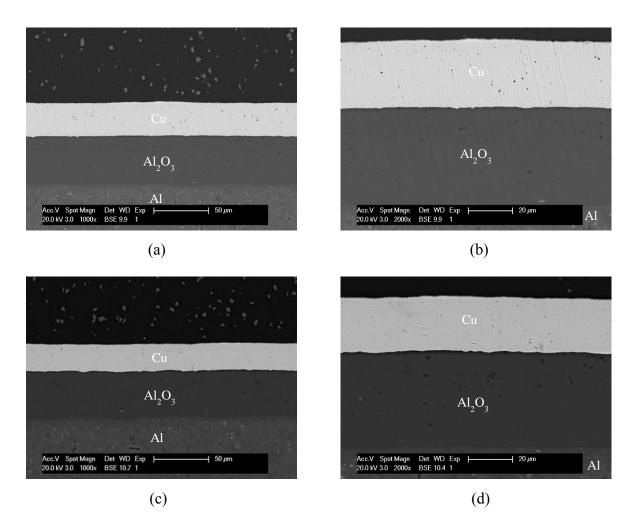

| Fig. 4.7 | Cross-section SEM images of an Al circuit board after test of 500 thermal cycles between -40 and +85 $^{\circ}$ C: (a) 1000× magnification, and (b) 2000× magnification. There is no visible change after the thermal cycling test                                                                                                                                    | 56 |

| Fig. 4.8 | Cross-section SEM images of Al circuit boards after storage at $250^{\circ}$ C for 10 hours: (a) $1000\times$ magnification, and (b) $2000\times$ magnification and 100 hours: (c) $1000\times$ magnification, and (d) $2000\times$ magnification, respectively. There is no visible change after the high temperature storage test                                   | 57 |

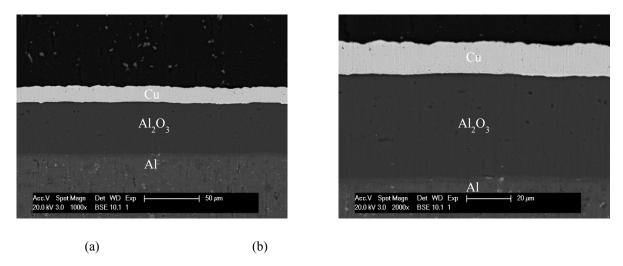

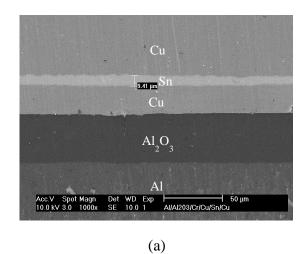

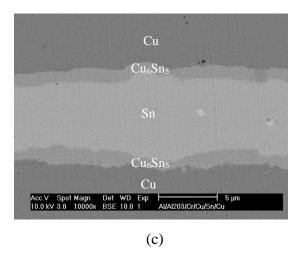

| Fig. 4.9 | Cross-section SEM images of Cu substrate bonded to an Al circuit board using fluxless tin at 240°C. The joint thickness is 9.4 $\mu$ m including Cu6Sn5 layers. The Cu substrate is 10 mm $\times$ 12 mm in size                                                                                                                                                      | 50 |

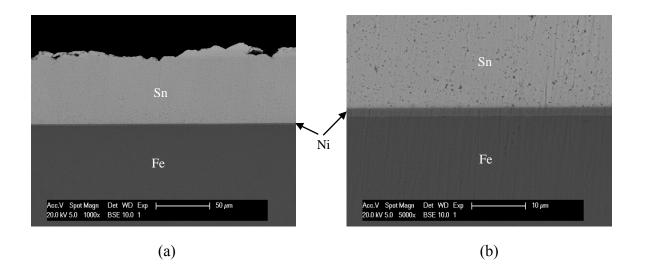

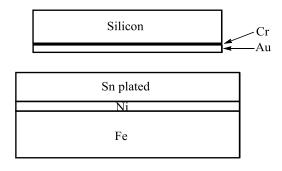

| Fig. 5.1 | Cross-section SEM images of a typical as-plated Fe substrate at (a) low magnification (1000×) and (b) high magnification (5000×). The substrate is electroplated with 1.5 $\mu$ m Ni and 70 $\mu$ m Sn                                          | 69 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 5.2 | Cross-section SEM images of sample A at (a) low magnification ( $1000\times$ ) and (b) high magnification ( $5000\times$ ). The sample is a Si chip bonded to Ni-plated Fe substrate with fluxless Sn at 240 °C with reflow time of 300 seconds | 69 |

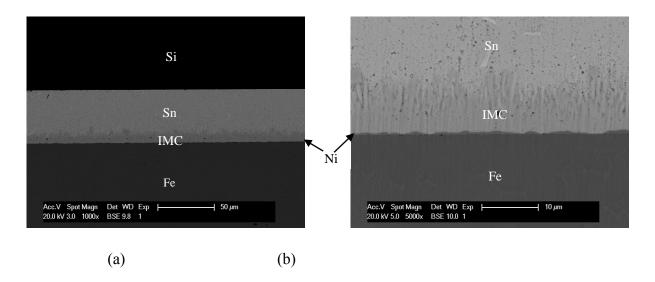

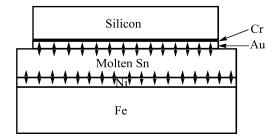

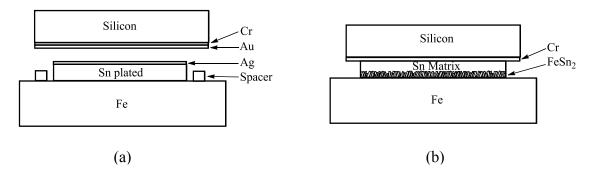

| Fig. 5.3 | Schematics illustrating the fluxless bonding mechanism                                                                                                                                                                                          | 71 |

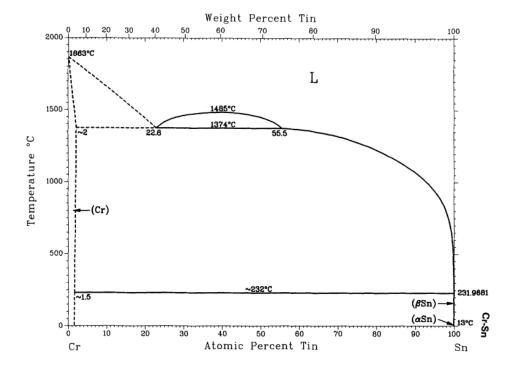

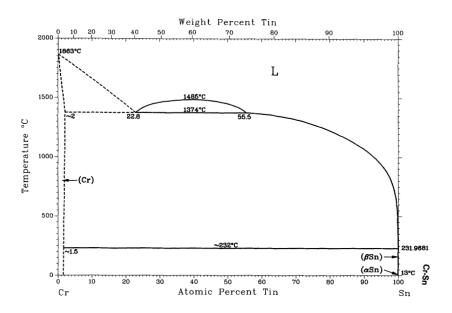

| Fig. 5.4 | The Cr-Sn binary phase diagram [8]                                                                                                                                                                                                              | 71 |

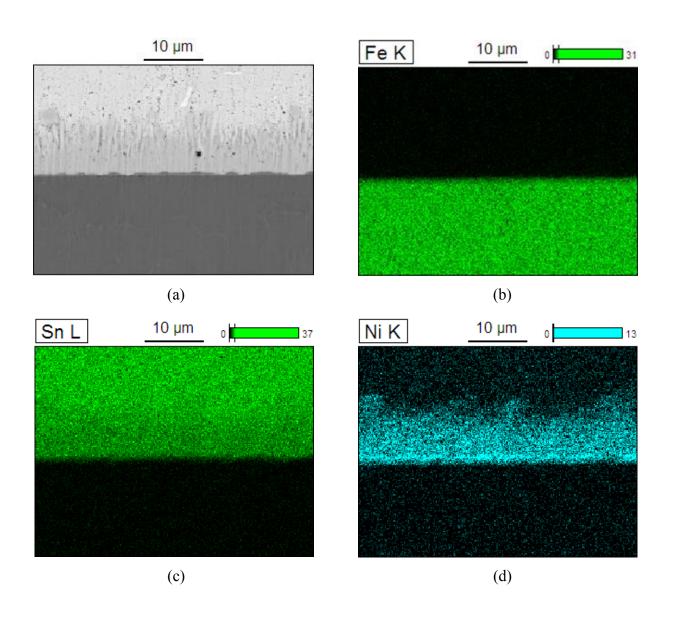

| Fig. 5.5 | Cross-section SEM images and element mappings at Sn/IMC/Ni of sample A. The Fe substrate was plated with 1.5 $\mu$ m Ni followed by 70 $\mu$ m Sn. The reflow time is 300 seconds during bonding                                                | 73 |

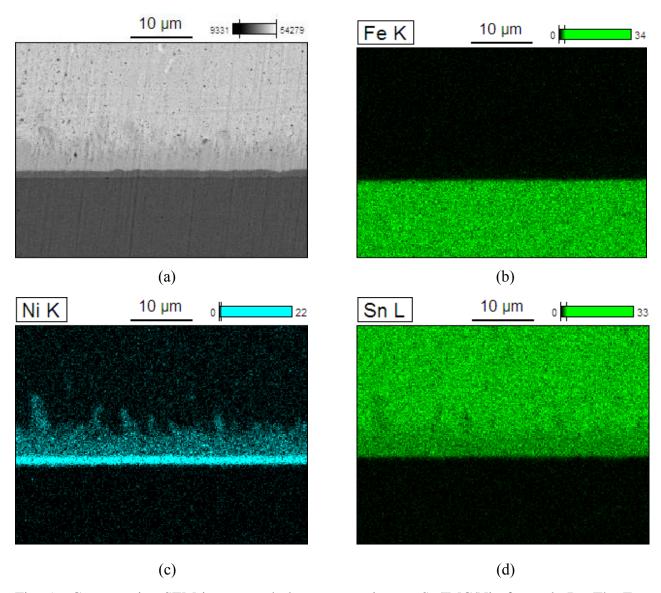

| Fig. 5.6 | Cross-section SEM images and element mappings at Sn/IMC/Ni of sample B. The Fe substrate was plated with 1.5 $\mu m$ Ni followed by 70 $\mu m$ Sn. The reflow time is 200 seconds during bonding                                                | 75 |

| Fig. 5.7 | Cross-section SEM images and element mappings at Sn/IMC/Ni of sample C. The Fe substrate was plated with 4.5 $\mu$ m Ni followed by 70 $\mu$ m Sn. The reflow time is 200 seconds during bonding                                                | 76 |

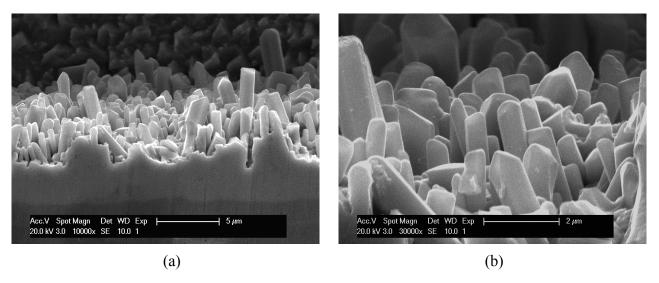

| Fig. 5.8 | SEM images of sample D showing the cross-section view of Ni3Sn4 IMC at (a) low magnification (10000×) and (b) high magnification (30000×). Sn was etched away to expose the IMC microstructure                                                  | 77 |

| Fig. 5.9 | SEM images of sample E showing the top view of $Ni_3Sn_4$ IMC at (a) low magnification (10000×) and (b) high magnification (30000×). Sn was etched away to expose the IMC microstructure                                                        | 77 |

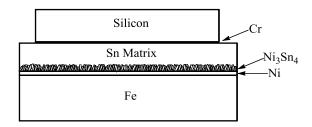

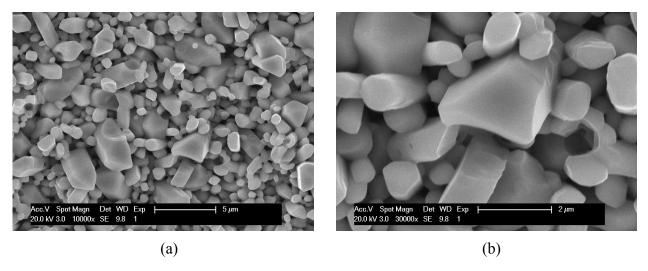

| Fig. 6.1 | Schematics illustrating: (a) Bonding structure and configuration and (b) Layer structure after bonding                                                                                                                                          | 84 |

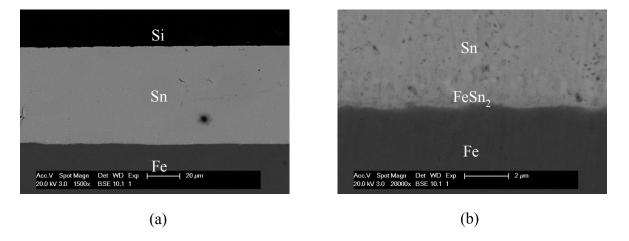

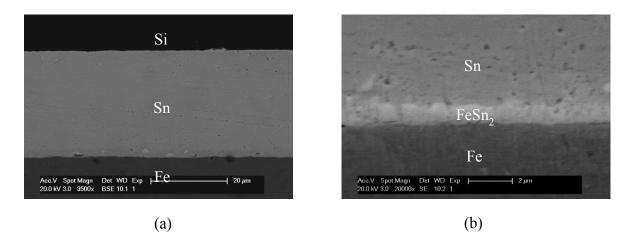

| Fig. 6.2 | Cross-section SEM images of the sample using 50 $\mu$ m spacers at (a) lower magnification (1500×) and (b) higher magnification (20000×) showing the Sn/Fe interface                                                                            | 85 |

| Fig. 6.3 | Cross-section SEM images of the sample using 30 $\mu$ m spacers at (a) lower magnification (3500×) and (b) higher magnification (20000×) showing the Sn/Fe interface                                                                            | 87 |

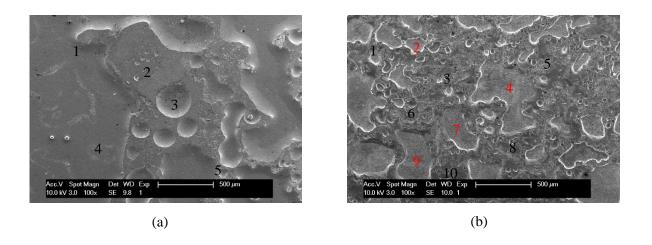

| Fig. 6.4 | Top-view SEM images of (a) sample 2 and (b) sample 4 on Fe substrate side after the shear tests. The chemical compositions of the marked regions are shown in Table 6.2 and Table 6.3                                                           | 88 |

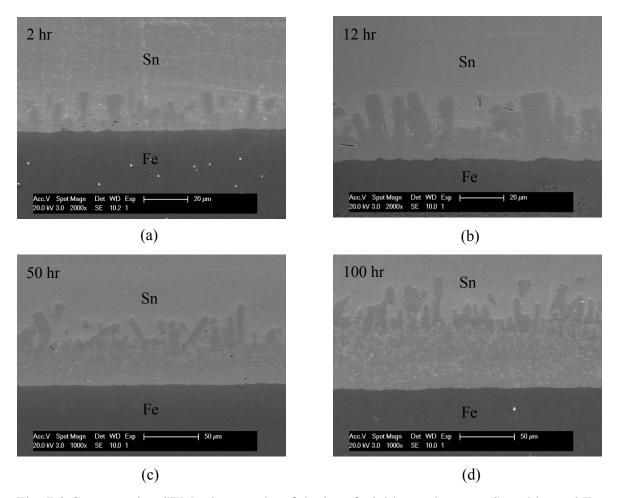

| Fig. 7.1 | Cross-section SEM micrographs of the interfacial layers between Sn solder and Fe metal substrates annealing at 250°C for (a) 2 hr, (b) 12 hr, (c) 50 hr and (d) 200 hr                                                                              | 96  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 7.2 | Cross-section SEM micrographs of the interfacial layers between Sn solder and Fe metal substrates annealing at 335°C for (a) 2 hr, (b) 12 hr, (c) 50 hr and (d) 100 hr                                                                              | 97  |

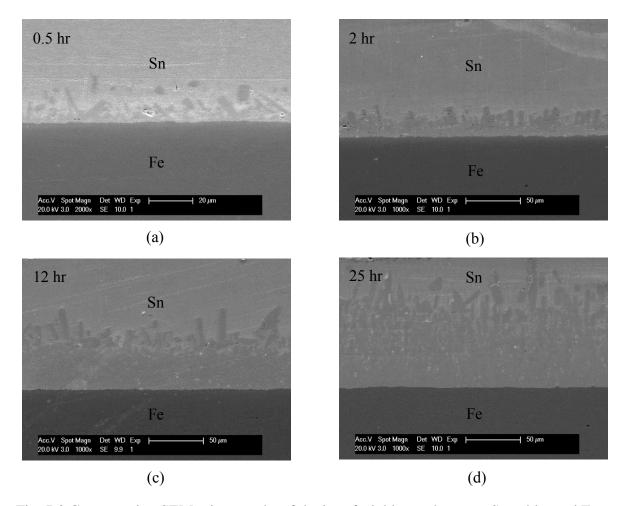

| Fig. 7.3 | Cross-section SEM micrographs of the interfacial layers between Sn solder and Fe metal substrates annealing at 400°C for (a) 0.5 hr, (b) 2 hr, (c) 12 hr and (d) 25 hr                                                                              | 98  |

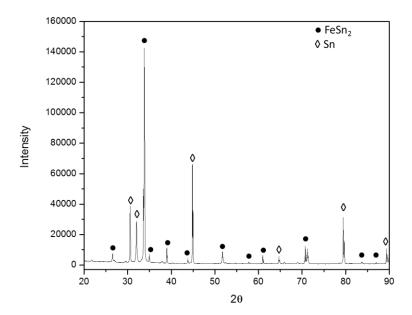

| Fig. 7.4 | X-ray diffraction pattern obtained from the top surface of the etched sample reacted at 400°C for 25 hours                                                                                                                                          | 99  |

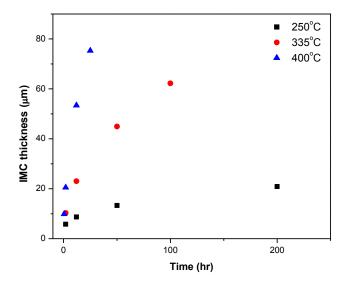

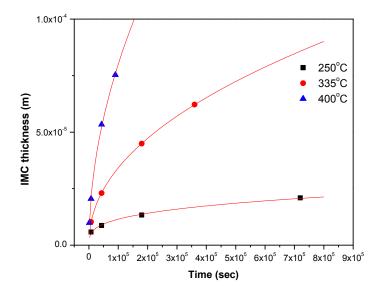

| Fig. 7.5 | Variation in the average thickness of the IMC with annealing time at 250°C, 335°C and 400°C                                                                                                                                                         | 100 |

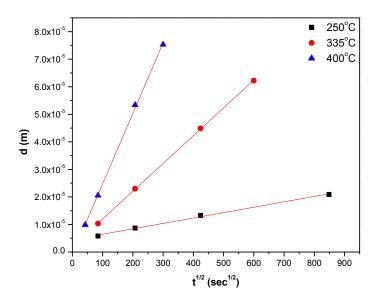

| Fig. 7.6 | Variation in the average thickness of the IMC as a function of the square root of annealing time at 250°C, 335°C and 400°C. The straight lines represent fits of the data by linear regression                                                      | 101 |

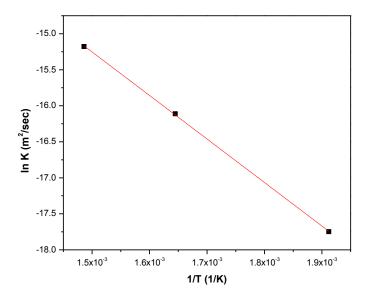

| Fig. 7.7 | Arrhenius plot for evaluating the activation energy for the growth of IMC. The straight line represents a fit of the data by linear regression                                                                                                      | 102 |

| Fig. 7.8 | Variation in the average thickness of the IMC with annealing time at $250^{\circ}$ C, $335^{\circ}$ C and $400^{\circ}$ C. The curves represent fits of the data by regression with the equation $d = kt^n$                                         | 103 |

| Fig. 8.1 | The Cr-Sn binary phase diagram [22]                                                                                                                                                                                                                 | 112 |

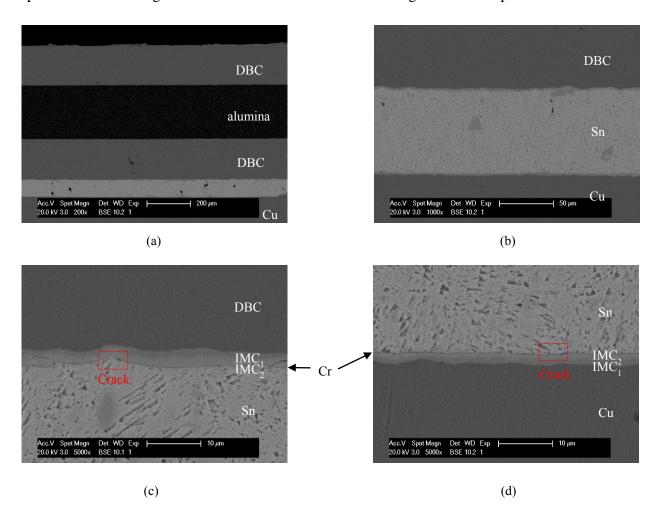

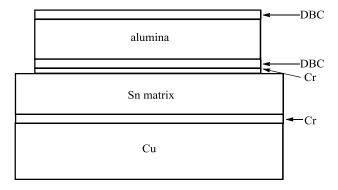

| Fig. 8.2 | Cross-section SEM images of sample A described in Table I at (a) low magnification (200×), (b) low magnification (1000×), (c) high magnification (5000×) at DBC/Cr/Sn interface, and (d) high magnification (5000×) at Sn/Cr/Cu substrate interface | 115 |

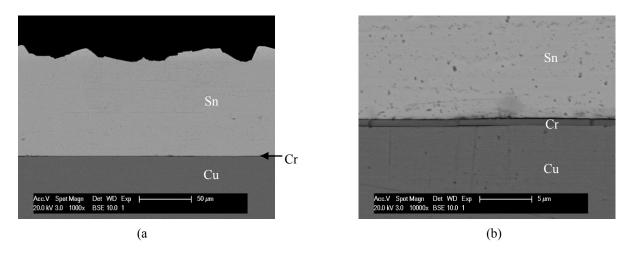

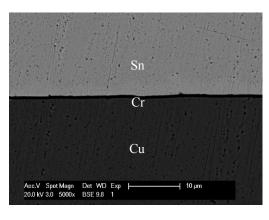

| Fig. 8.3 | Cross-section SEM images of a typical as-plated Cu substrate at (a) low magnification (1000×) and (b) high magnification (10000×). The substrate was E-beam deposited with 500 nm Cr and 100 nm Cu and was electroplated with 30 $\mu m$ Sn         | 117 |

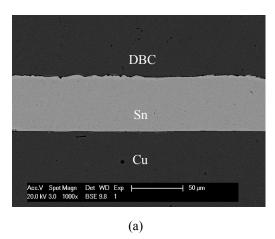

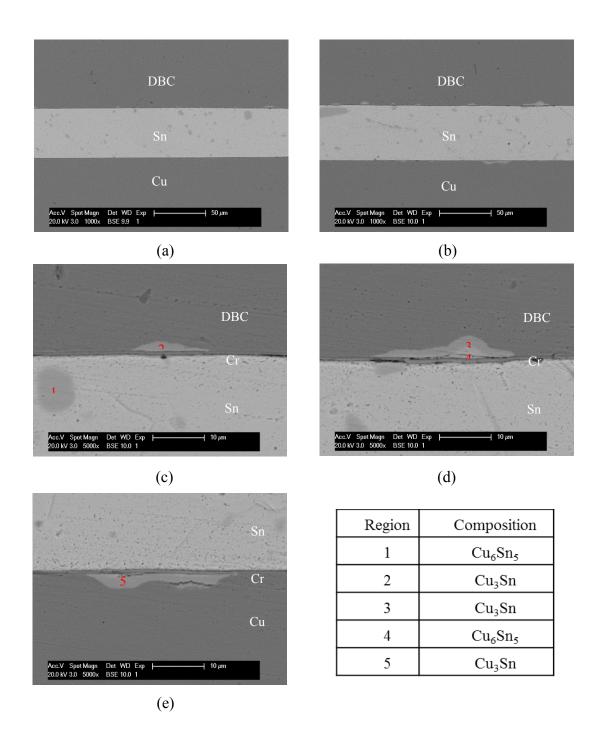

| Fig. 8.4 | Cross-section SEM images of sample B described in Table I at (a) low magnification (1000×), (b) high magnification (5000×) at DBC/Cr/Sn interface, and (c) high magnification (5000×) at Sn/Cr/Cu substrate interface                               | 119 |

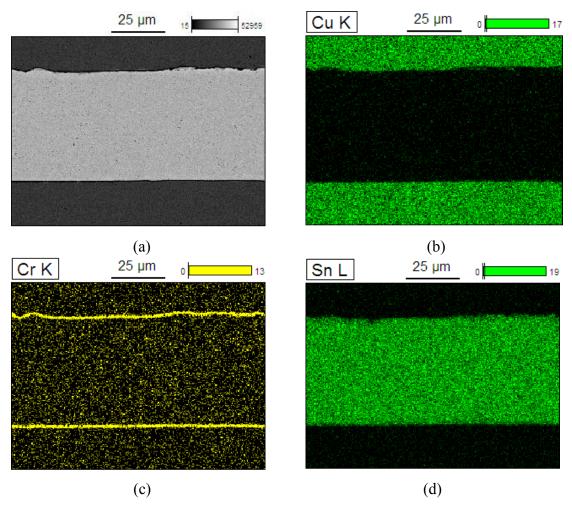

| Fig. 8.5 | Cross-section SEM image and element mappings of sample B described in Table 8.1                                                                                                                                                                                                                                                                                                                                       | 119 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

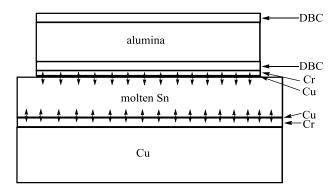

| Fig. 8.6 | Schematics illustrating the fluxless bonding mechanism                                                                                                                                                                                                                                                                                                                                                                | 120 |

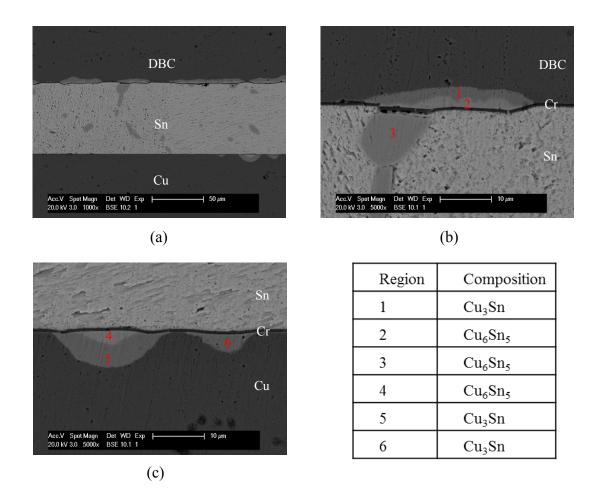

| Fig. 8.7 | Cross-section SEM images of sample C described in Table I at (a) low magnification (1000×) of the portion where IMC formation occurs only at DBC/Cr/Sn interface, (b) low magnification (1000×) of the portion where IMC formation occurs at DBC/Cr/Sn and Sn/Cr/Cu substrate interfaces, (c-d) high magnification (5000×) at DBC/Cr/Sn interface, and (e) high magnification (5000×) at Sn/Cr/Cu substrate interface | 122 |

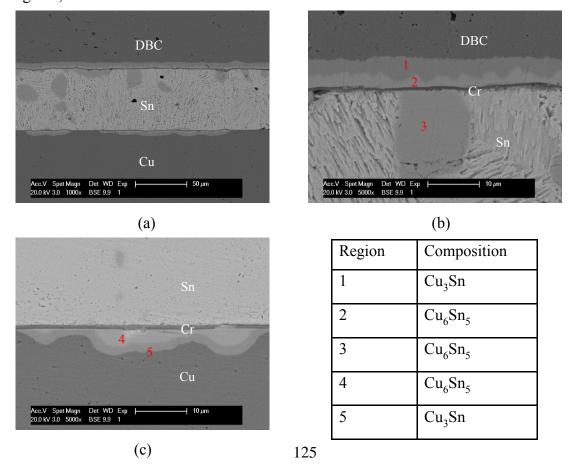

| Fig. 8.8 | Cross-section SEM images of sample D described in Table 8.1 at (a) low magnification (1000×), (b) high magnification (5000×) at DBC/Cr/Sn interface, and (c) high magnification (5000×) at Sn/Cr/Cu substrate interface                                                                                                                                                                                               | 124 |

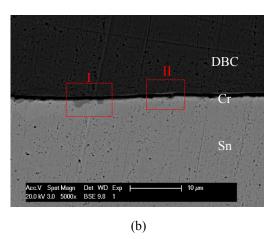

| Fig. 8.9 | Cross-section SEM images of sample E described in Table 8.1 at (a) low magnification (1000×), (b) high magnification (5000×) at DBC/Cr/Sn interface, and (c) high magnification (5000×) at Sn/Cr/Cu substrate interface                                                                                                                                                                                               | 126 |

# LIST OF TABLES

|           |                                                                                                                                                                           | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1.1 | Four basic requirements for oxidation-free fluxless bonding technology                                                                                                    | 6    |

| Table 3.1 | EDX data of three regions marked as 1, 2 and 3 at the Sn/IMCs/Cu interface, as shown in Fig. 3.2(b)                                                                       | 28   |

| Table 3.2 | EDX data of three regions marked as 1, 2 and 3 at the Si/Sn/IMCs/Cu interface shown in Fig. 3.3(b)                                                                        | 30   |

| Table 3.3 | EDX data of two regions marked as 1 and 2 at the Si/IMCs/Cu interface shown in Fig. 3.5(c)                                                                                | 33   |

| Table 3.4 | EDX data of three regions marked as 1, 2 and 3 at the Sn/IMCs/Cu interface shown in Fig. 3.7(b)                                                                           | 36   |

| Table 3.5 | Fracture forces, shear strengths and fracture modes of the six samples bonded using 50 $\mu m$ spacer after the shear tests                                               | 38   |

| Table 4.1 | Measured resistance of alumina layers grown by various anodization processes and electrolytes on Al boards. The area of alumina layer is $20~\text{mm}\times20~\text{mm}$ | 53   |

| Table 5.1 | Designs of samples of Si chip bonded to Ni-plated Fe substrate using fluxless Sn at 240 °C reflow temperature                                                             | 67   |

| Table 6.1 | Fracture forces and shear strengths of the six samples bonded using 30 µm spacer after the shear tests                                                                    | 87   |

| Table 6.2 | EDX analysis data of five regions marked as 1, 2, 3, 4 and 5, as shown in Fig. 6.4(a)                                                                                     | 89   |

| Table 6.3 | EDX analysis data of ten regions marked from 1 to 10, as shown in Fig. 6.4(b)                                                                                             | 89   |

| Table 8.1 | Samples of DBC alumina substrate bonded to Cu substrate using fluxless Sn at 240°C reflow temperature                                                                     | 114  |

| Table 8.2 | Typical CTE values of the materials                                                                                                                                       | 116  |

#### **ACKNOWLEDGMENTS**

I would like to express my deepest gratitude to my advisor, Professor Chin C. Lee, for his guidance, mentorship and support. His working style greatly influences how I conduct research. He teaches me to review the fundamental theories and pay attention to the details when conducting research. In addition, I would also like to thank him for his nominations for numerous fellowships and the financial support from. Without his mental and financial support, it could never have been possible for me to complete my PhD. I would like to extend my gratefulness to my committee members: Professor Farghalli Mohamed, Professor James Earthman, Professor Frank G. Shi, Professor Mark Bachman, and Professor Glenn Healey, for their valuable suggestions on my research.

My appreciation also goes to Dr. Chu-Hsuan Sha and Dr. Wen-Pei Lin. Without their guidance, I could not have learned all experimental skills so quickly. I also appreciate their valuable discussions and comments even after their graduation. Many thanks go to my lab mates, Yuan-Yun, Yi-Ling, Yongjun, Ja-Ming and Shao-Wei, for their kind support. I also want to thank INRF staff, Jake, Vu, Mo, David and Li-Feng for their assistance on conducting experiments. I have to show my greatest gratitude to my friends at UCI, Li-Wen, Meg, Huang-Hsiang, Shih-Kai and Bryce, for the bonded friendship and kind support. I would like to extend my sincere gratitude to my parents and sisters for their unconditional love and support. Their encouragement is the strongest driving force for overcoming difficulties. In my heart, my family always occupies an important part. This dissertation could never been completed without their love and support.

#### **CURRICULUM VITAE**

#### Shou-Jen Hsu

2005 Bachelor of Science Department of Chemistry National Taiwan University, Taipei, Taiwan 2006-2008 Teaching Assistant Department of Materials Science and Engineering National Chiao Tung University, Hsinchu, Taiwan 2008 Master of Science in Engineering, Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan 2009-2010 Research Assistant Department of Materials Science and Engineering National Chiao Tung University, Hsinchu, Taiwan 2011-2014 Graduate Student Researcher Materials & Manufacturing Technology Department of Electrical Engineering and Computer Science University of California at Irvine, Irvine, CA, USA 2013 **Teaching Assistant** Department of Electrical Engineering and Computer Science Course: Electrical Engineering Analysis University of California at Irvine, Irvine, CA, US

Doctor of Philosophy in Engineering

Materials & Manufacturing Technology

University of California at Irvine, Irvine, CA, US

2015

#### **PUBLICATIONS**

#### Journal Articles

- 1. S.-J. Hsu and C. C. Lee, "Growth Kinetics of Intermetallic Compounds between Sn and Fe Liquid-Solid Reaction Couples," submitted

- 2. S.-J. Hsu and C. C. Lee, "Fluxless Bonding of Si Chips to Low Carbon Steel Boards Using Electroplated Sn Solder," submitted

- 3. S.-J. Hsu, C.-H. Sha and C. C. Lee, "Fluxless Bonding of Si chips to Aluminum Boards Using Electroplated Sn Solder," Journal of Materials Science-Materials in Electronics, vol. 25, pp. 3276-3284, Aug. 2014

- 4. S.-J. Hsu and C. C. Lee, "Fluxless Tin Bonding Process with Suppressed Intermetallic Growth", IEEE Transactions on Components Packaging and Manufacturing Technology, vol. 4, pp. 551-559, Apr. 2014

- 5. C. C. Lee, S.-J. Hsu, and Y.-Y. Wu, "Fluxless Tin and Silver-Indium Bonding Processes for Silicon onto Aluminum," Journal of Electronic Materials, vol. 43, pp. 9-15, Jan. 2014

- 6. S.-J. Hsu, C.-H. Sha, and C. C. Lee, "Initial Success on Aluminum Circuit Board Technology," IEEE Transactions on Components Packaging and Manufacturing Technology, vol. 3, pp. 1625-1631, Oct. 2013

- 7. S.-J. Hsu and C. C. Lee, "Fluxless Tin Bonding of Silicon Chips to Iron Substrates," Journal of Materials Science-Materials in Electronics, vol. 24, pp. 2890-2896, Aug. 2013

#### Published Conference Proceedings and Conference Presentations

- 1. S.-J. Hsu and C. C. Lee, "Bonding of SiC chips to copper substrates using Ag-In system" in IEEE 65th Electronic Components and Technology Conference (ECTC), 2015, accepted

- 2. S.-J. Hsu and C. C. Lee, "Fluxless Tin Bonding of Silicon Chips to Iron," in IEEE 63<sup>rd</sup> Electronic Components and Technology Conference (ECTC), 2013, pp. 2276-2279

- 3. S.-J. Hsu and C. C. Lee, "A Monolithic Aluminum Circuit Board Structure," in IEEE 63rd Electronic Components and Technology Conference (ECTC), 2013, pp. 1346-1349

- 4. S.-J. Hsu and C. C. Lee, "Surface Finish and Treatment on Iron Substrates for Electronic Packaging," in 2013 IEEE International Symposium on Advanced Packaging Materials (APM), 2013, pp. 246-257

- 5. S.-J. Hsu and C. C. Lee, "The Fluxless Soldering Process without Intermetallic Compounds," in 2013 IEEE International Symposium on Advanced Packaging Materials (APM), 2013, pp. 44-51

6. S.-J. Hsu, C.-H. Sha, and C. C. Lee, "Fluxless Tin Bonding of Silicon Chips to Aluminum Substrates," in IEEE 62nd Electronic Components and Technology Conference (ECTC), 2012, pp. 1136-1139

#### ABSTRACT OF THE DISSERTATION

Fluxless Tin Bonding Processes with Intermetallic Study and Aluminum Circuit Board

Technology

by

Shou-Jen Hsu

Doctor of Philosophy in Engineering

University of California, Irvine, 2015

Professor Chin C. Lee, Chair

This research starts with developing fluxless bonding process using electroplated Sn solder between Si chip and Al substrate. The joint thickness was controlled either by bonding pressure or by incorporating Cu spacers.  $Cu_6Sn_5$  and  $Cu_3Sn$  IMCs are observed at Sn/Cu interface. A new two-step anodization process is also introduced to grow high quality alumina on Al boards and coat thick Cu layer over the alumina to produce a Cu/alumina/Al insulated metal substrate (IMS) structure. The measured resistance and breakdown voltage of the as-formed 50  $\mu$ m anodic alumina layer is larger than 40 M $\Omega$  and 600 VDC, respectively. To test the reliability of the boards, they were put through 500 cycles of thermal cycling test and high temperature storage test. To ensure its compatibility with soldering operations, Cu substrates were bonded to the Al boards using a fluxless tin process.

The fluxless bonding process is also applied to bond Si chips to low carbon steel substrates electroplated with Ni with desired thickness. Ni<sub>3</sub>Sn<sub>4</sub> is the only IMC formed at the Sn/Ni interface. In order to compare the result to the case without using underbump metallurgy. Sn was electroplated over low carbon steel directly and then Si was bonded to the low carbon steel

substrate. Sn solder layer was bonded to Fe substrate by forming FeSn<sub>2</sub> at the Sn/Fe boundary. These results suggest that Sn-Fe reaction system should be another promising bonding pair candidate that could mitigate excessive IMC thickness. The liquid Sn/solid Fe reaction couples were fabricated and annealed at different temperatures. The growth kinetics of FeSn<sub>2</sub> was modeled by parabolic law and empirical power law.

We finally move to develop a fluxless bonding process with suppressed IMC formation. According to Cr-Sn phase diagram, there is no IMC formation in Cr/Sn system. Cr is thus selected as the barrier metal. Several bonding experiments have been performed and the preliminary results show that high quality Sn joints could be produced with little IMC formation before high temperature aging.

## **Chapter One**

### Introduction

## 1.1 Electronic Packaging

To make integrated circuit (IC) chips operational, they need to be bonded and connected to packages using appropriate bonding medium. The packages along with the bonding medium serve the purposes of power distribution, signal distribution, heat dissipation, and protection for IC chips. To perform well, the packages are commonly bonded to solders due to the natures of high thermal conductivities, high electrical conductivities, and the low processing temperature. In current electronic packaging industries, the reliability of solder joints is a key design factor. Compared to extremely reliable solid-state devices, having the failure rate in parts-per-million (ppm), solder joints or interconnections have much higher failure rate, leading to short life time of products [1]. This short life time results from the use of flux in conventional soldering processes and the shear stress developed when bonding materials with mismatch in thermal expansion coefficient.

Another potential issue arises as the chip size continues to scale down. When more and more transistors are placed on the same Si chip size, larger pin-out numbers and smaller solder joints are inevitable. According to International Technology Roadmap for Semiconductors (ITRS),

by 2018, the pitch in flip-chip interconnects will become smaller than 70 µm for high performance applications [2]. Two problems occur. The first is increase in shear strain. The aspect ratio of flip-chip joints is constrained to 0.7 because it goes through molten phase in the reflow process. Therefore, smaller joints become shorter as well, resulting in larger shear strain arising from CTE mismatch between Si chips and package substrates. The second is increase in stress in the joints. Since intermetallic (IMC) thickness in the joint does not scale down with joint size, ratio of IMC thickness to joint height increases. This further enlarges the shear stress because the IMC does not deform as the soft solder does to accommodate CTE mismatch. To solve the problems mentioned above, solid state bonding technique is investigated.

In what follows, the soldering process and fluxing action are first reviewed. Fluxless bonding technique is then discussed. The dissertation outline is given at last.

## 1.2 The Soldering Process

Different from adhesive bonding and direct bonding techniques, soldering bonding relies on the chemical reaction between solders and as-bonded parts. Commonly used solder alloys contain elements that have low melting temperatures such as tin (Sn), indium (In), and bismuth (Bi). In the soldering process, the solder materials melt and react with to-be-bonded parts to form

intermetallic compounds (IMCs). Take Sn-based lead-free solder on copper as an example, during soldering process, solder melts and wets copper. The molten Sn solder dissolves copper (Cu) atoms to form solid Cu<sub>6</sub>Sn<sub>5</sub> IMC at the interface as portrayed in Fig. 1.1. This Cu<sub>6</sub>Sn<sub>5</sub> IMC layer joints solder and copper together. Thus, the intermetallic formation is an essential reaction to achieve bonding in nearly all soldering systems.

Fig. 1.1 A solder joint needs intermetallic formation to be achieved

## 1.3 The Fluxing Action

To achieve soldering joint formation, the chemical reaction that forms IMCs between molten phase and substrate need to occur. However, solder and substrate metals have a native oxide layer on their surface. These oxide layers usually have melting temperature higher than the soldering temperature, i.e. the melting temperatures of SnO and SnO<sub>2</sub> are 1,080°C and 1,630°C, respectively. They are also lighter than solders. During reflow process, the oxide layer does not melt and forms a thin film on the surface of molten solders. This oxide layer shields the molten phase from reacting with substrate metals. The joint, thus, is not formed unless the oxide layer is

removed. The flux containing resin acids mainly react with metal oxides such as CuO and SnO as follows,

$$2 \text{ R-COOH} + \text{CuO} \rightarrow (\text{R-COO})_2\text{Cu} + \text{H}_2\text{O}$$

$$2 \text{ R-COOH} + \text{SnO} \rightarrow (\text{R-COO})_2 \text{Sn} + \text{H}_2 \text{O}$$

where R represents the carboxyl residue. For the case of abietic acid,  $R = C_{19}H_{29}$ . In above equations, the Cu and Sn oxides convert into salts and water. As exhibited in Fig. 1.2, the fresh solder and base metals can contact intimately to form IMCs during reflow process once the metal oxides are removed by fluxing actions. As a result, the joint is achieved. During fluxing action, residues are accompanied, which are known to cause voids and uneven thickness in joints, leading to degrading the performance of device [3, 4]. In addition, some electronic devices are restricted from using flux such as optoelectronic devices, medical devices, and laser diodes because residues contaminate and corrode devices [5]. The fluxless process, thus, become very critical to improve reliability in the electronic packaging.

Fig. 1.2 Molten flux converts oxides into salts to expose fresh solder and fresh base metal, and to

## 1.4 Fluxless Bonding Technique

There are several approaches to achieve fluxless bonding. The first method is using acid vapor, acetic or formic acid, to reduce metal oxides [8-10]. Fundamentally, this method is similar to the conventional soldering process except that vapor chemicals rather than liquid chemicals are used. Acid vapor is known to be corrosive to devices as well. Another fluxless method is to treat the solder by fluorine (F) to convert tin oxide into tin oxyfluoride which can be dissolved by molten solder. The third method, invented by our group, is providing oxidation-free environment from solder manufacture to joint formation [11-13]. During the entire process, solders are prevented from oxidation. Table 1.1 lists the four requirements to prevent oxidation. First, solder materials should be fabricated in an oxidation-free environment such as vacuum deposition or electroplating method. Second, there should be a thin capping layer, usually gold (Au) or silver (Ag) layer, on the solder materials to protect inner solders from oxidation when solders are exposed to air. During the reflow process, this thin capping layer should dissolve and become part of joints. The fresh solders can react with base metals to form IMCs. Finally, the bonding process should be performed in vacuum, inert gas, or H<sub>2</sub> environment to inhibit oxidation. This oxidation-free fluxless soldering technology was first reported by our group in 1995 [14], and has been applied to developing various fluxless processes based on Sn-Au, Sn-Cu, Sn-Ag, Sn-Bi, Sn-In, In-Au, In-Cu, In-Ag binary systems and In-Pb-Au ternary system [12-18].

The purpose of this dissertation is to produce solder joint between semiconductor dies or ceramic boards and commonly used metal substrates. Pure Sn is used as the bonding medium. The advantage of pure Sn system is that Sn is soft and ductile. It can endure large shear strain caused by CTE mismatch between semiconductor dies and substrates. The dissertation outline is presented in next section.

Table 1.1 Four basic requirements for oxidation-free fluxless bonding technology

| Process                     | Approach                              |

|-----------------------------|---------------------------------------|

| Solder manufacture          | Electroplating or vacuum deposition   |

| A capping layer over solder | Ag or Au                              |

| Dealing with capping layer  | Dissolution                           |

| Bonding environment         | Vacuum or inert gas or H <sub>2</sub> |

#### 1.5 Dissertation Outline

In this dissertation, fluxless bonding techniques using electroplated Sn system are employed for various bonding designs and a new anodization method is developed to demonstrate the possibility and advantages of the aluminum circuit board technology. The materials fabrication, bonding furnace setup and process flow, and anodization process flow are described in Chapter 2.

In Chapter 3, a fluxless bonding process was developed to bond Si chip to Al boards using Cu as underbump metallurgy (UBM). This process surmounts the huge coefficient of thermal expansion (CTE) mismatch between Si (3 ppm/°C) and Al (23 ppm/°C). The solder joint thickness was controlled either by bonding pressure of 0.6, 2.5 and 32 psi or by incorporating Cu spacers of 50 μm in thickness. Scalloped-shaped Cu<sub>6</sub>Sn<sub>5</sub> and thin Cu<sub>3</sub>Sn intermetallic compounds (IMC) were formed at the Sn/Cu interface. Despite the large CTE mismatch, the joints are still well bonded. The bonding strength of the joint was evaluated by shear test. All the samples pass the strength requirement specified in MIL-STD-883H method 2019.8.

In Chapter 4, a novel Al circuit board technology fabricated using two-step anodization method and Cu electroplating was proposed and designed. Electrical resistance and breakdown voltage of the 50  $\mu$ m anodic alumina layer were measured as > 40 M $\Omega$  and 600 VDC, respectively. The reliability tests on the Al circuit board were also conducted. The samples pass 500 cycles of thermal cycling test between -40°C and +85°C and 100 hours of high temperature storage test at 250°C. Cu substrate was also successfully bonded to the Al circuit board using electroplated Sn to ensure its compatibility with soldering operation.

In Chapter 5, a fluxless process of bonding Si chip to low carbon steel (Fe) using nickel (Ni) as underbump metallurgy was developed. The choice of Ni comes from the general idea that Ni is thought to possess slower rate of reaction with Sn. The reaction between Ni and Sn was

studied by varying the electroplated Ni UBM thickness and reflow time. It is observed that Ni<sub>3</sub>Sn<sub>4</sub> is the only IMC formed at the Sn/Ni interface. To investigate the microstructure and morphology of the Ni<sub>3</sub>Sn<sub>4</sub> IMC, the bulk of Sn was etched away to reveal the 3D microstructure.

In order to compare the result in Chapter 5 to the bonding of Si chip to low carbon steel

without using UBM, Si chip was bonded directly to Sn-electroplated Fe substrate. The results were reported in Chapter 6. It is shown that FeSn<sub>2</sub> is the only IMC phase observed at the Sn/Fe interface. The IMC thickness is only 1.1 to 1.5 μm. This suggests that Sn-Fe reaction system should be another promising bonding pair candidate that could mitigate excessive IMC thickness.

In Chapter 7, the growth kinetics of FeSn<sub>2</sub> IMC between Sn and Fe liquid-solid reaction couple was studied. The growth kinetics of FeSn<sub>2</sub> was modeled by parabolic law and empirical power law. Based on the models, the growth constants, activation energy and time exponents were established from the data coming from different annealing temperatures.

In Chapter 8, a fluxless bonding process between direct-bonded Cu (DBC) alumina substrate and Cu substrate was developed with suppressed IMC formation at the bonding interface. The fundamental concept is to use Cr as the barrier layer between Sn and Cu. Several bonding experiments have been performed and the preliminary results show that high quality Sn joints could be produced with a little IMC formation before high-temperature aging. After aging at homologous temperature of 0.9 of Sn for 100–200 hours, Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn IMCs are formed

locally at some microcracks or pinholes on the Cr layer. They are caused by the penetration of molten Sn through microcracks or pinholes and reaction with the underlying Cu.

In Chapter 9, a summary is given to point out important conclusions in this dissertation.

## 1.6 References

- R. R. Tummala, ed., Fundamentals of Microsystems Packaging, New York: McGraw-Hill, pp.21, 2001

- International Technology Roadmap for Semiconductors, 2005 Ed, Assembly and Packaging,

2005

- K. Mizuishi, M. Tokuda, and Y. Fujita, "Fluxless and substantially voidless soldering for semiconductor chips," IEEE Electronic Component Conference, pp.330, Los Angeles, CA, May 9-11, 1998

- G. Humpston and D. M. Jacobson, "Fluxless soldering processes," Advanced Materials & Processes, 162, pp.35, 2004

- 5. Wei Lin and Y. C. lee, "Study of fluxless soldering using formic acid vapor," IEEE Trans. Advanced Packaging, 22, pp. 592-601, Nov. 1999

- Chin C. Lee and William W. So, "Fluxless bonding and soldering technology," Proc. International Electronic Devices and Materials Symposia, pp.318-326, Tainan, Taiwan, Dec. 20-23, 1998

- 7. William S. So and Chin C. Lee, "A Fluxless process of fabricating In-Au joints on copper substrates," IEEE Trans. Components and Packaging Technology, 23, pp. 377-382, June 2000

- 8. N. Koopman, S. Bobbio, S. Nangalia, J. Bousaba, B. Peikarski, "Fluxless soldering in air and nitrogen," Proc. IEEE Electronic Components and Technology Conference, pp. 595-605, Orlando, Florida, June 2-4, 1993

- 9. P. A. Moskowitz, H. L. Yeh, and S. K. Ray, "Thermal dry process soldering," J. Vac. Sci. Technol., A4, pp.838, 1986

- 10. Wei Lin and Y. C. lee, "Study of fluxless soldering using formic acid vapor," IEEE Trans. Advanced Packaging, 22, pp. 592-601, Nov. 1999

- K.-M. Chu, J.-S. Lee, H. S. Cho, H.-H. Park, and D. Y. Jeon, "A fluxless flip-chip bonding for VCSEL arrays using silver-coated indium solder bumps," IEEE Trans. Electronics Packaging Manufacturing, 27, pp.246, 2004

- G. Matijasevic, Y.-C. Chen and C. C. Lee, "Copper-tin multilayer composite solder for fluxless processing," International J. of Microcircuits and Electronic Packaging, 17, 108-117, 2nd Otr.1994

- 13. R. W. Chuang, D. Kim, J. Park, and C. C. Lee, "A fluxless process of producing tin-rich gold-tin joints in air," IEEE Trans. Components and Packaging Technology, 27, pp.177-181, March, 2004

- C. C. Lee, C. Wang, and G. Matijasevic, "A new bonding technology using gold and tin multilayer composite structures," IEEE Trans. Components, Hybrids and Manufacturing Technology, 14, pp.407-412, 1991

- C. C. Lee, C. Wang, G. Matijasevic, "Gold-indium alloy bonding below the eutectic temperature," IEEE Trans. Components, Hybrids and Manufacturing Technology, 16, pp.331-316, 1993

- 16. C. C. Lee and Y.-C. Chen, "Indium-copper multilayer composite for fluxless oxidation-free bonding," Thin Solid Film, 283, pp.243-246, 1996

- 17. Y.-C. Chen, W. W. So, and C. C. Lee, "A fluxless bonding technology using indium-silver multilayer composites" IEEE Trans. Components, Packaging, and Manufacturing Technology, Part A, 20, pp.46-51, 1997

- 18. J. Kim and C. Lee, "Fluxless Sn-Ag bonding in vacuum using electroplated layers," Materials Science and Engineering A, 448, pp.348-.50, 2007

# **Chapter Two**

## **Experiment Setup and Techniques**

#### 2.1 Materials Fabrication

In the electronic packaging field, vacuum deposition, stencil printing, and electroplating method are three common methods to fabricate solder layers. In our cases, electron beam evaporation and electroplating are the two techniques we use for conducting experiments.

## 2.1.1 Electron Beam Evaporation

Electron beam (e-beam) evaporation is a form of physical vapor deposition (PVD). PVD processes are commonly used for the deposition of metallic films, because they can be performed at lower process risk and cheaper in regards to materials cost that Chemical Vapor Deposition (CVD). In e-beam evaporation, a target anode is bombarded with an electron beam given off by a charged tungsten filament under high vacuum. The electron beam causes atoms from the target to transform into the gaseous phase. The gas molecules are able to evaporate freely and then condense on all surfaces inside the chamber. The entire process takes place inside of a vacuum chamber and multi-layer coatings can be deposited in one duty cycle.

The vacuum deposition provides clean, uniform, and well thickness controlled metal layers. In one high vacuum cycle, usually 2×10<sup>-6</sup> to 3×10<sup>-6</sup> torrs, up to three or four metal layers can be deposited. These metal layers are efficiently prevented from oxidations. However, during deposition, the substrates undergo high temperature, which may incur unwanted interdiffusion and reaction between deposited metal layers and also cause breakage when bonding CTE mismatch materials. In addition, it is difficult to produce metal layers thicker than 10µm using vacuum deposition method, and to build and maintain a vacuum system is costly. In our experiment, e-beam deposition is used to produce thin metal films, serving as adhesion layers and capping layers.

Stencil printing and electroplating method, thus, become economical alternatives. Stencil printing is a wide used thick-film process for applying films of viscous solder pastes on substrates at room temperature. The typical stencil printing process starts with an UBM. Solder paste is stencil printed on the UBM, and then reflowed to form solder bumps. Since solders are exposed to air and get oxidized during manufacture and printing processes, flux is employed during the reflow process. As described in Section 1.3, joint quality degrades due to the usage of flux. In this research, the electroplating process is adapted to produce solder layers.

## 2.1.2 Electroplating

Electroplating is a process of depositing a metal layers on a conductive substrate immersed in an electrolytic bath composed of a solution of the salt of the metal to be plated. The deposition is driven by external DC current. The anode is made of the metal to be plated, and the cathode connects to the substrate. Take silver (Ag) electroplating as an example. At the anode, Ag atoms are dissolved by  $Ag \rightarrow Ag^+ + e^-$ , and the reduction reaction at the cathode is  $Ag^+ + e^- \rightarrow Ag$ . The Ag ions, thus, are plated onto the substrate surface. Compared to vacuum deposition, electroplating is less expensive and easily to fabricate thick layers. It can be implemented at relative low temperature, from room temperature to 80°C. Although solders produced by electroplating method might get oxidized during manufacture, the metal oxides can be removed using proper chemical treatments. If the metal structure is designed well, the fresh metal can be protected by an outer capping layer and realize the fluxless bonding feature.

## 2.2 Vacuum Furnace and Bonding Setup

In this research, all of bonding process is done in a vacuum furnace built in house as depicted in Fig. 2.1 [1]. The vacuum furnace consists of a quartz cylinder, two stainless steel plates, a heating platform, and a ceramic post. The quartz cylinder, having the inner diameter of 130 mm and height of 200 mm, is sandwiched between two steel plates to construct a vacuum chamber.

The interference between the cylinder and the steel plate is sealed by an O-ring. It is easy to observe the sample during the reflow process because to the transparency of quartz. The temperature is monitored by two type-K thermocouples (Chromel+ Alumel-) at two locations, the top surface of sample and the sidewall of platform. Inside the vacuum furnace, a graphite platform is supported by a ceramic poster standing at the center of the base stainless steel plate.

Fig. 2.1 Schematic of the vacuum furnace showing key components: (a) quartz cylinder, (b) upper stainless plate, (c) base plate, (d) graphite platform, (e) heating wire, (f) electrical feedthroughs, (g) platform thermocouple, and (h) sample thermocouple

The graphite platform, having the size of 75×75×10 mm<sup>3</sup>, is drilled with many holes to allow the heating wire (Nickel-Chromium alloy) going through the body of the block. The wire is

electrically insulated from the graphite using ceramic tubes as shown in Fig. 2.2. Graphite was chosen as the material of the platform because it has been experimentally proven that it absorbs 97% of radiation and is a nearly perfect emitter of radiation [2]. Therefore, the platform will absorb a maximum amount of heat given off by the wires. It is also easy to machine and can withstand very high temperature.

Fig. 2.2 Photo of the graphite heating platform

To achieve thermal isolation of the platform from the upper and base plates, a ceramic poster having relatively low thermal conductivity is utilized to support the platform. Once the chamber is pumped down, heat transfers to the upper and base plates from the platform through radiation mechanism only. Because the plates are constructed of stainless steel, being able to reflect and scatter radiation, the plates will not absorb much heat radiation and can keep cooled to low temperature with natural convection by ambient air. It is designed so that the platform is well

thermally isolated from the chamber enclosure that includes the cylinder wall and two steel plates. This is a unique feature of the furnace design. It allows for the platform to be heated to high temperatures while the temperature of the rest of the chamber remains relatively low, which is very important in the safety issue and the ability to seal the chamber in vacuum using O-rings. The upper plate is mounted with an ultra-Torr connector to take the small K-type thermocouple probe for measuring the sample temperature. The base plate contains four ports with National Pipe Thread (NPT). Two of these are occupied by feedthroughs. One feedthrough is for a pair of copper wires to pass into the chamber to connect to the two ends of the heating wire. The other is for thermocouple wires. The third port is used for the vacuum gauge, and the fourth port is for connecting to a mechanical pump. In this design, the chamber is allowed to pump down to 50 millitorrs and the maximum temperature of platform reaches up to 450°C.

To conduct the reflow process in the vacuum chamber, the samples electroplated with solder layers are mounted in a graphite fixture and applied with a static pressure to ensure intimate contact. The assembly is then placed on the graphite platform. Once the vacuum furnace is pumped down and kept at 50 to 100 millitorrs to suppress oxidation during reflow, the temperature controller is turned on to heat up the platform. The reflow process is carried out at wide ranges of temperature and dwell time for different bonding systems. After reaching the peak temperature, the heater is turned off and the assembly is allowed to cool down naturally to room temperature in

a vacuum environment. Comparing to bonding in air, the amount of oxygen available to oxidize the molten solder is reduced by a factor of 15,200 in 50 millitorrs of vacuum.

#### 2.3 Characterization Techniques

#### 2.3.1 X-Ray Diffraction (XRD)

X-ray diffraction is used to identify the crystalline phases present in materials and to measure the structural properties, such as average grain size, crystallinity, lattice parameter, strain, and crystal defect, of multilayer films. X-ray diffraction peaks are produced by constructive interference of a monochromatic beam of x-rays scattered at specific angles from each lattice plane in a sample. An X-ray, generated by a cathode ray tube, is filtered to produce monochromatic radiation. These X-rays are then collimated to concentrate and direct the ray towards to the sample. The constructive interference happens when the interaction of incident rays and lattice plan satisfy Bragg's Law,  $n\lambda = 2d\sin\theta$ , where  $\lambda$  is the wavelength of electromagnetic radiation, d is the lattice spacing in the crystalline sample, and  $\theta$  is the diffraction angle. The peak intensities are determined by the atomic arrangement within the lattice planes. These diffracted X-rays are then detected, processed and counted. Therefore, the X-ray diffraction pattern is the fingerprint of periodic atomic arrangements of a sample. By scanning the sample through a range of 20 angles, all possible diffraction directions of the lattice can be attained. In this study, it was applied to different materials and their results are presented as a plot of diffraction intensity corresponding to diffraction angles. Finally, to obtain these results, Rigaku SmartLab X-ray Diffractometer was used for X-ray diffraction analysis.

# 2.3.2 Scanning Electron Microscope (SEM)/Energy Dispersive X-ray Spectroscopy (EDX)

SEM is an electron microscope that uses focused beam of high energy electrons to image specimens. The high energy electrons interact with the atoms that make up the sample generating a variety of signals from the surface of the specimens. These signals, which includes secondary electrons (SE), back-scattered electrons (BSE), diffracted backscattered electrons (EBSD), characteristic X-rays, visible light (cathodoluminescence), specimen current, and transmitted electrons, reveal the specimens' surface topographies, chemical compositions, orientations, and crystalline structures. Fig. 2.3 displays the interaction volume and the signals produced by the interaction between electron beam and specimens [3]. The SE detector installed in the SEM captures the SE imaging high-resolution morphologies and topographies for the specimens' surfaces. Due to the very narrow electron beam, SEM micrographs have a large depth of field,

yielding a three-dimensional surface image of a specimen. BSE detectors may also be used in a SEM to illustrate contrasts in the composition of multiphase specimens. For instance, a stronger BSE intensity is detected if a larger number of backscattered electrons reaching to a BSE detector. Larger atoms, with a greater Z-number, have a higher probability of producing elastic collisions due to their larger cross-sectional area. Thus, elements with a greater atomic number (Z) show brighter images than smaller atomic number in BSE images. X-ray is also produced during the interaction of an electron beam with a specimen. The energy-dispersive detector is used to separate the characteristic x-rays of different elements into an energy spectrum. In addition, EDX software system is used to analyze the energy spectrum for determining the specific elements in the specimen. Energy dispersive X-ray spectroscopy can be used to find the chemical composition of materials in small area ( $\sim 10^{-6}$  mm<sup>2</sup>), and can create element composition mappings over this area. The spot size, defined as the diameter of the electron beam, depends on the density and atomic number of the interested elements and accelerating voltage. In this dissertation, Philips XL-30 FEG SEM was used.

Fig. 2.3 The interaction volume and the signals produced by the interaction between the electron beam and specimen

# 2.4 References

- 1. Chin C. Lee, Dave T. Wang, and Won S. Choi, "Design and construction of a compact vacuum furnace for scientific research," Review of Scientific Instruments, American Institute of Physics, 77, 125104, pp.125104.1-125104.5, Dec. 2006

- 2. <a href="http://www.egglescliffe.org.uk/physics/astronomy/blackbody/bbody.html">http://www.egglescliffe.org.uk/physics/astronomy/blackbody/bbody.html</a>

- 3. <a href="http://www.ammrf.org.au/myscope/sem/background/concepts/interactions.php">http://www.ammrf.org.au/myscope/sem/background/concepts/interactions.php</a>

# **Chapter Three**

# Fluxless Bonding of Si chips to Aluminum Boards Using Electroplated Sn Solder

#### 3.1 Introduction

Aluminum (Al) and its alloys have long been used in numerous products ranging from wrapping foils to airplanes. Al has the advantages of high thermal conductivity, high electrical conductivity, light weight, excellent resistance to corrosion, low cost, and ease of forging and machining. Despite all these advantages, its applications in electronic products have been limited to heatsinks [1-3] and casings. It has seldom been considered a substrate material to mount semiconductor chips and modules. There are two fundamental reasons: high coefficient of thermal expansion (CTE) and being unsolderable. Thus, the electronic industry has avoided its use as boards or substrates. The CTE mismatch between Si of 3 ppm/°C and Al of 23 ppm/°C is probably the highest among bonding pairs in electronic packaging. However, the use of Al is inevitable by virtue of its remarkable advantages as mentioned above. Al is extremely lightweight compared to other metals, making it the promising base material in manufacturing automobile and aircraft components and light-emitting diode (LED) lighting packages.

In this research, we set out to investigate techniques to surmount these two fundamental drawbacks and subsequently demonstrate the results that lead us to rethink aluminum and give aluminum another chance to perform. Our objective is to use Al as substrates or blocks to mount high power chips or modules using tin (Sn) without flux. An example of high power module is 100-watt LEDs assembled on a copper base that is attached to Al block for heat conduction. Present technique uses conductive adhesive to attach the module to the Al block [4-6]. The problem is that the adhesive has poor thermal conductivity. Another example is high power automobile module on alumina substrate that is attached to copper (Cu) base-plate for heat conduction. Using Al base-plate instead of Cu base-plate has advantages in reducing cost and weight and decreasing fuel consumption as well. The density of Al is only 30% of Cu. The price of Al is only 25% of Cu by weight and only 8% of Cu by volume.

In this research, we report preliminary results of fluxless bonding Si chips to Al substrates using Sn as the bonding medium. This work follows our previous works on other material systems [7-9]. After the samples were bonded, the quality and microstructure of the joints were examined using scanning electron microscopy (SEM) and the composition of the joints was studied with energy dispersive X-ray spectroscopy (EDX). The joint strength was examined by shear test. In what follows, we first present the experimental design and procedures. Experimental results are then reported and discussed. Finally, a short summary is given.

# 3.2 Experimental Design and Procedures

The soldering process used in electronic industries is a chemical reaction between metals which forms intermetallic compound (IMC) at the interfaces. It is believed that the IMC layer links the solder to the base metal. For Sn-containing solder on Cu, the IMCs are Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn. Since Sn does not react with Al to form IMC, Al by itself is not solderable. The most popular method to make Al solderable is the zincation process, followed by electroless nickel plating and immersion gold deposition. The zincation process dissolves the surface aluminum oxide and deposits zinc (Zn) through electrochemical exchange reaction in alkaline zincate solution. Nonetheless, Zn deposition stops when the Al substrate is all covered with Zn. As a result, the zinc layer deposited is thin "20-50 nm" and multiple zincation operations are necessary for better surface uniformity and adhesion strength [10-12].

Instead of the zincation process, we developed an alternative technique to make Al solderable. Based on our experience and with the facilities available to us, we use electron beam evaporation to deposit Cr/Cu on Al for making it solderable. This process is easier to implement and can produce more reliability and reproducible results. Al substrates with 99% purity and dimensions of  $20.6 \text{ mm} \times 25.4 \text{ mm} \times 1.7 \text{ mm}$  (width  $\times$  length  $\times$  thickness) were sheared from Al 1100 sheet. They were thoroughly cleaned and slightly etched to remove surface oxide. Thin 100

nm Cr and 200 nm Cu layers were deposited on 6 mm × 6 mm area of the Al substrates in a high vacuum (2×10<sup>-6</sup> torr) electron beam evaporation system. The Cr layer acts as an adhesion layer and the Cu layer prevents the Cr layer from oxidation. An additional 25 μm thick Cu was further electroplated in a pyrophosphate Cu plating bath at ambient temperature with current density of 30 mA/cm<sup>2</sup>. Subsequently, a Sn layer of 85 μm thick was electroplated in a stannous bath under the condition of 43°C and pH of 1 with current density of 30 mA/cm<sup>2</sup>. Silver (Ag) of 100 nm in thickness was then electroplated over Sn as capping layer to prevent Sn from oxidation. The Cr/Cu dual layer is employed as the interface layer between Sn solder and Al substrates.

Two-inch n-type Si wafers of 0.27 mm thick in (100) orientation were deposited with 30 nm Cr and 100 nm Au layers using electron beam evaporation. The Cr layer is an adhesion layer and the Au layer protects the Cr layer from oxidation when exposing to air. The wafers were then diced into 5 mm  $\times$  5 mm and 5 mm  $\times$  10 mm chips to be ready for bonding.

The first design is bonding a 5 mm  $\times$  5 mm Si chip on a 6 mm  $\times$  6 mm Al substrate on which 85  $\mu$ m of Sn was plated. The desired Sn solder joint thickness is controlled by applying different static pressures throughout bonding process. The Si chip was placed face down on Al substrate whereby the pressure was applied on the backside of Si chip. The assembly was mounted on a heater graphite platform in a chamber. Static pressures selected are 0.6 psi (0.004 MPa), 2.5 psi (0.017 MPa), and 32 psi (0.221 MPa), respectively. The chamber was pumped down and kept

at 80 millitorrs to suppress oxidation and then the graphite platform was heated and temperature was monitored by a thermocouple during bonding process. The bonding process was conducted at  $240^{\circ}$ C with a dwell time of 3 minutes. The heater was then turned off and the assembly was allowed to cool down naturally to room temperature in vacuum environment. Later, an improved bonding process was developed to precisely control the solder joint thickness by integrating 50  $\mu$ m thick Cu spacers between the Si chip and the Al substrate. Fig. 3.1 depicts the bonding structure and configuration using Cu spacers to control joint thickness. A 5 mm  $\times$  10 mm Si chip and Al substrate having 6 mm  $\times$  6 mm  $\times$  85  $\mu$ m (width  $\times$  length  $\times$  thickness) Sn solder were held together and two 50  $\mu$ m thick Cu shim spacers were inserted in between. A 70 g weight (4 psi) was exerted on the Si chip to ensure intimate contact. The assembly was then bonded using the same process aforementioned. In all processes, no flux was used.

Fig. 3.1 Bonding structure and configuration of controlling joint thickness using Cu spacer

To evaluate the joint quality and to study the microstructure, the samples were mounted in epoxy resin, cut into halves, and polished properly for SEM cross-section image examination and

EDX composition analysis. Shear tests were implemented to measure the fracture force of the 6 samples bonded using the 50  $\mu$ m thick Cu spacer.

## 3.3 Experimental results and discussion

# 3.3.1 Bonding design I

In the first design, different bonding pressures of 0.6 psi (0.004 MPa), 2.5 psi (0.017 MPa) and 32 psi (0.221 MPa) were employed to assess the fluxless bonding feasibility. The first assembly was bonded under 0.6 psi. Fig. 3.2 shows cross-section SEM images of a typical bonded portion. The upper interface between the silicon and the solder layer is sharp without any IMCs. The lower interface has two IMC layers as shown in Fig. 3.2(b).

Of these two IMC layers, the upper one (IMC1) exhibits scallop-shaped morphology. This type of morphology is favored by a high rate of free energy change [13-16]. Beneath IMC1 is another layer of thin IMC (IMC2). From EDX analysis data listed in Table 3.1, chemical compositions of IMC1 and IMC2 are  $Cu_6Sn_5$  and  $Cu_3Sn$ , respectively.

Fig. 3.2 Cross-section SEM images of the sample under bonding pressure of 0.6 psi at (a) low magnification ( $1000\times$ ), (b) high magnification ( $5000\times$ ) and (c) low magnification ( $500\times$ ), showing the joint on the edge

Table 3.1 EDX data of three regions marked as 1, 2 and 3 at the Sn/IMCs/Cu interface, as shown in Fig. 3.2(b)

| Region | Composition (atomic %) |      | Thickness |

|--------|------------------------|------|-----------|

| Region | Cu                     | Sn   | (µm)      |

| 1      | 0                      | 100  | 62-72     |

| 2      | 53.7                   | 46.3 | 0-7       |

| 3      | 75.3                   | 24.1 | 0-1       |

As can be seen in Fig. 3.2(a), the joint is quite uniform and is approximately 70 µm in thickness. When the Sn layer melts during bonding, the molten Sn wets the Cu on the Al substrate and Au on the Si chip very well. This could be seen in Fig. 3.2(c). Theoretically, the maximum stress-free shear strain is a commonly used indicator of possible breakage caused by CTE mismatch in a bilayer structure of different materials connected together by solder. In this model, it is assumed that both Si chip and Al substrate are free to contract during cooling down. This indicator is calculated by the equation [17],

$$\gamma = \frac{(\alpha_1 - \alpha_2)(T_2 - T_1)^{\frac{L}{2}}}{h}$$

(1)

where  $\alpha_1$  and  $\alpha_2$  are the CTE of silicon chip and aluminum, respectively,  $T_2$  is the solidifying or the bonding temperature,  $T_1$  is room temperature,  $T_2$  is diagonal length of the Si chip,  $T_2$  is the bonding layer thickness. Based on Eq. 1, the maximum stress-free shear strain for the Si-Al bonding pair with 70  $\mu$ m Sn is calculated to be 26%. It is worth noting that "stress-free" means that the Si and Al are mechanically decoupled and no stress is induced. However, Si and Al are coupled once the solder solidifies. Thus, the stress-free strain is always higher than the actual strain.

This led us to reduce the Sn solder joint thickness by increasing the bonding pressure to 2.5 psi. On the cross section of the sample cut and polished as shown in Fig. 3.3, no voids are observed except a few Kirkendall voids near the Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn IMC layers. Similarly, a scallop-shaped IMC layer and underlying thin IMC layer are observed. The EDX analysis results are listed in Table 3.2 and the EDX element mappings are displayed in Fig. 3.4.

Fig. 3.3 Cross-section SEM images of the sample under bonding pressure of 2.5 psi at (a) low magnification ( $2000\times$ ) and (b) high magnification ( $5000\times$ )

Table 3.2 EDX data of three regions marked as 1, 2 and 3 at the Si/Sn/IMCs/Cu interface shown in Fig. 3.3(b)

| Region | Composition (atomic %) |      | Thickness |

|--------|------------------------|------|-----------|

| Region | Cu                     | Sn   | (µm)      |

| 1      | 0                      | 100  | 1-6       |

| 2      | 54.2                   | 45.8 | 0-6       |

| 3      | 74.2                   | 25.8 | 0-1       |

Fig. 3.4 EDX element mappings of the sample under bonding pressure of 2.5 psi

The compositions of the upper and lower IMC layers are determined as  $Cu_6Sn_5$  and  $Cu_3Sn$ , respectively. The thickness of Sn layer in the joint is approximately 1  $\mu m$  at the peaks of the scallop-shaped IMC layer and 6  $\mu m$  at the grooves. The joint thickness including IMCs is about 7