### UC Irvine UC Irvine Electronic Theses and Dissertations

#### Title

Verifiable Integrity and Availability for Code and Execution in Simple Embedded Systems

Permalink https://escholarship.org/uc/item/7983n05g

Author De Oliveira Nunes, Ivan

Publication Date 2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Verifiable Integrity and Availability for Code and Execution in Simple Embedded Systems

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Networked Systems

by

Ivan De Oliveira Nunes

Dissertation Committee: Dr. Gene Tsudik, Chair Dr. Ardalan Amiri Sani Dr. N. Asokan

Portion of Chapter 3 © 2019 The USENIX Association Portion of Chapter 5 © 2020 The USENIX Association All other materials © 2021 Ivan De Oliveira Nunes

## TABLE OF CONTENTS

|              |                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                     |

|--------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| LI           | ST (                      | OF FIC           | GURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{vi}$                                            |

| LI           | ST (                      | OF TA            | BLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | viii                                                     |

| A            | CKN                       | OWLI             | EDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ix                                                       |

| C            | URR                       | ICUL             | UM VITAE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xi                                                       |

| $\mathbf{A}$ | BSTI                      | RACT             | OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xiv                                                      |

| 1            | <b>Intr</b><br>1.1        | oducti<br>Disser | i <b>on</b><br>tation Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | f 1<br>4                                                 |

| 2            | Bac<br>2.1<br>2.2<br>2.3  | Attest           | nd<br>: Low-end Embedded Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>6</b><br>8<br>9<br>13                                 |

| 3            | <b>VR</b> .<br>3.1<br>3.2 | Introd           | <b>Werifiable Remote Attestation for Simple Embedded Systems</b> Suction       Suction         iew of VRASED       Successful Stress         Adversary Capabilities & Verification Axioms       Successful Stressful Stre | 5 <b>17</b><br>19<br>20<br>21<br>23<br>25<br>26          |

|              | 3.3                       |                  | ing VRASED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28<br>28<br>31<br>33<br>35<br>36<br>38<br>40<br>42<br>42 |

|          | 3.4  | Alternative Designs                                                   | 44  |

|----------|------|-----------------------------------------------------------------------|-----|

|          |      | 3.4.1 Erasure on SW-Att                                               | 44  |

|          |      | 3.4.2 Compiler-Based Clean-Up                                         | 45  |

|          |      | 3.4.3 Double-HMAC Call                                                | 45  |

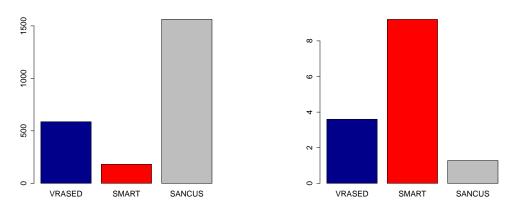

|          | 3.5  | Evaluation                                                            | 46  |

|          |      | 3.5.1 Implementation                                                  | 46  |

|          |      | 3.5.2 Verification Results                                            | 47  |

|          |      | 3.5.3 Performance and Hardware Cost                                   | 48  |

|          |      | 3.5.4 Comparison with Other Low-End RA Architectures                  | 49  |

|          | 3.6  | Related Work                                                          | 50  |

|          | 3.7  | Conclusion                                                            | 52  |

|          | 3.8  | Appendix: RA Soundness and Security Proofs                            | 53  |

|          | 0.0  | 3.8.1 Proof Strategy                                                  | 53  |

|          |      | 3.8.2 Machine Model                                                   | 53  |

|          |      | 3.8.3 RA Soundness Proof                                              | 54  |

|          |      | 3.8.4 RA Security Proof                                               | 56  |

|          | 3.9  | Appendix: Verifier Authentication                                     | 58  |

|          |      | Appendix: FPGA Deployment and Sample Application                      | 61  |

|          | 0.10 | Appendix. IT ON Deployment and bample Application                     | 01  |

| <b>4</b> | RA   | <b>FA:</b> Remote Attestation with TOCTOU Avoidance                   | 63  |

|          | 4.1  | Introduction                                                          | 65  |

|          | 4.2  | Problem Scope & Definitions                                           | 67  |

|          |      | 4.2.1 Detection, Prevention & Memory Immutability                     | 67  |

|          |      | 4.2.2 Device Model & MCU Assumptions                                  | 68  |

|          |      | 4.2.3 RA Definitions, Architectures & Adversary Model                 | 69  |

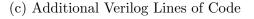

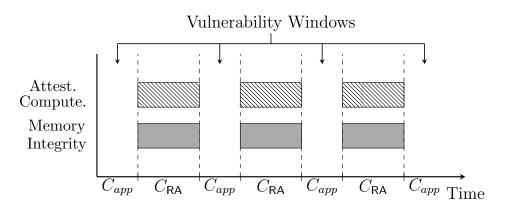

|          | 4.3  | RA TOCTOU                                                             | 72  |

|          |      | 4.3.1 Notation                                                        | 72  |

|          |      | 4.3.2 TOCTOU-Security Definition                                      | 73  |

|          |      | 4.3.3 TOCTOU-Secure RA vs. Consecutive Self-Measurements              | 75  |

|          | 4.4  | $RATA_A$ : RTC-Based TOCTOU-Secure Technique                          | 77  |

|          |      | 4.4.1 $RATA_A$ : Design & Security                                    | 78  |

|          |      | 4.4.2 $RATA_A$ : Implementation & Verification                        | 80  |

|          | 4.5  | $RATA_B$ : Clockless TOCTOU-Secure RA Technique                       | 82  |

|          |      | 4.5.1 $RATA_B$ – Design & Security                                    | 82  |

|          |      | 4.5.2 $RATA_B$ : Implementation & Verification                        | 85  |

|          | 4.6  | Evaluation                                                            | 87  |

|          | 4.7  | Using $RATA$ to Enhance RA & Related Services                         | 89  |

|          |      | 4.7.1 Constant-Time RA                                                | 90  |

|          |      | 4.7.2 Atomicity & Real-Time Settings                                  | 91  |

|          |      | 4.7.3 Collective RA Protocols and Device-to-Device Malware Relocation | 93  |

|          |      | 4.7.4 Runtime Attestation                                             | 95  |

|          | 4.8  | Related Work                                                          | 96  |

|          | 4.9  | Conclusions                                                           | 97  |

|          |      | Appendix: Proof of Theorem 3                                          | 99  |

|          |      |                                                                       | 101 |

|          | **** |                                                                       |     |

|          | 4.12 | Appendix: $RATA$ Implementation with SANCUS                                                                                                |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| <b>5</b> | API  | EX: From Remote Attestation to Verified Proofs of Execution 106                                                                            |

|          | 5.1  | Introduction                                                                                                                               |

|          | 5.2  | Related Work                                                                                                                               |

|          | 5.3  | Proof of Execution (PoX) Schemes                                                                                                           |

|          |      | 5.3.1 PoX Adversary Model & Security Definition                                                                                            |

|          |      | 5.3.2 MCU Assumptions                                                                                                                      |

|          | 5.4  | APEX: A Secure PoX Architecture                                                                                                            |

|          |      | 5.4.1 Protocol and Architecture                                                                                                            |

|          |      | 5.4.2 APEX Sub-Properties at a High-Level                                                                                                  |

|          | 5.5  | Formal Specification & Verified Implementation                                                                                             |

|          |      | 5.5.1 Machine Model                                                                                                                        |

|          |      | 5.5.2 Security & Implementation Correctness                                                                                                |

|          |      | 5.5.3 APEX Sub-Properties in LTL                                                                                                           |

|          | 5.6  | Implementation & Evaluation                                                                                                                |

|          |      | 5.6.1 Evaluation Results                                                                                                                   |

|          |      | 5.6.2 Comparison with CFA                                                                                                                  |

|          |      | 5.6.3 Proof of Concept: Authenticated Sensing and Actuation 134                                                                            |

|          | 5.7  | Limitations & Future Directions                                                                                                            |

|          | 5.8  | Conclusion                                                                                                                                 |

|          | 5.9  | Appendix: Sub-Module Verification                                                                                                          |

|          |      | Appendix: Proofs of Implementation Correctness & Security                                                                                  |

|          |      | Appendix: Software Transformation                                                                                                          |

|          |      |                                                                                                                                            |

| 6        |      | ROT: Trigger-based Active Root Of Trust148                                                                                                 |

|          | 6.1  | Introduction                                                                                                                               |

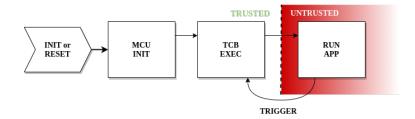

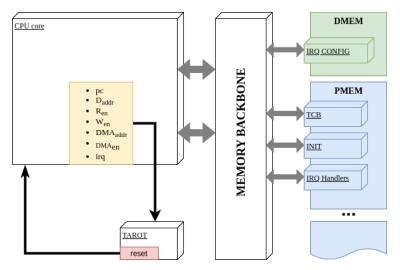

|          | 6.2  | $TAROT \text{ Overview} \dots \dots$ |

|          | 6.3  | $TAROT$ in Detail $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $156$                                                              |

|          |      | 6.3.1 Notation, Machine Model, & Assumptions                                                                                               |

|          |      | 6.3.2 TAROT End-To-End Goals Formally 162                                                                                                  |

|          |      | $6.3.3  TAROT \text{ Sub-Properties}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                     |

|          |      | $6.3.4  TAROT \text{ Composition Proof}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  165$                                      |

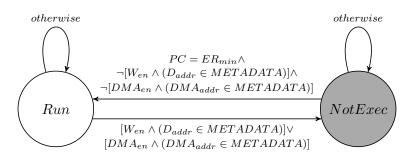

|          |      | 6.3.5 Sub-Module Implementation+Verification                                                                                               |

|          |      | 6.3.6 TCB Confidentiality 170                                                                                                              |

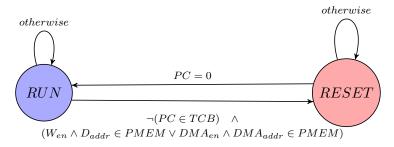

|          |      | $6.3.7  \text{Resets \& Availability}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    |

|          | 6.4  | Sample Applications                                                                                                                        |

|          |      | 6.4.1 GPIO-TCB: Critical Sensing+Actuation                                                                                                 |

|          |      | 6.4.2 TimerTCB: Secure Real-Time Scheduling                                                                                                |

|          |      | 6.4.3 NetTCB: Network Event-based trigger                                                                                                  |

|          |      | 6.4.4 Comparison with [115] and [60]                                                                                                       |

|          | 6.5  | Implementation & Evaluation                                                                                                                |

|          | 6.6  | Related Work                                                                                                                               |

|          | 6.7  | Conclusions                                                                                                                                |

| 7 Final Remarks | 183 |

|-----------------|-----|

| Bibliography    | 185 |

### LIST OF FIGURES

#### Page

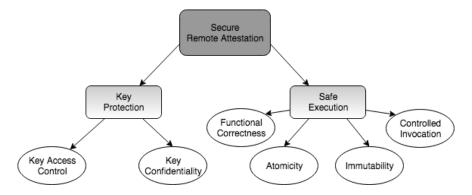

| $2.1 \\ 2.2$             | Attestation interaction                                                                                                                   | 9<br>16              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

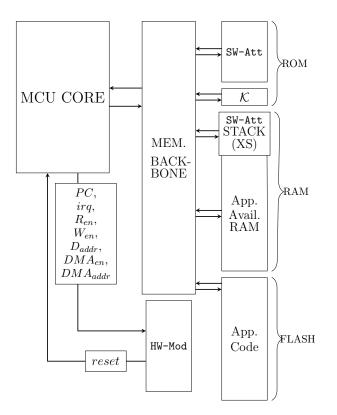

| 3.1<br>3.2<br>3.3<br>3.4 | Properties of secure RA                                                                                                                   | 23<br>24<br>26<br>28 |

| $3.5 \\ 3.6 \\ 3.7$      | RA security definition for VRASED                                                                                                         | 32<br>33<br>36       |

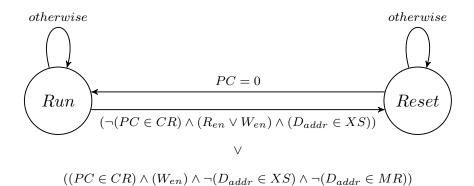

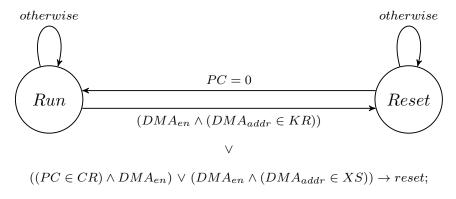

| 3.8<br>3.9<br>3.10       | Verified FSM for atomicity and controlled invocation                                                                                      | $38 \\ 40 \\ 42$     |

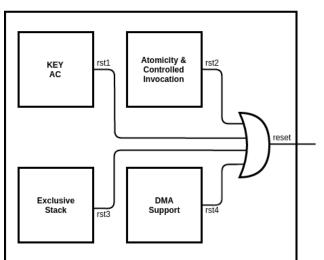

| 3.11<br>3.12             | HW-Mod composition from sub-modules                                                                                                       | $43 \\ 51$           |

| 3.14                     | SW-Att Implementation with Vrf authentication                                                                                             | 59<br>61<br>62       |

| $4.1 \\ 4.2$             | Consecutive Self-Measurements                                                                                                             | 75<br>77             |

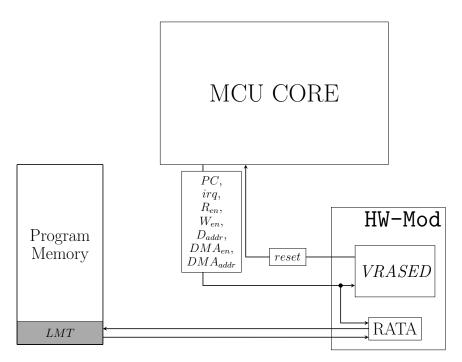

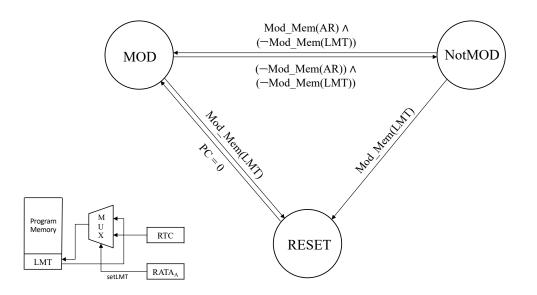

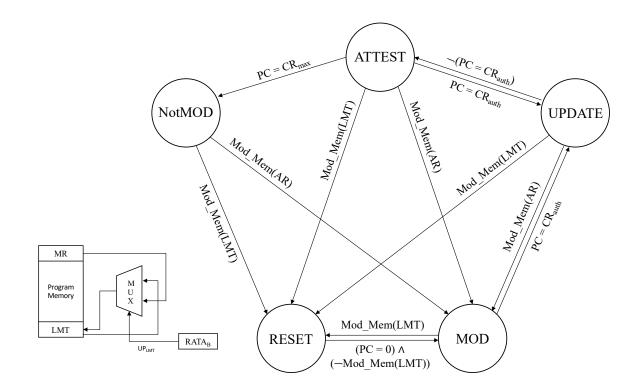

| $4.3 \\ 4.4 \\ 4.5$      | $RATA$ module in the overall system architecture $RATA_A$ FSM for RTC-based TOCTOU-secure RA $RATA_B$ FSM for clock-less TOCTOU-secure RA | 78<br>80<br>86       |

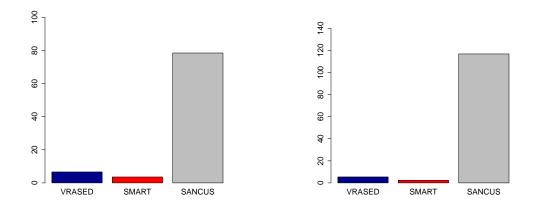

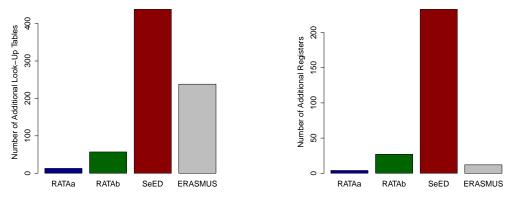

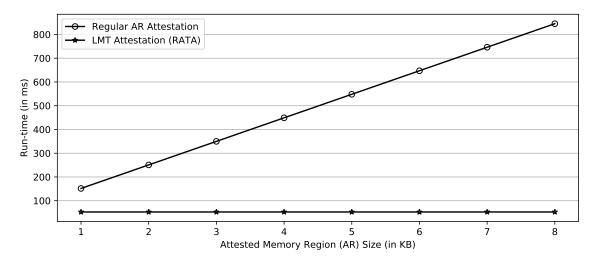

| 4.6<br>4.7               | Hardware overhead. Comparison between $RATA$ and techniques based on self-measurements                                                    | 89                   |

| -                        | (Case-2), as a function of $ AR $ . $ LMT $ is 32 Bytes. Results on the MSP430 MCU running at 8MHz.                                       | 90                   |

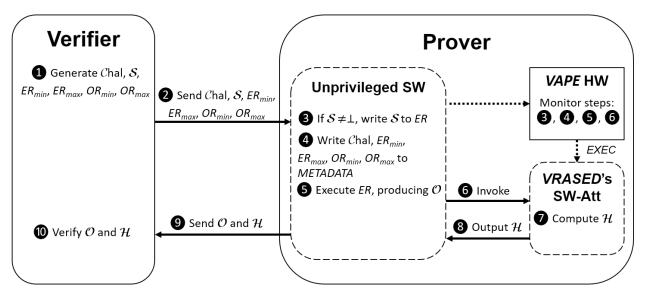

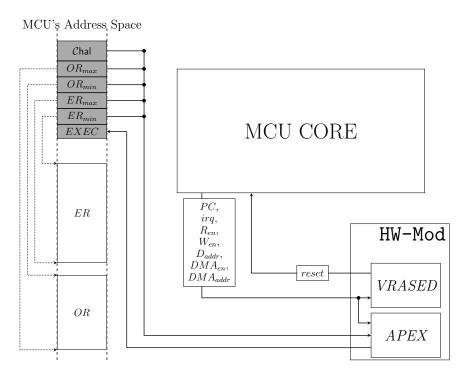

| $5.1 \\ 5.2$             | Overview of <i>APEX</i> workflow                                                                                                          | 120<br>121           |

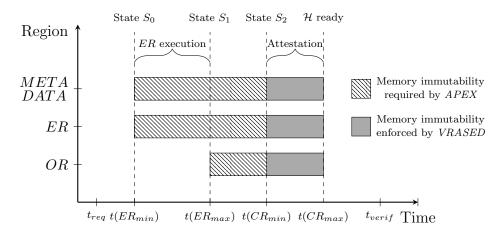

| 5.3  | Illustration of time intervals that each memory region must remain unchanged<br>in order to produce a valid $\mathcal{H}$ ( $EXEC = 1$ ). $t(X)$ denotes the time when |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | In order to produce a value $\pi$ ( $EXEC = 1$ ). $\iota(X)$ denotes the time when $PC = X$ .                                                                          | 128 |

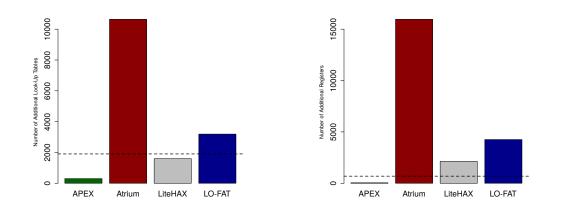

| 5.4  | Overhead comparison between <i>APEX</i> and CFA architectures. Dashed lines                                                                                            | 120 |

|      | represent total hardware cost of MSP430                                                                                                                                | 134 |

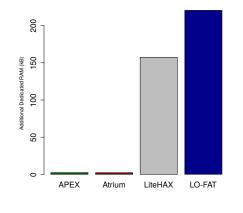

| 5.5  | Hardware setup for a fire sensor using <i>APEX</i>                                                                                                                     | 136 |

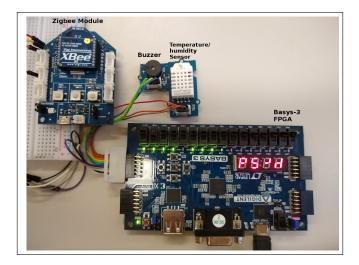

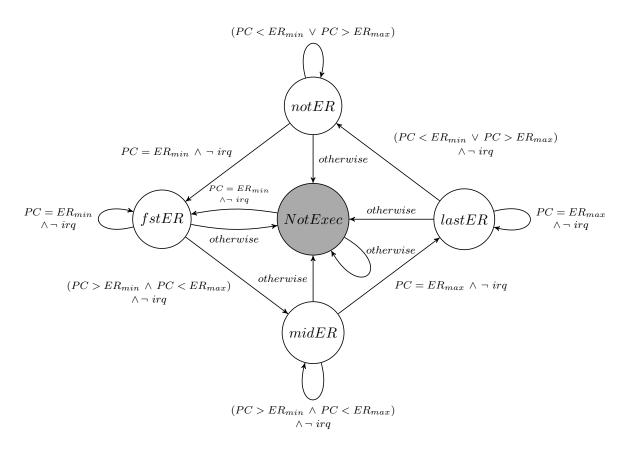

| 5.6  | Verified FSM for LTLs 5.5-5.7, a.k.a., EP2- Ephemeral Atomicity.                                                                                                       | 140 |

| 5.7  | Verified FSM for LTL 5.11, a.k.a., MP3- Challenge Temporal Consistency.                                                                                                | 141 |

| 5.8  | Code snippets for (a) fire sensor described in Section 5.6.3 (b) linker script $\ .$                                                                                   | 145 |

| 6.1  | TAROT Software Execution Flow                                                                                                                                          | 152 |

| 6.2  | $TAROT$ in the MCU architecture $\ldots \ldots \ldots$ | 153 |

| 6.3  | MCU machine model (subset) in LTL                                                                                                                                      | 161 |

| 6.4  | Formal Specification of <i>TAROT</i> end-to-end goals                                                                                                                  | 162 |

| 6.5  | Formal specification of sub-properties verifiably implemented by <i>TAROT</i> hard-                                                                                    |     |

|      | ware module.                                                                                                                                                           | 164 |

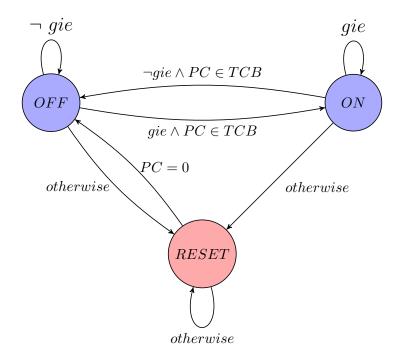

| 6.6  | Verified FSM for LTL 6.6.                                                                                                                                              | 167 |

| 6.7  | Verified FSM for LTL 6.8                                                                                                                                               | 168 |

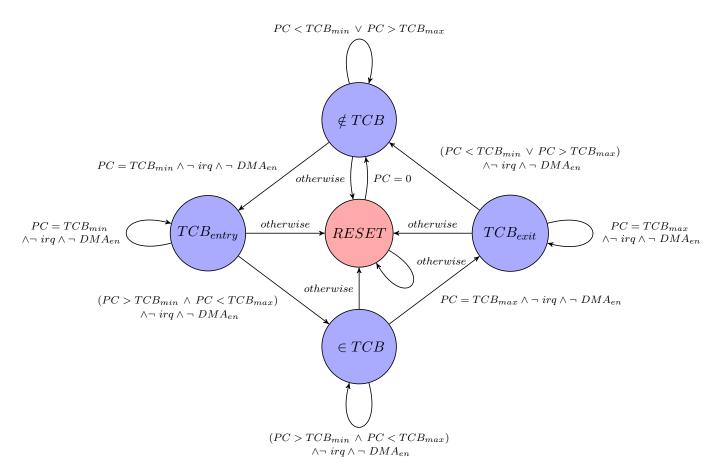

| 6.8  | Verified FSM for LTLs 6.9–6.11                                                                                                                                         | 169 |

| 6.9  | Verified FSM for LTL 6.12                                                                                                                                              | 171 |

| 6.10 | Program Entry Point                                                                                                                                                    | 172 |

|      | Trigger Setup                                                                                                                                                          | 173 |

|      | GPIO Handling Routine                                                                                                                                                  | 174 |

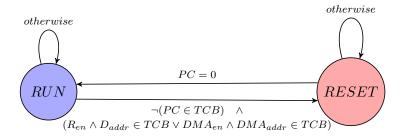

|      | $IRQ_{cfg}$ initialization                                                                                                                                             | 174 |

|      | Timer Trigger Setup                                                                                                                                                    | 175 |

|      | Timer Handle Routine                                                                                                                                                   | 175 |

|      | UART Trigger Setup                                                                                                                                                     | 176 |

|      | NetTCB Handler Routine and TCB Implementation                                                                                                                          | 176 |

| 6.18 | Comparison with passive RoTs: Hardware overhead                                                                                                                        | 180 |

### LIST OF TABLES

#### Page

| 3.1<br>3.2<br>3.3<br>3.4 | Summary of <i>VRASED</i> -relevant notation |     |

|--------------------------|---------------------------------------------|-----|

| $4.1 \\ 4.2$             | Summary of <i>RATA</i> -relevant notation   |     |

| $5.1 \\ 5.2$             | Summary of <i>APEX</i> -relevant notation   |     |

| $6.1 \\ 6.2 \\ 6.3$      | Summary of TAROT-relevant notation          | 179 |

### ACKNOWLEDGMENTS

Wow, looks like it's time to end this chapter of my life! Looking back, these past five years were unbelievable. I feel very lucky and I thank God for putting all the amazing people that I list below in my path. At this point, there's probably one thing I am sure about: I couldn't have come this far without these people. Tell me about "standing on the shoulders of giants", Google Scholar (or whoever said it originally)!

I must start by thanking the person who brought me this far, my Ph.D. advisor, Gene Tsudik. For teaching me everything I know in computing security. For offering amazing feedback and seminal ideas that were instrumental to this entire process. For genuinely caring about my success and for helping me to pursue the career that I've always dreamed of.

I would also like to thank my committee members, Ardalan Amiri Sani and N. Asokan, for their interest in my research and for taking the time to provide me with their mentorship and constructive criticism. It was a great pleasure to have such outstanding researchers on my Ph.D. committee.

In addition to my Ph.D. mentors, I could not have come this far without my early mentors and educators. I am immensely thankful to all of them for the many, many lessons. I would like to cite and especially thank my M.Sc. advisors – Antonio Loureiro and Pedro Vaz De Melo – and my Bachelor's advisors – Magnos Martinello and Roberta Lima Gomes – who were the very first to introduce me to the "research world".

I am immensely thankful to all of my co-authors. Someone once told me: "If you're not smart, you need smart co-authors." Well... guilty as charged. I do have pretty amazing co-authors! The list is too long, so I won't risk trying to name one by one. It has been really amusing and humbling to work with such a fantastic and diverse group of people. Out of these many co-authors, I especially thank Norrathep Rattanavipanon (who worked along with me in major parts of this dissertation), Sashidhar Jakkamsetti, Seoyeon Hwang, Chris Wood, and Esmerald Aliaj. These were/are also Ph.D. students at UCI who were directly involved on some of the hands-on parts of my Ph.D. research.

Out of the friends I've made during my five years at UCI, I couldn't forget to mention the Sprout Lab members that overlapped with my generation: Norrathep Rattanavipanon, Ercan Ozturk, Tyler Kaczmarek, Chris Wood, Yoshimichi Nakatsuka, Seoyeon Hwang, Sashidhar Jakkamsetti, and Gene Tsudik. Thanks for all the fun times together! I hope to see you around very soon!

Sorry if this is starting to take too long, but outside UCI, the list of personal friends and family that deserve my gratitude isn't small either. I am truly blessed to have all of you in my life.

First and foremost, I thank my wife, Renata, for her unconditional love and support. For being there for me at every step of the way. For being my best friend. I am so proud of what we've achieved together so far and I can't wait to start this new chapter of our lives. I thank my parents – Joao and Angelica – and my brother – Igor. I've always felt all of you close to my heart, no matter how physically distant. You've been my strongest and longest-term supporters. You gave me everything. Knowing that you were there for me and seeing your genuine joy in each and every one of my accomplishments (no matter how small) is what always kept me moving forward.

Finally, I thank all my family members – especially my grandparents (Nilo, Venina, Rolando, and Marina), parents in law (Renato and Rosangela), my sister-in-law (Fernanda), and all my many uncles, aunts, and cousins. I am also thankful to all my friends – especially from Darwin, CsF-Irvine, UFES-09, and WiseMap-UFMG. Thank you for your best wishes and for staying in touch despite the distance!

### CURRICULUM VITAE

#### Ivan De Oliveira Nunes

#### **EDUCATION**

**Ph.D. in Networked Systems** University of California, Irvine

M.S. in Computer Science Universidade Federal de Minas Gerais

**B.S. in Computer Engineering** Universidade Federal do Espirito Santo **2021** *Irvine*, *California*

**2016** Belo Horizonte, MG, Brazil

> **2014** Vitoria, ES, Brazil

> > 2021–Current

Irvine, California

2016 - 2021

Rochester, New York

#### PROFESSIONAL EXPERIENCE

Assistant Professor Rochester Institute of Technology

**Graduate Research Assistant** University of California, Irvine

Summer Associate (Ph.D. Intern) Visa Research Summer 2017, Spring & Summer 2018 Palo Alto, California

Ph.D. Intern

SRI International

Summer 2019, Summer 2020 Menlo Park, California

#### PAPERS IN SUBMISSION OR UNDER REVIEW

Esmerald Aliaj, Ivan De Oliveira Nunes, and Gene Tsudik. **TAROT : Trigger-based Active Root-Of-Trust (for Tiny Embedded Devices).** Undergoing Major Revisions to (conditionally) appear at USENIX Security Symposium. 2022.

#### **REFEREED CONFERENCE PUBLICATIONS**

Mahmoud Ammar, Bruno Crispo, Ivan De Oliveira Nunes, and Gene Tsudik. **Delegated Attestation: Scalable Remote Attestation of Commodity CPS by Blending Proofs of Execution with Software Attestation.** ACM Conference on Security and Privacy in Wireless and Mobile Networks (WiSec). 2021.

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, Norrathep Rattanavipanon, and Gene Tsudik. On the TOCTOU Problem in Remote Attestation. ACM Conference on Computer and Communications Security (CCS). 2021. Ivan De Oliveira Nunes, Sashidhar Jakkamsetti and Gene Tsudik. **DIALED: Data Integrity Attestation for Low-end Embedded Devices.** Design Automation Conference (DAC). 2021.

Ivan De Oliveira Nunes, Xuhua Ding, and Gene Tsudik. On the Root of Trust Identification Problem. In 20th ACM/IEEE Conference on Information Processing in Sensor Networks (IPSN). 2021.

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, and Gene Tsudik. **Tiny-CFA: A Minimalistic Approach for Control Flow Attestation Using Verified Proofs of Execution.** In Design, Automation & Test in Europe Conference & Exhibition (DATE). 2021.

Ivan De Oliveira Nunes, Karim Eldefrawy, Norrathep Rattanavipanon, and Gene Tsudik. APEX: A Verified Architecture for Proofs of Execution on Remote Devices under Full Software Compromise. In 29th USENIX Security Symposium (USENIX Security 20). 2020.

Ivan De Oliveira Nunes, Karim Eldefrawy, Norrathep Rattanavipanon, Michael Steiner, and Gene Tsudik. VRASED: A verified hardware/software co-design for remote attestation. In 28th USENIX Security Symposium (USENIX Security 19), pp. 1429-1446. 2019.

Ivan De Oliveira Nunes, Ghada Dessouky, Ahmad Ibrahim, Norrathep Rattanavipanon, Ahmad-Reza Sadeghi, and Gene Tsudik. Towards systematic design of collective remote attestation protocols. In 2019 IEEE 39th International Conference on Distributed Computing Systems (ICDCS), pp. 1188-1198. IEEE, 2019.

Ivan De Oliveira Nunes, Karim Eldefrawy, Norrathep Rattanavipanon, and Gene Tsudik. **PURE: Using Verified Remote Attestation to Obtain Proofs of Update, Reset and Erasure in low-End Embedded Systems.** In IEEE/ACM International Conference On Computer Aided Design (ICCAD), pp. 1-8. 2019.

Ivan O. Nunes and Gene Tsudik. **KRB-CCN: Lightweight Authentication and Access Control for Private Content-Centric Networks.** In International Conference on Applied Cryptography and Network Security (ACNS), pp. 598-615. Springer, Cham, 2018.

Ivan De Oliveira Nunes, Karim Eldefrawy, and Tancrede Lepoint. Secure Non-interactive User Re-enrollment in Biometrics-Based Identification and Authentication Systems. In International Symposium on Cyber Security Cryptography and Machine Learning (CSCML), pp. 162-180. Springer, Cham, 2018.

Ivan O. Nunes, Gene Tsudik, and Christopher A. Wood. Namespace tunnels in contentcentric networks. In 2017 IEEE 42nd Conference on Local Computer Networks (LCN), pp. 35-42. IEEE, 2017.

Ivan O. Nunes, Clayson Celes, Michael D. Silva, Pedro OS Vaz de Melo, and Antonio AF

Loureiro. **GRM: Group Regularity Mobility Model.** In Proceedings of the 20th ACM International Conference on Modelling, Analysis and Simulation of Wireless and Mobile Systems (MSWIM), pp. 85-89. 2017.

Michael D. Silva, Ivan O. Nunes, Raquel AF Mini, and Antonio AF Loureiro. **ST-Drop: A** novel buffer management strategy for D2D opportunistic networks. In 2017 IEEE Symposium on Computers and Communications (ISCC), pp. 1300-1305. IEEE, 2017.

Antonio L. Maia Neto, Artur LF Souza, Italo Cunha, Michele Nogueira, Ivan Oliveira Nunes, Leonardo Cotta, Nicolas Gentille et al. **AoT: Authentication and access control for the entire iot device life-cycle.** In Proceedings of the 14th ACM Conference on Embedded Network Sensor Systems (SenSys), pp. 1-15. 2016.

Ivan Oliveira Nunes, Pedro OS Vaz de Melo, and Antonio AF Loureiro. **Group mobility: Detection, tracking and characterization.** In 2016 IEEE International Conference on Communications (ICC), pp. 1-6. IEEE, 2016.

#### **REFEREED JOURNAL PUBLICATIONS**

Ivan De Oliveira Nunes, Karim Eldefrawy, and Tancrede Lepoint. SNUSE: A secure computation approach for large-scale user re-enrollment in biometric authentication systems. Future Generation Computer Systems 98 (2019): 259-273.

Ivan O. Nunes, Clayson Celes, Igor Nunes, Pedro OS Vaz de Melo, and Antonio AF Loureiro. **Combining spatial and social awareness in D2D opportunistic routing.** IEEE Communications Magazine 56, no. 1 (2018): 128-135.

Ivan O. Nunes, Clayson Celes, Pedro OS Vaz de Melo, and Antonio AF Loureiro. **GROUPS-NET: Group meetings aware routing in multi-hop D2D networks.** Computer Networks 127 (2017): 94-108.

Ivan O. Nunes, Pedro OS Vaz de Melo, and Antonio AF Loureiro. Leveraging D2D multihop communication through social group meeting awareness. IEEE Wireless Communications 23, no. 4 (2016): 12-19.

#### ABSTRACT OF THE DISSERTATION

Verifiable Integrity and Availability for Code and Execution in Simple Embedded Systems

By

Ivan De Oliveira Nunes

Doctor of Philosophy in Networked Systems University of California, Irvine, 2021

Dr. Gene Tsudik, Chair

Modern society is increasingly surrounded by, and is growing accustomed to, a wide range of Cyber-Physical Systems (CPS), Internet-of-Things (IoT), and smart devices. They often perform safety-critical functions, e.g., personal medical devices, automotive CPS as well as industrial and residential automation (such as sensor-alarm combinations). On the lower end of the scale, these devices are small, cheap, and specialized sensors and/or actuators. They tend to host small CPUs, have small amounts of memory, and run simple software. If such devices are left unprotected, consequences of forged sensor readings or ignored actuation commands can be catastrophic, particularly, in safety-critical settings. This prompts the following questions: (1) How to trust data produced, or guarantee that actions will be performed, by a simple remote embedded device?, (2) How to bind actions and results to the execution of expected software? and, (3) Can (1) and (2) be attained even if all software on a device can be modified and/or compromised (e.g., by malware) at any given time?

This dissertation presents a set of hardware/software co-designs for obtaining several security services – namely remote attestation, TOCTOU-avoidance, proofs of execution, and root of trust availability – which can be used to assure the integrity and availability of software and its execution, even on some of the most resource-constrained micro-controllers. We realize these services with four formally verified and publicly available architectures (VRASED, RATA, APEX, and TAROT) and show how they have been securely implemented atop the TI MSP430 micro-controller at a relatively low-cost.

# Chapter 1

# Introduction

The number and diversity of special-purpose computing devices has been increasing dramatically. This includes all kinds of embedded devices, cyber-physical systems (CPS) and Internet-of-Things (IoT) gadgets, utilized in various "smart" or instrumented settings, such as homes, offices, factories, automotive systems, and public venues. Tasks performed by these devices are often safety-critical. For example, a typical industrial control system depends on physical measurements (e.g., temperature, pressure, humidity, speed) reported by sensors, and on actions taken by actuators, such as: turning on the A/C, sounding an alarm, or reducing speed.

A cyber-physical control system is usually composed of multiple sensors and actuators, at the core of each is a micro-controller unit (MCU), typically running simple software, often on "bare metal", i.e., with no microkernel or hypervisor. They tend to be operated by a remote central control unit and despite their potential importance to overall system functionality, low-end devices are typically designed to minimize cost, physical size and energy consumption.

A compromised MCU can spoof sensed quantities or ignore actuation commands, leading to

potentially catastrophic results. For example, in a *smart* city, large-scale erroneous reports of electricity consumption by smart meters might lead to power outages. A medical device that returns incorrect values when queried by a remote physician might result in a wrong drug being prescribed to a patient. A compromised car engine temperature sensor that reports incorrect (low) readings can lead to undetected overheating and major damage. Unfortunately, these examples are not theoretical or hypothetical. Actuation devices have been abused by malware to impact both security and safety in the Stuxnet [111] case. Whereas malware on sensors can undermine privacy by obtaining ambient information [51]. Furthermore, clever malware can turn vulnerable IoT devices into zombies that can become sources for DDoS attacks. For example, in 2016, a multitude of compromised *smart* cameras and DVRs formed the Mirai Botnet [12] which was used to mount a massive-scale DDoS attack (the largest in history). However, despite very real risks of remote software compromise, most users believe that these devices execute expected software and thus perform their expected function.

At the lower-end of the spectrum, MCUs are designed with extremely strict constraints on monetary cost, physical size, and energy consumption (e.g, TI MSP430<sup>1</sup> and Atmel ATMega AVR<sup>2</sup>). Therefore, it is unrealistic to expect such devices, by themselves, to prevent malware infection via sophisticated security mechanisms (e.g., similar to those available on laptops, smartphones, and other types of higher-end embedded devices).

To address this problem, several tiny Roots-of-Trust (RoTs) [49, 87, 10, 22, 68] were proposed to enable Remote Attestation (RA), i.e., remote verification of an embedded device's software state. These tiny RoTs are typically designed as hardware/software (hybrid) co-designs, aiming to achieve the same level of security of more expensive hardware-based architectures (see Chapter 2 for details) at much lower hardware cost. Despite substantial progress over the past decade, to the best of our knowledge, prior architectures have the following limitations:

<sup>&</sup>lt;sup>1</sup>http://www.ti.com/microcontrollers/msp430-ultra-low-power-mcus/applications.html <sup>2</sup>https://www.microchip.com/design-centers/8-bit/avr-mcus

- Little or no attention has been devoted to formal verification. In particular, no hybrid RA designs and implementations have been formally verified with respect to claimed security properties. We argue that the high-assurance and rigor derivable from utilizing computer-aided formal verification to guarantee security of the design and implementation of RA techniques can increase RA robustness and thus its potential for practical adoption.

- 2. Prior RA techniques verify the remote device at the time when RA functionality is executed, thus providing no information about the state of the device before the current RA execution or between consecutive RA executions. Therefore, presence of transient malware that infects the device and leaves prior to the next RA instance can not be detected. This important problem, called Time-Of-Check-Time-Of-Use (TOCTOU), is well-known in the research literature and remained unaddressed in the context of hybrid RA.

- 3. Prior techniques can be used to prove that a given binary is present on a remote device, but cannot prove successful execution of that binary. They are also cannot bind claimed execution outputs/results (e.g., a sensed value) to the correct execution of the attested binary (e.g., a sensing task).

- 4. All prior techniques *operate reactively*. Therefore, they can not *guarantee* that a desired action *will be performed*, since malware controlling the device can trivially block access to the RoT by ignoring/discarding received commands. This is a major and important problem because it allows malware to effectively "brick" or incapacitate a potentially huge number of (possibly mission-critical) devices.

In this dissertation we address these limitations by presenting four core architectures. Specifically, we describe the design, implementation, and formal verification of:

1. VRASED: the first formally verified hybrid RA architecture.

- 2. *RATA*: the first hybrid RA architecture secure against TOCTOU attacks.

- 3. *APEX*: an architecture for generating unforgeable proofs of software execution in lowend embedded systems.

- 4. *TAROT*: an active RoT architecture, which guarantees that safety-critical tasks are always performed upon specific trigger-s, despite compromise of the MCU application software.

#### 1.1 Dissertation Structure

Chapter 2 overviews concepts that are relevant to the dissertation as a whole, including its scope, the foundational security service – Remote Attestation (RA) – and the proof strategy and verification methodology used to argue security of architectures proposed in the following chapters. Chapter 3 presents *VRASED*: a verified hardware/software co-design for remote attestation targeting low-end embedded devices. Chapter 4 provides a systematic treatment and a formal definition for the Time-Of-Check Time-Of-Use (TOCTOU) problem in RA, as well as *RATA*: a hardware component that makes hybrid RA techniques TOCTOU-Secure (e.g., it detects presence of transient malware). Chapter 5 focuses on the problem of proving correct execution of attested software in a low-end embedded device, a functionality referred to as Proof of Execution (PoX). This chapter presents *APEX*: a formally verified PoX architecture built atop (and securely composed with) *VRASED*. Next, Chapter 6 explores guaranteed execution of expected safety-critical tasks/actions on low-end MCUs. It introduces TAROT: a trigger-based active root of trust that is also formally specified and verified.

We note that Chapter 2 only includes background on topics relevant to the dissertation as a whole. Background specific to a particular chapter is provided within that chapter. Similarly, system and adversary models are defined on a per-chapter basis. For the most part, notation is consistent across chapters.

# Chapter 2

# Background

#### Abstract

This chapter overviews background concepts for dissertation. We start, in Section 2.1, by defining the scope of targeted devices. We motivate this choice and discuss some general intended contributions (specific contributions are outlined in subsequent chapters). Next, in Section 2.2, we overview Remote Attestation (RA): a security service that enables verification of the software state of a potentially compromised remote device – a prover ( $\mathcal{P}rv$ ) – by a trusted verifier ( $\mathcal{V}rf$ ). RA also serves as a foundation to many other security services. We review RA in detail since one of the contributions presented in this dissertation is VRASED (Chapter 3): a formally verified RA architecture. Additionally, Chapter 4 discusses an important RA security feature (RA TOCTOU-Security) and Chapter 5 develops a verified architecture for proofs of execution that is built upon RA. Lastly, in Section 2.3, we present the formal verification methodology and proof strategy used across the remaining chapters to prove security of the proposed security architectures at both protocol and implementation levels. We note that this chapter only overviews concepts that are relevant to the dissertation as a whole. Concepts and definitions that are only relevant or applicable to a particular chapter are discussed within that chapter.

#### 2.1 Scope: Low-end Embedded Devices

This work focuses on CPS/IoT sensors and actuators (or hybrids thereof) with low computing power. These are some of the smallest and weakest devices based on low-power single-core Micro-Controller Units (MCUs) with only a few KBytes of program and data memory. Two prominent examples are: Atmel AVR ATmega and TI MSP430: 8- and 16-bit CPUs, typically running at 1-16MHz clock frequencies, with  $\approx 64$  KBytes of addressable memory. SRAM is used as data memory with the size normally ranging between 4 and 16KBytes, while the rest of address space is available for program memory. They have neither Memory Management Units (MMUs) to support virtual memory nor Memory Protection Units (MPUs) to control access to any parts of memory. They also lack architectural support for privileged/exception layers. Therefore, such devices usually run software atop "bare metal" and execute instructions in place (physically from program memory).

In terms of practicality and applicability, we believe that a security architecture suitable for these lowest-end MCU-s could be adapted (and potentially enriched) for higher-end devices with larger hardware budgets, while the other direction is more challenging. In addition, simpler devices are easier to model and reason about formally. Hence, they represent a good starting point for the design and verification of provably secure architectures such as the ones proposed in this work.

Our implementations are based on MSP430. This choice is due to public availability of a well-maintained open-source MSP430 hardware design from Open Cores [56]. Nevertheless, we believe that our machine models and methodology are applicable to other low-end MCUs in the same class, such as Atmel AVR ATmega. We also hope that some lessons learned in this work can be useful to design and prove security of similar services targeting higher-end devices in the future.

#### 2.2 Attestation in Low-end Devices

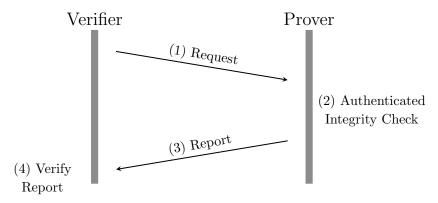

Attestation facilitates detection of malware presence on a remote device. Specifically, it allows a trusted verifier ( $\mathcal{V}rf$ ) to remotely measure the software state of an untrusted remote device ( $\mathcal{P}rv$ ). As shown in Figure 2.1, attestation is typically obtained via a simple challenge-response protocol:

- 1.  $\mathcal{V}$ rf sends an attestation request containing a challenge ( $\mathcal{C}$ hal) to  $\mathcal{P}$ rv. This request might also contain a token derived from a secret that allows  $\mathcal{P}$ rv to authenticate  $\mathcal{V}$ rf.

- Prv receives the attestation request and computes an *authenticated integrity check* over its memory and Chal. The memory region might be either pre-defined, or explicitly specified in the request.

- 3.  $\mathcal{P}rv$  reports the result to  $\mathcal{V}rf$ .

- 4.  $\mathcal{V}rf$  receives the result from  $\mathcal{P}rv$ , and checks whether it corresponds to a valid memory state.

Figure 2.1: Attestation interaction

The authenticated integrity check can be realized as a Message Authentication Code (MAC) over  $\mathcal{P}rv$ 's memory. Computing a MAC requires  $\mathcal{P}rv$  to have a unique secret key, denoted by  $\mathcal{K}$  – either a symmetric key shared with  $\mathcal{V}rf$ , or a private key for which the corresponding public key is known to  $\mathcal{V}rf$ . In this dissertation we assume the former, noting that security differences between the two cases are small. This  $\mathcal{K}$  must reside in secure storage, where it is

**not** accessible to any software running on  $\mathcal{P}rv$ , except for trusted and typically immutable attestation code (or attestation hardware engine, when present). Since most RA threat models assume a fully compromised software state on  $\mathcal{P}rv$ , secure storage implies some level of hardware support. Most attestation techniques fall into three groups: software-based, hardware-based, and hybrid.

Software-based (or timing-based) attestation is the only viable approach for legacy devices with no hardware security features. Without hardware support, it is (currently) impossible to guarantee that  $\mathcal{K}$  is not accessible by malware that fully compromises  $\mathcal{P}rv$  software state. Therefore, security of software-based approaches [98, 76] is attained by setting strict thresholds for communication delays between  $\mathcal{V}rf$  and  $\mathcal{P}rv$  (instead of relying on cryptographic secrets). Thus, software-based attestation is unsuitable for multi-hop and jitter-prone communication (not remote), or settings where a compromised  $\mathcal{P}rv$  is aided (during attestation) by a more powerful accomplice device. It also requires strong constraints and assumptions on the hardware platform and attestation usage [71, 75].

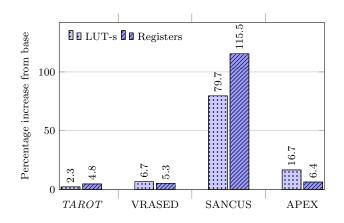

Hardware-based approaches, on the other extreme, enable attestation to happen remotely but require either i)  $\mathcal{P}rv$ 's attestation functionality to be housed entirely within dedicated hardware, e.g., Trusted Platform Modules (TPMs) [109]; or ii) modifications to the CPU semantics or instruction sets to support the execution of trusted software, e.g., SGX [64] or TrustZone [14]. Such hardware features are too expensive (in terms of physical area, energy consumption, and actual cost) for low-end devices. SANCUS [87] developed a hardwarebased RA architecture specifically targeting low-end devices (MSP430, in particular). However, its footprint is heavy, increasing the total hardware cost by more than 100% that of the unmodified MSP430 CPU core.

While neither hardware- nor software-based approaches are well-suited for settings where low-end devices are not directly connected (e.g, remote IoT settings), **hybrid** RA (based on HW/SW co-design) is a more promising approach. **Hybrid** RA aims at providing the same security guarantees as hardware-based techniques with minimal hardware support. SMART [49] is the first hybrid RA architecture targeting low-end MCUs. In SMART, the authenticated integrity check is implemented in software. SMART's small hardware footprint guarantees that the attestation code runs safely and that the attestation key is not leaked. HYDRA [48] is a hybrid RA scheme that relies on a secure boot hardware feature and on a formally verified secure micro-kernel. Trustlite [68] modifies MPU and CPU exception engine hardware to implement RA on the Intel Siskiyou Peak research platform [108]. Tytan [22] is built on top of Trustlite, extending its capabilities for applications with real-time requirements.

Most RA architectures (including the ones mentioned thus far) focus on measuring a snapshot of  $\mathcal{P}rv$ 's memory at the time of the attestation computation<sup>1</sup>. As such, they are useful to measure executables, i.e., to prove to  $\mathcal{V}rf$  that a particular binary is currently installed on  $\mathcal{P}rv$ . however, they are usually insufficient to prove execution or execution properties. For example, they can not prove that the attested binary is ever executed. Additionally, consider runtime/data-oriented attacks [106] that tamper with execution state on the program's stack or heap to arbitrarily divert the program's execution flow and/or corrupt computation results. Such attacks need not modify the executable itself. Thus, they are not detectable by RA alone. Runtime attacks can be launched by a variety of means. For instance, in languages such as C, C++, and Assembly (which are widely used to program MCU-s), buffer overflows [39] can overwrite functions' return addresses, hijacking the program's control-flow and launching well-known Return-Oriented Programming (ROP) attacks [102]. These attacks are especially dangerous for low-end MCU-s that can not avail themselves of more sophisticated OS-based mitigations, e.g., canaries, Address Space Layout Randomization (ASLR), and Control-Flow Integrity (CFI) techniques, available in high-end platforms.

<sup>&</sup>lt;sup>1</sup>We note that the term RA may be used more broadly to refer to other forms of attestation (e.g., content attestation). In the context of this dissertation, RA reffers specifically to a service used to measure memory in remote devices.

**Runtime attestation** [6, 45, 44, 116, 43, 105, 91], including both control-flow attestation (CFA) and data-flow attestation (DFA), augments RA capability to enable detection of control-flow and data-only attacks. In a nutshell, CFA techniques provide  $\mathcal{V}rf$  with a report that allows it to not only learn if the expected code is loaded on  $\mathcal{P}rv$ , but also which particular instruction path was taken during each execution of this program. In other words, CFA provides  $\mathcal{V}rf$  with an authentic and unforgeable report that allows  $\mathcal{V}rf$  to learn if instructions of a given program were executed in a particular expected/legal order, or a set thereof. This is typically achieved by securely logging information associated with the destination of each control-flow altering instruction, e.g., jumps, branches, returns, during program execution. Similarly, DFA allows  $\mathcal{V}rf$  to detect whether intermediate computation values (e.g., stored in local variables) were corrupted throughout the attested program's execution by securely logging modifications to these variables into an authenticated report log.

Prior CFA and DFA techniques have been implemented on medium- to high-end embedded devices (e.g., Raspberry Pi, and RISC-V based processors), by leveraging trusted hardware support, such as ARM TrustZone (in [6, 105]) or hardware branch monitors/hardware hash engines (in [45, 44, 116]). However, for the lowest-end MCU-s, these requirements are too costly, as their hardware overhead is often higher than the total cost of the MCU's core itself, in terms of size, energy and monetary cost.

Despite much progress, a major missing aspect in RA research is high-assurance and rigor obtained by using formal methods to guarantee security of a concrete RA design and its implementation (hardware and software). We believe that verifiability and formal security guarantees are particularly important for hybrid RA designs aimed at low-end embedded and IoT devices, as hybrid designs are hard to implement correctly and their proliferation keeps growing. This serves as the main motivation for our efforts to develop a formally verified RA architecture (Chapter 3) and subsequent verified TOCTOU-Secure RA architecture (Chapter 4) which enhances hybrid RA against migratory and self-relocating malware, as well as makes RA substantially more efficient.

Given the lack of suitable approaches to prove execution properties in low-end devices, our work also proposes the development and formal verification of an architecture for proofs of execution (Chapter 5) in low-end devices. In subsequent work [43, 91], this architecture was also shown to be sufficient, as the only hardware feature, to obtain CFA and DFA.

Finally, we observe that the aforementioned architectures focus on the problem of "proving integrity", i.e., they offer proofs for  $\mathcal{P}rv$ 's state or that actions (e.g., execution, updates, erasure & reset/reboot [41, 9, 15]) have happened. However, they can not guarantee that actions/commanded tasks will be performed by a low-end (and potentially compromised)  $\mathcal{P}rv$ . This problem – related to **availability** – is the focus of Chapter 6.

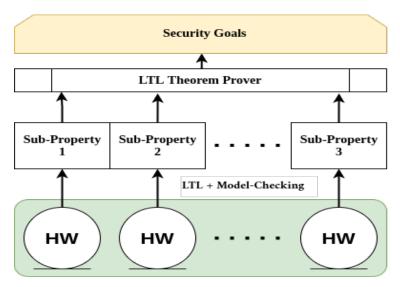

# 2.3 Linear Temporal Logic, Model Checking, and Formal Verification

Computer-aided formal verification typically involves three basic steps. First, the system of interest (e.g., hardware, software, communication protocol) is described using a formal model, e.g., a Finite State Machine (FSM). Second, properties that the model should satisfy are formally specified. Third, the system model is checked against formally specified properties to guarantee that the system retains them. This can be achieved by either Theorem Proving [79] or Model Checking [36]. In this work, we use the latter to verify the implementation of system sub-modules, and the former to prove new properties derived from the combination (conjunction) of machine model axioms and sub-properties that were proved for the implementation of individual sub-modules.

In one instantiation of model checking, properties are specified as *formulae* using Linear

Temporal Logic (LTL) and system models are represented as FSMs. Hence, a system is represented by a triple  $(S, S_0, T)$ , where S is a finite set of states,  $S_0 \subseteq S$  is the set of possible initial states, and  $T \subseteq S \times S$  is the transition relation set – it describes the set of states that can be reached in a single step from each state. The use of LTL to specify properties allows representation of expected FSM behavior over time.

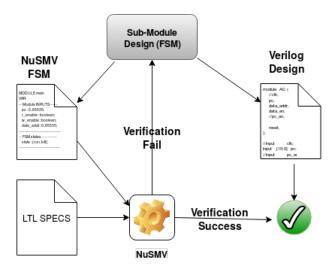

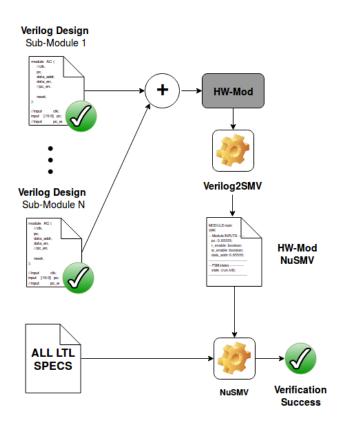

Our verification strategy applies the widely used model checker NuSMV [34], geared for verifying generic HW or SW models. For digital hardware described at Register Transfer Level (RTL) – which is the case in this work – conversion from Hardware Description Language (HDL) to NuSMV models is simple. Furthermore, it can be automated [65], because the standard RTL design already relies on describing hardware as an FSM. We rely on this automated verification pipeline to verify several sub-modules of all architectures discussed in this dissertation. Details of this pipeline are presented in Chapter 3.

LTL specifications are is particularly useful for verifying sequential systems. In addition to propositional connectives, such as conjunction ( $\wedge$ ), disjunction ( $\vee$ ), negation ( $\neg$ ), and implication ( $\rightarrow$ ), LTL extends propositional logic with **temporal quantifiers**, thus enabling sequential reasoning. In this work, we are interested in the following LTL quantifiers:

- $\mathbf{X}\phi \mathrm{ne}\underline{X}\mathrm{t}\phi$ : holds if  $\phi$  is true at the next system state.

- $\mathbf{F}\phi \underline{\mathbf{F}}$ uture  $\phi$ : holds if there exists a future state where  $\phi$  is true.

- $\mathbf{G}\phi \underline{\mathbf{G}}$  lobally  $\phi$ : holds if for all future states  $\phi$  is true.

- $\phi \mathbf{U} \psi \phi \underline{\mathbf{U}}$ ntil  $\psi$ : holds if there is a future state where  $\psi$  holds and  $\phi$  holds for all states prior to that.

- $\phi \mathbf{W} \psi \phi \mathbf{W}$ eak until  $\psi$ : holds if, assuming a future state where  $\psi$  holds,  $\phi$  holds for all states prior to that. If  $\psi$  never becomes true,  $\phi$  must hold forever. Or, more formally:  $\phi \mathbf{W} \psi \equiv (\phi \mathbf{U} \psi) \lor \mathbf{G}(\phi)$

- $\phi \mathbf{B} \psi \phi \underline{\mathbf{B}}$ efore  $\psi$ : holds if the existence of state where  $\psi$  holds implies the existence of an earlier state where  $\phi$  holds. This temporal quantifier can be expressed using **U**

through the equivalence:  $\phi \mathbf{B} \psi \equiv \neg(\neg \phi \mathbf{U} \psi)$ .

This set of temporal connectives combined with propositional connectives (with their usual meanings) allows us to specify powerful rules. NuSMV works by checking LTL specifications against the system FSM for all reachable states in such FSM.

A model checker (NuSMV in our case) performs proofs through automated and exhaustive enumeration of all possible system states. If the desired specification is found not to hold for specific states (or transitions between states), a trace of the model that leads to the erroneous state is provided, and the implementation can then be fixed accordingly. As a consequence of exhaustive enumeration, proofs for complex systems that involve complex properties often do not scale well due to so-called "state explosion" problem.

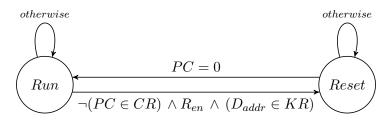

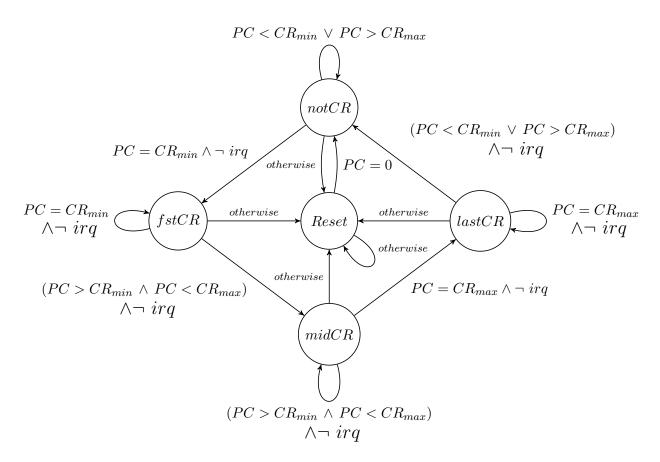

To cope with this problem, our verification approach is to specify smaller LTL sub-properties separately and verify each respective sub-module for compliance. In this process, our verification pipeline automatically converts digital hardware, described at RTL using Verilog, to Symbolic Model Verifier (SMV) [85] FSMs using Verilog2SMV [65] (see Chapter 3 for details). The SMV representation is then fed to NuSMV [35] for verification. Finally, the composition of the LTL sub-properties (verified in the model checking phase) is proven to achieve the end-to-end implementation goals (which are more complex LTL statements) of the particular system using an LTL theorem prover [47]. The verification strategy is depicted in Figure 2.2.

Depending on the security service, end-to-end goals for the implementation may themselves capture the overall security definition (e.g., Chapter 6) for the system. In other cases, especially when security depends on cryptographic assumptions, end-to-end implementation goals are required so that a cryptographic security proof (e.g., cryptographic reduction) holds. The latter is the case in Chapters 3, 4, and 5.

Figure 2.2: Overall Verification strategy

# Chapter 3