## UC Irvine UC Irvine Electronic Theses and Dissertations

#### Title

Towards Engineering Computer Vision Systems: From the Web to FPGAs

#### Permalink

https://escholarship.org/uc/item/78b6q2wv

Author Taheri, Sajjad

Publication Date 2019

#### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Towards Engineering Computer Vision Systems: From the Web to FPGAs

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Sajjad Taheri

Dissertation Committee: Professor Alexandru Nicolau, Chair Professor Alexander Veidenbaum, Co-chair Professor Nikil Dutt

© 2019 Sajjad Taheri

# DEDICATION

To my mother, Nahid.

# TABLE OF CONTENTS

|                        | F                                                                                                                                                                                                                                                                                                                                                         | Page                                          |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| $\mathbf{L}\mathbf{I}$ | IST OF FIGURES                                                                                                                                                                                                                                                                                                                                            | $\mathbf{v}$                                  |

| LI                     | LIST OF TABLES vii                                                                                                                                                                                                                                                                                                                                        |                                               |

|                        | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                            |                                               |

| A                      | CKNOWLEDGMENIS                                                                                                                                                                                                                                                                                                                                            | viii                                          |

| $\mathbf{C}$           | URRICULUM VITAE                                                                                                                                                                                                                                                                                                                                           | ix                                            |

| $\mathbf{A}$           | BSTRACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                               | xi                                            |

| 1                      | Introduction         1.1       Challenges of Portable and Efficient Computer Vision         1.2       Thesis Contributions         1.2.1       Regarding Software Quality                                                                                                                                                                                 | $egin{array}{c} 1 \\ 3 \\ 4 \\ 7 \end{array}$ |

| 2                      | OpenCV.js: Computer Vision Processing for the Open Web platform         2.1       Introduction         2.2       Compiling to The Web         2.2.1       Portable Low-level Formats for Web Compilation         2.3       Generating OpenCV.js         2.4       Using OpenCV.js         2.5       Performance Evaluation         2.6       Availability | 8<br>8<br>10<br>12<br>16<br>20<br>23<br>27    |

| 3                      | Parallel Processing in OpenCV.js3.1Parallel Processing using ECMAScript SIMD3.2Thread-level Parallelism Using Web Workers                                                                                                                                                                                                                                 | <b>28</b><br>29<br>31                         |

| 4                      | A Library for FPGA Implementation of Vision Algorithms         4.1 Introduction to OpenVX         4.1.1 Examples         4.2 A Computer Vision Library for FPGAs         4.2.1 FPGA Technology and High-level Synthes         4.2.2 Library Design and Implementation         4.2.3 Programming Interface                                                 | <b>34</b><br>35<br>40<br>44<br>44<br>47<br>54 |

| <b>5</b> | A F   | camework for FPGA Acceleration of Computer Vision Algorithms | 56 |

|----------|-------|--------------------------------------------------------------|----|

|          | 5.1   | High-Level Optimizing Transformations                        | 58 |

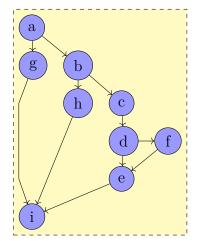

|          | 5.2   | Pipelining using Graph Partitioning                          | 62 |

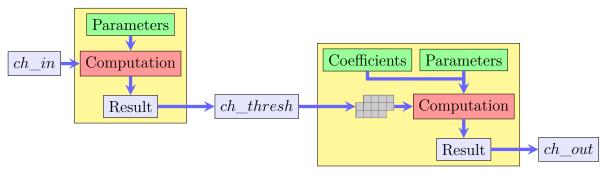

|          |       | 5.2.1 Data Streaming Patterns                                | 66 |

|          | 5.3   | FPGA-Specific Optimizing Transformations                     | 68 |

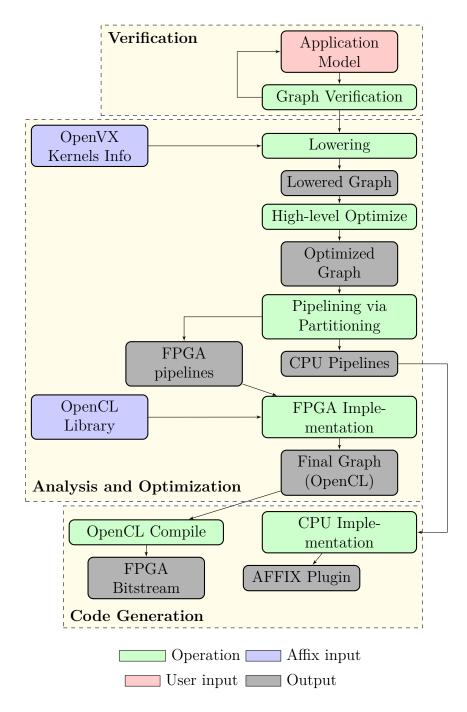

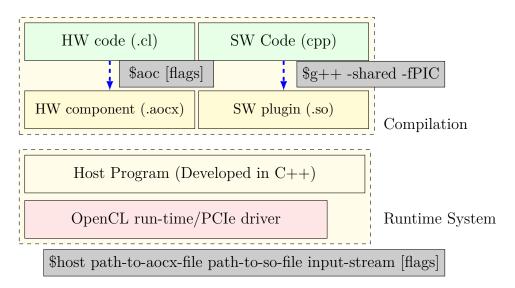

|          | 5.4   | Automatic Flow                                               | 70 |

|          | 5.5   | Usage and Software Architecture                              | 73 |

|          |       | 5.5.1 User-Defined Kernels                                   | 74 |

|          | 5.6   | Evaluation                                                   | 75 |

|          | 5.7   | Availability                                                 | 83 |

| 6        | Con   | clusions and Future Directions                               | 84 |

| Bi       | bliog | raphy                                                        | 87 |

# LIST OF FIGURES

## Page

| $     \begin{array}{l}       1.1 \\       1.2 \\       1.3 \\       1.4     \end{array} $                          | Camera sensor size trend                                                                                                                 | $2 \\ 2 \\ 4 \\ 5$                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>2.1</li> <li>2.3</li> <li>2.2</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol> | Number of JavaScript lines of code in Gmail source code                                                                                  | $     \begin{array}{r}       11 \\       12 \\       12 \\       13 \\       13 \\       14 \\       15 \\       16 \\     \end{array} $ |

| 2.9<br>2.10                                                                                                        | Compilation of a sample $C++$ program into WASM by Emscripten<br>OpenCV.js components and its interactions with web applications and web | 17                                                                                                                                       |

| 2.11<br>2.12<br>2.13<br>2.14<br>2.15<br>2.16<br>2.17                                                               | APIs                                                                                                                                     | <ol> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>24</li> <li>25</li> <li>26</li> <li>27</li> <li>27</li> </ol>                   |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Scalar vs SIMD addition of four integers                                                                                                 | 29<br>30<br>31<br>32<br>32<br>33                                                                                                         |

| 4.1  | Typical OpenVX use cases                                                  | 36 |

|------|---------------------------------------------------------------------------|----|

| 4.2  | OpenVX graph lifecycle                                                    | 37 |

| 4.3  | Vision function data access patterns                                      | 38 |

| 4.4  | An image pyramid with four levels                                         | 40 |

| 4.5  | Lane detection algorithm example                                          | 41 |

| 4.6  | Lane detection algorithm graph                                            | 42 |

| 4.7  | Demonstration of lane detection algorithm                                 | 42 |

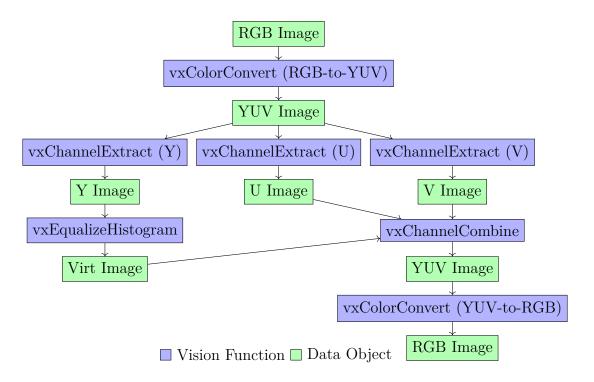

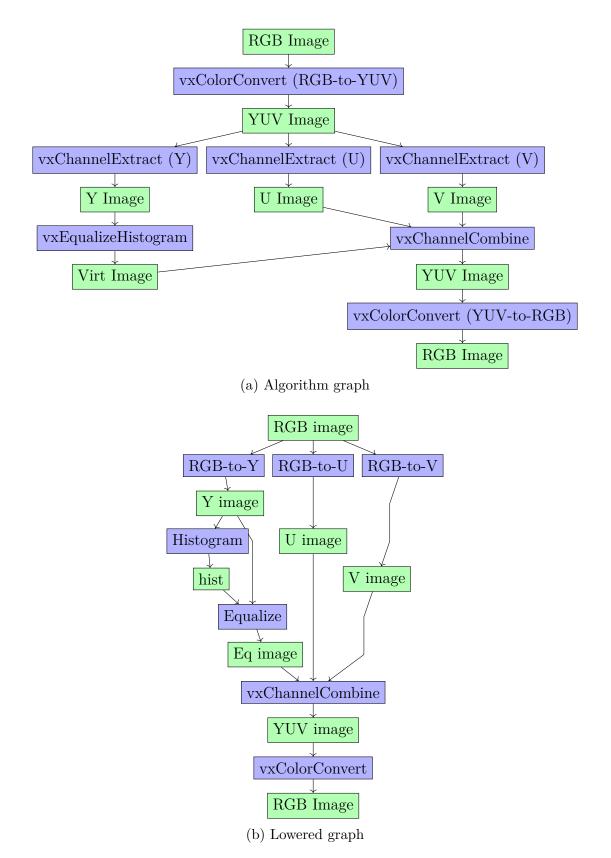

| 4.8  | Automatic contrast algorithm graph                                        | 43 |

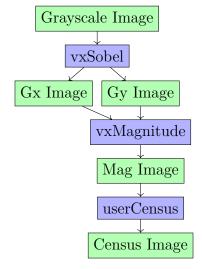

| 4.9  | Census transform algorithm graph                                          | 43 |

| 4.10 | Synthesis of a sample OpenCL kernel                                       | 46 |

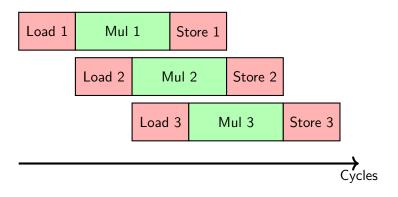

| 4.11 | Effect of pipelinig in FPGA synthesis of loops                            | 47 |

| 4.12 | Using the line buffer for streaming image processing                      | 50 |

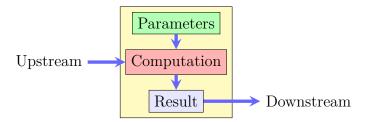

|      | General implementation of pixel-wise kernels                              | 50 |

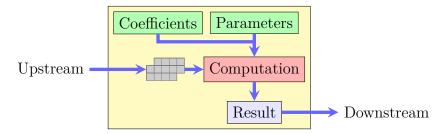

|      | General implementation of stencil kernels                                 | 50 |

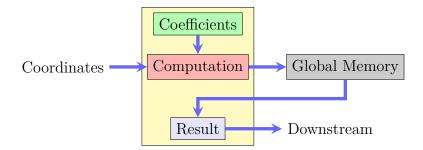

| 4.15 | General implementation of gemotric transformation kernels                 | 51 |

| 4.16 | General implementation of statistical kernels                             | 51 |

| 4.17 | Comparison of kernel communication mechanism                              | 52 |

| 4.18 | Comparison of host FPGA transfer mechanisms                               | 53 |

| 4.19 | Describing a simple FPGA pipeline with the proposed library API           | 55 |

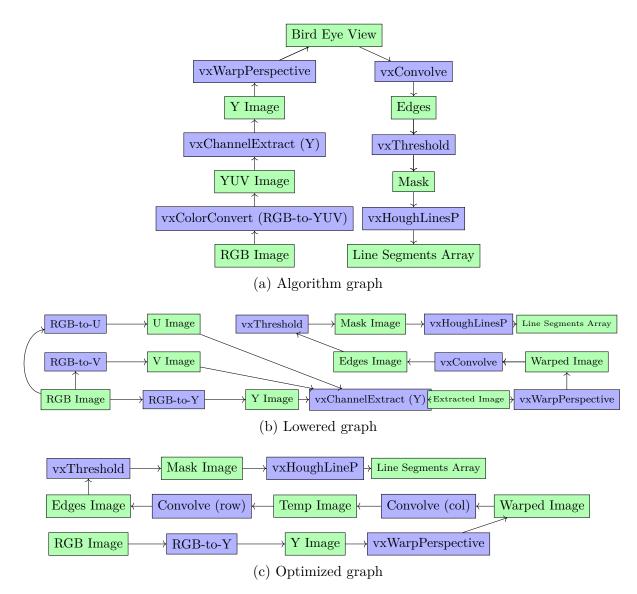

| 5.1  | High level optimization of lane detection algorithm                       | 60 |

| 5.2  | High level optimization of Automatic contrast algorithm                   | 61 |

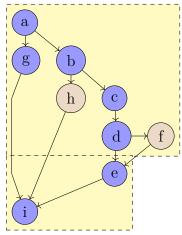

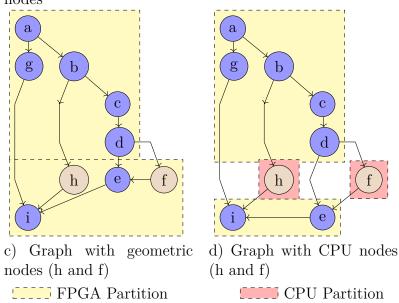

| 5.3  | Partitioning of a sample algorithm graph with different vision node types | 01 |

| 0.0  | composition                                                               | 64 |

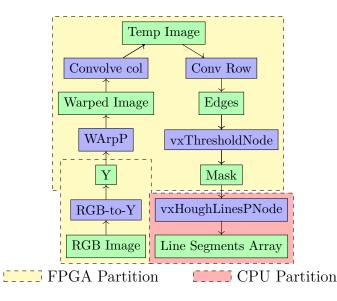

| 5.4  | Partitioning of the lane detection algorithm graph                        | 66 |

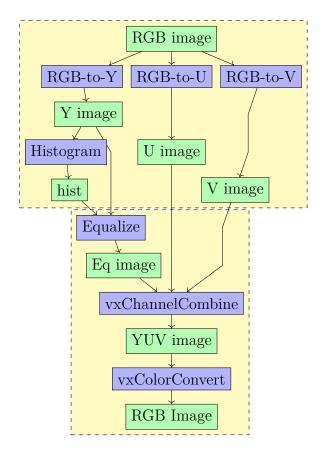

| 5.5  | Partitioning of automatic contrast algorithm graph                        | 67 |

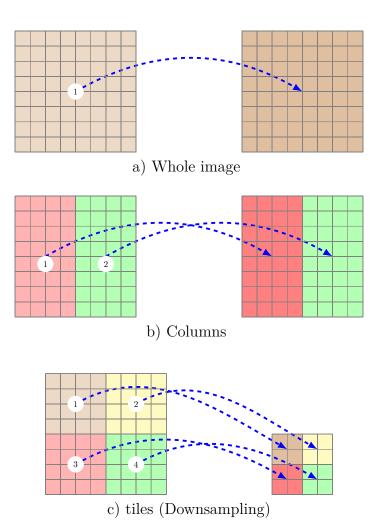

| 5.6  | Different policies to partition and stream the images                     | 69 |

| 5.7  | Simplified OpenCL code for FPGA implementation of the lane detection al-  | 00 |

| 0    | gorithm example                                                           | 71 |

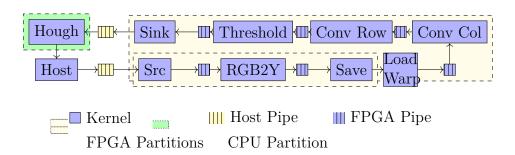

| 5.8  | Visualization of the generated system for lane detection algorithm graph  | 71 |

| 5.9  | AFFIX framework flow                                                      | 72 |

| 5.10 | AFFIX software architecture and components                                | 74 |

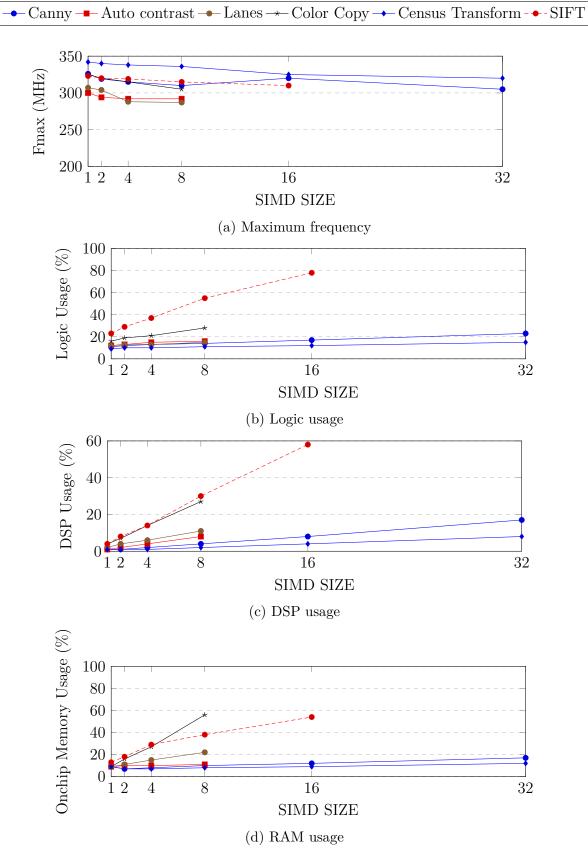

| 5.11 | Arria 10 resource utilization and maximum working frequency of algorithms |    |

| -    | with different SIMD width                                                 | 81 |

## LIST OF TABLES

## Page

| $2.1 \\ 2.2$        | OpenCV.js modules and provided functions                                                                                        | 18<br>23 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1                 | ECMAScript SIMD types and operations                                                                                            | 30       |

| 4.1                 | Categorization of supported OpenVX vision functions                                                                             | 39       |

| $5.1 \\ 5.2 \\ 5.3$ | Logic saving of separable implementation of 2D filters                                                                          | 70<br>76 |

| - 1                 | different SIMD width                                                                                                            | 79       |

| 5.4                 | Throughput per Energy (MegaBytes per Joule) comparison of CPU and Ar-<br>ria10 accelerated algorithms with different SIMD width | 79       |

| 5.5                 | Design power consumption (Watts) of CPU and Arria10 accelerated algorithms with different SIMD width                            | 82       |

## ACKNOWLEDGMENTS

I am grateful to my advisors, professor Alex Nicolau and professor Alex Veidenbaum, for their patience, support, and guidance.

I would like to thank Professor Nikil Dutt for his participation in the thesis committee and providing helpful feedback.

I feel fortunate to receive mentorship from Dr. Moh Haghighat, senior principal engineer at Intel. He was always a source of inspiration and motivation for me.

I would like to shout out to my colleagues and partners in crime, Hoda Malekpour, Zhi Chen, Maral Amir, Majid Shoushtari, Bryan Donyanavard, Hamid Nejatollahi, Payman Behnam, Jin Heo, Siavash Rezaei, Laleh Beni, Tiago Muck, Aniket Shivam, Gongjin Sun, and Junjie Shen for their friendship and for sharing the pain.

I would like to thank Ningxin Hu and our Google Summer of Code interns for putting a tremendous effort during the release process of OpenCV.js.

This research was financially supported by UC Irvine graduate division and Intel corporation.

## CURRICULUM VITAE

## Sajjad Taheri

#### **EDUCATION**

| <b>Doctor of Philosophy in Computer Science</b> | <b>2019</b>          |

|-------------------------------------------------|----------------------|

| University of California, Irvine                | <i>Irvine, CA</i>    |

| Bachelor of Science in Computer Engineering     | <b>2010</b>          |

| University of Tehran                            | <i>Tehran, Iran</i>  |

| RESEARCH EXPERIENCE                             |                      |

| <b>Graduate Student Researcher</b>              | <b>2014–2019</b>     |

| University of California, Irvine                | <i>Irvine, CA</i>    |

| TEACHING EXPERIENCE                             |                      |

| <b>Teaching Assistant</b>                       | <b>2015–2019</b>     |

| University of California, Irvine                | <i>Irvine, CA</i>    |

| INDUSTRY EXPERIENCE                             |                      |

| Mentor                                          | June 2017–Sept. 2017 |

| Coogle Summer of Code                           | Inving $CA$          |

Google Summer of Code

Software Engineering Intern Mozilla

June 2017–Sept. 2017 Irvine, CA

June 2015–Sept. 2015 Mountain View, CA

#### **REFEREED JOURNAL PUBLICATIONS**

| Computer Vision for the Masses<br>Intel Parallel Universe (April 2018 Issue)                                                                                               | 2018                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                           |                     |

| AFFIX: Automatic Acceleration Framework for FPGA<br>Implementation of OpenVX Vision Algorithms<br>ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPG | <b>2019</b><br>GA)  |

| Acceleration framework for fpga implementation of<br>OpenVX graph pipelines<br>IEEE International Symposium on Field-Programmable Custom Computing Mach<br>(FCCM)          | <b>2018</b><br>ines |

| <b>OpenCV.js: Computer vision processing for the open</b><br><b>web platform</b><br>ACM International Conference on Multimedia Systems (MMSys)                             | 2018                |

| WebRTCbench: A benchmark for performance assess-<br>ment of webRTC implementations<br>IEEE Embedded Systems for Real-Time Multimedia (ESTIMedia)                           | 2015                |

#### SOFTWARE

| OpenCV.js                             | https://github.com/ucisysarch/opencvjs |

|---------------------------------------|----------------------------------------|

| A computer vision library for the web |                                        |

| AFFIV                                 | https://mithub.com/aciiodt/offin       |

AFFIX https://github.com/sajjadt/affix A framework for FPGA acceleration of computer vision algorithms

## ABSTRACT OF THE DISSERTATION

Towards Engineering Computer Vision Systems: From the Web to FPGAs

By

Sajjad Taheri

Doctor of Philosophy in Computer Science University of California, Irvine, 2019 Professor Alexandru Nicolau, Chair

Computer vision is an interdisciplinary field to obtain high-level understanding from digital images. It has many applications that impact our daily lives, such as automation, entertainment, healthcare, etc. However, computer vision is very challenging. This is in part due to the intrinsically difficult nature of the problem and partly due to the complexity and size of visual data that need to be processed. To be able to deploy computer vision in many practical use cases, sophisticated algorithms and efficient implementations are required.

In this thesis, we consider two platforms that are suitable for computer vision processing, yet they were not easily accessible to algorithm designers and developers: the Web and FPGA-based accelerators. Through the development of open-source software components, we highlight challenges associated with vision development on each platform and demonstrate opportunities to mitigate them.

The Web is the world's most ubiquitous computing platform which hosts a plethora of visual content. Due to historical reasons such as insufficient compute performance and lack of API support for acquiring and manipulating images, computer vision is not mainstream on the Web. We show that in light of recent web developments such as vastly improved JavaScript performance and the addition of APIs such as WebRTC, efficient computer vision processing can be realized on web clients. Through novel engineering techniques, we translate a popular

open-source computer vision library (OpenCV) from C++ to JavaScript and optimize its performance for the web environment. We demonstrate that hundreds of computer vision functions run in browsers with performance close to their original C++ version. We believe this will result in an immersive and perceptual web with transformational effects, including in online shopping, education, and entertainment, among others.

Field Programmable Gate Arrays (FPGA)s are a promising solution to mitigate the computational cost of vision algorithms through hardware pipelining and parallelism. However, an efficient FPGA implementation of computer vision algorithms requires hardware design expertise and a considerable amount of engineering person-hours. We show that graph-based specifications, such as OpenVX can significantly improve FPGA design productivity. Since such abstraction lacks implementation details, a vision algorithm designer can only focus on the algorithm itself and rely on another party with hardware knowledge to implement the design efficiently on a specific platform. During this process, different implementation configurations that satisfy various design constraints, such as performance and power consumption, can be explored. Furthermore, the graph-based model permits system-level optimizations that are not possible with traditional function-level acceleration. Towards this goal, we develop a framework that optimizes and implements vision algorithms that are described in OpenVX spec on different FPGA architectures. This framework hides low-level hardware optimization and implementation details from computer vision algorithm designers and enables them to quickly develop and verify FPGA implementations of vision algorithms without sacrificing performance.

# Chapter 1

# Introduction

Computer or machine vision is a field of computer science that brings solutions for computers to extract high-level understanding from images. Scientists in this field are trying to improve the quality and quantity of understanding, automate this process, and develop highperformance, and energy-efficient implementations. Computer vision has an ever-increasing number of applications in our daily life. It has wide usage in object detection [83, 59], face recognition [100, 73], autonomous vehicles [32, 45], and health care [33]. Emerging technologies such as Virtual and Augmented Reality (VR and AR) involve numerous computer vision algorithms for tracking, scene understanding, and scene construction [34, 13, 72, 65].

Over the past few decades, several technical advances have contributed significantly to the field of computer vision:

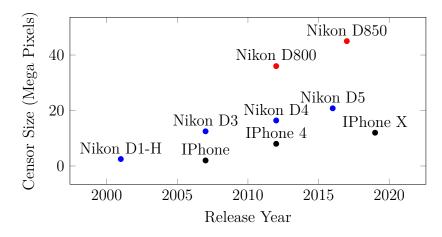

Availability of CMOS sensors with high resolution to capture high-quality images. For instance, as Figure 1.1 shows, the quality of sensors has increased over several years. High-quality digital cameras capture images details measure the difference between colors with very high accuracy.

Figure 1.1: Camera sensor size trend

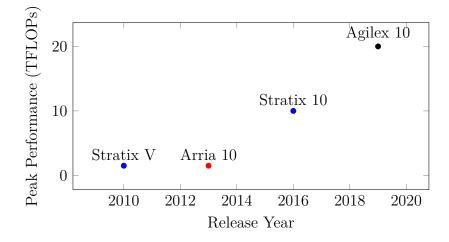

Figure 1.2: Floating-point operation performance of modern FPGAs

- 2. Availability of faster hardware with parallel processing capabilities: Computer vision algorithms exhibit inherent parallelism such that the same set of operations applies to each pixel. Parallel hardware has always been promising solutions for vision algorithms. SIMD processors, GPUs, FPGAs, and specialized ASIC designs can improve performance and power consumption orders of magnitude. Applying stateof-the-art algorithms on large data requires powerful hardware. Figure 1.2 shows the floating-point performance improvement of several high-end FPGAs released by Intel during recent years.

- 3. Software stack and open-source libraries that facilitates building computer vi-

sion systems without reinventing the infrastructure has led to a dramatic increase in software development productivity [16, 49, 101].

- 4. Advances in deep learning: Neural networks can learn the relationships between inputs and outputs that are often nonlinear. After AlexNet breakthrough performance in 2012 [55], Convolutional Neural Networks (CNNs) got huge attention and wide usage. They significantly improve decision processes in different areas such as object detection and classification and are now considered state-of-the-art techniques.

- 5. Availability of large image databases collections: One of the main reasons that contribute to the success of neural networks is the availability of a large amount of labeled training data. Datasets are often categorized toward different various vision tasks such as image classification [28], scene segmentation [23], face detection [47], and activity recognition [87].

# 1.1 Challenges of Portable and Efficient Computer Vision

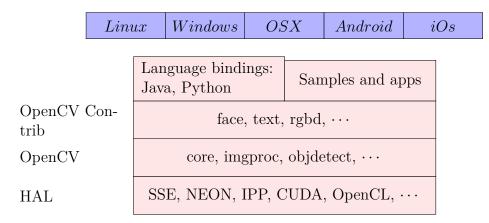

Computer vision is computationally intensive and involves sophisticated algorithms. The efficient implementation of these algorithms is very challenging and needs expertise not only in computer vision but also software design and hardware optimization. Hence, open-source software such as OpenCV are often used to build real-world systems. OpenCV is designed for computational efficiency and with real-time use cases in mind [16]. OpenCV is very comprehensive, and as shown in Figure 1.3 is implemented as a set of modules. It offers a large number of primitive vision kernels and applications ranging from image processing, object detection, tracking, and deep neural networks (DNNs). Furthermore, it supports a wide variety of operating systems and is optimized for a range of parallel hardware such as

Figure 1.3: OpenCV source code structure and platform support

multicores, vector extensions, and GPUs. It is developed in C++, but bindings for languages such as Python and Java are available.

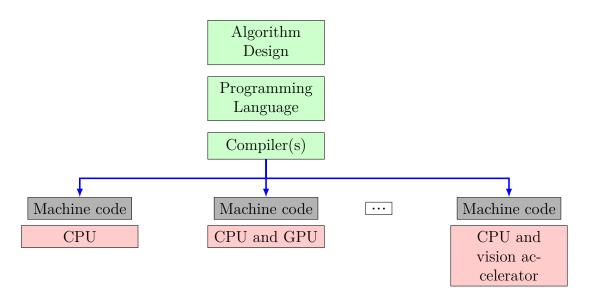

A critical requirement of real-time computer vision is efficiency. Researchers have developed software, hardware, and software-hardware optimization methods to improve resource consumption, performance, and energy efficiency of computer vision systems. Implementing systems that are portable in regards to performance and power efficiency is not trivial. Since many of the optimizations depend on the underlying hardware, in practice, software implementations such as OpenCV have platform-specific optimizations that are hard-coded and enabled at compile-time. However, manual optimization is very tedious. Utilizing hardware parallelism efficiently without sacrificing portability is the subject of extensive research. Many works have used portable and high-level abstraction of programs and compilers that convert them into optimized binary for the underlying hardware [15, 30, 80].

## **1.2** Thesis Contributions

This dissertation's contributions include two disjoint efforts. We consider two platforms that are suitable for computer vision processing, yet they were not easily accessible to algorithm designers and developers: (1) the Web and (2) FPGA-based accelerators.

Figure 1.4: Using compilers to produce high-performance machine codes for diverse hardware platform targets

- 1. The Web is the most ubiquitous computing platform with billions of connected devices. Its popularity in online commerce, entertainment, science, and education has been increasing tremendously. There is also an ever-growing amount of multimedia content on the Web. Despite such rapid progress in quantity and quality of content, computer vision processing on the web browsers has not been a common practice. One approach taken by developers was to offload vision processing tasks to the server. This approach, however, sacrifices user privacy and suffers from always-online requirements and the increase in data transfer bandwidth and latency. With a massive boost in JavaScript execution performance, and HTML5 APIs to access media devices, the Web can unleash the huge potential in education, entertainment, and commerce. However, a web-based computer vision library with quality and quantity of OpenCV to work as infrastructure to build computer vision systems is lacking.

- 2. Computer vision acceleration improves performance and energy-efficiency dramatically and is in high demand. For example, some applications require detecting hundreds of objects in a few milliseconds. This task is not feasible on modern CPUs even with expert implementation. FPGAs are a promising solution to improve the speed and

mitigate the computational cost of vision algorithms through hardware pipelining and parallelism while offering excellent power efficiency [63, 114, 46, 67]. However, an efficient FPGA implementation of a vision algorithm requires hardware design expertise and a considerable amount of engineering person-hours. Unfortunately, developers may not be familiar with FPGA design, let alone efficient implementation. Even a CPU implementation of vision algorithms using programming languages such as C/C++ is time-consuming and error-prone. Moreover, despite advances in High-Level Synthesis (HLS) tools, they are still not able to generate efficient hardware implementation for vision algorithms developed in general-purpose programming languages. The main reason is that HLS tools do not incorporate specific optimization methods of vision algorithms, which are critical to the efficient implementation of such algorithms.

To address the above-mentioned challenges, this dissertation makes the following list of contributions:

#### Web-based platform:

- 1. It provides a comprehensive computer vision library for the Web by porting an existing computer vision library that is developed in a native language (i.e., OpenCV) to JavaScript. It provides an expansive set of functions with an optimized implementation that offers a near-native level of performance.

- 2. It shows how the library performance can be further improved through JavaScript SIMD and thread-based parallelism.

#### **FPGA-based** platform:

1. It develops a scalable OpenCL library of image processing and computer vision kernels such that they can be configured using various input parameters. This library can be used in any OpenCL program or as part of a high-level vision framework.

2. It provides a heterogeneous framework called AFFIX to transform OpenVX graphbased algorithms to CPU-FPGA implementation. It employs several algorithm and hardware-specific optimization techniques. This enables vision developers to develop, verify, and test FPGA implementation of a vision algorithm quickly and without the need to know a DSL or FPGAs.

The research presented in this dissertation has been published in peer-reviewed conference proceedings [95, 97, 96, 94].

#### 1.2.1 Regarding Software Quality

As part of this dissertation, we developed software libraries and tools for computer vision processing with the focus on maximizing efficiency and portability. We have taken into account the ISO 9126 software quality standards in the development process.<sup>1</sup>

- 1. Functionality: Required functions are correctly implemented.

- 2. Usability: Provided software is easy to use and learn.

- 3. Efficiency: System resources (e.g., memory and CPU) are used efficiently when providing the required functionality.

- 4. Portability: The software can adapt to changes in its environment well.

$<sup>^{1}</sup>https://en.wikipedia.org/wiki/Software\_quality\#Measurement$

# Chapter 2

# OpenCV.js: Computer Vision Processing for the Open Web platform

## 2.1 Introduction

The Web is the most ubiquitous compute platform with billions of connected devices. Its popularity in online commerce, entertainment, science, and education has been increasing tremendously. There is also an ever-growing amount of visual content on the Web. Despite such rapid progress in quantity and quality of content, computer vision processing on the web browsers has not been a common practice. We believe that the lack of client-side vision processing is due to several limitations:

- 1. Lack of standard Web APIs to access and transfer multimedia content

- 2. Inferior JavaScript performance (the standard language of the Web). Computer vision

often complex algorithms that involve a sheer amount of computation, making them very time-consuming.

3. lack of open-source and accessible computer vision libraries to facilitate software development for the Web.

Newly introduced web standards address the limitations mentioned above and can empower the Web with computer vision capabilities:

- 1. Addition of camera support and plugin-free multimedia delivery on the Web: HTML5 introduced several new web APIs to capture, transfer, and present multimedia content in browsers without the need for third-party plugins. Among them, Web Real-Time Communication (WebRTC) allows capturing and peer-to-peer transportation of multimedia content [52, 95], and video element API can be used to display videos. Recently added Immersive Web API (WebXR) can be used to create immersive user experiences through browser hosts by providing access to augmented reality (AR) and virtual reality (VR) capabilities [9].

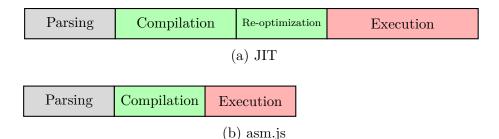

- 2. Improved JavaScript performance: JavaScript is the dominant programming language of the Web. Since it is an interpreted language with dynamic typing, it's performance is inferior to compiled languages such as C++. With advances in Just-In-Time (JIT) compilation [36, 42, 86, 12], and with the introduction of WebAssembly (WASM) [41], a portable binary format for the web compilation, web clients can reach the near-native level of performance and handle more demanding tasks.

There are already efficient computer vision libraries developed in native languages such as C++. However, they cannot be used in browsers without relying on unpopular browser extensions which pose security and portability issues. There have been few efforts to develop computer vision libraries in JavaScript [113, 62, 43]. However, they often provide a handful

of vision functions from certain domains such as object detection, video tracking, or deep learning. Expanding them with new algorithms and optimizing the implementation is a challenging task. On the other hand, Accelerated shape detection API [21] provides functions to detect shapes such as faces and bar codes while the efficient implementation is left to browser vendors. The works mentioned above suffer from the lack of either functionality, performance, or portability. An alternative approach to the client-side computation taken by developers was to offload vision processing tasks to the servers. This approach, however, sacrifices user privacy and suffers from always-online requirements and the increase in data transfer bandwidth and latency.

In this chapter, we describe our effort to provide a computer vision library for the Web that solves the mentioned shortcomings. Our approach is to translate the popular OpenCV library from C++ to a format that is highly optimizable on the Web. We show that this approach works great on the Web for several reasons:

- 1. OpenCV provides an expansive set of functions with optimized implementations.

- 2. It performs more efficiently than JavaScript implementations and performance can further improve through parallelism.

- 3. Developers can have access to a big collection of existing resources such as tutorials and examples.

## 2.2 Compiling to The Web

Most modern standards-compliant web applications are developed in JavaScript, CSS, and HTML [7]. In this model, HTML and CSS codes describe the HTML components, their appearance, and the layout while the JavaScript code implements the program logic. JavaScript

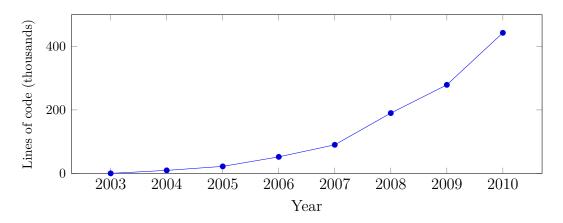

Figure 2.1: Number of JavaScript lines of code in Gmail source code

is an interpreted language and lacks the performance of languages such as C++ where the compiler can translate programs efficiently to the hardware beforehand. As web applications are getting larger and more demanding, web developers are interested in higher performance JavaScript execution. Figure 2.1 for instance shows how Gmail JavaScript code size has increased 50x in the course of 6 years [5].

Since 2004 an era called the browser war started, in which browsers started to compete with each other in JavaScript execution performance. Several approaches based on the idea of Just in time (JIT) compilation were proposed to make JavaScript faster on browsers. For instance, Gal proposed to record traces from program execution and compile the hot traces to efficient machine code [36]. Other approaches such as [42] infer types at run-time and compile individual functions to machine code. However, the compilation is happening at run-time, and since compilation with higher optimization levels is time-consuming, their scope is often limited to an execution trace or a single function. Furthermore, JavaScript is dynamically-typed, and changes in variables type during run-time will require re-compilation of the generated machine code. As an example, consider the example JavaScript function from Figure 2.2. Operator + in the fourth line will have a different implementation based on the operand types. While for numerical operands it would be an arithmetic addition; for string operands, it would be string concatenation. To be able to compile this function to

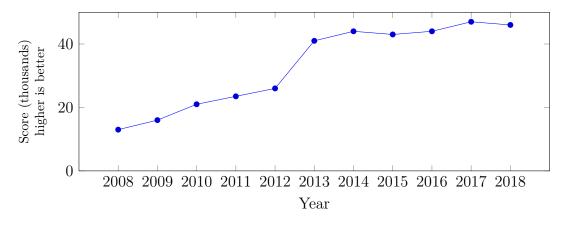

Figure 2.3: Chrome JavaScript engine (V8) benchmark score

machine code, the compiler must be able to infer the types correctly. Even with the correct type inference, the types can change at run time. Hence it might be necessary to monitor the code in case of changes in data types.

Figure 2.3 shows the steady performance improvement of executing the V8 benchmark over time in chrome [18]. However, performance has not improved significantly since 2015. Several approaches, such as plugins [56], ActiveX [76], and PNaCl [29], are proposed to achieve higher (near-native) performance. While they offer high performance, they did have not gained mainstream adoption due to portability and security issues. For instance, Apple forbids Java and Flash plugins on iOS devices, including the iPhone and iPad.

```

1 function add(a, b) {

2 return a + b;

3 }

```

Figure 2.2: Implementation of *add* Function in JavaScript

#### 2.2.1 Portable Low-level Formats for Web Compilation

Mozilla research proposed using a subset of JavaScript called asm.js to improve JavaScript execution performance even beyond JIT capabilities. Asm.js has two properties that allow JavaScript engines to perform an extra level of optimizations and even, compile the entire program ahead of the execution.

- It uses type coercion technique to enforce the code to be statically-typed. JavaScript engines can compile statically-typed JavaScript code ahead of the execution. Figure 2.4 displays an example of coercion to specify integer addition.

- 2. It uses JavaScript arrays to represent program memory such as heap and stack. Most modern browsers have optimized array access. Figure 2.5 shows how various sections of program memory such as stack and heap, can be implemented using typed arrays.

```

1 function add(x, y) {

2 x = x | 0;

3 y = y | 0;

4 return (x + y) | 0;

5 }

```

Figure 2.4: Using type coercion to force the JavaScript engine to generate integer addition

```

1

var buffer = new ArrayBuffer(32*1024);

2

var HEAP8 = new Int8Array(buffer);

3

var HEAP32 = new Int32Array(buffer);

4

5

function access_byte(index) {

6

return HEAP8[index];

7

}

8

9

function access_word(index) {

10

return HEAP32[index];

11

}

```

Figure 2.5: Using arrays to represent program memory in asm.js

Developing programs manually in asm.js is tedious. In fact, asm.js is intended as a target for translating programs developed in other languages to the Web using a tool called Emscripten. Emscripten is a compiler toolchain developed by Mozilla research to translate LLVM (Low-Level Virtual Machine) bit code to asm.js [112]. Using LLVM will make it possible to convert

Figure 2.6: JIT vs asm.js run-time breakdwon

many languages such as C++ or Java to JavaScript since there a large number of language frontends supported by LLVM. The ability to port programs developed in compiled languages such as C++ to browsers is very compelling. Since not only programs can run faster, a vast amount of existing code becomes available to the Web. Some programmers might even prefer them to develop in JavaScript. For example, Figure 2.7 shows a sample C++ source file that is converted to asm.js equivalent code via Emscripten.

While asm.js performance is impressive, there are several shortcomings. Generated JavaScript programs tend to be very large, and parsing and compiling big JavaScript files becomes the bottleneck, especially on mobile devices with weaker processors. This issue was one of the main motivations for the development of WebAssembly [41].

WebAssembly (WASM) is a binary format that is designed to be a compiler target for the Web. It models an abstract stack machine, where instructions either pushes or pops values to/from the stack. WASM instructions are designed to be as close to native instructions as possible. It is fast to load and runs safely at predictably near-native speed. Although WASM is modeled by a stack machine, browsers will not necessarily follow that execution model and compile it to a format that runs more efficiently on modern processors. WASM can be represented in binary and textual format. The textual format is intended for human maintainability while the binary format is intended for production.

Figure 2.8 shows a simple function in WASM that performs integer addition. It starts with an empty stack, pushes the input parameters into the stack, then the last instruction pops

```

1 int sum_five(unsigned char* array) {

2    int res = 0;

3    for (int i = 0; i < 5; ++i) {

4        res += array[i];

5    }

6    return res;

7 }</pre>

```

(a) Sample C++ program

```

1

var buffer = new ArrayBuffer(32768);

2

var HEAP8 = new global.Int8Array(buffer);

3

function sum_five($0) {

0 = 0 | 0;

4

var \$1 = 0, \$10 = 0, \$11 = 0, \$12 = 0, \$13 = 0, \$14 = 0,

5

15 = 0, 2 = 0, 3 = 0, 4 = 0, 5 = 0, 6 = 0, 7 =

0, \$8 = 0, \$9 = 0, label = 0, sp = 0;

6

sp = STACKTOP;

7

STACKTOP = STACKTOP + 16|0; if ((STACKTOP|0) >= (

STACK_MAX(0)) abortStackOverflow(16(0);

8

$1 = $0;

9

$2 = 0;

10

3 = 0;

while(1) {

11

12

$4 = $3;

5 = ($4|0) < (5);

13

14

if (!($5)) {

break;

15

16

}

17

$6 = $1;

$7 = $3;

18

19

8 = ((86) + (87)|0);

20

9 = \text{HEAP8}[8>>0]|0;

21

10 = 9\&255;

22

$11 = $2;

23

12 = ((\$11) + (\$10))|0;

24

$2 = $12;

25

$13 = $3;

26

14 = ((13) + 1) | 0;

27

3 = 14;

28

}

```

#### (b) Emscripten-emitted asm.js code

Figure 2.7: Compilation of a sample C++ program into asm.js by Emscripten.

```

1 (func (param $0 i32) (param $1 i32)

2 local.get $1

3 local.get $0

4 i32.add)

```

Figure 2.8: WASM implementation of an integer addition function in textual format

the operands, calculates their sum, and pushes the result into the stack again. The return value of the function will be the last element left on the stack.

Compared to asm.js, WASM is more compact and is much quicker to parse and compile. WASM will eventually make asm.js obsolete. However, WASM is still under development and not fully supported by older JavaScript engines. We have used Emscripten to compile the OpenCV source code into both asm.js and WASM. Both versions offer the same functionality and can be used interchangeably.

## 2.3 Generating OpenCV.js

This section describes the process of generating OpenCV.js from OpenCV source doe. We have used Emscripten to compile OpenCV to the web. However, for two reasons, several OpenCV components must be excluded:

- 1. Not all of OpenCV's offerings are compatible with the web. For instance, functions to access media devices such as cameras, and graphical user interfaces, are platform-dependent and cannot be compiled to the web. Those functions, however, can be implemented using HTML5 primitives. For instance, media capture getUserMedia can be used to access media devices, and the Canvas element can display graphics.

- 2. Some of OpenCV functions are only used in certain application domains that are not common in typical web development. For instance, camera calibration functionality

```

1 int sum_five(unsigned char* array) {

2     int res = 0;

3     for (int i = 0; i < 5; ++i) {

4        res += array[i];

5     }

6     return res;

7  }</pre>

```

(a) Sample C++ program

```

1

(module

2

(type $t0 (func))

3

(type $t1 (func (result i32)))

4

(func $__wasm_call_ctors (type $t0))

(func $sum_five (export "sum_five") (type $t1) (result i32)

5

6

i32.const 0

i32.load8_u offset=1024

7

8

i32.const 0

9

i32.load8_u offset=1025

10

i32.add

11

i32.const 0

12

i32.load8_u offset=1026

13

i32.add

14

i32.const 0

15

i32.load8_u offset=1027

16

i32.add

17

i32.const 0

18

i32.load8_u offset=1028

19

i32.add)

20

(table $T0 1 1 anyfunc)

21

(memory $memory (export "memory") 2)

22

(global $g0 (mut i32) (i32.const 66576))

(global $__heap_base (export "__heap_base") i32 (i32.const

23

66576))

24

(global $__data_end (export "__data_end") i32 (i32.const 1029))

25

(global $array (export "array") i32 (i32.const 1024))

(data (i32.const 1024) "\01\02\03\04\05"))

26

```

(b) Emscripten-emitted WASM code in textual format

Figure 2.9: Compilation of a sample C++ program into WASM by Emscripten.

| Module           | Provided Functions                                                  |

|------------------|---------------------------------------------------------------------|

| Core             | Image manipulation and core arithmetic                              |

| Image Processing | Numerous functions to process and analyze images                    |

| Video            | Video processing algorithms such as tracking, background segmen-    |

|                  | tation and optical flow                                             |

| Object Detection | Haar and HOG based cascade classifiers                              |

| DNN              | Inference of Caffe, Torch, TensorFlow trained networks              |

| GUI              | Helper functions to provide graphical user interface, to access web |

|                  | images and videos, and to display content                           |

Table 2.1: OpenCV.js modules and provided functions

has applications in automation and robotics. To reduce the size of the generated library for general usage, we have identified the least commonly used functions from OpenCV and excluded them from the library. However, since many of the excluded functions can be useful in special use cases, we have provided a mechanism to extend the library with a list of user-selected functions.

Table 2.1 categorizes and lists the functions that are included within OpenCV.js.

Computer vision programs developed in C++ can access configuration files on the host machine. Browsers, however, are sandboxed for security purposes and do not give web applications access to regular files on the local machine. OpenCV.js provides a virtual file system that can pack all the necessary files that the program will have to access. The virtual file system can be modified at run-time by adding or modifying the files.

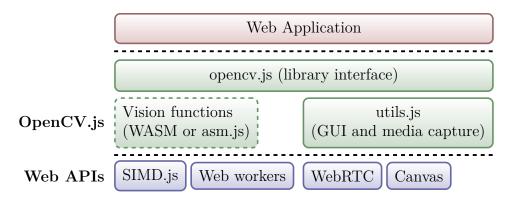

Figure 2.10 shows an overview of OpenCV.js and how it interacts with web applications and standard web APIs. Web applications will use Opencv.js API to access the provided functions as listed in Table 2.1. While the vision functions from OpenCV are compiled either into WASM or asm.js, GUI features, and media capture capabilities are provided by a JavaScript module (util.js). OpenCV.js utilizes standard web APIs such as WebRTC and

Figure 2.10: OpenCV.js components and its interactions with web applications and web APIs

Video/Canvas for media access and GUI capabilities and uses web workers and SIMD.js to implement parallel algorithms.

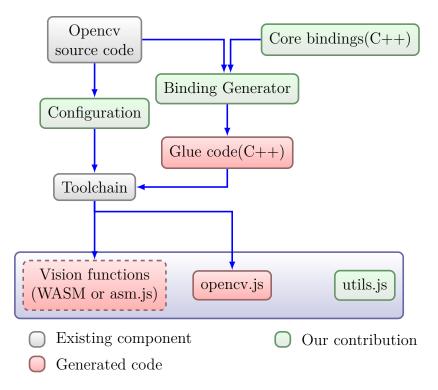

During the compilation process with Emscripten, C++ high-level language information such as class and function identifiers are replaced with mangled names. It is almost impossible for developers to develop programs through mangled names. We develop an interface for the library that exposes OpenCV entities such as functions and classes to JavaScript similar to normal OpenCV that many programmers are already exposed to it. Since OpenCV is enormous, and growing continuously through new contributions, continually updating the port by hand is impractical. Hence, we propose a semi-automatic approach that takes care of the tedious parts of the translation process while allowing the expert insight that enables high-quality/efficient code production. Figure 5.9 lists the steps involved in the process of converting OpenCV C++ code to JavaScript.

At first, the OpenCV source code is configured to disable components and implementations that are platform-specific or translate poorly to the web. Emscripten provides a framework called Embind that can call arbitrary functions in Emscripten-compiled C++ and pass arguments (which involves type translation) from a JavaScript. To use Embind, we extract information about classes and functions from the OpenCV source code automatically. Figure 2.12 shows the binding information that is generated for a sample OpenCV class. For

```

1bool haar_cvt::convert(const String& oldcascade,<br/>const String& newcascade)

```

(a) Original function signature

```

1 function __ZN2cv8haarcvtL7convertERKNS_6StringES3_(

2 $oldcascade,

3 $newcascade)

```

(b) Generated function signature with the mangled name

Figure 2.11: Compilation of a sample C++ function into JavaScript by Emscripten.

the sake of efficiency, binding information of OpenCV core module, which includes OpenCV main data structure (i.e., "cv::Mat"), is manually provided.

We maintain a white list of OpenCV classes and functions that are included in the final JavaScript build. This list can be updated by users to include or exclude OpenCV modules and functions. By providing the binding information and functions white list, Emscripten generates a glue code that maps JavaScript symbols to C++ symbols and compiles it along with the rest of the OpenCV library into JavaScript. The output of this process will be a JavaScript file (opencv.js) that serves as the library interface along with WASM or asm.js implementation of OpenCV functions. utils.js which includes GUI, I/O, and utility functions, and is implemented separately, will also be linked with the rest of opencv.js.

## 2.4 Using OpenCV.js

OpenCV.js API is based on OpenCV C++ API and shares many similarities with it. For instance, it exports C++ functions to JavaScript with the same name and signature. It also supports function overloading and default parameters. This similarity makes migration to JavaScript easier for users who are already familiar with OpenCV development in C++. Although OpenCV.js ports C++ classes to JavaScript objects with the same member func-

```

1

class CV_EXPORTS_W MSER : public Feature2D {

2

public:

3

CV WRAP static Ptr<MSER> create(

4

int _delta=5, int _min_area=60, int _max_area=14400,

5

double _max_variation=0.25, double _min_diversity=.2,

6

int _max_evolution=200, double _area_threshold=1.01,

\overline{7}

double _min_margin=0.003, int _edge_blur_size=5);

8

9

CV_WRAP virtual void setDelta(int delta) = 0;

10

CV_WRAP virtual int getDelta() const = 0;

// The rest of class declaration

11

12 };

```

(a) MSER class declration in OpenCV source code

```

emscripten::class_<cv::MSER, base<Features2D>>("MSER")

1

2

.class_function("create",

3

select_overload<Ptr<MSER>(int, int, int, double,double,int,double

,douboe,int)>

4

(&Wrappers::create_MSER_wrapper)

.function("setDelta",

5

6

select overload<int(cv::MSER&)>(&Wrappers::MSERT set delta wrap),

7

pure_virtual())

8

.function("getDelta",

9

select_overload<int(cv::MSER&)>(&Wrappers::MSERT_get_delta_wrap),

10

pure_virtual())

11

// The rest of class bindings

12

;

```

(b) Generated binding information for MSER class

Figure 2.12: Example of binding generation

Figure 2.13: The flow of generating OpenCV.js from OpenCV source code

tions and properties, basic data types are different between the two versions. For instance, JavaScript is using double-precision floating-point numbers for all numerical types, whereas, in C++, numerical values have several type options (e.g., short, int, and floating-point). JavaScript engines use the garbage collector(GC) to manage program memory. However, GC activity hurts performance. Hence, OpenCV.js uses static memory management, and programmers are responsible for freeing OpenCV.js objects when they are no longer in use. Since manual memory management for primitive types is tedious, we have used JavaScript equivalents for basic C++ types such as numbers, boolean values, and strings. All *std* :: *vectors* are translated into JavaScript arrays except for vectors of cv :: *Mat*. This is particularly helpful since by removing the vector, it will remove all the cv :: *Mat* elements automatically. Table 2.2 shows equivalent JavaScript data types for basic C++ data types.

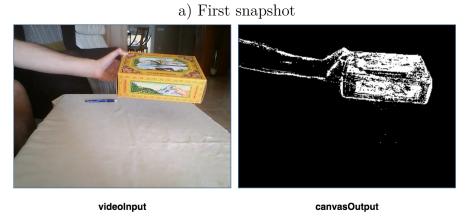

Figure 2.14 shows a sample JavaScript program. This program uses MOG2 method (based on the Gaussian mixture model [118]) provided by OpenCV.js to subtract the background

| C++ Type                           | JavaScript Type  |

|------------------------------------|------------------|

| Numerical types (e.g., int, float) | Number           |

| bool                               | Boolean          |

| enum                               | Constant         |

| std::string                        | String           |

| Primitive types (e.g. cv::Point)   | Value objects    |

| std::vector (of primitive types)   | JavaScript Array |

| std::vector (of cv::Mat)           | cv.Vector        |

Table 2.2: JavaScript equivalent types of basic OpenCV C++ data types

from the input video. This example works on top of a simple HTML page with an HTML5 video element named *videoInput* serving as the input source and a canvas element named *canvasOutput* which renders the program output. In the line 21, *cv.VideoCapture* utility function is invoked to access input video frames from the video element. In lines 22 and 23, two OpenCV matrices are created to hold the input and output frames. In the 24th line, a background subtractor is instantiated. The background subtraction algorithm needs to access the history of frames from the input video to correctly partition the image in the foreground and background. This example assumes that the input video contains 30 frames per second. Hence, a timer is used to invoke *processVideo* function every 1/30 of a second. At every invocation of *processVideo* function, we feed the next frame of the video to the background subtractor and extract the foreground mask (line 10). In line 11, we will display the result on the output canvas and then schedule the function for processing the next video frame (line 14). Figure 2.15 shows two snapshots of running this program inside a browser.

### 2.5 Performance Evaluation

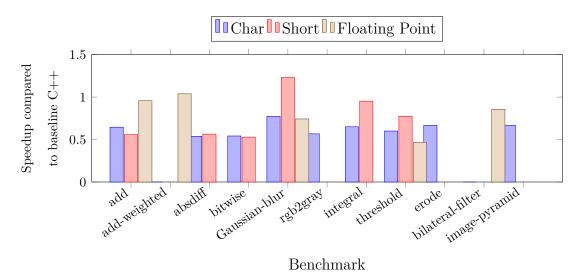

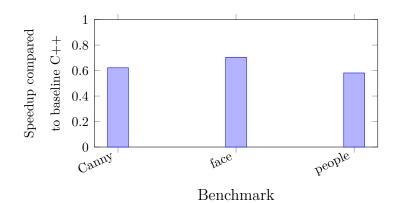

This section presents the performance evaluation of OpenCV.js. Our evaluation workloads include both primitive kernels that perform simple operations such as pixel-wise addition or convolution and more sophisticated vision applications. Our selected vision applications

```

1

function processVideo() {

\mathbf{2}

try {

3

if (!streaming) { // clean and stop.

4

frame.delete(); fgmask.delete(); fgbg.delete();

5

return;

}

\mathbf{6}

7

let begin = Date.now();

8

// start processing.

9

cap.read(frame);

10

fgbg.apply(frame, fgmask);

11

cv.imshow('canvasOutput', fgmask);

12

// schedule the next one.

13

let delay = 1000/FPS - (Date.now() - begin);

setTimeout(processVideo, delay);

14

15

} catch (err) {

16

utils.printError(err);

17

}

18

};

19

20 var video = document.getElementById('videoInput'),

21

cap = new cv.VideoCapture(video),

frame = new cv.Mat(video.height, video.width, cv.CV_8UC4),

22

23

fgmask = new cv.Mat(video.height, video.width, cv.CV_8UC1),

24

fgbg = new cv.BackgroundSubtractorMOG2(500,16,true);

25

const FPS = 30;

// schedule the first frame

26

27

setTimeout(processVideo, 0);

```

Figure 2.14: Example OpenCV.js program to subtract background from the input video

videoInput

canvasOutput

b) Second snapshot

Figure 2.15: Two snapshots of the sample OpenCV. js program from Figure 2.14 running in a web browser

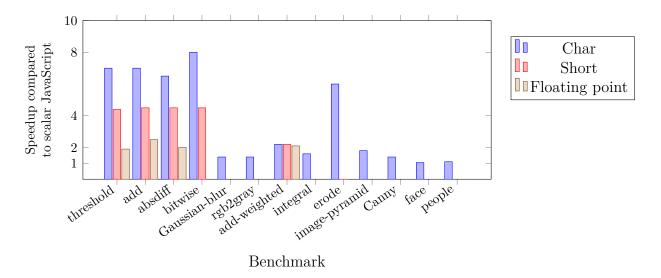

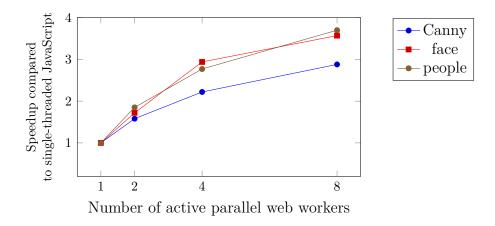

include implementation of **Canny**'s algorithm for finding edges [20], finding **faces** using Haar cascades [58], and finding **people** by using histogram of gradients as features [26]. We have used an instance of Firefox 56 running on Intel Corei7-3770 CPU with 8GB of RAM with Ubuntu 16.04 as our set up and ran experiments over sequences of video data (400-600 frames) collected from Xiph.org archive. Figures 2.16 and 2.17 show the performance of simple kernels and vision applications running in the browser compared to their desktop equivalent with parallelism disabled. Experiments are repeated for different pixel types that are supported by the benchmarks. As was shown, in all cases, the performance is close to the native.

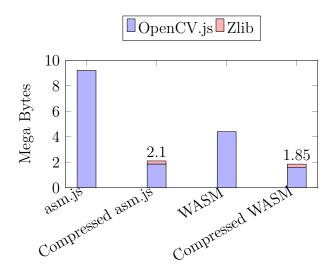

While we found WASM and asm.js performance to be close, the WASM build of the library is significantly faster to initialize (more than 20x faster) and is more compact. To reduce the library size, we have used a JavaScript port of the Zlib library to decompress a zipped version of the OpenCV.js at run-time. Figure 2.18 shows the size comparison of different builds of OpenCV.js. Note that the size of the library depends on the list of functions that are distributed with the library, which is subject to frequent changes.

Figure 2.16: Performance comparison of native and WASM versions of primitive kernels

Figure 2.17: Performance comparison of native and WASM versions of vision applications

Figure 2.18: Size comparison of asm.js and WASM versions of OpenCV.js\*

# 2.6 Availability

OpenCV.js is released as part of the master branch of OpenCV library<sup>1</sup> and can be compiled directly from the latest OpenCV source code releases. This will also ensure that it will be tested to work with all future OpenCV releases and features.

<sup>&</sup>lt;sup>1</sup>https://www.gihtub.com/opencv/opencv

# Chapter 3

# Parallel Processing in OpenCV.js

Computer vision is computationally demanding. On our evaluation platform, each iteration of Canny, face, and people applications developed with OpenCV.js take on average 7 ms, 345 ms, and 323 ms to process an image with a resolution of 640 by 480 pixels respectively. While in this case, Canny is fast enough to be computed in real-time, face, and people detection examples do not support real-time and interactive use cases. Fortunately, computer vision algorithms are inherently parallel, and with good algorithm design and optimized implementation for parallel hardware, a significant speedup can be achieved. OpenCV already comes with parallel implementations of algorithms for various hardware architectures. In this section, we demonstrate how two parallel processing techniques that target multicore processors (multithreading) and SIMD (Single-Instruction-Multiple-Data) units can be used to significantly improve the performance of OpenCV.js. We have skipped GPU implementations at the moment due to the lack of a standard web API for general-purpose programming on GPUs.

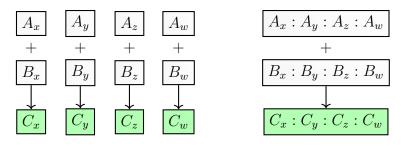

Figure 3.1: Scalar vs SIMD addition of four integers

# 3.1 Parallel Processing using ECMAScript SIMD

ECMAScript SIMD, formerly known as SIMD.js, is a web API that exposes processor vector capabilities to the web [6, 50]. ECMAScript SIMD is compatible with the common subset of Intel SSE2 and ARM NEON instruction sets that runs efficiently on both architectures. Both instruction sets define vector instructions that operate on 128-bit wide vector registers. SIMD instructions can operate all vector data points simultaneously. Figure 3.1 shows how vector registers can be utilized to add four integers using one vector instruction. ECMAScript SIMD defines integer vector types of i8x16, i16x8, i32x4, i64x2 that can hold eight short integers, sixteen bytes, four integers, and two long integers, respectively. It also defines two floating vector types of f32x4 and f64x2 that can hold four floating-point and two doubleprecision floating-point numbers. Table 3.1 lists ECMAScript SIMD vector instructions that are available for use on each vector type.

SIMD is proven to be very effective in speeding up multimedia, graphics, and scientific workloads [79, 50, 93]. Many OpenCV functions, including core routines, are already implemented using vector intrinsics [79]. We have adopted the work done by [48] to translates OpenCV vectorized implementations using SSE2 intrinsics into JavaScript with SIMD.js instructions. The inclusion of SIMD.js parallel implementations will not affect the library interface. Currently, SIMD.js can only be used in the asm.js context and is supported by Mozilla Firefox and Microsoft Edge browsers. Since SIMD in WASM is planned to have the same spec as SIMD.js, similar performance numbers are expected.

| Vector Types         | Operations                                        |  |  |

|----------------------|---------------------------------------------------|--|--|

| i8x16, i16x8, i32x4, | splat, extract_lane_s, replace_lane, add,         |  |  |

| i64x2, f32x4, f64x2  | sub, neg, eq, ne                                  |  |  |

| i8x16, i16x8, i32x4, | shl, shr_s, shr_u, any_true, all_true, lt_s,      |  |  |

| i64x2                | $lt\_u, le\_s, le\_u, ge\_s, ge\_u, gt\_s, gt\_u$ |  |  |

| f32x4, f64x2         | lt, gt, le, ge, abs, min, max, div, sqrt, con-    |  |  |

|                      | vert_to_int                                       |  |  |

| i8x16, i16x8, i32x4, | mul                                               |  |  |

| i64x2, f32x4         |                                                   |  |  |

| i8x16, i16x8         | add_saturate_s, add_saturate_u, sub_sat-          |  |  |

|                      | urate_s, sub_saturate_u, narrowing                |  |  |

| i8x16, i16x8, i32x4  | widening                                          |  |  |

| v128                 | and, or, xor, not, bitselect, load, store         |  |  |

Table 3.1: ECMAScript SIMD types and operations

Benchmark

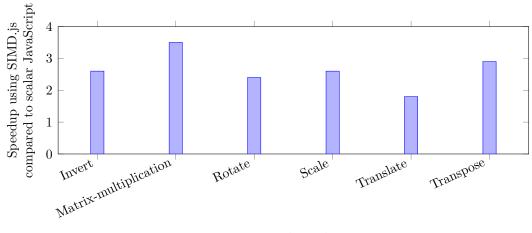

Figure 3.2: Performance comparison of vectorized and scalar JavaScript implementation of matrix operations (asm.js version)

Figure 3.3: Performance improvement with JavaScript vectorization (asm.js version)

Figure 3.3 shows the speedup that is obtained by SIMD.js on selected kernels and applications running on Firefox. Up to 8x speedup is achieved for primitive kernels. As expected, the speedup is higher for smaller data types, since more data points are packed in vector registers. There are fewer vectorization opportunities in complex functions such as Canny, face, and people detection.

### 3.2 Thread-level Parallelism Using Web Workers

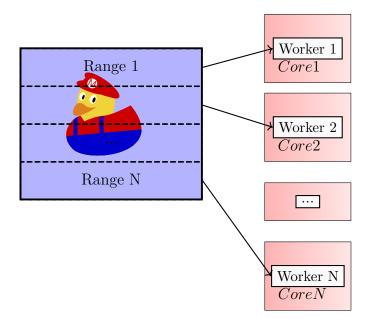

JavaScript programs use web workers [8] for parallel processing of compute-intensive tasks. Web workers communicate by passing messages, which incur a high cost for transferring large messages such as images. SharedArrayBuffer [4] is recently proposed as storage that can be shared between multiple web workers. It can be used to implement the sharedmemory parallel programming model. OpenCV uses the *parallel\_for* framework for parallel implementation of algorithms. In this framework, parallel implementations of algorithms implement the base class *ParallelLoopBody* that process a portion of images. As shown in Figure 3.4, at run-time workloads are partitioned into multiple smaller workloads that a range

Figure 3.4: multi-threaded image processing with Parallel\_for implementation

```

1 public ParallelLoopBody

2 {

3 public:

4 virtual void operator () (const Range& range) const;

5 }

```

Figure 3.5: Base class for implementing parallel algorithms in OpenCV

specifies each. These workloads can be distributed among available compute threads for concurrent processing. OpenCV supports a variety of multithreading backends depending on the operating system such as Intel Threading Basic Blocks (TBB) [75], Windows threading, Apple GCD, OpenMP [25], and Posix Threads [17]. With recent Emscripten developments, we were able to translate P-threads API into equivalent JavaScript using web workers with shared array buffers. OpenCV.js build with multithreading support has a pool of web workers and allocate a worker when a new thread is spawned. Besides, it exposes OpenCV API to dynamically adjust the concurrency such as changing the number of concurrent threads such as "cv.SetNumThreads".

To observe the performance using multiple web workers, we measured the performance of three application benchmarks that did not gain from SIMD vectorization. We used different

Figure 3.6: Speedup achieved using multiple web workers (asm.js)

numbers of workers up to 8. OpenCV load balancing algorithm divides the workload evenly between threads. Figure 3.6 shows that on a processor with 8 logical cores, between 3 to 4 times performance speedup is obtained. Note that a similar trend is observed on native p-threads implementation of the mentioned functions. It should be noted that parallelism improvement from multiple threads and SIMD are additive.

# Chapter 4

# A Library for FPGA Implementation of Vision Algorithms

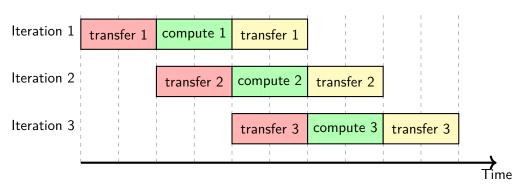

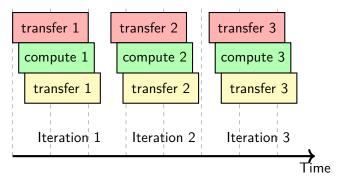

The ever-growing usage of computer vision in our daily lives [2] requires real-time and powerefficient implementations. FPGAs are very effective in accelerating various computer vision algorithms [63, 114, 46, 67]. Unfortunately, developers may not be familiar with FPGA design, let alone efficient implementation. Even a CPU implementation of vision algorithms using programming languages such as C/C++ is time-consuming and error-prone. Moreover, despite advances in High-Level Synthesis (HLS) tools, they are still not able to generate efficient hardware implementation for vision algorithms developed in general-purpose programming languages (e.g., C++) [19, 107, 84]. The main reason is that HLS tools do not incorporate specific optimization methods of vision algorithms, which are critical to the efficient implementation of such algorithms. On the other hand, popular vision libraries, such as OpenCV [16], only provide efficient implementations for CPUs and GPUs. FPGA designers often consider the application-specific design and implementation on FPGAs. For example, several computer vision applications including stereo vision [51, 104, 53], SIFT [103, 74], CNNs and DNNs [35, 38, 115, 116] have been designed and implemented for FPGA acceleration.

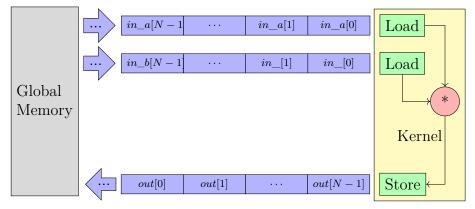

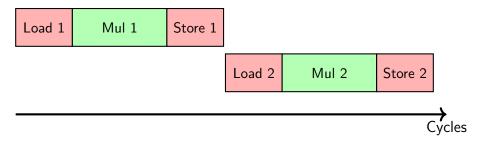

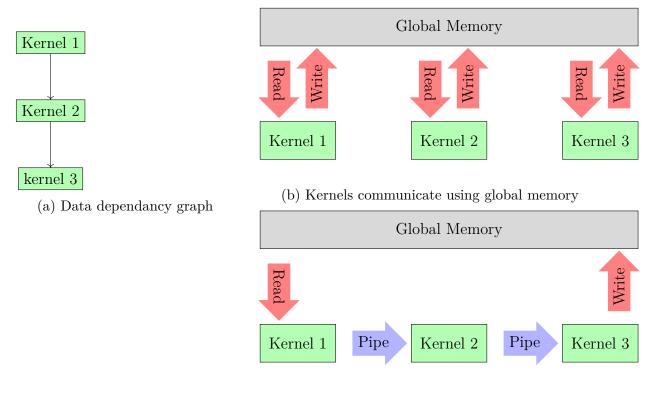

This chapter presents a scalable library developed in OpenCL that provides the basic blocks for building computer vision systems on FPGAs. This library supports a wide variety of vision kernels and can be configured with different structural and functional parameters. It can be used as part of an OpenCL program independently or as part of a high-level framework. To make the library portable, We have tried to use vendor-specific functions as little as possible.

### 4.1 Introduction to OpenVX

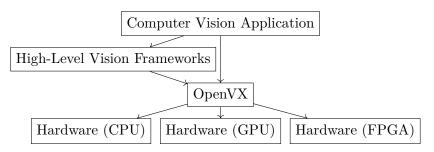

OpenVX is an open standard for cross-platform acceleration of computer vision algorithms [81]. OpenVX defines a set of primitive and widely used vision kernels that can be connected to describe computer vision pipelines as Directed Acyclic Graphs (DAG). In such DAGs, nodes represent data processing kernels while the edges represent data dependencies between them. This model maps nicely to computer vision development since many vision pipelines can be modeled as DAGs. Figure 4.1 shows how OpenVX specification can be used in computer vision algorithm development process. While it can be used directly to model the application, it can also be used as an implementation backend for high-level computer vision frameworks.

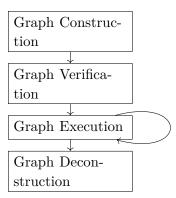

Figure 4.2 shows different stages in lifecycle of an OpenVX algorithm graph. Initially, the vision developer instantiates the OpenVX elements to describe the algorithm graph. After the graph definition is finalized, the graph is verified for soundness. For instance, the graph must be connected, should not include any loops, and parameters passed to the graph elements must have values within the valid range. Upon successful verification, graphs can be executed, possibly for repeated times. No graph verification is needed for subsequence

OpenVX is designed to achieve the following list of objectives:

- System-level optimization: OpenVX graph-based model provides greater optimization opportunities above the traditional function level that applies to the whole system [81]. An example of such optimizations is kernel aggregation, in which a specific set of nodes in a graph are replaced with a single node that offers the same functionality. Another example is tiling, in which, images are broken down to smaller sub-images called tiles that can be processed separately. Processing tiles lead to a smaller memory footprint and cache-friendly implementations. Tiles can also potentially be processed in parallel.

- **Portability**: OpenVX abstracts away hardware-specific details from the algorithm specification. Hence graphs can target different platforms.

- Improved productivity: Decoupling the specification and the implementation makes developing vision algorithms easier. Computer vision developers can focus on algorithm design and rely on platform vendors to provide the optimized implementation. In addition, a single specification can be translated into different implementations that meet different performance and power budget constraints.

Figure 4.1: Typical OpenVX use cases

Figure 4.2: OpenVX graph lifecycle

executions unless there are changes in the graph definition. Finally, after the execution is finished, the graph will be deconstructed to free up resources.

Various hardware vendors have provided their implementation of OpenVX run-time for optimizing and executing the graphs such as Nvidia VisionWorks [3] and AMD AmdoVX [1]. Tagliavini et al. proposed a run-time solution for optimizing OpenVX graphs on embedded many-core accelerators [91, 92]. OpenVX has also been investigated for building computer vision systems with real-time constraints [46, 108, 31, 109].

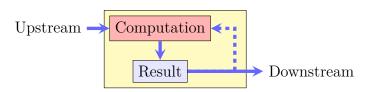

OpenVX defines several vision processing constructs to describe algorithm graphs:

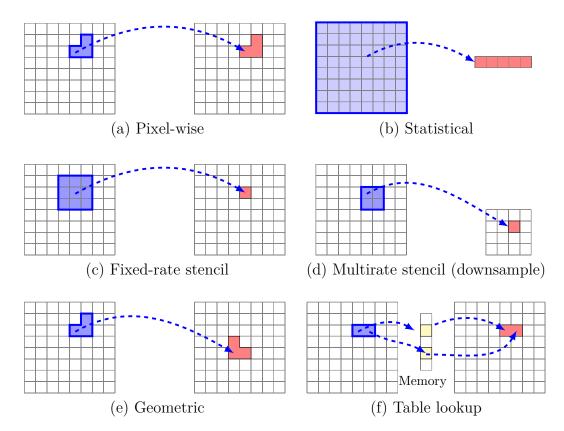

1. Vision function nodes: OpenVX provides a set of widely used primitive vision functions that act as basic blocks of building more complex algorithms. We have thoroughly analyzed all the vision functions provided<sup>1</sup> and classified them based on the pattern that they access to input image pixels. Table 4.1 lists various categories of vision functions.

<sup>&</sup>lt;sup>1</sup>Based on OpenVX version 1.2

Figure 4.3: Vision function data access patterns

| Category              | Formal Definition                                                  | Vision Functions                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pixel-wise            | out(x, y) = f(in(x, y))                                            | absolute difference, accumulate, accumulate<br>squared, accumulate weighted, addition/sub-<br>traction, bitwise operations, channel com-                         |

|                       |                                                                    | bine, channel extract, color convert, convert<br>bit depth, magnitude, phase, pixel-wise mul-<br>tiplication, threshold, min, max                                |

| Fixed-rate<br>Stencil | $out(x,y) = \sum_{i=-k}^{i=k} \sum_{j=-k}^{j=k} f(in(x+i,y+j))$    | Box filter, Sobel filter, non-maxima sup-<br>pression, custom convolution, erode, dilate,<br>Gaussian blur, nonlinear filter, integral im-<br>age, Median filter |

| Multi-rate<br>Stencil | $out(x,y) = \sum_{i=-k}^{i=k} \sum_{j=-k}^{j=k} f(in(Nx+i, Ny+j))$ | down-sample, scale image                                                                                                                                         |

| Statistical           | $out = \sum_{i=0}^{i=Width} \sum_{j=0}^{j=Height} f(in(i,j))$      | histogram, mean, standard deviation,<br>Min,max location                                                                                                         |

| Geometric             | out(x, y) = in(h(x, y), h'(x, y))                                  | remap, warp affine, warp perspective                                                                                                                             |

| Table<br>lookup       | out(x, y) = table[in(x,y)]                                         | table lookup                                                                                                                                                     |

| Non-<br>primitive     | N/A                                                                | equalize histogram, fast corners, Harris cor-<br>ners, Gaussian image pyramid, optical flow<br>pyramids, Canny edges, LBP, HOG, Hough-<br>LinsP                  |

Table 4.1: Categorization of supported OpenVX vision functions

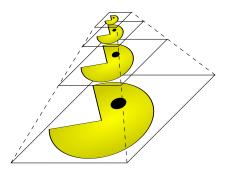

Figure 4.4: An image pyramid with four levels

- 2. Data object nodes: OpenVX defines several objects to represent data used by algorithms, including images, scalars, arrays, and image pyramids. Image pyramids (Figure 4.4) represent an image at multiple scales. For robustness and scale-invariance, computer vision systems often process multiple scales of images. Data objects have properties associated with them, such as their type and size that must be either set during the DAG construction time by the designer or be inferred from the rest of the graph.

- 3. Select nodes: Select nodes implement predication in vision algorithms. They have two input images and produce one output image, all with the same pixel type. A Boolean input value is used to select one of the inputs and set it as the output.

- 4. Delay object nodes: Delay objects are nodes that provide access to arbitrary data objects (e.g., image, array, scalar) from the Nth previous DAG invocation where N is a parameter provided by the algorithm designer. They are in particular used in video processing algorithms that require information from multiple frames. Examples of such algorithms include optical flow, motion detection, and background extraction.

#### 4.1.1 Examples

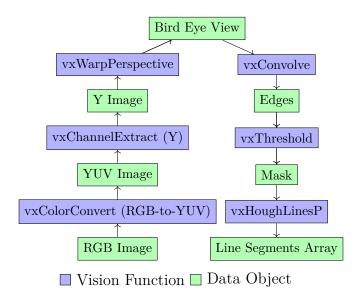

OpenVX can be used to implement a wide variety of image processing and computer vision algorithms. In this section, we describe several illustrative examples.

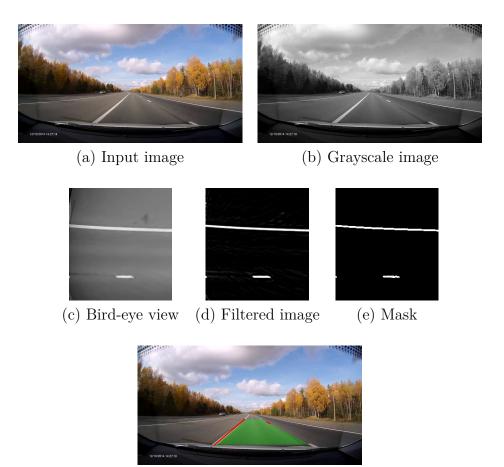

Lane Detection (LD) Algorithm One of the fundamental vision algorithms in autonomous driving cars is Lane Detection (LD). Many LD algorithms are proposed over time [110, 45]. A simple LD algorithm is described in Figure 4.5 while the corresponding OpenVX graph is shown in Figure 4.6. Figure 4.7 shows the output of different stages of the algorithm on a sample input frame. Color input frame captured by a camera in front of a vehicle (Figure 4.7(a)) will be converted to a gray-scale image (Figure 4.7(b)). Then, using a perspective transform, a certain area of interest is considered for further processing (Figure 4.7(c)). The image will be enhanced using a filter and threshold operation to highlight the lanes better (Figure 4.7(d,e)). Finally, lane segments will be detected using probabilistic *Hough* transform (Figure 4.7(f)). The Hough transform algorithm detects geometric shapes such as lines and circles in an image [64].

```

Inputs: Image in_img, Matrix transoform_mat, Matrix filter,

1

2

Integer thresh val

3

Output: Array line_segments

begin

4

5

y_{img} \leftarrow convert_to_grayscale(in_img)

b img \leftarrow warp perspective(y img, transoform mat)

6

7

f_{img} \leftarrow filter(b_{img}, filter)

t_img \leftarrow threshold(f_img, thresh_val)

8

line_segments \leftarrow houghlinsp(t_img)

9

10

return line segments

11

end

```

Figure 4.5: Lane detection algorithm example

Automatic Contrast adjusts the contrast of the input color (RGB) image based on the histogram of pixel intensity values. Figure 4.8 shows the OpenVX graph of automatic contrast graph.