### **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

LO Generation and Distribution for 60GHz Phased Array Transceivers

#### **Permalink**

https://escholarship.org/uc/item/767642t2

#### **Author**

Marcu, Cristian

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

### LO Generation and Distribution for 60GHz Phased Array Transceivers

by

#### Cristian Marcu

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electrical Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor Paul K. Wright

Fall 2011

### LO Generation and Distribution for 60GHz Phased Array Transceivers

Copyright 2011

by

Cristian Marcu

#### Abstract

LO Generation and Distribution for 60GHz Phased Array Transceivers

by

#### Cristian Marcu

Doctor of Philosophy in Electrical Engineering

University of California, Berkeley

Professor Ali M. Niknejad, Chair

Increased memory capacity and processing power in mobile devices has created a need for radios that can transmit data at multi-Gb/s rates over a short range. However, battery capacity has not kept pace with these advances so power consumption must be kept to a minimum to maintain long battery life. Furthermore, consumer devices require low cost components due to the strong market pressures continuously driving down Average Selling Prices (ASP) leading to diminishing margins. This means a fully integrated solution including RF and baseband components is more attractive than a modular solution.

The allocation of 7GHz of unlicensed bandwidth in the 60GHz band and the increasing speed of CMOS technology provides an excellent opportunity for low cost, high data rate, fully integrated radios to fulfill the unique requirements of modern mobile devices. Phased array transceivers using simple modulation schemes should be used due to their high energy efficiency. Phased arrays use spatial power combining to help overcome the high path loss at 60GHz and also provide beam-steering capabilities which can help to overcome fading issues and create a secure means of communication.

Significant progress has been been made recently in the design of mm-wave CMOS building blocks and transceivers, including some phased array transceivers. However, very little attention has been paid to systematic optimization and design of the LO generation and distribution subsystem. In this thesis we use the baseband phase shifting architecture as a vehicle for optimizing LO generation and distribution in phased array transceivers. We propose strategies for optimal low power design with a focus on holistic optimization from architectural choices down to block level design resulting in an optimal and scalable LO distribution methodology. Finally, we present sample designs of building blocks such as oscillators and phase locked loops as well as a full LO generation and distribution subsystem for a 4-element baseband phased-array transceiver in a standard digital 65nm CMOS process.

To my wife Alex, my mom and dad, and my sister Gabi.

I couldn't have done it without your love and support.

## Contents

| Li | List of Figures |                                      |    |  |

|----|-----------------|--------------------------------------|----|--|

| Li | st of           | Tables                               | x  |  |

| 1  | Intr            | roduction                            | 1  |  |

|    | 1.1             | The 60GHz Band                       | 1  |  |

|    | 1.2             | CMOS for 60GHz                       | 4  |  |

|    | 1.3             | 60GHz Transceivers                   | 5  |  |

|    |                 | 1.3.1 Link Budget Analysis           | 7  |  |

|    |                 | 1.3.2 Phased Arrays                  | 9  |  |

|    | 1.4             | Related Work                         | 12 |  |

|    | 1.5             | Thesis Outline                       | 13 |  |

|    |                 | 1.5.1 Design Methodology             | 13 |  |

| 2  | Pass            | sive Design                          | 14 |  |

|    | 2.1             | Lumped Resonant Tanks                | 14 |  |

|    | 2.2             | Distributed Resonant Tanks           | 17 |  |

|    | 2.3             | Tapered Transmission Line Resonators | 22 |  |

|    | 2.4             | MEMS Resonators                      | 25 |  |

|    | 2.5             | Passive Components                   | 28 |  |

|    |                 | 2.5.1 Inductors                      | 28 |  |

|    |                 | 2.5.2 Capacitors                     | 31 |  |

|    |                 | 2.5.3 Varactors                      | 34 |  |

|    |                 | 2.5.4 Transmission Lines             | 39 |  |

|   | 2.A  | Deriva  | ation of Lumped Resonant Tank Bandwidth      | 44  |

|---|------|---------|----------------------------------------------|-----|

|   | 2.B  | Deriva  | ation of Distributed Resonant Tank Bandwidth | 45  |

|   | 2.C  | Series- | to-Parallel Transformation                   | 47  |

| 3 | Volt | tage C  | ontrolled Oscillator                         | 49  |

|   | 3.1  | A Sho   | rt Introduction to Oscillators               | 49  |

|   | 3.2  | Design  | n of a Cross-Coupled Oscillator              | 50  |

|   |      | 3.2.1   | Startup Conditions                           | 51  |

|   |      | 3.2.2   | Tuning the Tank                              | 56  |

|   |      | 3.2.3   | Phase Noise                                  | 59  |

|   |      | 3.2.4   | Design Optimization                          | 64  |

|   | 3.3  | Other   | Fundamental Mode Oscillator Topologies       | 67  |

|   |      | 3.3.1   | Colpitts                                     | 67  |

|   |      | 3.3.2   | Common-Drain Colpitts                        | 73  |

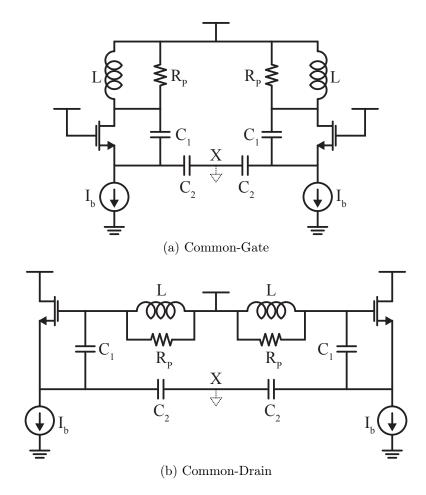

|   |      | 3.3.3   | Differential Versions                        | 77  |

|   | 3.4  | Cross-  | Over Frequency                               | 77  |

|   | 3.5  | The P   | ush-Push Oscillator                          | 82  |

|   | 3.6  | Design  | a Case Studies                               | 90  |

|   |      | 3.6.1   | Push-push Oscillator Prototype               | 90  |

|   |      | 3.6.2   | Fundamental Oscillator Prototype             | 92  |

|   |      | 3.6.3   | Performance Summary and Comparison           | 96  |

| 4 | Low  | Powe    | er Phase Locked Loop Design                  | 99  |

|   | 4.1  | Phase   | Locked Loop Dynamics                         | 101 |

|   |      | 4.1.1   | The Linear Phase Domain Model                | 101 |

|   |      | 4.1.2   | First Order PLL                              | 104 |

|   |      | 4.1.3   | Second Order PLL                             | 106 |

|   |      | 4.1.4   | The Charge Pump and Phase Frequency Detector | 107 |

|   |      | 4.1.5   | The Charge Pump PLL                          | 111 |

|   | 4.2  | Noise   | in Charge Pump Phase Locked Loops            | 114 |

|   |      | 4.2.1   | Noise Contributors                           | 115 |

|    |       | 4.2.2   | Design Optimization                         | 117 |

|----|-------|---------|---------------------------------------------|-----|

|    | 4.3   | Freque  | ency Dividers                               | 119 |

|    |       | 4.3.1   | Flip-Flop Dividers                          | 119 |

|    |       | 4.3.2   | Injection Locked Dividers                   | 124 |

|    |       | 4.3.3   | Regenerative Dividers                       | 126 |

|    |       | 4.3.4   | Prescalers                                  | 127 |

|    | 4.4   | Sampl   | e Design                                    | 131 |

|    | 4.A   | Spectr  | al Purity Metrics                           | 138 |

| 5  | LO    | Distril | bution                                      | 140 |

|    | 5.1   | Mixer   | LO Requirements                             | 140 |

|    | 5.2   | LO Ge   | eneration Strategy                          | 144 |

|    | 5.3   | Mixer   | LO Buffer Design Methodology                | 148 |

|    |       | 5.3.1   | Scalable Amplifier Model                    | 149 |

|    |       | 5.3.2   | Scalable Transformer Model                  | 150 |

|    |       | 5.3.3   | Equation Based Buffer Design                | 151 |

|    |       | 5.3.4   | Optimization Based Buffer Design            | 156 |

|    |       | 5.3.5   | Comparision Between Buffer Design Methods   | 158 |

|    |       | 5.3.6   | Injection Locked Oscillator As an LO Buffer | 160 |

|    | 5.4   | LO Di   | stribution Strategy                         | 163 |

|    | 5.5   | Design  | n Case Study                                | 169 |

| 6  | Con   | clusio  | n                                           | 173 |

| Ri | hlion | ranhy   |                                             | 174 |

# List of Figures

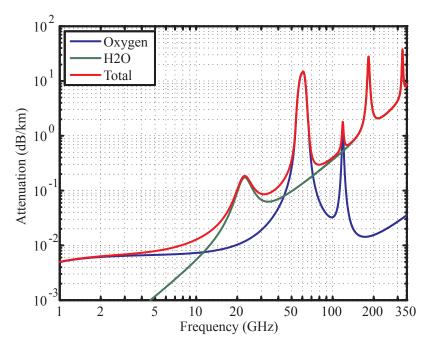

| 1.1  | Attenuation due to molecular resonances in the atmosphere (sea-level, $25^{\circ}C$ , $7.5g/m^3$ water vapor density)                                                                                 | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

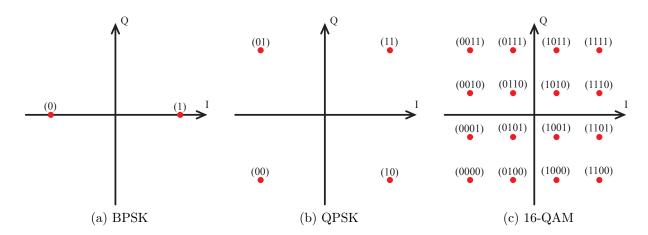

| 1.2  | Constellations of simple modulation schemes                                                                                                                                                           | 2  |

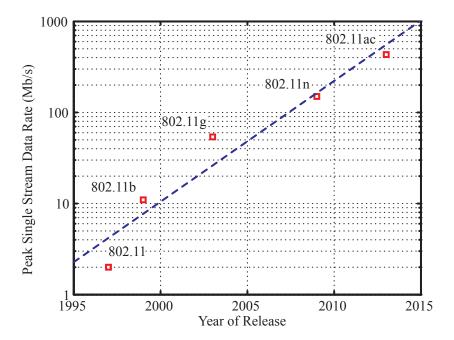

| 1.3  | Evolution of WLAN data rates                                                                                                                                                                          | 3  |

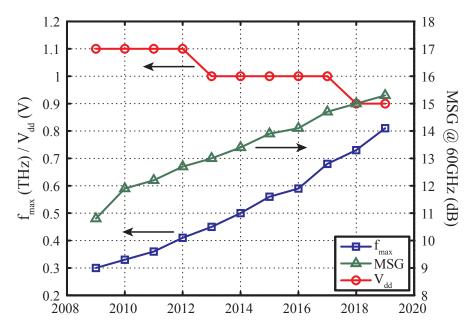

| 1.4  | ITRS Roadmap for RF CMOS Technology                                                                                                                                                                   | 4  |

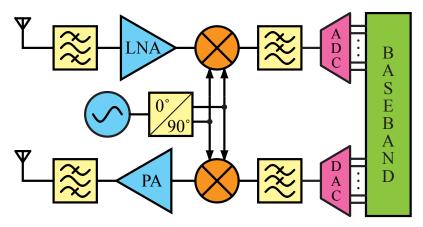

| 1.5  | Direct conversion transceiver block diagram                                                                                                                                                           | 6  |

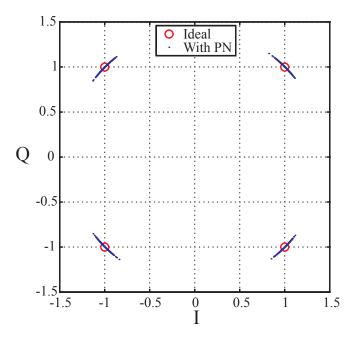

| 1.6  | QPSK constellation with noisy carrier                                                                                                                                                                 | 7  |

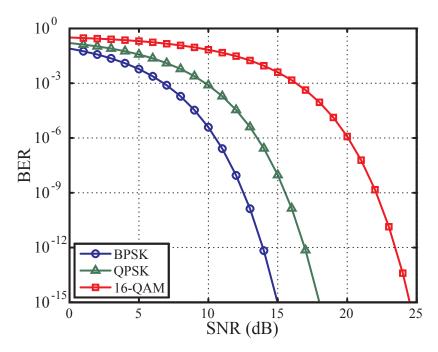

| 1.7  | BER as a function of SNR for different modulation schemes                                                                                                                                             | 8  |

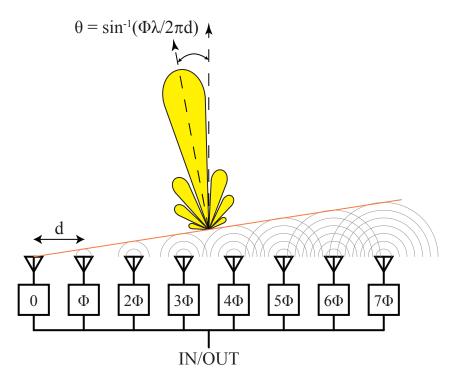

| 1.8  | Uniform linear 8-element phased array transceiver block diagram                                                                                                                                       | 9  |

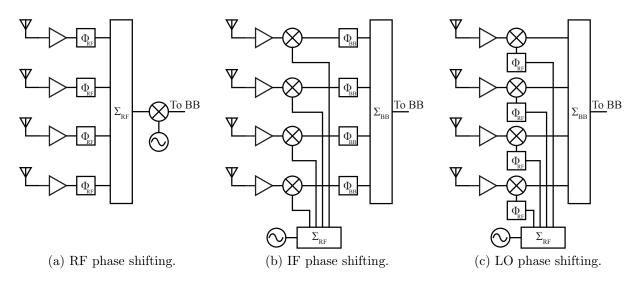

| 1.9  | Phased array architectures                                                                                                                                                                            | 10 |

| 2.1  | Lumped resonant tanks                                                                                                                                                                                 | 16 |

| 2.2  | Transmission line with arbitrary load                                                                                                                                                                 | 17 |

| 2.3  | RLGC ladder representation of transmission line                                                                                                                                                       | 18 |

| 2.4  | Ideal transmission line input impedance                                                                                                                                                               | 19 |

| 2.5  | Lossy transmission line input impedance (plotted for Q=10)                                                                                                                                            | 21 |

| 2.6  | Current and voltage standing waves for a quarter-wavelength transmission line.                                                                                                                        | 22 |

| 2.7  | A tapered quarter wave transmission line utilizes wide width and large gap spacing when the current is high (voltage is low) and narrow width and small gap when the voltage is high (current is low) | 23 |

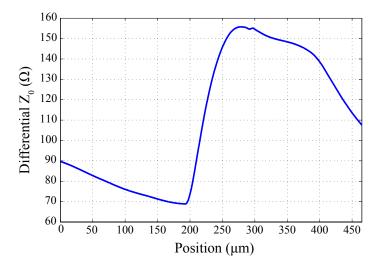

| 2.8  | The layout of the optimized quarter wave line. The characteristic impedance, $Z_o$ , is non-constant. Slotting is introduced to satisfy design rules                                                  | 24 |

| 2.9  | The optimum characteristic impedance profile                                                                                                                                                          | 25 |

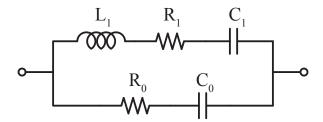

| 2.10 | MEMS resonator model                                                                                                                                                                                  | 26 |

| 2.11 | MEMS resonator impedance                                              | 27 |

|------|-----------------------------------------------------------------------|----|

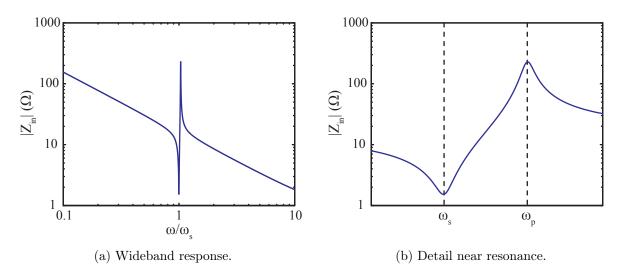

| 2.12 | Single turn ring inductor                                             | 28 |

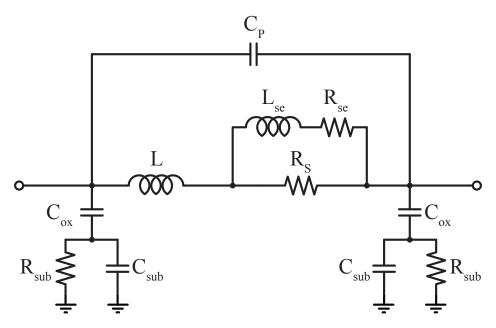

| 2.13 | Wideband lumped element inductor model                                | 29 |

| 2.14 | Simplified inductor model valid over a narrow frequency range         | 31 |

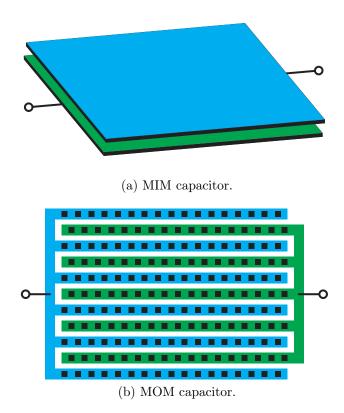

| 2.15 | On-chip capacitor structures                                          | 32 |

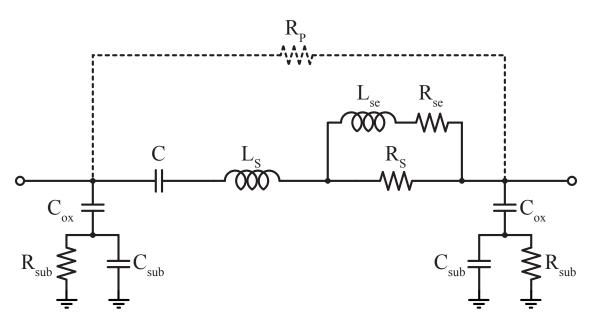

| 2.16 | Wideband lumped element capacitor model                               | 33 |

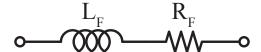

| 2.17 | Simplified capacitor model valid over a narrow frequency range        | 33 |

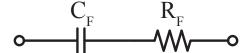

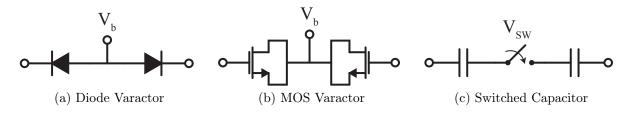

| 2.18 | Switched capacitor                                                    | 34 |

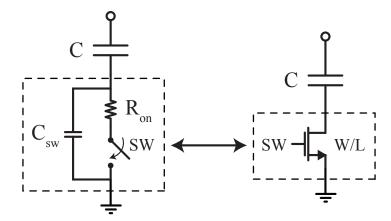

| 2.19 | Diode varactor                                                        | 35 |

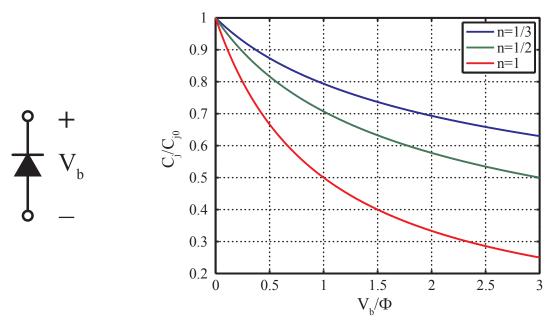

| 2.20 | MOS varactor                                                          | 37 |

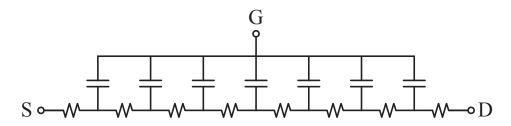

| 2.21 | Distributed channel impedance model for MOS varactor                  | 37 |

| 2.22 | MOS varactor layout                                                   | 39 |

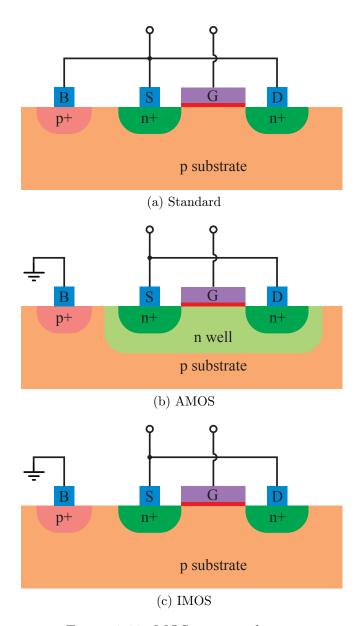

| 2.23 | On-chip transmission lines                                            | 40 |

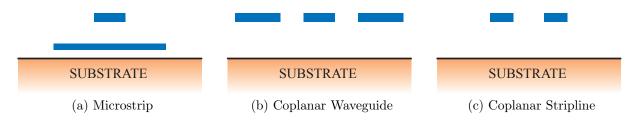

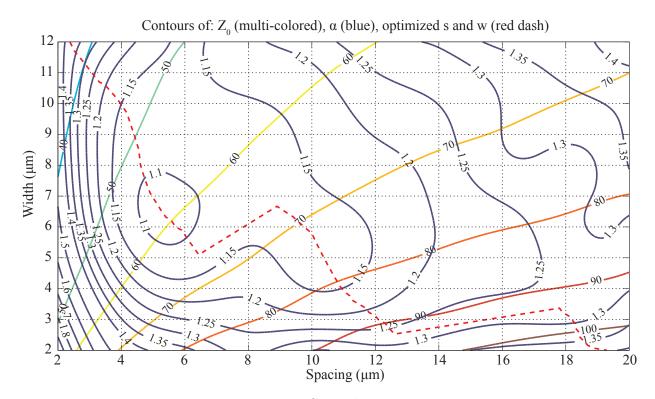

| 2.24 | CPW design space                                                      | 41 |

| 2.25 | CPW design space                                                      | 42 |

| 2.26 | E-fields for the two modes present in the CPW structure               | 43 |

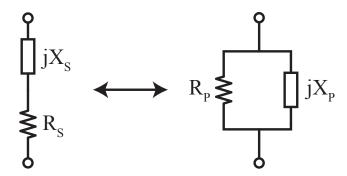

| 2.27 | Series and parallel representations of a complex impedance            | 47 |

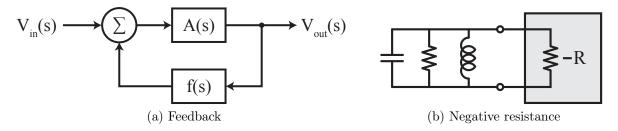

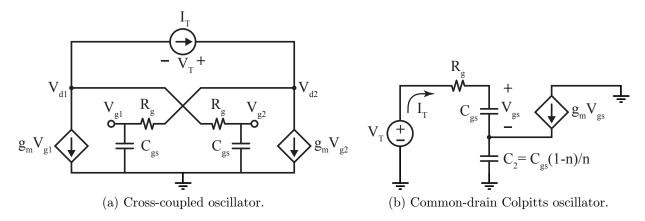

| 3.1  | Mechanisms of oscillation                                             | 50 |

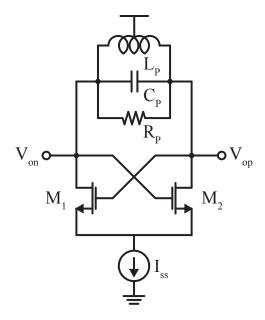

| 3.2  | Cross-coupled differential pair VCO with tuning                       | 51 |

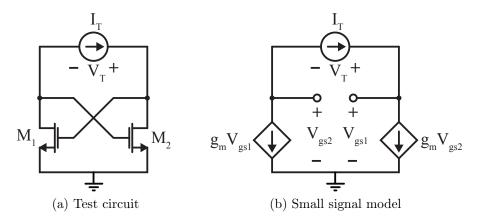

| 3.3  | Cross-coupled differential pair input impedance                       | 52 |

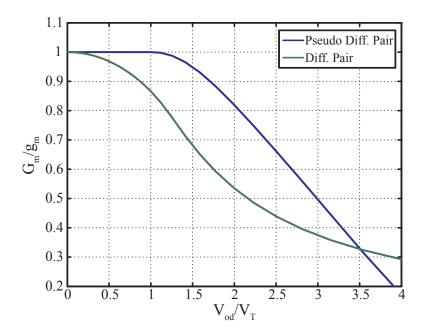

| 3.4  | Large signal $G_m$                                                    | 54 |

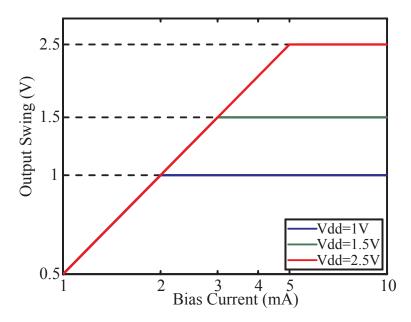

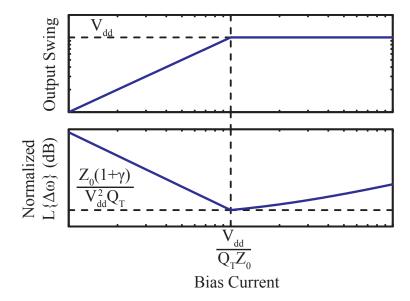

| 3.5  | Current limited vs. voltage limited operation. $(Z_o = 50, Q_T = 10)$ | 55 |

| 3.6  | Variable capacitor architectures                                      | 56 |

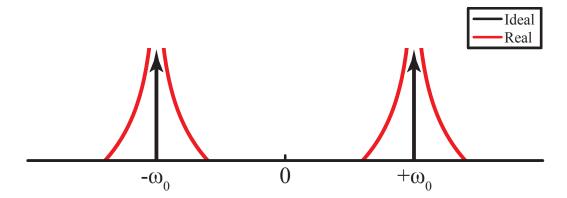

| 3.7  | Oscillator output spectrum                                            | 59 |

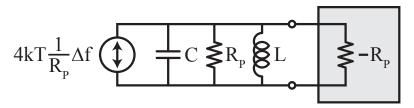

| 3.8  | Oscillator LTI noise model                                            | 60 |

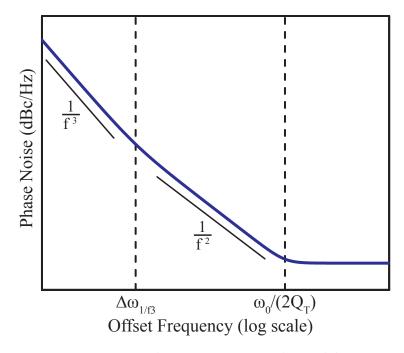

| 3.9  | Phase noise: Leeson's model                                           | 62 |

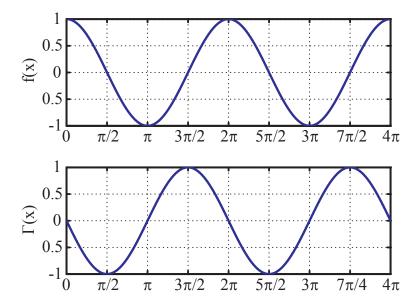

| 3.10 | Output waveform and ISF of an ideal sinusoidal oscillator             | 64 |

|      | Phase noise optimization.                                             | 67 |

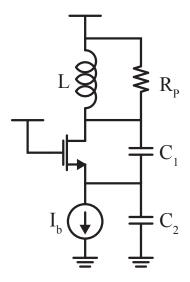

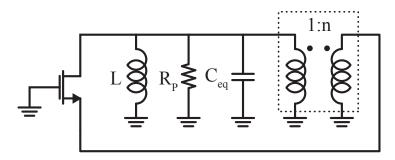

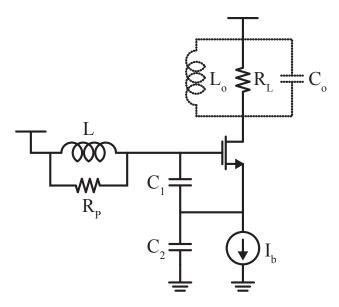

|      | Colpitts oscillator schematic                                         | 68 |

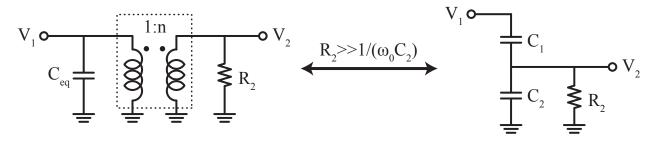

|      | Capacitive divider as ideal transformer                               | 68 |

|      |                                                                       |    |

| 3.14 | Colpitts oscillator effective model (biasing omitted)                                                                               | 69  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

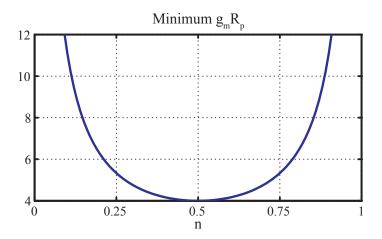

| 3.15 | Colpitts startup constraint                                                                                                         | 70  |

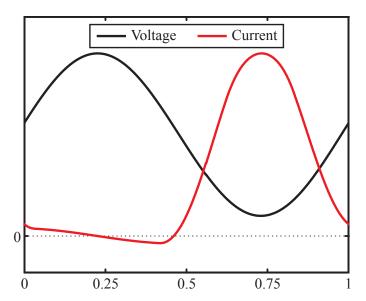

| 3.16 | Colpitts oscillator waveforms                                                                                                       | 72  |

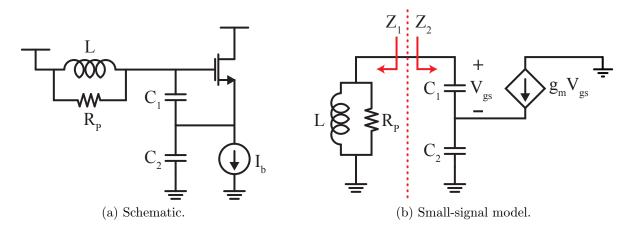

| 3.17 | Common-Drain Colpitts Oscillator                                                                                                    | 74  |

| 3.18 | Common-drain Colpitts oscillator provides buffering for free                                                                        | 75  |

| 3.19 | Differential Colpitts Oscillators                                                                                                   | 76  |

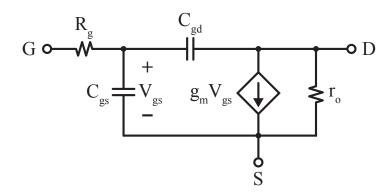

| 3.20 | Transistor small-signal model                                                                                                       | 77  |

| 3.21 | Oscillator small signal models including $R_g$ and $C_{gs}$                                                                         | 79  |

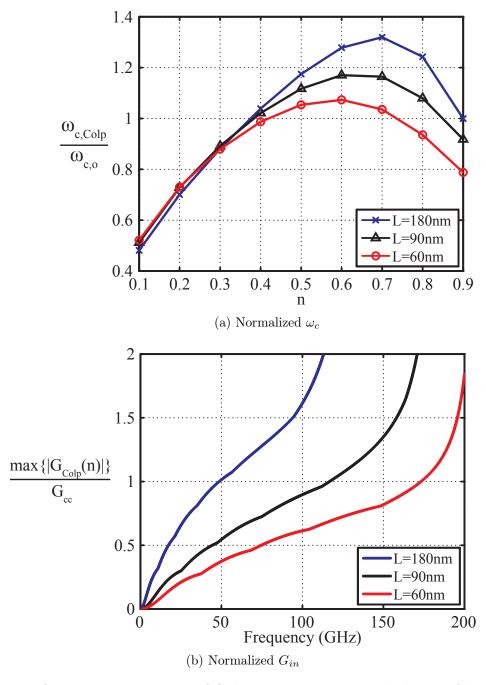

| 3.22 | Performance comparisons of Colpitts versus cross-coupled core. All simulations are performed in a 65nm process node                 | 81  |

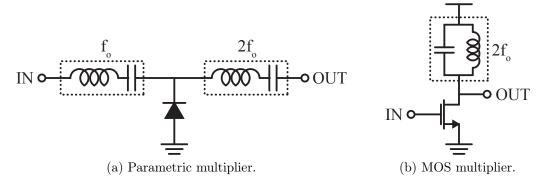

| 3.23 | Frequency multipliers                                                                                                               | 82  |

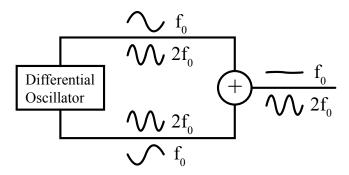

| 3.24 | Push-push principle                                                                                                                 | 84  |

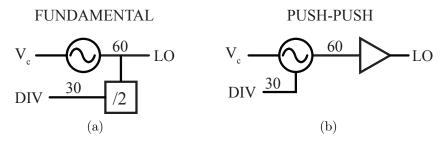

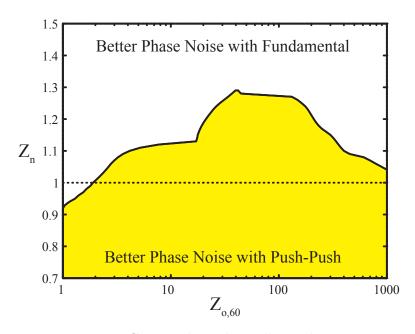

| 3.25 | Fundamental vs. push-push                                                                                                           | 85  |

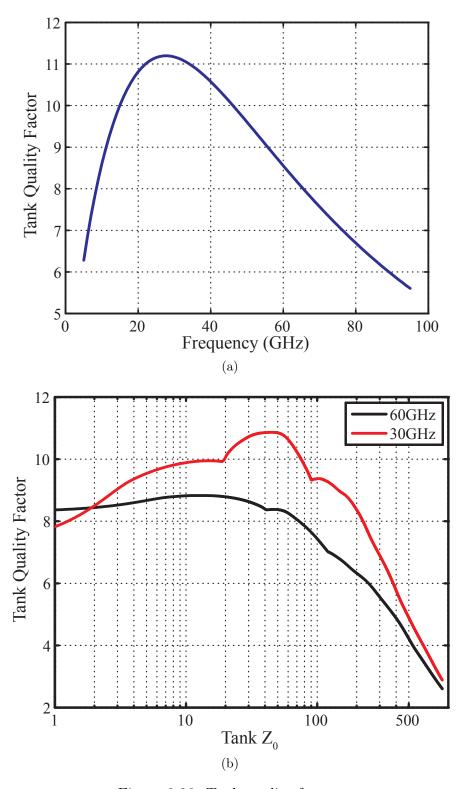

| 3.26 | Tank quality factor                                                                                                                 | 88  |

| 3.27 | 60GHz push-push oscillator design space                                                                                             | 89  |

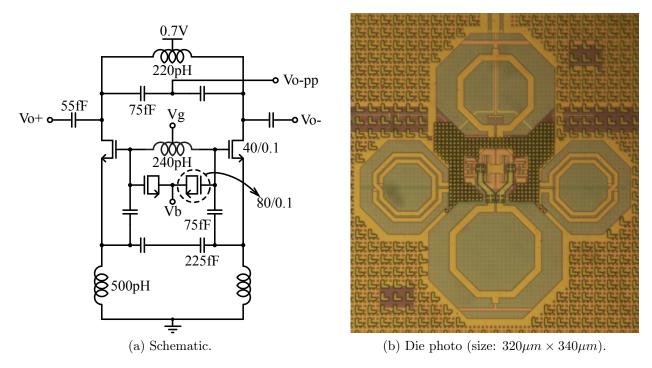

| 3.28 | Push-push oscillator prototype                                                                                                      | 91  |

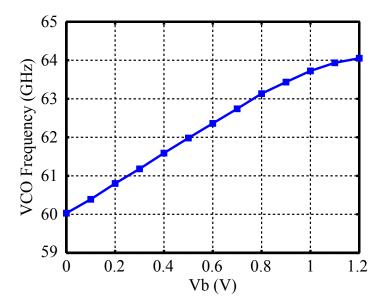

| 3.29 | Push-push oscillator measured tuning range                                                                                          | 92  |

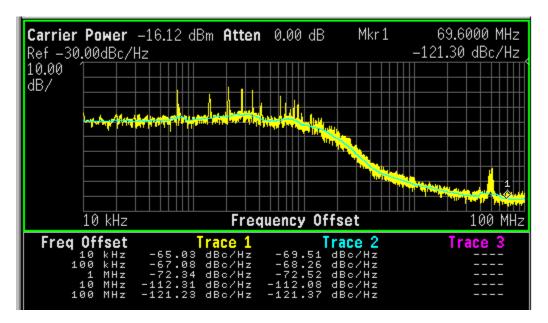

| 3.30 | Push-push oscillator measured phase noise                                                                                           | 93  |

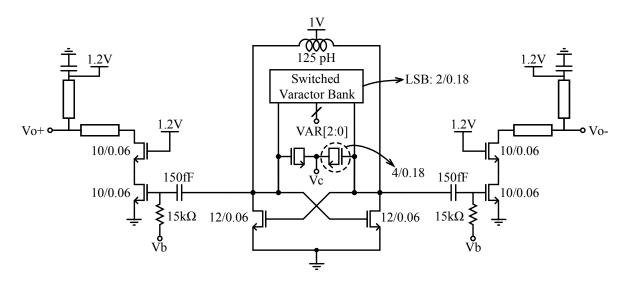

| 3.31 | Cross-coupled oscillator schematic                                                                                                  | 93  |

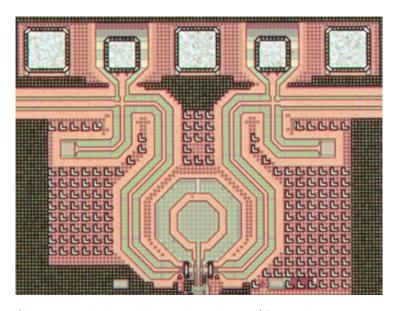

| 3.32 | Cross-coupled oscillator die photo. (Area shown: $490 \mu m \times 380 \mu m$ )                                                     | 94  |

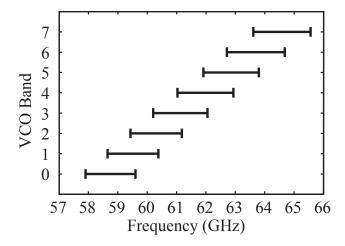

| 3.33 | Cross-coupled oscillator measured tuning range                                                                                      | 96  |

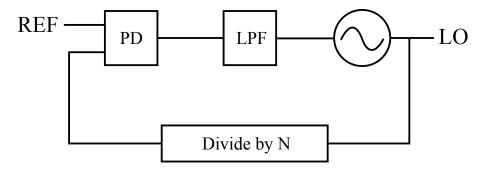

| 4.1  | A general phase locked loop                                                                                                         | 99  |

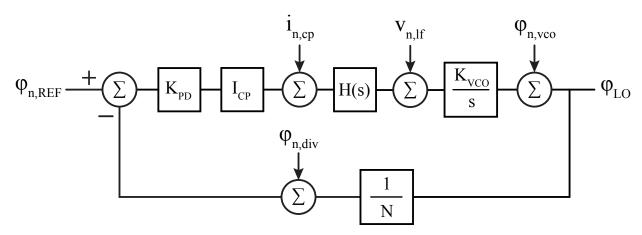

| 4.2  | Phase domain model                                                                                                                  | 101 |

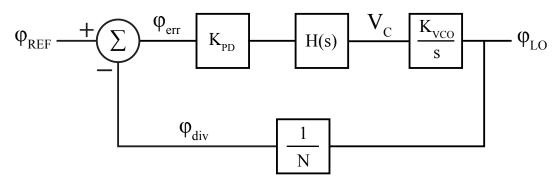

| 4.3  | XOR phase detector                                                                                                                  | 102 |

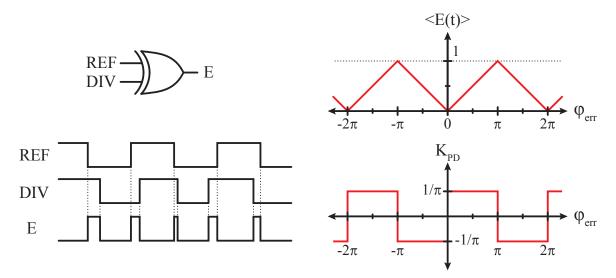

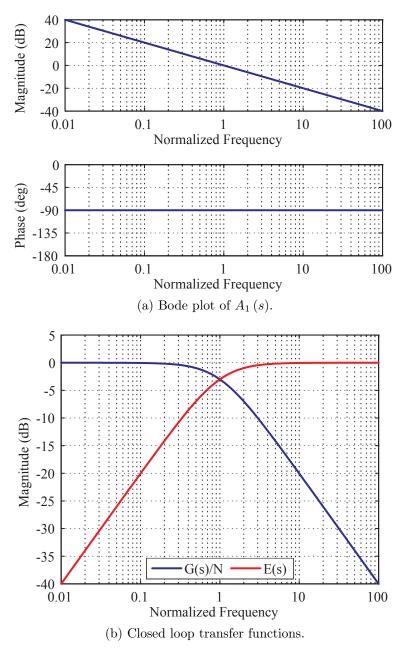

| 4.4  | First order loop response                                                                                                           | 105 |

| 4.5  | A first-order loop filter                                                                                                           | 106 |

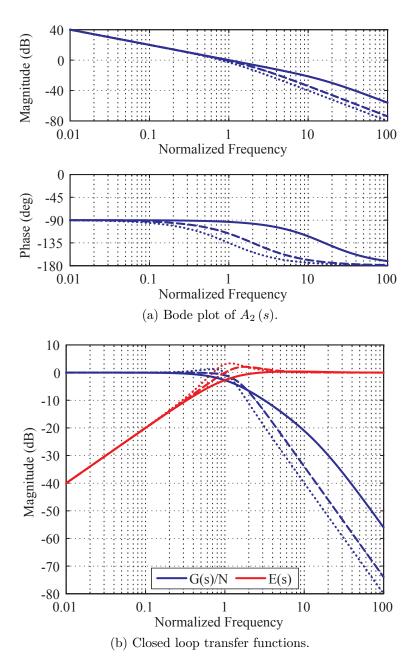

| 4.6  | Second order loop response (dotted: $\zeta=1/2,PM=52^\circ;$ dashed: $\zeta=1/\sqrt{2},PM=65^\circ;$ solid: $\zeta=2,PM=86^\circ).$ | 108 |

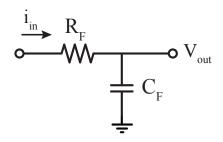

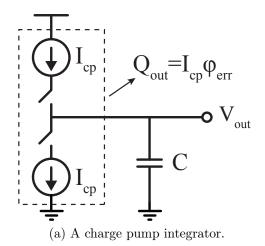

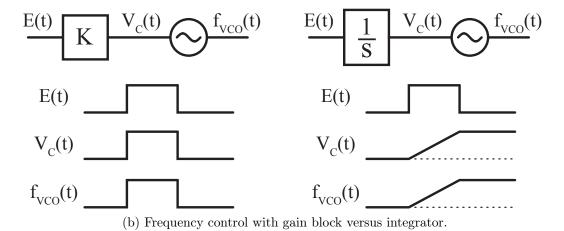

| 4.7  | Adding an integrator to the loop filter                                                                                             | 109 |

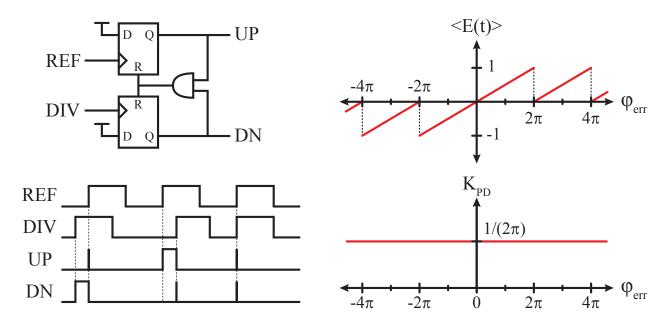

| 4.8  | A flip-flop based Phase Frequency Detector (PFD)                                                                                    | 110 |

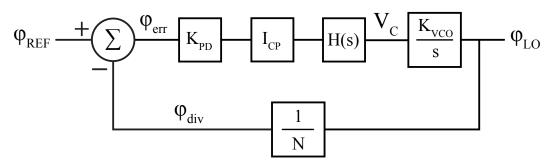

| 4.9  | Charge pump based PLL                                                                                                                                              | 111 |

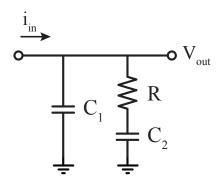

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

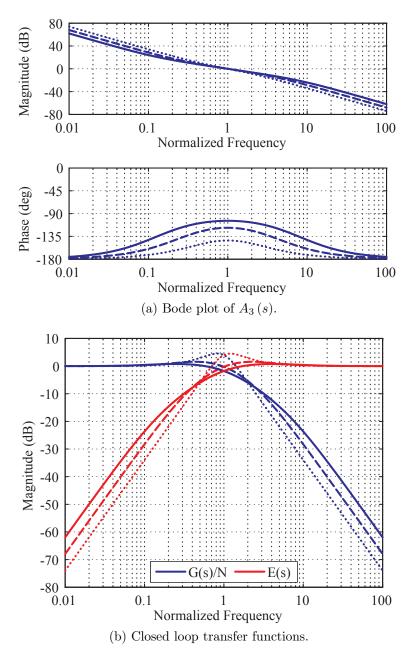

| 4.10 | Second order loop filter for charge pump PLL                                                                                                                       | 112 |

| 4.11 | Third order Type-II loop response (dotted: $f_p/f_z=4$ , $PM=37^\circ$ ; dashed: $f_p/f_z=16$ , $PM=62^\circ$ ; solid: $f_p/f_z=64$ , $PM=76^\circ$ )              | 113 |

| 4.12 | PLL noise sources                                                                                                                                                  | 114 |

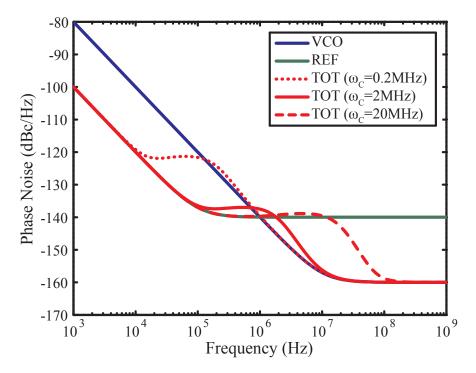

| 4.13 | Selection of PLL bandwidth based on phase noise                                                                                                                    | 118 |

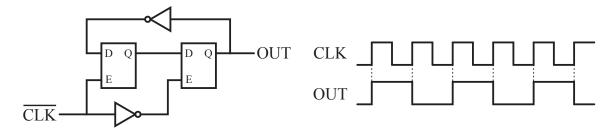

| 4.14 | Master-slave flip-flop divide by 2                                                                                                                                 | 119 |

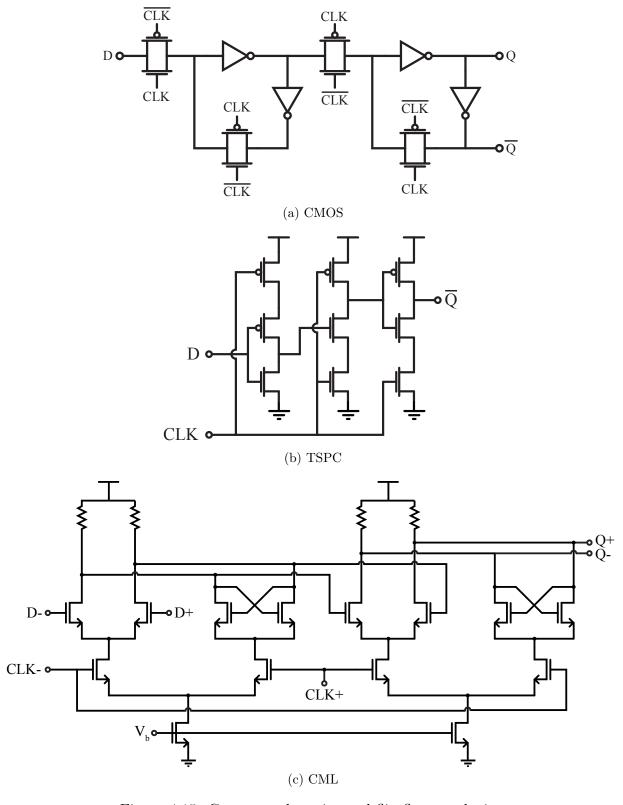

| 4.15 | Common edge-triggered flip-flop topologies                                                                                                                         | 121 |

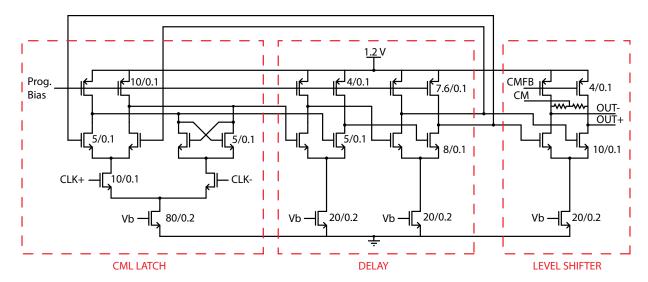

| 4.16 | CML pulsed-latch divider                                                                                                                                           | 123 |

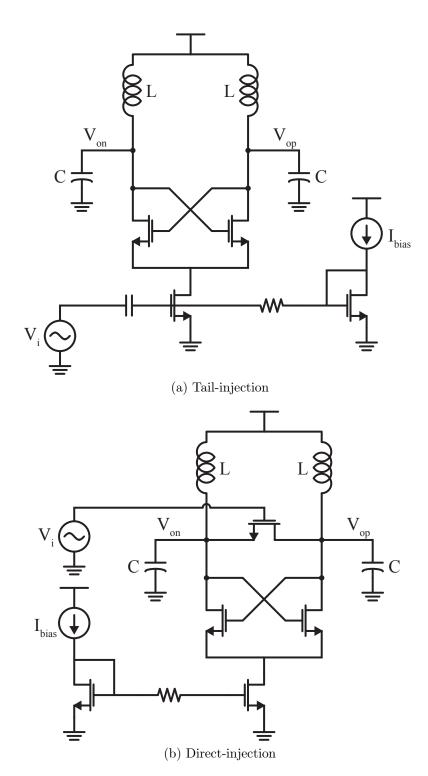

| 4.17 | Injection locked dividers                                                                                                                                          | 125 |

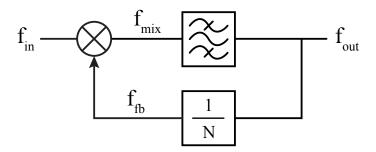

| 4.18 | Regenerative (Miller) divider                                                                                                                                      | 126 |

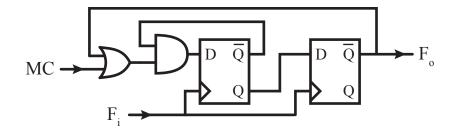

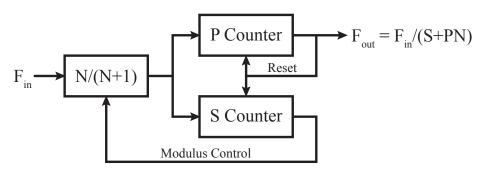

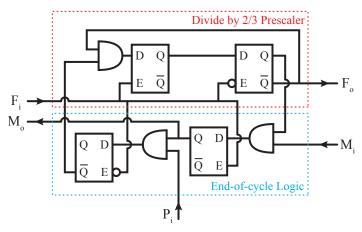

| 4.19 | 2/3 prescaler                                                                                                                                                      | 128 |

| 4.20 | Program/Swallow Counter                                                                                                                                            | 128 |

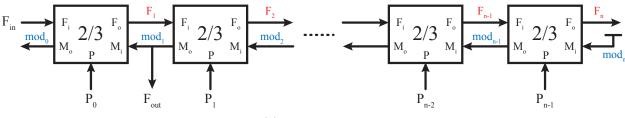

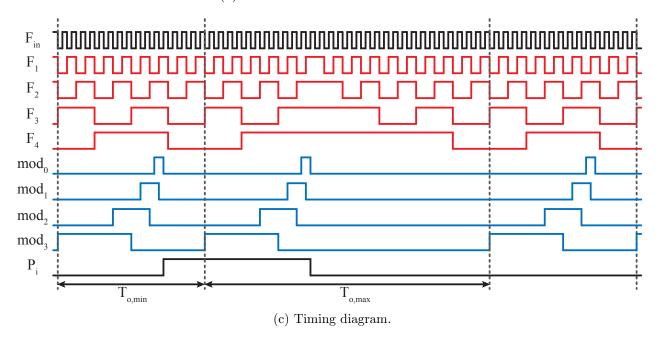

| 4.21 | Vaucher modular prescaler                                                                                                                                          | 130 |

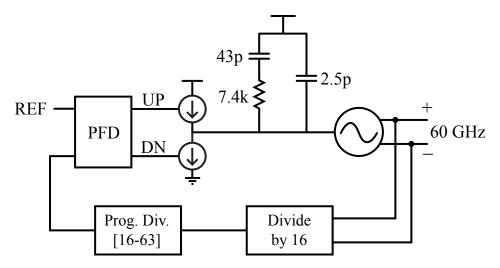

| 4.22 | Integer-N PLL block diagram                                                                                                                                        | 131 |

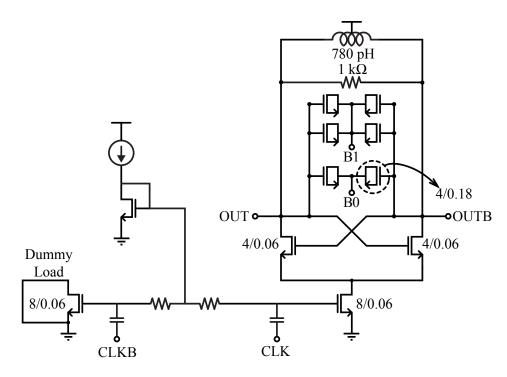

| 4.23 | Schematic of injection locked divider                                                                                                                              | 132 |

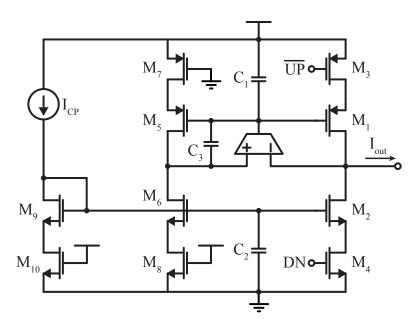

| 4.24 | Simplified charge pump schematic                                                                                                                                   | 133 |

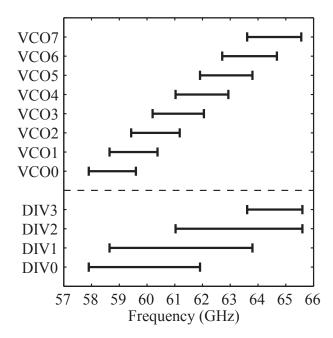

| 4.25 | Measured VCO and injection locked divider tuning range. (Measurement of divider tuning range limited by VCO.)                                                      | 134 |

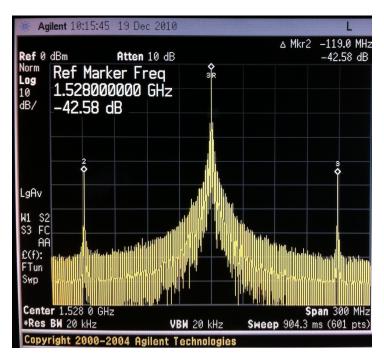

| 4.26 | Spectrum of locked PLL at 61GHz downconverted with external mixer to allow measurement with Agilent E4440A Spectrum Analyzer. Reference spurs are less than -40dBc | 135 |

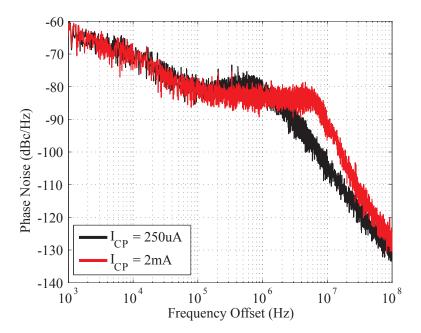

| 4.27 |                                                                                                                                                                    | 136 |

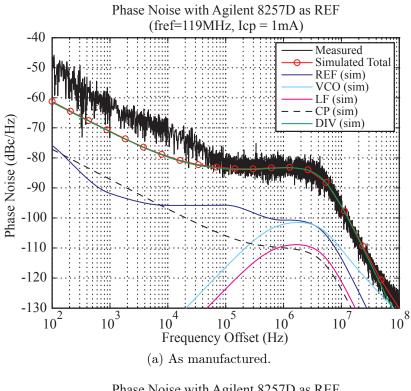

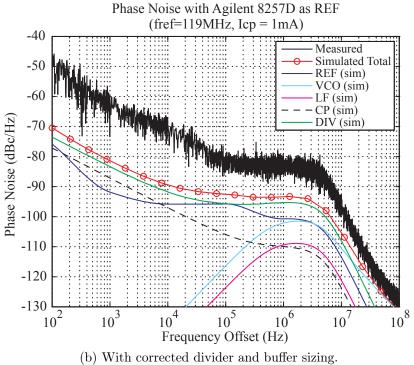

| 4.28 | Comparison between measured PLL phase noise and system simulation (including individual contributors)                                                              | 137 |

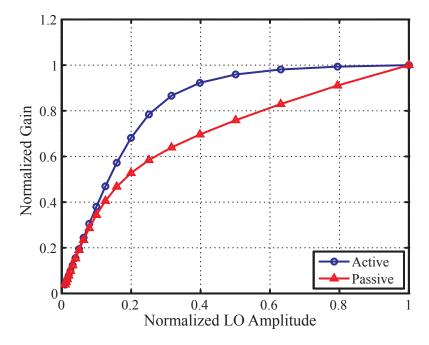

| 5.1  | Comparison of mixer gain vesus LO amplitude                                                                                                                        | 141 |

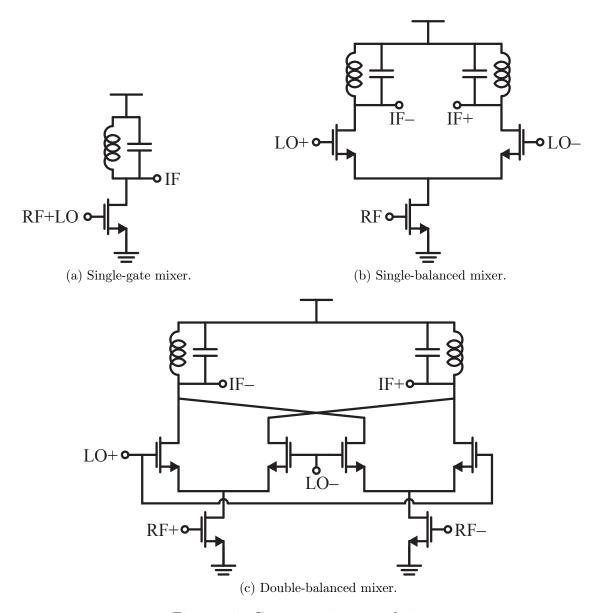

| 5.2  | Common mixer topologies                                                                                                                                            | 142 |

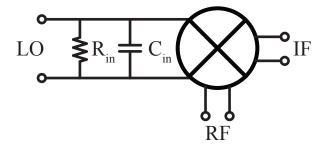

| 5.3  | Mixer input admittance                                                                                                                                             | 142 |

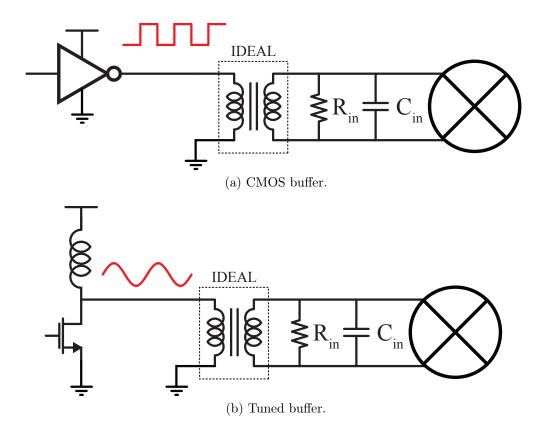

| 5.4  | LO buffer topologies                                                                                                                                               | 143 |

| 5.5  | LO generation strategies                                                                                                                                           | 145 |

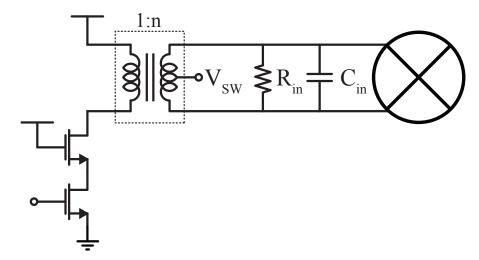

| 5.6  | LO buffer schematic                                                                                                                                                | 147 |

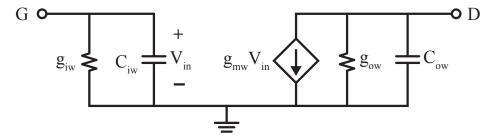

| 5.7  | Width-scalable transistor model                                                                                                              | 149 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

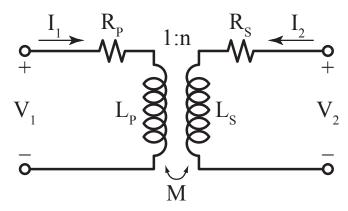

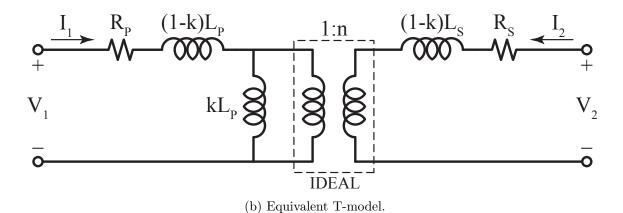

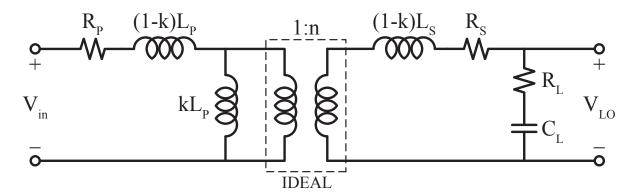

| 5.8  | Transformer models                                                                                                                           | 150 |

| 5.9  | Model of transformer with effective mixer load                                                                                               | 152 |

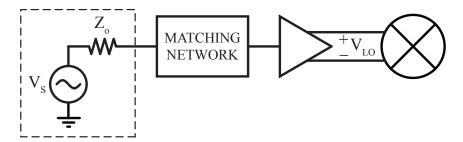

| 5.10 | Matched buffer driven by source with impedance $Z_o$                                                                                         | 155 |

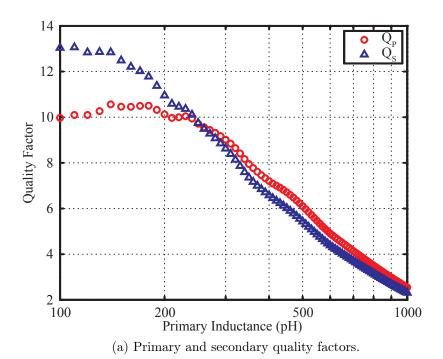

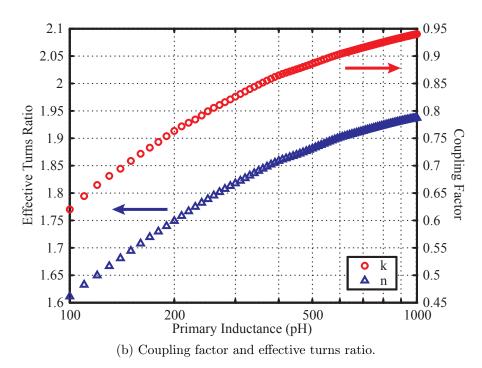

| 5.11 | Simulated 1:2 transformer parameters as a function of $L_p$                                                                                  | 157 |

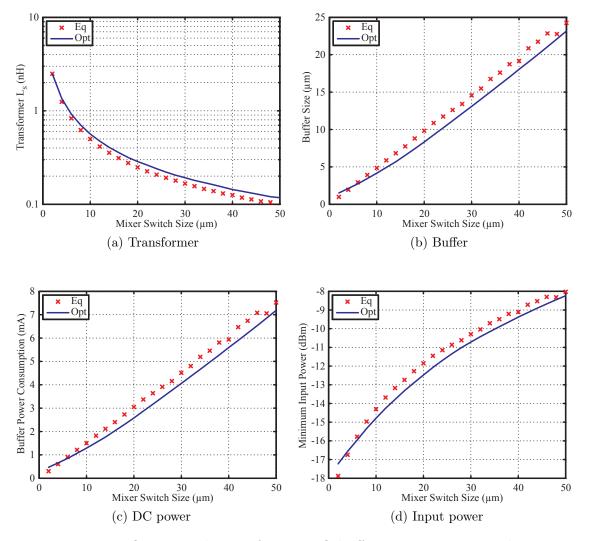

| 5.12 | Optimum design of Mixer LO buffer versus mixer switch size                                                                                   | 161 |

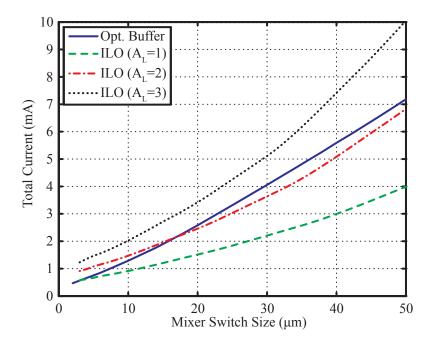

| 5.13 | Current required for an ILO as a function of mixer switch size and loop gain (optimized buffer result added for comparison)                  | 163 |

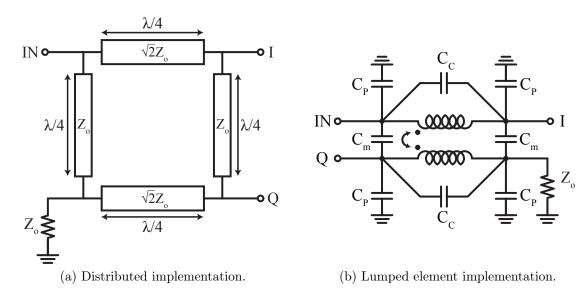

| 5.14 | 90° Hybrids                                                                                                                                  | 164 |

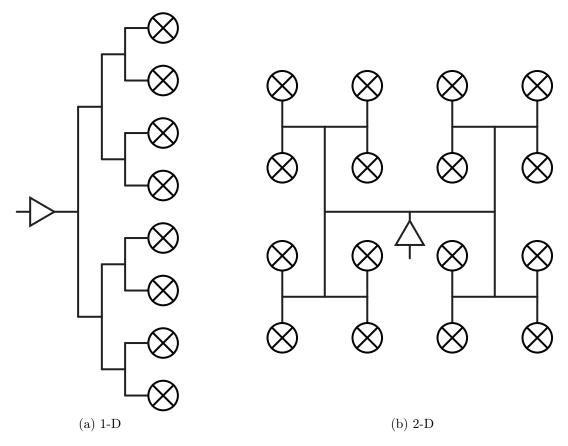

| 5.15 | Tree distribution networks                                                                                                                   | 166 |

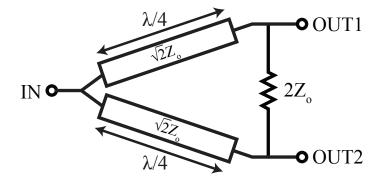

| 5.16 | Wilkinson power splitter                                                                                                                     | 166 |

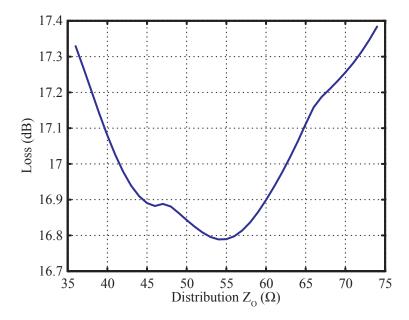

| 5.17 | Loss of LO distribution network for a sample 16 element linear array with $250\mu m$ pitch                                                   | 168 |

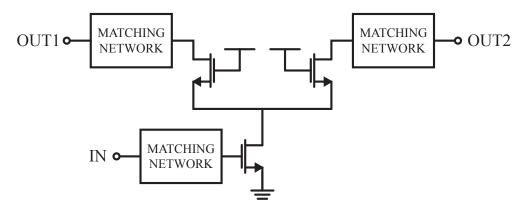

| 5.18 | Active splitter.                                                                                                                             | 168 |

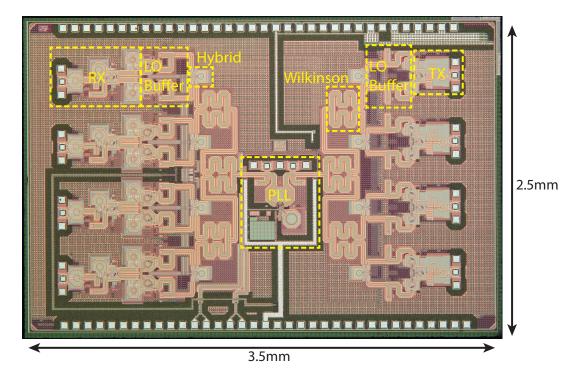

| 5.19 | 4-element 60GHz phased array transceiver die photo                                                                                           | 169 |

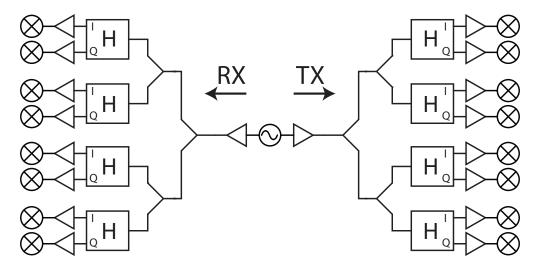

| 5.20 | Phased array transceiver LO block diagram                                                                                                    | 170 |

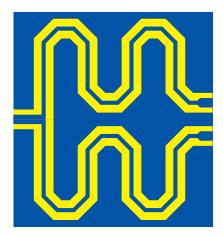

| 5.21 | Compact 2-way Wilkinson power divider layout                                                                                                 | 171 |

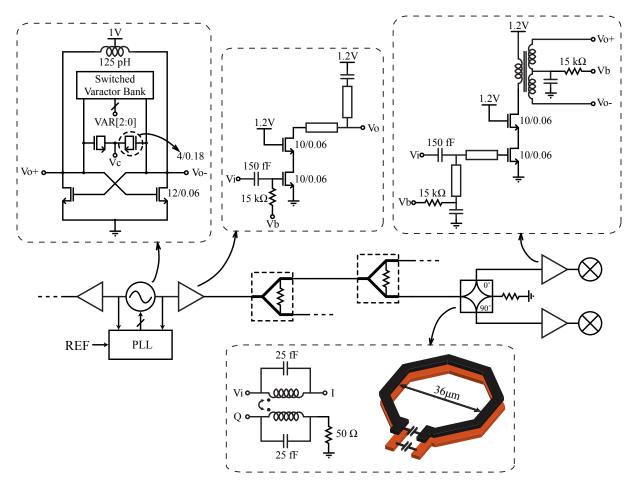

| 5.22 | Schematic of VCO, LO buffers, and LO distribution chain including Wilkinson power splitters and transformer coupled lumped quadrature hybrid | 172 |

## List of Tables

| 1.1 | Phased array architecture comparison                      | 12  |

|-----|-----------------------------------------------------------|-----|

| 2.1 | Frequency-Q product of MEMS resonators                    | 28  |

| 3.1 | Sample values of $n_{opt}$ for Colpitts oscillator        | 73  |

| 3.2 | Push-push versus fundamental oscillator selection         | 89  |

| 3.3 | Push-Push oscillator performance summary and comparison   | 97  |

| 3.4 | Fundamental oscillator performance summary and comparison | 97  |

| 4.1 | PLL performance summary and comparison                    | 138 |

### Acknowledgments

This work is the culmination of collaborations with many wonderful and talented people and would not have been possible without their contributions. I would first like to thank my advisor Prof. Ali M. Niknejad for his help and support. From teaching, to research, to the job search, he was always available with great advice. I would like to also thank Prof. Elad Alon for invaluable guidance and feedback over many years and numerous projects. I would also like to thank Prof. Paul K. Wright for being a part of my thesis committee and providing valuable feedback.

Graduate school is a significant undertaking with many challenges both personal and professional. I would like to thank two people in particular for taking on these challenges with me and making my time at Berkeley such a memorable experience, Jesse Richmond and Michael Mark. I thank you both deeply for your friendship and I can say without a doubt that meeting and getting to know you was the best part of grad school. Thank you also to my friends from BWRC that always kept life fun and interesting: Mervin John, Louis Alarcon, Debopriyo Chowdhury, Amin Arbabian, and Maryam Tabesh. Thank you also for all of our technical discussions and late night coffee runs to keep us working into the wee morning hours. Last, but definitely not least, I would like to thank all the people that I've had the pleasure to work with over the years and who have provided so much insight and technical advice: Mounir Bohsali, Babak Heydari, Wei-Hung Chen, Zhiming Deng, Patrick Reynaert, Ehsan Adabi, Bagher Afshar, Lingkai Kong, Jiashu Chen, Jungdong Park, and Chintan Thakkar.

Finally, I would like to deeply thank my family for all of their love and support. My mom, Domnica, and my dad, Mihai, have sacrificed so much so I could be where I am today. You have always pushed me to be the best I can be and have supported me no matter what I chose to do. To my sister, Gabi, thank you for always being there for me. We've come a long way from where we started and been all over the world. I hope I can be as helpful and supportive to you as you've been for me. Special thanks have to go to my loving wife, Alex. Your love and support have kept me going in good times and bad and I couldn't have asked for a better woman to share my life with. I thank you from the bottom of my heart.

## Chapter 1

## Introduction

Increased memory capacity and processing power in mobile devices has led to demands of ever increasing data rate communication in order to enable fast synchronization capabilities for mobile devices as well as media sharing and access. However, battery life is still at a premium in mobile devices, and power consumption must be kept low despite the increased data rate. The demands on these systems results in a need for radios that can transmit data at multi-Gb/s rates over a distance of less than 10m while consuming power on the order of hundreds of mW or less.

### 1.1 The 60GHz Band

The FCC has allocated a license free band of approximately 9GHz from 57GHz-66GHz with similar allocations available around the world. Attenuation due to oxygen in the atmosphere is on the order of 10-20dB/km in this band (Fig. 1.1), while rain can introduce as much as 40-50dB/km of additional attenuation [Liebe81, Smith82]. Due to this high loss, the 60GHz band is not useful for long range communication. At medium range, however, the attenuation provides security and the possibility of frequency reuse since the signal of one transmitter will not interfere with another placed only a few km away. Medium range uses in the past have included point-to-point links over distances of 1-2km with highly directional antennas for applications such as fiber extension or cellular backhaul.

At very short range, on the order of 10s of meters or less, we do not have to contend with atmospheric absorption. However, common building materials are very lossy. Transmitting a signal through a wall, for example, can attenuate it by 40-50dB while a reflection results in 10-20dB of attenuation. This implies that 60GHz links are most efficient in line-of-sight arrangements and will mostly be limited to operation within the same room or floor due to power constraints.

Figure 1.1: Attenuation due to molecular resonances in the atmosphere (sea-level,  $25^{\circ}C$ ,  $7.5g/m^3$  water vapor density).

Figure 1.2: Constellations of simple modulation schemes.

Figure 1.3: Evolution of WLAN data rates.

The large bandwidth allocated around 60GHz means that high data rate communication can be achieved with very simple modulation schemes (Fig. 1.2). These types of simple modulation schemes are not very spectrally efficient but are power efficient since they do not require complicated baseband processing, and the requirements on front-end linearity and carrier spectral purity are relaxed when compared to Orthogonal Frequency Division Multiplexing (OFDM) schemes. Binary Phase Shift Keying (BPSK), and Quadrature Phase Shift Keying (QPSK) are constant envelope modulation schemes. Non-constant envelope modulation such as Quadrature Amplitude Modulation (QAM) can be used to increase data rates further but this type of modulation does require moderate linearity in the front-end and a high purity carrier for low Bit Error Rate (BER) communication. The modulation depth is thus practically limited to 16-QAM for 60GHz transceivers due to these requirements and the need for low power consumption.

Fig. 1.3 shows the evolution of data rates for Wireless Local Area Network (WLAN) radios based on the IEEE 802.11 standard first introduced in [IEE97] for operation in the 2.4GHz ISM band and later ammended to include the much larger 5GHz ISM band as well as data rate enhancements in both bands.<sup>1</sup> Existing WLAN solutions can provide service throughout a house with multiple floors at data rates as high as 150Mb/s. The upcoming 802.11ac ammendment will extend the maximum single stream data rate up to 433Mb/s between transceivers of the type suitable for mobile applications. The 60GHz band is thus well situated to provide short-range, high data rate communication within a line-of-sight environment, augmenting the lower data rates but higher range of legacy WLAN solutions.

<sup>&</sup>lt;sup>1</sup>http://grouper.ieee.org/groups/802/11/Reports/802.11 Timelines.htm

Figure 1.4: ITRS Roadmap for RF CMOS Technology.

Two competing standards are currently making their way through the IEEE standards-making bodies to address this opportunity. One is an ammendment to the existing 802.11 standard, dubbed 802.11ad and has a focus on backward compatibility and interoperability with legacy 802.11 devices. The other standard is 802.15.3c [IEE09] and comes from the Wireless Personal Area Network (WPAN) community normally associated with low power and low data rate Wireless Sensor Networks (WSN). Both standards are actually very similar and market forces will likely drive them closer together and toward interoperability. The challenge then from the circuit side is to build a compact 60GHz transceiver to meet the high data rate requirements of these standards with low power consumption and cost since these are the key drivers in consumer mobile applications.

### 1.2 CMOS for 60GHz

Traditionally, mm-wave design has been limited to expensive III-V compound technologies due to their higher speed, and thus higher gain, compared to Silicon technologies. However, the microprocessor and memory industry has continued to push advances in Silicon, increasing the speed of Complementary Metal Oxide Semiconductor (CMOS) processes year by year (Fig. 1.4).<sup>2</sup> Today, CMOS technologies have more than enough speed for mm-wave design and the gain available at 60GHz continues to increase. This increase in speed, however, has to come at the expense of a continued reduction in supply voltage. The dynamic power

<sup>&</sup>lt;sup>2</sup>http://www.itrs.net/reports.html

consumption of a digital gate is given by

$$P_{dyn} = \alpha C V_{dd}^2 f \tag{1.1}$$

where  $\alpha$  is the activity factor, C is the total load capacitance,  $V_{dd}$  is the supply voltage, and f is the clock frequency. Therefore, for digital signal processing, lowering the supply voltage helps to significantly reduce power consumption. Unfortunately, noise, linearity, and output power all require higher supply voltages to improve. Therefore, analog design gets harder with reduced supply voltages. This means we must be more careful when designing in CMOS and we must make the right architectural choices to enable circuit design at reduced supply voltages. Holistic optimization from architecture down to individual building blocks is a necessity.

At the same time, CMOS provides many advantages over other more exotic technologies. The first of these advantages comes from the low power consumption of digital signal processing in CMOS. This enables complete integration of mm-wave circuits with low frequency mixed-signal circuits and digital signal processing all on the same die, eliminating the need for complex and costly packaging of multiple dies. There is also an inherent operational efficiency in this integration since all signals are processed on the same die so no high frequency and/or high dynamic range IO is necessary.

High speed CMOS digital signal processing also allows built-in-self-test (BIST) capabilities to be integrated on the same die. This reduces test time and test complexity, one of the largest cost centers in semiconductor manufacturing. BIST allows transceivers to self-test and self-calibrate helping to quickly screen out faulty parts or debug problems to increase yield.

Finally, the small wavelength of 60GHz signals also provides advantages for integration of passive components. At 60GHz, the free-space wavelength is approximately 5mm, while the on-chip wavelength is approximately 2.4mm. These dimensions are on the order of typical die sizes for integrated circuits. On one hand this means that distributed effects must be taken into account, making circuit design more difficult. On the other hand, lumped passive components such as capacitors and inductors become very small and easy to integrate. At these frequencies, even antennas can be integrated on-chip thus removing any need to move mm-wave signals on- and off-chip.

### 1.3 60GHz Transceivers

The block diagram of a typical direct conversion transceiver is shown in Fig. 1.5. It consists of a transmitter path, a receiver path, and baseband which generates data to be transmitted and processes received data. The data generated by the baseband is first converted to an analog signal by the digital to analog converter (DAC) and upconverted to RF by a mixer. The upconverted signal is then amplified by the power amplifier (PA) and sent to

Figure 1.5: Direct conversion transceiver block diagram.

the antenna to be transmitted. On the receive side a low noise amplifier (LNA) amplifies the received signal from the antenna and a mixer converts the signal down to baseband. The resulting signal is then digitized by an analog to digital converter (ADC) and processed by the baseband to extract the information. Both transmit (TX) and receive (RX) paths require a high frequency Local Oscillator (LO) signal to be delivered to the mixer for up and down conversion respectively. This carrier signal is noisy and introduces phase variations to the modulation constellation. For example, Fig. 1.6 shows the effect of carrier phase noise on a QPSK constellation. If the carrier phase noise is too large, the transmitted data cannot be recovered without errors. Therefore, one of the main requirements on the LO generation is low phase noise.

Beside the LO there are other sources of noise which serve to corrupt the received signal. First, an antenna will receive noise from its environment proportional to the observed bandwidth, B.

$$N_{ant} = kTB (1.2)$$

The filters in the RX are thus designed to limit the bandwidth to the desired signal bandwidth to limit this source of noise. Second, all circuits in the receiver chain contribute their own noise due to the presence of active devices and/or resistive losses. For any circuit, the noise factor, F, is defined as the ratio of SNR at its input to SNR at its output.

$$F = \frac{SNR_i}{SNR_o} \tag{1.3}$$

The noise figure, NF, is simply the noise factor converted to dB.

$$NF = 10log_{10}F \tag{1.4}$$

The noise factor is always greater than 1 so the noise figure is always greater than 0dB. For a cascade of multiple blocks, each with noise factor  $F_i$  and gain  $G_i$ , the noise figure of the

Figure 1.6: QPSK constellation with noisy carrier.

cascade is given by<sup>3</sup>

$$F_{tot} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots$$

(1.5)

### 1.3.1 Link Budget Analysis

The maximum communication distance for a transceiver is limited by the amount of power we can transmit, antenna gains, and noise. For a receiver using an antenna with gain  $G_r$ , the power received from a transmitter at a distance d sending power  $P_t$  into an antenna with gain  $G_t$  at frequency f can be found using the Friis free-space path loss equation [Friis46]

$$P_r = P_t G_t G_r \left(\frac{c}{4\pi f d}\right)^2 \tag{1.6}$$

where c is the speed of light. The path loss is simply the received power normalized to the transmitted power

$$L_{chan} = G_t G_r \left(\frac{c}{4\pi f d}\right)^2 \tag{1.7}$$

Notice that for a fixed antenna gain the path loss gets worse with increasing frequency. To get a feeling for how large this loss can be at 60GHz, we can solve (1.7) assuming 0dBi gain

<sup>&</sup>lt;sup>3</sup>Original derivation by [Friis44] but can also be found in [Razavi98, pg. 45] or [Gonzalez97, pg. 298].

Figure 1.7: BER as a function of SNR for different modulation schemes.

antennas at either end of the link, resulting in a loss of 68dB at a distance of only 1m. This loss assumes a clear line of sight between the transmitter and receiver, so any obstacles or reflections could increase this number dramatically.

Antennas with high gain are expensive and bulky and therefore not compatible with low cost mobile applications. Increasing the maximum communications distance thus requires either increasing the transmitted power or reducing the minimum required received power by increasing the receiver sensitivity. The maximum power that can be transmitted by a PA is limited by fundamental process parameters such as supply voltage and passive component losses so there is a fundamental limit on the ouptut power that can be achieved from a stand-alone transmitter.

On the receiver side, the minimum required input power is determined from the minimum required SNR. The SNR for a given BER depends on the particular modulation scheme. Fig. 1.7 shows the BER versus SNR for three different modulation schemes assuming an Additive White Gaussian Noise (AWGN) channel [Tse05]. A modulation scheme and required BER are first elected and the minimum required SNR is found. The minimum input power to the receiver can then be calculated from the signal bandwidth and the receiver noise figure using

$$P_{in} \ge SNR + NF + 10log_{10} (kTB) \tag{1.8}$$

Therefore, for a given signal bandwidth and modulation scheme the only way to increase the sensitivity of a stand-alone receiver is to decrease the noise figure. Since there are fundamental limits to how low a noise figure can be, there are fundamental limits to a stand-alone receiver's sensitivity.

Figure 1.8: Uniform linear 8-element phased array transceiver block diagram.

### 1.3.2 Phased Arrays

A phased array transceiver (Fig. 1.8) can be used to overcome these fundamental limitations on transmit power and receive sensitivity. Such a transceiver consists of multiple elements, each with its own antenna and phase shifter, positioned in an array with spacing on the order of the wavelength of the carrier frequency. The most common type of array is a uniform linear array with  $\lambda/2$  spacing. The antennas can be either directional themselves or omnidirectional, transmitting in all directions. For a low cost 60GHz phased array, planar antennas must be used which are roughly omnidirectional but require very little area.

In the TX, each element transmits the same signal shifted in phase by each element's phase shifter. The transmitted signals then add in space. The phase settings are used to align the transmitted signals from each antenna such that they add constructively only in one direction and cancel each other out in other directions. Most of the energy is thus transmitted in a very narrow beam whose direction can be changed by adjusting the phase shift in each element.

In a very similar way, in the RX, each element receives the same signal (but uncorrelated noise). The phase shifters are then used to realign the received signals such that only signals arriving from a certain direction add up constructively while signals coming from other directions cancel each other out. The array thus has very high sensitivity in one direction and very low sensitivity in all other directions.

A phased array thus behaves just like a mechanically steered, highly directional atenna. The

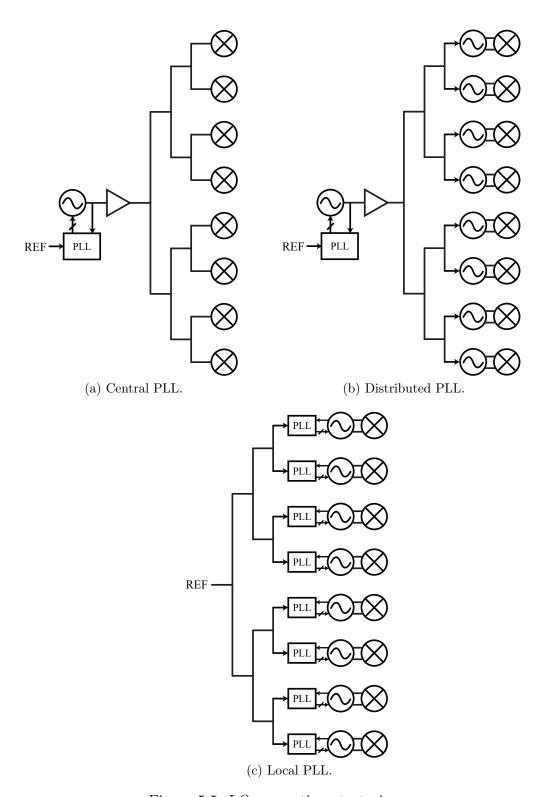

Figure 1.9: Phased array architectures.

advantage is that simple, low cost antennas can be used, and steering can be accomplished very quickly and accurately by adjusting the phase of each phase shifter. A phased array is used either to break the fundamental limitations on transmit power and receive sensitivity of a stand-alone transceiver or to relax the requirements on the performance of each element for a given level of overall array performance. In the TX, the equivalent isotropically radiated power (EIRP) increases with the square of the number of elements, N.

$$EIRP_{array} = N^2 \cdot P_{tx,el} \tag{1.9}$$

In the RX, the received signals are added together after being phase shifted appropriately leading to an  $N^2$  improvement in received signal power from the desired direction. However, each receiver also receives the same level of uncorrelated noise which, when added together, results in an increase in received noise by a factor of N. The array SNR thus only improves by a factor of N over the SNR of each individual receiver element.

$$SNR_{array} = N \cdot SNR_{el} \tag{1.10}$$

Thus, if both the TX and RX use arrays with N elements the link budget is improved by a factor of  $(N^3)$ .

The phase shifting operation can be performed in one of three ways. As shown in Fig. 1.9 the phase shifter can be placed either in the RF path, the LO path, or in the baseband (also called IF phase shifting).<sup>4</sup> Phase shifting in the RF path (Fig. 1.9a) [Natarajan07] requires wide band and low loss phase shifters. Wide bandwidth is required due to the wide signal bandwidth being transmitted, and low loss is required to maintain low noise figure in the RX or high efficiency in the TX. After initial amplification using an LNA, the

<sup>&</sup>lt;sup>4</sup>Fig. 1.9 shows an RX array but the same ideas apply for a TX array.

signals are combined at RF which means the combiner must also be low loss and wideband. However, only one mixer and LO are needed. Unfortunately, RF phase shifters and power combiners are bulky and have significant loss which is directly in the sensitive signal path in this architecture. Furthermore, it is difficult to achieve well controlled high phase resolution for RF phase shifters.

Phase shifting at baseband (Fig. 1.9b) requires an LNA and mixer in each element and an identical LO to be fed to each element for downconversion. Phase shifting is performed on the downconverted signal using IF phase shifters. Luckily, IF phase shifters are very compact and can have very wide bandwidth and resolution while maintaining low power consumption as shown in [Marcu09]. After phase shifting, the individual signals must be combined. Since this combination is done at baseband simple current summation can be used very effectively. The advantage of this topology is that it allows for very flexible and low power phase shifters and combiners as well as a very modular architecture. Digital signal processing can also be utilized to perform more complex signal manipulations to achieve the desired array behavior. This is not possible with the RF architecture since the signal arriving at the baseband has already been combined. The disadvantages are that each element is in effect a full transceiver and a high frequency signal, the LO, must be split and distributed to each. The bandwidth of the LO path is no longer determined by the signal bandwidth but by the LO tuning range requirements which could be larger. However, the LO path is largely insensitive to amplitude variations so linearity and loss are much less of a concern here as opposed to the signal path (as long as the LO maintains sufficient signal swing).

The final architecture is phase shifting in the LO path (Fig. 1.9c) [Hashemi05, Babakhani06, Natarajan06]. This architecture also requires each element to have an LNA and mixer. However, each mixer is fed an appropriately phase shifted LO signal. The mixing action causes the phase of the LO to get transferred to the downconverted signal. This can be shown by multiplying the RF signal, a carrier with arbitrary amplitude modulation  $V_m(t)$  and phase modulation  $\theta_m(t)$ , with the LO signal, a carrier with phase shift  $\phi$ , as shown in (1.11). Applying a low pass filter removes the upper side-band at frequency ( $\omega_{RF} + \omega_{LO}$ ), leaving only the desired modulation signal with phase shift  $\phi$ , as shown in (1.12).

$$V_{IF} = \left[V_m(t)\cos\left(\omega_{RF}t + \theta_m(t)\right)\right] \cdot \cos\left(\omega_{LO}t + \phi\right)$$

$$= \frac{1}{2}V_m(t)\left[\cos\left(\theta_m(t) + \phi\right) + \cos\left(\left(\omega_{RF} + \omega_{LO}\right)t + \theta_m(t) + \phi\right)\right] \qquad (1.11)$$

$$V_{IF}\Big|_{LPF} = \frac{1}{2}V_m(t)\cos\left(\theta_m(t) + \phi\right) \qquad (1.12)$$

In this architecture high frequency phase shifting is required as in the RF architecture and LO distribution is required as in the IF architecture. The only advantage is that signal combination can be performed simply at baseband as in the IF architecture. Unfortunately, this topology has the disadvantages of both previous architectures without providing significant new advantages.

The foregoing analysis is summarized in Table 1.1. While both RF and IF phase shifting architectures provide similar performance, very little attention has been paid to the latter.

|                       | Phase Shift in RF | Phase Shift in IF | Phase Shift in LO |

|-----------------------|-------------------|-------------------|-------------------|

| LO distribution       | No                | Yes               | Yes               |

| Phase Shift Frequency | High              | Low               | High              |

| Phase Shift Bandwidth | Wide              | Wide (Scalable)   | Narrow            |

| Combiner Frequency    | RF                | IF                | IF                |

| Signal Combining      | Early             | Late              | Late              |

Table 1.1: Phased array architecture comparison

With advances in CMOS technology allowing high speed and low power baseband phase shifters and signal processing, IF phase shifting is becoming more attractive.

### 1.4 Related Work

Significant progress has been made in the design of mm-wave circuitry in silicon leading to higher levels of integration in 60GHz transceivers. For example, Floyd et al. described an integrated mm-wave front-end implemented in a SiGe process in [Floyd06]. However, being in a SiGe process makes a fully integrated solution costly since baseband signal processing should be performed in a separate chip in a modern scaled CMOS process for low power consumption. Multiple CMOS 60GHz transceivers achieving Gb/s data rates have also been presented with varying levels of integration, including [Wang07], [Tanomura08], [Pinel08], [Tomkins09], and [Marcu09]. Unfortunately, most of these solutions (except [Marcu09]) are either not completely integrated, missing digital signal processing, and in some cases LO generation and distribution, or give little insight into the design challenges and trade-offs. As explained in the previous section, however, a phased array transceiver is needed for efficient communication at high data rates and the works listed above are single-element transceivers.

More recently there have been an increasing number of demonstrations of 60GHz phased array transceivers. [Reynolds10] and [Valdes-Garcia10b] presented a 16-element phased array RX and TX respectively in a  $0.12\mu m$  SiGe process. While these arrays show excellent performance, they are targeted for wall-powered applications and consume too much power for mobile devices. CMOS based phased arrays have also been shown by [Cohen10] and [Emami11] both utilizing the RF phase shifting architecture. [Emami11] is another array targeted at wall-powered applications and thus consuming too much power for mobile devices. [Cohen10], on the other hand, presents a very low power phased array but at the expense of reduced performance (gain, noise figure, output power).

The RF phase shifting architecture is popular due to its simplicity. Once the signal is phase shifted and combined at RF, the remaining radio (mixer and IF/baseband processing) is identical to the standard, single-element, transceiver shown in Fig. 1.5. However, the baseband phase shifting architecture provides multiple advantages and should be explored

further. Some work has begun to address the particular design challenges of baseband phased arrays [Borremans09, Raczkowski10] but no fully integrated solutions have been shown and, more importantly, there has been no effort to systematically study and optimize the LO distribution. If left unchecked, a sub-optimal design of this subsystem could cause it to be one of the largest power consumers even in a single-element transceiver, as we have shown previously in [Marcu09]. A systematic optimization approach is needed.

### 1.5 Thesis Outline

This thesis examines the LO generation and distribution challenge for fully integrated, high data rate, 60GHz phased array transceivers utilizing a baseband phase shifting architecture. Strategies for optimal low power design are presented with a focus on holistic optimization from architectural choices down to block level design. Since mm-wave design greatly depends on the quality and performance of passive components, the details of passive design are described first in Chapter 2. Next, the design of low power voltage controlled oscillators (VCO) is explored in Chapter 3. LO generation using a Phase-Locked Loop (PLL) is then described in Chapter 4. Finally, optimal LO distribution strategies for fully integrated phased array transceivers are discussed in detail in Chapter 5.

### 1.5.1 Design Methodology

Throughout this thesis, the focus will be on reducing power consumption and cost. Therefore, only standard digital CMOS processes are used with no costly analog process options such as Ultra Thick Metal (UTM) layers or Metal-Insulator-Metal (MIM) capacitors. Due to the skin effect, currents at mm-wave frequencies are confined to the conductor surface and so, the additional metal thickness of UTM does not reduce losses significantly. Passive components can be either lumped or distributed (see Chapter 2) and no preference is assumed. Either choice will be shown to be valid depending on the particular circumstances of each design. Nevertheless, all interconnect and passive components are simulated using a full-wave 3D EM simulator such as Ansoft's HFSS in order to carefully account for all parasitic loading and distributed effects. Finally, all transistors use standard design kit models with layout parasitic extraction for extrinsic parasitic resistances and capacitances.

## Chapter 2

## Passive Design

It is often said that the performance of mm-wave circuits comes down to the quality of the passives rather than the active circuits. At low-GHz frequencies, passive design generally involves ensuring matching within arrays of components and proper shielding. Passives at these frequencies are simply lumped components with parasitics. At mm-wave frequencies, on the other hand, passives are an integral part of the design process at every step due to distributed effects that arise at such high frequencies. Every trace, every route, every component, both active and passive, must be carefully placed taking into account the resuting parasitics and distributed effects in order to ensure accurate, high performance designs. In this chapter we will describe the design of passive components at 60GHz. We will begin by describing the characteristics of lumped and distributed resonant tanks. Next, we will discuss the implementation of individual passive components used to build these tanks as well as the trade-offs involved in their design. We will focus specifically on the implications of integrating these components on silicon for high frequency applications.

### 2.1 Lumped Resonant Tanks

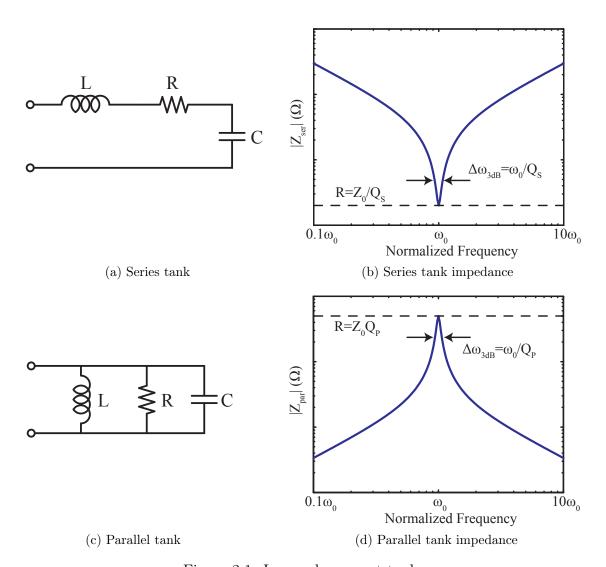

A resonant tank for an oscillator can be implemented either using lumped components such as inductors and capacitors, or in a distributed fashion, using transmission lines. In this section we will describe the design using lumped components. There are two types of tanks which are used with different oscillator topologies. The series RLC tank (Fig. 2.1a), has an impedance given by

$$Z_{ser} = j\omega L + \frac{1}{j\omega C} + R \tag{2.1}$$

where the resistor, R, represents the series losses present in the inductor and capacitor. We can now define three new terms critical in the following discussion: the resonance frequency,

$\omega_o$ , the series quality factor,  $Q_s$ , and the tank characteristic impedance,  $Z_o$ .

$$\omega_o \triangleq \frac{1}{\sqrt{LC}} \tag{2.2}$$

$$Q_s \triangleq \frac{\omega_o L}{R} \tag{2.3}$$

$$Z_o \triangleq \sqrt{\frac{L}{C}} \tag{2.4}$$

Note that  $Q_s$  can be written in mutliple, equivalent ways if we make use of  $\omega_o$  and  $Z_o$ .

$$Q_s = \frac{\omega_o L}{R} = \frac{1}{\omega_o CR} = \frac{\sqrt{L/C}}{R} = \frac{Z_o}{R}$$

(2.5)

Using the newly defined variables,  $\omega_o$  and  $Z_o$ , (2.1) can be rewritten as (2.6).

$$Z_{ser} = R \left[ 1 + jQ_s \left( \frac{\omega}{\omega_o} - \frac{\omega_o}{\omega} \right) \right]$$

(2.6)

Immediately we can see that at the resonance frequency, the imaginary part goes to zero and the impedance is equal to the resistance, R. The impedance is plotted versus frequency, normalized to the resonance frequency, in Fig. 2.1b showing the minimum occurs at resonance as expected. To completely generalize this equation, we can also use  $Z_o$ , the characteristic impedance of the tank. Using (2.2) and (2.4), we can show that  $Z_o = \omega_o L$ , so that (2.6), can be written as (2.7)

$$Z_{ser} = Z_o \left[ \frac{1}{Q_s} + j \left( \frac{\omega}{\omega_o} - \frac{\omega_o}{\omega} \right) \right]$$

(2.7)

Furthermore, some algebraic manipulation (reproduced in Appendix 2.A) can demonstrate that the bandwidth is inversely proportional to  $Q_s$ .

$$\Delta\omega_{3dB} = \frac{\omega_o}{Q_s} \tag{2.8}$$

The parallel *RLC* tank, on the other hand, (Fig. 2.1c), has an admittance equal to

$$Y_{par} = \frac{1}{i\omega L} + j\omega C + \frac{1}{R} \tag{2.9}$$

For the parallel tank, we define the parallel quality factor,  $Q_p$ , as

$$Q_p \triangleq \frac{\omega_o C}{G} \tag{2.10}$$

where  $G = R^{-1}$ . Similar to  $Q_s$ , we can also use (2.2) and (2.4) to rewrite  $Q_p$  in a number of equivalent ways.

$$Q_p = \frac{\omega_o C}{G} = \frac{R}{\omega_o L} = \frac{R}{\sqrt{L/C}} = \frac{R}{Z_o}$$

(2.11)

Figure 2.1: Lumped resonant tanks.

Using (2.2) and (2.10), (2.9) can be rewritten as (2.12).

$$Y_{par} = G \left[ 1 + jQ_p \left( \frac{\omega}{\omega_o} - \frac{\omega_o}{\omega} \right) \right]$$

(2.12)

Finally, the impedance is simply the inverse of (2.12)

$$Z_{par} = \frac{R}{1 + jQ_p \left(\frac{\omega}{\omega_o} - \frac{\omega_o}{\omega}\right)}$$

(2.13)

which can also be written in terms of the tank characteristic impedance given by (2.4).

$$Z_{par} = \frac{Z_o}{\frac{1}{Q_p} + j\left(\frac{\omega}{\omega_o} - \frac{\omega_o}{\omega}\right)}$$

(2.14)

Figure 2.2: Transmission line with arbitrary load.

Once again, at the resonance frequency, the imaginary part goes to zero and the impedance is just equal to the resistance, R. However, in this case, this is the maximum impedance over all frequencies (Fig. 2.1d). Nevertheless, the bandwidth is still inversely proportional to the quality factor.

$$\Delta\omega_{3dB} = \frac{\omega_o}{Q_p} \tag{2.15}$$

In modern scaled CMOS processes, quality factors for integrated LC tanks near 60GHz are generally less than 20, significantly lower for highly tunable tanks due to the higher losses of variable capacitors.

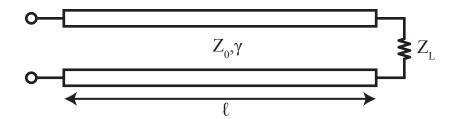

### 2.2 Distributed Resonant Tanks

The two types of resonant tanks we have discussed thus far are made up of lumped components, however, the same behavior can be emulated with distributed components, namely transmission lines. A transmission line (Fig. 2.2) can be fully described by two complex numbers: the characteristic impedance,  $Z_o$ , and the propagation constant,  $\gamma$ . In general,  $Z_o$  can be assumed to be real for all practical purposes even for moderately lossy transmission lines. The propagation constant, on the other hand, is generally complex and is defined as

$$\gamma = \alpha + j\beta \tag{2.16}$$

where  $\alpha$  is the loss of the transmission line, given in nepers per meter (1 neper  $\approx 8.686 \text{dB}$ ), and  $\beta$  is the propagation constant, given in radians per meter, which is a function of frequency and the phase velocity of the transmission line,  $\nu_p$ ,<sup>1</sup>

$$\beta = \frac{\omega}{\nu_p} \tag{2.17}$$

Furthermore, a signal of frequency  $\omega$  has a wavelength,  $\lambda$ , given by

$$\lambda = \frac{2\pi\nu_p}{\omega} \tag{2.18}$$

<sup>&</sup>lt;sup>1</sup>The phase velocity is the velocity of light in a given medium.

Figure 2.3: *RLGC* ladder representation of transmisison line.

This allows us to rewrite  $\beta$  directly as a function of the wavelength.

$$\beta = \frac{2\pi}{\lambda} \tag{2.19}$$

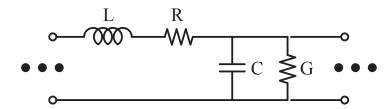

Any transmission line can also be represented by a distributed RLGC ladder network shown in Fig. 2.3 which is made up of the series inductance and resistance, and shunt capacitance and conductance, per unit length. The well known Telegrapher's Equations [Pozar04, Collin00] can then be used to describe the voltage and current at any point x along the line.

$$\frac{dV(x)}{dx} = -(R(x) + j\omega L(x)) \cdot I(x)$$

(2.20)

$$\frac{dI(x)}{dx} = -(G(x) + j\omega C(x)) \cdot V(x)$$

(2.21)

The distributed parameters are related to  $Z_o$  and  $\gamma$  by (2.22) and (2.23) respectively.

$$Z_o = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \tag{2.22}$$

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)} \tag{2.23}$$

For a lossless line (R = 0, G = 0) the above relations reduce to

$$Z_o = \sqrt{\frac{L}{C}} \tag{2.24}$$

$$\gamma = j\omega\sqrt{LC} \tag{2.25}$$

Using (2.17) and (2.25) we can then see that the phase velocity is given by

$$\nu_p = \frac{1}{\sqrt{LC}} \tag{2.26}$$

The input impedance of a loaded transmission line, like the one shown in Fig. 2.2, depends both on the load,  $Z_L$ , as well as its length,  $\ell$ , [Niknejad07, pg. 300].

$$Z_{in} = Z_o \frac{Z_L + Z_o \tanh \gamma \ell}{Z_o + Z_L \tanh \gamma \ell}$$

(2.27)

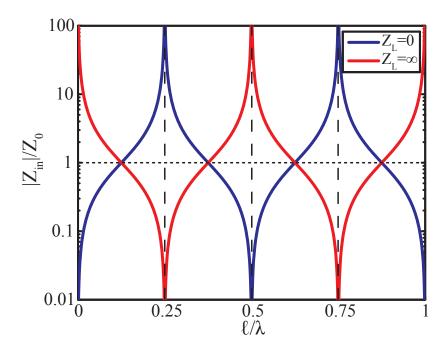

Figure 2.4: Ideal transmission line input impedance.

At the extremes, we can either make the load a short circuit  $(Z_L = 0)$  or an open circuit  $(Z_L = \infty)$ . For a lossless transmission line  $\gamma$  becomes completely imaginary. So, using (2.19), the input impedance is then given by (2.28) and (2.29) for the two cases respectively (both shown in Fig. 2.4).<sup>2</sup>

$$Z_{sc,i}(\ell) = jZ_o \tan\left(2\pi\frac{\ell}{\lambda}\right)$$

(2.28)

$$Z_{oc,i}(\ell) = \frac{-jZ_o}{\tan\left(2\pi\frac{\ell}{\lambda}\right)}$$

(2.29)

From Fig. 2.4 we can see that the absolute value of the input impedance of a short circuited lossless transmission line goes to infinity if the length is equal to  $\lambda/4$  (or any odd multiple of  $\lambda/4$ ) and goes to zero for all even multiples of  $\lambda/4$ . The absolute value of the input impedance of an open circuited lossless transmission line, on the other hand, goes to infinity for lengths equal to even multiples of  $\lambda/4$ , and zero for lengths equal to odd multiples of  $\lambda/4$ . In order to keep the area and loss low, we will limit our study to only the smallest possible designs. Conceptually we can see that a shorted line of length  $\lambda/4$ , or an open line of length  $\lambda/2$  looks like an ideal parallel LC tank. Similarly, an open line of length  $\lambda/4$ , or a shorted line of length  $\lambda/2$  looks like an ideal series LC tank.

Unfortunately, the real world is not ideal and transmission lines do exhibit loss. Just like real LC tanks, transmission line tanks cannot provide zero or infinite input impedance. For

$<sup>^{2}</sup>$ The subscript i has been used to represent the ieal, lossless case.

a realistic, lossy transmission line tank we can define a resonant quality factor,  $Q_r$ .

$$Q_r \triangleq \frac{\beta}{2\alpha} \tag{2.30}$$

This definition leads to the same relationship between center frequency and bandwidth as the quality factor of an LC tank given in (2.15). The derivation can be found in Appendix 2.B. To enable comparisons to lumped tanks we will now derive equations for the input impedance of a lossy transmission line resonant tank as a function of frequency,  $\omega$ , and the resonant quality factor,  $Q_r$ . We begin with the general equation for the input impedance of a lossy transmission line given by (2.27) and look at the two special loading cases, open and short.

$$Z_{sc}(\ell) = Z_o \tanh(\gamma \ell)$$

(2.31)

$$Z_{oc}(\ell) = \frac{Z_o}{\tanh(\gamma \ell)}$$

(2.32)

Let us assume that we are designing for a particular resonance frequency,  $\omega_o$ , which has an associated wavelength,  $\lambda_o$ , given by 2.33.

$$\lambda_o = \frac{2\pi\nu_p}{\omega_o} \tag{2.33}$$

Next, the resonant quality factor,  $Q_{r,o}$ , for our transmission line at the design frequency,  $\omega_o$ , is given by

$$Q_{r,o} = \frac{\beta_o}{2\alpha}$$

$$= \frac{\omega_o}{2\alpha\nu_p}$$

(2.34)

Finally, we normalize our transmission length,  $\ell$ , to the design wavelength,  $\lambda_o$ , calling the result,  $\ell_n$ , which leads to

$$\ell = \lambda_o \ell_n

= \frac{2\pi \nu_p \ell_n}{\omega_o}$$

(2.35)

We can now use (2.17) and (2.34) to rewrite  $\gamma$  as

$$\gamma = \alpha + j\beta

= \frac{\omega_o}{2Q_{r,o}\nu_p} + j\frac{\omega}{\nu_p}$$

(2.36)

assuming that the loss is constant across frequency. This is not strictly correct as will be described later but for our current purposes it is a reasonable and useful simplification. The

Figure 2.5: Lossy transmission line input impedance (plotted for Q=10).

$tanh(\gamma \ell)$  term in (2.31) and (2.32) can now be rewritten using (2.35) and (2.36).

$$tanh (\gamma \ell) = \tanh \left[ \left( \frac{\omega_o}{2Q_{r,o}\nu_p} + j\frac{\omega}{\nu_p} \right) \frac{2\pi\nu_p \ell_n}{\omega_o} \right]$$

$$= \tanh \left[ 2\pi \ell_n \left( \frac{1}{2Q_{r,o}} + j\frac{\omega}{\omega_o} \right) \right]$$

(2.37)

Putting this term back into (2.31) and (2.32) yields our final simplified expressions (plotted in Fig. 2.5).

$$Z_{sc}(\omega) = Z_o \tanh \left[ 2\pi \ell_n \left( \frac{1}{2Q_{r,o}} + j\frac{\omega}{\omega_o} \right) \right]$$

(2.38)

$$Z_{oc}(\omega) = \frac{Z_o}{\tanh\left[2\pi\ell_n\left(\frac{1}{2Q_{r,o}} + j\frac{\omega}{\omega_o}\right)\right]}$$

(2.39)

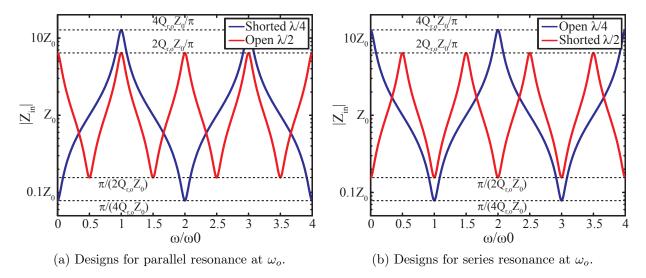

There is, however, one important distinction between transmission line resonant tanks and their lumped equivalents. As we can see from (2.38) and (2.39), the tanh term gives rise to a periodicity in the frequency response. Thus, a transmission line tank of a given length will exhibit multiple resonances at frequencies for which the line length is a multiple of  $\lambda/4$ . In practice this means that a given tank will resonate not just at the designed frequency but also at its harmonics (Fig. 2.5). However, this is generally not a concern for mm-wave designs since active devices exhibit very low gain at the higher harmonics. Furthermore, the loss mechanisms present in transmission lines designed on silicon tend to increase with frequency. Metal loss increases with the square root of frequency due to the skin effect, while dielectric loss, due to the loss tangent, increases proportional to frequency. In practice,

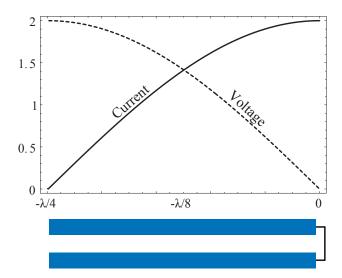

Figure 2.6: Current and voltage standing waves for a quarter-wavelength transmission line.

startup conditions will usually only be met at the fundamental frequency but not at its harmonics so no parasitic oscillations will occur. Nevertheless, this effect should be known to the designer and care must be taken to ensure that oscillation can only occur at the desired frequency by design rather than chance.

## 2.3 Tapered Transmission Line Resonators

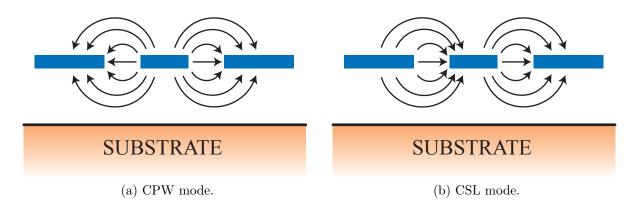

Transmission line resonators exhibit another interesting property, the standing wave. This effect can be explicated to reduce loss through tapering of the transmission line. We will use the shorted  $\lambda/4$  resonator as our example but the analysis can also be applied to other lengths and load conditions. Since many applications require a differential oscillator design, let us use a coplanar stripline (described below in Section 2.5.4).

When a shorted length of transmission line is driven by a sinusoidal signal, the signal travels down the transmission line to the load. Upon reaching the load it is completely reflected back towards the source due to the impedance mismatch caused by the short. The reflected wave then travels back toward the source and the total signal along the line is the superposition of the incident and reflected waves. This superposition forms a standing wave with wavelength equal to  $\lambda$  [Gonzalez97]. If we were to measure the voltage at any point along the transmission line we would observe a sine wave of constant amplitude. At different points along the line, the amplitude would vary but its phase would not.

A  $\lambda/4$  line then holds exactly one quarter of the standing wave. To find the resulting current wave we can decouple the Telegrapher's equations (2.20) and (2.21) which gives us a second-order system of differential equations. Assuming low loss conditions (R = G = 0) the result is the differential equation representation of an arbitrary transmission line in the voltage

Figure 2.7: A tapered quarter wave transmission line utilizes wide width and large gap spacing when the current is high (voltage is low) and narrow width and small gap when the voltage is high (current is low).

domain [Womack62, Youla64]

$$\frac{d^{2}V\left(x\right)}{dx^{2}} - \frac{1}{L\left(x\right)} \cdot \frac{dL\left(x\right)}{dx} \cdot \frac{dV\left(x\right)}{dx} - \omega^{2}L\left(x\right)C\left(x\right)V\left(x\right) = 0 \tag{2.40}$$

$$I(x) = -\frac{1}{j\omega L(x)} \cdot \frac{dV(x)}{dx}$$

(2.41)

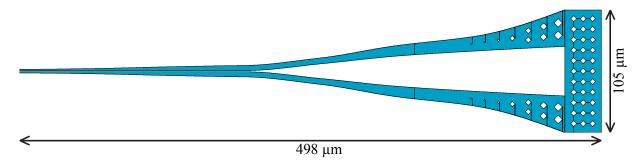

As we can see from (2.41), the current is 90° out of phase with the voltage. The standing waves along our  $\lambda/4$  resonator are shown in Fig. 2.6 for a coplanar stripline (CPS).<sup>3</sup> At the shorted end of the line, the voltage is at a minimum and the current at a maximum, so the losses at this point come mainly from the series resistance of the metal lines. Conversely, at the driven end, the voltage is at a maximum and the current at a minimum, so the losses at this point come mainly from the shunt conductance between the differential lines. This phenomenon can be exploited to lower the losses of the resonator and thus raise the quality factor. At the shorted end of the line we would like to increase the conductor width to reduce the series resistance. Since the voltage is low at this point, the shunt conductance is not very important. Conversely, at the driven end of the line, where the voltage is at a maximum we would like to reduce the width and spacing of the conductors to reduce the shunt conductance due to substrate coupling. Since the current is low at this point the resulting large series resistance of the line is not important. Along the rest of the line, shunt conductance and series resistance can be traded-off to reduce overall loss. Conceptually, the resulting taper should have a shape similar to Fig. 2.7.

The preceding discusison has completely ignored the effects of such a taper on the characteristic impedance of the line at each point and thus the question must be asked: does the characteristic impedance have to be constant along the taper? The simple answer is no. The idea of tapering a transmission line has been studied and used extensively in the microwave community for many years as a way to provide a conjugate match between two sections of transmission line with different characteristic impedances. As early as the 1930s many authors had worked out solutions for the behavior of a tapered transmission line with

<sup>&</sup>lt;sup>3</sup>The CPS transmission line is described in Section 2.5.4.

Figure 2.8: The layout of the optimized quarter wave line. The characteristic impedance,  $Z_o$ , is non-constant. Slotting is introduced to satisfy design rules.

characteristic impedance profiles that varied in a specified manner (e.g.: linear, exponential, Gaussian, etc.). However, it is not immediately obvious how these results can be applied to tapering resonators.

For simplicity let us begin by assuming constant characteristic impedance is maintained accross the entire taper. Luckily, a CPS line's dimensions can be adjusted to achieve infinitely many combinations of series loss versus shunt loss while maintaining a constant characteristic impedance. In fact, [Andress05] showed that if the characteristic impedance is kept constant along the taper, the transmission line can be thought of as a piecewise construction of infinitesimaly small uniform transmission line segments with the same characteristic impedance,  $Z_o$ , but different complex propagation constant,  $\beta$ . Using this construction, the voltage and current profiles along the line can be calculated in the phase domain which is related to the physical domain defined by the position, z, along the line by

$$\theta(z) = \int_0^z \beta(z') dz' \tag{2.42}$$

In the phase domain, the voltage and current profiles of a tapered resonator with constant characteristic impedance are always sinusoidal in shape just as shown in Fig. 2.6 for a uniform resonator in the physical domain. This closed form solution then allows a straightforward optimization of the series and shunt losses directly in the phase domain. The result is a quality factor improvement of ideally 60% over the best untapered resonator.

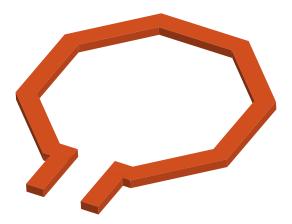

On the other hand, if the characteristic impedance is allowed to vary, the current and voltage profiles will no longer be sinusoidal even in the phase domain. Their solution can still be found analytically if the characteristic impedance profile is well behaved (e.g.: linear [Lu97], exponential [Womack62]) but for arbitrary lines, only numerical solutions are possible. An optimization method was developed in [Marcu08b] which optimized the transmission line taper for a 60GHz resonator, without constraints on the characteristic impedance profile, based on a numerical solver for the voltage and current profiles.<sup>4</sup> The resulting taper (Fig. 2.8) achieved a quality factor of 15, a 70% improvement over the untapered resonator at 60GHz,

<sup>&</sup>lt;sup>4</sup>Details of the optimization methodology can be found in [Marcu08a].

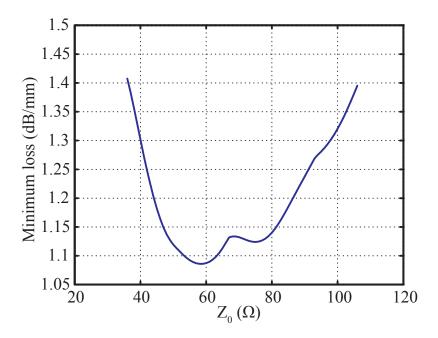

Figure 2.9: The optimum characteristic impedance profile.

and a 10% increase over the maximum achievable for a constant characteristic impedance taper. The resulting optimum characteristic impedance profile is shown in Fig. 2.9. Examining the layout and characteristic impedance profile we can immediately recognize that the optimization maximized the capacitance per unit length (low  $Z_o$ ) at one end, and maximized the inductance per unit length (high  $Z_o$ ) at the other. In effect, the optimization built the closest thing it could to an LC tank. In fact, at 60GHz the optimum tapered transmission line resonator achieves performance on par with an optimized lumped LC tank [Marcu08a]. Unfortunately, the LC tank also occupies less die area and is thus the better choice for most designs at 60GHz.

## 2.4 MEMS Resonators