# **UC Berkeley**

# **Consortium on Deburring and Edge Finishing**

## **Title**

Formulation of the Chip Cleanability Mechanics from Fluid Transport

## **Permalink**

https://escholarship.org/uc/item/75v1m1bj

## **Authors**

Garg, Saurabh Dornfeld, David Klaus Berger

## **Publication Date**

2009-04-02

Peer reviewed

# Formulation of the Chip Cleanability Mechanics from fluid transport

S. Garg<sup>1, ,</sup> D. Dornfeld<sup>1</sup>, K. Berger<sup>2</sup>

<sup>1</sup>University of California Berkeley, Mechanical Engineering Department, CA-94720

<sup>2</sup>Daimler AG, Material Technology Department, 70546 Stuttgart, Germany Email: sgarg@berkeley.edu

#### Abstract

The presence of solid particle contaminant chips in high performance and complex automotive components like cylinder heads of internal combustion engines is a source of major concern for the automotive industry. Current industrial cleaning technologies, simply relying on the fluid transport energy of high pressure or intermittent high impulse jets discharged at the water jacket inlets of the cylinder head, fail to capture the dynamics of interaction between the chip morphology and the complex workpiece landscape. This work provides a preliminary insight into an experimental investigation of the mechanics of chip transport at play, and how it can be used to build an effective chip optimization model that significantly aids in improving the cleanability of contaminant chips. The objective is to relate the mechanics of chip transport with the chip form parameters as much as possible, which makes the objective and constraints in the optimization model quantifiable. The end objective is of course to transmit this information upstream of the manufacturing pipeline in the form of a Design for Cleanability (DFC) feedback, which highlights the industrial cleaning problem as a design centric issue.

### Keywords

Design for Cleanability; Workpiece bottleneck; Chip critical dimension; Fluid Lift force; Fluid Drag force; Chip Orientation.

#### Introduction

Chip formation is a very significant aspect of any basic machining process. Unfortunately chip production has conventionally been considered to be only of secondary importance for a production process. The most important emphasis has been given to the finished workpiece and its attributes like surface roughness, ease of machining, dimensional accuracy etc., and in mass production, to achieving the desired production rate and quality control at lowest costs to the facility or the company.

The type of chip produced is a good indicator of the machining conditions, the properties of workpiece, tooling material and the quality of machined surface while chip load is an effective measure of cutting forces. But in mass manufacturing, where most of these essential elements of production process are known or fixed at the design stage itself in order to achieve specified values of final properties like hardness, toughness, surface quality etc., and due to cost constraints governing optimum tool life; chip formation is often ignored as a potential area for directing concern.

The firsts of the manufacturing concerns related to chip formation dealt with the obstacle provided by the chip generation to the motion of the tool. A simple example is the flute of a drill bit whose function is to allow chips from the workpiece to easily climb up and create way for further drilling. In similar ways, much work has been done in the industrial research to break the chips and remove them from the machining area to facilitate further machining.

The challenges due to the chip formation take a major role because of their capacity to act as solid particle contaminants for high performance mechanical components like engine cylinder heads. Contamination of mechanical parts due to process impurities and machining chips that get embedded onto their surface is an important industrial concern as far as the functionality of these parts is concerned because it can lead to their sudden and catastrophic failure during the use phase. Thus, cleaning of mechanical components assumes great significance from an industrial standpoint.

Contaminant chips can either be the chips from the common machining operations that enter the narrow intricate channels of workpiece geometry, or they may be loose burrs which remain in the workpiece after detachment from the surface. Important work on burr formation and minimization (size, location, shape, etc.) has been done by Dornfeld [1] and co-workers. Although the problem of cleanability of mechanical components has greater complexities compared to deburring such as lack of easy accessibility requiring fluid jets with sufficient pressures and velocities in most internal parts of the workpiece; a complex nature of types of contaminants such as loose chips, sand mold particles, surface grease, dirt etc., it is important to combine the knowledge of both to build a rigorous chip optimization model.

The chip morphology plays an important role in influencing the cleanability of chips. The most commonly used industry standard for chip classification based on morphology is the ISO-Classification 3685 [2], as is used in this work. Literature review shows that some amount of research has been done involving the chip size and geometry as applied to machining technology. Reich-Weiser and Dornfeld [3] presented an experimental investigation of the influence of machining parameters on chip geometry for enhanced cleanability. In their work, process parameters such as feed-rate, spindle speed, depth of cut, and tool lubrication have been correlated with chip geometry and size for milling and drilling processes. Viharos et al. [4] provided an ANN based chip-form classification model for the turning process. Their work involved building predictive models for cutting chip form based on process parameters, direct measured values of cutting forces and torques, and calculated factors of typical monitoring signals. Sturenberg [5] worked on optical classification of chips generated during the cutting or the machining phase as well as the assembly phase based on chip geometry, and then modifying the tool design for easy removal of such chips from the machined workpiece based on the types of chips specific to that process for which the tool is used. Avila [6] performed a black box experimental approach of testing the cleanability of different chip geometries using the Impulse cleaning Machine. He found that chip form selectively affects the cleanability of different chip types.

The current work focuses on tracing the root of cleanability at the lowest level: which involves local interactions between workpiece and chip geometry and chip-cleaning fluid. Brute force methods for cleaning currently used in industry for increasing water pressures in hope of increasing cleaning force may not be effective and rather may prove more costly in terms of expensive and complicated equipments required for higher pumping power. It is felt that although it is difficult to exactly formulate a theory for such kind of chip-workpiece-fluid interactions, understanding and establishing some kind of a framework through experimental investigation to assess and analyze the impact of the chip size and geometry vis-à-vis the critical bottleneck dimensions of the workpiece (narrowest channels of engine cylinder head in the current case) can give us the key to understanding the fundamentals of cleanability problem. It would then be meaningful to attack the problem at the grass-root level by focusing on all the stages of manufacturing pipeline starting from the design stage keeping in mind the requirements for generation of only those chip forms that are amenable to cleaning by our existing methods and also keeping a bound on chip sizes during the machining stages so as not to generate chips that are comparable in size to the bottleneck internal dimensions of the workpiece. Thus, integration of cleanliness as an engineering constraint into the early stages of the product development process is critical to the manufacture of mechanical components that meet cleanliness requirements at the lowest possible costs.

#### **Experimental Setup**

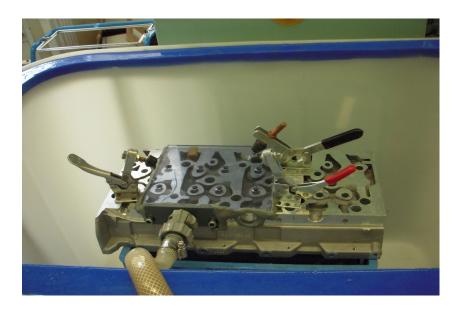

The experiments were performed at the production department lab, Daimler AG, Stuttgart. The diesel engine cylinder head OM 646 was used for the purpose. A cross section of the cylinder head passing through the water jacket was first made in Catia CAD software, to ensure two basic criteria are met: firstly, the volumetric flow rate of water passing through the water jacket does not fall below 75-80% of the original amount, so that actual cleaning conditions are maintained as much as possible. Secondly, the section should be made at an appropriate height in the water jacket so that the emerging landscape has characteristic bottlenecks representative of the actual cylinder head. A plexiglass sheet was used to cover the cross section of the head, and was clamped in position with four clamps. Chips of different geometries such as helical, spiral, ribbon etc. and varying sizes were pre-collected, washed of the lubricant using an ultrasonic vibrator and then separated for use in the experiment. Figure 1 shows the experimental setup used.

Fig. 1 Experimental setup for investigating chip transport through a cut OM 646

## Formulation of Cleanability Mechanics: Observations and Inferences

As was described above, the purpose of the experiments was to observe and formulate the chip cleanability mechanics and relate it with the chip form parameters as much as possible in order to build an effective chip optimization model that significantly aids in improving the cleanability of contaminant chips. The following observations highlight the mechanics of the chip cleanability at play.

#### 1. Chip Critical and Workpiece Bottleneck dimensions:

It was observed that as is intuitively expected, the chip critical dimension should be smaller than the workpiece bottleneck dimension, in order for the chips to overcome the bottleneck. A workpiece bottleneck may be a narrow constriction in the width of a channel, or it may be a height obstacle in the cross-sectional landscape which requires the chip to elevate itself above a threshold barrier. However, there are no existing methods or approaches that clearly delineate how to evaluate the chip critical and workpiece bottleneck dimensions.

Methods to determine the bottleneck dimensions of the cylinder head:

- 1) Using a sequence of cut cross sectional layers: The CAD model of the cylinder head is sectioned into a series of layers across its width and a particular feature in the internal landscape is analyzed for its dimension across those layers until a minima is reached somewhere. That establishes the bottleneck dimension for that feature of interest.

- 2) Using the negative of the cylinder head, i.e. the sand mold: The Al-Si cylinder heads mostly used in automotive industry are manufactured from the sand-casting process. The sand-mold acts as the negative of the cylinder head and thus the dimensions of the mold represent the internal dimensions of the channels and holes of the cylinder head geometry.

Methods to estimate the chip critical dimension:

The specific geometry type of the chips can be exploited to estimate the chip critical dimension.

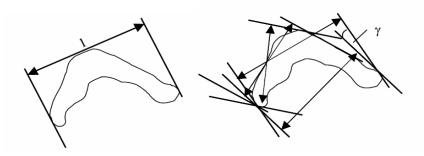

For ribbon chips, one can estimate the size based on a direct adaptation of the ISO recommendation [7] for estimating particle size, i.e. the size of the particle is determined by its longest dimension, which is the longest distance between any two parallel lines drawn touching the surface of the particle.

Fig. 2 Critical dimension for the ribbon chip = I

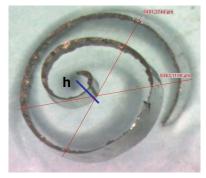

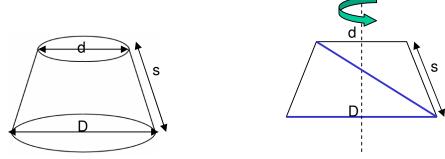

For the spiral chips, the authors propose that these chips can be modeled on the lines of a regular cylinder, which bounds the smallest volume of space completely enclosing the chip. This is the minimum volume of a known regular geometry that can very accurately model a spiral chip.

Fig. 3 Basic geometrical measurements in a (a) flat spiral, (b) raised spiral

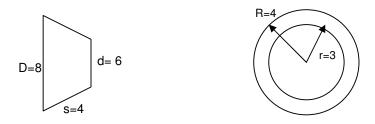

For the figure 3(a) which represents a flat spiral, the easily measurable parameters that are sufficient to determine the critical dimension are the maximum spiral diameter ('D') and the chip

width 'h'. For the figure 3(b) which represents a raised spiral, the height of the spiral will be different from the chip width and thus needs to be recorded separately.

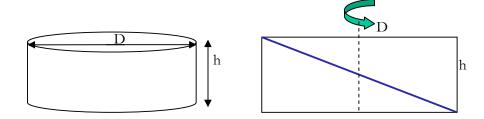

Fig. 4 (a) Modeling of relevant chip forms on the lines of a regular cylinder with appropriate parameters, (b) Rotation of a rectangle generates a cylindrical surface of revolution

Figure 4(a) shows a cylindrical geometry with the parameters adapted from the spiral chip. The cylinder can also be envisioned as a surface of revolution of a rectangle around the axis of rotation shown. The critical dimension of the chip is then given by the largest diagonal of the rectangle, as shown in equation 1.

Spiral chip critical dimension =

$$\sqrt{D^2 + h^2}$$

(1)

The critical dimension of other common geometries that can be modeled as an approximate cylinder include helical washer, tubular helical, raised conical spiral and conical helical.

Similarly, a conical spiral geometry can also be modeled along the lines of a frustum of a cone, as shown in figure 5., where the measurable parameters are the maximum diameter (of the base of the cone) 'D', the minimum diameter (of the top part of the frustum) 'd', and the slant height or the chip width 's'. The chip critical dimension is then expressed by equation 2.

Fig. 5 (a) Conical spiral chip geometry (b) Modeling the geometry as a frustum of a cone (c) An isosceles trapezium on rotation generates the solid body of revolution shown in (b)

Conical Chip critical dimension = larger of 'D' or

$$\sqrt{(s^2 + Dd)}$$

(2)

The mass of the spiral chips (flat and conical) can also be calculated from a knowledge of the geometrical parameters of the chips. When these chips are compressed slightly to align the spirals with one another, they can be modeled on the lines of a hollow cylinder and a cone (frustum) respectively, with known mensurational expressions for determination of volume, which along with a knowledge of the density of chip material can give a good geometrical estimation of the mass of these chips.

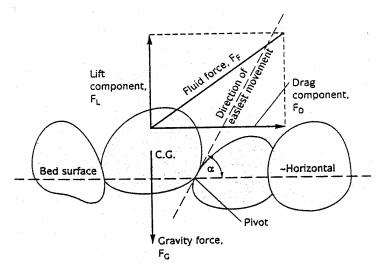

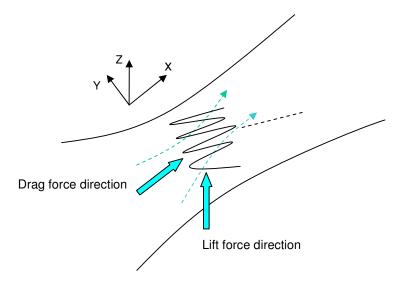

### 2. Importance of Chip Projected Surface Areas: Role of Fluid drag and lift forces

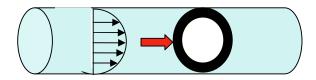

The entrainment of a particle into a turbulently flowing fluid is important in a wide range of natural phenomenon. Entrainment refers to the motion of a particle in the bulk of the fluid rather than rolling along the surface of a bed of particles. Consequently, a particle in motion in a fluid stream must be acted upon by a drag force that acts in the direction of the fluid motion and helps to transport the particle in the direction of the fluid motion; and a fluid lift force that helps in lifting the particle against the net weight force which has a tendency to keep the particle to the surface of the fluid bed. Figure 6 shows these forces acting on a particle on a surface bed that can cause its entrainment into the fluid stream. Figure 7 is a corresponding schematic as applied to the transport of a chip in the cleaning fluid medium.

Fig. 6 Forces acting on a particle that experiences entrainment into a fluid stream

Fig. 7 A schematic diagram of the fluid forces on an entrained chip in a flowing stream

The drag force can be expressed as the sum of all pressure forces in the direction of the fluid flow as shown in equation 3.

$$D = \oint p(\vec{n}.\vec{i})dA \tag{3}$$

Here 'D' is the drag force acting on the chip in the direction of fluid flow, 'p' is the fluid pressure, n = n is the normal to the surface area of the chip, and n = n is the direction of fluid flow.

The above equation can also be expressed in the following way (Eqs. 4, 5) by taking the projection of the chip surface area in the direction of the fluid flow.

$$D = \oint p((dA\vec{n}).\vec{i}) \tag{4}$$

$$D = \oint p \left( dA_{proi} \right)_i \tag{5}$$

Similarly, the lift force can also be seen to be proportional to the chip projected surface area in the *z* direction as shown in equation 6.

$$L = \oint p(dA_{proj})_z \tag{6}$$

The effect of projected surface areas on the cleanability of a chip can be seen in the figure 8 below. For the same flow conditions, the cleaning fluid was able to transport the chip out of the workpiece bottleneck for the chip orientation as shown in figure 8(a) while it could not in the case of figure 8(b).

Fig. 8 Chip orientation with (a) higher projected surface area (b) smaller projected area in the direction of fluid flow (into the plane of paper)

Upon measurement of the basic chip dimensions, the maximum diameter 'D' (base) was found to be roughly 8 mm, minimum diameter 'd' (bottom) as 6 mm and the maximum chip width 's' as 4 mm. The workpiece bottleneck dimension was found greater then 9 mm.

Conical Chip critical dimension = larger of 'D' or  $\sqrt{(s^2 + Dd)}$  = 8 mm

In that respect, there is no size constraint for the passage of chip through the bottleneck. With all conditions remaining the same and assuming pressure variation across the section of the chip as constant, a good estimate of the ratio of drag forces experienced by the two chip orientations can be obtained by considering the ratio of their projected surface areas as shown in figure 9.

Fig. 9 Projected surface area estimation for two different orientations of a conical spiral chip

Projected surface area in figure =

$$\frac{1}{2}(D+d)\sqrt{(s^2-(\frac{D-d}{2})^2)^2}$$

= 27.11 square mm

Projected surface area in figure =  $\pi(R^2 - r^2)$  = 21.99 square mm

This tells us that the increase in projected surface area in the first case is around 23%, which is one of the reasons why the drag force is higher. The other important reason is shown in figure 10. Because the cleaning fluid (water) under the experimental flow conditions used here, has an expected parabolic laminar profile which has the maximum fluid momentum at the center of the profile, the second chip orientation with a hollow concentric ring shaped projected area loses a potentially large amount of fluid drag force.

Fig. 10 A Laminar fluid flow profile through the chip orientation shown in fig. 8(b) and 9(b)

#### 3. Chip Orientation Effects

The orientation of chips is also critical for their effective transport and cleanability. The projected surface area of the chips changes with a change in their orientation, as noted before. In that respect, chips that have higher projected surface areas for more stable orientations will have a better chance of getting cleaned effectively. Experiments were performed to note the effect of different orientations on the overall transport of different chip geometries through a bottleneck workpiece dimension. It must be noted however that we cannot control or predict the orientation that a chip will take while passing through a bottleneck dimension. Thus geometries that inherently have a higher projected surface area for their more stable orientations will have a higher probability of getting transported.

#### 4. Effect of Back pressure on the chip transport

The effect of back pressure was observed as an interesting effect in the experiments that has a potential for application as an important phenomenon in the redesign of next generation cleaning machines. If a closed system cleaning for a workpiece like a cylinder head is followed, intermittent cleaning by disrupting the flow of normal tap water stream through the water jacket inlet can suddenly cause a pressure drop to exist inside the workpiece across a trapped chip. Consequently there is a back pressure on a trapped chip equivalent to the difference in atmospheric pressure and the vacuum pressure inside the cylinder head. This pressure difference can be large enough to drive air into the workpiece from outside the water jacket outlet. This effect can be used to re-channelize chips that have been trapped in a critical cross-section by forward water flow transport, out of it into other channels; or to allow a different orientation for more favorable chip cleanability in the same channel.

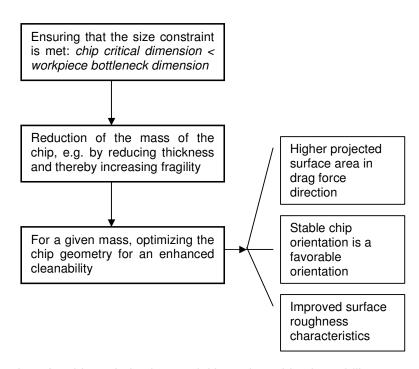

#### **Chip Optimization Model**

The resulting model for chip optimization for enhanced cleanability is an outcome of incorporating and assembling the various pieces of chip cleanability mechanics. It involves addressing the three main aspects of chip attributes: mass, geometry and size.

The size constraint at all times should be to keep the chip critical dimension less than the workpiece bottleneck dimension.

Within this larger umbrella, a reduction in the mass of the chip (or thickness, for the same cross sectional area) will aid in a better chip transport. This is because firstly the impulse fracture ability (as noted through some prior research experiments at Daimler [5]) shows an improvement with lighter and more fragile chips. Secondly, lighter chips experience lesser net weight force and hence a consequent higher lift force, which again aids in their transport in the fluid stream.

For a given mass, the next endeavor should be to optimize the chip geometry. This involves preferring those chip geometries that have a higher projected surface area in the direction of the drag force or the cleaning force; geometries that have higher projected areas inherent in their more stable orientations; and controlling the surface roughness of the chips produced in the manufacturing operations for a lowered or reduced adhesion with the workpiece surface.

The model is summed up in a diagrammatic flowchart representation as shown in figure 11.

Fig. 11 A flowchart representation of a chip optimization model based on chip cleanability mechanics

#### **Conclusions**

This paper discusses the importance of following a bottom-up approach in trying to address the problem of cleanability of contaminant chips in the automotive industry. Understanding

and formulating the mechanics of chip transport in a fluid medium for a given workpiece landscape is essential for building a cleanability driven overall chip optimization model as well as to use the science behind the mechanics to develop the technology for a new generation of cleaning machines that are more effective and economical. The requirements for the optimal chips from a cleanability perspective, is thus an information that in turn should travel up the manufacturing pipeline to induce design related changes (Design for Cleanability 'DFC' feedback) at both process and systems level, which highlights the industrial cleaning problem as a design centric issue. This approach should also be closely tied with a Design for Environment (DFE) feedback with an aim to minimize the environmental impact of the cleaning processes and raw materials and reducing the energy use consumption.

#### **Acknowledgments**

This work is supported by National Science Foundation (NSF) Research Grant DMI-20062085 and Pan-Pacific MIRAI (Manufacturing Institute for Research on Advanced Initiatives). The authors would also like to thank Daimler AG for providing access to laboratory facilities and Mr. Dezsoe Schilling for his insights and contributions to this work. To learn more about the research activities of the LMAS please visit <a href="http://lmas.berkeley.edu">http://lmas.berkeley.edu</a>. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the National Science Foundation.

#### References

- [1] Ávila M., Gardner J., Reich-Weiser C., Vijayaraghavan A., Tripathi S., Dornfeld D., (2005), "Burr Minimization Strategies and Cleanability in the Aerospace and Automotive Industry", SAE Transactions, Paper 2005-01-3327

- [2] "Tool-life testing with single-point turning tools", ISO 3685-1977(E)

- [3] Reich-Weiser C., and Dornfeld D., (2006), "Experimental Investigation of the Influence of Machining Parameters on Chip Geometry for Enhanced Cleanability", Laboratory for Manufacturing and Sustainability, Consortium on Deburring and Edge Finishing

- [4] Viharos Zs. J., Markos S., Szekeres Cs., (2003), "ANN-based chip-form classification in turning", XVII IMEKO World Congress Metrology in the 3<sup>rd</sup> millennium, Dubrovnik, Croatia, pp. 1469-1473

- [5] Sturenberg B., (2008), "Systematic investigation of the chips caused by residual dirt behavior", Doctoral Thesis, Daimler AG, Stuttgart, Germany

- [6] Ávila M., Dornfeld D., Berger K., (2006), "Analysis of residual chip geometries during Impulse machine cleaning tests", Summer Research, DaimlerChrysler, Stuttgart, Germany

- [7] "Particle sizing and counting by microscopic analysis", ISO 16232-7 (2007)