## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Efficient thermal management for multiprocessor systems

#### **Permalink**

https://escholarship.org/uc/item/70z2d3nv

#### **Author**

Coşkun, Ayşe Kıvılcım

### **Publication Date**

2009

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Efficient Thermal Management for Multiprocessor Systems

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science and Engineering

by

Ayşe Kıvılcım Coşkun

### Committee in charge:

Tajana Šimunić Rosing, Chair Kenny C. Gross Rajesh Gupta Tara Javidi Andrew B. Kahng Dean Tullsen

Copyright

Ayşe Kıvılcım Coşkun, 2009

All rights reserved.

| Chair                                                    |

|----------------------------------------------------------|

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| on microfilm and electronically:                         |

|                                                          |

| and it is acceptable in quality and form for publication |

| The dissertation of Ayşe Kıvılcım Coşkun is approved,    |

University of California, San Diego

## DEDICATION

To my parents and my sister.

### EPIGRAPH

For a successful technology, reality must take precedence over public relations, for nature cannot be fooled.

—Richard P. Feynman

## TABLE OF CONTENTS

|           | Signature Page iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Dedication iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | Epigraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | List of Figures viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | Acknowledgments xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Vita and Publications xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | Abstract of the Dissertation xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter 1 | Introduction11.1 Temperature-Induced Challenges21.2 Thesis Contributions3                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 2 | Temperature and Reliability Simulation 7  2.1 Related Work 7  2.2 Phase-Based Reliability Simulation 9  2.2.1 Long-Term Performance Modeling 10  2.2.2 Power Modeling 11  2.2.3 Thread Management 12  2.2.4 Thermal Modeling 13  2.2.5 Reliability Modeling 13  2.3 Methodology 15  2.4 Design and Implementation of Runtime Management Policies for Multicore Systems 19  2.4.1 Power Management Policies 19  2.4.2 Migration and Scheduling Policies 20  2.4.3 Voltage/Frequency Scaling Policies 20  2.4.4 Hybrid Techniques 22 |

|           | 2.5       Experimental Results       23         2.5.1       Accuracy       23         2.5.2       Evaluation of Runtime Policies       24                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 2.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 3    | Static Temperature-Aware Job Scheduling                         | $\frac{37}{37}$ |

|--------------|-----------------------------------------------------------------|-----------------|

|              | 3.1.1 Linearization                                             | 44              |

|              | 3.2 Experimental Methodology                                    | 45              |

|              | 3.3 Experimental Results                                        | 49              |

|              | 3.4 Summary                                                     | 54              |

| Chapter 4    | Low-Overhead Dynamic Temperature Management                     | 56              |

|              | 4.1 Dynamic Temperature-Aware Job Scheduling                    | 57              |

|              | 4.1.1 State-of-the-Art Load Balancing Schedulers                | 57              |

|              | 4.1.2 Thermal Management Techniques for MPSoCs                  | 58              |

|              | 4.1.3 Low-Overhead Temperature Aware Scheduling                 | 59              |

|              | 4.2 Thermal Management Using Online Learning                    | 61              |

|              | 4.3 Results                                                     | 64              |

|              | 4.4 Summary                                                     | 69              |

| Chapter 5    | Proactive Temperature Balancing                                 | 72              |

|              | 5.1 Temperature Prediction with Autoregressive Moving Averaging |                 |

|              | (ARMA)                                                          | 73              |

|              | 5.2 Runtime Adaptation                                          | 77              |

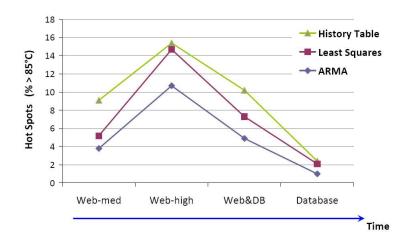

|              | 5.3 Comparison with Other Predictors                            | 80              |

|              | 5.3.1 Exponential Averaging                                     | 80              |

|              | 5.3.2 History Predictor                                         | 82              |

|              | 5.3.3 Recursive Least Squares                                   | 84              |

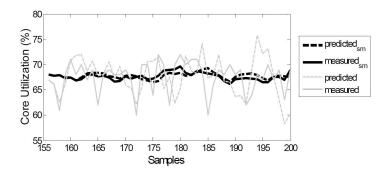

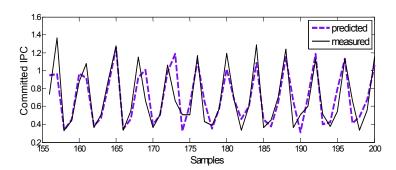

|              | 5.4 Workload Prediction                                         | 85              |

|              | 5.5 Proactive Job Allocation                                    | 86              |

|              | 5.6 Results                                                     | 89              |

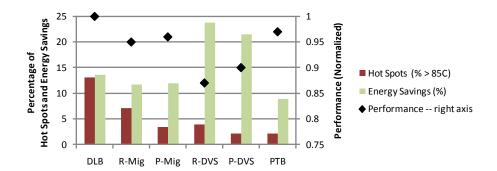

|              | 5.6.1 UltraSPARC T1 Implementation                              | 89              |

|              | 5.6.2 Phase-Based Architecture-Level Simulator                  | 96              |

|              | 5.7 Summary                                                     | 100             |

| Chapter 6    | Summary and Future Work Directions                              | 102             |

|              | 6.1 Fast Reliability Simulation Over Long Time Frames           | 103             |

|              | 6.2 Performance-Efficient Thermal Management                    | 104             |

|              | 6.3 Future Directions                                           | 106             |

|              | 6.3.1 Temperature Modeling and Management in 3D Systems         | 106             |

|              | 6.3.2 Managing Parallel Workloads in Multicore Architectures    | 107             |

| Bibliography |                                                                 | 109             |

## LIST OF FIGURES

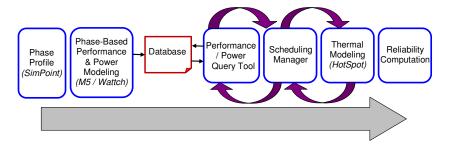

| Figure 2.1:  | Design Flow                                                                  | 10  |  |  |  |  |

|--------------|------------------------------------------------------------------------------|-----|--|--|--|--|

| Figure 2.2:  | Floorplan of the 16-Core CPU                                                 | 16  |  |  |  |  |

| Figure 2.3:  | .3: Thread Assignment Strategy for Balance Location                          |     |  |  |  |  |

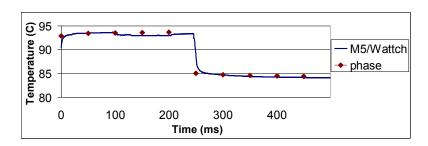

| Figure 2.4:  | Comparison of Temperature Responses for bzip2 Using Two Simula-              |     |  |  |  |  |

|              | tion Methodologies                                                           | 24  |  |  |  |  |

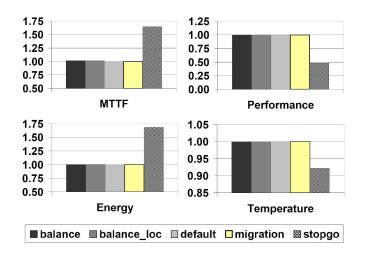

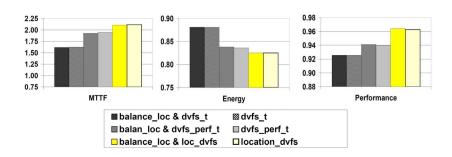

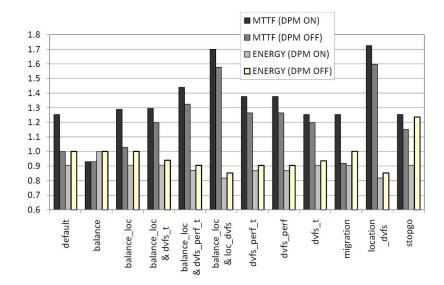

| Figure 2.5:  | Comparison of Workload Allocation Techniques                                 | 26  |  |  |  |  |

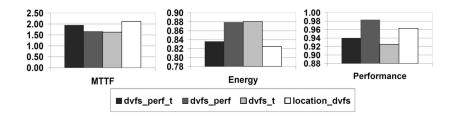

| Figure 2.6:  | Comparison of DVFS-Based Techniques                                          | 28  |  |  |  |  |

| Figure 2.7:  | Comparison of Hybrid Techniques                                              | 28  |  |  |  |  |

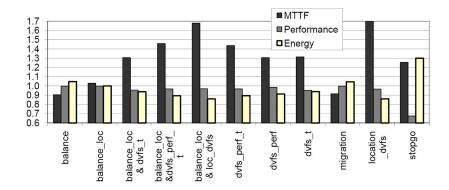

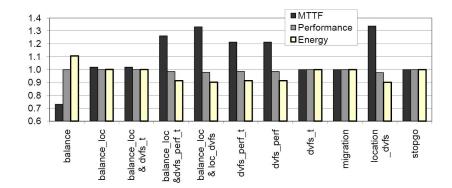

| Figure 2.8:  | Effect of System Utilization (2 Idle Cores)                                  | 29  |  |  |  |  |

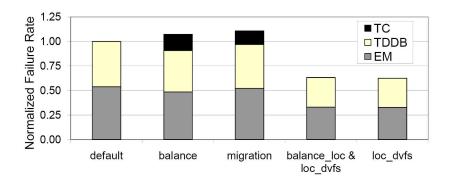

| Figure 2.9:  | Contributions of Failure Mechanisms                                          | 30  |  |  |  |  |

| Figure 2.10: | Effect of System Utilization (4 Idle Cores)                                  | 32  |  |  |  |  |

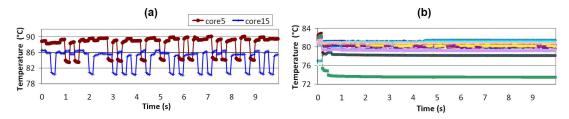

|              | (a) Cycles Caused by the <i>Migration</i> Policy; (b) Stable Thermal Profile |     |  |  |  |  |

|              | of $Balance\_Location \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                 | 32  |  |  |  |  |

|              | MTTF and Energy Effects of DPM                                               | 34  |  |  |  |  |

| O            |                                                                              |     |  |  |  |  |

| Figure 3.1:  | Example Task Graph                                                           | 38  |  |  |  |  |

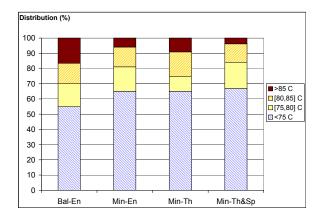

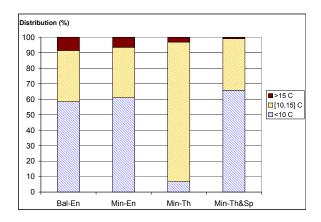

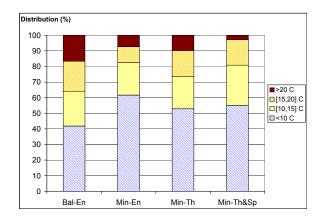

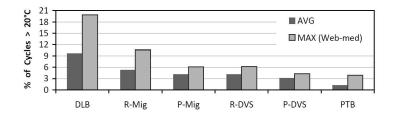

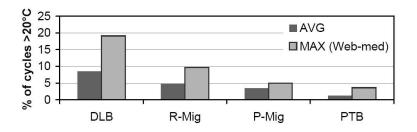

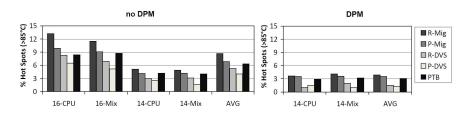

| Figure 3.2:  | Distribution of Thermal Hot Spots (with DPM)                                 | 51  |  |  |  |  |

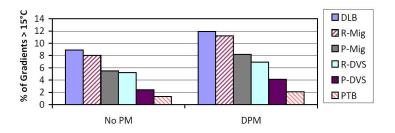

| Figure 3.3:  | Distribution of Spatial Gradients (with DPM)                                 | 5]  |  |  |  |  |

| Figure 3.4:  | Temporal Variations (with DPM)                                               | 52  |  |  |  |  |

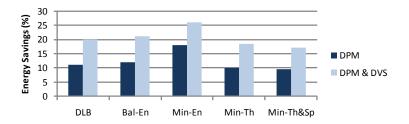

| Figure 3.5:  | Energy Savings with DPM and DVS&DPM                                          | 53  |  |  |  |  |

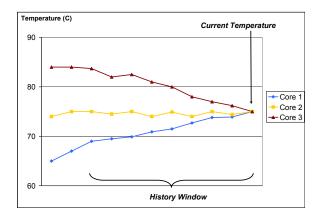

| Figure 4.1:  | Effect of Temperature History                                                | 59  |  |  |  |  |

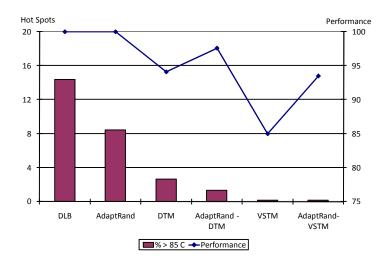

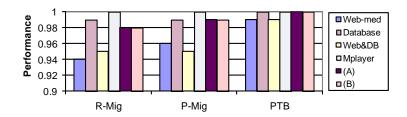

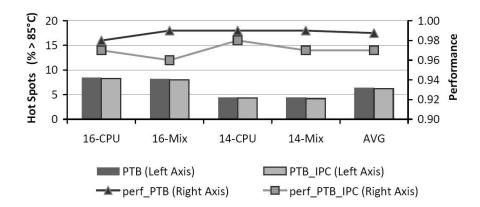

| Figure 4.2:  | Comparison of Hot Spots and Performance Cost                                 | 65  |  |  |  |  |

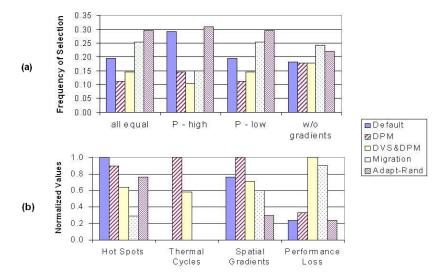

| Figure 4.3:  | (a) Effect of Loss Function on Expert Selection, (b) Evaluation of           |     |  |  |  |  |

| _            | Expert Strategies                                                            | 67  |  |  |  |  |

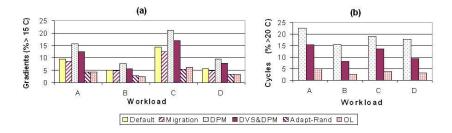

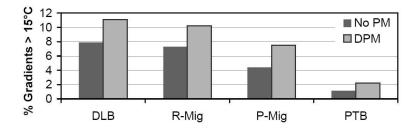

| Figure 4.4:  | (a) Thermal Cycles, (b) Spatial Gradients                                    | 68  |  |  |  |  |

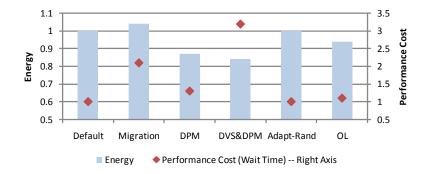

| Figure 4.5:  | Energy and Performance Evaluation                                            | 69  |  |  |  |  |

| 1 18410 1.0. | Enorgy and refreshmence Evaluation 111111111111111111111111111111111111      | 0.6 |  |  |  |  |

| Figure 5.1:  | Flow Chart of the Proposed Technique                                         | 73  |  |  |  |  |

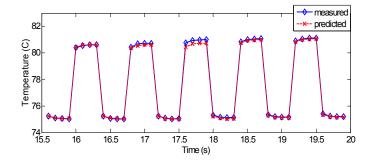

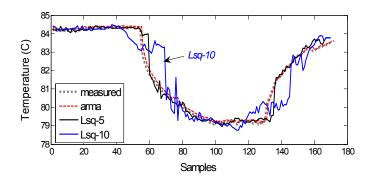

| Figure 5.2:  | Temperature Prediction                                                       | 76  |  |  |  |  |

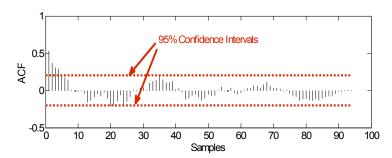

| Figure 5.3:  | Autocorrelation Function of the Residuals                                    | 76  |  |  |  |  |

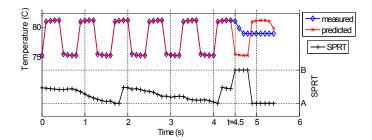

| Figure 5.4:  | Online Detection of Variations in Thermal Characteristics                    | 79  |  |  |  |  |

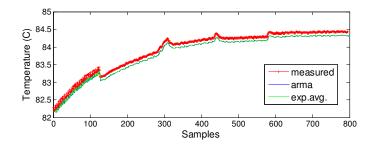

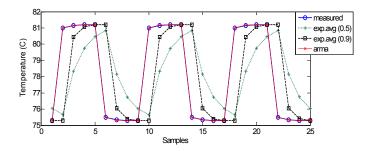

| Figure 5.5:  | Comparison of Predictors - Stable Temperature                                | 80  |  |  |  |  |

| Figure 5.6:  | Comparison of Predictors - Thermal Cycling                                   | 81  |  |  |  |  |

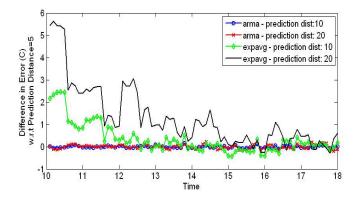

| Figure 5.7:  | Predicting Further Ahead with Exponential Averaging                          | 81  |  |  |  |  |

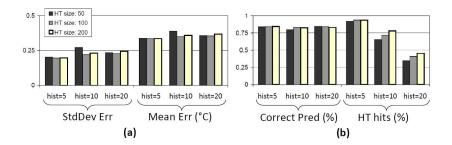

| Figure 5.8:  | Accuracy-Size Trade-Off for the History Predictor                            | 82  |  |  |  |  |

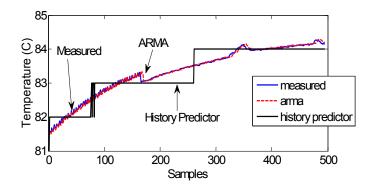

| Figure 5.9:  | Comparison of ARMA and History Predictor                                     | 83  |  |  |  |  |

| Figure 5.10: | Comparison of ARMA and Recursive Least Squares Predictor                     | 84  |  |  |  |  |

| Figure 5.11: | Prediction of Core Utilization                                               | 86  |  |  |  |  |

| Figure 5.12: | Prediction of Committed IPC                                                  | 86  |  |  |  |  |

|              | Energy Savings, Hot Spots, and Performance - with DPM (Simulator)            | 92  |  |  |  |  |

|              | Temperature Cycles - with DPM (Simulator)                                    | 93  |  |  |  |  |

| Figure 5.15: | Spatial Gradients (Simulator)                                                | 93  |  |  |  |  |

|              | Spatial Gradients (Real Implementation)                                      | 95  |  |  |  |  |

| Figure | 5.17: | Thermal Cycles - with DPM (Real Implementation) 98     |

|--------|-------|--------------------------------------------------------|

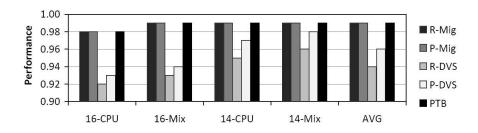

| Figure | 5.18: | Normalized Performance (Real Implementation)           |

| Figure | 5.19: | Proactive Balancing Results for Various Predictors 97  |

| Figure | 5.20: | Thermal Hot Spots (16-Core System)                     |

| Figure | 5.21: | Performance of Policies on the 16-Core Architecture 98 |

| Figure | 5.22: | Thermal Results for ARMA IPC Predictor                 |

## LIST OF TABLES

| Table 2.1: | Delay and Power Model Assumptions                               | 13 |

|------------|-----------------------------------------------------------------|----|

| Table 2.2: | HotSpot Parameters                                              | 13 |

| Table 2.3: | Architectural Parameters                                        | 17 |

| Table 2.4: | Workload Characteristics                                        | 18 |

| Table 2.5: | Power Estimation Error of Our Framework Compared to M5/Wattch . | 24 |

| Table 2.6: | Number of Migrations and V/f Changes (per Second)               | 31 |

| Table 3.1: | Summary of All the ILP Objective Functions                      | 40 |

| Table 3.2: | ILP Formulation for Min-Th&Sp                                   | 41 |

| Table 3.3: | Variables Used in the ILP                                       | 42 |

| Table 3.4: | Power and Area Distributions of the Units                       | 46 |

| Table 3.5: | Workload Characteristics                                        | 47 |

| Table 3.6: | Summary of Experimental Results                                 | 50 |

| Table 4.1: | Pseudo-Code for the Online Learning Algorithm                   |    |

| Table 4.2: | Loss Function                                                   | 63 |

| Table 4.3: | Thermal Hot Spots                                               | 68 |

| Table 5.1: | Thermal Hot Spots and Performance (Simulator)                   | 91 |

| Table 5.2: | Temperature Results for Combined Workloads (Simulator)          | 94 |

| Table 5.3: | Hot Spots (Real Implementation)                                 | 94 |

| Table 5.4: | Workload Characteristics for the Architectural Simulator        | 98 |

#### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Tajana Simunic Rosing, for her guidance during my PhD. I must also thank my doctoral committee, Dr. Kenny Gross, Dr. Rajesh Gupta, Dr. Tara Javidi, Dr. Andrew B. Kahng, and Dr. Dean Tullsen for their valuable feedback and contributions.

My internship at Sun Microsystems during my PhD has been an invaluable experience, and I appreciate the help, support, and the enjoyable working environment my colleagues at Sun have provided. I especially thank the System Dynamics Characterization and Control team at Sun, including Dr. Keith Whisnant. I am also grateful to Dr. David Atienza and Dr. Giovanni De Micheli, as it has been a pleasure to work with them during the summers I spent at EPFL and afterwards.

I cannot thank Dr. Yusuf Leblebici enough for his contributions to my academic career since my early years in college, and for his insightful advice during critical times. I also thank Dr. Brad Calder for his guidance when I was trying to find my research direction.

I would like to thank all my lab mates, co-authors, and friends at UC San Diego, especially Gaurav Dhiman, Shervin Sharifi, Giacomo Marchetti, Edoardo Regini, Priti Aghera, Raid Ayoub, Richard Strong, Kresimir Mihic, and the Architecture Lab folks for their friendship and contributions to my research during my PhD years. I thank also my professors at Sabanci University, Turkey, for inspiring me to pursue an academic career.

I have been surrounded with an exceptional circle of friends, and would like to thank especially Ozge Cavus, Fikriye Kurban, Selim Guncer, Didem Turker, Hasim Mardin, Vuslat and Beste Nazilli, Deniz Kebabci, and Justin Burke for their support, tolerance, and for sharing the ups and downs. I thank Denis Dondi for his love and companionship, and for his patience during stressful times.

The greatest thanks are for all of my family, who had my best interest in their hearts at all times, who loved, supported and motivated me. I feel extremely lucky to have such a big and wonderful family. I am dedicating this thesis to my parents, Nermin Sungar and Umur Coskun, and my sister, Dr. Safak Coskun, for they have always encouraged my curiosity and my ambition to follow my dreams. They have made me the person I am today, taught me to believe in myself, and reminded me what is important in life.

The research that forms the basis of this dissertation has been funded in part by Sun Microsystems, UC MICRO, Center for Networked Systems (CNS) at UCSD, Cisco, Qualcomm, IBM, MARCO/DARPA Gigascale Systems Research Center, NSF MRI Greenlight #0821155, and NSF CCF #0916127.

The text of Chapter 2 is in part a reprint of the material from the paper, Ayse K. Coskun, Richard Strong, Dean Tullsen and Tajana Rosing, "Evaluating the Impact of Job Scheduling and Power Management on Processor Lifetime for Chip Multiprocessors", in Proceedings of SIGMETRICS/Performance 2009–Joint International Conference on Measurement and Modeling of Computer Systems, 2009. The dissertation author was the primary researcher and author, and the co-authors involved in the publication [22] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Chapter 3 is in part a reprint of the material from the paper, Ayse K. Coskun, Tajana Simunic Rosing, Keith Whisnant and Kenny Gross, "Static and Dynamic Temperature-Aware Scheduling for Multiprocessor SoCs", in IEEE Transactions on VLSI, September 2008. The dissertation author was the primary researcher and author, and the co-authors involved in the publication [21] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Sections 4.1 and 4.3 are in part reprints of the material from the papers, Ayse K. Coskun, Tajana Simunic Rosing and Keith Whisnant, "Temperature Aware Task Scheduling in MPSoCs", in Proceedings of Design Automation and Test in Europe (DATE), 2007, and Ayse K. Coskun, Tajana Simunic Rosing, Keith Whisnant and Kenny Gross, "Static and Dynamic Temperature-Aware Scheduling for Multiprocessor SoCs", in IEEE Transactions on VLSI, September 2008. The dissertation author was the primary researcher and author, and the co-authors involved in the publications [17] and [21] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Sections 4.2 and 4.3 are in part a reprint of the material from the paper, Ayse K. Coskun, Tajana Simunic Rosing and Kenny Gross, "Temperature Management in Multiprocessor SoCs Using Online Learning", in Proceedings of Design Automation Conference (DAC), 2008. The dissertation author was the primary researcher and author, and the co-authors involved in the publication [19] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Chapter 5 is in part a reprint of the material from the papers, Ayse

K. Coskun, Tajana Simunic Rosing, and Kenny Gross, "Utilizing Predictors for Efficient Thermal Management in Multiprocessor SoCs", in IEEE Transactions on CAD, 2009, and Ayse K. Coskun, Tajana Simunic Rosing and Kenny Gross, "Proactive Temperature Balancing for Low Cost Thermal Management in MPSoCs", in Proceedings of International Conference on Computer-Aided Design (ICCAD), 2008. The dissertation author was the primary researcher and author, and the co-authors involved in the publications [20] and [15] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Section 6.3.1 is in part a reprint of the material from the paper, Ayse K. Coskun, Tajana Simunic Rosing, Jose Ayala, David Atienza and Yusuf Leblebici, "Dynamic Thermal Management in 3D Multicore Architectures", in Proceedings of Design Automation and Test in Europe (DATE), 2009. The dissertation author was the primary researcher and author, and the co-authors involved in the publication [18] directed, supervised, and assisted in the research which forms the basis for that material.

The text of Section 6.3.1 is in part a reprint of the material from the paper, Ayse K. Coskun, Andrew B. Kahng and Tajana Simunic Rosing, "Temperature- and Cost-Aware Design of 3D Multiprocessor Architectures", in Proceedings of Euromicro Conference on Digital System Design (DSD), 2009. The dissertation author was the primary researcher and author, and the co-authors involved in the publication [16] directed, supervised, and assisted in the research which forms the basis for that material.

#### VITA

| 2003      | B. S. in Microelectronics Engineering, Sabanci University, Istanbul, Turkey                |

|-----------|--------------------------------------------------------------------------------------------|

| 2003-2009 | Graduate Student Researcher, University of California, San Diego                           |

| 2006      | M. S. in Computer Science and Engineering, University of California, San Diego             |

| 2006-2009 | Intern in System Dynamics Characterization and Control (SDCC), Sun Microsystems, San Diego |

| 2009      | Ph. D. in Computer Science and Engineering, University of California, San Diego            |

#### **PUBLICATIONS**

Ayse K. Coskun, Tajana Simunic Rosing, and Kenny Gross. "Utilizing Predictors for Efficient Thermal Management in Multiprocessor SoCs". *IEEE Transactions on CAD*, To appear in 2009.

Ayse K. Coskun, Tajana Simunic Rosing, Keith Whisnant and Kenny Gross. "Static and Dynamic Temperature-Aware Scheduling for Multiprocessor SoCs". *IEEE Transactions on VLSI*, vol.16 no.9, pp. 1127-1140, Sept. 2008.

Ayse K. Coskun, Tajana Simunic Rosing, Kresimir Mihic, Yusuf Leblebici and Giovanni De Micheli. "Analysis and Optimization of MPSoC Reliability". *Journal of Low Power Electronics (JOLPE)*, vol.2 no.1, pp.56-69, April 2006.

Ayse K. Coskun, Tajana Simunic Rosing, Jose Ayala and David Atienza. "Modeling and Dynamic Management of 3D Multicore Systems with Liquid Cooling". To appear in *IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC)*, October 2009.

Francesco Zanini, Ayse K. Coskun, David Atienza and Giovanni De Micheli. "Optimal Multi-Processor SoC Thermal Simulation via Adaptive Differential Equation Solvers". To appear in *IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC)*, October 2009.

Ayse K. Coskun, Tajana Rosing and Andrew B. Kahng. "Temperature- and Cost-Aware Design of 3D Multiprocessor Architectures". *Euromicro Conference on Digital System Design (DSD)*, pp. 183-190, 2009.

Ayse K. Coskun, Richard Strong, Dean Tullsen and Tajana Rosing. "Evaluating the Impact of Job Scheduling and Power Management on Processor Lifetime for Chip Multiprocessors". SIGMETRICS/Performance 2009–Joint International Conference on Measurement and Modeling of Computer Systems, pp.169-180, 2009.

Ayse K. Coskun, Tajana Simunic Rosing, Jose Ayala, David Atienza and Yusuf Leblebici. "Dynamic Thermal Management in 3D Multicore Architectures". *Proceedings of Design Automation and Test in Europe (DATE)*, pp. 1410-1415, 2009.

Ayse K. Coskun, Tajana Simunic Rosing and Kenny Gross. "Proactive Temperature Balancing for Low Cost Thermal Management in MPSoCs". *Proceedings of International Conference on Computer-Aided Design (ICCAD)*, pp. 250-257, 2008.

Ayse K. Coskun, Tajana Simunic Rosing and Kenny Gross. "Proactive Temperature Management in MPSoCs". *Proceedings of International Symposium on Low Power Electronics and Design (ISLPED)*, pp. 165-170, 2008.

Ayse K. Coskun, Tajana Simunic Rosing and Kenny Gross. "Temperature Management in Multiprocessor SoCs Using Online Learning". *Proceedings of Design Automation Conference (DAC)*, pp. 890-893, 2008.

Ayse K. Coskun, Tajana Simunic Rosing, Keith Whisnant and Kenny Gross. "Temperature-Aware MPSoC Scheduling for Reducing Hot Spots and Gradients". *Proceedings of Asia and South Pacific Design Automation Conference (ASPDAC)*, pp. 49-54, 2008.

Ayse K. Coskun, Tajana Simunic Rosing and Keith Whisnant. "Temperature Aware Task Scheduling in MPSoCs". *Proceedings of Design Automation and Test in Europe* (*DATE*), pp. 1659-1664, 2007.

Satish Narayanasamy, Ayse K. Coskun and Brad Calder. "Transient Fault Prediction Based on Anomalies in Processor Events". *Proceedings of Design Automation and Test in Europe (DATE)*, pp. 1140-1145, 2007.

Ayse K. Coskun, Tajana Simunic Rosing, Yusuf Leblebici and Giovanni De Micheli. "A Simulation Methodology for Reliability Analysis in Multi-Core SoCs". *Great Lakes Symposium on VLSI (GLSVLSI)*, pp. 95-99, 2006.

#### ABSTRACT OF THE DISSERTATION

#### Efficient Thermal Management for Multiprocessor Systems

by

Ayşe Kıvılcım Coşkun Doctor of Philosophy in Computer Science and Engineering University of California San Diego, 2009 Tajana Šimunić Rosing, Chair

High temperatures and large thermal variations on the die create severe challenges in system reliability, performance, leakage power, and cooling costs. Designing for worst-case thermal conditions is highly costly and time-consuming. Therefore, dynamic thermal management methods are needed to maintain safe temperature levels during execution. Conventional management techniques sacrifice performance to control temperature and only consider the hot spots, neglecting the effects of thermal variations. This thesis focuses on developing performance-efficient techniques to achieve safe and balanced thermal profiles on multiprocessor system-on-chips (MPSoCs).

Modeling performance, temperature, and reliability of MPSoCs with high accuracy and reasonable simulation time is a challenge, because we need to keep track of instruction-level activities and also simulate sufficiently long real-time execution to have meaningful reliability estimates. The first contribution of this thesis is a fast simulation framework, which evaluates reliability of runtime policies or design-time decisions accurately in a matter of hours—whereas traditional architecture-level simulators would have to run for days.

Job scheduling on an MPSoC has a significant impact on temperature and reliability. For systems with a priori known workloads, this thesis proposes a scheduling optimization method which outperforms other static energy or temperature management techniques in terms of reducing thermal hot spots and gradients. However, having an accurate design-time workload estimate is not possible for most systems. This work introduces dynamic techniques to address runtime variations in workload. The key aspects of these dynamic techniques are low-performance impact and adaptation capability.

Reacting after thermal events occur reduces the efficiency of thermal management policies. This thesis proposes a novel proactive management approach to address this issue, and shows that utilizing a thermal forecast for temperature-aware scheduling achieves significant gains in both temperature and performance. All the novel management policies introduced in this thesis are evaluated using an experimental framework based on real-life systems and workloads. In the experiments on an UltraSPARC T1 processor, proactive thermal management achieves remarkable results with an average 60% reduction in hot spot occurrences, 80% reduction in spatial gradients and 75% reduction in thermal cycles in comparison to reactive thermal management, while also improving performance.

## Chapter 1

## Introduction

Power consumption of chips has increased substantially for the last few decades to accommodate the rising performance demand. Higher power consumption combined with smaller device dimensions increase power densities and on-chip temperatures. A number of critical challenges arise due to high temperatures, including lower reliability, higher cooling costs, and performance degradation. The difficulty of managing these challenges, especially the prohibitively high cooling costs, have motivated the shift from designing single-core highly-complex architectures to multicore chips that integrate several simpler, lower power cores [38]. Today, advances in process technology enable manufacturing complete multiprocessor SoCs including CPUs, memories and communication architectures on a single die. The Sun UltraSPARC T1 [38] and the IBM Cell [35] are examples of such multicore processors.

The hardware parallelism supplied by the multicore architectures enables achieving higher performance per Watt. However, the power density is still at a rising trend, as we continue to shrink the feature sizes and improve the performance of our systems at the cost of higher power consumption. In deep submicron process technologies, high temperatures, process imperfections, and reduced voltage margins have already made the systems much more vulnerable to failures. In addition, as we progress to designing many-core systems, we manufacture larger chips which potentially have dramatically higher temperature variations across the die. These variations add to the existing challenges caused by high temperatures, as they degrade system reliability, performance, and cooling efficiency. Therefore, multicore systems still face a great amount of temperature-induced problems.

To address the need of efficient thermal management of multicore systems, this thesis analyzes the effects of design-time and runtime decisions on temperature, and develops techniques to manage temperature without a substantial effect on performance. This introductory chapter provides an overview of the temperature-induced challenges and the prior work in thermal management. It also highlights the contributions of the thesis.

## 1.1 Temperature-Induced Challenges

One of the obvious results of high temperatures is higher cooling costs. This increase is due to both the need for more expensive packaging solutions and to the cooling energy consumed by the system fans that are supplying the air to cool the package. Leakage power, which is a significant portion of total power for 65nm and below, is exponentially related to temperature. High temperatures adversely affect performance as well, as the effective operating speed of devices decreases with high temperatures.

Temperature also has a strong effect on system reliability. Hot spots exponentially accelerate failure mechanisms such as electromigration, stress migration, and dielectric breakdown, which cause permanent device failures [34]. In fact, a small difference in the operating temperature (i.e.,  $10-15^{o}C$ ) can result in a 2X difference in the lifetime of the devices [70].

Addressing thermal hot spots alone is not enough to improve reliability. Temporal and spatial thermal gradients affect device reliability even at moderate temperatures [44]. The failure rate due to thermal cycling (i.e., temporal fluctuations in temperature) increases with higher magnitude and frequency of the temperature cycles [34]. For example, a  $10^{\circ}C$  increase in the magnitude of cycles can cause about 16X decrease in mean-time-to-failure of metallic structures [34]. Thermal cycling causes accelerated package fatigue and plastic deformations of materials, leading to permanent failures. Such cycles are created either by low frequency power changes such as system power on/off cycles, or by more frequent workload rate changes and power management decisions (e.g., putting idle units in deep sleep mode) [52].

High spatial temperature gradients, which can easily occur on today's large multicore SoCs, also cause performance and reliability degradation. In process technologies below  $0.13 \ \mu m$ , reliability issues arise due negative bias temperature instability (NBTI) and hot carrier injection (HCI) effects, as the operating temperatures and electric fields

reach high enough values to accelerate these mechanisms during device lifetime [39]. When the temperature gradient is large, the delay characteristics of devices may change in a sufficiently different amount due to NBTI and HCI to cause the circuits to fail in meeting timing constraints [39]. In addition, increasing temperature increases local resistances, and as a result, elevates circuit delays and IR drop as well [55]. Global clock networks are especially vulnerable to large spatial variations. Every 20 degrees increase in temperature causes 5-6% increase in Elmore delay in interconnects. As a result, clock skew problems become noticeable for spatial variations of even 15-20 degrees [1]. Another important adverse effect of spatial gradients is lower cooling efficiency. As the cooling infrastructure (i.e., heat sink and fans) needs to take care of the highest temperature on the chip, large on-chip variations result in over-cooling and waste energy.

Initially, designers have addressed thermal challenges at design time to ensure that the reliability, performance, and leakage power constraints are met. Temperature-aware floorplanning (e.g., [54]) or improving the cooling infrastructure are examples of offline techniques. However, due to the increase in power densities with each new technology node and the high integration levels in systems, designing for worst-case has become very costly and time consuming [11]. Therefore, designing for better-than-worst-case conditions and implementing dynamic thermal management strategies to guarantee safe temperatures at runtime have become a common practice.

Conventional dynamic thermal management methods maintain temperature below critical values by slowing down or stalling the processor upon reaching a predetermined threshold temperature value (e.g., [59])—hence, such methods trade-off performance for reliability. Well-known techniques for thermal management include fetch-toggling [59], dynamic voltage/frequency scaling [59, 24], thread migration [29] or hybrid techniques that combine two or more of management methods to improve performance [40].

#### 1.2 Thesis Contributions

Prior thermal management work has focused on thermal hot spots, but the effects of thermal variations in time and space have not been considered. For example, a dynamic power management (DPM) policy that turns off idle cores to save energy can have conflicting goals with a thermal management policy that lowers and balances the temperature. DPM without thermal constraints can create large cycles or gradi-

ents due to the ultra-low power sleep modes it utilizes, and consequently can degrade reliability—even though it may reduce the average temperature at the same time. Therefore, developing policies to take care of both hot spots and variations while maintaining desired performance and energy levels is an important challenge. This thesis focuses on the design of performance-efficient thermal management techniques that prevent the temperature-induced reliability and performance degradation as much as possible, as opposed to only avoiding critically high temperatures.

Achieving performance-efficiency requires identifying the workload characteristics at design time or at runtime and exploiting these characteristics to make intelligent management decisions. For MPSoCs, workload scheduling has a substantial effect on temperature. Thus, temperature-aware scheduling has the potential to overcome temperature-induced challenges at a low performance cost. To this end, for systems with known workloads (such as some embedded systems), this work introduces a job scheduling optimization method that minimizes hot spots and gradients while maintaining the timing requirements of the workload.

In most real-life systems, it is difficult to accurately estimate runtime workload conditions during design. Workload varies at runtime, requiring dynamic management methods to manage temperature. Multiprocessor systems provide several advantages for dynamic management. First, MPSoCs are typically under-utilized for a significant portion of their lifetime. Therefore, intelligent workload allocation and scheduling policies can improve the thermal profile dynamically at a low performance cost in comparison to slowing down or stalling execution. Second, many chips today contain a number of sensors and counters that provide real-time information about the system dynamics (e.g., temperature, performance, etc.). The thermal management policies proposed in this work utilize such information for tuning the runtime management policy to efficiently fit the current workload conditions. We utilize these properties of MPSoCs to design low-cost dynamic scheduling techniques that reduce and balance temperature.

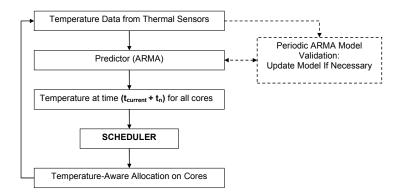

Existing dynamic thermal management methods are reactive, that is, they take action after a thermal emergency occurs. This work discusses a novel technique to forecast temperature dynamics, and shows how this forecast can be utilized for proactive management. Proactive temperature-aware job scheduling tracks the system dynamics as collected by the sensors, learns these dynamics, estimates the near-future temperature, and adjusts job scheduling in advance to mitigate thermal problems before they occur.

This way, the system can operate at a much more desirable performance-temperature trade-off point in comparison to reacting to thermal emergencies.

The contributions of this thesis are outlined as the following:

- It provides a simulation framework for analyzing the effects of runtime management decisions (e.g., workload migration, power management, voltage/frequency scaling, job scheduling) in multiprocessor systems with high accuracy and reasonable simulation time. The details of this simulation framework are in Chapter 2.

- For systems with a known set of jobs, it proposes an optimization technique to compute the static schedule for minimizing the hot spots and thermal gradients. The optimization technique is able to reduce the frequency of hot spots by 35%, spatial gradients by 85% and thermal cycles by 61% in comparison to the optimal schedule for minimizing energy. This static scheduling method is discussed in Chapter 3.

- As workload varies during execution for many real-life systems, this thesis introduces two dynamic management techniques: (1) Adaptive-Random, which is a temperature-aware scheduling policy that reduces the hot spots and thermal gradients; and (2) Online Learning, which selects the best policy for the current workload among a given set of thermal management and scheduling policies. Both techniques have very-low runtime overhead and adaptation capability. Chapter 4 provides the details of these low-overhead dynamic management techniques.

- It shows that reactive thermal management strategies cannot effectively utilize the performance capacity of multicore architectures, and proposes a proactive method to learn the system dynamics and forecast thermal events before they occur. Using the thermal forecast, *Proactive Temperature Balancing* achieves a significantly better temperature-performance trade-off in comparison to reactive thread migration or voltage/frequency scaling methods. The proactive management method is discussed in Chapter 5.

- The experimental methodology to analyze and evaluate the proposed methods is based on real-life systems and workloads. The dynamic job scheduling methods are implemented on an UltraSPARC T1 processor [38]. In the experiments performed on the UltraSPARC T1, proactive thermal management achieves 60% reduction

in hot spot occurrences, 80% reduction in spatial gradients and 75% reduction in thermal cycles on average in comparison to reactive thermal management, while also improving performance.

## Chapter 2

# Temperature and Reliability Simulation

Modeling temperature and the effects of temperature on reliability is essential for simulation and analysis of thermal management policies. This chapter first provides an overview of the related work in temperature and reliability modeling. Section 2.2 proposes a novel approach for accurate and fast temperature and reliability modeling at architecture level for multiprocessor systems. We discuss the experimental methodology in Section 2.3. In Sections 2.4 and 2.5, we show how to use the novel simulation framework for analyzing the effects of runtime management techniques on reliability, performance, and energy.

#### 2.1 Related Work

Traditionally, SoCs and thermal packages have been designed considering the worst case temperature that can be reached during execution. As designing for the worst-case is getting prohibitively expensive with every process technology, detailed thermal modeling has become a requirement for both thermal and reliability management of systems. Temperature and reliability modeling enables evaluating and implementing both design-time and run-time temperature optimization methods. This way, we can reduce the area and performance costs of cooling solutions.

Thermal modeling is typically accomplished by constructing an equivalent RC network of the chip. Heat flow is analogous to the current passing through a thermal

resistance in the RC network. The transient behavior of temperature is modeled by means of the thermal capacitance. Compact thermal modeling tools, such as HotSpot, address the need for detailed thermal analysis (e.g., [59]). HotSpot models the vertical and horizontal thermal resistances and capacitances automatically for the given floorplan and package information. It takes into account the lateral thermal diffusion on chip as well. To speed-up the thermal modeling process, which is computationally costly, Atienza et al. introduce an FPGA-based fast thermal emulation framework [3]. This framework also constructs the RC network for the given chip, and the emulation platform can reduce the simulation time considerably in comparison to simulation while maintaining accuracy.

Few papers in the literature have taken reliability explicitly into account. Reliability management has been mostly addressed previously as a way of optimizing the policies or architecture at design-time (e.g., [62]). The Reliability-Aware Microprocessor (RAMP) provides a reliability model at the architecture level for temperature-induced intrinsic hard failures [62]. RAMP analyzes the effects of application behavior on reliability, and enables optimizing the architectural configuration and the voltage/frequency setting at design time to meet the reliability target. Previous work also shows that aggressive power management can adversely affect reliability due to fast thermal cycles, and optimization methods that consider reliability constraints provide energy savings while improving the MPSoC lifetime [52].

The SimPoint tool [57] addresses the problem of long simulation times, and it provides clustering analysis to identify a few representative points that can be simulated to predict the performance of the entire application. Biesbrouck et al. [5] use individual program phase information (a complete phase trace) to guide multithreaded simulation. This is accomplished by creating a *Co-Phase Matrix*, which represents the per-thread performance for each potential combination of the single-threaded phase behaviors that occur when multiple programs are run together.

Instead of summarizing the application behavior as in SimPoint, we need to capture the entire behavior to perform meaningful reliability analysis. The work presented in this chapter uses SimPoint's phase identification mechanism to capture a complete phase trace as part of the simulation process. This phase-based framework is able to simulate much longer periods of real-life execution in reasonable time frames.

### 2.2 Phase-Based Reliability Simulation

Simultaneous modeling of performance and reliability presents new methodological challenges that require tools and solutions radically different than traditional architectural investigation. This section describes the entire simulation infrastructure with a specific focus on the two most novel aspects of the framework: long time-frame performance estimation and the integrated reliability simulation.

To analyze runtime management techniques fairly, we need a fully integrated performance, power, and thermal model of the entire chip multiprocessor. This is because we are interested in evaluating management techniques that observe the temperature and power characteristics of the processor, and make management decisions accordingly. Also, we want to capture various types of effects that the architectural simulation provides; e.g., workload-dependent utilization of specific architectural structures and their impact on power and temperature, the time-varying behavior of individual applications, etc. However, thermal events that affect reliability, such as thermal cycles, happen over larger time scales than architecture-level simulation. Architecture-level simulators typically evaluate system behavior at instruction-level and run a total of several hundred million instructions. Interactive architecture-level simulation of the full benchmark is not practical, as just a single detailed architecture-level simulation corresponding to several minutes of real execution time requires weeks or months to complete. Therefore, we introduce new performance modeling mechanisms, integrated with our power, thermal, and reliability models, that allows accurate modeling of execution behavior over tens or hundreds of seconds.

Our simulation framework is shown in Figure 2.1. The performance modeling front-end combines a full-program phase profile with detailed architecture-level simulation of every distinct program phase at all possible frequency settings, including both performance and power characteristics. This characterization is gathered in a database that can be later queried while the full MPSoC simulation progresses. This way, we can model the effects of changing frequency, migrating jobs, etc., without further architecture-level simulation. After scheduling decisions are made and the resulting performance and power data are produced, we can model time-varying temperature effects across the entire chip. The temperature curves are then fed into the reliability models, producing the expected failure rates.

Figure 2.1: Design Flow

#### 2.2.1 Long-Term Performance Modeling

Our framework relies on two simplifying assumptions that are critical to making this problem tractable. The first is that the time constants over which temperature varies do not require us to fully capture cycle-by-cycle variances in the temperature portion of the model. The instruction-level variations are captured in the performance model, but only summarized in the latter stages. This allows us to replace the cycle-by-cycle data with a stair-step graph, presenting performance and power behavior as constant at the average values over individual intervals. Thus, we can capture the program behavior with little loss of accuracy.

This is accurate because we model systems with private L2 caches, which is a likely architectural scenario in future systems [42]. At 16 cores and above, the interconnect cost of a shared cache would be extremely high. This assumption has been demonstrated to be accurate even on research that does not require this type of long simulation [41]. Even with the small core counts in current multicore systems, the AMD dual-core and quad-core Opteron, the IBM Power6, and the coming Intel Nehalem processor all have private L1 and L2 caches. For shared L2 caches, interactions between threads is higher and system-level accuracy of the simulation framework is reduced.

A phase of an application is a segment of execution during which a measured program metric is relatively stable. In our framework, we capture a complete phase profile of each application, beginning to end. Then, using the performance simulator integrated with the power modeling tool, and utilizing a finite number of simulation samples for each phase, we reconstruct the power and execution properties of the complete program. In fact, we do this for all voltage and frequency settings available, so that we can reconstruct the complete program even in the face of an arbitrary number

of voltage/frequency changes.

We use SimPoint [57] methodology to identify the various phases within the applications and to characterize complete program execution. A program's execution is divided into intervals of 100 million instructions. Once we assign each interval to a representative phase, we represent a program's execution by a Phase-ID trace [5]. Thus, at any instruction during a program's execution, we use this file to determine the current phase and to identify points of transition between phases. By running simulations at each phase point in the performance simulator and composing performance/power statistics with the Phase-ID trace, we create both a power and a performance trace.

We capture these program traces in a database which can be queried by the Scheduling Manager (see Figure 2.1) at distinct intervals. Given a program start point, an interval length in cycles, and a frequency setting, the query tool returns the average instructions per second (IPC) and power levels across the interval, and the point the program reaches in execution at the end of the interval. Thus, at runtime, the scheduling manager can make decisions about thread migration, thread stalling, or voltage/frequency changes, and query the database to model the precise effects.

#### 2.2.2 Power Modeling

Power modeling requires coupling the execution traces obtained from the performance simulator with a tool that computes the power consumption for each functional unit. This coupling converts the performance parameters (e.g., cache accesses, branch predictions, etc.) into estimates for transistor switching, and then the power model utilizes these estimates for calculating the instantaneous power values. An example of such power modeling tools is Wattch [12], which is also used in this work.

Transistors consume power when they switch output values, but they also leak power even when they do not switch. The former is referred to as dynamic power, and historically has been the dominant factor; however, as technology shrinks, leakage power becomes increasingly important. We compute the leakage power of CPU cores based on structure areas, temperature, and supply voltage. To account for the temperature and voltage effects on leakage, we use the second-order polynomial model proposed by Su et al. [66]. This model computes the change in leakage power for the given differential temperature and voltage values, assuming a base leakage power density of  $0.5W/mm^2$  at 383K [8]. We determine the coefficients in the polynomial model empirically to match

the normalized leakage values in [66].

#### 2.2.3 Thread Management

We design a scheduling manager which enables the simulation of a large array of thread management policies. The mechanisms available for managing temperature include adjusting the frequency/voltage of a core (DVFS or DVS), putting an idle core into a low-power sleep mode (DPM), migrating computation off of a hot core, and policies that stop activity on a hot core (i.e., clock- or fetch-gating). In each policy, the scheduling manager makes a set of decisions after each scheduling interval, and it may incorporate performance and thermal information from the prior interval. After making those decisions for each thread and core, the scheduling manager then queries the performance database to obtain the power and performance behavior of each core over the next interval. Our simulation sampling intervals (i.e., 50 ms) are shorter than a scheduling interval, so there would be multiple exchanges with the performance database before another scheduling decision is made.

Since the scheduling manager keeps track of performance and power information, it also has the responsibility of modeling complex phenomena such as the delay from thread migrations. The model simulates the effects on power and performance for the following phenomena: thread migration, DVFS, starting a new application on a core, core sleep, and core wakeup. Our assumptions for several of the delays modeled are presented in Table 2.1. We model two aspects of the cost of thread migration among cores. We measure the software overhead in M5's full system mode as the time for Linux to migrate a thread from one core to another idle core and to start execution. This thread migration takes less than 3.0  $\mu s$ . We also attribute architecture overhead to cold start effects in the branch predictor, caches, TLBs, etc. We measure cold start effects by starting each benchmark at many different points in the program, and then computing the average loss in performance. The average loss is 204  $\mu s$ , but the loss varies wildly by benchmark—i.e., from 2 to 740  $\mu s$ . Note that cold start effects dominate the migration penalty. To address the highly variable overhead, we model a distinct migration penalty for each benchmark.

ParameterModel ValueSampling Interval50msThread Migration Delaysyscall delay + cold start effectsDVFS Delaysyscall delay + 20E-6sWakeup Delay25msApplication Startup Delaysyscall delay + cold start effectsTransition Power<br/>(to and from sleep states)10W

Table 2.1: Delay and Power Model Assumptions

Table 2.2: HotSpot Parameters

| Parameter                  | Value              |

|----------------------------|--------------------|

| Die Thickness              | 0.1mm              |

| Core Area                  | $14.44mm^2$        |

| L2 area (total of 2 banks) | $10.56mm^2$        |

| Convection Capacitance     | 140 J/K            |

| Convection Resistance      | $0.1~\mathrm{K/W}$ |

#### 2.2.4 Thermal Modeling

Automated thermal modeling requires power traces for each unit as input, in addition to the chip and package characteristics such as die thickness, heat sink convection properties, etc. Therefore, we feed the detailed power trace derived by the combination of the scheduling manager and the performance/power database into the thermal model. We modify HotSpot's [59] (block model) settings to model the thermal characteristics of an 16-core die. We use the steady state temperature of each unit as the initial temperature values. We summarize the HotSpot parameters in Table 2.2. We calculate the die characteristics based on the trends reported for 65nm process technology [29].

#### 2.2.5 Reliability Modeling

Once we generate a full thermal trace, we use this trace as input to our reliability model. Our work targets temperature-induced reliability problems. The most commonly studied temperature-induced intrinsic hard failure mechanisms are electromigration, time dependent dielectric breakdown, and thermal cycling [34, 62].

**Electromigration** (EM) occurs in interconnects as a result of the momentum transfer from electrons to ions that construct the interconnect lattice and leads to hard failures such as opens and shorts in metal lines. The EM failure rate ( $\lambda_{EM}$ ), based on

Black's model, is given in Equation 2.1. In the equation,  $E_a$  is the activation energy, k is the Boltzmann's constant, T is the temperature, J and  $J_{crit}$  are the current density and the threshold current density, respectively, and  $A_0$  is a material dependent constant. We represent the first half of the equation with the term  $\lambda_{EM}^0$ , which can be considered as a constant (an average technology/circuit dependent value).

$$\lambda_{EM} = A_0 (J - J_{crit})^{-n} e^{(-E_a/kT)} = \lambda_{EM}^0 e^{(-E_a/kT)}$$

(2.1)

Time dependent dielectric breakdown (TDDB) is a wear-out mechanism of the gate dielectric, and failure occurs when a conductive path is formed in the dielectric. TDDB is caused by the electric field and temperature, and the failure rate is defined in Equation 2.2. Similar to the EM failure rate equation, we use  $\lambda^0_{TDDB}$  to represent the first half of the equation. Both EM and TDDB failure rates are exponentially dependent on temperature.

$$\lambda_{TDDB} = A_0 e^{\gamma E_{ox}} e^{(-E_a/kT)} = \lambda_{TDDB}^0 e^{(-E_a/kT)}$$

(2.2)

Thermal cycling (TC) is caused by the large difference in thermal expansion coefficients of metallic and dielectric materials, and leads to cracks and other permanent failures. The thermal cycling effect is modeled by the Coffin-Mason equation [34]. Slow thermal cycles happen because of low frequency power changes such as power on/off cycles. Fast cycles occur due to events such as power management decisions. Although lower frequency cycles have generally received more attention, recent work shows that thermal cycles due to power or workload variations can also degrade reliability [49, 52]. The failure rate due to thermal cycling is formulated as in Equation 2.3.

$$\lambda_{TC} = C_0 (\Delta T - \Delta T_o)^{-q} f \tag{2.3}$$

In this equation,  $\Delta T$  is the temperature cycling range. The elastic portion of the thermal cycle is shown as  $\Delta T_o$ . Elastic thermal stress refers to reversible deformation occurring during a cycle, and  $\Delta T_o$  should be subtracted from the total strain range. Typically,  $\Delta T_o \ll \Delta T$  [34], so the  $\Delta T_o$  component can be dropped from the equation.

$C_0$  is a material dependent constant, q is the Coffin-Manson exponent, and f is the frequency of thermal cycles. Note that the Coffin-Manson equation [34] computes the number of cycles to failure. Therefore, the mean-time-to-failure (MTTF) in years is the number of cycles multiplied by the period of the cycles.

Computing the frequency of cycles is not straightforward in a simulation of an irregular, dynamic system. To resolve this problem, we observe the recent temperature history on each core to compute  $\Delta T$  and f. We set the initial length of the history window to 5 seconds, and adjusted the length dynamically depending on how many cycles are observed. For example, if no temperature cycles are observed in the last interval, we increment the history window length to capture slower cycles.  $\Delta T$  is the temperature differential observed in the last interval. We set a higher band of 80% and a lower band of 20% of the temperature range recorded in the last interval, and count the number of times the temperature exceeds the higher band or goes below the lower band, and use that to calculate the number of cycles in this period. In this way, we can account for the contribution of cycles with varying temperature differentials and varying periods.

For combining the failure rates, as in RAMP [62] we use the sum-of-failure-rates model. This model assumes that all the individual failure rates are independent. MTTF is  $1/\lambda$  for constant failure rates; therefore, we average the failure rate observed throughout the simulation and compute the corresponding average MTTF. The average MTTF value reported for 65nm technology is 7 years [64].

For moderate temperatures at 65nm technology, Srinivasan, et al. [63] demonstrate that the contribution of electromigration, dielectric breakdown, and cycling to the overall failure rate are similar to each other. This allows us to calibrate the constants in each failure equation ( $\lambda_{EM}^0$ ,  $\lambda_{TDDB}^0$ , and  $C_0$ ) to give a system MTTF of 7 years at nominal temperature. We use the same constants all throughout the experiments, which means that the relative impact of different failure mechanisms might change depending on the conditions. For example, if the temperature is high, then the effect of EM or TDDB is higher than TC.

## 2.3 Methodology

This section describes other details of our simulation infrastructure that impact the results shown in the following sections. These, in general, are details that are rela-

| CORE 12             | L2 <sup>12</sup> -2 | CORE 13             | L2 <sup>13</sup> -2 | CORE 14             | L2 <sup>14</sup> -2 | CORE 15             | L2 <sup>15</sup> -2 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| L2 <sup>12</sup> -1 |                     | L2 <sup>13</sup> -1 |                     | L2 <sup>14</sup> -1 |                     | L2 <sup>15</sup> -1 |                     |

| CORE 8              | L2 <sup>8</sup> -2  | CORE 9              | L2 <sup>9</sup> -2  | CORE 10             | L2 <sup>10</sup> -2 | CORE 11             | L2 <sup>11</sup> -2 |

| L2 <sup>8</sup> -1  |                     | L2 <sup>9</sup> -1  |                     | L2 <sup>10</sup> -1 |                     | L2 <sup>11</sup> -1 |                     |

| CORE 4              | L2 <sup>4</sup> -2  | CORE 5              | L2 <sup>5</sup> -2  | CORE 6              | L2 <sup>6</sup> -2  | CORE 7              | L2 <sup>7</sup> -2  |

| L2 <sup>4</sup> -1  |                     | L2 <sup>5</sup> -1  | _                   | L2 <sup>6</sup> -1  |                     | L2 <sup>7</sup> -1  |                     |

| CORE 0              | L2 <sup>0</sup> -2  | CORE 1              | L2 <sup>1</sup> -2  | CORE 2              | L2 <sup>2</sup> -2  | CORE 3              | L2 <sup>3</sup> -2  |

| L2 <sup>0</sup> -1  |                     | L2 <sup>1</sup> -1  |                     | L2 <sup>2</sup> -1  |                     | L2 <sup>3</sup> -1  |                     |

Figure 2.2: Floorplan of the 16-Core CPU

tively independent of our framework described in this chapter, such as the specific tools we use, processor core model, and the workload.

We use the M5 Simulator [6] for performance modeling. M5's out-of-order execution model is based on SimpleScalar 3.0 [13], and provides a detailed model of an Alpha 21264 processor. Anticipating continued scaling of core counts, the CPU we model is a 16-core multiprocessor manufactured at 65nm. The floorplan for this CPU is provided in Figure 2.2. Each core has out-of-order issue, a private data cache, instruction cache, L2 cache, and memory channels. Each core possesses three voltage and frequency settings for dynamic voltage/frequency scaling: 1.200V at 2.0GHz, 1.187V at 1.900GHz, and 1.06V at 1.7GHz which represent DVFS settings of 100% (original), 95% (step-1), and 85% (step-2), respectively. The architectural parameters of each core are depicted in Table 2.3.

We utilize Wattch [12] for the dynamic power modeling of cores in our framework. We integrate Wattch with M5 to provide dynamic and cycle accurate power measurements for each application. We develop a power model for 65nm by scaling the parameters within Wattch to match published power values for 65nm technology. The variation in dynamic power range we observe matches the power distribution on a similar core [31], on which the majority of applications (including SPEC) have less than 16% power dissipation difference from the other applications.

The leakage model we use is found to match closely with measurements [66], and

CPU Clock  $2.0 \mathrm{Ghz}$ **ICache** 64KB 2-way @1ns (2 cyc) **DCache** 64KB 2-way @1ns (2 cyc) L2Cache 2MB 8-way @10ns (20 cyc) (2 banks) 100ns (200 cyc) Memory Latency **Branch Predictor** 21264-style tournament predictor Issue out-of-order ROB 128 entry Issue Width 4 4 IntAlu, 2 IntMult, 2 FPALU, 2 FPMultDiv **Functional Units Physical Regs** 128 Int. 128 FP IQ entries 64  $\overline{\text{Vdd}}$ 1.2V**DVFS Settings** 100%, 95%, 85%

Table 2.3: Architectural Parameters

the leakage values produced in our work are in line with expected values (i.e., 30-40% of the total power consumption for 65nm).

To model power dissipation of L2 caches, we use CACTI [67] (an integrated memory performance, area, leakage, and dynamic power model) and obtain the typical power consumption of a memory block with the given size and properties, and then use these values throughout the simulation.

To create representative workloads, we classify all SPEC2K benchmarks in terms of their variability and memory boundedness. The distinction between CPU bound and memory bound applications is particularly important in this study because it impacts how performance scales as the frequency changes. We model both homogeneous and heterogeneous workloads in terms of the applications' CPU or memory boundedness. As our execution model does not extend to parallel programs, the homogeneous workloads stand in for both homogeneous server-type workloads and parallel applications with few stalls for communication. However, our homogeneous and heterogeneous multiprogrammed workloads best represent a server environment, where the average lifetime of the processor can significantly affect overall costs.

We use the ratio of memory-bus transactions to instructions as a metric to classify applications as memory or CPU-bound, as suggested by Wu et al. [72]. We classify applications along several other dimensions. By constructing our workloads from applications with different phase variability, power savings potential and CPU/memory boundedness, we seek to represent a wide range of real world workloads.

Table 2.4: Workload Characteristics

| Wkload name | Description | Cores    | Benchmarks                               |

|-------------|-------------|----------|------------------------------------------|

|             |             | Utilized |                                          |

| hom_16_cpu  | Homogen.    | 16       | sixtrack*16                              |

|             | CPU Bound   |          |                                          |

| hom_16_mem  | Homogen.    | 16       | mcf*16                                   |

|             | MEM Bound   |          |                                          |

| het_16_cpu  | Hetero.     | 16       | mesa*3, bzip2_program*3, crafty*2,       |

|             | CPU Bound   |          | eon_rushmeier*3, vortex1*2, sixtrack*3   |

| het_16_mem  | Hetero.     | 16       | mcf*4, art110*4, equake*3, gcc_166*3,    |

|             | MEM Bound   |          | swim*2                                   |

| het_16_mix  | Hetero.     | 16       | mcf*2, mesa, art110, sixtrack*2, equake, |

|             | MIX         |          | bzip2_program, eon_rushmeier*2, swim,    |

|             |             |          | applu, twolf, crafty, apsi, lucas        |

| het_12_cpu  | Hetero.     | 12       | mesa*2, bzip2_program*3, crafty*2,       |

|             | CPU Bound   |          | eon_rushmeier*2, vortex1*1, sixtrack*2   |

| het_14_cpu  | Hetero.     | 14       | mesa*2, bzip2_program*3, crafty*2,       |

|             | CPU Bound   |          | eon_rushmeier*2, vortex1*2, sixtrack*3   |

| het_12_mix  | Hetero.     | 12       | mcf*2, mesa, art110, sixtrack*2, swim    |

|             | MIX         |          | eon_rushmeier*2, crafty, apsi, lucas     |

| het_14_mix  | Hetero.     | 14       | mcf*2, mesa, art110, sixtrack*2,         |

|             | MIX         |          | eon_rushmeier*2, swim, twolf,            |

|             |             |          | crafty, apsi, lucas, equake              |

Table 2.4 describes each workload. We model workloads with 12–16 threads—our CMP architecture is constructed to not have thermal issues when lightly loaded, which is the expected behavior for the next few processor generations. We construct both homogeneous and heterogeneous workloads, and CPU-bound, memory-bound, and mixed workloads. The mixed workloads contain applications from both extremes, as well as some in the middle of our categorization. In the time frames we model, several of the applications complete execution. In those cases, we continually restart the application at the beginning to get consistent behavior across the experiment.

A common performance metric on multicore platforms is a raw count of IPC. However, this metric gives undeserved bias towards high-IPC threads as performance may be increased by running more CPU bound threads. To circumvent this difficulty, we use the Fair Speedup Metric (FS) [14, 61]. FS is computed by finding the harmonic mean of each thread's speed-up over a baseline policy of running the thread at the highest frequency and voltage. Although some applications repeat multiple times during

our simulations, we compute FS in such a way that the overall contribution of each application is the same.

### 2.4 Design and Implementation of Runtime Management Policies for Multicore Systems

The simulation infrastructure allows us to design and evaluate various job allocation and thermal management strategies. We divide these techniques into four categories: (1) power management policies that change the power consumption of a core by putting it into sleep or idle state, (2) policies that change what is running on a core via migration or scheduling, (3) policies that continue to execute the same thread but change speed (via DVFS), and (4) hybrid policies that combine DVFS and scheduling. The management policies evaluate the system characteristics at every scheduling period, and make a decision accordingly. In all cases, the scheduling tick is set to every 200ms. The threshold temperature for all the temperature-triggered policies is  $85^{\circ}C$ . The **default** policy keeps the initial assignment of jobs to cores fixed, and no workload migration or voltage/frequency scaling occurs on the fly.

#### 2.4.1 Power Management Policies

Dynamic Power Management (DPM) is one of the techniques we investigate to manage power. DPM puts cores in sleep state to save energy. We implement a fixed timeout policy [37], which is one of the commonly used DPM policies. For each core, the policy waits for a timeout period when the core is idle, and then turns off the core. This is to ensure that we do not turn off cores for very short idle times, where turning off the core would not amortize the cost of transitioning to and from the sleep state. The time period to amortize the cost of going to sleep is called the breakeven time ( $t_{be}$ ). We assume a sleep state power value of 0.05W, and based on the active and idle power dissipation values we compute the  $t_{be}$  to be around 200ms. A simple and effective way to set the timeout period is  $t_{timeout} = t_{be}$  [37]. DPM can be integrated with any of the other policies we discuss in this section for improving the energy savings.

**Stop\_Go** [24] runs each core at the default (highest) frequency and voltage setting until a core reaches the thermal threshold. At this point, the core is stalled and the clock is gated to reduce power consumption. If the core's temperature goes below the

temperature threshold in the next sampling interval, execution continues. We assume that each core can be clock-gated individually.

#### 2.4.2 Migration and Scheduling Policies

These techniques attempt to move computation off of hot cores either via migration or as a response to a thermal event (i.e., high temperature) as a matter of policy.

Migration sends jobs that have exceeded a thermal threshold to the coolest core that has not been assigned a new thread during the current scheduling period. If the coolest core selected is already running a job, we swap the jobs among the hot and cool cores. This technique can be thought of as an extension of core-hopping or activity migration techniques [26, 29] to the case of many cores and many threads.