## **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Compensation for Lithography Induced Process Variations during Physical Design

#### **Permalink**

https://escholarship.org/uc/item/6zk5h8ch

#### **Author**

Chin, Eric Yiow-Bing

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

#### Compensation for Lithography Induced Process Variations during Physical Design

by

Eric Yiow-Bing Chin

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Andrew Neureuther, Chair Professor Kameshwar Poolla Professor John Wawrzynek Professor Fiona Doyle

Spring 2011

## Compensation for Lithography Induced Process Variations during Physical Design

Copyright 2011 by Eric Yiow-Bing Chin

#### Abstract

Compensation for Lithography Induced Process Variations during Physical Design

by

#### Eric Yiow-Bing Chin

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Andrew Neureuther, Chair

This dissertation addresses the challenge of designing robust integrated circuits in the deep sub micron regime in the presence of lithography process variability. By extending and combining existing process and circuit analysis techniques, flexible software frameworks are developed to provide detailed studies of circuit performance in the presence of lithography variations such as focus and exposure. Applications of these software frameworks to select circuits demonstrate the electrical impact of these variations and provide insight into variability aware compact models that capture the process dependent circuit behavior. These variability aware timing models abstract lithography variability from the process level to the circuit level and are used to estimate path level circuit performance with high accuracy with very little overhead in runtime.

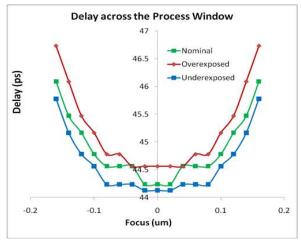

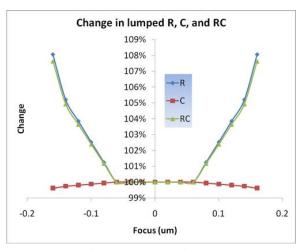

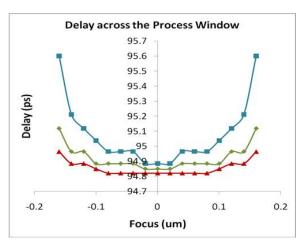

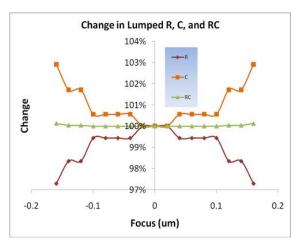

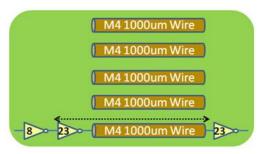

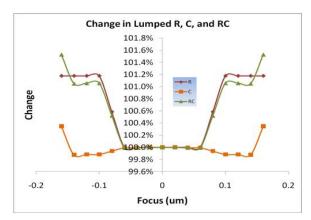

The Interconnect Variability Characterization (IVC) framework maps lithography induced geometrical variations at the interconnect level to electrical delay variations. This framework is applied to one dimensional repeater circuits patterned with both 90nm single patterning and 32nm double patterning technologies, under the presence of focus, exposure, and overlay variability. Studies indicate that single and double patterning layouts generally exhibit small variations in delay (between 1-3%) due to self compensating RC effects associated with dense layouts and overlay errors for layouts without self-compensating RC effects. The delay response of each double patterned interconnect structure is fit with a second order polynomial model with focus, exposure, and misalignment parameters with 12 coefficients and residuals of less than 0.1ps. The IVC framework is also applied to a repeater circuit with cascaded interconnect structures to emulate more complex layout scenarios, and it is observed that the variations on each segment average out to reduce the overall delay variation.

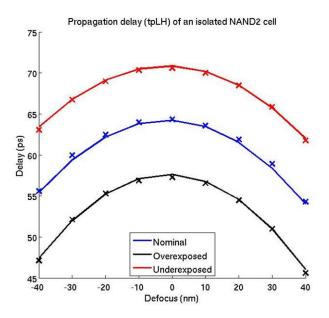

The Standard Cell Variability Characterization (SCVC) framework advances existing layout-level lithography aware circuit analysis by extending it to cell-level applications utilizing a physically accurate approach that integrates process simulation, compact transistor models, and circuit simulation to characterize electrical cell behavior. This framework is applied to combinational and sequential cells in the Nangate 45nm Open Cell Library, and the timing response of these cells to lithography focus and exposure variations demonstrate Bossung like behavior. This behavior permits the process parameter dependent response to be captured in a nine term variability aware compact model based on Bossung fitting equations. For a two

input NAND gate, the variability aware compact model captures the simulated response to an accuracy of 0.3%. The SCVC framework is also applied to investigate advanced process effects including misalignment and layout proximity.

The abstraction of process variability from the layout level to the cell level opens up an entire new realm of circuit analysis and optimization and provides a foundation for path level variability analysis without the computationally expensive costs associated with joint process and circuit simulation. The SCVC framework is used with slight modification to illustrate the speedup and accuracy tradeoffs of using compact models. With variability aware compact models, the process dependent performance of a three stage logic circuit can be estimated to an accuracy of 0.7% with a speedup of over 50,000. Path level variability analysis also provides an accurate estimate (within 1%) of ring oscillator period in well under a second.

Another significant advantage of variability aware compact models is that they can be easily incorporated into existing design methodologies for design optimization. This is demonstrated by applying cell swapping on a logic circuit to reduce the overall delay variability along a circuit path. By including these variability aware compact models in cell characterization libraries, design metrics such as circuit timing, power, area, and delay variability can be quickly assessed to optimize for the correct balance of all design metrics, including delay variability.

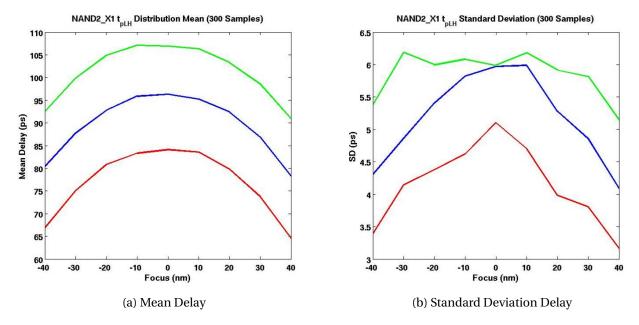

Deterministic lithography variations can be easily captured using the variability aware compact models described in this dissertation. However, another prominent source of variability is random dopant fluctuations, which affect transistor threshold voltage and in turn circuit performance. The SCVC framework is utilized to investigate the interactions between deterministic lithography variations and random dopant fluctuations. Monte Carlo studies show that the output delay distribution in the presence of random dopant fluctuations is dependent on lithography focus and exposure conditions, with a 3.6 ps change in standard deviation across the focus exposure process window. This indicates that the electrical impact of random variations is dependent on systematic lithography variations, and this dependency should be included for precise analysis.

To Mom and Dad, with everlasting love

## **Contents**

| Li | List of Figures |                                                              |    |

|----|-----------------|--------------------------------------------------------------|----|

| 1  | Intr            | roduction                                                    | 1  |

|    | 1.1             | Motivation                                                   | 1  |

|    | 1.2             | Dissertation Organization                                    | 2  |

|    | 1.3             | Unique Dissertation Contributions                            | 4  |

| 2  | Bac             | kground                                                      | 5  |

|    | 2.1             | Lithography Variability                                      | 5  |

|    | 2.2             | Physical Design Methodologies                                | 7  |

|    | 2.3             | Modeling Variability in Design                               | 8  |

|    | 2.4             | Coping with Lithography Variability                          | 9  |

|    |                 | 2.4.1 Strategy #1: Avoid Poor Layouts                        | 9  |

|    |                 | 2.4.2 Strategy #2: Layouts Regularization                    | 10 |

|    |                 | 2.4.3 Strategy #3: Statistical Design Analysis               | 10 |

|    |                 | 2.4.4 Strategy #4: Contour Based Compact Transistor Modeling | 10 |

|    |                 | 2.4.5 Strategy #5: Lithography Simulation Speedups           | 11 |

|    | 2.5             | Summary                                                      | 11 |

| 3  | Too             | ls for Circuit Variability Analysis                          | 13 |

|    | 3.1             | Introduction                                                 | 13 |

|    | 3.2             | Existing Electronic Design Automation (EDA) Tools            | 13 |

|    |                 | 3.2.1 TCAD Simulation Tools                                  | 13 |

|    |                 | 3.2.2 Mask Data Preparation Tools                            | 14 |

|    |                 | 3.2.3 Circuit Simulation Tools                               | 14 |

|    |                 | 3.2.4 Physical Implementation Tools                          | 14 |

|    | 3.3             | Lithography Aware Circuit Analysis                           | 15 |

|    | 3.4             | Creating Variability Aware Analysis Models                   | 15 |

|    | 3.5             | Developed Methodologies                                      | 16 |

|    |                 | 3.5.1 Process Variation Net Scanning                         | 16 |

|    |                 | 3.5.2 Interconnect Variability Characterization              | 17 |

|    |                 | 3.5.3 Standard Cell Variability Characterization             | 18 |

|    | 3.6             | Summary                                                      | 18 |

| 4 | Inte | erconnect Variability Modeling                          | 20       |

|---|------|---------------------------------------------------------|----------|

|   | 4.1  | Introduction                                            | 20       |

|   | 4.2  | Interconnect Delay                                      | 20       |

|   | 4.3  | 90nm and 32nm Process Technology Characterization       | 22       |

|   | 4.4  | One Dimensional Interconnect Studies                    | 23       |

|   |      | 4.4.1 90nm Single Patterning Results                    | 23       |

|   |      | 4.4.2 32nm Double Patterning Results                    | 27       |

|   | 4.5  | Compact Delay Modeling                                  | 28       |

|   | 4.6  | Cascaded Interconnect Scenarios                         | 31       |

|   | 4.7  | Summary                                                 | 33       |

| 5 | Bas  | ic Standard Cell Variability Modeling                   | 34       |

| Ū | 5.1  | Introduction                                            | 34       |

|   | 5.2  | Standard Cell Delay Characterization                    | 34       |

|   | 5.3  | Geometrical Biasing of Rectangular Transistors          | 35       |

|   | 5.4  | Contour Based Timing Characterization                   | 37       |

|   | 0.1  | 5.4.1 High Level Overview                               | 37       |

|   |      | 5.4.2 Lithography Models and Simulation                 | 37       |

|   |      | 5.4.3 Contour Based Device Analysis                     | 37       |

|   | 5.5  | NAND2 Cell Timing Analysis                              | 39       |

|   | 5.5  | 5.5.1 Cell Schematic and Layout                         | 39       |

|   |      | 5.5.2 Poly Layer Focus Exposure Variations              | 39       |

|   |      |                                                         | 39<br>40 |

|   |      | J                                                       | 40       |

|   | г.с  | 5.5.4 Comparison of Two Different Layout Contexts       |          |

|   | 5.6  | Compatibility of Contour Based Compact Timing Models    | 42       |

|   | 5.7  | Comparison of Variability Aware Timing Models           | 43       |

|   | 5.8  | Summary                                                 | 44       |

| 6 | Adv  | anced Standard Cell Variability Modeling                | 46       |

|   | 6.1  | Introduction                                            | 46       |

|   | 6.2  | MUX2 Timing Analysis                                    | 46       |

|   |      | 6.2.1 Cell Schematic and Layout                         | 46       |

|   |      | 6.2.2 Poly and Active Layer Variations                  | 47       |

|   |      | 6.2.3 Poly and Active Misalignment Variations           | 47       |

|   |      | 6.2.4 Comparison of Two Different Layout Contexts       | 48       |

|   | 6.3  | Timing Components for Multiple Stage Logic Cells        | 50       |

|   |      | 6.3.1 Core Delay Component                              | 50       |

|   |      | 6.3.2 Layout Proximity Component                        | 50       |

|   | 6.4  | Extension to Sequential Cell and Power Characterization | 51       |

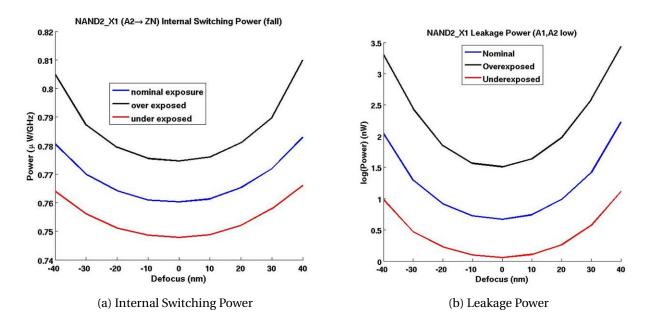

|   |      | 6.4.1 Power Characterization                            | 51       |

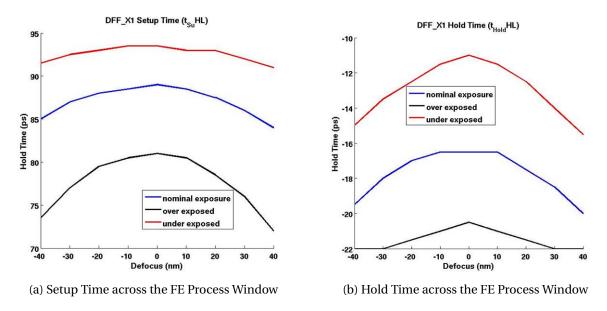

|   |      | 6.4.2 Sequential Cell Characterization                  | 52       |

|   | 6.5  | Summary                                                 | 53       |

| 7  | Patl  | n Level Variabili | ity Analysis in Cell Based Design                                   | 54   |

|----|-------|-------------------|---------------------------------------------------------------------|------|

|    | 7.1   | Introduction .    |                                                                     | . 54 |

|    | 7.2   | Path Level Circ   | ruit Analysis                                                       | . 54 |

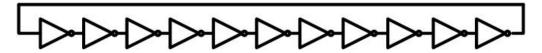

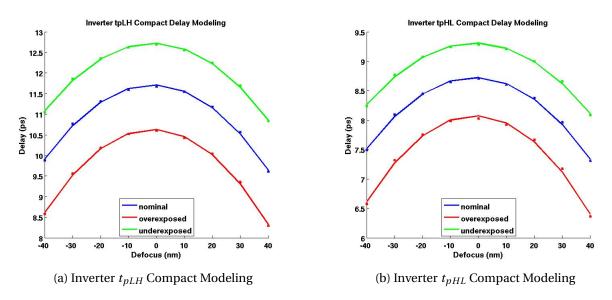

|    |       | 7.2.1 Ring Osc    | cillator Period Estimation                                          | . 54 |

|    |       | 7.2.2 Circuit P   | Path Delay Estimation                                               | . 56 |

|    |       | 7.2.3 Speedup     | o of Circuit Analysis with Compact Models                           | . 58 |

|    | 7.3   | Composite Cur     | rrent Source Modeling                                               | . 59 |

|    | 7.4   | Sensitivity Driv  | ven Circuit Optimization                                            | . 60 |

|    | 7.5   |                   | uit Analysis                                                        |      |

|    |       | 7.5.1 Statistica  | al Timing Analysis Focus Exposure Models                            | . 63 |

|    |       | 7.5.2 Systema     | atic versus Random Variations                                       | . 64 |

|    |       | 7.5.3 Analysis    | s of Random Variability using Geometrical Biasing                   | . 64 |

|    |       | 7.5.4 Analysis    | s of Random Variability using Standard Cell Variability Characteri- |      |

|    |       | zation (S         | SCVC)                                                               | . 64 |

|    | 7.6   | Summary           |                                                                     | . 65 |

| 8  | Con   | clusions          |                                                                     | 67   |

|    | 8.1   | Dissertation Su   | ımmary                                                              | . 67 |

|    | 8.2   | Future Work .     |                                                                     | . 69 |

|    | 8.3   | Final Words .     |                                                                     | . 70 |

| Bi | bliog | raphy             |                                                                     | 71   |

# **List of Figures**

| 2.1  | Sample Bossung Plot                                                           | 6  |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | High Level Overview of Physical Design Methodologies                          | 8  |

| 3.1  | Process Variation Net Scanning Methodology                                    | 16 |

| 3.2  | Interconnect Variability Characterization Methodology                         | 17 |

| 3.3  | Standard Cell Variability Characterization Methodology                        | 18 |

| 4.1  | Interconnect equivalent RC delay model                                        | 21 |

| 4.2  | Delay as a function of length for driver size S                               | 21 |

| 4.3  | 90nm and 32nm Bossung Curves                                                  | 24 |

| 4.4  | General Interconnect Topology                                                 | 24 |

| 4.5  | 90nm Interconnect Structure #1 (Isolated Wire)                                | 25 |

| 4.6  | 90nm Interconnect Structure #2 (Center of Array)                              | 26 |

| 4.7  | 90nm Interconnect Structure #3 (End of Array)                                 | 27 |

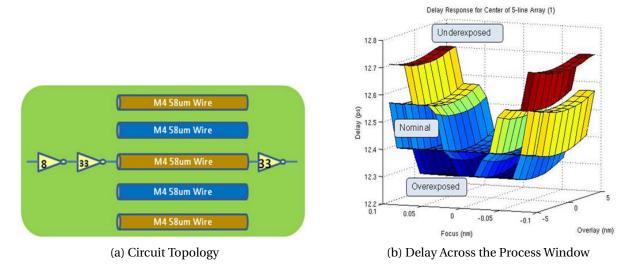

| 4.8  | 32nm Interconnect Structure #1 (Center Array)                                 | 28 |

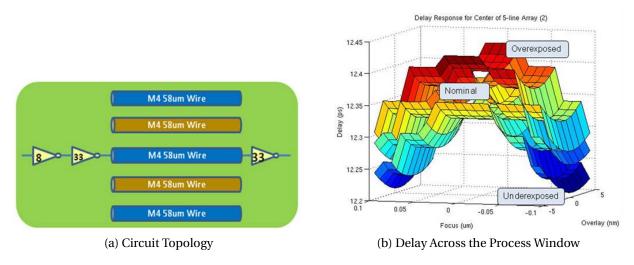

| 4.9  | 32nm Interconnect Structure #2 (Center Array)                                 | 29 |

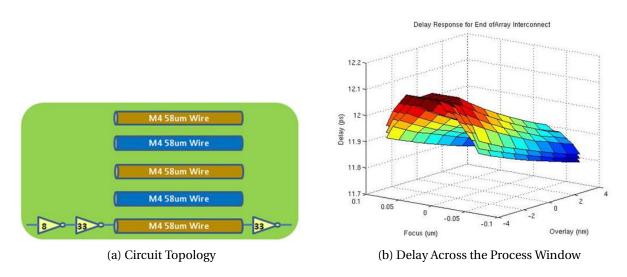

| 4.10 | 32nm Interconnect Structure #3 (End of Array)                                 | 29 |

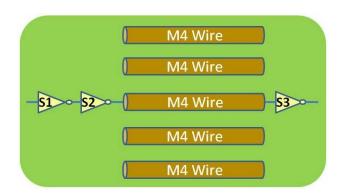

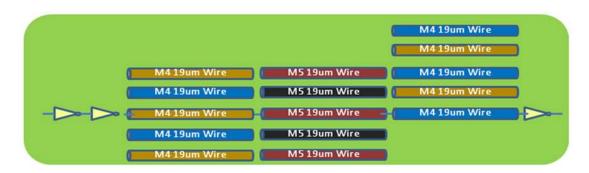

| 4.11 | Three Segment Interconnect Structure #1                                       | 32 |

| 4.12 | Three Segment Interconnect Structure #2                                       | 32 |

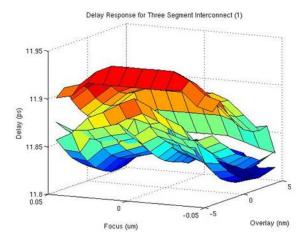

| 4.13 | Delay Response for Three Segment Interconnect Structure #1                    | 32 |

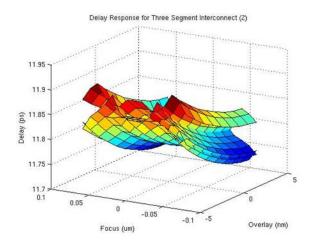

| 4.14 | Delay Response for Three Segment Interconnect Structure #2                    | 33 |

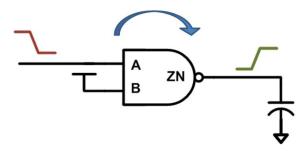

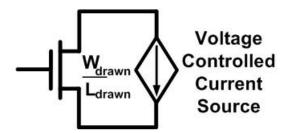

| 5.1  | Signal Propagation of a 2 Input NAND Gate from Input A to Output ZN           | 35 |

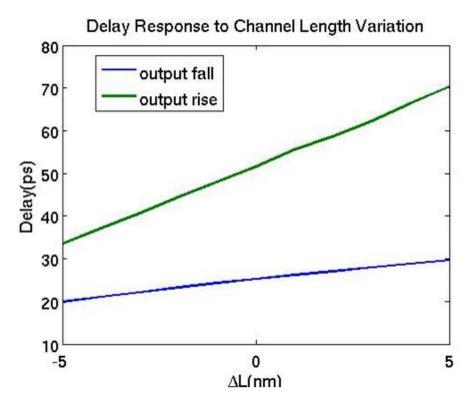

| 5.2  | Delay Response of a Minimum Sized Inverter to Systemic Changes in Channel     |    |

|      | Length L                                                                      | 36 |

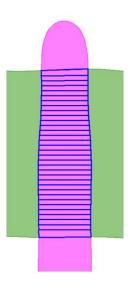

| 5.3  | Transistor Slicing Example                                                    | 38 |

| 5.4  | Accurate Table Lookup Based Device Model                                      | 39 |

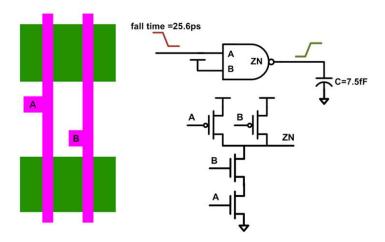

| 5.5  | NAND2 Layout and Circuit Schematic                                            | 40 |

| 5.6  | Propagation Delay Response to Poly Focus Exposure (FE) Variations with 9 Term |    |

|      | Bossung Model Fit                                                             | 41 |

| 5.7  | Propagation Delay Response to Poly and Active FE Variations                   | 41 |

| 5.8  | Second Layout Context for NAND2 Timing Characterization                       | 42 |

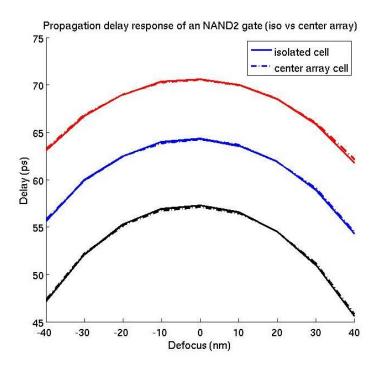

| 5.9  | NAND2 Propagation Delay Response to Poly FE Variations for 2 Layout Contexts  | 43 |

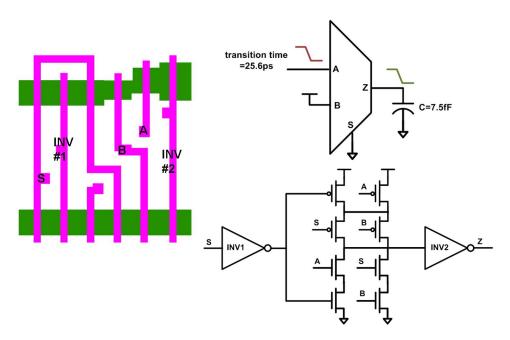

| 6.1  | MUX2 Layout and Circuit Schematic                                            | 47 |

|------|------------------------------------------------------------------------------|----|

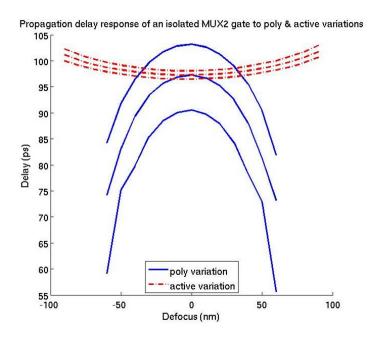

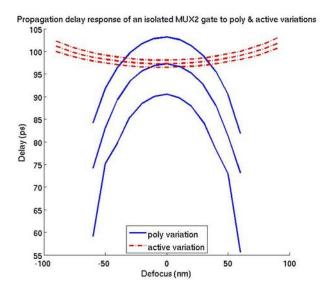

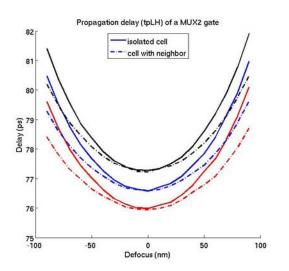

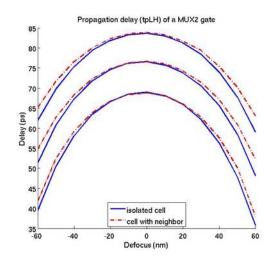

| 6.2  | Propagation Delay Response to Poly and Active FE Variations                  | 48 |

| 6.3  | Poly and Active Misalignment Variations                                      | 49 |

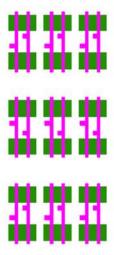

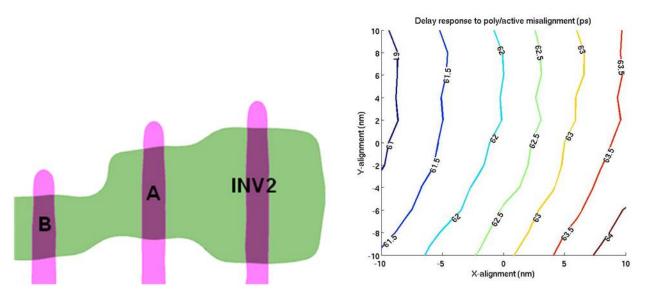

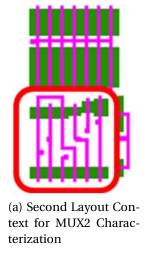

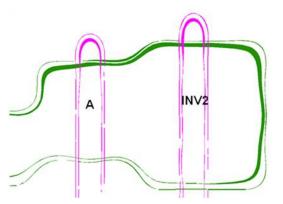

| 6.4  | MUX2 Layout Context                                                          | 49 |

| 6.5  | MUX2 Layout Proximity Effect                                                 | 50 |

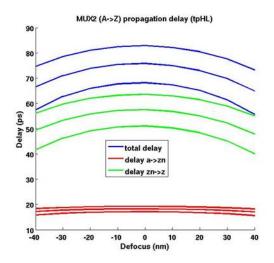

| 6.6  | Delay Components of MUX2 Cell                                                | 51 |

| 6.7  | NAND2 Power Characterization                                                 | 52 |

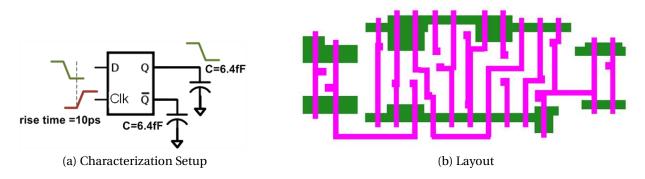

| 6.8  | D Flip Flop (DFF_X1) Cell                                                    | 52 |

| 6.9  | D Flip Flop Sequential Cell Timing Characterization                          | 53 |

| 7.1  | 11 Stage Ring Oscillator                                                     | 55 |

| 7.2  | Variability Aware Compact Modeling for Inverter Cell                         | 55 |

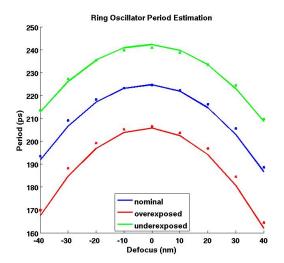

| 7.3  | Ring Oscillator Period Estimation                                            | 56 |

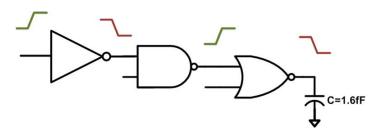

| 7.4  | Three Logic Depth Circuit                                                    | 56 |

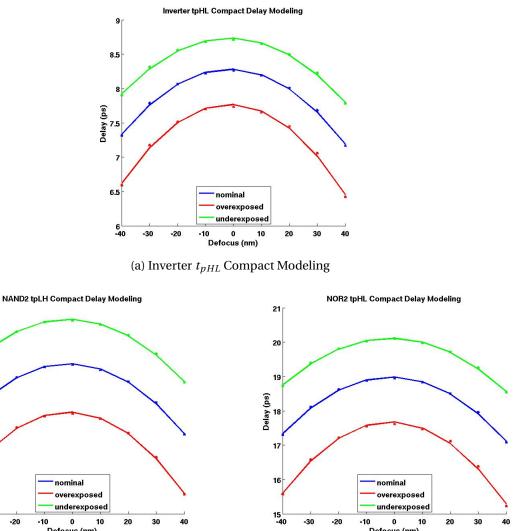

| 7.5  | Variability Aware Compact Modeling for Cells in Circuit Path                 | 57 |

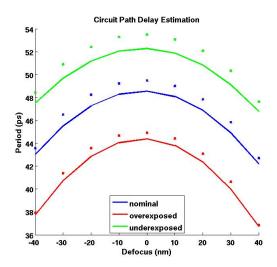

| 7.6  | Circuit Path Delay Estimation                                                | 58 |

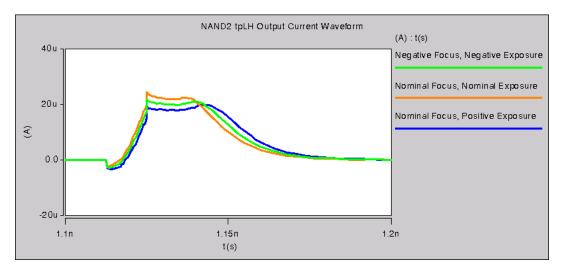

| 7.7  | NAND2 tpLH Output Current Waveform                                           | 59 |

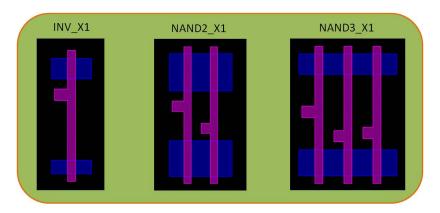

| 7.8  | Cell Layouts                                                                 | 60 |

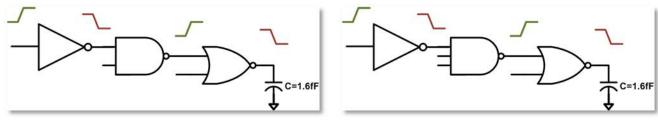

| 7.9  | Cell Swapping Circuit Scenarios                                              | 62 |

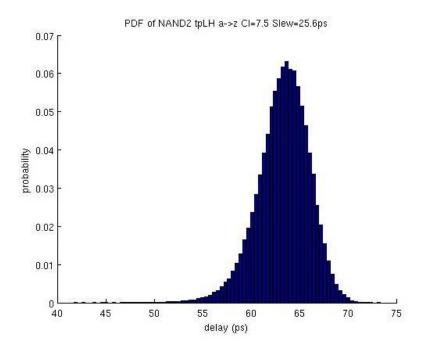

| 7.10 | NAND2 Probability Distribution Function                                      | 63 |

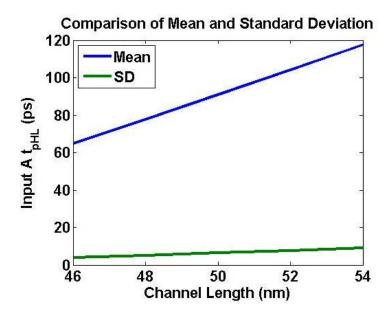

|      | Mean and Standard Deviation of NAND2 Delay (Geometrical Biasing) with 10,000 |    |

|      | Monte Carlo $V_T$ simulations                                                | 65 |

| 7.12 | NAND2 Delay Results (SCVC) with 300 Monte Carlo $V_T$ simulations            | 66 |

#### Acknowledgments

When I first arrived at UC Berkeley in August 2005, I had very limited research experience underneath my belt. I am indebted to Professor Andrew Neureuther, my primary research advisor, for changing this. Through these many years of kind patience and mentorship, he imparted crucial skills that permitted me to grow into a proficient researcher and forge my own paths.

One of my earliest memories in my graduate career was attending my first research conference with Professor Neureuther. I was seated next to Professor Neureuther during some of the technical sessions, and he gladly answered my questions and provided his unique insight into the highs and lows of each presented paper.

Experiences like these recurred throughout my time as a graduate student at UC Berkeley. I continued attending different types of research events to present my work, increase my knowledge base, and network with fellow researchers in my fields of interest. Many of the organizations sponsoring these events have provided financial support for my research, and I am grateful for their efforts. These include the FLCC, IMPACT, SRC, UC Discovery, SPIE, and OSA organizations. Special thanks to Professors Neureuther and Poolla for leading the intercampus FLCC and IMPACT grants that advance semiconductor research through the support of graduate students like myself.

Semiconductor Research Corporation (SRC) deserves special acknowledgement for providing additional financial and technical support. My research was partially funded by SRC Grant #1443. SRC and IBM also jointly provided nearly three years of full financial support by naming me as an IBM/SRC Graduate Fellow. I particularly enjoyed attending the annual SRC TECH-CON conferences, where SRC alumni, researchers, and faculty gather to discussing existing research and exchange ideas in a free flowing fashion.

I am grateful for my network of industrial contacts who have provided technical support and feedback during my graduate career. Thanks to Nevine Malek, Reha Bafrali, Everett Lee, and Sushil Padiyar for introducing me to lithography and OPC. Thanks to Tom Arns, Tom Lin, Yuri Apanovich, and Weiqing Guo for providing insight into CAD physical design methodologies. Thanks to Will Conley and Emmanuel Drege for providing advice on post-graduate careers. Thanks to Sani Nassif and Frank Liu for providing annual feedback on my research direction. Thanks to Luigi Capodieci for being a strong fellow advocate of design and manufacturing integration. Thanks to Supriya Madan and Yung-Ching Wu for sharing their special expertise on physical design methodologies. Thanks to Kenji Yamazoe for explaining lithography fundamentals.

My time in the Neureuther research group overlapped with a number of other graduate researchers: Greg McIntyre, Dan Ceperley, Wojtek Poppe, Juliet Rubinstein, Marshal Miller, Chris Clifford and Lynn Wang. Together, we had many fun times, some of which included attending post-conference corporate-hosted events and networking with former Neureuther students. In addition, most of us were involved in the PhotoBears student organization, which promoted interaction with the optics-related research groups of Professors Wu and Chang-Hasnain. These events often provided a welcome distraction from our usual hard-working graduate research routines.

Special thanks to Cooper Levy, who I took under my wing as an undergraduate researcher as part of a unique SRC outreach program. It was my pleasure to mentor Cooper and show him what I wished I had known starting out as a graduate student. Very quickly, he started performing at the level of a graduate researcher by performing advanced technical studies and analyses, some of which are described here in this dissertation.

Writing this dissertation turned out to be a bigger challenge than I had originally anticipated. My friends Jingwen Ouyang and Amiee Ho deserve special recognition for their continued encouragement and welcome distractions during periods where it was difficult to get writing done. Thank you for your friendship; I will forever appreciate your support during this time.

Lastly, I could not have succeeded without the unwavering support of my family, who encouraged me to embark on this Ph.D. path. Thank you Mom, Dad, Terence, and Bernard, for your continued support and love. You believed in me, knowing that I could accomplish what I had set out to do. Your undying faith in me allowed me to succeed as a Ph.D. researcher and become the person I am today.

## Chapter 1

## Introduction

#### 1.1 Motivation

Semiconductors are ubiquitous in modern society. Computing devices, mobile phones, cameras, digital memories, automobile sensors, and traffic light controllers are a small subset of components that incorporate semiconductor devices known as transistors. These transistors are carefully designed and arranged to form integrated circuits that process and transmit electronic signals within a semiconductor chip. In 1965, Gordon Moore made an astute observation that the transistor density in a chip doubles every two years, and theorized that this trend would continue [26]. This theory was later known as Moore's Law, and has been a strong driver of semiconductor technology scaling to date. The doubling of transistor density every two years has traditionally provided improvements in transistor performance and reductions in manufacturing costs.

Today, there are thousands of steps needed to develop a semiconductor chip for use in an end product. Circuit designers carefully design robust integrated circuits that meet performance targets and are ideally immune to manufacturing nonidealities. These designs are handed off to a manufacturing facility for fabrication. After fabrication, each chip is electrically tested to ensure acceptable circuit performance. Then the wafer is diced up to separate all the individual chips, and each chip is packaged so it can be incorporated into a bigger electronic system. For certain specialized chips, software interfaces are also developed to access the hardware capabilities of the chip. Post-packaging hardware and software testing might reveal certain flaws or bugs in the circuit performance that require a revision in integrated circuit design, process technology or a software workaround.

The successful development of a semiconductor chip requires close interaction between all the stakeholders in this complex process. Circuit designers must be aware of the potential manufacturing issues that affect design performance. Process technologists working in the fabrication facilities must understand how their optimizations affect design performance. Both circuit designers and process technologists must work with the testing teams to root cause any issues identified from post-fabrication testing. Should there be any bugs or flaws in functionality, all parties, including software and testing teams, need to come together to determine the appropriate fix.

Aggressive technology scaling in accordance with Moore's Law leads to additional challenges in this semiconductor development ecosystem. Process technologies no longer scale as easily as before, but innovative engineering solutions permit extending the lifetimes of existing process technologies. However, as device sizes become smaller and smaller, nanometer scale process non-idealities begin to affect circuit performance. Consequently, traditional design methodologies no longer accurately capture circuit performance. These process non-idealities must be understood, captured, and incorporated in circuit analysis, requiring tight collaboration between circuit designers and process technologists. The existing rate of technology scaling cannot be sustained with existing design and process paradigms, requiring new innovative methods to handle the complexities of semiconductor development in the deep sub micron regime.

## 1.2 Dissertation Organization

Developing solutions that address manufacturing complexities requires a broad understanding into key areas of semiconductor development. Gone are the days where expertise in a single area is sufficient. Even so, gaining expertise in multiple areas is difficult due to the enormous depth that can be developed in any single area. For this reason, there are many novel research solutions that address design and manufacturing complexity, but few are transferred to production semiconductor development due to their narrow scopes and limited applicability.

This dissertation addresses future-generation challenges in semiconductor development by developing solutions that incorporate lithography variability in design methodologies. It is extremely challenging to develop solutions that transcend design and process boundaries, as there has historically been limited information sharing between the two. In light of this, background in both of these areas is provided in Chapter 2. Starting with a process perspective, key physical causes of lithography variability are described. A brief overview of physical design methodologies is provided, leading to exploration of traditional corner based design methods that ensure design robustness to process variability. The chapter continues with a survey on recently introduced strategies that address lithography variability, followed by a discussion of the opportunity to incorporate lithography variability analysis at higher stages of design implementation, through the use of compact modeling techniques. These techniques compress lithography variability data into compact models that contain a limited number of process dependent parameters and can be quickly assessed with little time, taking fractions of a second to assess for any combination of input parameters.

Chapter 3 centers around the approach taken to create lithography variability aware compact models appropriate for use in physical design modules. The speed, compactness, and compatability of these models with existing design techniques allow designers to make appropriate tradeoffs between lithography variability and other performance metrics. Developing these models requires new analytical techniques that combine different existing design automation tools to transform lithography variability into electrical circuit variability. Still, integrating these tools is far from trivial due to proprietary data formats and different input/output requirements for each tools. Therefore, it is essential to develop integrated frameworks to per-

form lithography aware circuit analysis for the purpose of creating the desired compact models. The three frameworks developed for such analysis are detailed in this chapter.

The Interconnect Variability Characterization (IVC) framework is used to investigate interconnect level lithography variations in Chapter 4. Instead of utilizing an official process design kit (PDK) that restricts publication of data derived from PDK access, custom generated PDKs are utilized to perform studies and obtain results that can be openly published. The IVC framework is applied to a one dimensional repeater circuit with differing layout topologies under varying focus and exposure conditions at the 90nm node. Similar analysis is performed at the 32nm node, where double patterning is assumed and misalignment variability is introduced. For both technologies, the delay responses can be visualized on a three dimensional plot and are shown to be easily modeled using a 12 term second order polynomial equation. Designers can use these models to obtain insight into the degree of delay variability associated with specific circuit topologies and interconnect routing scenarios.

Chapter 5 explores lithography variability at the cell level using the Standard Cell Variability Characterization (SCVC) framework, the FreePDK45 design kit, and the Nangate 45nm Open Cell Library. One approach to create variability aware timing models utilizes geometrical biasing, which upsizes or downsizes the ideal transistor dimensions within a cell. Using this method, delay sensitivity tables are created to complement existing delay tables in standard cell libraries. The second approach utilizes lithography contour analysis to more precisely account for typical non-uniform transistor dimensions caused by lithography variations. With this approach, the timing performance in the presence of focus and exposure variations can be visualized in an electrical process window fit with a Bossung like compact model with a fraction of a picosecond accuracy. Chapter 6 illustrates that the SCVC framework is extensible for the more advanced topics of misalignment and layout proximity effects. Further studies on multi-stage combinational cells and sequential cells illustrate that the same compact model can be used to model advanced timing and power performance in the presence of lithographic variability.

Chapter 7 ties the cell level compact models developed in Chapters 5 and 6 into physical design methodologies through path level variability analysis. The first circuit path explored is an 11-stage ring oscillator. With pre-characterized compact models for an inverter cell, the ring oscillator period can be estimated for 27 different focus and exposure combinations to an accuracy of 1% in approximately 1/5 of a second. For a three stage combinational circuit path, an estimate of circuit path delay can be obtained across the same process window to an accuracy of 0.7%, with a speedup of over 50,000 compared to post-layout lithography aware circuit analysis. These immense speedups are achieved by moving computationally intensive lithography aware circuit analysis into cell level pre-characterized libraries.

While the ability to perform fast variability aware path level performance estimation is useful, the true power of these compact models lies in enabling design methodologies to compensate for lithography variations. This is demonstrated through manual analysis of a three stage combinational circuit path, where one of the cells is swapped out for another cell with less performance sensitivity to lithography variability at the expense of additional power. With additional automation, tradeoffs between lithography variability and other design metrics can be quickly assessed in physical design methodologies, allowing for lithography variability to be

included in circuit optimization.

## 1.3 Unique Dissertation Contributions

This dissertation results from multiple years of research dedicated towards developing solutions that address the complexity of designing digital circuits in the presence of variability. Most of the frameworks, studies, and results detailed in this dissertation, unless mentioned otherwise, are my own original works, developed under the mentorship of Professor Andrew Neureuther. Many thanks to Cooper Levy who, under my direct guidance, utilized my SCVC framework to perform lithography aware variability analysis on sequential cell timing performance and combinational cell power consumption. Cooper was also instrumental in running Monte Carlo simulations to model random dopant fluctuations, which led to the discovery that the distribution of cell performance is a function of lithography process parameters.

There are several original contributions in this dissertation that I feel are worth highlighting. I am proud of developing the IVC and SCVC frameworks, which integrate existing analysis techniques in a novel fashion to investigate the electrical impact of lithography process variations. I improved upon an existing contour based device analysis technique, boosting the accuracy of such analysis by replacing coarse transistor performance approximations with a more accurate table based lookup method that is detailed in Section 5.4.3. Recognizing that the cell level behavior in response to lithography focus and exposure variations follows a well behaved and very recognizable pattern, I captured the cell level electrical behavior in a compact model with little loss in accuracy. Later, I demonstrated that these cell level compact models, when combined with a specific circuit topology and generic timing calculations, permit path level variability aware circuit analysis at fast speeds with a slight tradeoff in simulation accuracy.

## **Chapter 2**

## **Background**

## 2.1 Lithography Variability

Fabricating a modern integrated circuit involves a myriad of wafer processing steps, including oxidation, ion implantation, diffusion, etching, lithography, chemical-mechanical polishing, annealing, and electroplating. As with any manufacturing system, there is some amount of uncontrollable process variability in each of these steps. One of the largest sources of variability is optical lithography, which is used to transfer patterns pre-defined on a mask to individual dies on the wafer. This mask transfer process is performed multiple times before fabrication is complete, to define front end layers and back end layers. Front end layers define device performance, and include well implant, active, polysilicon, and threshold implant layers. Back end layers affect interconnect performance, and include up to eleven metal and eleven via layers.

In 2010, state of the art process technologies utilize 193nm deep ultraviolet (DUV) optical projection lithography to define features on a silicon wafer. To meet the demands of shrinking feature sizes, process technology engineers create unique engineering solutions to extend the lifetime of 193nm DUV lithography. Since the incorporation of 193nm DUV lithography technology in semiconductor manufacturing, the standard lithography process has been refined by increasing the numerical aperture, changing the illumination source, moving to immersion lithography, using phase shift masks, and optical proximity correction (OPC) [39]. Each of these steps adds additional complexity to the process, with the benefit of extending the lifetime of 193nm DUV lithography.

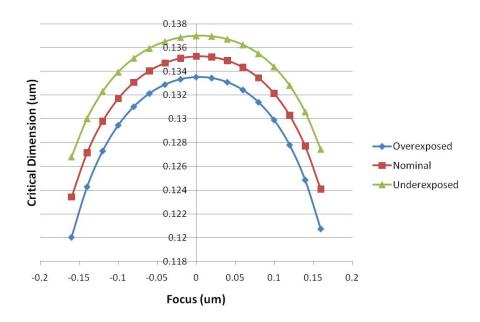

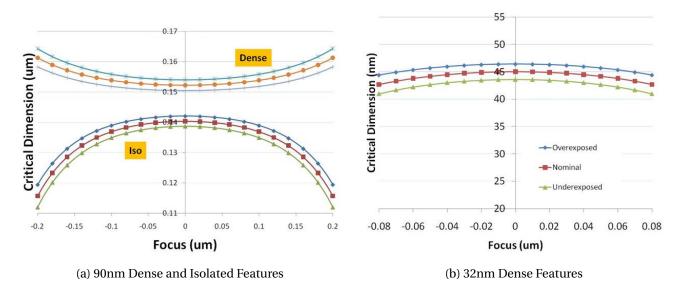

As process engineers strive to push 193nm DUV lithography to its limits, controlling lithography variability is becoming a top priority. State of the art process technologies utilize step and scan lithography systems where the slit and the wafer stage are continuously moving. These moving parts create position dependent focus and exposure variations on all processed wafers. To characterize the focus exposure process window, a focus exposure matrix is commonly used [27]. This is achieved by exposing the different dies on a wafer in a systematically varying fashion, with different focus and exposure conditions for each die. Dimensional measurements of a one dimensional test structure are taken at the same location for each die to create a Bossung plot which depicts how the measured critical dimension changes under different focus and exposure conditions [6]. An example Bossung plot obtained through lithography simulation is

Figure 2.1: Sample Bossung Plot

#### shown in Figure 2.1.

These focus and exposure variations, along with other lithography variations, distort the contours transferred from the mask patterns and ultimately alter the performance characteristics at the device, interconnect, circuit, and system levels. The behavior of the Bossung plot indicates that the identical layout feature resolves on wafer differently under different process conditions. In addition, the nature of patterns in the local proximity of the feature will affect its printability. Experimental data collected from a 90nm test wafer indicates that the presence of a neighboring dummy feature on the polysilicon layer affects ring oscillator performance, shifting the ring oscillator frequency by over 10% percent [30].

Lithography at the 32nm and 22nm nodes becomes even more complex, as select critical layers can no longer be patterned with a single mask due to small feature sizes and tight pitches. Instead, multiple patterning steps will be used to pattern a single layer, thus increasing process complexity. This opens up another source of variability, as neighboring features may be defined with separate masks each with different process conditions and misalignment.

One of the most highly anticipated replacements for 193nm DUV lithography is 13.5nm extreme ultraviolet (EUV) lithography, currently under development. It is expected that EUV lithography will be used at the 16nm node and below. Even so, EUV lithography will quickly enter the regime of sub-wavelength lithography, and the complexity of the process technology combined with continually shrinking feature sizes indicates that similar process non-idealities for EUV lithography will be observed as with 193nm DUV lithography.

## 2.2 Physical Design Methodologies

While process technologists strive to minimize lithography induced variability through process engineering and optimization, circuit designers strive to create robust designs that function across typically expected ranges of such variability. However, making changes in the design is not as simple as changing a design parameter and then resimulating the design to validate that it meets all the specifications. The latest computer chips today contain over one billion transistors, and many complex design methodologies are utilized to achieve the final design.

These design methodologies include custom design, analog and mixed signal (AMS) design, and physical design. The first two design methodologies are used to create design blocks with a limited number of transistors, and each transistor is tuned to achieve the final design. Due to the small number of transistors, simulation tools that model each transistor's behavior are used to characterize the circuit performance. In contrast, physical design methodologies integrate cells to achieve the circuit design performance. The number of cells in any one block can be in the order of hundreds of thousands of cells, and each cell generally contains multiple transistors.

To realize such large designs, physical design methodologies must handle the intricate process of cell level integration to meet block level cell specifications. This is achieved through abstraction of transistor level performance into cell level models, which are developed through the same transistor level circuit simulation methods used for custom design and AMS design. These cell level performance models can then be combined with behavioral and layout models for analysis in each step of physical design.

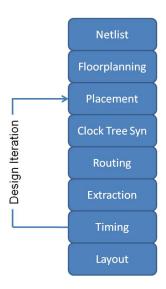

A high level overview of physical design methodologies is shown in Figure 2.2. First, a netlist or circuit schematic is generated from the desired circuit functionality. Then, a floorplan is created to define the physical layout area in which cells are allowed to be placed. Placement tools interpret the netlist and place cells in locations that are legalized, as defined during the previous stage. Clock tree synthesis is then used to route interconnect wires that distribute the clock signal evenly across the chip. Routing tools then connect the pins of each cell using interconnect wires that minimize wirelength and reduce delay. Interconnect extraction is used to determine the parasitic resistance and capacitance values along the chip. Finally, static timing analysis is performed to ensure the delays for all paths meet design specifications.

Though these modules each seem to be very self contained, there are many customizations in each module, and a single change can cause profound effects that ripple through other stages in the design. For example, an attempt might be made to minimize power in a block. One solution is to change the transistor threshold voltages of all cells in non-critical paths. However, some of these non-critical paths might turn into critical paths with timing violations, and so to address this one might increase the driving strength of problematic cells by swapping them with similar cells with larger transistor widths. The new cell might be bigger than the old cell, and thus the placement and routing of all other cells in the design might be modified. Ultimately, the designer must developed a customized design methodology specific to each block to meet all performance specifications. This is a very iterative process that involves many steps and customizations to achieve design closure.

Figure 2.2: High Level Overview of Physical Design Methodologies

## 2.3 Modeling Variability in Design

No matter which design methodology is used to realize a design, all the circuits within a design are simulated under different conditions to ensure design robustness. This provides a design guardband against expected values of process variability. The types of conditions that are chosen for circuit simulation depend on the level of analysis. Traditionally, these conditions are chosen at the corners of the process window and between three and nine different corners are used for simulation analysis.

In the case of transistor level circuit simulation, transistor models are provided for a range of process characteristics. Usually two transistor models are used for circuit analysis, one for NMOS transistors and the other for PMOS transistors [15]. Each model contains three different options to denote the transistor performance: slow, typical, and fast. A two letter combination is used to denote one corner case simulation condition. The first letter corresponds to the NMOS compact model and the second letter corresponds to the PMOS compact model. For example, a SF corner case simulation indicates a simulation performed using slow NMOS and fast PMOS transistors. With a two transistor models per simulation, there are nine possible corner cases: SS, ST, SF, TS, TT, TF, FS, FT, FF.

The corners for the cell level circuit simulation associated with physical design are different in nature. Instead of choosing corners corresponding to transistor performance, the corners are based on three factors: process, voltage, and temperature (PVT) [16]. The process conditions are identical to those used for transistor level circuit simulation; typically only SS, TT, and FF are used. There are three corner voltages used; for a design at a nominal 1.1V technology, 0.95V and 1.25V are the other two corners. There are also three corner temperatures: 0°C, 25°C, and 125°C. Using these corner values for process, voltage, and temperature, three datasets are created corresponding to the slowest, typical, and fastest PVT corners. For example, the slow PVT corner combines the SS process, 125°C temperature, and 0.95V voltage. Physical design methodologies utilize all three datasets to achieve a design robust to circuit and process vari-

ability.

The PVT corners for physical design involve analysis at the cell level, which model effects at the active, poly and contact layers. Proper circuit path analysis requires accounting for layout induced parasitic resistances and capacitances for all metal interconnect layers. Since the performance of a circuit is also dependent on the RC load of the interconnect wires, it is not surprising that corners are also used for interconnect analysis. There are usually at least five corners that are used in analysis: nominal, worst case capacitance, worst case delay, best case capacitance, and best case delay [17]. Each of these corners consist of some combination of best and worst case scenarios for resistance and capacitance for all metal layers.

For complete analysis of a silicon chip, some combination of corner case design analysis at all levels of abstraction must be performed. Analog blocks are simulated using slow and fast transistor models. Cell based blocks are simulated at different PVT corners. And for proper interconnect analysis, parasitic extraction is performed at different RC corners. For older technologies, it used to be the case that corner based analysis was sufficient to ensure a robust design. However, the physical phenomena associated with shrinking today's transistor sizes even smaller are becoming more significant. It continues to be an ongoing debate whether corner based design sufficiently accounts for process variability. Though it is possible to design circuits that pass all corner based analysis checks, certain unique combinations of process variations can still cause a real circuit failure that is undetected by corner case analysis.

## 2.4 Coping with Lithography Variability

The increasing challenges of semiconductor manufacturing at shrinking technology nodes have increased complexity in both process and design engineering, leading to closer design and process technology collaboration. In response to these challenges, new design strategies have been developed to model, mitigate, and control the impact of lithography variability.

### 2.4.1 Strategy #1: Avoid Poor Layouts

The conventional interface between semiconductor manufacturing and design is the design rule manual. The design rule manual is created through collaboration between manufacturing and design teams. Once the design rule manual is finalized, it serves as a contract that process technology will fabricate functional chips provided that the design meets all rules in the manual. Most of these rules are geometrical rules. Some rule examples include minimum distance between contacts and transistor gates, acceptable ranges of poly pitch, and metal-contact overlap distances.

Scaling at the same 193nm wavelength used in DUV lithography has made it increasingly difficult to print layouts permitted at earlier technology nodes. One strategy to combat this is to add additional rules to the design rule manual to restrict poor layouts from being incorporated into design. However, many poorly printing layouts are two dimensional in nature, and in recent years, attempts to restrict these specific layouts have led to a drastic increase in the number of design rules in the manual. To complement standard design rule checking tools, new algorithms have been developed to identify and classify problematic layout patterns using

pattern matching techniques [18, 20, 41]. These algorithms are part of a class of tools called physical verification tools that are run on layouts to ensure that they meet design rules and match the circuit intent.

#### 2.4.2 Strategy #2: Layouts Regularization

Another technique being used to improve printability is to restrict the possible layout patterns even further. In older technologies, poly features are allowed to run in both horizontal and vertical dimensions. However, at the 32nm technology node and beyond, most design kits only allow unidirectional poly running in a single direction. This reduces the amount of geometrical variation induced by lithography process variations, as well as allows unique off axis illumination sources to be used for poly printing.

There has also been effort at the cell level to co-optimize circuit performance and manufacturability. Starting off with printability friendly cell layouts increases the likelihood that the entire design will have reduced sensitivity to variability. One such approach derives cell layouts from a set of printability friendly patterns[22]. These cell layouts are known as regular fabrics, and a new set of physical implementation tools is created to leverage the regularity of the layouts. For a sample 65nm processor design, the usage of regular fabrics comes at a 6.7% area penalty with an estimated 6.8% increase in the number of good dies per wafer.

#### 2.4.3 Strategy #3: Statistical Design Analysis

An increasing number of process variability sources each significantly impacting circuit performance has led to an increase in the number of corners used in design analysis. However, analysis at these corners may not be totally comprehensive and may even be overly conservative. An alternative to corner based analysis is the use of statistical design analysis. The most prominent example of statistical analysis in physical design is in assessing performance of critical timing paths through Statistical Timing Analysis (SSTA).

Instead of calculating absolute delays for every process corner, SSTA propagates a distribution of signal arrival times at each node in the circuit path. Advanced SSTA algorithms can accurately predict bounds for statistical timing procedures with linear run time complexity[8, 3]. These bounds are calculated using provided confidence intervals, and the accuracy of these results is dependent on accurate models for process variations. A reputable commercial implementation of SSTA utilizes distributions in transistor channel length to model inter and intra die process variations. Obtaining accurate models for SSTA algorithms is an expensive process, requiring experimental characterization that create models which may no longer represent the often changing process technology.

## 2.4.4 Strategy #4: Contour Based Compact Transistor Modeling

At smaller technology nodes, wafer level contour profiles no longer produce rectangular transistors with uniform channel widths and lengths [21, 28]. Both active and poly corner rounding begin to encroach upon the transistor gate region, defined as the intersection of poly

geometries and active geometries. Additionally, lithography induced line edge roughness creates non-uniform channel lengths across the width of each device.

These non-uniform transistors are typically modeled by spatially subdividing each transistor contour into fine segments, each with its own effective gate width and gate length [33, 40, 7, 37]. These transistor segments are then simulated to determine the new performance of the transistor. Each original transistor in the circuit simulation is then replaced with a set of transistors in parallel that represent the new transistor performance. These models are validated against rigorous device simulation results.

#### 2.4.5 Strategy #5: Lithography Simulation Speedups

Lithography simulation is inherently a time consuming process. However, some methods have been developed that speed up this analysis with only a slight degradation in accuracy. A Pattern Matching engine was developed to allow quick assessment of lateral electrical field spillover effects based on a convolution kernel and full chip layout [19]. Using physics based kernel convolution models, the intensity deviation from focus and coma lens aberrations can be modeled accurately with a  $\mathbb{R}^2$  value of greater than 0.98 [25]. This intensity deviation can be translated to edge movement with a lithography simulation at the nominal process condition. Thus the geometrical impact of lithographic aberrations can be captured through fast kernel convolutions and one nominal lithography simulation.

## 2.5 Summary

The complexity of process and design engineering increases with smaller features sizes at every new technology node. Process engineers dedicate their efforts to tune and optimize the process to achieve performance targets and limit variability, while design engineers synthesize circuits that are robust to an acceptable range of process variability. New nanometer level effects arise from patterning smaller features using the same 193nm wavelength DUV technology. To mitigate these nanometer level effects, solutions have been developed that restrict problematic layouts with high variability and provide new design analysis techniques to account for process variability.

While these solutions have enabled continued scaling to the 45nm node and beyond, there are still areas for improvement in process and design co-optimization. Existing lithography aware analysis techniques, including those described in Section 2.4.4, require a layout to combine lithography variability with circuit performance. This may be permissible for designs with tens or hundreds of transistors due to small layout sizes, but is too rigorous for large scale layouts associated with physical design.

In the case of physical design, the design engineer is tasked with running the whole suite of tools illustrated in Figure 2.2 and must artfully tweak settings for each step to achieve desired performance targets. Existing lithography aware analysis techniques can only be run at the layout level when the design is mostly complete, and the results provide very limited insight to the designer about modifications needed to reduce variability in the circuit. Therefore analysis at the layout level is computationally expensive with very little benefit.

Clearly there is much opportunity to abstract lithography variability upstream into earlier stages of the design flow such as placement and routing. By making quantitative data about lithography variability available at higher levels of abstraction, proper tradeoffs between lithography variability and other design metrics can be achieved at earlier stages in the design, allowing for a more robust design. The abstraction of lithography variability is achieved by building upon existing design and lithography analysis techniques, and the details of this approach are detailed in Chapter 3.

## **Chapter 3**

## **Tools for Circuit Variability Analysis**

#### 3.1 Introduction

This chapter presents an approach to enable variability aware circuit analysis that transcends the boundaries between process technology and circuit design. Software requirements and functionality for tools in each of these areas are quite different in nature. For example, the speed, flexibility, and accuracy of a tool used in process simulation may be completely different from what is needed in design implementation and analysis. In this chapter, we review existing coverage of electronic design automation (EDA) tools and highlight challenges in incorporating these tools in a lithography aware analysis flow. From these assessments, we identify opportunities to create specialized tools that abstract the impact of lithography process variability into physical design methodologies, and detail three key frameworks that are developed to support this purpose.

## 3.2 Existing Electronic Design Automation (EDA) Tools

The electronic design automation industry provides a spectrum of software tools to aid in the design and manufacturing of electronic systems. These tools can be categorized into different areas based on the desired application. In considering the impact of process variability on circuit analysis, the core areas of interest are technology computer aided design (TCAD) simulation tools, mask data preparation (MDP) tools, circuit simulation tools, and physical implementation tools.

#### 3.2.1 TCAD Simulation Tools

Of all the EDA tools covered in this chapter, TCAD simulation tools are by far the most rigorous in terms of accuracy and physics based modeling. The purpose of such tools is precise modeling of physical effects, often times at the atomistic level. Thus developers often prioritize accurate modeling over simulation speed, resulting in tools that are appropriate for the development of process technology. These TCAD tools can be sub-divided into two distinct areas: process modeling and device modeling. Process modeling tools simulate topological profiles

for specific processing steps that occur in semiconductor fabrication. Examples include optical imaging simulation, photoresist modeling, etch profile edge simulation, CMP thickness modeling, and optical waveguide modeling. Device modeling simulates the electrical characteristics of devices created through a sequence of process steps, modeling advanced device characteristics including carrier transport, electron tunneling, and strain.

#### 3.2.2 Mask Data Preparation Tools

After the design of a chip is complete, the entire design layout is sent to a tapeout team that post-processes the layout to meet manufacturability criteria. This tapeout process includes layout scaling, fracturing, metal fill, manufacturability checking, and optical proximity correction (OPC). By far the most complex step is OPC, where the mask layout is modified by perturbing polygon edges to obtain the desired silicon contour on the wafer. This involves an iterative process with a lithography simulation after each step of layout perturbation. Since running a TCAD level optical imaging simulation tool on full-chip layouts would be far too time intensive, the lithography simulation used in OPC relies on a faster algorithm that incorporates a set of convolution kernels as an approximation to rigorous lithography simulation. Even with this approximation, performing OPC on a full chip microprocessor design may take on the order of days to run, with multiple machines and computer processors.

#### 3.2.3 Circuit Simulation Tools

Circuit simulation tools allow the designer to study the DC, AC, and transient behavior of circuits. The industry standard tool for circuit simulation is the Simulation Program with Integrated Circuit Emphasis (SPICE), which incorporates equation formulation, solutions to linear and nonlinear equations, and numerical integration [29]. Compact device models are used in conjunction with SPICE to model advanced device behavior. One prominent example of such models is the Berkeley Short-Chanel IGFET Model (BSIM), which contains hundreds of parameters to model device behavior [35]. These compact models are calibrated with both TCAD simulations and measured data, and are considered extremely accurate with modeling of advanced physical effects including short channel effects, temperature, layout dependent parasitics, and strain.

## 3.2.4 Physical Implementation Tools

Physical implementation tools are utilized to realize very large scale designs. Instead of striving to achieve optimal circuit performance through the tuning of each transistor, the designer is tasked with achieving area, power, and performance targets through the selection, placement, and routing of pre-designed cells within a large block. The basic building blocks of these designs are the individual cells, which contain up to 20 transistors. Abstract timing and power models for each cell are developed using standard cell characterization tools. Placement algorithms allow cells to be placed in rows of standard cells and optimized for small area and routability. Routing algorithms connect the pins of each cell to other cells or the ports of the

design. These tools are utilized to create designs with millions of transistors, without having to simulate each circuit path with standard circuit simulation tools, which would otherwise be infeasible due to time constraints.

## 3.3 Lithography Aware Circuit Analysis

To model the circuit level impact of lithography variations, process variability must be transformed to circuit performance. The conventional approach begins with a layout level lithography simulation, performed on the layers of interest. The resulting lithography contours are mapped to new device characteristics or parasitics through compact transistor models, such as those described in Section 2.4.4. The lithography aware circuit performance can be obtained through a subsequent circuit simulation performed using the updated device or parasitic characteristics.

There are two disadvantages to this approach. First, this analysis can only be performed after the layout is complete. Any subsequent layout change caused by a new placement or routing will modify the circuit topology and thus negate the results of lithography aware analysis. Secondly, this analysis is extremely costly to perform. To perform analysis at one lithography process condition, a very time consuming process and circuit simulation must be done. In the time it takes to do perform this analysis, another iteration of placement and routing could have been performed. Furthermore, this type of analysis should be performed at not only one process condition but multiple process points to provide feedback to the designer about circuit variability.

## 3.4 Creating Variability Aware Analysis Models

Conventional post-layout lithography analysis does not scale. For large designs with over 100,000 cells, this analysis is prohibitively time intensive. Moreover, this analysis yields information about the variability in performance of certain critical paths, but provides no feedback or tradeoffs that can be used to balance lithography induced variability with other design metrics such as area, timing, power, nose, electromigration, and IR drop. Therefore, the goal of this dissertation was to create compact models of lithography variability that are compatible with existing cell based design flows and fast enough to be used in parallel with the physical implementation modules. The speed, compactness, and compatibility of these models allow designers and EDA tools to make the appropriate tradeoffs between lithography variability and other design metrics.

The primary challenge in the creation of these models is that there is no existing framework to study the impact of lithography variations on circuit performance. Industry grade EDA tools focus on core areas including TCAD simulation, mask data preparation, circuit simulation, and physical implementation. Each of these tools has proprietary formats and operates with different inputs and outputs, often times at different levels of abstraction. To address this challenge, a set of unique process and design information frameworks have been developed that allows for the transformation of process level effects to circuit level impact.

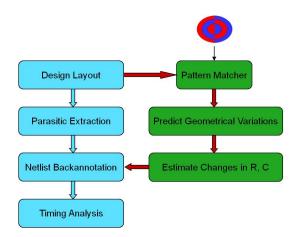

Figure 3.1: Process Variation Net Scanning Methodology

There are multiple considerations for the creation of compact variability models that we wish to create. These considerations change based on the actual application of these models. In general, a good model should be both fast and first-cut accurate, achieving the right balance of accuracy and runtime. Models should encapsulate variability with a flexible model that allows library size to scale efficiently, and should be easily incorporated into existing design methodologies.

## 3.5 Developed Methodologies

Three key frameworks have been developed that allow for the study of interaction between lithography variability and circuit performance. These frameworks integrate a wide range of tools across the EDA spectrum, including process simulators, device simulators, compact transistor models, circuit simulators, parasitic extraction tools, static timing analysis tools, and cell characterization tools.

### 3.5.1 Process Variation Net Scanning

Process Variation Net Scanning leverages the fast speed of pattern matching in conjunction with kernel convolution methods to obtain an accurate estimate of through focus lithography contours without simulations at multiple process points. The flow, as applied to interconnect level analysis, is demonstrated in Figure 3.1.

First, models similar to Kernel Convolution with Pattern Matching (KCPM) are applied to an existing layout to estimate changes in intensity at every point along the contour. Combined with a nominal lithography simulation which provides information about the image slope along the contour, the estimated change in contour can be predicted. From there, edge movements can be translated to geometrical variations in interconnect, and therefore estimated changes in parasitic resistance and capacitance. These estimated changes are back-annoted in the design netlist and are used to perform a new SPICE level timing analysis.

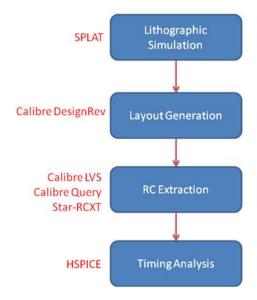

Figure 3.2: Interconnect Variability Characterization Methodology

This framework was applied to a 90nm digital design containing over 325,000 nets with an area of  $3.61mm^2$ , to study the impact of lithography coma variations in Metal 3 and defocus variations on Metal 4 [9]. KCPM results were obtained at every micron along straight interconnect wires, and those results are used to derive a new netlist with modified parasitics. A rerun of static timing analysis on the new netlist showed that the topmost critical paths have changed with new timing results. Runtime analysis of this methodology indicated that the speed of this KCPM approach can be made at least twice as fast as a comparable extraction run without the need for rigorous lithography simulation.

### 3.5.2 Interconnect Variability Characterization

Interconnect Variability Characterization combines process simulation, parasitic RC extraction, and SPICE level timing analysis to develop compact parameter interconnect timing models. Figure 3.2 depicts the methodology used to transform lithographic variations to delay variations.

First, lithographic simulation of a target pattern is performed across the process window. The response of critical dimensions across the process window is modeled, and a new rectangular layout with modified wire and space sizes is automatically generated. To model misalignment during double patterning, these wires are also shifted by an overlay factor. Then transistor level parasitic extraction is run to generate a netlist with extracted R and C parasitics. Finally, transient SPICE simulations are run for delay characterization.

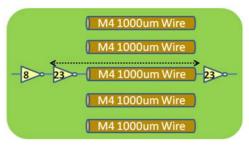

This framework is applied to one-dimensional repeater circuits to characterize the timing response to focus and exposure variations using single patterning and double patterning process technologies [11]. The delay responses of each homogenous interconnect structure are fit using an algebraic compact model containing 12 coefficients. The effects of advanced lithography structures are explored through the use of cascaded interconnect structures with the same

Figure 3.3: Standard Cell Variability Characterization Methodology

repeater circuit topology, and it is observed that the variations on each segment average out to reduce the overall delay variations. A through explanation of these studies is provided in Chapter 4.

#### 3.5.3 Standard Cell Variability Characterization

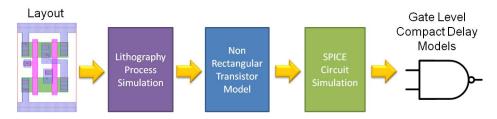

Standard Cell Variability Characterization combines existing non-rectangular transistor models and timing libraries to create a variability aware timing model. Figure 3.3 illustrates the methodology.

To begin, a layout context is generated for the cell under study. Then rigorous process simulation, including OPC and lithography simulation, is performed on the layout at multiple points within the process window. For each specific process condition, the contour of each transistor is extracted to generate a new device model that can be used for circuit simulation. Circuit simulation is performed using the new device models to obtain the delay response. Finally the delays are aggregated and used to fit cell level compact timing models that can be integrated in existing design flows.

This framework was applied to standard cells in the Nangate 45nm Open Cell Library to characterize cell level electrical performance in the presence of lithography variations, including focus and exposure [10]. Electrical data obtained through this framework showed that the timing response in the presence of focus and exposure variations can be fit with a nine term compact model that can be stored in existing standard cell timing libraries. Details on the basic development of this compact model are provided in Chapter 5, and the advanced exploration into complex cells and additional sources of lithographic variation is covered in Chapter 6. This framework is also used with a few modifications to explore lithography aware path level circuit analysis and tradeoffs in Chapter 7.

### 3.6 Summary

Conventional methods of analyzing the circuit level impact of lithography variations are not likely to be used in design-time analysis due to the burden of computational power and runtime. A more compact and abstract level of lithography aware circuit analysis is needed to provide relevant information to designers and design tools so that the appropriate tradeoffs between lithography variability and other circuit metrics can be performed. To accomplish this goal, models and tools across the EDA spectrum are leveraged to create unique process and

design information frameworks that facilitate the transformation of process data into circuit performance. Consequently, three key frameworks are developed that allow for fast analysis of lithography variability in the context of circuit performance.

## Chapter 4

## **Interconnect Variability Modeling**

#### 4.1 Introduction

Modern semiconductor chips contain as many as twelve layers of metal interconnect, each patterned with a separate mask and exposure step. Lithography induced process variations occur for each of these patterning layers. Traditional design methodologies guardband for these variations through corner case design and analysis. Design analysis of systematic lithography focus and exposure variations is not traditionally performed due to the extensive permutations of possible lithography variations for each level of interconnect, causing an explosion in the computational power needed for such analysis. Nonetheless, systematic lithography focus exposure variations will affect the dimension of wafer level features, ultimately affecting the circuit performance through changes in parasitic resistances and capacitances. In this chapter, we detail our studies of the circuit level impact of systematic lithography variability using the Interconnect Variability Characterization (IVC) framework, and discuss key observations of interconnect variability at the 90nm and 32nm technology nodes using a repeater circuit topology. For each of our studies, the circuit level response is then fit into a compact delay model that can be used to estimate the circuit level impact of process variations without the need for time consuming circuit simulations. Finally, we describe our efforts to extend the IVC framework that allows analysis of more complex interconnect scenarios.

## 4.2 Interconnect Delay

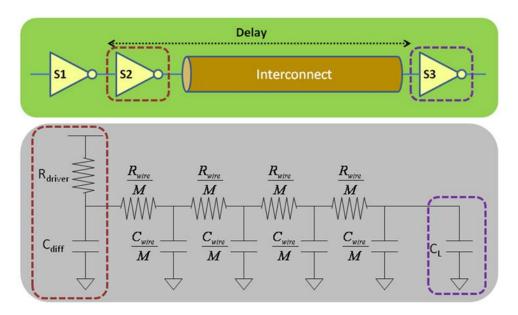

The total delay in a digital datapath can be decomposed into two components: the gate delay and the interconnect delay. These two quantities are not independent since the delay through the device is dependent on the load that it is driving. Thus when analyzing variations in physical interconnect layers, the effects of the source driver and load capacitance must be included for accurate analysis. Figure 4.1 shows the equivalent RC network for an inverter driving a load capacitance through an interconnect wire. The interconnect wire is modeled as a distributed RC network, and the resistance and capacitance of the driver, as well as the load capacitance, is included for accurate delay calculation.

Figure 4.1: Interconnect equivalent RC delay model

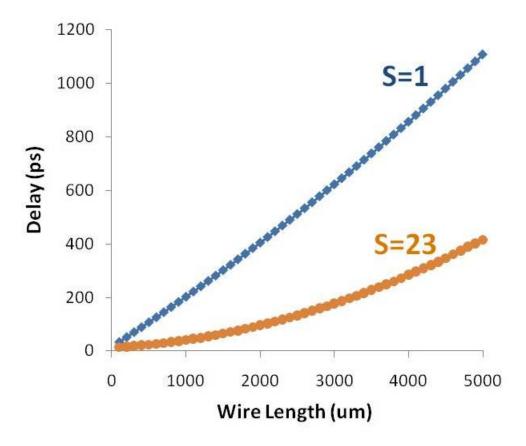

Figure 4.2: Delay as a function of length for driver size S

Figure 4.2 shows the characteristic response of the total delay as a function of length for two different driver sizes. There are two curves; one is linear and the other is quadratic with respect to length. The linear curve corresponds to the minimum sized device, which has a driver resistance of  $20k\Omega$ . The quadratic curve corresponds to a device of size 33, which has a driver resistance of  $0.25k\Omega$ . When the resistance of the driver is bigger than that of the wire, propagation delay increases linearly with the wire length [4]. In this mode of operation, the delay is dominated by delay through the device due to the limited amount of current provided by the driver. Increasing the size of the driver reduces driving resistance relative to the wire, resulting in a delay that is quadratic with respect to wire length. Modern high speed designs operate in this regime. Therefore the interconnect topologies studied in this work assume a large driver so that the overall delay is dominated by the interconnect delay.

To investigate the impact of lithography process variability at the interconnect levels, the Interconnect Variability Characterization framework, described in Section 3.5.2 and illustrated in Figure 3.2 is used. This framework leverages rigorous TCAD process tools to perform lithography characterization of small layout clips. These characterization results are generalized and used to create larger sized 1D interconnect layouts representative of post-lithography contours. The contours are then combined with parasitic extraction design analysis tools to determine the circuit level impact of lithography variability.

## 4.3 90nm and 32nm Process Technology Characterization

Integrated circuit manufacturers limit access to their official process design kits (PDK), which contain proprietary information about the process technology, device performance, and manufacturability targets. At the university level, access to these PDKs is difficult to achieve. PDK access is only made available through a non disclosure agreement which restricts any derived information can be used in publications, such as this dissertation. Thus, custom generated PDKs using assumptions from publicly available sources were used for this study.

Separate PDKs were generated for 90nm and 32nm technology nodes. The 90nm technology assumes a single lithography exposure and patterning step for each interconnect layer. In contrast, the 32nm technology assumes a double exposure and double patterning procedure. Device models for 90nm and 32nm high performance CMOS technology were provided by the NIMU group at Arizona State University [2, 42]. For each technology, a corresponding interconnect stack was derived using predictions from the ITRS roadmap[1]. The minimum intermediate metal pitch at the 90nm and 32nm nodes is 280nm and 90nm, respectively. Optimization methods from repeater insertion are applied to each technology to derive the optimal interconnect length L and driver sizing S [34]. The optimal values for 90nm technology are S=23 and L=921um. For 32nm, they are S=33 and L=58um.