## **UC Berkeley**

## **UC Berkeley Previously Published Works**

#### **Title**

Comparative Performance Analysis of Regulated Hybrid Switched-Capacitor Topologies for Direct 48 V to Point-of-Load Conversion

#### **Permalink**

https://escholarship.org/uc/item/6wx9595r

#### **Authors**

Zhu, Yicheng Ellis, Nathan M Pilawa-Podgurski, Robert CN

#### **Publication Date**

2024

#### DOI

10.1109/ojpel.2024.3478288

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution-NonCommercial-NoDerivatives License, available at <a href="https://creativecommons.org/licenses/by-nc-nd/4.0/">https://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Peer reviewed

© 2024 IEEE

IEEE Open Journal of Power Electronics

# Comparative Performance Analysis of Regulated Hybrid Switched-Capacitor Topologies for Direct 48 V to Point-of-Load Conversion

Y. Zhu N. M. Ellis R. C. N. Pilawa-Podgurski

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Received XX Month, XXXX; revised XX Month, XXXX; accepted XX Month, XXXX; Date of publication XX Month, XXXX; date of current version XX Month, XXXX.

Digital Object Identifier 10.1109/10.1109/OJPEL.2024.3478288

# Comparative Performance Analysis of Regulated Hybrid Switched-Capacitor Topologies for Direct 48 V to Point-of-Load Conversion

YICHENG ZHU (MEMBER, IEEE), NATHAN M. ELLIS (MEMBER, IEEE), AND ROBERT C. N. PILAWA-PODGURSKI (FELLOW, IEEE)

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA CORRESPONDING AUTHOR: YICHENG ZHU (e-mail: yczhu@berkeley.edu).

Yicheng Zhu was supported by the NVIDIA Graduate Fellowship Program during the 2023–2024 academic year. An earlier version of this paper was presented at the 2023 [EEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, October 29–November 2, 2023 [DOI: 10.1109/ECCE53617.2023.10362157] with the same title. This article expands upon our previous conference paper with an additional comparative analysis of transient performance, as well as in-depth discussions on the comparison results.

ABSTRACT Hybrid switched-capacitor (SC) converters have received increased attention for point-of-load (PoL) applications because they can effectively leverage the superior energy density of capacitors and the improved figures-of-merit of low-voltage switching devices. This article introduces an analytical framework for characterizing and comparing regulated hybrid SC topologies for direct 48-V-to-PoL conversion. In the proposed framework, a regulated hybrid SC topology is generally represented as a fixed-ratio SC stage merged with a subsequent regulated buck-type stage, with the total conversion ratio allocated between them. Three metrics are used for performance comparison: a) normalized switch stress as an indicator of efficiency, b) normalized passive component volume as an indicator of power density, and c) normalized total inductor current slew rate as an indicator of transient performance. This framework reveals that increasing the SC stage conversion ratio reduces switch stress and passive component volume while accelerating the falling slew rate of the total inductor current, thereby improving efficiency, power density, and load step-down transient performance concurrently. Although a larger SC step-down ratio typically decreases the rising slew rate of the total inductor current, potentially impairing the load step-up transient performance, proper designs can achieve balanced load step-up and step-down transient performances.

**INDEX TERMS** Comparative analysis, high conversion ratio, hybrid switched-capacitor (SC) converter, point-of-load (PoL), voltage regulation module (VRM).

#### I. Introduction

THE YBRID switched-capacitor (SC) converters have attracted increased attention for 48-V step-down conversion in data center [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32], [33], [34], [35] and automotive [36], [37] applications, due to their potential to provide improved solutions with higher efficiency and power density compared to conventional designs. As an emerging class of power converters, hybrid SC converters can leverage the greatly superior energy density of capacitors compared to

inductors [38], while simultaneously benefiting from the improved figures-of-merit (FOM) of low-voltage switching devices over high-voltage counterparts [39]. For unregulated, fixed-ratio voltage step-down applications (e.g., 48-V-to-12-V intermediate bus converters), various resonant switched-capacitor (ReSC) [29], [30], [31], [32], [33] and multi-resonant switched-capacitor (MRSC) [34], [35] converters operating at or above resonance have been proposed, demonstrating their advantages over existing dc-dc solutions, such as multi-phase buck converters [40] and LLC converters [41]. Previous studies [42], [43], [44], [45] have shown how to analyze and compare different ReSC topologies and strategi-

1

cally size the passive components in each topology to achieve optimal performance. Additionally, multiple regulated hybrid SC topologies [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28] have been proposed for direct 48 V to point-of-load (PoL) conversion, particularly for 48-V voltage regulation modules (VRMs), where output voltage regulation is typically required. However, there is a lack of a method to theoretically compare the performance of regulated hybrid SC topologies, which could be useful for informing topology selection and converter design.

To fill this gap, this work aims to establish an analytical framework for the topological characterization and performance comparison of regulated hybrid SC topologies in direct 48-V-to-PoL applications. In the proposed framework, each topology is captured with topology-dependent characteristic vectors, which are then utilized to calculate three metrics for performance comparison: a) normalized switch stress as an indicator of efficiency, b) normalized passive component volume as an indicator of power density, and c) normalized total inductor current slew rate as an indicator of transient performance. Building on our previous conference paper [46], this article provides an additional comparative analysis of transient performance, as well as in-depth discussions on the comparison results. Based on this analytical framework, a comprehensive comparative analysis reveals that increasing the SC stage conversion ratio can reduce switch stress and passive component volume while speeding up the falling slew rate of the total inductor current, thereby improving efficiency, power density, and load step-down transient performance at the same time. Although a larger SC conversion ratio typically slows down the rising slew rate of the total inductor current, potentially impairing the load step-up transient performance, a converter with a larger SC conversion ratio can be properly designed to achieve balanced load step-up and step-down transient performances.

The remainder of this paper is organized as follows: Section II provides a general representation of regulated hybrid SC topologies consisting of a fixed-ratio SC stage merged with a subsequent regulated buck-type stage. Section III introduces the analytical framework with the three metrics for performance comparison, including a formalized analysis procedure using topology-dependent characteristic vectors. Based on the proposed framework, Section IV conducts a comparative analysis of the state-of-the-art 48-V-to-PoL regulated hybrid SC topologies and demonstrates the benefits of a larger SC stage conversion ratio. Finally, Section V concludes this article.

## II. General Representation of Regulated Hybrid SC Topologies

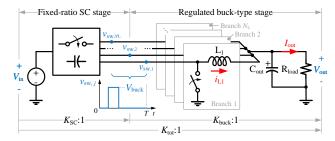

A regulated hybrid SC topology can be captured by the general representation depicted in Fig. 1. It consists of two stages: 1) a fixed-ratio SC stage for efficient and compact voltage conversion and 2) a regulated buck-type stage for the

FIGURE 1. General representation of a regulated hybrid SC topology consisting of a fixed-ratio SC stage and a regulated buck-type stage. The input voltage  $(V_{\rm in})$  is first stepped down to  $V_{\rm buck}$  by the SC stage. The buck-type stage then performs the remaining voltage conversion from  $V_{\rm buck}$  to the output voltage  $(V_{\rm out})$  with regulation. The total conversion ratio  $K_{\rm tot}:1$  is allocated between the SC stage and the buck-type stage.

remainder of the voltage conversion task and output voltage regulation. Moreover, when designed properly, the buck-type stage serves as an inductive load to the preceding SC stage, ensuring complete soft-charging operation [47]. It should be noted that a distinctive feature of high-performance hybrid SC topologies is that the two stages are not independent; instead, their operations are merged to achieve improved performance [48]. Additionally, although the buck-type stage can regulate the output voltage with duty cycle control and achieve multi-phase interleaving similar to a buck converter, it does not necessarily require dedicated pull-up switches due to its strategic merging with the preceding SC stage.

As is consistent with all previously cited works, this analysis considers only topologies where all switch-node voltages in Fig. 1 ( $v_{\rm sw,1},\ v_{\rm sw,2},\cdots,\ v_{\rm sw,NL}$ , where  $N_{\rm L}$  denotes the total number of inductors) switch between the same two voltage levels:  $V_{\rm buck}$  and 0.  $V_{\rm buck}$  is the highest voltage that the buck-type stage experiences (ignoring flying capacitor voltage ripples), thereby defined as the voltage stress on the buck-type stage. The input voltage ( $V_{\rm in}$ ) is first stepped down to  $V_{\rm buck}$  by the SC stage, where  $V_{\rm buck}$  can be calculated as

$V_{\text{buck}} = \frac{V_{\text{in}}}{K_{\text{SC}}},$  (1)

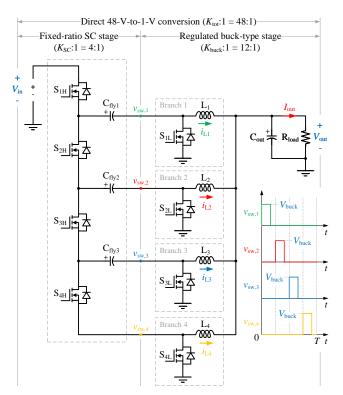

and  $K_{\rm SC}$  is the SC stage conversion ratio, also interchangeably referred to as the SC step-down ratio. The buck-type stage then performs the remaining voltage conversion from  $V_{\rm buck}$  to the output voltage ( $V_{\rm out}$ ) with regulation. Fig. 2 illustrates a four-branch series-capacitor buck (SCB) converter as an example of the general representation depicted in Fig. 1, where  $V_{\rm in}=48$  V and  $V_{\rm out}=1$  V. The high-side switches ( $S_{\rm 1H-4H}$ ) and flying capacitors ( $C_{\rm fly1-fly3}$ ) constitute the SC stage with a step-down ratio of 4:1 ( $K_{\rm SC}=4$ ). According to (1), the voltage stress on the buck-type stage can be obtained as  $V_{\rm buck}=12$  V. The buck-type stage, consisting of the low-side switches ( $S_{\rm 1L-4L}$ ) and inductors ( $L_{\rm 1-4}$ ), completes the remaining 12-V-to-1-V voltage conversion ( $K_{\rm buck}=12$ ) with regulation.

Since the total conversion ratio  $(K_{\text{tot}})$ , defined as  $K_{\text{tot}} = V_{\text{in}}/V_{\text{out}}$ , is allocated between the SC stage and the buck-

FIGURE 2. Four-branch SCB converter for direct 48-V-to-1-V conversion as an example of the general representation depicted in Fig. 1. The high-side switches  $(\mathbf{S}_{1\mathrm{H-}4\mathrm{H}})$  and flying capacitors  $(C_{\mathrm{fly1-fly3}})$  constitute the 4:1 SC stage; the low-side switches  $(\mathbf{S}_{1\mathrm{L-}4\mathrm{L}})$  and inductors  $(\mathbf{L}_{1-4})$  form the buck-type stage which performs the remaining 12-V-to-1-V voltage conversion with regulation. In this example, the voltage stress on the buck-type stage is  $V_{\mathrm{buck}}=12~\mathrm{V}$ .

type stage, if the SC stage achieves a larger step-down ratio  $(K_{\rm SC})$ , the voltage conversion burden on the buck-type stage  $(K_{\rm buck})$  can be reduced. At the same output voltage, buck converters with lower step-down ratios typically require smaller inductors and achieve higher efficiency. Given that magnetic components typically dominate the volume of power converters, it is favorable to design the SC stage to take on more voltage conversion burden so that the inductor volume of the buck-type stage can be reduced.

Although it is clear that a larger SC stage conversion ratio  $(K_{\rm SC})$  benefits the buck-type stage, there is still a concern that increasing  $K_{\rm SC}$  can impair overall efficiency. This is because achieving a larger SC step-down ratio generally requires more switching devices, which can lead to higher conduction and switching losses. Moreover, higher-order SC networks typically require more flying capacitors, potentially offsetting the inductor volume reduction seen in the buck-type stage. These concerns are addressed in the following sections.

# III. Analytical Framework for Topological Characterization and Performance Comparison

The proposed analytical framework focuses on three metrics for performance comparison: a) normalized switch stress  $(M_S)$  as an indicator of efficiency, b) normalized passive

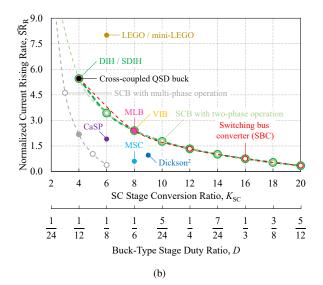

component volume  $(M_P)$  as an indicator of power density, and c) normalized falling and rising slew rates  $(\widehat{SR}_F)$  and  $(\widehat{SR}_F)$  of the total inductor current as indicators of transient performance. In the proposed framework, all three metrics are normalized and independent of output power and current levels, ensuring fair comparisons across different topologies. This section first discusses the key assumptions of the proposed framework, then provides the definitions and derivations of the three metrics, and finally introduces a formalized analytical procedure using topology-dependent characteristic vectors.

#### A. Key Assumptions

The proposed analytical framework is based on the following assumptions:

- Small-ripple approximation: It is selectively assumed that the magnitude of the switching ripple is much smaller than the dc component of capacitor voltages and inductor currents, which enables three subsequent assumptions:

- In the analysis of normalized switch stress, inductor current ripples and capacitor voltage ripples are assumed to be negligible.

- In the analysis of normalized passive component volume (where ripple cannot meaningfully be ignored), inductor current ripples and capacitor voltage ripples are assumed to be piecewise linear. In other words, capacitor voltage ripples are assumed to be negligible in inductor volume analysis, and inductor current ripples are assumed to be negligible in capacitor volume analysis.

- In the analysis of normalized total inductor current slew rate, all capacitor voltage ripples (including the output voltage ripple) are again assumed to be negligible.

- Uniform ripple ratios: Ripple ratios of all inductor currents  $(\alpha_{\rm I})$  are assumed to be the same. Ripple ratios of all capacitor voltages  $(\alpha_{\rm V})$  are assumed to be the same.

- Lossless energy transfer: Duty ratio is calculated based on the assumption that the converter is lossless with no requirement for output voltage droop compensation.

- Uniform energy density: All inductors are assumed to have the same volumetric energy density ( $\rho_{E,L}$ ). All capacitors are assumed to have the same volumetric energy density ( $\rho_{E,C}$ ).

The symbols used in this framework are defined in Table 1. Later symbols with the hat notation ( $\hat{\cdot}$ ) are normalized values with respect to their base values listed in Table 2.

**TABLE 1. Symbol definitions**

| Symbol                                                                                                                     | Definition                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $N_{ m S} \ N_{ m L} \ N_{ m C}$                                                                                           | Total number of switching devices<br>Total number of inductors<br>Total number of flying capacitors                                                                                                                                                                                                                                                                                                      |

| $V_{ m in} \ V_{ m buck} \ V_{ m out} \ I_{ m out}$                                                                        | Input voltage (base value for voltage) Buck-type stage input voltage (illustrated in Fig. 1) Output voltage Total output current (base value for current)                                                                                                                                                                                                                                                |

| $K_{ m tot} \ K_{ m SC} \ K_{ m buck}$                                                                                     | Total conversion ratio $(K_{\rm tot} = V_{\rm in}/V_{\rm out})$ SC stage conversion ratio $(K_{\rm SC} = V_{\rm in}/V_{\rm buck})$ Buck-type stage conversion ratio $(K_{\rm buck} = V_{\rm buck}/V_{\rm out})$                                                                                                                                                                                          |

| $\frac{V_{\mathrm{ds},i}}{I_{\mathrm{d(rms)},i}}$                                                                          | Peak blocking voltage across switch $i$ RMS value of the current through switch $i$                                                                                                                                                                                                                                                                                                                      |

| $ \begin{array}{c} \text{Vol}_{\text{tot}} \\ \text{Vol}_{\text{L},j} \\ \text{Vol}_{\text{C},k} \end{array} $             | Total passive component volume<br>Volume of inductor $j$<br>Volume of capacitor $k$                                                                                                                                                                                                                                                                                                                      |

| $L_j$ $I_{\mathrm{L},j}$ $\Delta i_{\mathrm{L},j,\mathrm{pp}}$ $T$ $D$ $D_{\mathrm{max}}$ $E_{\mathrm{L},j,\mathrm{peak}}$ | Value of inductor $j$ Average current of inductor $j$ Peak-to-peak current ripple of inductor $j$ Switching period of the buck-type stage Duty ratio of the buck-type stage Maximum duty ratio of the buck-type stage Peak energy stored in inductor $j$                                                                                                                                                 |

| $C_k$ $V_{C,k}$ $\Delta v_{C,k,pp}$ $q_{C,k}$ $E_{C,k,peak}$                                                               | Value of capacitor $k$ Mid-range voltage of capacitor $k$ Peak-to-peak voltage ripple of capacitor $k$ Accumulative charge flowing into capacitor $k$ between the peak and valley of capacitor $k$ 's voltage waveform Peak energy stored in capacitor $k$                                                                                                                                               |

| $\alpha_{\rm I}$ $\alpha_{\rm V}$ $\rho_{\rm E,L}$ $\rho_{\rm E,C}$ $\beta$                                                | Inductor current ripple ratio ( $\alpha_{\rm I} = \Delta i_{{\rm L},j,{\rm ap}}/I_{{\rm L},j}$ ) Capacitor voltage ripple ratio ( $\alpha_{\rm V} = \Delta v_{{\rm C},k,{\rm ap}}/V_{{\rm C},k}$ ) Volumetric energy density of inductors Volumetric energy density of capacitors Volumetric energy density ratio of capacitors to inductors ( $\beta = \rho_{{\rm E},{\rm C}}/\rho_{{\rm E},{\rm L}}$ ) |

| $SR_{F,j}$ $SR_{F}$ $SR_{R,j}$ $SR_{R}$                                                                                    | Maximum current falling slew rate of inductor $j$ Maximum total inductor current falling slew rate Maximum current rising slew rate of inductor $j$ Maximum total inductor current rising slew rate                                                                                                                                                                                                      |

TABLE 2. Base values for normalization

| Quantity   | Voltage     | Current      | Charge              | Volume                                           | Current<br>Slew Rate                   |

|------------|-------------|--------------|---------------------|--------------------------------------------------|----------------------------------------|

| Base value | $V_{ m in}$ | $I_{ m out}$ | $I_{\mathrm{out}}T$ | $\frac{V_{\rm out}I_{\rm out}T}{\rho_{\rm E,L}}$ | $\frac{2\alpha_{\rm I}I_{\rm out}}{T}$ |

#### B. Normalized Switch Stress

The normalized switch stress  $(M_{\rm S})$  is defined as the total switch stress normalized to the output power

$$M_{\rm S} = \frac{\sum\limits_{\rm switches} V_{\rm ds,\it i} I_{\rm d(rms),\it i}}{V_{\rm out} I_{\rm out}} = \underbrace{\frac{V_{\rm in}}{V_{\rm out}}}_{K_{\rm tot}} \cdot \sum_{i=1}^{N_{\rm S}} \underbrace{\frac{V_{\rm ds,\it i}}{V_{\rm in}}}_{\widehat{V}_{\rm ds,\it i}} \cdot \underbrace{\frac{I_{\rm d(rms),\it i}}{I_{\rm out}}}_{\widehat{I}_{\rm d(rms),\it i}}$$

$$= K_{\text{tot}} \sum_{i=1}^{N_{\text{S}}} \widehat{V}_{\text{ds},i} \widehat{I}_{\text{d(rms)},i}, \tag{2}$$

where  $V_{\mathrm{ds},i}$  is the peak blocking voltage across switch i when assuming no capacitor voltage ripple, and  $I_{\mathrm{d(rms)},i}$  is the root mean square (RMS) value of the current flowing through switch i when assuming no inductor current ripple.

The normalized switch stress  $M_{\rm S}$  indicates how much volt-ampere (VA) stress the switches in a topology experience when transferring one per-unit watt of power from the input to the output. It commonly serves as a proxy for switching device losses or semiconductor areas in a topology [42], [44], [45], [49]. A lower  $M_{\rm S}$  is desirable, as it indicates lower switching and conduction losses, thus contributing to higher efficiency. In addition, a lower  $M_{\rm S}$  indicates smaller switching device areas, which is favorable to higher power density.

#### C. Normalized Passive Component Volume

The total passive component volume ( $Vol_{tot}$ ) is the combined volume of all inductors and capacitors:

$$Vol_{tot} = \sum_{inductors} Vol_{L,j} + \sum_{capacitors} Vol_{C,k},$$

(3)

where  $Vol_{L,j}$  and  $Vol_{C,k}$  represent the volumes of inductor j and capacitor k, respectively.

This work adopts an energy-based approach to passive component volume assessment by analyzing the peak energy stored in each passive component [44], [45]:

$$Vol_{L,j} = \frac{E_{L,j,peak}}{\rho_{E,L}}$$

(4)

$$Vol_{C,k} = \frac{\rho_{E,L}}{\rho_{E,C}},$$

(5)

where  $E_{\mathrm{L},j,\mathrm{peak}}$  and  $E_{\mathrm{C},k,\mathrm{peak}}$  represent the peak energies stored in inductor j and capacitor k, respectively. The parameter  $\rho_{\mathrm{E},\mathrm{L}}$  and  $\rho_{\mathrm{E},\mathrm{C}}$  are the volumetric energy densities of inductors and capacitors, respectively [38], [50]. To determine the total passive component volume that a topology requires, this section first finds the minimum inductor and capacitor values that can meet chosen current and voltage ripple requirements and then calculates the peak energy stored in these passive components.

#### 1) Inductor Volume Calculation

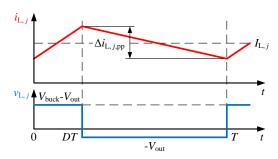

Fig. 3 illustrates the current and voltage waveforms of inductor j. Define the current ripple ratio ( $\alpha_{\rm I}$ ) as the ratio of the peak current ripple amplitude to the average inductor current:

$$\alpha_{\rm I} = \frac{\frac{1}{2}\Delta i_{\rm L,j,pp}}{I_{\rm L,i}},\tag{6}$$

where  $I_{\mathrm{L},j}$  and  $\Delta i_{\mathrm{L},j,\mathrm{pp}}$  are the average inductor current and peak-to-peak inductor current ripple, respectively, as annotated in Fig. 3. In this analysis, ripple ratios of all inductor currents are assumed to be the same for simplicity, but may be otherwise extended.

By integrating the inductor's current-voltage relation over  $t \in [DT, T]$ , we can obtain the peak-to-peak inductor current

VOLUME.

FIGURE 3. Current (top, red) and voltage (bottom, blue) waveforms of inductor j.  $I_{\mathrm{L},j}$  and  $\Delta i_{\mathrm{L},j,\mathrm{pp}}$  are the average inductor current and peak-to-peak inductor current ripple, respectively. The voltage applied across the inductor jumps between  $V_{\mathrm{buck}}-V_{\mathrm{out}}$  and  $-V_{\mathrm{out}}$ .

ripple as

$$\Delta i_{\mathrm{L},j,\mathrm{pp}} = \frac{V_{\mathrm{out}}}{L_j} (1 - D) T, \tag{7}$$

where D is the duty ratio of the buck-type stage. Based on the assumption of lossless energy transfer, D can be calculated as

$$D = \frac{1}{K_{\text{buck}}} = \frac{K_{\text{SC}}}{K_{\text{tot}}}.$$

(8)

We can obtain the minimum inductor value required to meet the chosen current ripple requirement ( $\alpha_I$ ) by substituting (6) and (8) into (7), which yields

$$L_j = \frac{V_{\text{out}}T}{2\alpha_{\text{I}}I_{\text{L},j}} \left(1 - \frac{K_{\text{SC}}}{K_{\text{tot}}}\right). \tag{9}$$

Therefore, the peak energy stored in the inductor is

$$E_{L,j,peak} = \frac{1}{2} L_j \left( I_{L,j} + \frac{1}{2} \Delta i_{L,j,pp} \right)^2$$

$$= \frac{1}{2} L_j (1 + \alpha_I)^2 I_{L,j}^2. \tag{10}$$

Substituting (9) into (10) and dividing by inductor volumetric energy density ( $\rho_{E,L}$ ), as shown in (4), yields the required inductor volume:

$$\operatorname{Vol}_{\mathrm{L},j} = \frac{(1 + \alpha_{\mathrm{I}})^{2} V_{\mathrm{out}} I_{\mathrm{L},j} T}{4\alpha_{\mathrm{I}} \rho_{\mathrm{E},\mathrm{L}}} \left( 1 - \frac{K_{\mathrm{SC}}}{K_{\mathrm{tot}}} \right). \tag{11}$$

According to the passive component survey in [38], it is a reasonable approximation to assume a constant volumetric energy density  $(\rho_{E,L})$  for the most energy-dense inductors rated between 1 A and 100 A, which are typically used to implement the regulated hybrid SC topologies for PoL applications discussed in this paper.

#### 2) Capacitor Volume Calculation

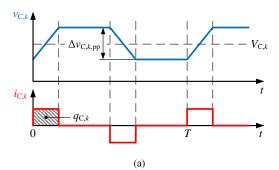

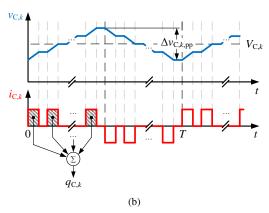

Fig. 4 illustrates the voltage and current waveforms of capacitor k for two scenarios: when the SC stage and the buck-type stage operate at the same frequency (Fig. 4(a)), and when the SC stage operates at a lower frequency than the buck-type stage (Fig. 4(b)). Define the voltage ripple ratio ( $\alpha_V$ ) as the ratio of the peak voltage ripple amplitude

FIGURE 4. Voltage (top, blue) and current (bottom, red) waveforms of capacitor k ( $C_k$ ). (a) When the SC stage and the buck-type stage operate at the same frequency. (b) When the SC stage operates at a lower frequency than the buck-type stage.  $V_{\mathrm{C},k}$  and  $\Delta v_{\mathrm{C},k,\mathrm{pp}}$  are the mid-range capacitor voltage and peak-to-peak capacitor voltage ripple, respectively.  $q_{\mathrm{C},k}$  is the accumulative charge flowing into capacitor k between the peak and valley of capacitor k's voltage waveform and is illustrated as the shaded area.

to the mid-range capacitor voltage:

$$\alpha_{\rm V} = \frac{\frac{1}{2}\Delta v_{\rm C,k,pp}}{V_{\rm C,k}},\tag{12}$$

where  $V_{\mathrm{C},k}$  and  $\Delta v_{\mathrm{C},k,\mathrm{pp}}$  are the mid-range capacitor voltage and peak-to-peak capacitor voltage ripple, respectively, as annotated in Fig. 4. The *mid-range* voltage is the average of the maximum and minimum values of the capacitor voltage waveform and is distinct from the time-averaged or dc voltage of a capacitor [51]. In this analysis, ripple ratios of all capacitor voltages are assumed to be the same.

Illustrated as the shaded area on the capacitor current waveform in Fig. 4,  $q_{C,k}$  represents the accumulative charge flowing into capacitor k between the peak and valley of capacitor k's voltage waveform. When the SC stage operates at a lower frequency than the buck-type stage, a flying capacitor can be charged multiple times before being discharged (e.g., the LEGO [7], [8] and Mini-LEGO [18], [19] topologies), as shown in Fig. 4(b). In this scenario, all charges flowing into the capacitor should be summed together when calculating  $q_{C,k}$ . It should be noted that the capacitor does not necessarily need to absorb charge consecutively, as depicted in Fig. 4(b). If the capacitor charging and discharging events are interspersed,  $q_{C,k}$  is the

net charge flowing into the capacitor between the peak and valley of the capacitor's voltage waveform. Therefore, this analysis does not rely on the assumption that the SC stage and the buck-type stage operate at the same frequency. The effect of asynchronous operating frequencies between the two stages on the size of flying capacitors can be captured by  $q_{\mathrm{C},k}$ . With  $q_{\mathrm{C},k}$ , the peak-to-peak capacitor voltage ripple can be obtained as

$$\Delta v_{\mathrm{C},k,\mathrm{pp}} = \frac{q_{\mathrm{C},k}}{C_k}.\tag{13}$$

We can obtain the minimum capacitor value required to meet the chosen voltage ripple requirement ( $\alpha_V$ ) by substituting (12) into (13), which yields

$$C_k = \frac{q_{\mathrm{C},k}}{2\alpha_{\mathrm{V}}V_{\mathrm{C},k}}.\tag{14}$$

Thus, the peak energy stored in the capacitor is

$$E_{C,k,peak} = \frac{1}{2} C_k \left( V_{C,k} + \frac{1}{2} \Delta v_{C,k,pp} \right)^2$$

$$= \frac{1}{2} C_k (1 + \alpha_V)^2 V_{C,k}^2. \tag{15}$$

Substituting (14) into (15) and dividing by capacitor volumetric energy density ( $\rho_{E,C}$ ), as shown in (5), yields the required capacitor volume:

$$\operatorname{Vol}_{C,k} = \frac{E_{C,k,\text{peak}}}{\rho_{E,C}} = \frac{(1 + \alpha_{V})^{2} V_{C,k} q_{C,k}}{4\alpha_{V} \rho_{E,C}}.$$

(16)

Similar to  $\rho_{E,L}$ , the volumetric energy density  $(\rho_{E,C})$  for the most energy-dense capacitors rated between 10 V and 100 V, which are typically used to implement the regulated hybrid SC topologies for PoL applications discussed in this paper, can be assumed to be constant, according to [38].

#### 3) Normalization of Passive Component Volume

The normalized passive component volume  $(M_P)$  is defined as the total passive component volume  $(Vol_{tot})$  normalized to the base volume  $(Vol_{base})$  and is equal to the combined normalized volume of all inductors  $(\widehat{Vol}_{L,j})$  and capacitors  $(\widehat{Vol}_{C,k})$ :

$$M_{\rm P} = \frac{\text{Vol}_{\text{tot}}}{\text{Vol}_{\text{base}}} = \frac{\sum_{\text{inductors}} \text{Vol}_{\text{L},j} + \sum_{\text{capacitors}} \text{Vol}_{\text{C},k}}{\text{Vol}_{\text{base}}}$$

$$= \sum_{j=1}^{N_{\rm L}} \widehat{\text{Vol}}_{\text{L},j} + \sum_{k=1}^{N_{\rm C}} \widehat{\text{Vol}}_{\text{C},k}. \tag{17}$$

As listed in Table 2, in this analysis, the base value for volume is chosen as

$$Vol_{base} = \frac{V_{out}I_{out}T}{\rho_{EL}},$$

(18)

where T is the switching period of the buck-type stage and  $\rho_{E,L}$  is the volumetric energy density of inductors. This base value is chosen because it ensures that the normalized passive component volume  $(M_{\rm P})$  is dimensionless and independent of the output power  $(V_{\rm out}I_{\rm out})$ . It is worth noting that this

base volume is arbitrarily defined relative to the inductor density,  $\rho_{E,L}$ . Alternatively, the capacitor density,  $\rho_{E,C}$ , can be used to produce consistent relative results. The ratio of the volumetric energy density of capacitors to that of inductors is defined as

$$\beta = \frac{\rho_{\rm E,C}}{\rho_{\rm E,L}},\tag{19}$$

and is typically in the range of 50-1000, depending on the specific passive component technologies used [38].

Normalizing the inductor volume in (11) and the capacitor volume in (16) to the base value for volume in (18) yields the normalized inductor volume  $(\widehat{\mathrm{Vol}}_{\mathrm{L},j})$  and the normalized capacitor volume  $(\widehat{\mathrm{Vol}}_{\mathrm{C},k})$  as

$$\widehat{\text{Vol}}_{\text{L},j} = \frac{\text{Vol}_{\text{L},j}}{\text{Vol}_{\text{base}}} = \frac{(1 + \alpha_{\text{I}})^2}{4\alpha_{\text{I}}} \cdot \left(1 - \frac{K_{\text{SC}}}{K_{\text{tot}}}\right) \cdot \underbrace{\frac{I_{\text{L},j}}{I_{\text{out}}}}_{\widehat{I}_{\text{L},j}}$$

$$= \frac{(1 + \alpha_{\text{I}})^2}{4\alpha_{\text{I}}} \left(1 - \frac{K_{\text{SC}}}{K_{\text{tot}}}\right) \widehat{I}_{\text{L},j}. \tag{20}$$

$$\widehat{\text{Vol}}_{C,k} = \frac{\text{Vol}_{C,k}}{\text{Vol}_{\text{base}}} = \frac{(1 + \alpha_{\text{V}})^2}{4\alpha_{\text{V}}} \cdot \underbrace{\frac{\rho_{\text{E,L}}}{\rho_{\text{E,C}}}}_{1/\beta} \cdot \underbrace{\frac{V_{\text{in}}}{V_{\text{out}}}}_{K_{\text{tot}}} \cdot \underbrace{\frac{V_{\text{C},k}}{V_{\text{in}}}}_{\widehat{V}_{\text{C},k}} \cdot \underbrace{\frac{q_{\text{C},k}}{I_{\text{out}}T}}_{\widehat{q}_{\text{C},k}}$$

$$= \frac{(1 + \alpha_{\text{V}})^2}{4\alpha_{\text{V}}\beta} K_{\text{tot}} \widehat{V}_{C,k} \widehat{q}_{C,k}, \qquad (21)$$

where  $\beta$  is the volumetric energy density ratio of capacitors to inductors defined in (19).

Summing the normalized volumes of all inductors and capacitors by substituting (20) and (21) into (17) yields

$$M_{\rm P} = \sum_{j=1}^{N_{\rm L}} \frac{(1+\alpha_{\rm I})^2}{4\alpha_{\rm I}} \left(1 - \frac{K_{\rm SC}}{K_{\rm tot}}\right) \hat{I}_{{\rm L},j} + \sum_{k=1}^{N_{\rm C}} \frac{(1+\alpha_{\rm V})^2}{4\alpha_{\rm V}\beta} K_{\rm tot} \hat{V}_{{\rm C},k} \hat{q}_{{\rm C},k} .$$

(22)

Applying Kirchhoff's current law (KCL) to the average currents at the output node (i.e., the positive terminal of the load), we can obtain:

$$I_{\text{out}} + \langle i_{\text{Cout}} \rangle = \sum_{j=1}^{N_{\text{L}}} I_{\text{L},j},$$

(23)

where  $\langle i_{\rm Cout} \rangle$  denotes the average value of the current through the output capacitor ( $C_{\rm out}$ ). Note that the average value of the current through a capacitor in a periodic steady state is zero. Therefore,  $\langle i_{\rm Cout} \rangle = 0$ , meaning

$$I_{\text{out}} = \sum_{j=1}^{N_{\text{L}}} I_{\text{L},j}.$$

(24)

As a result, the sum of all normalized average inductor currents can be simplified as

$$\sum_{j=1}^{N_{\rm L}} \widehat{I}_{{\rm L},j} = \frac{1}{I_{\rm out}} \sum_{j=1}^{N_{\rm L}} I_{{\rm L},j} = 1.$$

(25)

Equation (22) can be simplified using (25) as

$$M_{\rm P} = \frac{\left(1 + \alpha_{\rm I}\right)^2}{4\alpha_{\rm I}} \left(1 - \frac{K_{\rm SC}}{K_{\rm tot}}\right) + \frac{\left(1 + \alpha_{\rm V}\right)^2}{4\alpha_{\rm V}\beta} K_{\rm tot} \sum_{k=1}^{N_{\rm C}} \widehat{V}_{{\rm C},k} \widehat{q}_{{\rm C},k}.$$

(26)

Note that the derivation of  $M_{\rm P}$  does not rely on balanced inductor currents (i.e.,  $I_{\rm L,1}=I_{\rm L,2}=\cdots=I_{\rm L,NL}$ ). Instead, the final expression for  $M_{\rm P}$  in (26) also applies to topologies where inductor currents are not equal (e.g., the DIH topology presented in [52], [53]), since the KCL equation in (25) always holds.

The normalized passive component volume  $(M_{\rm P})$  is a dimensionless value that indicates the relative volume of passive components required to meet the specified ripple requirements across various topologies when transferring one per-unit watt of power from input to output, at a given switching frequency and inductor volumetric energy density. A smaller normalized passive component volume is desirable, as it indicates higher power density.

#### D. Normalized Total Inductor Current Slew Rate

Fast dynamic response to load transients is typically required for PoL power converters [54], [55]. When a step change in the load current occurs, the maximum total inductor current slew rate determines the fastest response a converter can achieve to recover the output voltage, regardless of the control scheme. Therefore, the maximum total inductor current slew rate represents the physical limit of a converter's transient performance. In the proposed analytical framework, the falling and rising slew rates of the total inductor current are chosen as indicators of transient performance.

#### 1) Total Inductor Current Falling Slew Rate

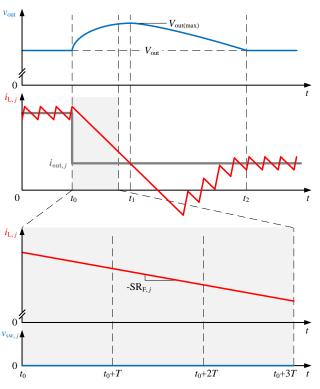

Fig. 5 illustrates the key waveforms of a regulated hybrid SC converter, as shown in Fig. 1, during a load step-down transient. The load transient begins at  $t_0$  when the load current  $(i_{\text{out}})$  suddenly drops. The output voltage  $(v_{\text{out}})$  reaches its peak at  $t_1$  when the inductor current  $(i_{\text{L},j})$  crosses the load current flowing through branch j  $(i_{\text{out},j})$ ; it recovers to the nominal value  $(V_{\text{out}})$  at  $t_2$ . Note that although the output voltage overshoot  $(V_{\text{out}(\max)} - V_{\text{out}})$  is exaggerated in Fig. 5 for clear illustration, it is assumed to be much smaller than  $V_{\text{out}}$ .

The fastest way of recovering  $v_{\rm out}$  during the load step-down transient is by grounding all switch nodes and allowing the inductor currents to fall at the maximum rate. The maximum total inductor current falling slew rate (SR<sub>F</sub>) represents the physical limit of a topology's performance during load step-down transients. Therefore, SR<sub>F</sub> is chosen as a metric to compare the transient performance of different topologies. To derive SR<sub>F</sub>, we first need to obtain the maximum inductor current falling slew rate for each branch and then sum them together. Assuming the output voltage

FIGURE 5. Load step-down transient waveforms of branch j. From top to bottom: the output voltage waveform  $(v_{\mathrm{out}})$ , the waveforms of the current flowing through inductor j  $(i_{\mathrm{L},j})$  and the load current flowing through branch j  $(i_{\mathrm{out},j})$ , the zoomed-in waveform of the inductor current over three switching cycles, and the switch-node voltage waveform seen by inductor j  $(v_{\mathrm{sw},j})$ . The fastest way of recovering  $v_{\mathrm{out}}$  to the nominal value  $(V_{\mathrm{out}})$  is by grounding all switch nodes and allowing the inductor currents to fall at the maximum rate.

overshoot is much smaller than the nominal output voltage  $(V_{\rm out})$  due to the existence of the large output capacitor  $(C_{\rm out})$ , the maximum current falling slew rate of inductor j  $(SR_{{\rm F},j})$  can be approximated as

$$SR_{F,j} = \frac{V_{\text{out}}}{L_i},\tag{27}$$

which can be rewritten as

$$SR_{F,j} = \frac{K_{tot}}{K_{tot} - K_{SC}} \cdot \frac{2\alpha_{I}I_{L,j}}{T}$$

(28)

with the expression for  $L_j$  in (9) substituted into (27).

Therefore, the total inductor current falling slew rate can be obtained using the average KCL relationship in (24) as

$$SR_{F} = \sum_{j=1}^{N_{L}} SR_{F,j} = \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{SC}} \cdot \frac{2\alpha_{I} \sum_{j=1}^{N_{L}} I_{L,j}}{T}$$

$$= \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{SC}} \cdot \frac{2\alpha_{I} I_{\text{out}}}{T}.$$

(29)

#### 2) Total Inductor Current Rising Slew Rate

Fig. 6 depicts the load step-up transient waveforms of a regulated hybrid SC converter. Similar to the load step-

down transient illustrated in Fig. 5, this load step-up transient begins at  $t_0$  when the load current ( $i_{out}$ ) suddenly increases. The output voltage reaches its valley  $(V_{\text{out(min)}})$  at  $t_1$  when the inductor current crosses the load current flowing through branch j ( $i_{\text{out},j}$ ); it recovers to the nominal value ( $V_{\text{out}}$ ) at  $t_2$ . The output voltage undershoot  $(V_{\text{out}} - V_{\text{out}(\min)})$  is assumed to be much smaller than  $V_{\text{out}}$ , although it is exaggerated in Fig. 6 for clear illustration.

The fastest way of recovering  $v_{\mathrm{out}}$  is by operating all branches at the maximum duty ratio  $(D_{max})$  and forcing the inductor currents to rise at the maximum rate. Unlike the conventional multi-phase buck converter, many regulated hybrid SC topologies have an upper limit on the achievable duty ratio. For, example, the SCB converter with multi-phase operation shown in Fig. 2 has a maximum duty ratio of  $1/N_{\rm L}$ . A discussion of how this upper limit on the duty ratio affects the load step-up transient performance of regulated hybrid SC topologies will be provided in Section IV.

The maximum total inductor current rising slew rate (SR<sub>R</sub>) represents the physical limit of a topology's performance during load step-up transients. Therefore, SR<sub>R</sub> is chosen as a metric for the performance comparison of load step-up transients. Based on the small-ripple approximation, the maximum current rising slew rate of inductor j (SR<sub>R, i</sub>) can be obtained as

$$SR_{R,j} = \frac{\langle v_{\text{sw},j} \rangle - V_{\text{out}}}{L_j},$$

(30)

where  $\langle v_{\text{sw},i} \rangle$  denotes the average value of the switch-node voltage,  $v_{\text{sw},j}$ , over a switching period:

$$\langle v_{\text{sw},j} \rangle = D_{\text{max}} V_{\text{buck}}.$$

(31)

Substituting (9) and (31) into (30) and recognizing that  $V_{\rm buck}/V_{\rm out} = K_{\rm tot}/K_{\rm SC}$  yields

$$SR_{R,j} = \left(D_{\text{max}} \frac{K_{\text{tot}}}{K_{\text{SC}}} - 1\right) \cdot \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{\text{SC}}} \cdot \frac{2\alpha_{\text{I}} I_{\text{L},j}}{T}.$$

(32)

Therefore, the total inductor current rising slew rate can be obtained as

$$SR_{R} = \sum_{j=1}^{N_{L}} SR_{R,j}$$

$$= \left(D_{\max} \frac{K_{\text{tot}}}{K_{\text{SC}}} - 1\right) \cdot \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{\text{SC}}} \cdot \frac{2\alpha_{\text{I}} \sum_{j=1}^{N_{L}} I_{\text{L},j}}{T}$$

$$= \left(D_{\max} \frac{K_{\text{tot}}}{K_{\text{SC}}} - 1\right) \cdot \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{\text{SC}}} \cdot \frac{2\alpha_{\text{I}} I_{\text{out}}}{T}.$$

(33)

#### 3) Normalization of Total Inductor Current Slew Rate

As listed in Table 2, in this analysis, the base value for the current slew rate is chosen as

$$SR_{base} = \frac{2\alpha_I I_{out}}{T}.$$

(34)

This base value is chosen because it is a common term in the expressions for the total inductor current falling and

FIGURE 6. Load step-up transient waveforms of branch j. From top to bottom: the output voltage waveform  $(v_{\mathrm{out}})$ , the waveforms of the current flowing through inductor j ( $i_{L,j}$ ) and the load current flowing through branch j ( $i_{\mathrm{out},j}$ ), the zoomed-in waveform of the inductor current over three switching cycles, and the switch-node voltage waveform seen by inductor j ( $v_{\mathrm{sw},j}$ ). The fastest way of recovering  $v_{\mathrm{out}}$  to the nominal value  $(V_{

m out})$  is by operating all branches at the maximum duty ratio  $(D_{

m max})$  and forcing the inductor currents to rise at the maximum rate.

rising slew rates (SR<sub>F</sub> and SR<sub>R</sub>) shown in (29) and (33), respectively. More importantly, it ensures that the expressions for the normalized current slew rates are dimensionless and independent of the output current  $(I_{out})$ .

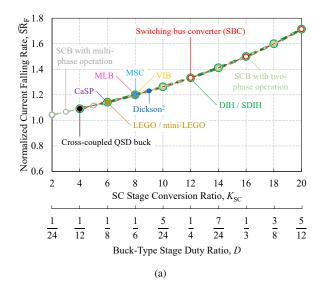

Normalizing the total inductor current falling and rising slew rates in (29) and (33) to the base value in (34) yields the normalized total inductor current falling slew rate (SR<sub>F</sub>) and the normalized total inductor current rising slew rate  $(SR_B)$  as

$$\widehat{SR}_{F} = \frac{SR_{F}}{SR_{base}} = \frac{K_{tot}}{K_{tot} - K_{SC}}$$

(35)

$$\widehat{SR}_{F} = \frac{SR_{F}}{SR_{\text{base}}} = \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{\text{SC}}}$$

$$\widehat{SR}_{R} = \frac{SR_{R}}{SR_{\text{base}}} = \left(D_{\text{max}} \frac{K_{\text{tot}}}{K_{\text{SC}}} - 1\right) \cdot \frac{K_{\text{tot}}}{K_{\text{tot}} - K_{\text{SC}}}.$$

(36)

Since  $K_{\text{tot}}$  is a constant determined by the application,  $\widehat{SR}_{\mathrm{F}}$  is a function of the SC stage conversion ratio  $(K_{\mathrm{SC}})$ only, as can be seen in (35). Additionally, equation (36) shows that  $\widehat{SR}_R$  is a function of the SC stage conversion ratio ( $K_{\rm SC}$ ) and the maximum duty ratio ( $D_{\rm max}$ ).

#### E. Formalized Analysis Procedure

According to (2) and (26), the following topology-dependent characteristic parameters are needed to calculate the normalized metrics  $M_{\rm S}$  and  $M_{\rm P}$ :  $\hat{V}_{{\rm ds},i}$ ,  $\hat{I}_{{\rm d(rms)},i}$ ,  $\hat{V}_{{\rm C},k}$ , and  $\hat{q}_{{\rm C},k}$ . To

8 VOLUME. formalize the analytical procedure, we define the following four topology-dependent characteristic vectors:

• Switch voltage stress vector:  $\hat{\mathbf{V}}_{\mathrm{ds}} = \left(\hat{V}_{\mathrm{ds},i}\right)_{1\leqslant i\leqslant N_{\mathrm{S}}}$

• Switch current stress vector:

$$\widehat{\mathbf{I}}_{\mathrm{d(rms)}} = \left(\widehat{I}_{\mathrm{d(rms)},i}\right)_{1\leqslant i\leqslant N_{\mathrm{S}}}$$

• Capacitor voltage vector:  $\widehat{\mathbf{V}}_{\mathrm{C}} = \left(\widehat{V}_{\mathrm{C},k}\right)_{1\leqslant k\leqslant N_{\mathrm{C}}}$

ullet Capacitor charge vector:  $\widehat{\mathbf{q}}_{\mathrm{C}} = (\widehat{q}_{\mathrm{C},k})_{1\leqslant k\leqslant N_{\mathrm{C}}}$

with which we can rearrange (2) and (26) as

$$M_{\rm S} = K_{\rm tot} \widehat{\mathbf{V}}_{\rm ds}^{\top} \widehat{\mathbf{I}}_{\rm d(rms)},$$

(37)

and

$$M_{\rm P} = M_{\rm P,L} + M_{\rm P,C},$$

(38)

where  $M_{

m P,L}$  is the normalized inductor volume

$$M_{\rm P,L} = \frac{\left(1 + \alpha_{\rm I}\right)^2}{4\alpha_{\rm I}} \left(1 - \frac{K_{\rm SC}}{K_{\rm tot}}\right),\tag{39}$$

and  $M_{\rm P,C}$  is the normalized capacitor volume

$$M_{\rm P,C} = \frac{(1 + \alpha_{\rm V})^2}{4\alpha_{\rm V}\beta} K_{\rm tot} \hat{\mathbf{V}}_{\rm C}^{\top} \hat{\mathbf{q}}_{\rm C}, \tag{40}$$

in which  $\cdot^{\top}$  denotes the transpose of a vector. The characteristic vectors of state-of-the-art 48-V-to-PoL regulated hybrid SC topologies are listed in Appendix A.

Equations (37) and (38) provide a formalized analytical procedure of  $M_{\rm S}$  and  $M_{\rm P}$  that can be automated. Equations (39) and (40) reveal two properties of  $M_{\rm P,L}$  and  $M_{\rm P,C}$ :

- As the SC stage conversion ratio  $(K_{\rm SC})$  increases, the normalized inductor volume  $(M_{\rm P,L})$  decreases and the normalized capacitor volume  $(M_{\rm P,C})$  increases. This is intuitive because increasing the SC stage conversion ratio means shifting more voltage conversion burden from the buck-type stage to the SC stage, reducing the inductor volume but necessitating a higher-order SC network, which requires more and larger flying capacitors.

- Topologies with the same SC stage conversion ratio (K<sub>SC</sub>) have the same normalized inductor volume (M<sub>P,L</sub>) because the only topology-independent parameter in (39) is K<sub>SC</sub>, while K<sub>tot</sub>, α<sub>I</sub>, α<sub>V</sub> and β are all constants. Therefore, the difference in the normalized passive component volume among different topologies with the same SC stage conversion ratio only comes from the difference in the normalized capacitor volume (M<sub>P,C</sub>).

These two properties will be used in the comparative analysis of the normalized passive component volume in Section IV-C.

# IV. Comparative Performance Analysis of 48-V-to-PoL Regulated Hybrid SC Topologies

Based on the analytical framework established in Section III, this section performs a comparative analysis of state-of-the-

art 48-V-to-1-V hybrid SC topologies and demonstrates the benefits of a larger SC stage conversion ratio.

#### A. Performance Comparison

Tables 3 and 4 summarize the key characteristics and the three normalized metrics of state-of-the-art regulated hybrid SC topologies for 48-V-to-1-V conversion. The year listed for each topology is when it was first proposed. If a topology has yielded more than one publication, the two most representative references are provided in the citation: 1) the earliest publication where the topology was first proposed, and 2) the latest publication that provides the most thorough explanation of the topology and/or includes experimental results from the best-performing hardware prototype.

The normalized passive component volume ( $M_{\rm P}$ ) of each topology is calculated using the following ripple ratios:  $\alpha_{\rm I}=15\%$  and  $\alpha_{\rm V}=5\%$ . The reasons for selecting these ripple ratios are explained below. As a rule of thumb, the peak-to-peak inductor current ripple ( $\Delta i_{\rm L,pp}$ ) of a buck converter is typically designed to be between 20% and 40% of the full-load output current [56]. In this analysis, it is assumed that  $\Delta i_{\rm L,pp}$  is 30% (average of 20% and 40%) of the per-branch averaged current at full load, resulting in  $\alpha_{\rm I}=15\%$ . In addition, the peak-to-peak capacitor voltage ripple ( $\Delta v_{\rm C,pp}$ ) is assumed to be 10% of the mid-range capacitor voltage, following the rule of thumb for the small-ripple approximation to be valid, which yields  $\alpha_{\rm V}=5\%$ .

The normalized switch stress  $(M_{\rm S})$  of each topology is calculated under the assumption of negligible inductor current ripples and capacitor voltage ripples, as mentioned in Section III-A. Inductor current ripples can be ignored in the analysis of the normalized switch stress because their influence on switch RMS current stress is typically very small. For example, the RMS value of the current flowing through the high-side switch in a buck converter, which exhibits a pulsating current waveform with linear ripple, can be given as

$$I_{\rm d(rms)} = I_{\rm L} \sqrt{D} \sqrt{1 + \frac{1}{3} \alpha_{\rm I}^2}, \tag{41}$$

where  $I_{\rm L}$  is the average inductor current, D is the duty ratio, and  $\alpha_{\rm I}$  is the inductor current ripple ratio as defined in (6). Even if  $\alpha_{\rm I}=20\%$  (i.e.,  $\Delta i_{\rm L,pp}=0.4I_{\rm L}$ ), the RMS current  $(I_{\rm d(rms)})$  changes by only 0.7% ( $\sqrt{1+\frac{1}{3}\times0.2^2}=1.007$ ). Therefore, inductor current ripples are typically negligible in the calculation of switch RMS current stress. Similarly, capacitor voltage ripples are ignored in the calculation of switch voltage stress because they are assumed to be small compared to the mid-range voltages ( $\alpha_{\rm V}=5\%$ ).

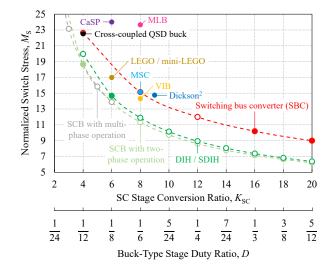

#### B. Analysis of Normalized Switch Stress

To better visualize the influence of the SC stage conversion ratio  $(K_{\rm SC})$ , Fig. 7 plots the normalized switch stress  $(M_{\rm S})$  of different topologies against their SC stage conversion ratio  $(K_{\rm SC})$ . Solid dots represent topologies with hardware

| Year Topology |                                                    | SC Stage Conversion         | Buck-Type Stage Conversion    | Buck-Type   | Stage Duty Ratio     | Complete                          |

|---------------|----------------------------------------------------|-----------------------------|-------------------------------|-------------|----------------------|-----------------------------------|

| Tear          | Торогоду                                           | Ratio $(K_{\mathrm{SC}}:1)$ | Ratio $(K_{\mathrm{buck}}:1)$ | Nominal (D) | Maximum $(D_{\max})$ | Soft-Charging?                    |

| 2005          | Series-capacitor buck with                         | 2:1                         | 24:1                          | 0.042       | 0.5                  | _ Yes                             |

|               | multi-phase operation [1]                          | 3:1                         | 16:1                          | 0.063       | 0.333                |                                   |

| 2011          | Series-capacitor buck with two-phase operation [2] | 4:1                         | 12:1                          | 0.083       | 0.5                  | Yes                               |

| 2020          | Crossed-coupled QSD buck [12]                      | 4:1                         | 12:1                          | 0.083       | 0.5                  | Yes                               |

| 2018          | DIH [4], [5]                                       | 6:1                         | 8:1                           | 0.125       | 0.5                  | Yes, with split-<br>phase control |

| 2019          | LEGO [7], [8]                                      | 6:1                         | 8:1                           | 0.125       | 1.0                  | No                                |

| 2023          | Mini-LEGO [18], [19]                               | 0.1                         | 0.1                           | 0.123       | 1.0                  | 110                               |

| 2020          | SDIH [13], [14]                                    | 6:1                         | 8:1                           | 0.125       | 0.5                  | Yes, with split-<br>phase control |

| 2021          | CaSP [15]                                          | 6:1                         | 8:1                           | 0.125       | 0.333                | Yes                               |

| 2020          | MLB [9], [10]                                      | 8:1                         | 6:1                           | 0.167       | 0.5                  | Yes                               |

| 2020          | VIB [20], [21]                                     | 8:1                         | 6:1                           | 0.167       | 0.25                 | No                                |

| 2022          | MSC [22], [23]                                     | 8:1                         | 6:1                           | 0.167       | 0.25                 | Yes                               |

| 2022          | Dickson <sup>2</sup> [24]                          | 9:1                         | 5.33:1                        | 0.188       | 0.333                | Yes                               |

| 2023          | 16-to-1 switching bus converter (SBC) [25], [26]   | 16:1                        | 3:1                           | 0.333       | 0.5                  | Yes                               |

| 2023          | 20-to-1 switching bus converter (SBC) [27], [28]   | 20:1                        | 2.4:1                         | 0.417       | 0.5                  | Yes                               |

FIGURE 7. Normalized switch stress  $(M_{\rm S})$  of state-of-the-art regulated hybrid SC topologies for 48-V-to-1-V conversion. Solid dots represent topologies with hardware demonstrations in previous literature, while hollow circles represent theoretically-existent topologies that have not been implemented previously. A lower normalized switch stress  $(M_{\rm S})$  is more desirable.

demonstrations in previous literature, while hollow circles

represent theoretically-existent topologies that have not been implemented previously. Some extendable topologies are plotted with dashed curves connecting different possible implementations at different SC stage conversion ratios. As shown in Fig. 7, with a larger SC stage conversion ratio, the buck-type stage duty ratio (D) can be extended.

The maximum achievable SC stage conversion ratio  $(K_{\rm SC(max)})$  of a regulated hybrid SC topology is limited by its maximum duty ratio  $(D_{\rm max})$  and the total conversion ratio  $(K_{\rm tot})$ . More specifically, the maximum output voltage of a regulated hybrid SC topology is given by

$$V_{\text{out(max)}} = \frac{D_{\text{max}}V_{\text{in}}}{K_{\text{SC}}}.$$

(42)

Since  $V_{\mathrm{out(max)}}$  must be greater than  $V_{\mathrm{out}}$ , the SC stage conversion ratio must not exceed

$$K_{\rm SC} < \frac{D_{\rm max}V_{\rm in}}{V_{\rm out}} = D_{\rm max}K_{\rm tot}.$$

(43)

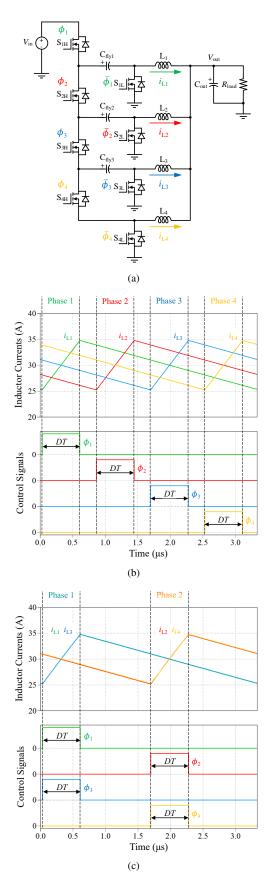

The series-capacitor-buck (SCB) topology was first proposed in [1] with multi-phase operation and then extended in [2] with two-phase operation. Fig. 8(a) shows a fourphase SCB converter as an example. In the multi-phase operation illustrated in Fig. 8(b), each inductor operates in an individual phase; in the two-phase operation illustrated in

TABLE 4. Performance comparison of state-of-the-art regulated hybrid SC topologies for 48-V-to-1-V conversion

| Year         | Topology                                                        | Normalized                       |               | malized Pas<br>nent Volum |              | Normalized Total Indu                | ctor Current Slew Rate              |

|--------------|-----------------------------------------------------------------|----------------------------------|---------------|---------------------------|--------------|--------------------------------------|-------------------------------------|

|              |                                                                 | Switch Stress $(M_{\rm S})^{-1}$ | $\beta = 500$ | $\beta = 100$             | $\beta = 50$ | Falling Slew Rate $(\widehat{SR}_F)$ | Rising Slew Rate $(\widehat{SR}_R)$ |

| 2005         | Series-capacitor buck with                                      | 31.6                             | 2.12          | 2.14                      | 2.17         | 1.04                                 | 11.5                                |

|              | multi-phase operation [1]                                       | 23.1                             | 2.08          | 2.12                      | 2.18         | 1.07                                 | 4.62                                |

| 2011         | Series-capacitor buck with two-phase operation [2]              | 18.7                             | 2.04          | 2.10                      | 2.19         | 1.09                                 | 5.45                                |

| 2020         | Crossed-coupled QSD buck [12]                                   | 24.2                             | 2.03          | 2.08                      | 2.13         | 1.09                                 | 5.45                                |

| 2018         | DIH* [4], [5]                                                   | 14.7                             | 2.02          | 2.40                      | 2.87         | 1.14                                 | 3.43                                |

| 2019<br>2023 | LEGO <sup>†</sup> [7], [8]<br>Mini-LEGO <sup>†</sup> [18], [19] | 17.6                             | 2.03          | 2.41                      | 2.89         | 1.14                                 | 8.00                                |

| 2020         | SDIH* [13], [14]                                                | 14.7                             | 2.02          | 2.40                      | 2.84         | 1.14                                 | 3.43                                |

| 2021         | CaSP [15]                                                       | 23.5                             | 1.95          | 2.02                      | 2.11         | 1.14                                 | 1.90                                |

| 2020         | MLB [9], [10]                                                   | 23.7                             | 1.88          | 2.03                      | 2.22         | 1.20                                 | 2.40                                |

| 2020         | VIB <sup>‡</sup> [20], [21]                                     | 14.3                             | 1.88          | 2.07                      | 2.3          | 1.20                                 | 0.60                                |

| 2022         | MSC [22], [23]                                                  | 15.1                             | 1.86          | 1.95                      | 2.06         | 1.20                                 | 0.60                                |

| 2022         | Dickson <sup>2</sup> [24]                                       | 14.8                             | 1.81          | 1.90                      | 2.01         | 1.23                                 | 0.96                                |

| 2023         | 16-to-1 switching bus converter (SBC) [25], [26]                | 10.2                             | 1.51          | 1.69                      | 1.91         | 1.50                                 | 0.75                                |

| 2023         | 20-to-1 switching bus converter (SBC) [27], [28]                | 8.99                             | 1.34          | 1.56                      | 1.84         | 1.71                                 | 0.34                                |

<sup>\*</sup> In the DIH [4], [5] and SDIH [13], [14] topologies, all flying capacitor voltage ripples are designed to have equal magnitude, which enables simple split-phase control timing. Since the mid-range voltages across different flying capacitors are different, the voltage ripple ratios of different flying capacitors in these two works are not uniform. Nevertheless, the normalized passive component volume  $(M_P)$  listed in this table assumes uniform voltage ripple ratios for all flying capacitors, which requires more complex split-phase control timing.

Fig. 8(c), the inductors are divided into two groups: the odd-numbered group and the even-numbered group, each operating in an individual phase with a 180° phase shift. Compared to the multi-phase operation, the two-phase operation can extend the maximum duty ratio from  $D_{\rm m-ph(max)}=\frac{1}{N}$  to  $D_{\rm 2-ph(max)}=\frac{1}{2},$  where N is the number of branches. Because the SC stage conversion ratio of a SCB converter is equal to its number of branches (i.e.,  $N=K_{\rm SC,m-ph}),$  the maximum duty ratio for multi-phase operation can be expressed as  $D_{\rm m-ph(max)}=\frac{1}{K_{\rm SC,m-ph}}.$  According to (43), the SC stage conversion ratio  $(K_{\rm SC,m-ph})$  for multi-phase operation is limited by

$$K_{\rm SC,m-ph} < D_{\rm m-ph(max)} K_{\rm tot} = \frac{K_{\rm tot}}{K_{\rm SC,m-ph}},$$

(44)

which can be rearranged as

$$K_{\rm SC, m-ph} < \sqrt{K_{\rm tot}}.$$

(45)

Similarly, the SC stage conversion ratio  $(K_{SC,2-ph})$  for two-phase operation is limited by

$$K_{\text{SC,2-ph}} < D_{\text{2-ph(max)}} K_{\text{tot}} = \frac{K_{\text{tot}}}{2}.$$

(46)

For 48-V-to-1-V conversion ( $K_{\rm tot}=48$ ), these upper limits are  $K_{\rm SC,m-ph}<6.9$  and  $K_{\rm SC,2-ph}<24$ , respectively. Since  $K_{\rm SC,m-ph}$  must be an integer and  $K_{\rm SC,2-ph}$  must be an even number, the maximum achievable SC stage conversion ratios for multi-phase operation and two-phase operation are  $K_{\rm SC,m-ph(max)}=6$  and  $K_{\rm SC,2-ph(max)}=22$ , respectively. As  $K_{\rm SC}$  increases, the voltage stress on all switches decreases while the current stress on most switches increases. Nevertheless, the increase in switch current stress does not offset the voltage stress reduction. Therefore, as shown in Fig. 7, the net result is that the normalized switch stress of a SCB converter decreases as  $K_{\rm SC}$  increases. This means that a SCB converter with a larger SC stage

<sup>†</sup> Small filter capacitors (C<sub>filter</sub>) are not taken into account in the capacitor volume analysis, although they are used in the hardware prototypes of the LEGO [7], [8] and Mini-LEGO [18], [19] topologies to filter the high-frequency pulsating current from the buck-type stage. Additionally, the charge-sharing loss between the filter capacitors and the flying capacitors is not captured in this analysis.

<sup>&</sup>lt;sup>‡</sup> In addition to flying capacitors, an intermediate bus capacitor ( $C_{\rm IB}$ ) is included in the capacitor volume calculation for the VIB topology [20], [21] as well. As mentioned in [20], [21], its value is chosen to be  $C_{\rm IB} = C_{\rm F}/2.34$ , where  $C_{\rm F}$  is the charge pump capacitance. The normalized voltage stress on  $C_{\rm IB}$  is 1/2. The charge-sharing loss between the intermediate bus capacitor and the flying capacitors is not captured in this analysis.

FIGURE 8. Four-branch SCB converter. (a) Schematic drawing. (b) Multiphase operation. (c) Two-phase operation.

conversion ratio has the theoretical potential of achieving higher efficiency. Compared to multi-phase operation, two-phase operation can better leverage the benefits of a larger SC stage conversion ratio since it extends the upper limit on the number of branches.

Although two-phase operation does result in a larger net output current ripple than multi-phase operation, this does not necessarily require a larger output capacitor in PoL applications. The size of the output capacitor in these applications is mainly dictated by transient performance requirements, such as limiting the maximum output voltage overshoot and undershoot. Typically, an output capacitor that is sufficiently large to meet these transient requirements also ensures that the steady-state output voltage ripple stays well below the maximum acceptable levels. Therefore, there is no need to increase the output capacitance when changing from multi-phase operation to two-phase operation. In fact, as will be explained in Section IV-D, since two-phase operation enables a faster transient response than multi-phase operation, the output capacitance can potentially be reduced.

The DIH [4], [5] and SDIH<sup>1</sup> [13], [14] topologies can be viewed as SCB topologies under two-phase operation, but with the inductors operating in the same phase merged into one large inductor by short-circuiting the odd-numbered and even-numbered switch nodes, respectively [14]. Given that the scaling law of magnetics favors larger components [57], combining multiple small inductors into one large inductor can typically improve the overall performance of magnetic components. However, short-circuiting the switch nodes can bring about the hard-charging of flying capacitors. In DIH and SDIH topologies with an even SC conversion ratio, this can only be overcome by the split-phase control [58]. The additional secondary phases introduced by the split-phase control reduce the effective duty ratio, resulting in slightly higher normalized switch stress for the DIH and SDIH topologies compared to a SCB topology under two-phase operation, as shown in Fig. 7. Due to the sensitivity of splitphase control timing to component sizing, either capacitors with high stability, such as Class I multilayer ceramic capacitors (MLCCs) that have lower energy densities, or active split-phase control [59], [60] must be used to ensure complete soft-charging.

The switching bus converter (SBC) [25], [26], [27], [28] merges a 2-to-1 SC front-end with two SCB modules through two *switching buses*, which allows for the removal of intermediate bus capacitors and redundant switches. Reference [26] provides a detailed illustration of the two-stage merging process in Fig. 4 and explains the advantages of the switching-bus-based architecture over the existing dc-bus-based architecture. Each downstream SCB module operates in the two-phase fashion illustrated in Fig. 8(c). Therefore, the SBC extends the maximum duty ratio ( $D_{\rm max}$ ) to 50% and similarly enables a larger SC stage conversion ratio. For 48-

<sup>&</sup>lt;sup>1</sup>The SDIH topology was first proposed in [13] under the alias *D-2L-ni\_Reg*.

V-to-1-V conversion ( $K_{\rm tot}=48$ ), the SC stage conversion ratio of the SBC cannot exceed

$$K_{\text{SC,SBC}} < D_{\text{max}} K_{\text{tot}} = 24,$$

(47)

according to (43). Given that the SBC merges a 2-to-1 SC front-end with two SCB modules under two-phase operation, the SC stage conversion ratio of the SBC must be a multiple of 4. Therefore, the maximum achievable SC stage conversion ratio is  $K_{\rm SC,SBC(max)}=20$ . As discussed in [26], the switching-bus-based architecture ensures complete soft-charging operation, thus avoiding the need for split-phase control. The switching bus concept was first introduced in [24] with the Dickson<sup>2</sup> topology. Other switching-bus-based topologies include MLB [9], [10] and CaSP [15] topologies.

Fig. 7 shows that, in general, increasing the SC stage conversion ratio of a regulated hybrid SC topology reduces its normalized switch stress, thereby improving efficiency. One possible concern about using the normalized switch stress as an indicator of efficiency is that it only captures the power losses in semiconductor switches but excludes the losses in flying capacitors and inductors. Flying capacitor equivalent series resistance (ESR) conduction loss is typically lower than 5% of total loss and is thereby negligible. However, inductor core loss and winding loss cannot be neglected. As the SC stage conversion ratio increases, the voltage stress  $(V_{\rm buck})$  on the subsequent buck-type stage is reduced, and therefore, the inductor size is decreased, resulting in a smaller core volume and lower dc resistance (DCR). This means that the inductor losses are reduced when the SC stage conversion ratio is increased. Consequently, the conclusion that increasing the SC stage conversion ratio is favorable for efficiency improvement holds, even with the inductor losses taken into consideration.

#### C. Analysis of Normalized Passive Component Volume

Fig. 9 shows the normalized passive component volume  $(M_{\rm P})$  of different topologies against their SC stage conversion ratio  $(K_{SC})$ , assuming an inductor current ripple ratio of  $\alpha_{\rm I} = 15\%$ , a capacitor voltage ripple ratio of  $\alpha_{\mathrm{V}}~=~5\%$ , and three different energy density ratios of capacitors to inductors:  $\beta = 500, 100, 50$ . Table 5 lists three practical examples for calculating the energy density ratio ( $\beta$ ) between capacitors and inductors. The commercial capacitor component TDK C3216X7R1H106K160AE [61] is rated at 50 V and is assumed to withstand a peak voltage of 25 V. Under a dc bias of 25 V, its capacitance derates to 3.5 μF. Therefore, the volumetric energy density of this capacitor component, when biased at a dc voltage of 25 V, is calculated as  $\frac{1}{2}CV^2$  divided by its volume, which is equal to 134 μJ/mm<sup>3</sup>. Similarly, the volumetric energy density of a commercial discrete inductor component, Coilcraft SLR1065-301KEC [62], at its saturation current (32 A) is calculated as  $\frac{1}{2}LI^2$  divided by its volume, yielding 0.256  $\mu$ J/mm<sup>3</sup>. Therefore, in this example, the energy density ratio between

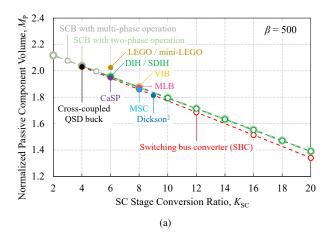

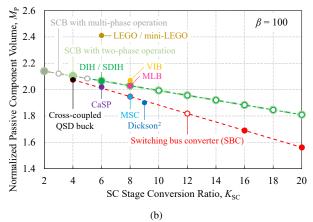

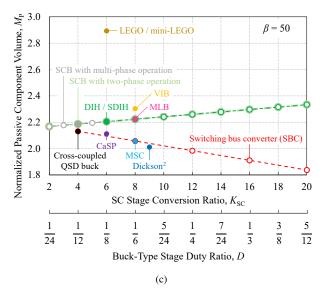

FIGURE 9. Normalized passive component volume  $(M_{\rm P})$  of state-of-theart regulated hybrid SC topologies for 48-V-to-1-V conversion  $(\alpha_{\rm I}=15\%,\,\alpha_{\rm V}=5\%)$ . (a)  $\beta=500$ . (b)  $\beta=100$ . (c)  $\beta=50$ . Solid dots represent topologies with hardware demonstrations in previous literature, while hollow circles represent theoretically-existent topologies that have not been implemented previously. A smaller normalized passive component volume  $(M_{\rm P})$  is more desirable.

these two commercial components is  $\beta_{\rm DL}=\frac{134}{0.256}=523$ , which is representative of the energy density ratios between

|  | TABLE 5. | Practical examples for ca | alculating the energ | v density ratio (£ | (3) between capacitors and induc | tors |

|--|----------|---------------------------|----------------------|--------------------|----------------------------------|------|

|--|----------|---------------------------|----------------------|--------------------|----------------------------------|------|

| Component         | Part Number                                              | Parameters                                                                        | Dimensions                              | Volumetric Energy Density                                                                |

|-------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|

| Capacitor         | TDK C3216X7R1H106K160AE [61]                             | Rated voltage: 50 V<br>Capacitance: 3.5 μF (@ 25 V)                               | $3.2\times1.6\times1.6~\mathrm{mm}^3$   | 134 μJ/mm <sup>3</sup> (@ 25 V)                                                          |

| Discrete Inductor | Coilcraft SLR1065-301KEC [62]                            | Saturation current: 32 A<br>Inductance: 275 nH (@ 32 A)<br>DCR: 0.48 mΩ           | $10.4\times8.0\times6.6~\text{mm}^3$    | 0.256 $\mu$ J/mm <sup>3</sup> (@ 32 A)<br>( $\beta_{\rm DL} = \frac{134}{0.256} = 523$ ) |

| Coupled Inductor  | Customized four-phase coupled inductor presented in [27] | Saturation current: 45 A Inductance: 260 nH* (@ 45 A) DCR: $0.16 \text{ m}\Omega$ | $18.5\times10.5\times3.2~\mathrm{mm}^3$ | 1.69 $\mu$ J/mm <sup>3</sup> (@ 45 A)<br>$(\beta_{\rm CL} = \frac{134}{1.69} = 79)$      |

<sup>\*</sup> Per-phase steady-state inductance (four-phase average value at D = 0.417).

commercial Class II MLCCs and discrete inductors. Note that this example assumes 50% voltage utilization of the capacitor component, meaning that it is assumed to operate at 50% of its rated voltage. When fully utilized, commercial Class II MLCCs can achieve an approximately 1000 times higher energy density compared to commercial discrete inductors [38]. Due to DC flux cancellation, coupled inductors can achieve the same per-phase steady-state inductance with a smaller core volume compared to discrete inductors [63]. As listed in Table 5, the customized four-phase coupled inductor presented in [27] achieves a volumetric energy of 1.69 µJ/mm<sup>3</sup> at its saturation current, which is 6.6 times higher than the commercial discrete inductor component. The energy density ratio between the commercial capacitor component (TDK C3216X7R1H106K160AE) and this customized four-phase coupled inductor is  $\beta_{\rm CL} = \frac{134}{1.69} = 79$ . These practical examples demonstrate that  $\beta = 500$  can be used in topological comparisons involving commercial discrete inductors, while  $\beta$  may decrease to 100 or even 50 when customized coupled inductors are used.

As can be seen in Fig. 9(a), when  $\beta = 500$  (for example, when discrete inductors are used), the normalized passive component volume  $(M_P)$  of the regulated hybrid SC topologies decreases as their SC stage conversion ratio  $(K_{SC})$ increases. The normalized passive component volume is the sum of the normalized inductor volume and the normalized capacitor volume (i.e.,  $M_{\rm P}=M_{\rm P,L}+M_{\rm P,C}$ ). Recall the first property of  $M_{

m P,L}$  and  $M_{

m P,C}$  mentioned at the end of Section III-E: as  $K_{\rm SC}$  increases,  $M_{\rm P,L}$  decreases and  $M_{\rm P.C}$  increases. However, since capacitors have much higher volumetric energy densities compared to discrete inductors, as demonstrated in Table 5, the increase in capacitor volume does not offset the inductor volume reduction. As a result, the total passive component volume decreases as the SC stage conversion ratio increases. This shows that when discrete inductors are used, increasing the SC stage conversion ratio of a regulated hybrid SC topology reduces its passive component volume, thereby improving power density.

As  $\beta$  decreases (for example, when coupled inductors with higher energy densities are used), the inductor volume