## **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Hardware Variability-Aware Embedded Software Adaptation

#### **Permalink**

https://escholarship.org/uc/item/6wg2g0t9

#### **Author**

Wanner, Lucas Francisco

## **Publication Date**

2014

Peer reviewed|Thesis/dissertation

## University of California Los Angeles

# Hardware Variability-Aware Embedded Software Adaptation

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Lucas Francisco Wanner

© Copyright by Lucas Francisco Wanner 2014

#### Abstract of the Dissertation

# Hardware Variability-Aware Embedded Software Adaptation

by

#### Lucas Francisco Wanner

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2014 Professor Mani B. Srivastava, Chair

With scaling of semiconductor fabrication technologies and the push towards deep sub-micron technologies, individual transistors are now composed by a small number of atoms. This makes it difficult to achieve precise control of manufacturing quality, with the added consequence that even slight differences in manufacturing can result in significant fluctuation in critical device and circuit parameters (such as power, performance, and error characteristics) of parts across the die, die-to-die and over time due to changing operating conditions and age-related wear-out. Instance and temperature-dependent variation, particularly in power consumption, has a direct impact on application quality and system lifetime for battery powered, energy constrained systems.

In this work we discuss software approaches to handle variability in power consumption of embedded systems. We characterize power variation in contemporary embedded processors, introduce tools for the evaluation of variability-aware software, and focus on two variability-aware software approaches: task activation control through variability-aware duty cycle scheduling and algorithmic choice.

We measured and characterized active and leakage power for a contemporary ARM Cortex M3 processor, and found that across a temperature range of 20–60°C

there is 10% variation in active power, and 14x variation in leakage power. As embedded processors in more advanced technologies become commonplace, the variations will increase significantly.

While contemporary hardware already suffers from variability, the evaluation of a variability-aware software stack faces two main challenges: first, commercially available platforms typically do not provide means to "sense" or discover variability. Second, even if this sensing capability was available, evaluating a software stack across a statistically significant number of hardware samples and ambient conditions would prove exceedingly costly and time consuming. We introduce VarEMU, an extensible framework for the evaluation of variability-aware software that provides users with the means to emulate variations in power consumption and fault characteristics and to sense and adapt to these variations in software.

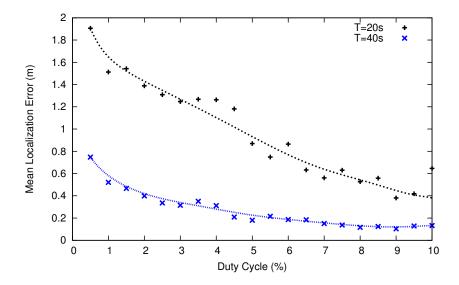

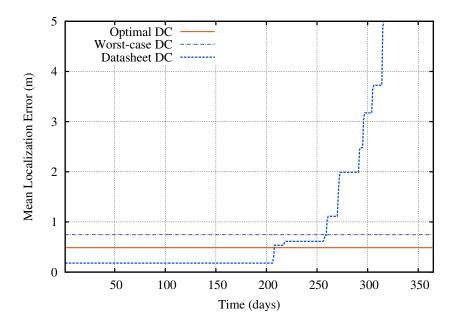

We introduce variability aware duty cycling methods and a duty cycle abstractions for embedded operating systems (TinyOS and FreeRTOS) that allow applications to to explicitly specify lifetime and minimum duty cycle or quality requirements for individual tasks, and dynamically adjust duty cycle rates and task activation schedules so that overall quality of service is maximized in the presence of power variability. We show that variability-aware duty cycling yields a 3–22x improvement in total active time over schedules based on worst-case estimations of power, with an average improvement of 6.4x across a wide variety of deployment scenarios based on collected temperature traces. Conversely, datasheet power specifications fail to meet required lifetimes by 7–15%, with an average 37 days short of a required lifetime of one year. Finally, we show that a target localization application using variability-aware duty cycle yields a 50% improvement in quality of results over one based on worst-case estimations of power consumption.

In addition to task activation control though duty cycling, a *choice* of software to be executed provides further opportunities for optimization. We introduce ViRUS (Virtual function Replacement Under Stress), an application runtime sup-

port system that adjusts service quality according to variability-aware policies. In ViRUS, different code paths implement the same function with varying quality-of-service for different energy costs. Mutations from one version to another are triggered by monitoring vectors of variability and energy stress. We demonstrate ViRUS with a framework for transparent function replacement in shared libraries and a polymorphic version of the standard C math library in Linux. Application case studies show how ViRUS can tradeoff upwards of 4% degradation in application quality for a band of upwards of 50% savings in energy consumption.

The dissertation of Lucas Francisco Wanner is approved.

Mario Gerla

Puneet Gupta

Jens Palsberg

Mani B. Srivastava, Committee Chair

University of California, Los Angeles 2014

## Table of Contents

| 1 | Intr | oducti | ion                                          | 1  |

|---|------|--------|----------------------------------------------|----|

|   | 1.1  | Contr  | ibutions                                     | 3  |

|   | 1.2  | Relate | ed Work                                      | 5  |

|   |      | 1.2.1  | Task Activation Control                      | 5  |

|   |      | 1.2.2  | Selective use of Hardware Resources          | 6  |

|   |      | 1.2.3  | Adaptation of Hardware Parameters            | 7  |

|   |      | 1.2.4  | Adaptation of Software Parameters            | 7  |

|   |      | 1.2.5  | Dynamic Recompilation                        | 8  |

|   |      | 1.2.6  | Algorithmic Choice                           | 9  |

|   |      | 1.2.7  | Summary of Related Work                      | 10 |

|   | 1.3  | Organ  | nization                                     | 12 |

| 2 | Pov  | ver Co | nsumption Variability in Embedded Processors | 14 |

|   | 2.1  | Exper  | imental Setup                                | 14 |

|   | 2.2  | Sleep  | Mode Power Consumption                       | 15 |

|   |      | 2.2.1  | Analytical Modeling of Sleep Power           | 15 |

|   |      | 2.2.2  | Experimental Measurements                    | 18 |

|   | 2.3  | Active | e Mode Power Consumption                     | 20 |

|   |      | 2.3.1  | Analytical Modeling of Active Power          | 21 |

|   |      | 2.3.2  | Experimental Measurements                    | 22 |

|   | 2.4  | Power  | Projections for Advanced Technologies        | 24 |

| 3 | Eva  | luatio | n of Variability-Aware Software              | 27 |

|   | 3.1             | VarEN                                            | MU Architecture and Implementation | 28                                                                                              |

|---|-----------------|--------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------|

|   |                 | 3.1.1                                            | Cycle and Time Accounting          | 29                                                                                              |

|   |                 | 3.1.2                                            | Energy Accounting                  | 32                                                                                              |

|   |                 | 3.1.3                                            | NBTI Aging Model                   | 33                                                                                              |

|   |                 | 3.1.4                                            | Aging-aware Power and Delay Model  | 34                                                                                              |

|   |                 | 3.1.5                                            | Faults                             | 36                                                                                              |

|   | 3.2             | Softwa                                           | are Interfaces                     | 37                                                                                              |

|   |                 | 3.2.1                                            | Interaction with Emulated Software | 38                                                                                              |

|   |                 | 3.2.2                                            | Software Interface for Linux       | 39                                                                                              |

|   | 3.3             | Exper                                            | iments and Results                 | 45                                                                                              |

|   |                 | 3.3.1                                            | Time Accounting Accuracy           | 45                                                                                              |

|   |                 | 3.3.2                                            | Runtime Overheads                  | 47                                                                                              |

|   |                 |                                                  |                                    |                                                                                                 |

| 4 | Var             | iability                                         | y-Aware Duty Cycling               | 49                                                                                              |

| 4 | <b>V</b> ar 4.1 |                                                  | y-Aware Duty Cycling               | <b>49</b> 51                                                                                    |

| 4 |                 |                                                  |                                    |                                                                                                 |

| 4 |                 | Duty                                             | Cycle Scheduling                   | 51                                                                                              |

| 4 |                 | Duty 4.1.1                                       | Cycle Scheduling                   | 51<br>52                                                                                        |

| 4 |                 | Duty 4.1.1 4.1.2 4.1.3                           | Cycle Scheduling                   | <ul><li>51</li><li>52</li><li>53</li></ul>                                                      |

| 4 | 4.1             | Duty 4.1.1 4.1.2 4.1.3                           | Cycle Scheduling                   | <ul><li>51</li><li>52</li><li>53</li><li>54</li></ul>                                           |

| 4 | 4.1             | Duty 4.1.1 4.1.2 4.1.3 Variable 4.2.1            | Cycle Scheduling                   | <ul><li>51</li><li>52</li><li>53</li><li>54</li><li>55</li></ul>                                |

| 4 | 4.1             | Duty 4.1.1 4.1.2 4.1.3 Variable 4.2.1            | Cycle Scheduling                   | <ul><li>51</li><li>52</li><li>53</li><li>54</li><li>55</li><li>59</li></ul>                     |

| 4 | 4.1             | Duty 4.1.1 4.1.2 4.1.3 Variab 4.2.1 Duty         | Cycle Scheduling                   | <ul><li>51</li><li>52</li><li>53</li><li>54</li><li>55</li><li>59</li><li>67</li></ul>          |

| 4 | 4.1             | Duty 4.1.1 4.1.2 4.1.3 Variable 4.2.1 Duty 4.3.1 | Cycle Scheduling                   | <ul> <li>511</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>67</li> <li>69</li> </ul> |

| D. | ofono | 196                                          |

|----|-------|----------------------------------------------|

| 6  | Con   | clusions                                     |

|    | 5.7   | Discussion                                   |

|    |       | 5.6.4 Application case studies               |

|    |       | 5.6.3 Variable Quality Standard Math Library |

|    |       | 5.6.2 Microbenchmarks                        |

|    |       | 5.6.1 Memory Usage                           |

|    | 5.6   | Evaluation                                   |

|    | 5.5   | Variability Monitor                          |

|    | 5.4   | ViRUS controller                             |

|    | 5.3   | Library Generation                           |

|    | 5.2   | System Design for Algorithmic Choice         |

|    | 5.1   | System-Driven Algorithmic Choice 8           |

| 5  | Var   | ability-Aware Algorithmic Choice             |

|    | 4.4   | Application Results                          |

## LIST OF FIGURES

| 1.1 | ITRS projections of power variability                                    | 2  |

|-----|--------------------------------------------------------------------------|----|

| 2.1 | Experimental setup                                                       | 16 |

| 2.2 | Sleep power at room temperature                                          | 18 |

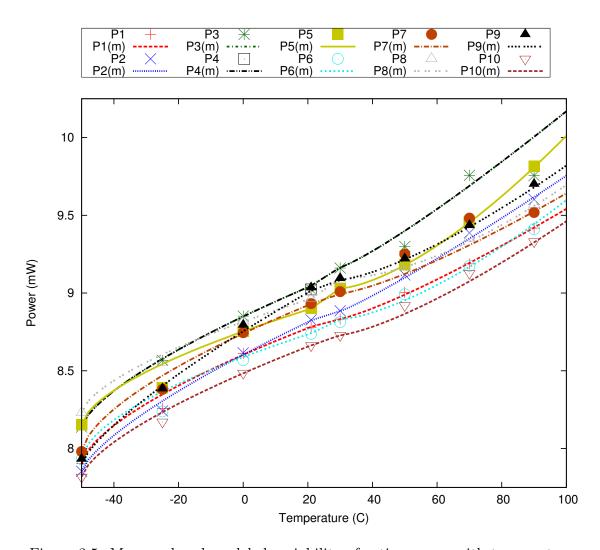

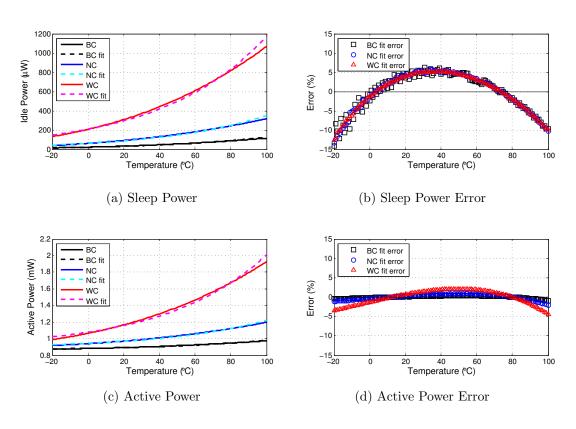

| 2.3 | Measured and modeled variability of sleep power with temperature         | 19 |

| 2.4 | Active power at room temperature                                         | 23 |

| 2.5 | Measured and modeled variability of active power with temperature        | 23 |

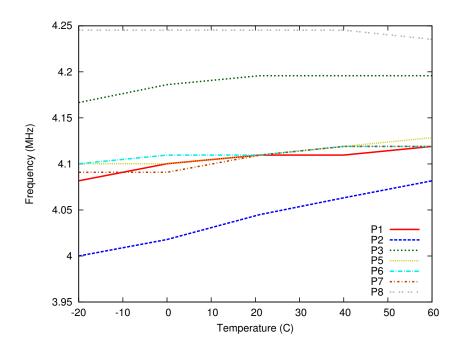

| 2.6 | Measured frequency variation with temperature                            | 24 |

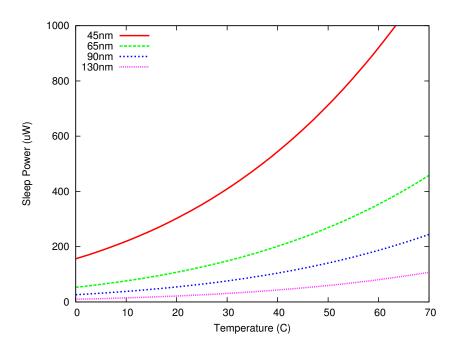

| 2.7 | Sleep power projection across technologies                               | 26 |

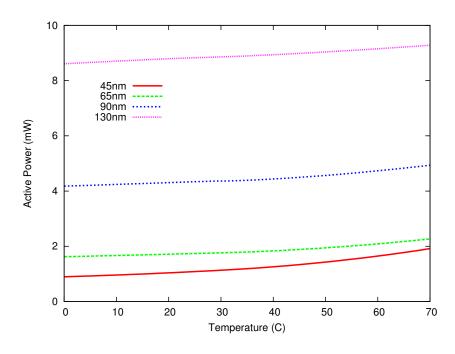

| 2.8 | Active power projection across technologies                              | 26 |

| 3.1 | VarEMU Architecture                                                      | 41 |

| 3.2 | Sleep Time Accounting                                                    | 42 |

| 3.3 | Stuck-at fault in the multiply instruction                               | 43 |

| 3.4 | VarEMU register layout                                                   | 43 |

| 3.5 | Linux application using VarEMU                                           | 44 |

| 3.6 | Time Accounting Accuracy                                                 | 47 |

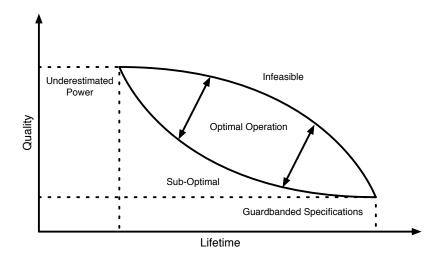

| 4.1 | Potential results of variability in terms of system quality and lifetime | 50 |

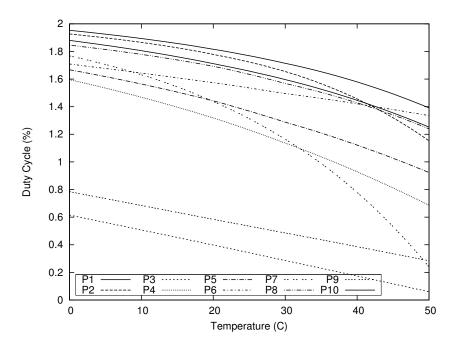

| 4.2 | Allowable duty cycle across SAM3U instances and temperature .            | 51 |

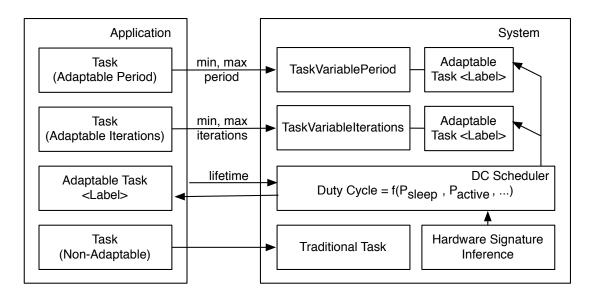

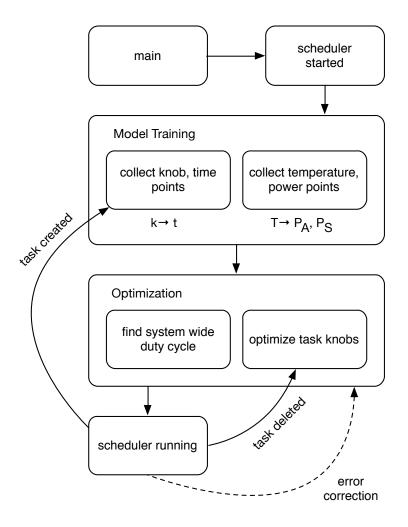

| 4.3 | Designing a software stack for variability-aware duty cycling            | 55 |

| 4.4 | System architecture for variability-aware duty cycle scheduling in       |    |

|     | TinyOS                                                                   | 57 |

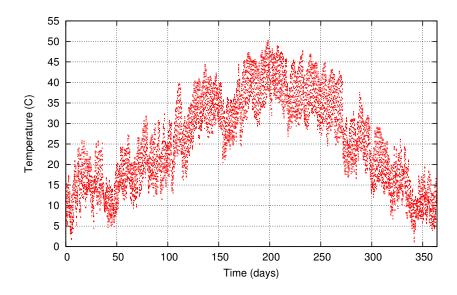

| 4.5 | Weather profile for Death Valley, CA, 2010                               | 60 |

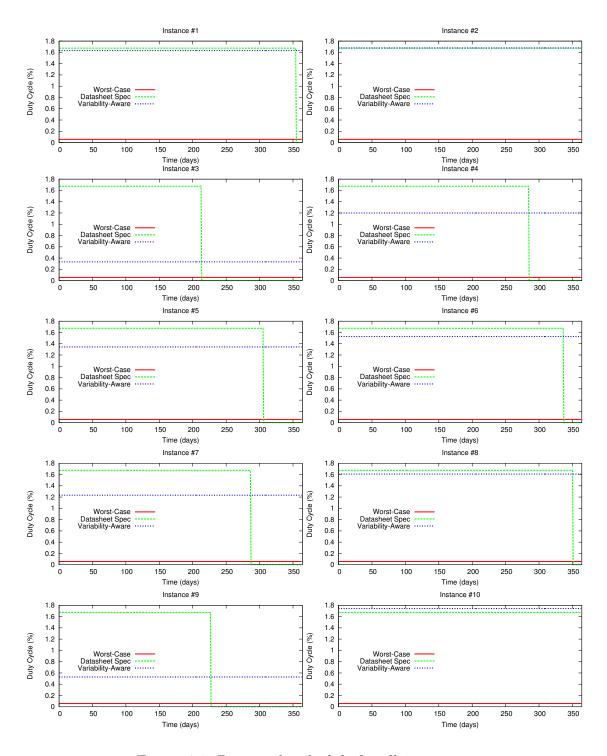

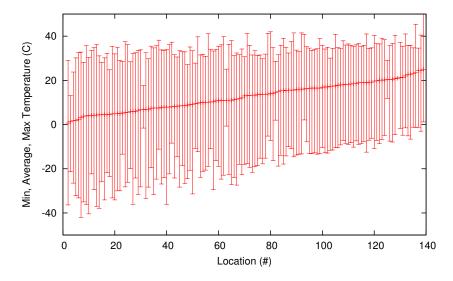

| 4.6  | Duty cycle schedule for all instances                               | 61 |

|------|---------------------------------------------------------------------|----|

| 4.7  | Results from duty cycle regimes across all instances                | 62 |

| 4.8  | Temperature profile for test locations                              | 63 |

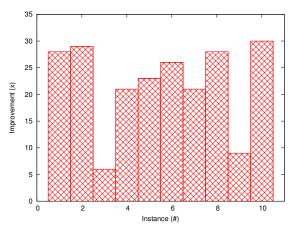

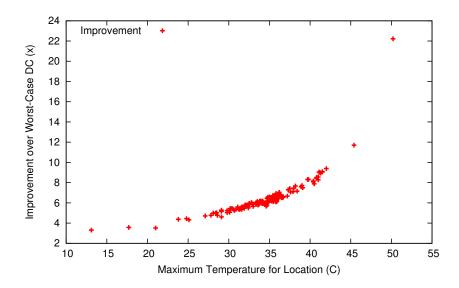

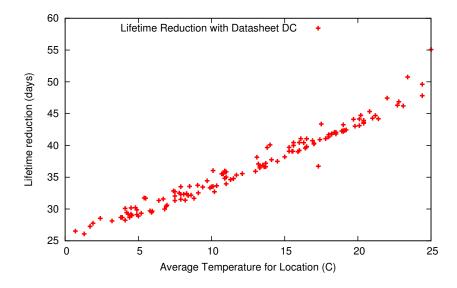

| 4.9  | Improvement over worst-case duty cycle for test locations           | 64 |

| 4.10 | Lifetime reduction with DC based on datasheet                       | 64 |

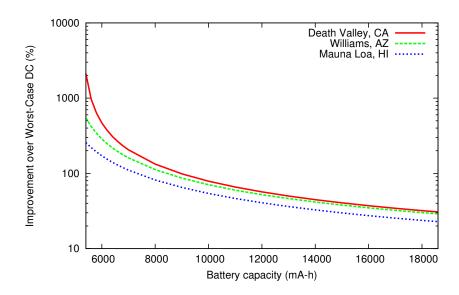

| 4.11 | Improvement over worst-case DC across battery capacities            | 65 |

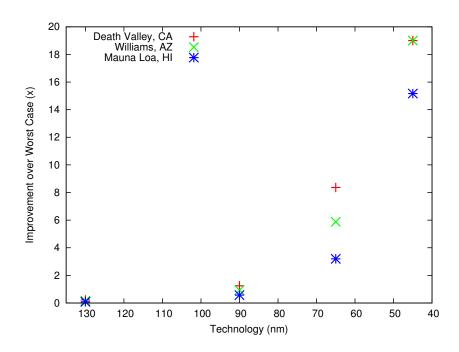

| 4.12 | Projection of improvement with scaling of technology                | 66 |

| 4.13 | VaRTOS Task and Application Example                                 | 70 |

| 4.14 | Modeling sleep and active power through linearization               | 73 |

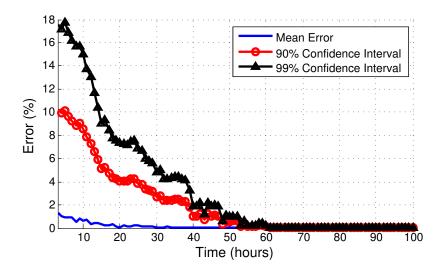

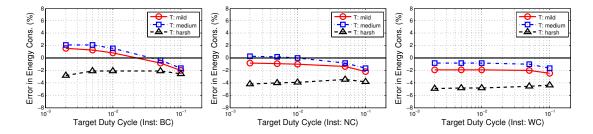

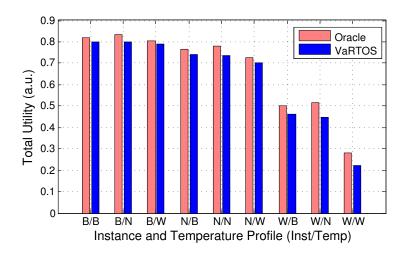

| 4.15 | Error convergence for sleep power modeling                          | 74 |

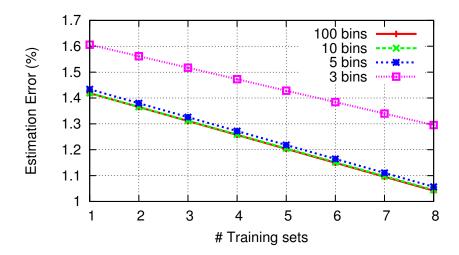

| 4.16 | Error in average power estimation for varying number of training    |    |

|      | years and histogram bins                                            | 75 |

| 4.17 | VaRTOS state chart                                                  | 77 |

| 4.18 | Error in energy consumption for various optimal duty cycles across  |    |

|      | deployment scenarios                                                | 79 |

| 4.19 | Total utility for VaRTOS vs. oracle system                          | 80 |

| 4.20 | Mean localization error across duty cycles                          | 82 |

| 4.21 | Mean localization with variability-aware, worst-case and datasheet- |    |

|      | based duty cycle schedules                                          | 83 |

| 5.1  | Exposing multiple functions with mismatched signatures              | 91 |

| 5.2  | Mutator function templates                                          | 92 |

| 5.3  | Constructor template. When the library is loaded prior to reaching  |    |

|      | the application's main function, the constructor for each function  |    |

|      | is executed                                                         | 93 |

| 5.4  | Function replacement algorithm                                      | 97   |

|------|---------------------------------------------------------------------|------|

| 5.5  | Variability Monitor Architecture                                    | 98   |

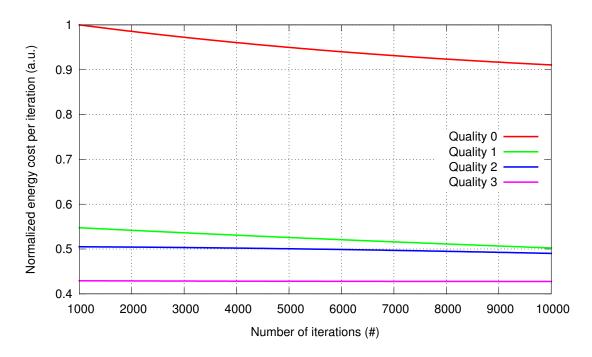

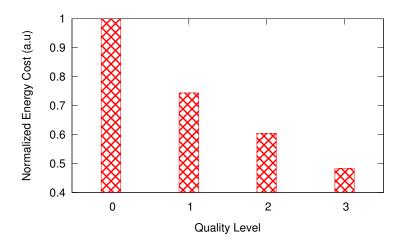

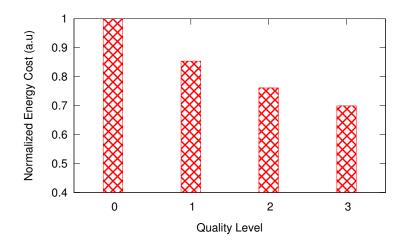

| 5.6  | Normalized energy cost of Whetstone iterations with different qual- |      |

|      | ity versions                                                        | 107  |

| 5.7  | Normalized energy cost of blackscholes with different quality       |      |

|      | versions                                                            | 109  |

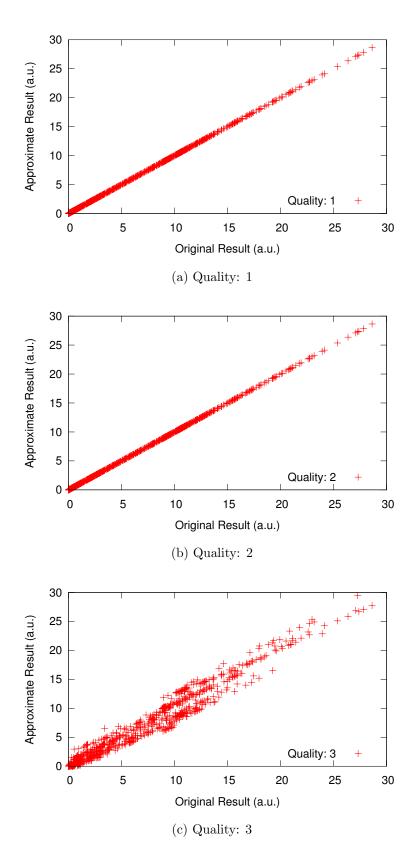

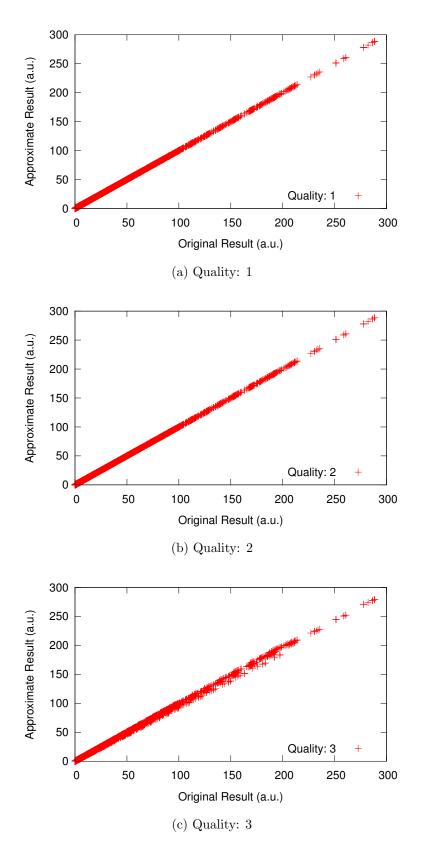

| 5.8  | Output for blackscholes with different quality levels               | 110  |

| 5.9  | Normalized energy cost of swaptions with different quality versions | s112 |

| 5.10 | Output for swaptions with different quality levels                  | 114  |

## LIST OF TABLES

| 1.1 | Classification of Software Adaptation Methods                       | 11  |

|-----|---------------------------------------------------------------------|-----|

| 2.1 | Sleep power model parameters across technologies                    | 25  |

| 2.2 | Active mode power model parameters across technologies              | 25  |

| 3.1 | Runtime overheads for VarEMU and the VarEMU kernel extensions       | 48  |

| 4.1 | Summary of Results for Variability-Aware Duty Cycling               | 59  |

| 5.1 | ViRUS configuration rules example. Each rule associates a func-     |     |

|     | tion with a vector of sensitivity (sensor and range) and acceptable |     |

|     | quality levels. Rules are resolved in order of priority             | 95  |

| 5.2 | ViRUS runtime overheads                                             | 102 |

| 5.3 | ViRUS math library memory usage                                     | 104 |

| 5.4 | NRMSE and MAPE for blackscholes                                     | 111 |

| 5.5 | NRMSE and MAPE for swaptions                                        | 112 |

#### ACKNOWLEDGMENTS

I would like to extend my to gratitude the many people that helped and guided me through my journey as a Ph.D. student.

To my advisor Mani Srivastava, for ideas, support, encouragement, and constructive criticism that not only made this work possible, but also immensely enriched my whole experience at UCLA.

To Puneet Gupta, for advice and guidance that helped shape and refine much of this work.

To my committee members Jens Palsberg and Mario Gerla for their time, interest, and valuable comments.

To Rajesh Gupta, Nikil Dutt, Subhasish Mitra, and my colleagues in the NSF Variability Expedition, for early feedback on ideas and results and for forming an inquisitive community around the problem of hardware variability.

To my friends, colleagues, and collaborators in the NESL and NanoCAD labs at UCLA, especially Rahul Balani, Paul Martin, Liangzhen Lai, Salma Elmalaki, Charwak Apte, Sadaf Zahedi, Gauresh Rane, Haksoo Choi, Newton Truong, Henry Herman, Thomas Schmid, Zainul Charbiwala, and Supriyo Chakraborty.

To my mother Filomena Hoff and my sister Joice Wanner, for their constant support that travels the furthest distances.

Finally, to my wife Gabriella Simon Maia, for making me happy every day.

This material is based upon work supported in part by CAPES/Fulbright grant #1892/07-0 and by the NSF under awards # CNS-0905580 and CCF-1029030. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of these agencies.

## $V_{ITA}$

| 2001-2004 | Undergraduate Research Assistant, Computer Science Department, Federal University of Santa Catarina, Brazil |

|-----------|-------------------------------------------------------------------------------------------------------------|

| 2004      | B.S. (Computer Science), Federal University of Santa Catarina                                               |

| 2004-2005 | Teaching Assistant, Computer Science Department, Federal                                                    |

| 2004–2008 | University of Santa Catarina, Brazil  Research Assistant, Software/Hardware Integration Labora-             |

|           | tory, Federal University of Santa Catarina                                                                  |

| 2006      | M.S. (Computer Science), Federal University of Santa Catarina                                               |

| 2008-2012 | Fulbright/CAPES Scholar                                                                                     |

| 2010-2011 | Teaching Assistant, Henry Samueli School of Engineering and<br>Applied Science, UCLA                        |

| 2008–2014 | Research Assistant, Networked and Embedded Systems Labo-                                                    |

|           | Treesearch Treesearch, Treesearch and Emisearch Systems East                                                |

## **PUBLICATIONS**

Lucas F. Wanner, Salma Elmalaki, Liangzhen Lai, Puneet Gupta, and Mani B. Srivastava, VarEMU: An emulation testbed for Variability-Aware Software, In Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS'13), 2013.

Paul Martin, Lucas F. Wanner, and Mani B. Srivastava, Runtime Optimization of System Utility with Variable Hardware, Submitted to *IEEE Transactions on Embedded Computing Systems (TECS)*,2013.

Lucas F. Wanner, Charwak Apte, Rahul Balani, Puneet Gupta, Mani B. Srivastava, Hardware Variability-Aware Duty Cycling for Embedded Sensors, In *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2013.

Rahul Balani, Lucas F. Wanner, and Mani B. Srivastava, Fast Iterative Optimization in Networked Cyber-Physical Systems, In *ACM Transactions in Embedded Computing Systems (TECS)*, 2013.

Yuwen Sun, Lucas F. Wanner, and Mani B Srivastava, Low-cost Estimation of Sub-system Power, In *International Green Computing Conference (IGCC'12)*, San Jose, California, June 2012.

Lucas F. Wanner, Rahul Balani, Sadaf Zahedi, Charwak Apte, Puneet Gupta, Mani B. Srivastava, Variability-Aware Duty Cycle Scheduling in Long Running Embedded Sensing Systems, In *Design, Automation and Test in Europe (DATE)*, Grenoble, France, March 2011.

Rahul Balani, Kaisen Lin, Lucas F. Wanner, Jonathan Friedman, Rajesh K. Gupta, Mani B. Srivastava, Programming Support for Distributed Optimization and Control in Cyber-Physical Systems, In *International Conference on Cyber-Physical Systems (ICCPS)*, Chicago, IL, April 2011.

Lucas F. Wanner, Charwak Apte, Rahul Balani, Puneet Gupta, Mani B. Srivastava, A Case for Opportunistic Embedded Sensing In Presence of Hardware

Power Variability, In Workshop on Power Aware Computing and Systems (Hot-Power '10), Vancouver, Canada, October 2010.

Lucas F. Wanner and Antônio A. Fröhlich, Operating System Support for Wireless Sensor Networks, In: *Journal of Computer Science*, 4(4):272-281, 2008.

Geovani R. Wiedenhoft, Lucas F. Wanner, Giovani Gracioli and Antônio Augusto Fröhlich, Power Management in the EPOS System, In: *SIGOPS Operating Systems Review*, 42(6):71-80, 2008.

Rafael Pereira Pires, Lucas F. Wanner and Antônio Augusto Fröhlich, A Framework for Configuration and Assembly of Routing Protocols for Wireless Ad-Hoc Networks, In *International Conference and Workshop on Ambient Intelligence and Embedded Systems*, Kiel, Germany, 2008.

Rafael Pereira Pires, Lucas F. Wanner and Antônio Augusto Fröhlich, An Efficient Calibration Method for RSSI-based Location Algorithms, In: *Intl. IEEE Conference on Industrial Informatics*, Daejeon, Korea, 2008.

Lucas F. Wanner, Augusto Born de Oliveira, and Antonio Augusto Frohlich. Configurable Medium Access Control for Wireless Sensor Networks. In *International Embedded System Symposium*, pages 401–410, Irvine, CA, USA, May 2007.

Augusto B. de Oliveira, Lucas Wanner, and Antonio Augusto Frohlich. Integrating Wireless Sensor Networks and the Grid through POP-C++. In *International Embedded System Symposium*, pages 411–420, Irvine, California, US, May 2007.

Arliones Stevert Hoeller Junior, Lucas F. Wanner, and Antonio Augusto Frohlich.

A Hierarchical Approach For Power Management on Mobile Embedded Systems. In 5th IFIP Working Conference on Distributed and Parallel Embedded Systems, pages 265–274, Braga, Portugal, October 2006.

Hugo Marcondes, Arliones Stevert Hoeller Junior, Lucas F. Wanner, and Antonio Augusto Frohlich. Operating Systems Portability: 8 bits and beyond. In 11th IEEE International Conference on Emerging Technologies and Factory Automation, pages 124–130, Prague, Czech Republic, 2006.

Lucas F. Wanner, Arliones Stevert Hoeller Junior, Augusto B. de Oliveira, and Antonio A. Frohlich. Operating System Support for Data Acquisition in Wireless Sensor Networks. In 11th IEEE International Conference on Emerging Technologies and Factory Automation, pages 582–585, Prague, Czech Republic, 2006.

Lucas F. Wanner, Arliones S. Hoeller Junior, Fauze V. Polpeta, and Antonio Augusto Frohlich. Operating System Support for Handling Heterogeneity in Wireless Sensor Networks. In 10th IEEE International Conference on Emerging Technologies and Factory Automation, Catania, Italy, September 2005.

## CHAPTER 1

## Introduction

Energy management methods in embedded systems rely on knowledge of power consumption of the underlying computing platform in various modes of operation. These power specifications are usually derived from the datasheets. Unfortunately, the microelectronic substrate is increasingly plagued by variability, especially in power consumption [BKN03, ITR], both across multiple instances of a system and in time over its usage life. As a result the "datasheet power specifications" are heavily guardbanded [JKS09, GKM05] leaving much of the energy potential or application quality untapped. The major sources of variability are:

- Semiconductor manufacturing. Scaling of physical dimensions faster than the optical wavelengths or equipment tolerances used in the semiconductor manufacturing line has led to increased process variability [Ber06, CGK02] which makes integrated circuit designs unpredictable.

- Environment. Ambient condition variability (e.g., voltage in unregulated power supplies and temperature).

- Aging. Transistor aging (e.g., due to negative bias temperature instability [ZVR09]) can change system power/performance over time.

- *Vendor*. Multi-sourcing of parts with identical specification from different vendors is common and can cause significant variation.

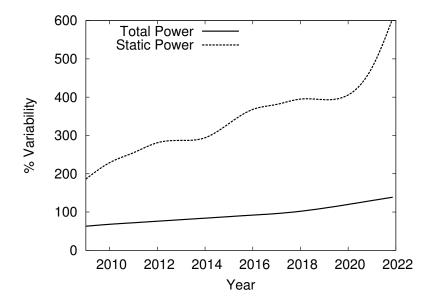

Figure 1 [ITR] shows that the manufacturing variability in sleep (or static) power and total power is likely to grow over 500% and 100% respectively in the

Figure 1.1: ITRS projections of power variability

next decade. Variability has been typically addressed by process, device and circuit designers with software designers remaining isolated from it by a rigid hardware-software interface, which leads to decreased chip yields and increased costs [JKS09].

Recently there have been some efforts to handle variability at higher layers of abstraction. For instance, software fault tolerance schemes have been used to address voltage [RGS09] or temperature variability [CCF07]. Hardware "signatures" are used to guide adaptation in quality-sensitive multimedia applications in [PGS11]. In embedded sensing, [MTY06, GM07] propose sensor node deployment schemes based on the variability in power across nodes.

In this work we discuss power variability for off-the-shelf embedded processors, and software approaches to handle variability in power consumption of embedded systems. In particular, we focus on instance and temperature dependent power variability that already manifests in contemporary embedded processors [BDS11]. For this, we (i) measure and characterize power for a contemporary embedded processor based on an ARM Cortex M3 core; (ii) derive projections of sleep and

active power for embedded processors with scaling of manufacturing technology; (iii) build a framework that enables testing and evaluation of variability-aware software strategies under different conditions; (iv) evaluate variability-aware duty cycle and reward-based scheduling methods under a variety of deployment scenarios and across projected future variation; (v) study the impact of duty cycle adaptation to application quality of inference; (vi) show how system-driven algorithmic choice can be leveraged to explore quality and energy cost tradeoffs in embedded applications.

#### 1.1 Contributions

The contributions of our work are the following:

- Measurement, characterization, and projections of power variation for embedded processors. Our measurements across several instances of a contemporary ARM Cortex M3 processor show that across a temperature range of 20–60°C there is 10% variation in active power, and 14x variation in leakage power.

- Design and implementation of VarEMU, an extension to the QEMU virtual machine monitor that serves as a framework for the evaluation of variability-aware software techniques. VarEMU provides users with the means to emulate variations in power consumption and in fault characteristics and to sense and adapt to these variations in software. Through the use (and dynamic change) of parameters in a power model, users can create virtual machines that feature both static and dynamic variations in power consumption.

- Proposal, implementation, and analysis of variability-aware duty cycle adaptation methods. We show that variability-aware duty cycling yields a 3–22x improvement in total active time over schedules based on worst-case estima-

tions of power, with an average improvement of 6.4x across a wide variety of deployment scenarios based on collected temperature traces.

- Embedded operating system extensions for variability-aware duty-cycle adaptation. Two implementations, one based on the TinyOS operating system for embedded sensors and one based on the FreeRTOS real-time kernel, allow applications to express elasticity through control knobs that the operating system can tune to adjust task duty cycle, quality, and energy cost. In both implementations, a variability-aware duty cycle scheduler dynamically adjusts application control knobs so that a system-wide allowable duty cycle rate is met and overall quality-of-service is maximized.

- Analysis of the impact of duty cycle to quality of sensing. We show that

a target localization application using variability-aware duty cycle yields a

50% improvement in quality of results over one based on worst-case estimations of power consumption.

- Design an implementation of ViRUS (Virtual function Replacement Under Stress), a framework for system-driven variability-aware algorithmic choice. ViRUS allows the runtime system to switch between blocks of code that perform roughly equivalent functionality at different quality-of-service levels when the system is under stress be it in the form of scarce energy resources, temperature emergencies, or various vectors of environmental and process variability with the ultimate goal of energy efficiency. We present a framework for function replacement in shared libraries in Linux demonstrated with a polymorphic version of the C math runtime library. We show how this system can help users in developing and analyzing tradeoffs between accuracy and energy consumption with variable hardware, and reduce the energy consumption with user-controlled quality-of-service degradation.

#### 1.2 Related Work

Variability, thus far, has been largely addressed by process, device and circuit designers. In this context, prior work that addresses variability can be classified into (i) statistical design approaches [NS05, DBM05, KPR06], (ii) post silicon compensation and correction [GC07, KS07, TKN02], and (iii) variation avoidance [CPR04, BMR07, GBR07]. Our work differs in that it addresses hardware variability in the software layer. The closest resemblance is with [PGS11], which proposes adapting software video codec configurations based on hardware signatures. In the context of embedded sensing, our work is closest to [MTY06, GM07], which propose sensor node deployment methodologies based on variability in leakage power across different nodes.

The range of possible responses that the software can make in response to variability include: alter the computational load by adjusting task activation; use a different set of hardware resources (e.g. use instructions that avoid a faulty module or minimize use of a power hungry module); change software parameters or the hardware's operational setting (e.g., tune software-controllable control knobs such as voltage/frequency; and change the code that performs a task, either by dynamic recompilation or through algorithmic choice.

#### 1.2.1 Task Activation Control

Variations in power consumption can be interpreted as changes in resource (energy) usage (and hence availability). Adaptation of work to resource availability is a common theme in embedded and real-time systems. In its simplest form, adaptation can be relegated to applications, with minimal system support. The system may, for example, keep track of energy consumption and notify applications to adapt in order to conserve energy when needed to meet a desired lifetime [FS99]. In energy harvesting, tasks can be adapted to cope with fluctuating

energy availability [KHZ07]. Likewise, in sensing applications, adaptive sampling mechanisms are used to minimize power consumption with different levels of data quality [AAG07].

In imprecise computation [LSL94], each task is designed to produce usable, approximate results whenever resource scarcity (e.g. due to transient failures or overloads) prevents the task from producing its desired precise result. Imprecise computation has been explored in the context of energy-aware systems, where tasks may be interrupted, producing an approximate but usable result, according to energy availability and lifetime requirements [CAC06, WWG08].

The issue of distributing available energy resources to tasks has also been explored in the literature. ECOSystem [ZEL02] introduced the concept of "Currentcy" to allocate energy resources to tasks. The system periodically distributes Currentcy to tasks, which adjust their workload according to availability. Cinder [RSL09] is an energy-aware system for mobile computing devices that features a Capacitor abstraction associated with tasks. Each capacitor represents a task's right to request energy from the system to perform its operations.

In chapter 4, we present system software strategies for variability-aware task activation control in duty cycled embedded systems. We present software stacks where applications define lifetime requirements and task activation bounds, and the variability-aware scheduler activates tasks at the maximum rate that meets that lifetime.

#### 1.2.2 Selective use of Hardware Resources

One strategy for coping with variability is to selectively choose units to perform a task from a pool of available hardware. ERSA (Error Resilient System Architecture) [LCB10] is an architecture for probabilistic applications that consists of small number of highly reliable cores, together with a large number of cores that

are less reliable but account for most of the computation capacity. An application can be divided into control-intensive resource management code that needs to be executed on error-free hardware while data-intensive computations are often more error-tolerant.

Random access memory chips are also subject to variations in power consumption [GKGar]. Variability-aware Memory Virtualization (VaMV) defines a memory allocation architecture that allows programmers to partition their address space into regions with different power, performance, and fault-tolerance guarantees [BDN12]. Over-dimensioned register files (for example, in Graphical Processing Units used for general-purpose computation) may also be allocated in a variability-aware fashion in order to minimize errors and power consumption [RBG13].

#### 1.2.3 Adaptation of Hardware Parameters

Variation-aware adjustment of hardware operating point, whether in context of adaptive circuits (e.g., [BKN03, GBR07, APM05]), adaptive micro architectures (e.g., [SBK06, EKD03, MJ06, TST07]) or software-assisted hardware power management (e.g., [DVA10, CLR09, TT08]) has been explored extensively in literature. A variability-aware software stack can leverage these mechanisms in an application-aware manner.

#### 1.2.4 Adaptation of Software Parameters

Application parameters can be dynamically adapted to explore energy, quality, and performance tradeoffs [HSC11]. For example, Green [BC10] provides a software adaptation modality where the programmer provides "breakable" loops and a function to evaluate quality of service for a given number of iterations. The system uses a calibration phase to make approximation decisions based on the quality

of service requirements specified by the programmer. At runtime, the system periodically monitors quality of service and adapts the approximation decisions as needed. In the mobile context, Powerleash [Fal12] monitors energy usage of background applications in smart phones. Applications inform their rate of progress to the system through a vector of arbitrary parameters. The system learns the correlation between each vector of application progress and energy usage. When energy usage exceeds a desired budget, the system scales the progress vector and returns it to the application, which in turn adapts its work accordingly in order to meet a desired rate of battery consumption.

Adaptation of software parameters can be used to maximally leverage the underlying hardware platform in presence of variations. In the context of multimedia applications, [PGS11] demonstrated how by adapting application parameters to the post manufacturing hardware characteristics across different die, it is possible to compensate for application quality losses that might otherwise be significant in presence of process variations. In H.264 encoding, adapting parameters such as sub-pixel motion estimation, FFT transform window size, run length encoding mechanism, and size of motion estimation search window can lead to significant yield improvements, a reduction in over-design as well as application quality improvements [PGS11].

### 1.2.5 Dynamic Recompilation

Optimizations performed in compile-time are limited by assumptions about the target hardware for which the code is compiled. With dynamic recompilation [VE01] different optimization techniques can be tested and profiled at runtime, so that code is matched to the capabilities of the hardware which is running it. Dynamic recompilation may be performed in a system-driven manner, with minimal support from applications, providing the same adaptation knobs as in compile time optimization, e.g., loop unrolling, memory optimization, and parallelization.

#### 1.2.6 Algorithmic Choice

One broad class of approaches for coping with hardware variability is for the software to switch to a different code path in anticipation of or in response to a variability event. Alternate code paths, or algorithmic choice have been explored in the energy-aware software literature. Petabricks [ACW09] and Eon [SKG07], for example, feature language extensions that allow programmers to provide alternate code paths. The runtime system dynamically chooses paths based on energy availability. In Petabricks, multiple versions of object code are created and profiled for execution time and quality using a sample set of input data. Paths for an application may be chosen statically or altered in runtime through accuracy valuations. A similar process is used in Green [BC10], where a combination of a calibration phase and runtime accuracy sampling are used by the application to define which function to execute from a set of possible candidates. In Eon, the runtime system dynamically chooses paths based on energy availability. Levels is an energy-aware programming abstraction for embedded sensors based on alternative tasks [LMM07]. Programmers define task levels, which provide identical functionality with different quality of service and energy usage characteristics. The run-time system chooses the highest task levels that will meet the required battery lifetime.

While these systems provide interesting design references for algorithmic choice, many of their assumptions do not hold true in the presence of variability. In Petabricks, execution time is the primary resource usage metric. Similarly, in Green power is assumed to be a function of execution time. With variability in active mode power, the energy cost of a fixed number of CPU cycles varies across instances and ambient conditions. Both systems rely on a calibration phase to reduce runtime overhead of evaluating quality-of-service and cost of different code paths. With variability, runtime cost of a given code path will also be variable across nominally identical devices and across the lifetime of a device, due both to

aging and changes in operating conditions. Levels triggers chances in run levels based on a history of power consumption and remaining lifetime of the system. As with the calibration phase in Petabricks and Green, a projection of future power consumption based on past history may lead to overly conservative or optimistic adaptation decisions due to variations in power consumption across time and due to ambient conditions.

While Petabricks, Eon, Green, and Levels do not consider hardware variability, similar mechanisms for expressing application elasticity can be leveraged in a variability-aware software system. For example, the application can read the current hardware signature, or register interest in receiving notifications or exceptions when a specific type or magnitude of changes occur in that signature. Application response to variability events could be structured as transitions between different run-levels, with code-blocks being activated or deactivated as a result of transitions.

Algorithms and libraries with multiple implementations can be matched to underlying hardware configuration to deliver the best performance [FJ05, LGP07]. Such libraries can be leveraged to choose the algorithm that best tolerates the predicted hardware variation and deliver a performance satisfying the quality-of-service requirement. With support from the OS, the switch to alternative algorithms may be done in an application-transparent fashion by relining a different implementation of a standard library function. In chapter 5, we present a software stack for system-driven variability-aware algorithmic choice.

#### 1.2.7 Summary of Related Work

Table 1.1 presents a classification of selected software adaptation methods. Each method is classified according to type of adaptation and as system or application-driven. In system-driven methods, the burden of adaptation lies in the system,

| Type of Adaptation      | Application-Driven | System-Driven            |

|-------------------------|--------------------|--------------------------|

| Task Activation Control | [FS99], [KHZ07],   |                          |

|                         | [LSL94], [WWG08]   |                          |

| Hardware Resources      | [LCB10]            | [BDN12]                  |

| Hardware Parameters     |                    | [DVA10], [CLR09], [TT08] |

| Software Parameters     | [BC10], [PGS11]    | [HSC11], [Fal12]         |

| Dynamic Recompilation   |                    | [VE01]                   |

| Algorithmic Choice      | [BC10], [LMM07],   |                          |

|                         | [ACW09], [SKG07]   |                          |

Table 1.1: Classification of Software Adaptation Methods

which provides the adaptation knobs, and initiates adaptation according some system-wide policy, potentially with input or direction from the application (e.g. bounds for task activations). In application-driven methods, the application provides the adaptation knobs, and initiates adaptation under application-specific policies, potentially with some support from the runtime system (e.g. sensors for remaining battery level).

While application-driven adaptation methods allow for wide flexibility of adaptation, they incur in increased complexity and a higher barrier of entry for application developers. Furthermore, system-wide optimization is typically not possible with application-specific methods, as individual applications can only adapt themselves and not the system as a whole. System-driven adaptation methods, on the other hand, are less flexible, as the only adaptation knobs available are those provided by the runtime system. Nevertheless, with system-driven adaptation, applications can be adapted with little or no added complexity, and optimization decisions can take the whole of the system into consideration. Our work in chapter 4 presents a software stack for system-driven task activation control where the system adapts duty cycle under application constraints. Chapter 5 presents a

variability-aware software stack for system-driven algorithmic choice.

## 1.3 Organization

The remainder of this text is organized as follows:

- Chapter 2 discusses power consumption variability in modern embedded processors. We measured power consumption for several instances of Atmel SAM3U processors, and found that for a temperature range of 20–60°C there is 10% variation in active power, and 14x variation in leakage power. Based on these measurements, we model sleep and active power as a function of instance and temperature, and project power consumption for advanced manufacturing technologies.

- Chapter 3 discusses evaluation strategies for variability-aware software and introduces the VarEMU emulator and its supporting software stack.

- Chapter 4 discusses variability-aware duty cycling. We explored variability-aware duty cycle schedulers for TinyOS and FreeRTOS where application modules specify to a range of acceptable activation parameters, and the scheduler selects the actual duty cycle based on run-time monitoring of instance-dependent power-temperature models. In an evaluation with ten instances of Atmel SAM3U processors, we found that variability-aware duty cycling yields a 3–22x improvement in total active time over schedules based on worst-case estimations of power, with an average improvement of 6.4x across a wide variety of deployment scenarios based on collected temperature traces. Conversely, datasheet power specifications fail to meet required lifetimes by 7–15%, with an average 37 days short of a required lifetime of one year. Finally, a target localization application using variability-aware duty cycle yields a 50% improvement in quality of results over one based on

worst-case estimations of power consumption.

- Chapter 5 presents a framework for system driven algorithmic choice for variability aware software featuring function replacement in shared libraries in Linux and demonstrated with a polymorphic version of the C math runtime library. We show how this system can help users in developing and analyzing tradeoffs between accuracy and energy consumption with variable hardware, and reduce the energy consumption with user-controlled quality-of-service degradation.

- Chapter 6 presents our concluding remarks.

## CHAPTER 2

# Power Consumption Variability in Embedded Processors

Power consumed in an embedded class microprocessor chip is broadly classified into active mode and sleep mode. In this chapter we study the temperature dependence of active and sleep mode power consumption in embedded processors and propose models to characterize it.

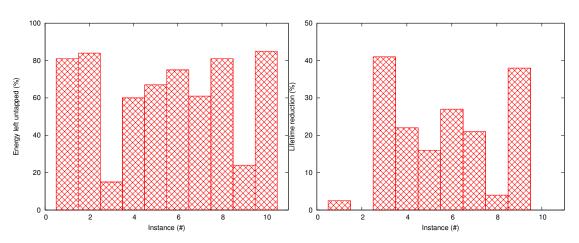

Our measurements show sleep and active power as a function of temperature across several instances of Atmel SAM3U microcontrollers in LQFP144 packages. While we have been unable to determine from available literature the precise technology node the chip is fabricated in, indirect evidence as well as the vintage suggests that it is most likely fabricated in a 130 nm process. The class of lowend 32-bit processors represented by the Cortex M3 is suitable for embedded applications where nodes perform data collection, aggregation, and inferences in a duty-cycled fashion. The variations we observed with the SAM3U are comparable to those found in other similar embedded processors [BDS11].

## 2.1 Experimental Setup

For our measurements, we used ten identical SAM3U-EK development boards. These boards feature jumpers that allow power measurements for different components. We measured current and voltage on going into the SAM3U core, with all peripherals except for the real time clock disabled. To obtain synchronized

voltage and current measurements we used a pair of Agilent 34410A digital multimeters with a basic accuracy of 0.06%, externally triggered by a function generator. Each measurement point represents the average power dissipated by the core across 50,000 measurements, with a sampling rate of 1,000 samples per second. We used a TestEquity 115F temperature chamber allowing control of ambient temperature with  $\pm 0.5^{\circ}$ C accuracy. Figure 2.1 illustrates our test setup.

## 2.2 Sleep Mode Power Consumption

With shrinking geometries the ratio of sleep mode power to active mode power has been increasing (as high as 40% in chips fabricated using 65nm technology) [PSB05]. This is due to the inability to turn devices "off" effectively as device dimensions continue to shrink. Manufacturing spread in transistor parameters can cause up to 20x variation in sleep mode power [BKN03] in addition to substantial variation with supply voltage and temperature. Specifically in context of embedded sensor platforms, which often are deployed in extreme ambient conditions, the variation in leakage power during the lifetime of a device may be substantial.

## 2.2.1 Analytical Modeling of Sleep Power

Sleep power has four main sources:

- sub-threshold leakage current that flows between source and drain of a MOS-FET for gate-to-source voltages below the threshold,

- 2. gate leakage current due to tunneling of carriers through the gate oxide to the substrate,

- 3. reverse-biased junction leakage current which flows from the source/drain regions to the substrate through the reverse biased p-n junctions due to

(a) SAM3U-EK Board

(b) Temperature Chamber

(c) Power Measurement Setup

Figure 2.1: Experimental setup

band-to-band tunneling and diffusion, and

4. gate-induced drain leakage current due to band to band tunneling in the region of overlap between the gate and drain.

At temperatures below 150°C, only the first two components are large enough, and of the two only sub-threshold leakage exhibits strong variability with temperature. Therefore, sleep power can be modeled as the following function of temperature (derived from BSIM4 compact device model [BSI]):

$$P_{sleep} = V_{dd}(AT^2e^{-B/T} + I_{gl})$$

$$\tag{2.1}$$

where A and B are technology-dependent constants,  $I_{gl}$  is the temperature-independent gate leakage current, and T is the core temperature. Coefficients in the model are fitted to individual instances, and hence capture both temperature and instance-dependent variability. We combine the sleep power model with a model of the thermal dynamics of a packaged chip [HQF10]:

$$RC\frac{dT(t)}{dt} + T(t) - RP(t) = T_{amb}$$

(2.2)

where T(t) and P(t) are the core temperature and power consumption of the chip at time t, R and C are the thermal resistance and capacitance of the chip package, and  $T_{amb}$  is the ambient temperature. At steady state  $\frac{dT(t)}{dt} = 0$ , so that  $T_{steady-state} = T_{amb} + RP(t)$ .

For the SAM3U in a LQFP144 package, the typical values of R and C are 50°C/W and 4–5 J/°C respectively. The nominal static power of SAM3U is 30  $\mu$ W. Nominal active power when operating at 4 MHz while performing a Dhrystone benchmark is 9 mW. From (2.2), when sleep mode power measurements are performed, the self-heating of the chip due to static power consumption is

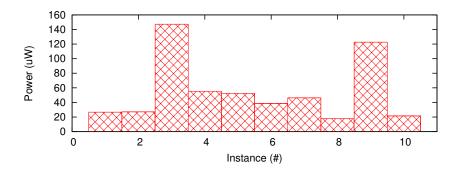

Figure 2.2: Sleep power at room temperature

negligible, and in active mode the temperature difference between ambient and core temperature is  $\sim 0.5$ °C.

#### 2.2.2 Experimental Measurements

Based on the preceding analysis, it is reasonable to assume that the static power follows a similar dependence on ambient temperature as given by (2.1). We verify this assumption through measurements and characterize each instance of microcontroller based on the above model.

For leakage measurements, we disable all peripheral devices in the SAM3U except for the Real-Time Clock (RTC), select the chip's internal 32kHz RC oscillator as clock source, configure the chip for wakeup with an RTC interrupt, and execute the "wait for event" instruction, which causes the processor to enter sleep mode. In addition to sleep, the SAM3U microcontroller features two other low power modes. The first, backup, completely powers off the core. While this results in the lowest possible power consumption, it also results in wakeup times more than 50 times larger than in other modes, and therefore is not practical for duty-cycled systems. The second low-power mode, wait, allows fast wakeup with some specific clock configurations and wakeup sources. In our measurements, we found power dissipated in wait mode to be equivalent to power in sleep mode with the aforementioned configuration.

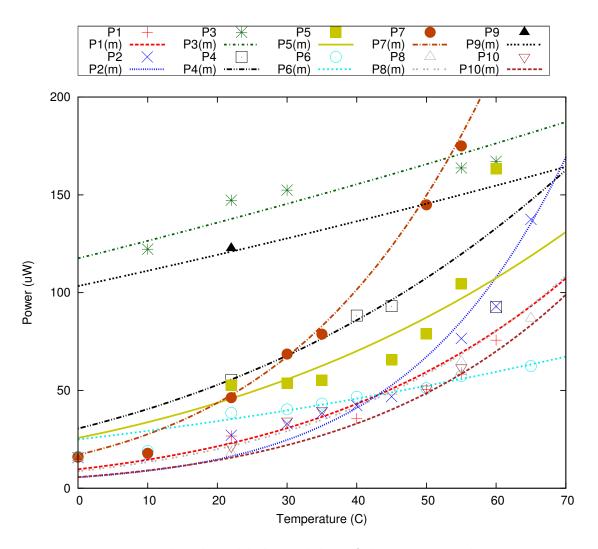

Figure 2.3: Measured and modeled variability of sleep power with temperature

Figure 2.2 shows that the variation in sleep power across ten instances of SAM3U at room temperature is approximately 8x. Figure 2.3 shows the experimental data for sleep power consumption of the SAM3U instances across a temperature range fitted to the analytic model discussed earlier, using minimum mean square error criterion. As expected, individual processor instances exhibit large sleep power variations over the temperature range. While change in sleep power for any individual processor is monotonic, the magnitudes of variations are different so that relative rankings of different processors change over temperature. Root mean square error between measurements and model across all instances is  $6.7 \ \mu\text{W}$ . Over a temperature range of  $20-60^{\circ}\text{C}$ , which is representative of the temperatures that embedded sensors deployed under unregulated and extreme ambient conditions often face (e.g. in factories, desert, etc.), total variation across all ten instances is 14x.

### 2.3 Active Mode Power Consumption

Active power has three main components: switching power, short circuit power, and active mode leakage. Switching power is consumed when devices switch between different logic values, and is given by  $P_{switching} = \alpha C V_{dd}^2 f$ , where  $\alpha$  is the activity factor that represents how often a gate switches per clock cycle, C is the capacitance at the switching node,  $V_{dd}$  is the supply voltage and f is the clock frequency. Short circuit power is dissipated during the time period when inputs ramp between logic levels and there is a direct path between supply to ground. Finally, devices that do not switch while in active mode also consume power. Leakage power has an exponential dependence on temperature, as elaborated in section 2.2.1. For our experiments, however,  $P_{active}/P_{sleep}$  is nominally  $\sim 300$ . Hence this component has a small effect only on the high temperature range dependence of the total active mode power.

### 2.3.1 Analytical Modeling of Active Power

The temperature dependence of active mode power can be explained by dividing the temperature range of interest into three regimes [WBA11].

(i) Low temperature regime: The contribution of active mode leakage is negligible as at low temperatures. An increase in threshold voltage  $V_{th}$  causes exponential decrease in leakage. The capacitance increase is a linear function of temperature and hence contributes to the linear dependence of active mode power. At low temperatures, inverse temperature dependence causes the decrease in active mode power to have a steeper slope as temperature reduces. The relationship with temperature is characterized as:

$$P_d = P_{T_1} + k_1 (T - T_1)^{\alpha} \tag{2.3}$$

where,  $0 < \alpha < 1$ ,  $T_1 < T < T_2$ ,  $k_1$  and  $\alpha$  are fitting parameters.  $T_1 < T < T_2$  defines the low temperature regime.

(ii) Nominal temperature regime: Short circuit and switching power have a linear dependence in this regime, and the active mode leakage is negligible. The relationship with temperature is characterized as:

$$P_d = P_{T_2} + k_2(T - T_2) (2.4)$$

where,  $T_2 < T < T_3$  and  $k_2$  is a fitting parameter.  $T_2 < T < T_3$  defines the nominal temperature regime.

(iii) High temperature regime: The switching power varies linearly (capacitance dependence is linear), short circuit power and active mode leakage give active mode power in this regime a super-linear dependence [WAB13]. The relationship with temperature is characterized as:

$$P_d = P_{T_3} + k_3 (T - T_3)^{\beta} \tag{2.5}$$

where,  $1 < \beta$ ,  $T_3 < T$ ,  $k_3$  and  $\beta$  are fitting parameters.  $T_3 < T$  defines the high temperature regime.

#### 2.3.2 Experimental Measurements

Figure 2.2 shows that the variation in active power across ten instances of SAM3U at room temperature is approximately 4%. Figure 2.5 shows the active power model fitted to our measured data for active mode power consumption across a temperature range. For this experiment, we used the same measurement setup as in the sleep mode power measurements. All SAM3U peripherals were disabled, except for the RTC. The core was clocked from the internal ring oscillator at 4MHz, continuously running a Dhrystone benchmark program. Root mean square error between measurements and model across all instances is 0.02 mW. Over a range of 20–60°C, total variation across all ten instances is 10%.

Interestingly, for the SAM3U processors we used, even the clock frequency varied by 2% across the temperature range and 6% across different instances as shown in Figure 2.6. To measure clock frequency, we toggled an I/O pin at a rate proportional to the core frequency, and observed the resulting frequency at different temperatures with a digital oscilloscope. All processors were set to operate nominally at 4 MHz. The clock is generated by an internal ring oscillator (RO). Generally, RO frequency decreases with an increase in temperature so there is always temperature compensation provided with the RO circuit to generate the clock at the specified frequency across temperature. We observe that the frequency increases with temperature. This is likely due to temperature over-compensation.

Figure 2.4: Active power at room temperature

Figure 2.5: Measured and modeled variability of active power with temperature

Figure 2.6: Measured frequency variation with temperature

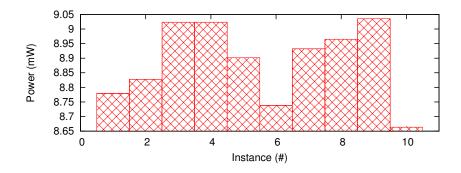

## 2.4 Power Projections for Advanced Technologies

The characterization discussed above was based on actual measurements from hardware manufactured in 130nm. Nominal power consumption variability is characterized in ITRS across sub-130 nm technology nodes. We use this data to project the spread of power vs. temperature curves. PTM 130, 90, 65 and 45 nm spice models were used to project the scaling of active and sleep mode power across these technology nodes based on a ring oscillator design. Relative temperature dependence was assumed to be the same as observed in the measurements. We assume that the temperature regimes remain constant across technologies. The projections can be refined by calibrating these regimes for advanced technology using real measurements. We also assume in our experiments that while in active mode 20% of devices are switching. Tables 2.1 and 2.2 list typical sleep and active mode power model parameters at each technology node. Figures 2.7 and 2.8 show expected projection of nominal sleep and active power across temperature resulting from these parameters for each node technology.

| Instance                  | A    | В      | $I_{gl}$ | $V_{dd}$ |

|---------------------------|------|--------|----------|----------|

| $\mathrm{Typ}\text{-}130$ | 1.0  | 2605.5 | 0.0      | 1.8      |

| Typ_90                    | 1.26 | 2400   | 0.2      | 1.8      |

| Typ65                     | 1.76 | 2300   | 0.6      | 1.8      |

| $Typ_45$                  | 2.52 | 2100   | 1        | 1.8      |

Table 2.1: Sleep power model parameters across technologies

| Instance     | $k_1$        | $k_2$        | $k_3$        | a          | b          |

|--------------|--------------|--------------|--------------|------------|------------|

| $Typ_{-}130$ | 0.0511       | 0.0095       | 0.003325     | 0.669      | 1.3456     |

| $Typ\_90$    | 0.0246       | 0.0046       | 0.0016       | 0.71       | 1.5228     |

| Typ65        | 0.0094       | 0.00175      | 0.000615     | 0.735      | 1.6335     |

| $Typ_45$     | 0.0046       | 0.000855     | 0.0003       | 0.755      | 1.722      |

|              | $P_{T1}(mW)$ | $P_{T2}(mW)$ | $P_{T3}(mW)$ | $T_2$ (°C) | $T_3$ (°C) |

| Typ_130      | 7.7          | 8.6          | 8.68         | 21         | 30         |

| $Typ_{-}90$  | 2.82         | 3.33         | 3.37         | 21         | 30         |

| Typ65        | 0.9          | 1.125        | 1.14         | 21         | 30         |

| Typ_45       | 0.364        | 0.479        | 0.4867       | 21         | 30         |

Table 2.2: Active mode power model parameters across technologies

Figure 2.7: Sleep power projection across technologies

Figure 2.8: Active power projection across technologies

### CHAPTER 3

# Evaluation of Variability-Aware Software

The evaluation of a variability-aware software stack faces two main challenges: first, commercially available platforms typically do not provide means to "sense" or discover variability. Second, even if this sensing capability was available, evaluating a software stack across a statistically significant number of hardware samples and ambient conditions would prove exceedingly costly and time consuming.

In hardware design, simulations at various levels of abstraction can be used to evaluate the impacts of hardware variability due to PVT (Process, Voltage, and Temperature) variations and circuit aging. While gate- and RTL-level simulators can co-simulate both software and hardware, their runtimes are orders of magnitude slower than real-time [CDB09]. Cycle-accurate architecture-level simulators like Wattch [BTM00], with typical runtimes of 2-3 orders of magnitude slower than real-time, suffer from the same problem. FPGA-based emulators like [KVR11, CLM12] can achieve similar runtime as real-time, but offer limited observability and controllability, and suffer from poor portability and flexibility.

We introduce VarEMU, an extensible framework for the evaluation of variability-aware software. VarEMU provides users with the means to emulate variations in power consumption and fault characteristics and to sense and adapt to these variations in software. VarEMU is an extension to the QEMU virtual machine monitor [QEM13], which relies on dynamic binary translation and supports a variety of target architectures with very good performance. For many target machines, QEMU provides faster than real time emulation. Because QEMU can run

unmodified binary images of physical machines, VarEMU enables the evaluation of complete software stacks, with operating system, drivers, and applications.

In VarEMU, timing and cycle count information is extracted from the code being emulated. This information is fed into a variability model, which takes configurable parameters to determine energy consumption and fault variations in the virtual machine. Energy consumption and susceptibility to faults are also subject to dynamic change according to an aging model. Control over faults and virtual energy sensors are exported as "variability registers" mapped into memory that is accessible to the software being emulated, closing the loop. This information is exposed through a variability driver in the operating system, which can be used to support software adaptation policies. Through the use of different variability emulation parameters that capture instance-to-instance, environmental, and age-related variation, VarEMU allows users to evaluate variability-aware software adaptation strategies across a statistically significant number of hardware samples and scenarios.

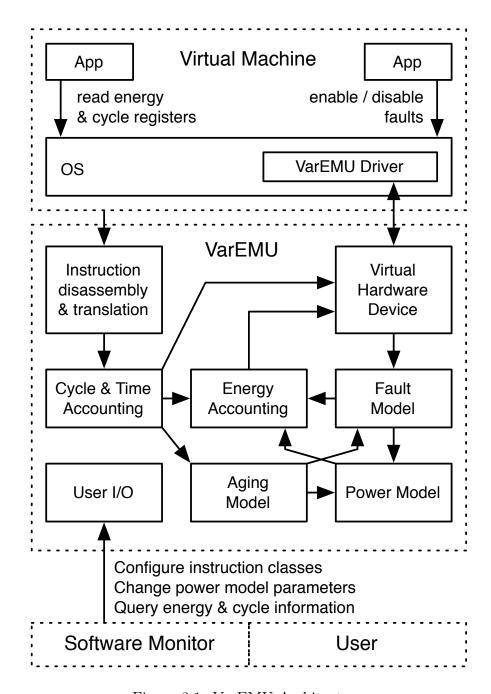

### 3.1 VarEMU Architecture and Implementation

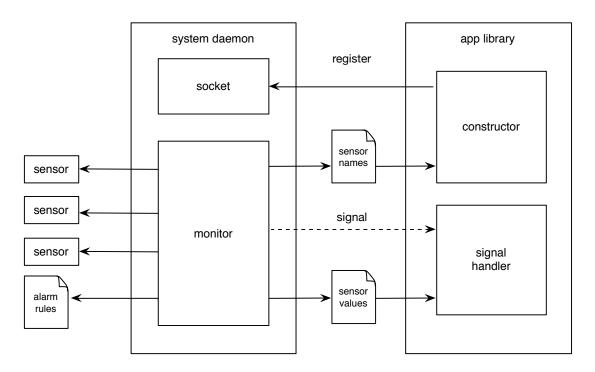

Figure 3.1 presents an overview of the VarEMU architecture. Applications in a virtual machine interact with VarEMU by querying for energy, cycle count, and execution registers for different classes of instructions and by allowing or disallowing faults in the execution of emulated instructions. An operating system driver mediates the interaction of applications with a virtual hardware device which exposes the VarEMU interface to the VM. On VMs without operating systems, applications handle this interaction directly.

When starting VarEMU, users provide a configuration file that sorts instructions into different classes and parameters to a model that is used to determine power consumption for each of the classes. These parameters are subject to dynamic change during runtime according to an aging model. Users may change parameters for the power model dynamically (e.g. to emulate variations in power consumption due to changes in temperature, the user would periodically change the temperature parameter of the power model). Users may also query the VM's cycle counters and energy registers.

Whenever an instruction is executed in the virtual machine, the cycle counter for its instruction class is incremented. Energy expenditure for a class of instruction is determined as a function of accumulated execution time for all instructions in that class and power consumption for the class as determined by a power model.

For instructions configured by the user as susceptible to faults, the execution of translated code may be preceded, succeed, or replaced with alternative, faulty operations. These operations may, in turn, cause changes to cycle counting (e.g. due to a less precise version of the instruction taking fewer cycles to complete) or change parameters in the power model (e.g. voltage or frequency). Faults are injected only when explicitly activated by emulated software. A runtime parameter passed from emulated software to the fault module when enabling faults allows users to configure which faults are enabled and/or the nature of faults (e.g. precision of a numerical operation). This allows users to study the effects of faults in instruction execution on individual applications phases, without compromising the stability of the runtime system. The remainder of this section describes the architecture and implementation of VarEMU.

#### 3.1.1 Cycle and Time Accounting

We account time in VarEMU on an *instruction class* basis. Each instruction is associated with a user-defined class. A data structure holds total number of cycles and time spent executing instructions of each class. To associate instructions with classes, each instruction in a translation block is augmented with an informa-

tion structure (vemu\_instr\_info) containing fields for the instruction operation code (opcode), instruction name, instruction class, number of cycles, fault status, and the instruction word itself.

When a new instruction word is found, its opcode is decoded, and the instruction information structure is filled with its corresponding default values. An input file in JSON format allows users to change the default number of cycles, class, and fault status for any instruction. The number of cycles may also be altered by the fault module at runtime.

A helper function in QEMU allows calling arbitrary functions from translated code. We use one such helper to perform a call to a function that increments the number of cycles for a given instruction class after each instruction is executed (vemu\_increment\_cycles). This function adds the number of cycles in the instruction's information structure to the total number of cycles for its instruction class. Likewise, it increments total active time for that instruction class, based on current (virtual) frequency. In processors where the number of cycles taken by an instruction is not constant, information from the instruction word (e.g. input registers used, immediate values) could be used to accurately determine the number of cycles.

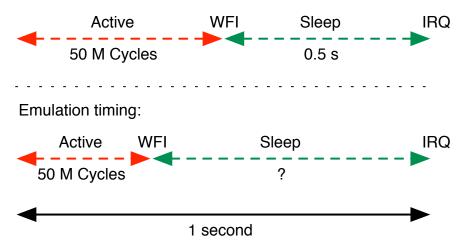

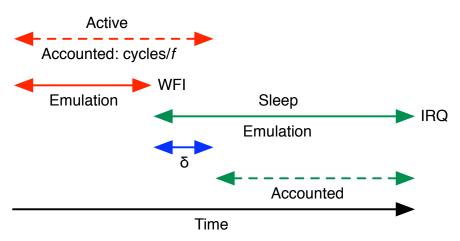

We must also account for cycles spent in standby or *sleep* modes. In many architectures, a special instruction (e.g. WFI in ARM, or HLT in x86 processors) puts the processor in standby mode. After this instruction is issued, the processor will not execute other instructions until an interrupt (typically from a timer or an external device) is fired. Keeping track of real sleep time (i.e., reflecting hardware timing) is important for applications (e.g., in energy-aware duty cycling), as well as for circuit aging models. When we encounter such an instruction, we store a timestamp with current VM time. When an interrupt occurs following standby we read a new timestamp, and add the time difference to the counter for total time spent in sleep mode.

Because QEMU runs virtual machines as best-effort, the actual execution frequency of emulated instructions may not match the (virtual) frequency of the hardware. If the VM never enters standby mode, there will be no adverse effects other than a discrepancy between total virtual time accounted with the cycle counters and wall clock time elapsed. If the VM does enter a standby mode, time spent in that mode must be adjusted to reflect hardware behavior.

Consider, for example, a system with periodic tasks where processor utilization is less than 100%. After the system completes tasks, it goes into standby mode, and waits for a timer interrupt corresponding to the next period. Figure 3.2a illustrates such a system, where processor frequency is 100 MHz, timer frequency is 1 Hz, task execution takes 50 M cycles (0.5 seconds), and time spent in standby mode is 0.5 seconds. If emulated execution is faster than hardware, sleep time in the VM would be greater than in hardware. Conversely, if emulation is slower than hardware, sleep time in the VM would be smaller than in hardware.

In order for sleep time accounting in VarEMU to reflect hardware timing, we keep track of emulated execution time for each active time cycle. When a sleep cycle is initiated, we calculate the delta between virtual execution time (from our cycle counters, reflecting hardware execution time) and emulated execution time for the last active period. We then deduct this delta from the sleep time interval. Figure 3.2b illustrates our solution. In cases where processor utilization in hardware is 100%, but emulated execution time is faster than hardware, it is possible for the sleep time interval to be negative. In this case, the hardware version of the processor would continue executing immediately after the standby instruction. We emulate this by returning a sleep interval of 0. The converse situation (emulated time is slower than virtual time) does not lead to a problem, as after continuing execution immediately after the standby instruction we deduct a negative delta from an interval of zero, leading to the correct sleep time interval.

### 3.1.2 Energy Accounting

Energy consumed by an instruction of a given class is determined as a function of execution time (number of cycles divided by frequency) and power for that class. Power is in turn determined by a model with arbitrary parameters (minimally, voltage and frequency). By fitting the power model with different parameters, users can emulate instance-to-instance variation. By changing parameters dynamically, users can emulate the effects of dynamic or environmental variation (e.g. due to changes in supply voltage or temperature). Power model parameters may also be dynamically changed with an aging model.

While active and sleep time are accounted on a per-event basis (i.e. on each instruction or sleep cycle), energy is accounted on demand, i.e. only when a read command is issued from emulated software or external monitor, or when one of the power model parameters change. For each energy accounting event, we keep track of sleep time and active time for each class of instructions since the last event, and accumulate energy for each interval in the appropriate energy registers. There is one active energy register per instruction class, and for sleep energy.

Energy accounting is independent of power model, so that users may define their own models. A power model implements three functions: The first function returns active power in Watts for a given class of instruction. The second returns sleep power in Watts as a function of standby mode (e.g. clock gated, power gated). The final function is used to change power model parameter n of class c to value v. Any power model must also define at least two parameters: frequency and voltage. The default power model for VarEMU, presented in Section 3.1.4 defines several additional parameters to capture static and dynamic variability.

### 3.1.3 NBTI Aging Model

Negative bias temperature instability (NBTI) is a circuit wear-out mechanism that will degrade the PMOS threshold voltage  $(V_{thp})$  and thus the circuit performance. To model the NBTI-induced aging effect in VarEMU, we use the analytical model for the  $|V_{thp}|$  degradation of a MOS transistor as in [CWC12, BWV06, WYB07].

$$|\Delta V_{thp}| = \left(\frac{\sqrt{K_v^2 T_{clk} \omega}}{1 - \beta_t^{1/2n}}\right)^{2n}$$

$$\beta_t = 1 - \frac{b_1 + \sqrt{b_2 (1 - \omega) T_{clk} exp(b_5/T)}}{b_3 + b_4 \sqrt{t}}$$

$$K_v = b_4 (V_{dd} - V_{thp}) exp(b_5/T)$$

(3.1)

where  $V_{dd}$  is the supply voltage,  $b_1$ ,  $b_2$ ,  $b_3$ ,  $b_4$ ,  $b_5$  are technology-dependent parameters.  $T_{clk}$  is the time period of one stress-recovery cycle,  $\omega$  is the duty cycle (the ratio of the time spent in stress to time period), t is the total lifetime of a transistor, n is a time exponent equal to 1/6 for an  $H_2$  diffusion model. Since NBTI-induced degradation is insensitive to the switching frequency when it is larger than 100Hz [BWV06], similar to [WYB07], we assume  $T_{clk} = 0.01s$  in this work.

Based on the aging model in (3.1), the key activity-related parameters are the duty cycle  $\omega$  and total lifetime t. In VarEMU, we use the cycle counting feature to implement the bookkeeping function for activity-related parameters, i.e. total normal runtime  $t_n$  and total runtime under power gating  $t_{pg}$ .

Since NBTI-induced degradation depends on the exact signal switching pattern, VarEMU reports the upper and lower bound aging scenarios. The upper bound of the aging scenario will be  $t = t_n + t_{pg}$  and  $\omega = t_n/t$ . The lower bound of the aging scenario will be  $t = t_n + t_{pg}$  and  $\omega = 0.5t_n/t$ . Since the model in (3.1) assumes a periodic stress-recovery pattern, this model may not be adequate to accurately capture NBTI effects under some dynamical scenarios like dynamic voltage scaling and long-term power-gating. Enabling dynamic will require either

more sophiscated aging models or aging simulators as in [CSG11] (too slow for our purpose).

### 3.1.4 Aging-aware Power and Delay Model

In this section we present the default power model for VarEMU which accounts for aging effects. The processor power consumption can be classified as active power and sleep power. Active power includes switching power and short circuit power. In VarEMU, we use the switching power model as in [RCN96]:

$$P_{switching} = \sum_{i=1}^{n} C_i \beta_i V_{dd}^2 f$$

(3.2)

where  $C_i$  is the equivalent switching capacitance for each instruction class i,  $\beta_i$  is the fraction of class i instructions in all instructions, and f is the clock frequency.

We use the short circuit power model as in [Vee84]:

$$P_{short} = \sum_{i=1}^{n} \eta_i (V_{dd} - V_{thn} - V_{thp})^3 f$$

(3.3)

where  $\eta_i$  is a technology- and design-dependent parameter for instruction class i,  $V_{thn}$  is the threshold voltage for NMOS, and  $V_{thp}$  is the threshold voltage for PMOS and equals  $|V_{thp0} + \Delta V_{thp}|$ ,  $V_{thp0}$  is the threshold voltage without degradation.

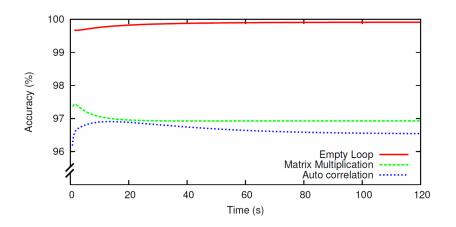

The sleep power can be modeled as:

$$P_{sleep} = V_{dd}(I_{sub} + I_g) (3.4)$$