#### **UC Irvine**

#### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Programmable Accelerators for Lattice-based Cryptography

#### **Permalink**

https://escholarship.org/uc/item/6mm0v17b

#### **Author**

Nejatollahi, Hamid

#### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

## $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

## Programmable Accelerators for Lattice-based Cryptography DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Hamid Nejatollahi

Dissertation Committee: Professor Nikil Dutt, Chair Professor Rainer Döemer Professor Ian G. Harris

## **DEDICATION**

To my parents, brothers, and my sister

## TABLE OF CONTENTS

|                           |                    | Pa                                                                                               | age                   |

|---------------------------|--------------------|--------------------------------------------------------------------------------------------------|-----------------------|

| LI                        | ST (               | OF FIGURES                                                                                       | v                     |

| LI                        | ST (               | OF TABLES                                                                                        | vii                   |

| $\mathbf{A}^{\mathbf{c}}$ | CKN                | OWLEDGMENTS                                                                                      | viii                  |

| $\mathbf{C}^{\gamma}$     | URR                | ICULUM VITAE                                                                                     | ix                    |

| $\mathbf{A}$              | BST                | RACT OF THE DISSERTATION                                                                         | xi                    |

| 1                         | Intr<br>1.1<br>1.2 | Trends, Challenges and Needs for Lattice-based Cryptography Implementations Thesis Contributions | 1<br>3<br>6<br>6<br>8 |

| 2                         | Bac                | kground and Related Works  2.0.1 Arithmetic and Components of Lattices                           | 10<br>11<br>24        |

|                           | 2.1                | Implementation challenges                                                                        | 30<br>31<br>39<br>61  |

|                           | 2.2                | Schemes                                                                                          | 65<br>66<br>66        |

| 3                         | 3.1                | ulation-based Cache-assisted Polynomial Multiplier         Background                            | <b>67</b> 68          |

|                           | 3.2                | Design Flow Steps                                                                                | 72<br>74<br>75<br>75  |

| $\mathbf{B}^{i}$ | ibliog         | graphy                                                                | 128     |

|------------------|----------------|-----------------------------------------------------------------------|---------|

| 7                | Cor            | nclusions and Future Directions                                       | 126     |

|                  | 6.4            | Conclusion                                                            | 124     |

|                  |                | 6.3.4 Comparison with CPU and FPGA                                    | 124     |

|                  |                | 6.3.3 Comparison with state-of-the-art PIM                            | 123     |

|                  |                | 6.3.2 Performance and Energy Consumption of CryptoPIM                 | 122     |

|                  |                | 6.3.1 Evaluation Setup                                                | 121     |

|                  | 6.3            | Evaluation                                                            | 121     |

|                  |                | 6.2.4 CryptoPIM Architecture                                          | 119     |

|                  |                | 6.2.3 CryptoPIM Building Blocks                                       | 117     |

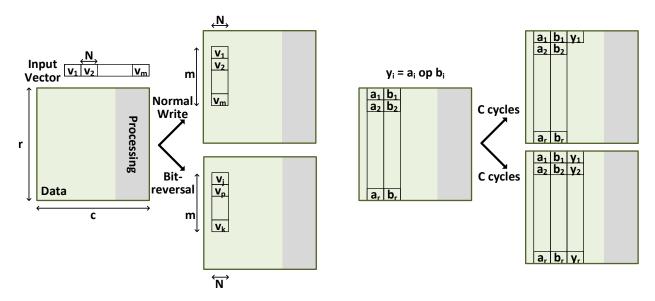

|                  |                | 6.2.2 Mapping Operations to PIM                                       | 114     |

|                  |                | 6.2.1 Operational Breakdown of Polynomial Multiplication              | 113     |

|                  | 6.2            | CryptoPIM for RLWE Polynomial Multiplier                              | 113     |

|                  | 6.1            | Background and Related Work                                           | 109     |

|                  | war            |                                                                       | 109     |

| 6                | $\mathbf{Cry}$ | ptoPIM: In-memory Acceleration for Lattice-based Cryptographic Har    |         |

|                  | 0.1            |                                                                       | 101     |

|                  | 5.4            | Conclusion and future work                                            | 107     |

|                  | 5.3            | Evaluation                                                            | 106     |

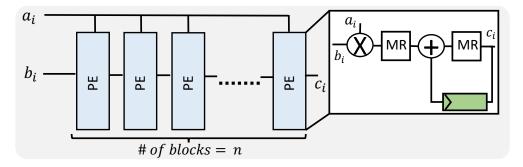

|                  |                | 5.2.2 Implementation of systolic array polynomial multiplier          | 104     |

|                  | 0.2            | 5.2.1 Systolic arrays                                                 | 103     |

|                  | 5.2            | Systolic Array polynomial multiplier                                  | 102     |

|                  |                | 5.1.3 Previous works                                                  | 101     |

|                  |                | 5.1.2 NTT-based multiplier                                            | 99      |

|                  | 0.1            | 5.1.1 Convolution-based multiplier                                    | 99      |

|                  | 5.1            | Background and Related Work                                           | 98      |

| 9                |                | Processors                                                            | -<br>98 |

| 5                | Free           | oloring Energy Efficient Quantum-resistant Signal Processing Using Ar |         |

|                  | 4.5            | Conclusion                                                            | 96      |

|                  | 4.4            | Design Space Exploration                                              | 92      |

|                  | 4.3            | Algorithm Analysis & Profiling                                        | 90      |

|                  | 4.2            | Design Space Exploration (DSE) Flow                                   | 88      |

|                  | 4.1            | Background                                                            | 87      |

| 4                | Sim            | nulation-based DMA-assisted Polynomial Multiplier                     | 87      |

|                  | 3.5            | Conclusion                                                            | 86      |

|                  | 3.4            | Evaluation                                                            | 79      |

|                  |                | 3.3.5 KCL (Key Consensus from Lattice)                                | 77      |

|                  |                | 3.3.4 R.EMBLEM                                                        | 76      |

|                  |                | 3.3.3 Dilithium                                                       | 76      |

## LIST OF FIGURES

|                   |                                                                                                                                                                                                                                          | Page           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1               | Accelerator taxonomy [205]                                                                                                                                                                                                               | 4              |

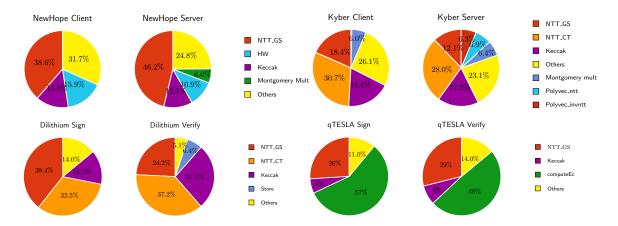

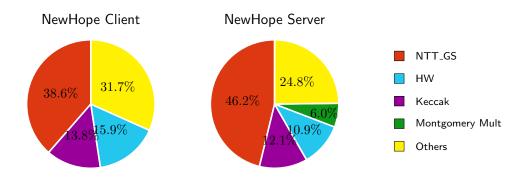

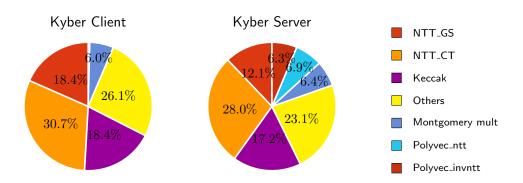

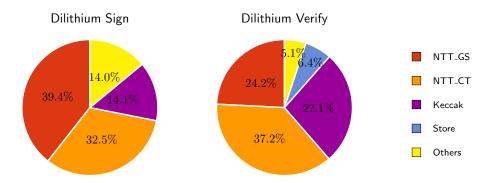

| 1.2               | Profiling results for the most promising LBC schemes. Profiling results are based on the user-level CPU cycles                                                                                                                           | 5              |

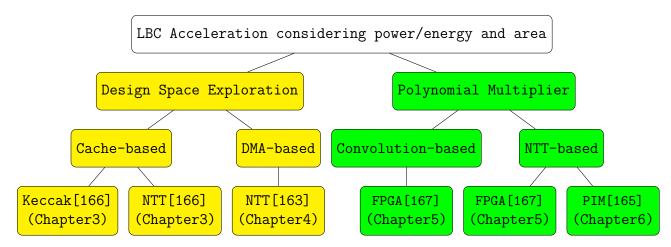

| 1.3               | Thesis Contribution                                                                                                                                                                                                                      | 6              |

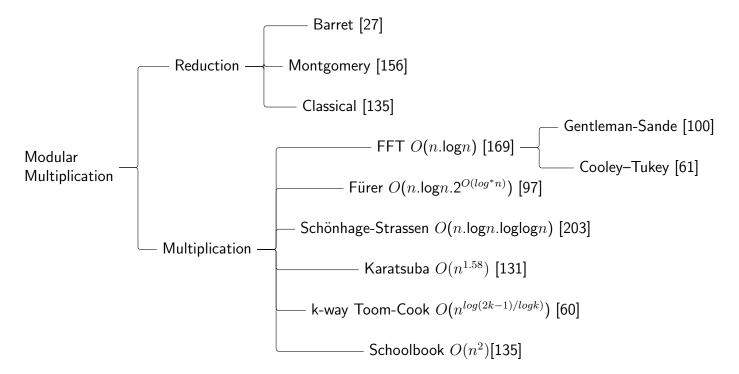

| 2.1<br>2.2        | Common modular Multiplication algorithms                                                                                                                                                                                                 | 12<br>21       |

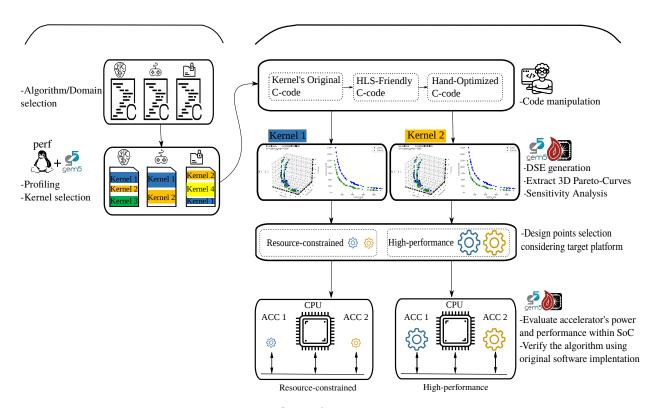

| 3.1<br>3.2<br>3.3 | Design flow of the accelerator generation                                                                                                                                                                                                | 72<br>75<br>76 |

| 3.4<br>3.5<br>3.6 | Profiling results for Dilithium: Sign - Verify                                                                                                                                                                                           | 77<br>77<br>78 |

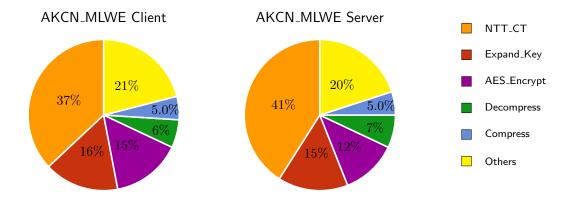

| 3.7               | Architectural template for generated accelerators for Keccak, NTT_CT and NTT_GS kernels                                                                                                                                                  | 79             |

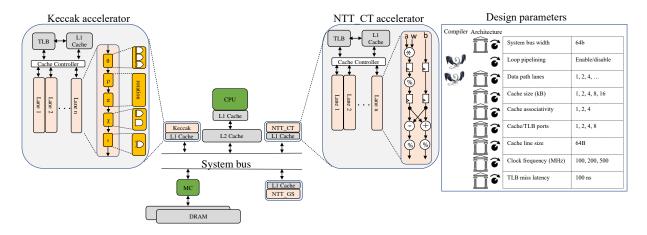

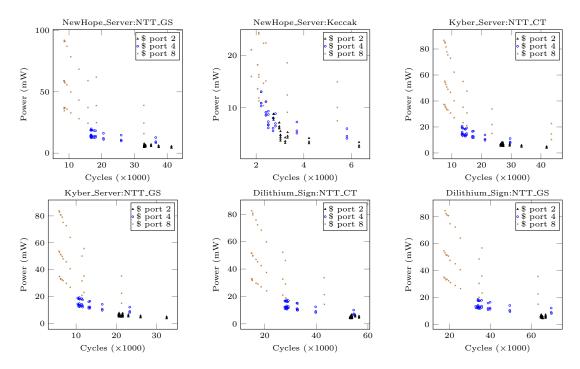

| 3.8               | The sensitivity of the accelerators' performance and power to the number of cache ports.                                                                                                                                                 | 79             |

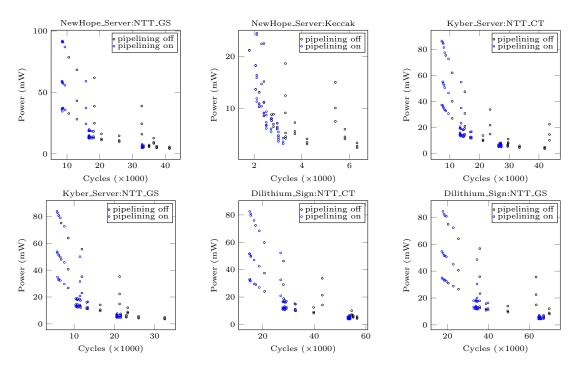

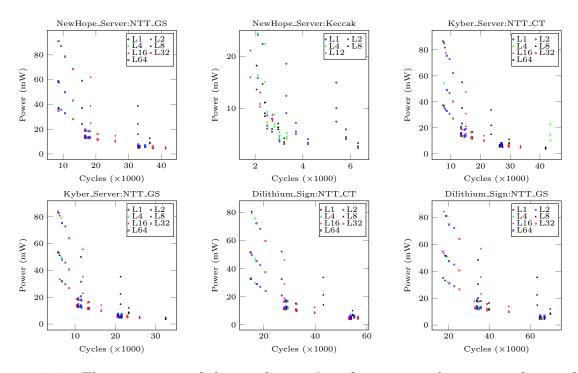

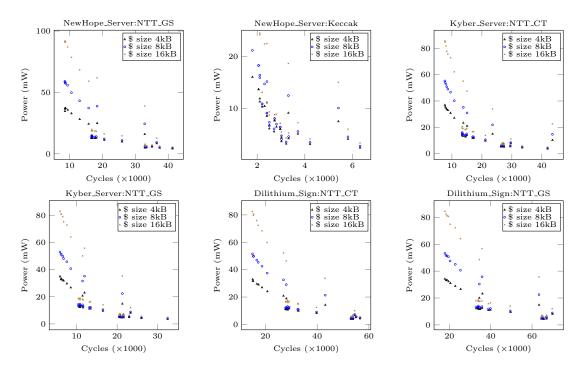

| 3.9               | The sensitivity of the accelerators' performance and power to the software pipelining                                                                                                                                                    | 80             |

| 3.10              | The sensitivity of the accelerators' performance and power to the number of lanes                                                                                                                                                        | 80             |

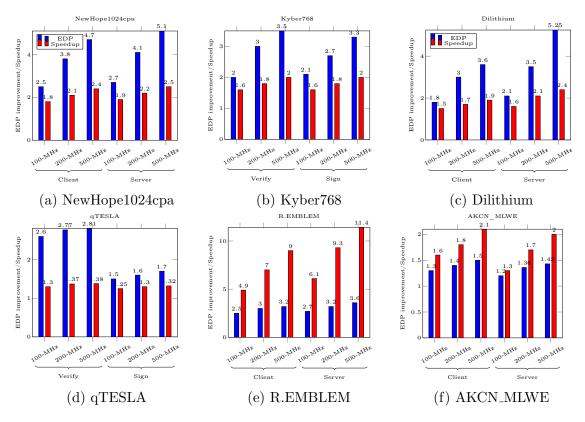

| 3.11<br>3.12      | The sensitivity of the accelerators' performance and power to the cache size. Delay and EDP improvement of the schemes when all the accelerators (fastest design points) at different frequencies are simultaneously attached to the bus | 81<br>86       |

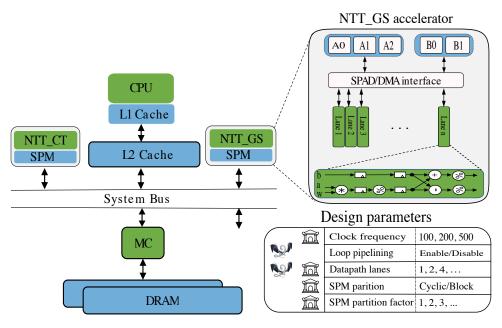

| 4.1<br>4.2        | Design flow of the accelerator generation                                                                                                                                                                                                | 89             |

|                   | column of the table; the next column is the searched spaced in this work                                                                                                                                                                 | 89             |

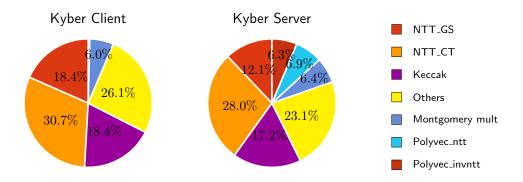

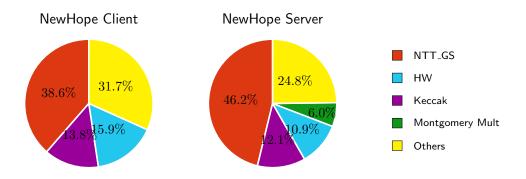

| 4.3               | Profiling results for Kyber based on the user-level CPU cycles                                                                                                                                                                           | 91             |

| 4.4<br>4.5        | Profiling results for NewHope based on the user-level CPU cycles                                                                                                                                                                         | 91             |

|                   | either cyclic or block                                                                                                                                                                                                                   | 93             |

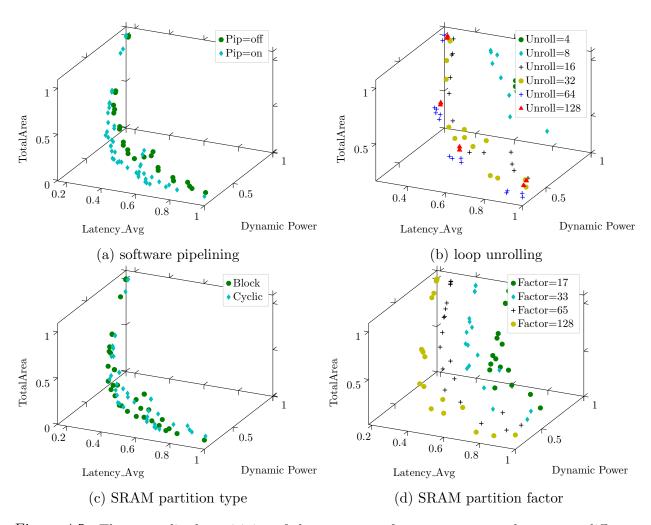

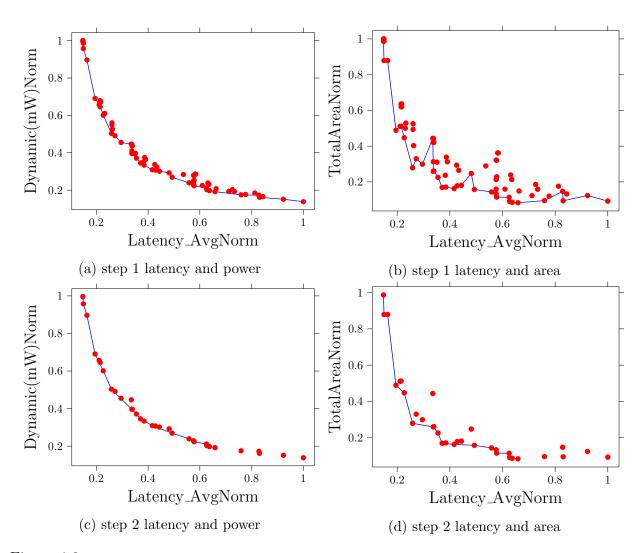

| 4.6 | Multi-objective optimization of 3D-Pareto fronts. The points that do not lie on the blue curve are the non-optimal points                                                                                                                                                                                                                                               | 94  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

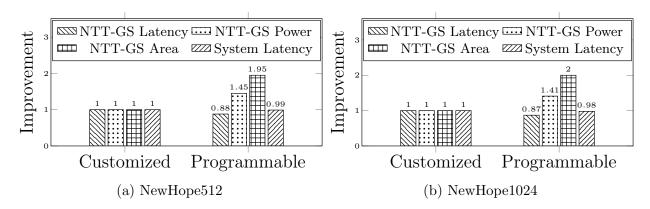

| 4.7 | Comparison of programmable and customized NTT_GS at 100MHz for NewHope512cpa and NewHope1024cpa. Numbers are normalized to the customized accelerator                                                                                                                                                                                                                   | 95  |

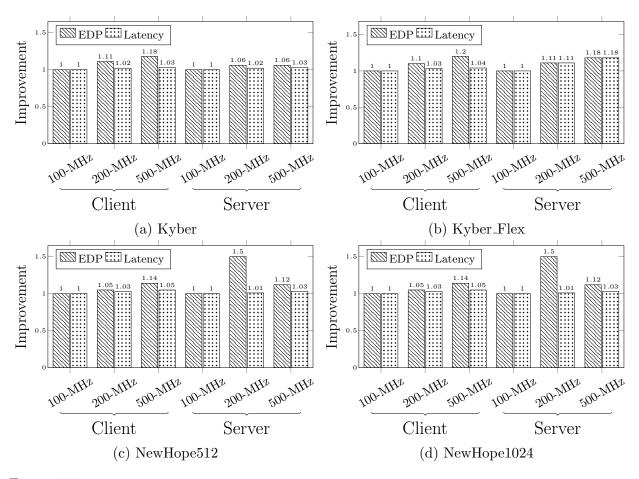

| 4.8 | Normalized latency and EDP improvement of the schemes when the accelerators at different frequencies are simultaneously attached to the bus. Numbers are normalized to the execution case of 100MHz                                                                                                                                                                     | 96  |

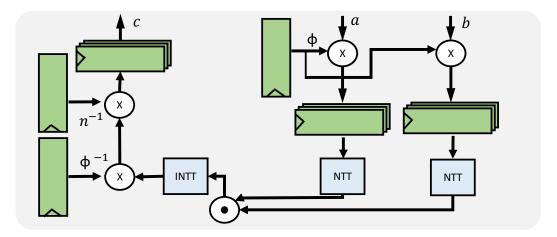

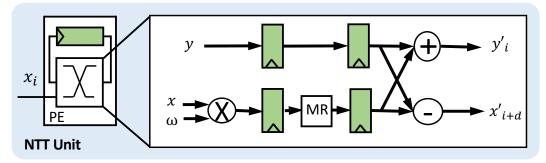

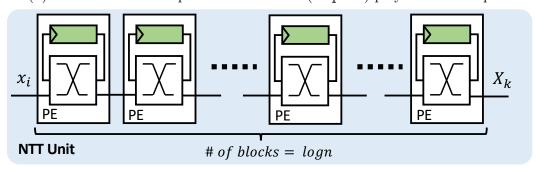

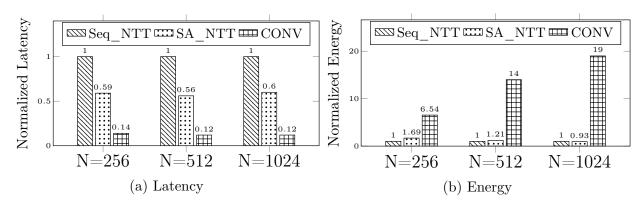

| 5.1 | (a) Polynomial multiplication using NTT units (b) NTT unit based on only one PE which processes inputs sequentially in $(n/2)logn$ iterations. In order to perform polynomial multiplication NTT unit is executed three times (c) NTT-based systolic array polynomial multiplier encompass $logn$ PE blocks as the performs butterfly approximation in $n/2$ iterations | 100 |

| 5.2 | each performs butterfly operation in $n/2$ iterations                                                                                                                                                                                                                                                                                                                   | 102 |

| 0.2 | is performed after each multiplication and addition.                                                                                                                                                                                                                                                                                                                    | 103 |

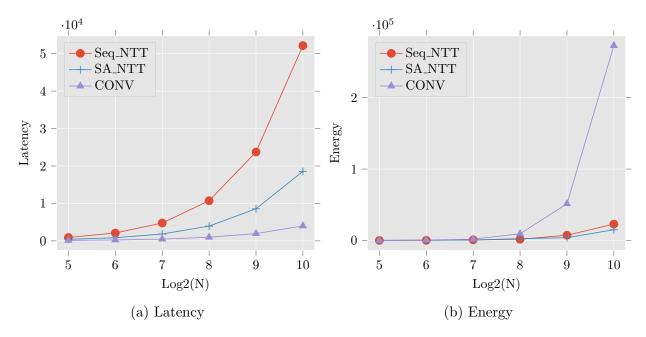

| 5.3 | Increase in the latency and energy of polynomial multiplier by the increase in                                                                                                                                                                                                                                                                                          |     |

|     | the size of the polynomials                                                                                                                                                                                                                                                                                                                                             | 105 |

| 5.4 | Comparison of the different polynomial multiplier designs, normalized to NTT, for polynomials with degree 256, 512 and 1024.                                                                                                                                                                                                                                            | 106 |

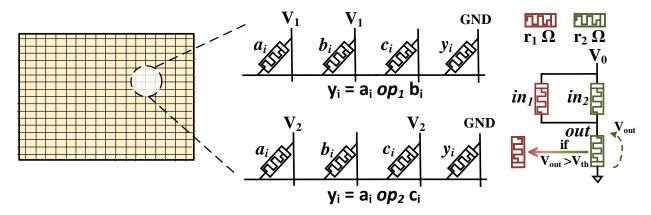

| 6.1 | Digital processing in memory (PIM) overview                                                                                                                                                                                                                                                                                                                             | 112 |

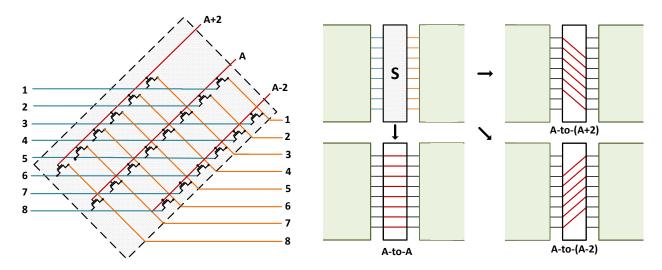

| 6.2 | Data representation and parallel operations in CryptoPIM                                                                                                                                                                                                                                                                                                                | 118 |

| 6.3 | (Left) Detailed circuit of fixed-function switch with 8 inputs/outputs and shift                                                                                                                                                                                                                                                                                        |     |

| C 1 | factor of 2. (Right) All possible connections for s=2                                                                                                                                                                                                                                                                                                                   | 119 |

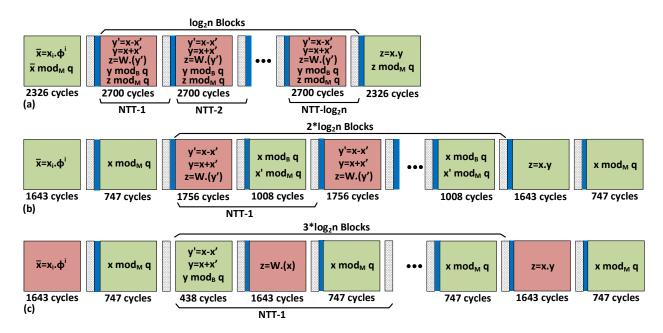

| 6.4 | Detailed stage-by-stage breakdown of (a) Area-efficient pipeline, (b) naive pipeline, and (c) CryptoPIM pipeline. The region between two consecutive blue bars represents a pipeline stage. The slowest stage in a pipeline is colored                                                                                                                                  |     |

|     | red                                                                                                                                                                                                                                                                                                                                                                     | 120 |

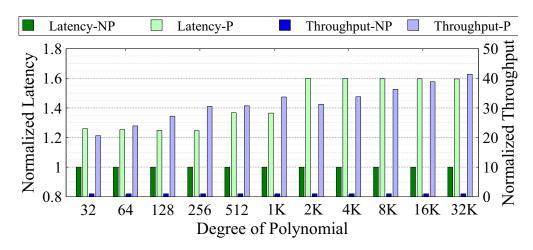

| 6.5 | Normalized latency and throughput of CryptoPIM for different degrees of polynomial. NP and P represent non-pipelined and pipelined designs respec-                                                                                                                                                                                                                      |     |

|     | tively                                                                                                                                                                                                                                                                                                                                                                  | 122 |

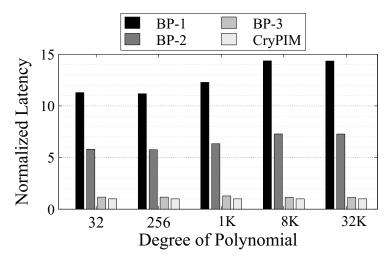

| 6.6 | Comparison of CryptoPIM with PIM baselines                                                                                                                                                                                                                                                                                                                              | 123 |

## LIST OF TABLES

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2.1<br>2.2<br>2.3 | Comparison of different Gaussian samplers; partially extracted from [79] Contemporary lattice-based schemes                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 2.4<br>2.5        | change schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30    |

| 3.1               | Size of loop and data types for NTT_GS and NNT_CT over different schemes. It should be mentioned that the data type for Keccak perform operations over uint64_t for al the schemes                                                                                                                                                                                                                                                                                                                                   | . 78  |

| 4.1               | Performance, energy, and EDP improvement of schemes with different polynomial degrees when the fastest NTT_GS and NTT_CT accelerators (100 MHz) are simultaneously connected to the CPU (2GHz) via DMA (1 GHz)                                                                                                                                                                                                                                                                                                       |       |

| 5.1               | High-level synthesis results on Zynq UltraScale++ for three different designs of polynomial multipliers. To multiply two polynomials using NTT-based multipliers, we need to execute NTT block three times, and each includes bit-reversal, forward NTT, and point-wised multiplication of the input vector with the precomputed twiddle factors. Although the degree of the polynomials in most of the RLWE-based schemes ranges from 256 to 1024, we also provide the results for other degrees to show the trends |       |

| 6.1<br>6.2        | Execution time (cycles) for modulo operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|                   | multiply two polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 125 |

#### ACKNOWLEDGMENTS

I am grateful to my advisor, professor Nikil Dutt for his patience, support, and guidance.

I would like to thank Professor Rainer Döemer and Professor Ian G. Harris for their participation in the thesis committee and providing helpful feedback.

I feel fortunate to receive mentorship from Dr. Rosario Cammarota, principal researcher at Intel Labs. He was always a source of inspiration and motivation for me.

I would like to shout out to my colleagues, Hossein Tajik, Majid Shoushtari, JurnGyu Park, Bryan Donyanavard, Tiago Mück, Chen-Ying Hsieh, Kasra Moazzemi, Sina Shahhosseini, Sina Labbaf, Biswadip Maity, Delaram Amiri, Emad Kasaeyan Naeini, Michael (Tao-Yi) Lee, Kenneth Stewart, Saehanseul Yi, Caio Batista de Melo, Jiyoung An, Khuong Vo, Amirhosein Mohaddesi, and Sujin Kang for their friendship and for sharing the pain.

Finally, my work would not have been possible without funding from the Electrical Engineering and Computer Science department as well as a gift from Qualcomm Technology Inc., or permission from the ACM and IEEE to include content from my previously published work in [160, 164, 163, 167, 165, 166].

## CURRICULUM VITAE

## Hamid Nejatollahi

#### **EDUCATION**

| Doctor of Philosophy in Computer Science                            | 2020                        |

|---------------------------------------------------------------------|-----------------------------|

| University of California, Irvine                                    | Irvine, CA                  |

| Master of Science in Computer Engineering<br>University of Tehran   | <b>2014</b> Tehran, Iran    |

| Bachelor of Science in Computer Engineering<br>University of Tehran | <b>2012</b><br>Tehran, Iran |

#### RESEARCH EXPERIENCE

| Graduate Student Researcher      | 2015 – 2020 |

|----------------------------------|-------------|

| University of California, Irvine | Irvine, CA  |

#### TEACHING EXPERIENCE

| Teaching Assistant               | 2015 – 2020 |

|----------------------------------|-------------|

| University of California, Irvine | Irvine, CA  |

#### INDUSTRY EXPERIENCE

| Embedded Engineer              | Jul. 2014–Jul. 2015 |

|--------------------------------|---------------------|

| Iranian Embedded Systems (IES) | Tehran, Iran        |

| Software Engineering Intern    | Sep. 2013–Jul. 2014 |

| Persian Architecture Systems   | Tehran, Iran        |

#### REFEREED CONFERENCE PUBLICATIONS

| CryptoPIM: In-memory Acceleration for Lattice-based<br>Cryptographic Hardware<br>ACM/IEEE Design Automation Conference (DAC)                                                 | 2020              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Exploring Energy Efficient Quantum-resistant Signal Processing Using Array Processors IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASS)      | <b>2020</b><br>P) |

| Flexible NTT Accelerators for RLWE Lattice-based<br>Cryptography<br>IEEE International Conference on Computer Design (ICCD)                                                  | 2020              |

| Domain-specific Accelerators for Ideal Lattice-based<br>Public Key Protocols<br>Cryptology ePrint Archive, Report 2018/608                                                   | 2018              |

| Trends, Challenges and Needs for Lattice-Based Cryptography Implementations ACM/IEEE International Conference on Hardware/Software Codesign and System Sythesis (CODES+ISSS) | <b>2018</b>       |

| REFEREED JOURNAL PUBLICATIONS                                                                                                                                                |                   |

| Synthesis of Flexible Accelerators for Early Adoption of Ring-LWE Post-quantumCryptography"                                                                                  | 2020              |

| Synthesis of Flexible Accelerators for Early Adoption of          | 2020 |

|-------------------------------------------------------------------|------|

| Ring-LWE Post-quantumCryptography,"                               |      |

| ACM Transactions on Embedded Computing Systems (TECS)             |      |

|                                                                   |      |

| Post-quantum Lattice-based Cryptography Implemen-                 | 2019 |

| Post-quantum Lattice-based Cryptography Implementations: A Survey | 2019 |

#### ABSTRACT OF THE DISSERTATION

Programmable Accelerators for Lattice-based Cryptography

By

Hamid Nejatollahi

Doctor of Philosophy in Computer Science

University of California, Irvine, 2020

Professor Nikil Dutt, Chair

Advances in computing steadily erode computer security at its foundation, calling for fundamental innovations to strengthen the weakening cryptographic primitives and security protocols. While many alternatives have been proposed for symmetric key cryptography and related protocols (e.g., lightweight ciphers and authenticated encryption), the alternatives for public key cryptography are limited to post-quantum cryptography primitives and their protocols. In particular, lattice-based cryptography is a promising candidate, both in terms of foundational properties, as well as its application to traditional security problems such as key exchange, digital signature, and encryption/decryption. At the same time, the emergence of new computing paradigms, such as Cloud Computing and Internet of Everything, demand that innovations in security extend beyond their foundational aspects, to the actual design and deployment of these primitives and protocols while satisfying emerging design constraints such as latency, compactness, energy efficiency, and agility.

In this thesis, we propose a methodology to design programmable hardware accelerators for lattice-based algorithms and we use the proposed methodology to implement flexible and energy efficient post-quantum cache- and DMA-based accelerators for the most promising submissions to the NIST standardization contest. We validate our methodology by integrating our accelerators into an HLS-based SoC infrastructure based on the X86 processor

and evaluate overall performance. In addition, we adopt the systolic architecture to accelerate the polynomial multiplication, which is the heart of a subset of LBC algorithms (i.e., ideal LBC), on the field programmable gate arrays (FPGAs). Finally, we propose a high-throughput Processing In-Memory (PIM) accelerator for number theoretic transform (NTT-) based polynomial multiplier.

## Chapter 1

## Introduction

A worldwide research effort is currently pursuing a scalable quantum computer. Quantum computers, as envisioned by Richard Feynman [90], use quantum mechanics to carry out computation that can reach an exponential speedup in several applications, such as quantum chemistry [172]. Exponential speed up can also be reached in other problems, such as the search for the period of a function. As demonstrated by Peter Shor [208], it would allow us to factorize integers in polynomial time and ultimately render the public key infrastructure insecure. Shore's algorithm needs 6146 and 2330 Qubits to break ECC-256 and RSA-3072, respectively, in 3848 seconds computing the elliptic curve discrete logarithms in  $E(F_p)$  and factoring an RSA modulus N needs 6146 and 2330 Qubits for RSA-3972 and ECC-256, respectively [193].

The scientific community is investing significant efforts to address the problem in a timely and effective way. Post-quantum cryptography is a vibrant area of research devoted to studying alternative public-key algorithms, executed on classical computers, but capable of withstanding quantum computational power. In December 2018, the US president signed H.R. 6227 to fund the National Quantum Initiative Act (NQI)<sup>1</sup>. The law authorizes 1.2 billion

<sup>1</sup>https://fas.org/sgp/crs/misc/R45409.pdf

to be invested in quantum information science over five years. NQI funding will go to the National Institute of Standards and Technology (NIST), National Science Foundation (NSF) Multidisciplinary Centers for Quantum Research and Education and to the Department of Energy Research and National Quantum Information Science Research Centers. The effort of governmental agencies in conducting the standardization of these novel algorithms endorses the urgency of the threat. The most relevant standardization effort is the NIST one, that started in 2017 with the submissions of potential candidates, and continues with the evaluation of the candidates for the next six to seven years, until the selection of the new standards. During the evaluation phase, the proposed algorithms will be analyzed and compared using various parameters, including the security and efficiency of software and hardware implementation.

Among the post-quantum cryptography families, the family of lattice-based cryptography (LBC) appears to be gaining acceptance. Its applications are proliferating for both traditional security problems (e.g., key exchange and digital signature), as well as emerging security problems (e.g., homomorphic schemes, identity-based encryption and even symmetric encryption). Lattice-based cryptographic primitives and protocols provides a rich set of primitives which can be used to tackle the challenges posed by deployment across diverse computing platforms, e.g., Cloud vs. Internet-of-Things (IoT) ecosystem, as well as for diverse use cases, including the ability to perform computation on encrypted data, providing strong (much better understood than before) foundations for protocols based on asymmetric key cryptography against powerful attackers (using Quantum computers and algorithms), and to offer protection beyond the span of traditional cryptography. Indeed, lattice-based cryptography promises to enhance security for long-lived systems, e.g., critical infrastructures, as well as for safety-critical devices such as smart medical implants [98].

# 1.1 Trends, Challenges and Needs for Lattice-based Cryptography Implementations

The emergence of new computing platforms, such as cloud Computing, software defined networks and Internet of Everything, demands the adoption of an increasing number of security standards, which in turn requires the implementation of a diverse set of cryptographic primitives, but this is only part of the story. At the computing platform level, we face a diversity of computing capability. On one end of the spectrum, in the cloud computing and software defined network space, applications demand high-performance, and energy efficiency of cryptographic implementations. This calls for the development of programmable hardware capable of running not only individual cryptographic algorithms, but full protocols efficiently, with the resulting challenge of designing for agility, e.g., designing computing engines that achieve the efficiency of Application-Specific Integrated Circuits (ASICs), while retaining some level of programmability. On the other end of the spectrum, in the IoT space, implementations of standardized cryptography to handle increased key sizes become too expensive in terms of cost, speed, and energy, but are necessary, e.g., in the case of long lived systems such as medical implants and image encryption algorithms [15]. In part, this demands the development of new and strong lightweight alternatives to symmetric key cryptography as well [14]. Furthermore, given the variety of applications and their interplay with the cloud, even in this case agility in the implementation becomes a key requirement. This poses tremendous challenges in the design and implementation of emerging standards for cryptography in a single embodiment, since the computing platforms exact diverging goals and constraints.

Figure 1.1 illustrate the taxonomy of the state-of-the-art accelerator architecture space. Compared to instruction-level accelerators, kernel-level accelerators implement large with more semantically rich functions of computation (e.g., Keccak and polynomial multiplica-

|                       | Part of the<br>Pipeline                  | Attached to<br>Cache                     | Attached to the<br>Memory Bus              | Attached to the I/O Bus        |

|-----------------------|------------------------------------------|------------------------------------------|--------------------------------------------|--------------------------------|

| Instruction-<br>Level | FPU,<br>SIMD,<br>DySER                   | Hwacha,<br>CHARM                         |                                            |                                |

| Kernel-<br>Level      | NPU,<br>10x10,<br>H.264                  | DANA, SNNAP, C-Cores, This Work: TECS'20 | AccStore, This Work: 1-ICCD'19 2-ICASSP'20 | This Work:<br>DAC'20           |

| Application-<br>Level | Oracle/Cavium<br>x86 AES,<br>Crypto Acc, | Key-Value Stores,<br>Memcached           | Sonic3D, IBM<br>Power7+,<br>HARP,          | GPU,<br>IBM Power,<br>Catapult |

Figure 1.1: Accelerator taxonomy [205].

tion) that leads to less flexibility [205]. Application level accelerators compute the whole application with the superior performance but the lowest flexibility. In the order dimension, accelerators can be tightly-coupled (i.e., part of the pipeline) or loosely-coupled to the processor. The more loose the connection to the CPU is, the more flexibility and lower performance are expected.

Cryptographic accelerators, such as X86 AES, are typically tightly-coupled application-level co-processors. However, the early adoption of quantum-resistant hardware is challenging because in this period of transition, during which candidates are still under the evaluation, a post-quantum standard is yet to be decided and also the parameters of the candidates themselves can change; subsequently, it is troublesome to commit to a specific algorithm and a specific set of parameters, knowing that they could be soon outdated [164].

The situation would change if the accelerators would be able to meet two requirements: 1) reach the required performance and 2) be flexible, thus "robust" to change in parameters

and algorithms (providing the so-called crypto-agility). To meet these goals, we propose to accelerate, instead of a complete algorithm, only several portions of the software routines, called micro-kernels. Compared to a whole dedicated accelerator, a micro-kernel accelerator does not reach the same level of performance, because the main processor executes parts of the computation. Subsequently, hardware acceleration based on micro-kernels is more flexible compared to the classical counterparts.

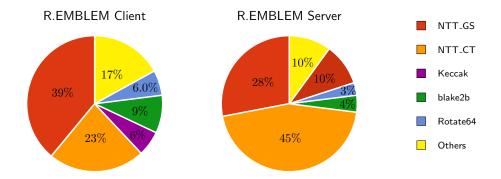

As shown in red, Figure 1.1, we design loosely-coupled kernel-level accelerators which are suitable for LBC schemes because the common resource-intensive kernels consumes most of the execution cycles and power. Figure 1.2 shows the profiling results for the most promising LBC schemes in the server-side (sign) client (verify). NewHope and Kyber are key encapsulation mechanisms (KEM) while Dilithium and qTESLA are digital signatures. NTT\_CT, NTT\_GS, and Keccak consume most of the cycles over different schemes for which we create flexible accelerators.

Figure 1.2: Profiling results for the most promising LBC schemes. Profiling results are based on the user-level CPU cycles

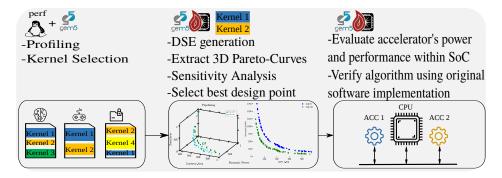

Figure 1.3: Thesis Contribution

#### 1.2 Thesis Contributions

Figure 1.3 divides our contribution into two wide parts: 1) design space exploration (DSE) of accelerators and verify the design in system on chip (SoC) for numerous LBC schemes. 2) Hardware acceleration of polynomial multiplier.

We focus on domain-specific programmable hardware accelerators because they are the most suitable, at this stage, to adopt post-quantum algorithms in hardware. We concentrate on lattice-based algorithms, the most promising family of quantum-resistant algorithms thanks to their versatility and their excellent performance. Around half of the submission to the first round of the NIST PQC Standardization Process belong to this family. After a year of evaluation, 26 of the candidates are chosen for the second round; twelve candidates belong to lattices, and the remaining 14 candidates belong to code-based, hash-based, supersingular elliptic curve isogeny, and multivariate cryptography [164].

#### 1.2.1 Design Space Exploration

As stated earlier, generation of domain specific accelerators involves considering the spectrum of the computing platforms which ranges from resource-constrained IoT devices to performance-driven cloud servers. Therefore, explore the security, performance, area, power, and energy trade-offs of the target kernels seems to be essential. In this dissertation, we adopt a Pre-RTL simulation framework to explore the design space of micro-kernel-based accelerators for a subset of (LBC) algorithms (i.e., ideal LBC) and implement the identified accelerators. Based on Figure 1.2, we explore design space of the below resource-intensive kernels:

- 1. **Keccak**. Keccak is a family of cryptographic primitives primarily as a candidate for the NIST SHA-3 competition [34]. The main transformation in the family is the Keccak-f[1600] permutation which is used in the sponge mode in the specification for the SHA-3 hash function. The hash function operates on a state of 1600 bits and is designed for easy implementation in both software and hardware.

- 2. Number theoretic transform (NTT). Polynomial multiplication is usually performed using the NTT, a variant of the Discrete Fourier Transform (DFT) for polynomial rings on finite arithmetic fields [160]. The process is slow due to the repeated use of expensive operations like multiplication and modulo reduction. Two common algorithms of performing NTT are Cooley-Tukey (NTT\_CT) [61], produces the result in the bit-reverse order by receiving the input in the correct order, and Gentleman-Sande (NTT\_GS) [100], receives the input in the reverse order and produces the output in the correct order. As can be seen in Figure 1.2, and NTT\_GS and NTT\_CT are the most resource-intensive kernels in the ideal LBC schemes.

We design cache-assisted [166] (Chapter3) and DMA-assisted [163] (Chapter4) accelerators and evaluate them into an HLS-based SoC infrastructure based on the X86 processor and evaluate overall performance, power, and energy.

#### 1.2.2 Hardware Acceleration of Polynomial Multiplier

Polynomial multiplication is the most time-consuming routine intideal LBC schemes. We design accelerators for two common methods to compute the polynomial multiplication.

- 1. Convolution-based multiplier. The easiest method to multiply two polynomials is to use the convolution (Schoolbook [135]) with the time complexity of  $O(n^2)$ . We adopt the systolic architecture [137] to accelerate the polynomial multiplication and implement on Zynq UltraScale+ FPGA [167] (Chapter5). Our design is 22x faster than the state-of-the-art FGPA implementation of the polynomial multiplier in the NewHope-Simple key exchange mechanism on a low-cost Artix7 FPGA [223] for polynomial degree n=1024.

- 2. NTT-based multiplier. Polynomial multiplier is usually implemented by the Number Theoretic Transform (NTT), which drops the time complexity of the polynomial multiplier from  $\mathcal{O}(n^2)$  to  $\mathcal{O}(n \cdot \log n)$ . We present FPGA-based [167] and processing in memory (PIM-) based [165] in Chapter5 and Chapter6, respectively.

- **FPGA-based NTT**. We design and implement two NTT-based polynomial multipliers on FPGAs.

- Seq\_NTT. Sequential NTT-based multiplier which consists of a single butterfly operator and perform the polynomial multiplication in serial. It achieves 3x speedup over the state-of-the-art on a low-cost Artix7 FPGA [223] for polynomial degree n=1024.

- SA\_NTT. When synthesized on a Zynq UltraScale+ FPGA, the *NTT-based* systolic array design (SA\_NTT) achieve on average 1.7x speedup over our sequential NTT-based multiplier which means it is 5x faster than the state-of-the-art [223] for polynomial degree n=1024.

• PIM-based NTT. We design a high throughput PIM-based NTT that

- achieves 31x throughput improvement with the same energy and 28% latency reduction compare to the our NTT on FPGA [167] (which itself is 3x faster than the state-of-the-art [223] for polynomial degree n=1024).

- provides 5x throughput improvement with the 20x energy reduction, but 6x latency increase compare to Convolution-based multiplier on FPGA [167].

- enables fast execution of the polynomial multiplication with the support of polynomials with degrees up to 32k, accommodating requirements for public key cryptographic systems for data at rest and in communication, and data in use, i.e., homomorphic encryption.

The rest of the thesis is organized as follows: Chapter 2 provides the background for LBC primitives and surveys the LBC implementations; Chapter 3 and Chapter 4 detail the designed cache- and DMA-based accelerators, respectively. Chapter 5 discusses the FPGA-based polynomial multipliers. Chapter 6 introduces the PIM-based polynomial multiplier. Finally, we conclude the thesis in Chapter 7.

## Chapter 2

## Background and Related Works

Lattice-based cryptographic primitives and protocols provides a rich set of primitives which can be used to tackle the challenges posed by deployment across diverse computing platforms, e.g., Cloud vs. Internet-of-Things (IoT) ecosystem, as well as for diverse use cases, including the ability to perform computation on encrypted data, providing strong (much better understood than before) foundations for protocols based on asymmetric key cryptography against powerful attackers (using Quantum computers and algorithms), and to offer protection beyond the span of traditional cryptography. Indeed, lattice-based cryptography promises to enhance security for long-lived systems, e.g., critical infrastructures, as well as for safety-critical devices such as smart medical implants [98]. In this chapter, we review the foundations of lattice-based cryptography, some of the more adopted instances of lattices in security, their implementations in software and hardware, and their applications to authentication, key exchange and digital signatures.

#### 2.0.1 Arithmetic and Components of Lattices

In this section, we provide an evaluation of the components in a lattice-based cryptosystem that guides the actual implementation. To components are critical: (a) the Polynomial multiplication for ideal lattices, and matrix multiplication for standard lattice are the main speedup bottlenecks; (b) The discrete Gaussian sampling is used to sample noise in order to hide the secret information. There are various algorithms for the sampler and multiplier in the literature, by providing the designer with a specific goal [160]. We briefly review different algorithms and outline their practical implementations in Section 2.1.1

There exist two main classes of lattice-based algorithms used in cryptography, namely NTRU and Learning with Error (LWE). The security of NTRU is based on hardness not-provably reducible to solving the Closest Vector Problem (CVP) in a lattice, whereas the security of LWE relies on provably reducible solving the Shortest-Vector Problem (SVP) in a lattice. Consequently, NTRU suffers from security guarantees, but in practice provides more flexibility and efficiency in the implementation. On the contrary, LWE problems are resistant to quantum attacks, while their relatively inefficient nature led researchers to devise more efficient formulations, e.g., over rings - Ring Learning with Errors (Ring-LWE).

Implementations are broadly classified in pure software, pure hardware, and hardware/software co-design cryptographic engines [160]. Implementation of the modulo arithmetic (multiplication and addition of big numbers) is a bottleneck in LBC. For Standard LWE schemes, matrix multiplication algorithms are adopted, whereas number theoretic transform (NTT) is a better choice for polynomial multiplication in Ring-LWE. A summary of modular arithmetic is presented in Figure 2.1.

In addition to the arithmetic portion, a bottleneck in lattice-based schemes is the extraction of the random term, which usually is implemented with a discrete noise sampler (from a discrete Gaussian distribution) and can be done with rejection, inversion, Ziggurat, or

Figure 2.1: Common modular Multiplication algorithms

Knuth-Yao sampling with moderate standard deviation for key exchange and public key encryption, and small standard deviation for digital signature to achieve a compact and secure signature.

When implemented, Standard LWE-based schemes exhibit a relatively large memory footprint due to large key size - hundreds of kilobyte for the public key - which render a straightforward implementation of standard LWE-based schemes impractical. The adoption of specific ring structures, e.g., Ring-LWE, offers key size reduction by a factor of n compared to Standard LWE [151], making Ring-LWE an excellent candidate for resource-constrained devices, such as Wi-Fi capable smart devices, including medical implants. Another avenue to address resource constrained devices is that memory footprint can be traded off with security assurance, which improves both efficiency and memory consumption.

High-performance Intel/AMD processors, which are notoriously equipped with AVX vector instructions, and ARM/AVR micro-controllers are popular platforms for software im-

plementations, as we will see in more detail in the coming sections. Practical software implementations of standard lattices, encryption scheme [122] and key exchange [42], have been published recently. For hardware implementations, FPGAs provide flexibility and customization but not agility. Hardware implementations of lattice-based schemes (e.g., BLISS-I [79] with higher security level) are about an order of magnitude faster than the hardware implementation of RSA-2048 [123]. Furthermore, another candidate platform to implement lattice-based schemes is application specific integrated circuits (ASICs) of which there appear to be no such implementations in the literature at this time. However, the main advantages and challenges for ASIC design of lattice-based schemes are presented in [170].

#### 2.0.1.1 The multiplier component

Matrix multiplication is used for the standard lattices, while polynomial multiplication is employed for ideal lattices. Arithmetic operations for a Ring-LWE based scheme are performed over a ring of polynomials. The most time and memory consuming part is the polynomial multiplication. The easiest way to multiply two polynomials is to use the Schoolbook algorithm with the time complexity of  $O(n^2)$  [135]. Let n and p be degree of the lattice (n is a power of 2) and a prime number ( $p = 1 \mod 2n$ ), respectively.  $Z_p$  denotes the ring of integers modulo p and  $x^{n+1}$  is an irreducible degree n polynomial. The quotient ring  $R_p$ , contains all polynomials with the degree less than n in  $Z_p$ , that defines as  $R_p = Z_p/[x^{n+1}]$  in which coefficients of polynomials are in the range [0,p).

The number theoretic transform (NTT) is a generalization of Fast Fourier Transform (FFT), which is carried out in a finite field instead of complex numbers. The latter could achieve time complexity of  $O(n\log n)$ . In other words,  $\exp(-2\pi j/N)$  with  $n^{th}$  primitive root of unity  $\omega_n$  which is defined as the smallest element in the ring that  $\omega_n^n = 1 \mod p$  and  $\omega_n^i \neq 1 \mod p$  for  $i \neq n$ . The main idea behind this is to use the point value representation instead of the coefficient representation by applying NTT in  $O(n\log n)$ ; thereafter performing point-

wise multiplication in O(n) and finally converting the result to coefficient representation by applying Inverse NTT (INTT) in  $O(n\log n)$ .

$$a(x) \times b(x) = NTT^{-1}(NTT(a) \odot NTT(b)) \tag{2.1}$$

Where  $\odot$  is the point-wise multiplication of the coefficients. If NTT is applied to a(x) with  $(a_0, ..., a_{n-1})$  as coefficients, we would have:

$$(\hat{a_0}, \dots, \hat{a_{n-1}}) = NTT(a_0, \dots, a_{n-1}) \tag{2.2}$$

$$\hat{a}_i = \sum_{j=0}^{n-1} a_i \omega^{ij} mod(p), i = 0, 1, ..., n-1$$

(2.3)

In order to retrieve the answer from point value representation using  $NTT^{-1}$ , it is sufficient to apply NTT function with  $-\omega$  and divide all the coefficients by n:

$$a_i = \sum_{j=0}^{n-1} \hat{a}_i \omega^{-ij} mod(p), i = 0, 1, ..., n-1$$

(2.4)

In order to compute NTT(a), we pad the vector of coefficients with n zeros that leads to doubling the input size. Negative wrapped convolution technique [227], avoids doubling the input size.

To improve efficiency of polynomial multiplications with NTT, combining multiplications of powers of  $\omega$  with powers of  $\psi$  and  $\psi^{-1}$  ( $\psi^2 = \omega$ ) is beneficial which requires storage mem-

ory for precomputed powers of  $\omega$  and  $\psi^{-1}$  in bit-reversed order [196, 185, 145]. NTT can be used only for the  $p=1\pmod{2}$  (mod 2 n) case where p is a prime integer. Suppose  $a'=(a_0,\psi a_1,...,\psi^{n-1}a_{n-1}),\ b'=(b_0,\psi b_1,...,\psi^{n-1}b_{n-1}),\ c'=(c_0,\psi c_1,...,\psi^{n-1}c_{n-1})$  to be coefficient vectors of the a,b,c that are multiplied component-wise by  $(1,\psi^1,...,\psi^{n-1})$ . Based on the negative wrapped convolution theorem, modulo  $(x^n+1)$  is eliminated and the degree of NTT and  $NTT^{-1}$  is reduced from 2n to n.

$$c' = NTT^{-1}(NTT(a') \odot NTT(b')) \tag{2.5}$$

$$c = (\psi^0 c'_0, \psi^{-1} c'_1, ..., \psi^{-n+1} c'_{n-1})$$

(2.6)

Two common algorithms to compute NTT are Cooley-Tukey butterfly (CT) [61] and Gentleman-Sande butterfly (GS) [100]. CT, decimation-in-time, outputs the result in the bit-reverse order by getting the input in the the correct order. GS, decimation-in-frequency, receives the input in the reverse order and produces the output in the correct order [145]. Employing GS to compute both NTT and  $NTT^{-1}$  involves in bit-reverse calculation [11]; however, bit-reverse step can be avoided by using CT for NTT and GS for  $NTT^{-1}$  [43, 145].

Other popular multiplication algorithms in literature are the Karatsuba algorithm (with time complexity of  $O(n^{\log 3/\log 2})$  [131]), and subsequent variants of it [65]. Schönhage-Strassen with time complexity of  $O(n.\log n.\log\log n)$  [203] outperforms the Karatsuba algorithm [52].

An extensive analysis and comparison for hardware complexity of various modular multiplications, including Schoolbook (classical), Karatsuba, and FFT, with different operand

size, are presented in [65]. Authors calculate hardware complexity of each multiplier by decomposing it into smaller units such as the full adder, half adder, multiplexer, and gate. Rafferty et al. [189] adopt the same approach to analyze large integer multiplications of both combined and individual multipliers. Karatsuba multiplier outperforms for operands greater or equal to 32 bits. Schoolbook imposes large memory footprint in order to store partial products which negatively impact performance that is mitigated by Comba [59] with the same time complexity but relaxing memory addressing by optimizing the sequence of partial products. Rafferty et al. compare hardware complexity, in terms of +, -, and \* units, of different combinations of classical (Comba), Karatsuba, and FFT (NTT for integers) for up to multipliers with 65536-bit operands. However, they evaluate the latency and clock frequency by implementing in hardware (Xilinx Virtex-7 FPGA) for up to 256-bits for the combination of NTT+Comba and 4096-bit for Karatsuba+Comba which are not in a good range for lattice-based cryptography (e.g.,  $1024 \times 14 = 14336$  bits are used for NewHope key exchange). Based on their (analytical) hardware complexity analysis, the combination of Karatsuba-Schoolbook is the best choice for operands under 64 bits. Karatsuba-Comba is preferable for operands for 64 bits to 256 bits. For larger operands, the lowest hardware complexity is achieved by combined multiplier NTT-Karatsuba-Schoolbook. It should be mentioned that results are for a single multiplication. Authors make some assumption for the sake of simplicity such as the shift operation is free and inputs are ready.

#### 2.0.1.2 The Sampler Component

The quality of a discrete Gaussian sampler is determined by a tuple of three parameters:  $(\sigma, \lambda, \tau)$ . In such a tuple  $\sigma$  is the standard deviation (adjusts dispersal of data from the mean),  $\lambda$  is the precision parameter (controls statistical difference between a perfect and implemented discrete Gaussian sampler), and  $\tau$  is the distribution tail-cut (determines amount of the distribution that we would like to ignore). Each of these parameters affects the secu-

rity and efficiency of the sampler. For instance, a smaller standard deviation decreases the memory footprint required to store precomputed tables. For encryption/decryption schemes  $\sigma$ =3.33 [143] is suggested. Digital signature sampling from a Gaussian sampler involves large  $\sigma$ =215 [79]. However, by employing Peikert's convolution lemma [173], the standard deviation can be reduced by order of magnitude which is a remarkable improvement on the precomputed table size. Speed and memory footprint is  $\lambda$  dependent, i.e., higher  $\lambda$  results in more secure but a slower and bigger sampler. The tail of the Gaussian distribution touches the x-axis at  $x=+\infty$  (considering only the positive side due to the symmetry) with negligible probability. Tail-cut parameter  $(\tau)$  defines the amount of the distribution that we would like to ignore, hence random number e is sampled in  $|e| \in \{0, \sigma \times \tau\}$  instead  $|e| \in \{0, \infty\}$ . Instead of the statistical distance, Rényi divergence technique [21] can be employed to measure the distance between two probability distributions (e.g., [11]). More precisely, in lattice-based cryptography, Rényi divergence is used to generalized security reductions. Sampling the discrete Gaussian distribution is one the most time and memory hungry parts of lattice-based cryptosystems, due to the demands of high precision, many random bits, and huge lookup tables. To be more specific, the obligatory negligible statistical distance between the implementation of a Gaussian sampler (approximated) and the theoretical (perfect) discrete Gaussian distribution imposes expensive precise floating point arithmetic (to calculate the exponential function) or large memory footprint (to store precomputed probabilities). To keep statistical distance less than  $2^{-\lambda}$ , floating point precision with more than standard double-precision is obligatory which is not natively supported by the underlying platform; thus software libraries should be used to perform higher floating-point arithmetic. It is impractical to sample from a perfect Gaussian sampler; hence a  $\lambda$ -bit uniform random integer is used to approximate the discrete sampler. Fortunately, it is proven that the Gaussian sampler could be used to achieve  $\lambda/2$  security level (approximated sampler) instead of  $\lambda$  level (perfect sampler), since (to date) there is no algorithm that can distinguish between

a perfect sampler ( $\lambda$  bits) and an approximate sampler ( $\lambda$ /2 bits) [198]. In other words,

we can cut half of the bits in the sampler which results in a smaller and faster sampler [122, 199, 26]. Reduction in precision parameter (from  $\lambda$  to  $\lambda/2$ ) changes tail-cut parameter ( $\tau$ ) as  $\tau = \sqrt{\lambda \times 2.ln(2)}$  [121]. Sampling from a Gaussian distribution may lead to a timing side-channel attack, which can be avoided by using a constant generic time Gaussian Sampling over integers [155]. Folláth provides a survey of different Gaussian samplers in lattice-based cryptography schemes with a more mathematical outlook [92]. Gaussian samples are classified into six categories and guidelines provided for choosing the best candidate on different platforms for specific parameter ranges. However, we organize Gaussian samplers into the following types discussed below. A Summary of advantage and disadvantages of each sampler are listed in Table 2.1.

#### Rejection Sampler

Firstly, x is sampled in  $(-\tau\sigma,\tau\sigma)$  uniformly at random where  $\tau$  and  $\sigma$  are tail-cut and standard deviation of Gaussian distribution. After that, x is rejected with the probability proportional to 1-exp $(-x^2/2\sigma^2)$ . The high rejection rate of samples (on average eight trials to reach acceptance) along with expensive calculation of exp() are the main reasons for the inefficiency [225]. Göttert et al. [103] employ rejection sampler for the first time within LBC. Remarkable speed and area improvement could be achieved by accomplishing rejection operation using lazy floating-point arithmetic [83].

#### Bernoulli Sampler

Bernoulli is an optimized version of rejection sampling in order to reduce average required attempts for a successful sampler from 10 to around 1.47 with no need to calculate exp() function or precomputed tables [178]. Bernoulli is introduced in [79] for lattice-based cryptography and used widely in the research community [183, 180, 122]. The main idea be-

hind Bernoulli sampling is to approximate sampling from  $D_{\mathbb{Z},k\sigma_2}$  using the distribution  $k \cdot D_{\mathbb{Z}^+,\sigma_2} + \mathbb{U}(\{0,...,k-1\})$  where  $\mathbb{U}$  is the uniform distribution. The procedure for Bernoulli sampler is shown below in 5 steps.

- 1. sample  $x \in \mathbb{Z}$  according to  $D_{\mathbb{Z}^+,\sigma_2}$  with probability density of  $\rho_{\sigma_2} = e^{-x^2/(2\sigma_2^2)}$

- 2. sample  $y \in \mathbb{Z}$  uniformly at random in  $\{0,...,k-1\}$  and calculate  $z \leftarrow y + kx, j \leftarrow y(y+2kx)$

- 3. sample  $b \leftarrow \mathcal{B}_{-j/2\sigma^2}$  where  $\sigma = k\sigma_2$  and  $\mathcal{B}$  is Bernoulli distribution. To sample from  $\mathcal{B}_c$  where c is a precomputed constant value, a uniform number  $u \in [0,1)$  with  $\lambda$ -bit precision is sampled; 1 is returned if u < c, otherwise 0 should be returned.

- 4. if b = 0 goto to step (1)

- 5. if z = 0 go to step (1), otherwise generate  $b \leftarrow \mathcal{B}_{1/2}$  and return  $(-1)^b z$  as the output

The standard deviation of the target Gaussian sampler  $D_{\mathbb{Z},k\sigma_2}$ , equals  $k\sigma_2$  where  $\sigma_2 = \sqrt{\frac{1}{2ln^2}} \approx 0.849$  where standard deviation of the binary Gaussian sampler  $D_{\mathbb{Z},\sigma_2}$  and  $k \in \mathbb{Z}^+$  are uniform distribution parameters. For schemes with small standard deviation (e.g., public key encryption) sampling from binary Gaussian distribution can be eliminated [183], while for digital signatures with large standard deviation, using Gaussian distribution is mandatory [180]. Gaussian distribution can be replaced with other distributions (e.g., uniform distribution [105]). Bernoulli approach avoids long integer calculation and employs single bit operations that make it beneficial for hardware implementation. The time dependency of Bernoulli makes it vulnerable to timing attacks that are resolved in the hardware implementation of BLISS in [180]. Precomputed tables in Bernoulli sampling are small, besides binary Gaussian distribution (easy to sample intermediate sampler) is independent of  $\sigma$  hence the Peikert convolution lemma (smaller  $\sigma$ ) does not have a considerable effect on the area. How-

ever, convolution lemma reduces the area of precomputed tables in CDT sampler by a factor of  $23 \times$  for BLISS (reduces  $\sigma$  from 215 to 19.47).

#### Binomial Sampler

Centered Binomial distribution  $(\psi_k)$  is a close approximation of rounded Gaussian sampler  $(\xi_{\sigma})$  that eliminates the need for computing exp() and precomputed large tables. Let  $\sigma = \sqrt{8}$  be the standard deviation of  $\xi_{\sigma}$  and a binomial distribution is parameterized with  $k = 2\sigma^2$ ; choosing  $\psi_k$  as the sampling distribution has negligible statistical difference with rounded Gaussian sampler with  $\sigma = \sqrt{8}$  [11]. Centered Binomial distribution  $(\psi_k)$  for integer  $k \geq 0$  is defined as sampling  $2 \cdot k$  random numbers uniformly from  $\{0,1\}$  as  $(a_1, ..., a_k, b1, ..., b_k)$  and output  $\sum_{i=1}^k (a_i, b_i)$  as the random sample [11]. Since k scales with power 2 of  $\sigma$ , it is not practical to use binomial sampling for digital signatures with large standard deviation. Binomial sampler has been employed inside software implementation of NewHope [12, 13, 216, 179], HILA5 [200], LAC [147], LIMA [211], Kyber [43, 16] and Titanium [215]. It also is used in hardware implementation of NewHope [223].

#### Ziggurat Sampler

Ziggurat sampler is a variation of rejection sampler introduced in [152] for a continuous Gaussian sampler  $^1$ . The discrete version of Ziggurat sampler is proposed in [47] which is suitable for schemes with large standard deviation. The area under the probability density function is divided into n rectangles with the same area whose size is proportional to the probability of sampling a point in each rectangle. The left and right corners of each rectangle are on the y-axis and Gaussian distribution curve, respectively. Each rectangle is stored using

<sup>&</sup>lt;sup>1</sup>Another method to sample from a continuous Gaussian is **Box-Muller** [45]. Box-Muller method transforms two independent uniforms into two independent discrete Gaussian distributions. pqNTRUSign [50] and NTRUEncrypt [229] use Box-Muller based Gaussian sampler.

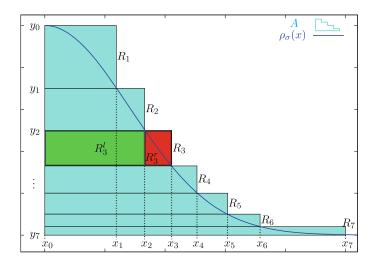

its lower right coordinates (Figure 2.2). Firstly, rectangle  $R_i$  and point  $x_i$  inside the rectangle is chosen uniformly at random. Since we are considering positive  $x_i$ , a random sign bit, s, is also required. If  $x_i \leq x_{i-1}$ ,  $x_i$  resides below the curve and would be accepted. Otherwise, a uniformly random  $y_i$  is sampled and if  $y_i \leq exp(x_i)$ , the random point  $(x_i, y_i)$  is accepted; otherwise new random x should be sampled and the process is repeated.

Figure 2.2: A partition of Ziggurat [47].

More rectangles reduce the number of rejections, better performance, and higher precision.

Due to its flexibility

#### Cumulative Distribution Table (CDT) Sampling

CDT is also known as the inversion sampling method [173]. CDT is faster than rejection and Ziggurat samplers by avoiding the use of expensive floating-point arithmetic [222]. Since in cumulative distribution all the numbers are less than 1, it is sufficient to use the binary expansion of the fraction. CDT requires a large table to store values of the cumulative distribution function (CDF) of the discrete Gaussian (highest memory footprint [92]) for which their size is a function of distribution tail-cut  $(\tau)$  and Gaussian parameter  $(\sigma)$ . Variable r is sampled uniformly at random in the range [0,1) with  $\lambda$  bits of precision. The goal is to find

an x whose probability is  $\rho(x) = S[x+1] - S[x]$  where S[x] equals the value of CDF at x. CDT performs a search, usually binary search, on the CDF to find the corresponded x. A standard CDT needs table of size at least  $\sigma\tau\lambda$  bits; for instance BLISS-IV ( $\sigma=13.4, \tau=215, \lambda=128$ ) and BLISS-I ( $\sigma=13.4, \tau=19.54, \lambda=128$ ) need at least pre-computed tables of size 630 kbits and 370 kbits for 192 and 128 bit post-quantum security, which is not practical for resource-constrained embedded devices [79]. By employing Peikert's convolution lemma [173], the size of precomputed tables are dropped by the factor of 11 by sampling twice from  $\tau' = \frac{\tau}{\sqrt{1+k^2}} = 19.47$  instead of sampling from a  $D_{Z,\tau}$  with  $\tau=215$ . Further improvements on table size are presented in [178] by employing adaptive mantissa size which halves the table size.

Pöppelmann et al. [181] proposed a hardware implementation of CDT sampler which is further optimized in [182, 180, 73]. Du et al. [72] propose an efficient software implementation of CDT that is vulnerable to timing attack which is resolved in [133] by suggesting a time-independent CDT sampler. Pöppelmann et al. [183] combine the CDF and rejection sampling to achieve a compact and reasonably fast Gaussian sampler.

#### Knuth-Yao sampler

The Knuth-Yao sampler [136] provides a near optimal sampling (suitable for the high precision sampling) thanks to its near entropy consumption of the random bits required by the sampling algorithm. Assume n to be number of possible values for each random variable r with the probability of  $p_r$ . The probability matrix is constructed based on the binary expansion of each variable whose  $r^{th}$  row denotes the binary expansion of  $p_r$ . According to the probability matrix, a discrete distribution generating the binary tree (DDG) is built whose  $i^{th}$  level corresponds to the  $i^{th}$  column of the probability matrix. Sampling is the procedure of walking through the DDG tree until a reaching a leaf and returning its value as the sampling value. At each level, a uniformly random bit indicates whether the left child

or right child of the current node should be visited in the future. The Knuth-Yao sampler is suitable for schemes with small standard deviations; thus Knuth-Yao is not suitable for digital signature because of its slow sampling caused by a high number of random bits. In order to minimize the statistical distance between the approximated distribution and the true Gaussian distribution, Knuth-Yao sampler needs large memory to store probability of the sample points with high precision, which is an issue on resource-constrained platforms. Combination of Knuth-Yao and CDT results in about halving the table sizes, which is still prohibitively large; however, the Bernoulli sampler offers the best-precomputed table size [79].

De Clercq et al. [66] introduce an efficient software implementation of the Ring-LWE based cryptosystem by using Knuth-Yao as a Gaussian sampler. Using a column-wise method for sampling, Roy et al. [197] propose the first hardware implementation of the Knuth-Yao sampling with small standard deviation which results in faster sampling. Same authors improve their implementation in [195].

Based on the presented results on [47], with the same memory budget, CDT beats rejection sampling and discrete Ziggurat. The Ziggurat sampler outperforms CDT and rejection sampling for larger values of the standard deviation. Ziggurat sampler bears almost the same speedup as Knuth-Yao, while it improves the memory footprint by a factor of 400. As stated earlier, due to the large standard deviation necessary for digital signature, Knuth-Yao sampler is not suitable for digital signatures. Inside an encryption scheme with  $\sigma_{LP} = 3.3$  [143], with the same security level ( $\lambda = 64$ ), Knuth-Yao sampler beats CDT in terms of number of operations performed in one second per slice of FPGA (Op/s/S) for time-independent implementation [133]. However, for a time-dependent Gaussian sampler with the same security level ( $\lambda = 94$ ), the CDT sampler proposed by Du and Bai [73] outperforms Knuth-Yao implementation of [195] in term of Op/s/S.

The Size of precomputed tables in a Bernoulli sampler is two orders of magnitude smaller than

Table 2.1: Comparison of different Gaussian samplers; partially extracted from [79].

| Sampler   | Speed    | FP exp() | Table Size                       | Table Lookup                 | Entropy                    | Features                              |

|-----------|----------|----------|----------------------------------|------------------------------|----------------------------|---------------------------------------|

| Rejection | slow     | 10       | 0                                | 0                            | $45+10log_2\sigma$         | suitable for constrained devices      |

|           |          |          |                                  |                              |                            | suitable for encryption               |

| Ziggurat  | flexible | flexible | flexible                         | flexible                     | flexible                   | requires high precision FP arithmetic |

|           |          |          |                                  |                              |                            | not suitable for HW implementation    |

| CDT       | fast     | 0        | $\sigma \tau \lambda$            | $log_2(\tau\sigma)$          | $2.1 + log_2\sigma$        | suitable for digital signature        |

| CD1       | last     |          | 017                              | 1092(10)                     | $2.1 \pm i0g_20$           | easy to implement                     |

| Knuth-Yao | fastest  | 0        | $1/2\sigma\tau\lambda$           | $log_2(\sqrt{2\pi e}\sigma)$ | $2.1 + log_2\sigma$        | not suitable for digital signature    |

| Bernoulli | fast     | 0        | $\lambda log_2(2.4\tau\sigma^2)$ | $\approx log_2\sigma$        | $\approx 6 + 3log_2\sigma$ | suitable for all schemes              |

| Binomial  | fast     | 0        | 0                                | 0                            | $4\sigma^2$                | not suitable for digital signature    |

that of CDT and Knuth-Yao sampler [79]; however, CDT has three times more throughput than Bernoulli for hardware implantation of BLISS in [180].

# 2.0.2 Lattice-based schemes

Security of the lattice-based cryptography schemes are based on hardness of solving two average-case problems, a.k.a Short Integer Solution (SIS) [154] and the Learning With Errors (LWE) problem [190].

Regev [190] proposed the Learning With Errors problem which can be reduced to a worst-case lattice problem like the Shortest Independent Vectors Problem (SIVP). In the proposed scheme, the ciphertext is  $\mathcal{O}(n\log n)$  times bigger than plaintext; however, in [175] ciphertext has the same length order compared to the plaintext. A smaller key size for LWE-based encryption is introduced as the LP scheme in [143]. Another difference between Regev's encryption scheme and LP scheme is that the former uses discrete Gaussian sampler in the key generation step, while LP employs Gaussian Sampler in encryption in addition to the key generation step.

## 2.0.2.1 Public Key Encryption

Public key encryption (PKE) is employed to encrypt and decrypt messages between two parties. Additionally, it is a basis for other cryptography schemes such as digital signatures. Generally, it consists of three steps including key generation, encryption, and decryption. The first party (Alice) generates two set of keys and keeps one of them private  $(sk_{Alice})$  and distributes the other key  $(pk_{Alice})$  to other party (Bob). In order to send the message M to Alice, Bob encrypts the message as  $S = Enc(M, pk_{Alice})$  where  $pk_{Alice}$  is Alice's public and Enc is encryption cipher. Thereafter, Alice decrypts the message as  $M = Dec(S, sk_{Alice})$  where Dec is the decryption cipher and  $sk_{Alice}$  is Alice's private key. Similarly, Alice should encrypt her message with Bob's public key  $(pk_{Bob})$  if she wants to send message to Bob. Encryption and decryption ciphers are one-way functions and are known publicly; hence the only secret data are private keys of the recipients which should be impossible to uncover using their corresponding public keys. Practical lattice-based PKE schemes are either based on NTRU related [115, 213] or LWE [190] (and its variants including RLWE [151], MLWE [142], ILWE [144] and MPLWE [194]) assumptions.

## 2.0.2.2 Digital Signature

Digitally signing a document involves sending the signature and document separately. In order to verify the authenticity of the message, the recipient should perform verification on both the signature and the document. Digital signature consists of three steps including key generation,  $\operatorname{Sign}_{sk}$ , and  $\operatorname{Verify}_{pk}$ . In the first step, secret key ( $\mathfrak{sk}$ ) and public key ( $\mathfrak{pk}$ ) are generated; signer keeps the secret key and all verifier parties have the public key of signer. During the sign step, signer applies the encryption algorithm on input message M with its private key and produces output S as  $S = \operatorname{Sign}_{sk}(M, sk_{signer})$ . Signer sends the tuple (M, S) to the Verifier who applies  $\operatorname{Verify}_{pk}(M, S)$  and outputs 1 if M and S are a valid message