# **UC San Diego**

### **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Ultra-Low-Power Sensors and Receivers for IoT Applications

#### **Permalink**

https://escholarship.org/uc/item/6m01s3vf

#### **Author**

Jiang, Haowei

### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### **Ultra-Low-Power Sensors and Receivers for IoT Applications**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Haowei Jiang

Committee in charge:

Professor Drew A. Hall, Chair Professor Gert Cauwenberghs Professor Young-Han Kim Professor Patrick P. Mercier Professor Gabriel M. Rebeiz

©

Haowei Jiang, 2019

All rights reserved.

| The Dissertation of Haowei Jiang is approved, and it is acceptable in quality and form for |

|--------------------------------------------------------------------------------------------|

| publication on microfilm and electronically.                                               |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

| Chair                                                                                      |

University of California San Diego

2019

## TABLE OF CONTENTS

| Signatu   | re Page i                                         | lii |

|-----------|---------------------------------------------------|-----|

| Table of  | f Contents                                        | iv  |

| List of I | Figures                                           | ix  |

| List of T | Tablesx                                           | ۷V  |

| Acknow    | vledgementsx                                      | vi  |

| Vita      | X                                                 | ix  |

| Abstrac   | t of the Dissertationxx                           | ζii |

| Chapter   | 1: Introduction                                   | . 1 |

| 1.1       | Motivation for Internet-of-Things Sensors         | . 1 |

| 1.2       | Event-Driven Communication Using Wake-up Receiver | . 3 |

| 1.3       | Compound Sensor Using Unified Analog Front-End    | . 5 |

| 1.4       | Scope of Dissertation                             | . 7 |

| Chapter   | 2: N-zero WuRXs with Active Envelope Detection    | . 8 |

| 2.1       | Introduction                                      | . 8 |

| 2.2       | Prior WuRX Architectures                          | 10  |

| 2.2       | .1 Low-or Uncertain-IF Architectures              | 10  |

| 2.2       | .2 Direct Envelope Detection Architectures        | 12  |

| 2.3       | Proposed WuRX Architecture                        | 12  |

| 2.3       | .1 Direct-ED RF Front-End Optimization            | 13  |

|     | 2.3  | .2    | Baseband Bandwidth Consideration             | 15 |

|-----|------|-------|----------------------------------------------|----|

|     | 2.3  | .3    | Digital Baseband Processing.                 | 15 |

| 2.  | .4   | Sys   | tem Analysis & Modelling                     | 16 |

|     | 2.4  | .1    | Sensitivity Analysis                         | 16 |

|     | 2.4  | .2    | Simulink Behavior Model                      | 18 |

| 2.  | .5   | Circ  | cuits Implementation                         | 19 |

|     | 2.5  | .1    | Transformer/Filter                           | 19 |

|     | 2.5  | .2    | Envelope Detector                            | 23 |

|     | 2.5  | .3    | Comparator and S/H Stage                     | 28 |

|     | 2.5  | .4    | Digital Baseband                             | 33 |

|     | 2.5  | .5    | Relaxation Oscillator                        | 36 |

| 2.  | .6   | Mea   | asurement Results                            | 37 |

| 2.  | .7   | Figu  | are of Merit and Comparison                  | 45 |

| 2.  | .8   | Sun   | nmary                                        | 46 |

| Cha | pter | 3: N  | -Zero WuRXs with Passive Envelope Detection  | 48 |

| 3.  | .1   | Intro | oduction                                     | 48 |

| 3.  | .2   | Sys   | tem Design Consideration                     | 51 |

|     | 3.2  | .1    | Carrier Frequency and Architecture Selection | 51 |

|     | 3.2  | .2    | RF Circuit Design Challenges                 | 52 |

|     | 3.2  | .3    | BB Circuit Design Challenges                 | 52 |

| 3.3 RF        | Circuit Design.                                   | 54 |

|---------------|---------------------------------------------------|----|

| 3.3.1         | Antenna                                           | 54 |

| 3.3.2         | Matching Network                                  | 55 |

| 3.3.3         | Envelope Detector                                 | 57 |

| 3.4 Bas       | seband Circuit Design                             | 59 |

| 3.4.1         | Baseband Amplifier                                | 60 |

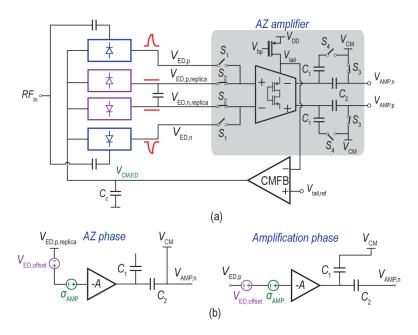

| 3.4.2         | Autozeroing Network                               | 62 |

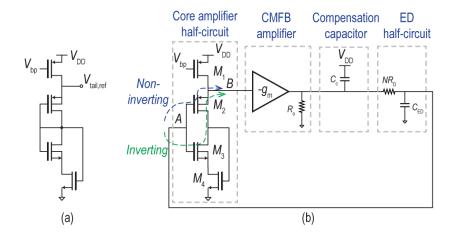

| 3.4.3         | Common-Mode Feedback                              | 64 |

| 3.4.4         | Comparator, Correlator, and Oscillator            | 66 |

| 3.5 Mea       | asurement Results                                 | 68 |

| 3.6 Cor       | nclusion                                          | 73 |

| Chapter 4: To | emperature Compensations in WuRXs                 | 74 |

| 4.1 Intr      | oduction                                          | 74 |

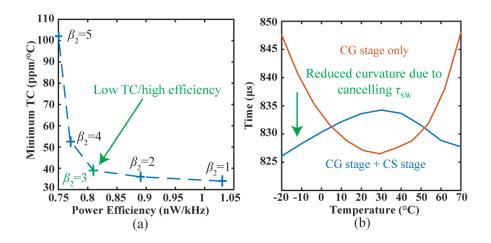

| 4.2 Rel       | axation Oscillator Temperature Compensation       | 75 |

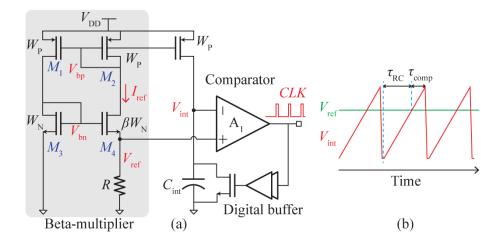

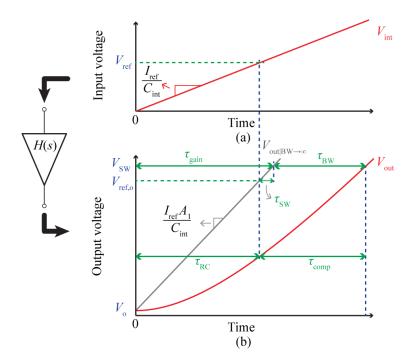

| 4.2.1         | Generic Relaxation Oscillator                     | 76 |

| 4.2.2         | Comparator Delay Analysis                         | 77 |

| 4.2.2         | .1 Comparator Delay Model                         | 77 |

| 4.2.2         | .2 Temperature Dependence of the Comparator Delay | 80 |

| 4.2.3         | Relaxation Oscillator Circuit Design              | 82 |

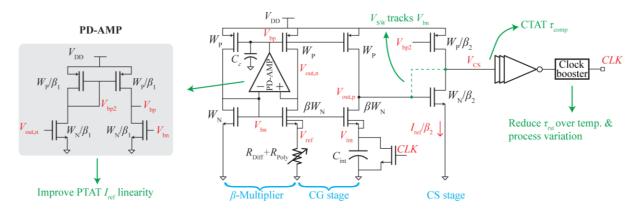

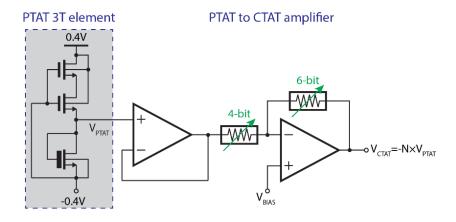

| 4.2.2         | .3 High Linearity PTAT Reference Generator        | 82 |

| 4.2.2        | Two-Stage $\tau_{SW}$ -Cancelling Comparator                       | 85  |

|--------------|--------------------------------------------------------------------|-----|

| 4.2.2        | Bias Resistor DAC (RDAC) and Clock Booster                         | 89  |

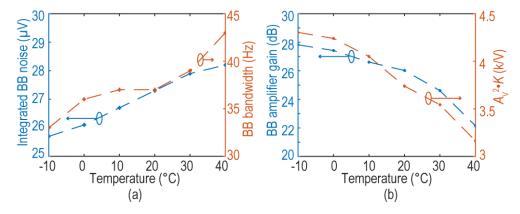

| 4.3 Sig      | rnal Path Temperature Compensation                                 | 90  |

| 4.3.1        | RF/Conversion Gain                                                 | 91  |

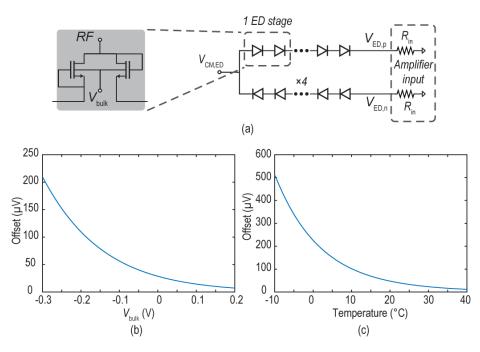

| 4.3.2        | ED Temperature-Stabilization via a CTAT Bulk Bias                  | 91  |

| 4.3.3        | BB Amplifier Temperature-Stabilization via a Constant-Current Bias | 92  |

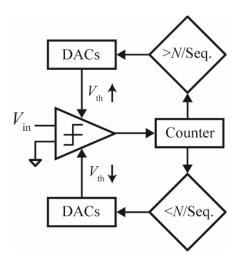

| 4.3.4        | Comparator Threshold Dynamic Tuning                                | 93  |

| 4.4 Me       | easurement Results                                                 | 94  |

| 4.4.1        | Relaxation Oscillator Measurement                                  | 94  |

| 4.4.2        | Signal Path across Temperature Measurement                         | 97  |

| 4.5 Con      | nclusion                                                           | 100 |

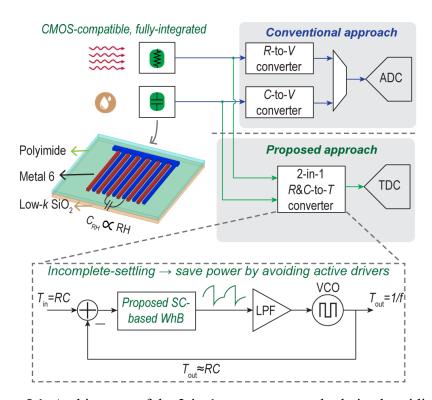

| Chapter 5: A | 2-in-1 Temperature and Humidity Sensor                             | 101 |

| 5.1 Intr     | roduction                                                          | 101 |

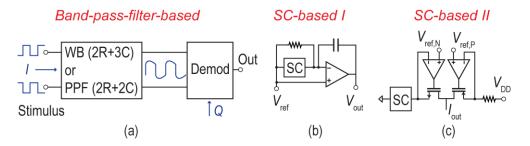

| 5.2 Prio     | or R- & C-Interfaces                                               | 104 |

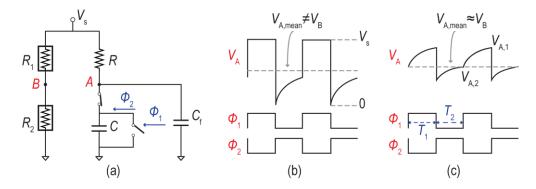

| 5.3 Inc      | omplete-Settling SC-Based WhB                                      | 106 |

| 5.4 Sys      | stem Design                                                        | 110 |

| 5.4.1        | System Architecture                                                | 110 |

| 5.4.2        | Dynamic Analysis                                                   | 112 |

| 5.4.3        | Sensitivity Analysis                                               | 114 |

| 5.5 Cir      | cuit Implementation                                                | 117 |

| 5.5.      | 1 SC Front-End                     | 117 |

|-----------|------------------------------------|-----|

| 5.5.      | 2 Chopper-Stabilized Active Filter | 119 |

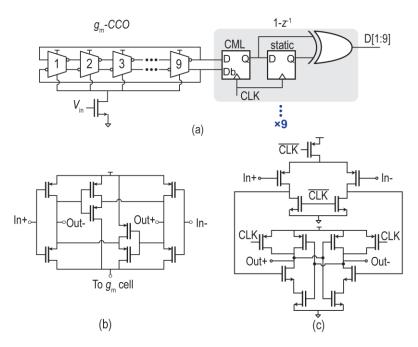

| 5.5       | 3 VCO & TDC                        | 121 |

| 5.6       | Measurement                        | 123 |

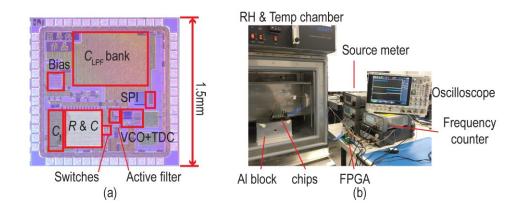

| 5.6.      | 1 PI-Coating & Measurement Setup   | 124 |

| 5.6.2     | 2 Measurement Results              | 125 |

| 5.7       | Conclusion.                        | 130 |

| Chapter ( | 6: Summary                         | 131 |

| 6.1       | Summary of Dissertation            | 131 |

| 6.2       | Areas for Future Work              | 133 |

| Referenc  | es.                                | 135 |

## LIST OF FIGURES

| Figure 1.1. Illustration of an IoT sensor                                                                                |

|--------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Diagram of (a) periodic wake-up and (b) employing a WuRX                                                     |

| Figure 1.3. N-ZERO circuit power saving as a function of event activity                                                  |

| Figure 2.1. Wake-up radio architectures: (a) mixer-based low-IF, (b) mixer-based uncertain-IF,                           |

| and (c) direct envelope detection                                                                                        |

| Figure 2.2. Overview of the proposed WuRX.                                                                               |

| Figure 2.3. WuRX Simulink model                                                                                          |

| Figure 2.4. WuRX BB Simulink model                                                                                       |

| Figure 2.5. Schematic of (a) transformer/filter and (b) equivalent circuit model                                         |

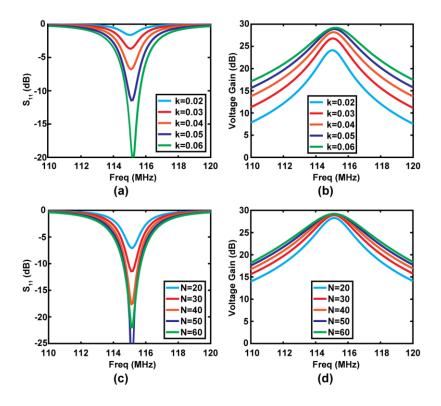

| Figure 2.6. Plot of (a) $S_{11}$ vs. $k$ ; (b) voltage gain vs. $k$ ; (c) $S_{11}$ vs. $N$ ; (d) voltage gain vs. $N$ 21 |

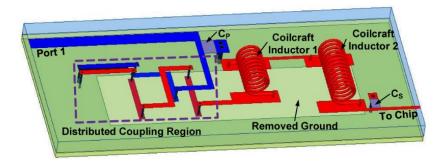

| Figure 2.7. 3-D model of the transformer/filter. 23                                                                      |

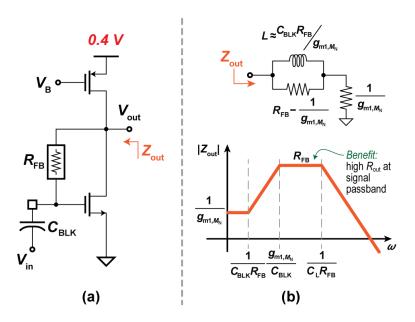

| Figure 2.8. (a) Schematic of proposed active-L biased ED; (b) active-L biasing circuit model and                         |

| Bode plot of ED output impedance                                                                                         |

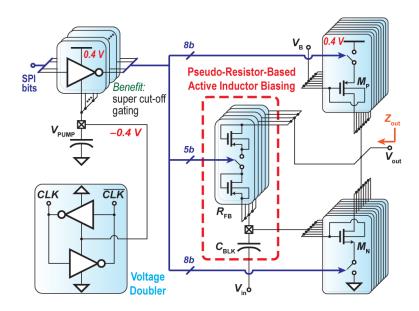

| Figure 2.9. Full schematic of the proposed low-voltage active-L biased DTMOS ED with                                     |

| boosted binary-weighted SPI control                                                                                      |

| Figure 2.10. Simulated ED output SNR vs. integrated comparator noise voltage for different                               |

| biasing schemes                                                                                                          |

| Figure 2.11. (a) Schematic of the dynamic two-stage comparator, and (b) simulation showing                |

|-----------------------------------------------------------------------------------------------------------|

| 1 <sup>st</sup> /2 <sup>nd</sup> stage output voltages                                                    |

| Figure 2.12. (a) Schematic of the comparator, S/H stage and clocking; (b) timing diagram of the           |

| of the early-reset feedback; (c) schematic of the early-reset feedback                                    |

| Figure 2.13. Digital correlator baseband logic with wake-up signal output driver                          |

| Figure 2.14. (a) Simulated switching threshold for inverter with minimum35                                |

| Figure 2.15. Schematic of the relaxation oscillator.                                                      |

| Figure 2.16. Simulated and measured transformer $S_{11}$ and voltage gain                                 |

| Figure 2.17. Measurement results of (a) ED conversion gain; (b) Scaling factor $k_{\rm ED}$               |

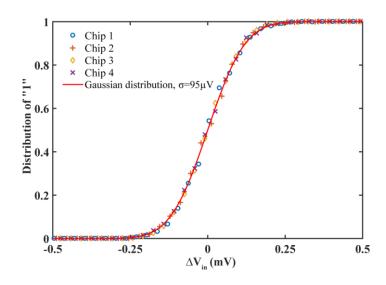

| Figure 2.18. Measured comparator noise CDFs                                                               |

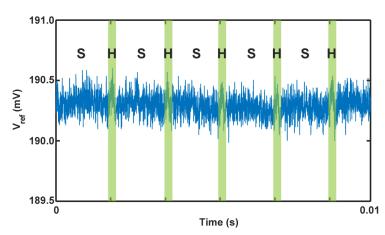

| Figure 2.19. Measured reference ladder output voltage with S/H phases annotated                           |

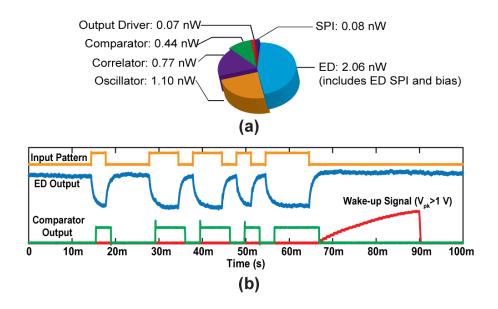

| Figure 2.20. (a) System power breakdown; (b) transient waveforms                                          |

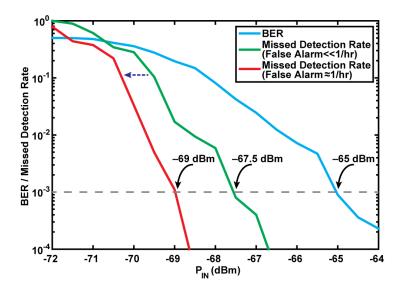

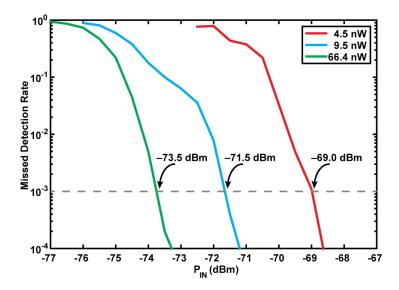

| Figure 2.21. BER and MDR waterfall curves with a 300 bps data rate                                        |

| Figure 2.22. MDR waterfall curves for different power settings with a 300 bps data rate 43                |

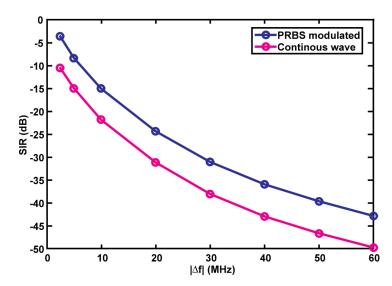

| Figure 2.23. SIR curve vs. interferer frequency offset $ \Delta f $ to carrier frequency for a worst-case |

| 300bps PRBS-modulated jammer and a CW jammer                                                              |

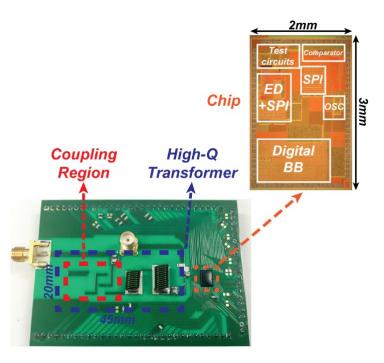

| Figure 2.24. Picture of annotated die micrograph (top); whole WuRX (bottom)                               |

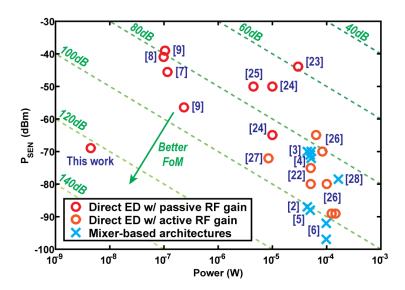

| Figure 2.25. Sensitivity vs. power (FoM <sub>LAT</sub> )                                                  |

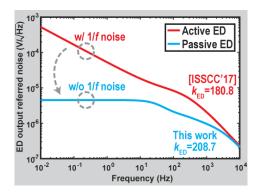

| Figure 3.1. Active ED vs. passive ED                                                                      |

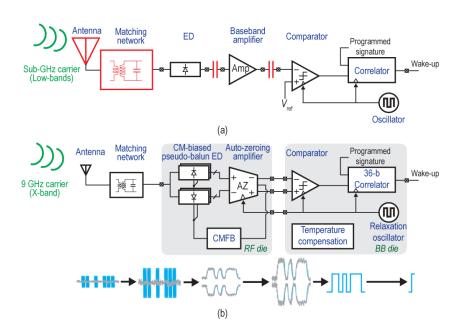

| Figure 3.2. Block diagram of (a) conventional ac-coupled WuRX and (b) the proposed WuRX.50         |

|----------------------------------------------------------------------------------------------------|

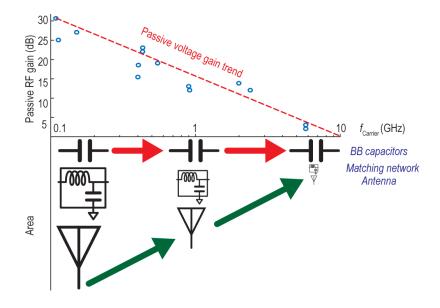

| Figure 3.3. MN voltage gain and component size vs. carrier frequency                               |

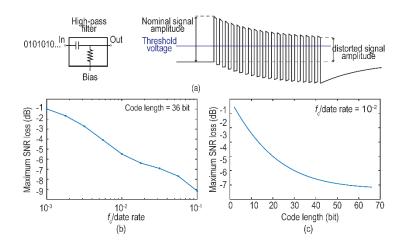

| Figure 3.4. Simulated waveform output when fc/data rate is 0.01 and simulated maxi-mum SNR         |

| loss (b) versus fc/data rate, and (c) versus code length                                           |

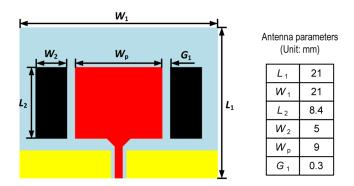

| Figure 3.5. 9 GHz patch antenna layout                                                             |

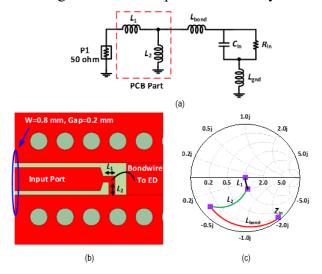

| Figure 3.6. (a) Schematic of the 9 GHz transformer, (b) Layout of the transformer, and (c)         |

| Matching procedure                                                                                 |

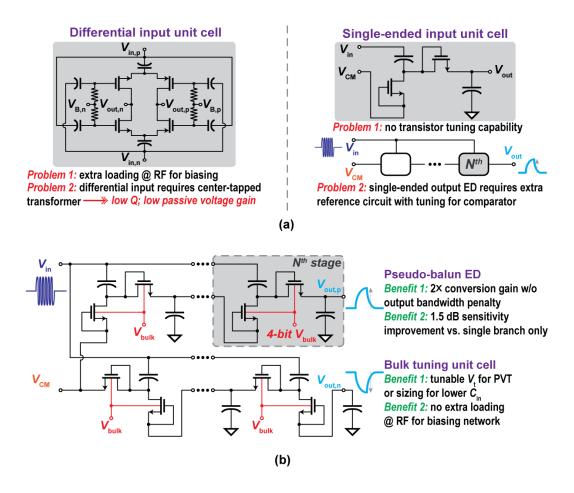

| Figure 3.7. (a) Conventional passive ED unit cells and architectures; (b) proposed passive         |

| pseudo-balun ED with bulk tuning unit cell                                                         |

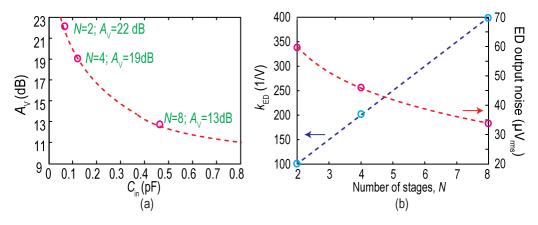

| Figure 3.8. Simulated (a) transformer gain vs. Cin, and (b) kED and ED noise vs. N                 |

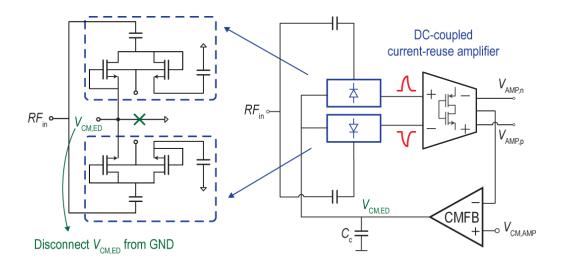

| Figure 3.9. Proposed (a) core amplifier and (b) CM-biased ED using global CMFB                     |

| Figure 3.10. (a) Circuit model showing the ED offset issue and simulated offset versus (b) ED      |

| bulk bias and (c) temperature                                                                      |

| Figure 3.11. Schematic of the proposed (a) replica ED and autozeroing network, and (b) half-       |

| circuit model during AZ phase and amplification phase                                              |

| Figure 3.12. Schematic of the (a) replica bias and (b) CMFB loop                                   |

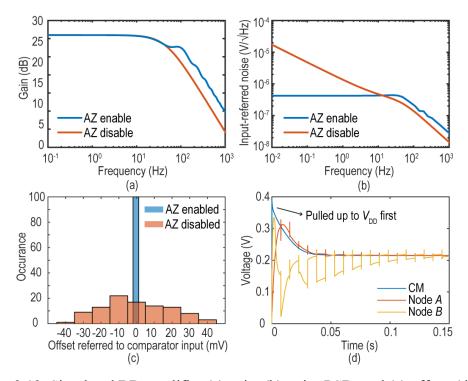

| Figure 3.13. Simulated BB amplifier (a) gain, (b) noise PSD, and (c) offset. (d) Startup transient |

| simulation                                                                                         |

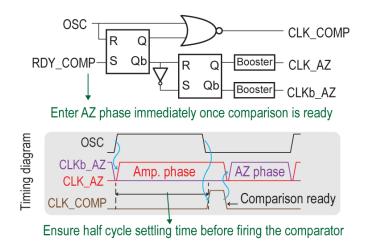

| Figure 3.14. Schematic and timing of the AZ and comparator clock generator                         |

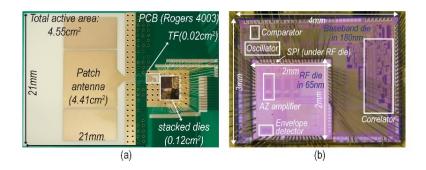

| Figure 3.15. Annotated photograph of (a) PCB and (b) stacked die                                   |

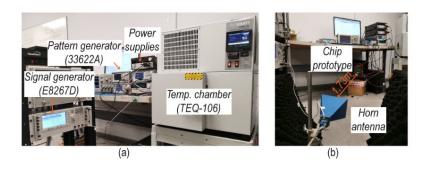

| Figure 3.16. Photos of (a) across temperature test setup, and (b) wireless test setup              |

|----------------------------------------------------------------------------------------------------|

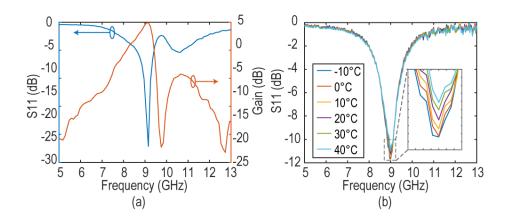

| Figure 3.17. Measured (a) antenna $S_{11}$ and gain, and (b) transformer $S_{11}$                  |

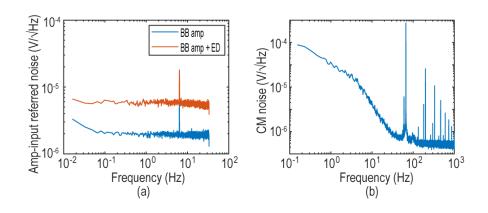

| Figure 3.18. Measured noise PSD in (a) differential-mode and (b) common-mode                       |

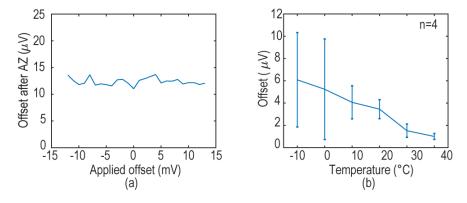

| Figure 3.19. Measured AZ amplifier (a) input-referred offset and (b) offset over temperature 70    |

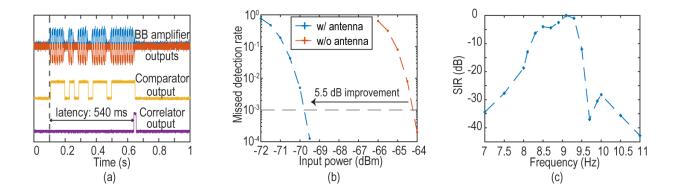

| Figure 3.20. Measured (a) transient waveform, (b) MDR curve, and (c) SIR versus frequency 71       |

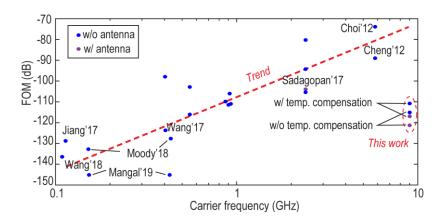

| Figure 3.21. Landscape of WuRXs. 72                                                                |

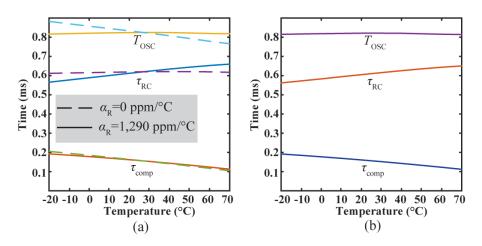

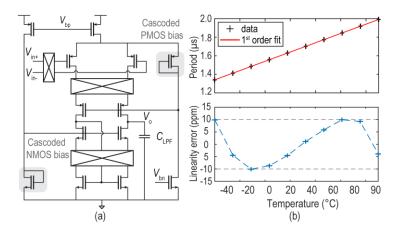

| Figure 4.1. (a) Schematic of a typical comparator-based relaxation oscillator, (b) illustration of |

| delay components, where $\tau_{\text{buf}}$ and $\tau_{\text{rst}}$ are too trivial to show        |

| Figure 4.2. Model of the comparator delay following an integrator. and driving a buffer 77         |

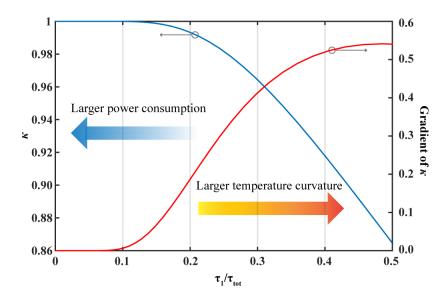

| Figure 4.3. Numerical solutions for $\kappa$ vs. $\tau_1/\tau_{tot}$ .                             |

| Figure 4.4. Schematic of a relaxation oscillator employing a two-stage comparator, along with      |

| PD-AMP in feedback to improve PTAT current temperature linearity                                   |

| Figure 4.5. Simulations showing (a) reference current vs. temperature, and (b) reference current   |

| vs. supply voltage                                                                                 |

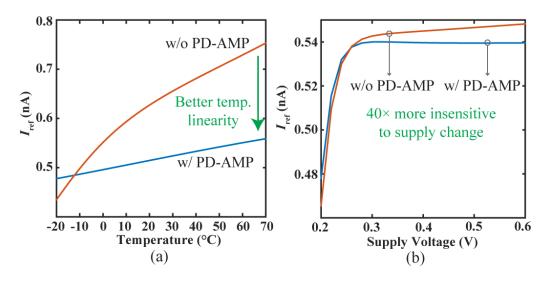

| Figure 4.6. Simulated waveforms for one oscillation cycle                                          |

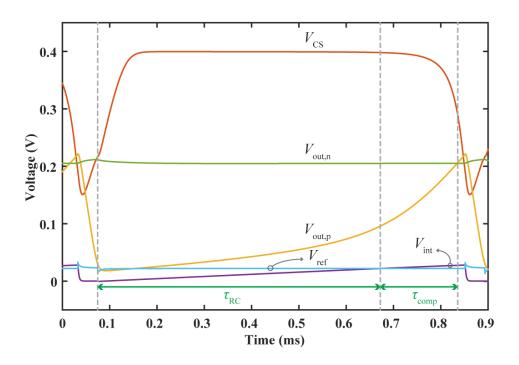

| Figure 4.7. Simulation showing (a) TC vs. power efficiency for different sizing ratios, and (b)    |

| $T_{\rm OSC}$ vs. temperature showing curvature                                                    |

| Figure 4.8. Simulated delays with (a) ideal resistors and (b) actual RDAC                          |

| Figure 4.9. Schematic of the ED bulk bias circuit                                                  |

| Figure 4.10. Block diagram of the comparator threshold dynamic tuning logic                              |

|----------------------------------------------------------------------------------------------------------|

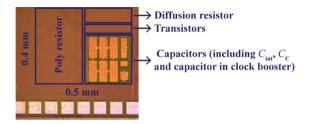

| Figure 4.11. Die photo annotated with components                                                         |

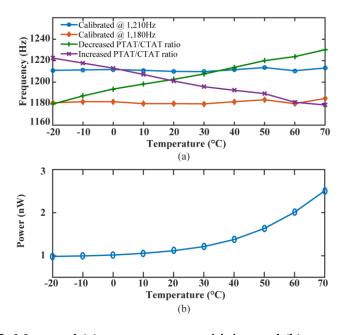

| Figure 4.12. Measured (a) temperature sensitivity, and (b) power vs. temperature                         |

| Figure 4.13. Measured (a) temperature sensitivity of 5 chips, (b) Allan deviation, (c) frequency         |

| and power vs. supply voltage, and (d) temperature sensitivity at different supply voltages 97            |

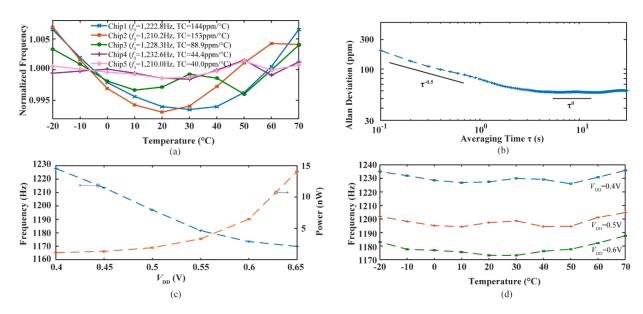

| Figure 4.14. Measured (a) ED bulk bias, and (b) BB amplifier current reference                           |

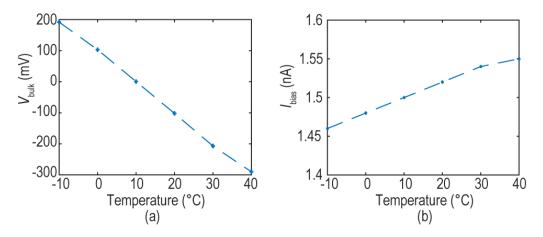

| Figure 4.15. Measured (a) BB bandwidth and noise, and (b) BB gain and RF/conversion gain 99              |

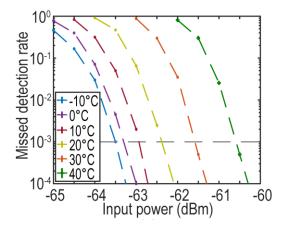

| Figure 4.16. Measured MDR curves over temperature                                                        |

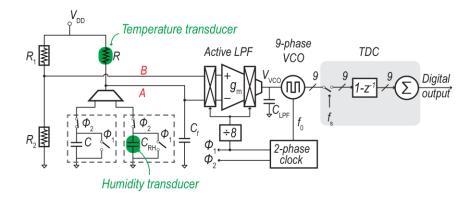

| Figure 5.1. Architecture of the 2-in-1 temperature and relative humidity sensor                          |

| Figure 5.2. Prior work that could be used for R&C sensing, based on (a) a band-pass-filter, (b) a        |

| SC integrator, and (c) a SC resistor and LDO.                                                            |

| Figure 5.3. (a) Schematic of a SC-based WhB and transient waveforms (not to scale) when (b) $C_{\rm f}$  |

| = 0 and (c) $C_f \gg C$                                                                                  |

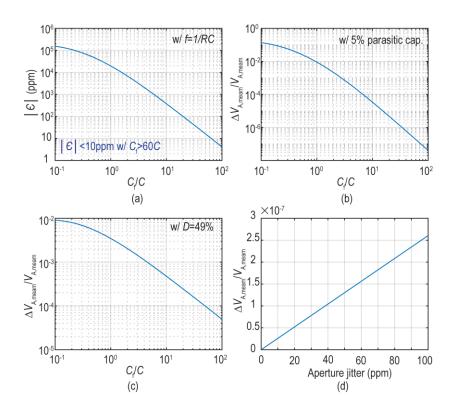

| Figure 5.4. Simulated (a) $ \epsilon $ vs. $C_f/C$ , WhB output change vs. $C_f/C$ (b) with 5% parasitic |

| capacitance, (c) with 49% duty cycle, and (d) with a clock phase error                                   |

| Figure 5.5. System schematic of the RH/Temp sensor using RCDC                                            |

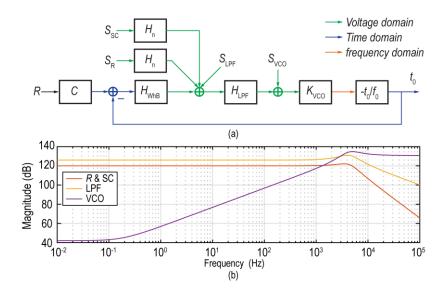

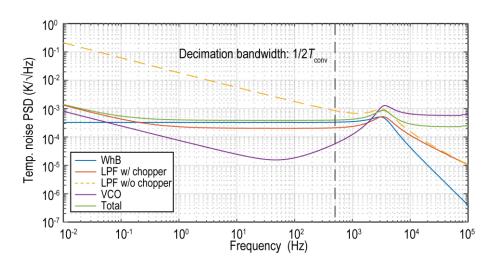

| Figure 5.6. (a) FLL block diagram and (b) NTFs of different blocks                                       |

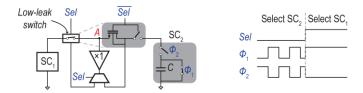

| Figure 5.7. Schematic and timing of the high isolation multiplexer scheme.                               |

| Figure 5.8. (a) Schematic of the active filter (b) simulated FLL transfer curve and linearity error. |

|------------------------------------------------------------------------------------------------------|

|                                                                                                      |

| Figure 5.9. Simulated FLL noise PSD referred to the temperature input                                |

| Figure 5.10. Schematic of (a) the VCO and TDC, (b) delay cell, and (c) double-tail latch 123         |

| Figure 5.11. Photograph of (a) annotated die and (b) measurement setup                               |

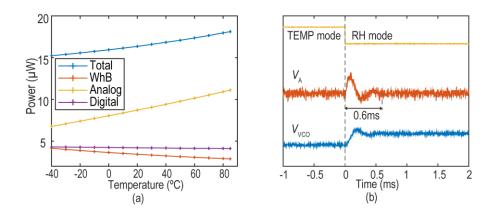

| Figure 5.12. Measured (a) power vs. temperature, and (b) waveforms during mode switching. 128        |

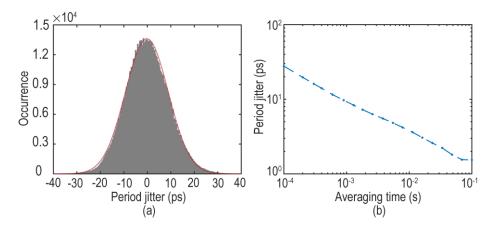

| Figure 5.13. Measured (a) FLL jitter histogram with 1 ms averaging, and (b) jitter vs. averaging     |

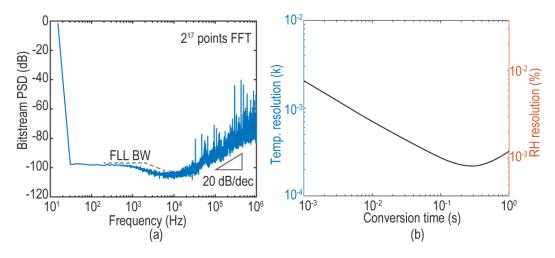

| time                                                                                                 |

| Figure 5.14. Measured (a) resolutions vs. $T_{conv}$ , and (b) TDC PSD                               |

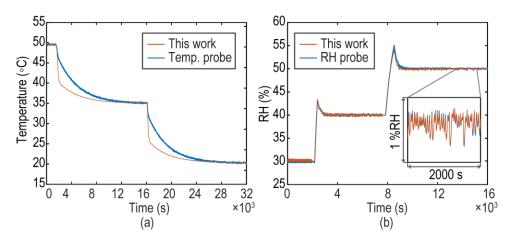

| Figure 5.15. Measured step response when (a) temp. changed and (b) RH changed 129                    |

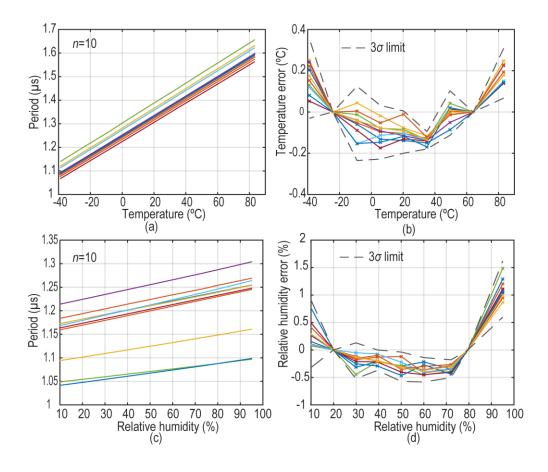

| Figure 5.16. Measured (a) temperature transfer curve, (b) temperature error, (c) RH transfer         |

| curve, and (d) RH error                                                                              |

## LIST OF TABLES

| Table 2.1. WuRX sensitivity breakdown                                          | 17    |

|--------------------------------------------------------------------------------|-------|

| Table 2.2. Comparison with State-of-the-Art WuRX prior 2017                    | 46    |

| Table 3.1. Comparison to state-of-the-art WuRXs                                | 72    |

| Table 4.1. Performance comparison of low power kHz-range integrated oscillator | 97    |

| Table 5.1. Performance comparison of environmental sensors                     | . 130 |

#### **ACKNOWLEDGEMENTS**

Over this past five years I have received support and encouragement from a great number of individuals. I would first like to acknowledge my advisor, Professor Drew Hall, for seeing my potential and accepting me into his research group at a time when I knew little about solid-state circuits. It is with his invaluable mentorship and guidance as well as his excellent insight into circuit design that I was able to accomplish the achievements presented in this dissertation. I would also like to thank all other principal investigators of the DARPA N-ZERO project, Professor Gabriel Rebeiz, Professor Patrick Mercier, and Professor Young-Han Kim, for their devotion and involvement into almost every step of my research. Together with them, I would like to thank Professor Gert Cauwenbergs, who also serves as my committee member, for the valuable input and feedback.

I also owe many thanks to my partners in the DARPA N-ZERO project, especially Li Gao, Po-Han Wang, and Pinar Sen, who have been working with me closely for the past four years. You are truly the most hardworking and relentless working mates that I have ever interacted with. I am proud for working with you and making the breakthrough into the N-ZERO wake-up receivers.

Next, I would also like to thank my fellow colleagues, who worked with me in the windowless room for years, for their help, advice, and friendship. I would like to acknowledge Edwin Hsu and Xiahan Zhou for being great sources of knowledge especially at the rough beginning of this journal. I would also like to thank Iric Huang, Da Ying, Somok Mandal, and Alex Sun for their great friendship and immense assistance. I would also like to express my gratitude to BioEE alumni and junior students, Venkatesh Alagarswamy, Rajesh Seenivasan, Tom

Phelps, Tianlei Sun, Saurabh Kulkarni, Corentin Pochet, Omid Ghadami, Michael Sveiven, Enhan Mak, Matthew Chan, and Aditi Jain for their help and support.

I would like to thank all my friends, who work from all kinds of disciplinaries, including electrical engineering, structure engineering, mechanical and aerospace engineering, bioengineering, and mathematics department for making my time here so enjoyable and memorable.

Last, but definitely not least, I would like to thank my family, my extended family, and my girlfriend for their never-ending support, encouragement, and understanding as well as for keeping me sane and laughing during the most stressful times. Most importantly, I would like to thank my mother, Hua, for her selfless love and the guidance for being a Ph.D. and a professor herself. This dissertation is dedicated to my family, a minor token of my immense gratitude.

Since portions of this dissertation have been published previously as a result of several collaborations, I must again acknowledge each of the authors for their tremendous contributions.

Chapter 2, in part, is based on materials from Haowei Jiang, Po-Han Peter Wang, Li Gao, Pinar Sen, Young-Han Kim, Gabriel M. Rebeiz, Drew A. Hall, Patrick P. Mercier, "A 4.5nW wake-up radio with –69dBm sensitivity," in *IEEE International Solid-State Circuits Conference*, San Francisco, CA, 2017, and Po-Han Peter Wang, Haowei Jiang, Li Gao, Pinar Sen, Young-Han Kim, Gabriel M. Rebeiz, Patrick P. Mercier, Drew A. Hall, "A Near-Zero-Power Wake-Up Receiver Achieving –69-dBm Sensitivity," in *IEEE Journal of Solid-State Circuits*. June 2018. The dissertation author was the primary investigator and author of these papers.

Chapter 3, in part, is a revision of the material as it appears in Haowei Jiang, Po-Han Peter Wang, Li Gao, Corentin Pochet, Gabriel M. Rebeiz, Drew A. Hall, Patrick P. Mercier, "A 22.3

nW, 4.55 cm<sup>2</sup> Temperature-Robust Wake-up Receiver Achieving a Sensitivity of -69.5 dBm at 9 GHz," in *IEEE Journal of Solid-State Circuits*, and Po-Han Peter Wang, Haowei Jiang, Li Gao, Pinar Sen, Young-Han Kim, Gabriel M. Rebeiz, Patrick P. Mercier, Drew A. Hall, "A 6.1-nW Wake-Up Receiver Achieving –80.5-dBm Sensitivity Via a Passive Pseudo-Balun Envelope Detector," in *IEEE Solid-State Circuits Letters*, May 2018. The dissertation author was the primary

investigator and author of these papers.

Chapter 4, in part, is based on materials presented in Haowei Jiang, Po-Han Peter Wang, Patrick P. Mercier and Drew A. Hall, "A 0.4-V 0.93-nW/kHz Relaxation Oscillator Exploiting Comparator Temperature-Dependent Delay to Achieve 94-ppm/°C Stability," in *IEEE Journal of Solid-State Circuits*, Oct. 2018, and Haowei Jiang, Po-Han Peter Wang, Li Gao, Corentin Pochet, Gabriel M. Rebeiz, Drew A. Hall, Patrick P. Mercier, "A 22.3 nW, 4.55 cm² Temperature-Robust Wake-up Receiver Achieving a Sensitivity of -69.5 dBm at 9 GHz," in *IEEE Journal of Solid-State Circuits*. The dissertation author was the primary investigator and author of these papers.

Chapter 5, in part, contains materials from Haowei Jiang, Chih-Cheng Huang, Matthew Chan and Drew A. Hall, "A 2-in-1 Temperature and Humidity Sensor Achieving 62 fJ·K<sup>2</sup> and 0.83 pJ·(%RH)<sup>2</sup>," in *IEEE Custom Integrated Circuits Conference*, Austin, TX, USA, 2019, and its journal version that has been submitted for publication. The dissertation author was the primary investigator and author of these papers.

Haowei Jiang

La Jolla, CA

September 2019

#### VITA

#### **EDUCATION**

| 2014 | Bachelor of Engineering in Electrical Engineering and Automation,<br>Huazhong University of Science and Technology, Wuhan, China       |

|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 2016 | Master of Science in Electrical Engineering<br>(Electronic Circuits and Systems),<br>University of California San Diego, La Jolla, USA |

| 2019 | Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems), University of California San Diego, La Jolla, USA    |

#### **PUBLICATIONS**

- **H. Jiang**, P. H. Wang, L. Gao, C. Pochet, G. M. Rebeiz, D. A. Hall, P. P. Mercier, "A 22.3 nW, 4.55 cm<sup>2</sup> Temperature-Robust Wake-up Receiver Achieving a Sensitivity of -69.5 dBm at 9 GHz," *Journal of Solid-State Circuits (JSSC)*, In Press.

- **H. Jiang**, C. Huang, M. Chan and D. A. Hall, "A 2-in-1 Temperature and Humidity Sensor," *Journal of Solid-State Circuits (JSSC)*, Submitted.

- **H. Jiang**, C. Huang, M. Chan and D. A. Hall, "A 2-in-1 Temperature and Humidity Sensor Achieving 62 fJ·K<sup>2</sup> and 0.83 pJ·(%RH)<sup>2</sup>," 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 2019.

- P. P. Wang, **H. Jiang**, L. Gao, P. Sen, Y. Kim, G. M. Rebeiz, P. P. Mercier, D. A. Hall, "A 6.1-nW Wake-Up Receiver Achieving –80.5-dBm Sensitivity Via a Passive Pseudo-Balun Envelope Detector," in *IEEE Solid-State Circuits Letters*, vol. 1, no. 5, pp. 134-137, May 2018

- **H. Jiang**, P. P. Wang, P. P. Mercier and D. A. Hall, "A 0.4-V 0.93-nW/kHz Relaxation Oscillator Exploiting Comparator Temperature-Dependent Delay to Achieve 94-ppm/°C Stability," in *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 53, no. 10, pp. 3004-3011, Oct. 2018.

- **H. Jiang**, X. Zhou, S. Kulkarni, M. Uranian, R. Seenivasan and D. A. Hall, "A Sub-1 μW multiparameter injectable BioMote for continuous alcohol monitoring," *2018 IEEE Custom Integrated Circuits Conference (CICC)*, San Diego, CA, 2018.

- P. P. Wang, **H. Jiang**, L. Gao, P. Sen, Y. Kim, G. M. Rebeiz, P. P. Mercier, D. A. Hall, "A Near-Zero-Power Wake-Up Receiver Achieving –69-dBm Sensitivity," in *IEEE Journal of Solid-State Circuits*, vol. 53, no. 6, pp. 1640-1652, June 2018.

- P. P. Wang, **H. Jiang**, L. Gao, P. Sen, Y. Kim, G. M. Rebeiz, P. P. Mercier, D. A. Hall, "A 400 MHz 4.5 nW –63.8 dBm sensitivity wake-up receiver employing an active pseudo-balun envelope detector," *IEEE European Solid State Circuits Conference (ESSCIRC)*, Leuven, 2017.

- T. Phelps, **H. Jiang** and D. A. Hall, "Development of a smartphone-based pulse oximeter with adaptive SNR/power balancing," *IEEE Engineering in Medicine and Biology Society (EMBC)*, Seogwipo, 2017.

- **H. Jiang**, P. H. Wang, L. Gao, P. Sen, Y. Kim, G. M. Rebeiz, D. A. Hall, P. P. Mercier, "A 4.5nW wake-up radio with –69dBm sensitivity," *2017 IEEE International Solid-State Circuits Conference (ISSCC)*, San Francisco, CA, 2017.

- **H. Jiang**, A. C. Sun, A. G. Venkatesh, and D. A. Hall, "An Audio Jack-Based Electrochemical Impedance Spectroscopy Sensor for Point-of-Care Diagnostics," *IEEE Sensors Journal*, vol. 17, no. 3, pp. 589–597, Feb. 2017.

- C. Hsu, **H. Jiang**, A. G. Venkatesh and D. A. Hall, "A Hybrid Semi-Digital Transimpedance Amplifier With Noise Cancellation Technique for Nanopore-Based DNA Sequencing," in *IEEE Transactions on Biomedical Circuits and Systems*, vol. 9, no. 5, pp. 652-661, Oct. 2015.

C. Hsu, A. G. Venkatesh, **H. Jiang** and D. A. Hall, "A hybrid semi-digital transimpedance amplifier for nanopore-based DNA sequencing," *IEEE Biomedical Circuits and Systems Conference (BioCAS) Proceedings*, Lausanne, 2014.

### **PATENTS**

P. P. Wang, **H. Jiang**, D. A. Hall, P. P. Mercier. "Low Power Wake-up Receiver," United Stated Patent 16194676, May 2019.

#### FIELDS OF STUDY

Major Field: Electrical Engineering

Studied in Electronic Circuits and Systems Professor Drew A. Hall

#### ABSTRACT OF THE DISSERTATION

#### **Ultra-Low-Power Sensors and Receivers for IoT Applications**

by

#### Haowei Jiang

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2019

Professor Drew A. Hall, Chair

The combination of ultra-low power analog front-ends and CMOS-compatible transducers enable new applications, such as environmental monitors, household appliances, health trackers, etc. that are seamlessly integrated into our daily lives. Furthermore, wireless connectivity allows many of these sensors to operate both independently and collectively. These techniques collectively fulfil the recent surge of internet-of-things (IoT) applications that have the potential to fundamentally change daily life for millions of people.

In this dissertation, the circuit and system design of wireless receivers and sensors is presented that explores the challenges of implementing long lifespan, high accuracy, and large coverage range IoT sensor networks. The first is a wake-up receiver (WuRX), which continuously monitors the RF environment to wake up a higher-power radio upon detection of a predetermined RF signature. This work both improves sensitivity and reduces power over prior art through a multi-faceted design featuring an impedance transformation network with large passive voltage gain, an active envelope detector with high input impedance to facilitate large passive voltage gain, a low-power precision comparator, and a low-leakage digital baseband correlator.

Although pushing the prior WuRX performance boundary by orders of magnitude, the first work shows moderate sensitivity, inferior temperature robustness, and large area with external lumped components. Thus, the second work shows a miniaturized WuRX that is temperature-compensated, yet still consumes only nano-watt power and millimeter area while operating at 9 GHz. To further reduce the area, a global common-mode feedback is utilized across the envelope detector and baseband amplifier that eliminates the need for off-chip ac-coupling components. Multiple temperature-compensation techniques are proposed to maintain constant bandwidth of the signal path and constant clock frequency. Both WuRXs operate at 0.4 V supply, consume near-zero power and achieve ~~70 dBm sensitivity.

Lastly, the first reported CMOS 2-in-1 relative humidity and temperature sensor is presented. A unified analog front-end interfaces on-chip transducers and converts the inputs into a frequency vis a high-linearity frequency-locked loop. An incomplete-settling switched-capacitor-based Wheatstone bridge is proposed to sense the inputs in a power-efficient fashion.

# Chapter 1

### Introduction

### 1.1 Motivation for Internet-of-Things Sensors

The combination of ultra-low power analog front-ends (AFEs) and CMOS-compatible transducers enable new applications, such as environmental monitors, household appliances, health trackers, etc. that are seamlessly integrated into our daily lives. Furthermore, wireless connectivity allows many of these sensors to operate both independently and collectively. These techniques collectively fulfil the recent surge of internet-of-things (IoT) applications that have the potential to fundamentally change daily life for millions of people.

The Internet-of-Things helps people live and work smarter as well as gain complete control over their lives. There are numerous real-world applications of the internet of things, ranging from consumer and enterprise to manufacturing and industrial [1]. In the consumer segment, for example, smart homes that are equipped with smart thermostats, smart appliances and connected

heating, lighting and electronic devices can be controlled remotely [2]. Wearable devices can collect, analyze and sending data to smartphones with the aim of making users' lives easier and more comfortable. In healthcare, IoT offers many benefits, including the ability to shift the centralized biomedical examinations towards the point-of-care to monitor patients more closely [3]–[8]. In agriculture, IoT-based smart farming systems can help monitor, for instance, light, temperature, humidity and soil moisture of crop fields using connected sensors. In a smart city, IoT sensors and deployments, such as smart streetlights and smart meters, can help alleviate traffic, conserve energy, monitor and address environmental concerns and improve sanitation.

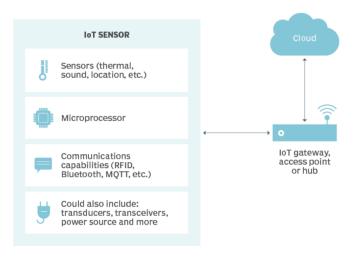

Wireless connectivity and sensing are the two cornerstone technologies to the IoT [9]. We are giving the world a digital nervous system: location data using GPS sensors; eyes and ears using cameras and microphones, along with sensory organs that can measure everything from temperature to acceleration depending on what the applications require. These inputs are digitized and placed onto networks: from wide area networks (WAN) to local area networks (LAN) and even personal area networks (PAN). Therefore, as shown in Figure 1.1, an IoT sensor is the kind of node equipped with certain types of sensors and has communication capability. With an expectation of rapidly increased IoT sensors [1], there is a surging demand of developing wireless communication circuits and sensing circuits that are oriented for IoT usage.

### An IoT sensor in action

Figure 1.1. Illustration of an IoT sensor from [1].

### 1.2 Event-Driven Communication Using Wake-up Receiver

There is a growing class of event-driven devices that require instant-on wireless connectivity, but only use the radio to communicate intermittently throughout their lifetime. For example, smart homes equipped with smart sensors and automatic appliances, only use or need their radios when prompted by an event. In these applications, the energy spent synchronizing the radios, or maintaining a connected state, dominates, as opposed to the energy spent communicating, sensing, and processing data [10], [11].

Because of the intermittent nature of event-driven communication, IoT radios spend much of their time in a sleep state, where the radios are not capable of sending or receiving packets, in an effort to conserve energy and reduce their average power consumption. This creates a challenge when two radios need to establish communication with each other. Both radios need to wake up and communicate at the same time, which requires the radios to be synchronized with one

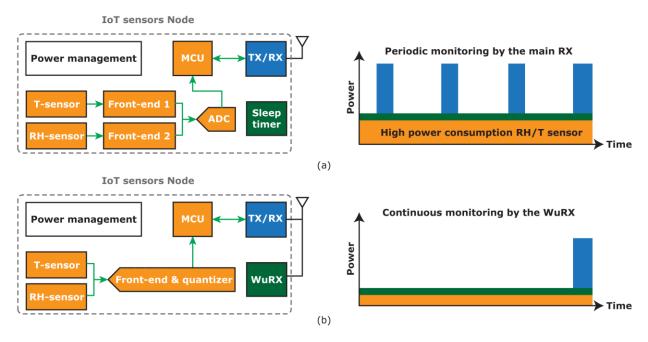

another. As shown in Figure 1.2(a), the conventional method to synchronize the IoT nodes is to periodically wake up their radios to check for wireless messages triggered by a random event. However, this doesn't solve the power problem of event-driven communication, since energy is wasted every time a radio wakes up to try and establish communication and it fails. Although the energy spent could be low by having a low duty cycle, it will inevitably increase the latency, which has a maximum value limited by the application. This tradeoff between power and latency is not ideal.

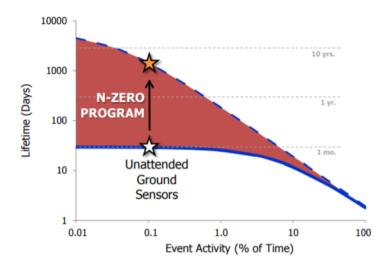

A wake-up radio (WuRX) can be used as a superior alternative to conventional method. The WuRX acts as a secondary receiver within an asynchronous protocol. While the other radios are conserving power in an ultra-low power sleep state, the WuRX continuously monitors the RF environment for events and enables the main communication radio when it detects another radio trying to communicate [Figure 1.2(b)]. Because the WuRX remains always-on, it must be ultra-low power, which is the main specification that drives WuRX design. This event-driven synchronization methodology is energy efficient because the high-power receiver remains off as long as possible and only wakes when communication is necessary. In sensor settings with low event activity, considerable extension (1 month  $\rightarrow$  10 years) of battery life can be achieved, as shown in Figure 1.3[12].

This is the motivation behind the Near-Zero Power (N-ZERO) program, which was founded by the US Defense Advanced Research Projects Agency (DARPA). This program aimed to develop a WuRX that consumes less than 10 nW power, corresponding to the self-discharge of a typical button cell battery sitting on a shelf unused [13]. The body of this dissertation's work is based on the outcome from the N-ZERO program.

Figure 1.2. Diagram of (a) periodic wake-up and (b) employing a WuRX.

Figure 1.3. N-ZERO circuit power saving as a function of event activity from [12].

### 1.3 Compound Sensor Using Unified Analog Front-End

One IoT node typically consists of a cluster of sensors, which detect similar physical or chemical parameters to provide a comprehensive assessment. By sharing the micro-processer unit and the radio, this approach is power- and cost-efficient. For example, an IoT node for surveillance purpose should be equipped with motion, vibration, and sound sensors; while a node for monitoring the food supply chain should be equipped with relative humidity and temperature (RH/Temp.) sensors.

A key challenge in this vision is to combine the sensors in a compact and power efficient manner as they utilize fundamentally different transduction mechanisms and therefore typically require different AFEs. Different mechanisms include voltage [14], current [15], [16], resistive [17], capacitive [18] and inductive [19] transduction. From the circuit perspective, a conventional way to integrate different sensing mechanisms is to convert multiple parameters into the voltage domain, and then use an analog-to-digital converter (ADC) to digitize them. As shown in Figure 1.2(a), this is commonly used architecture for the existing RH/Temp. environmental sensors [20], [21], which show inferior power efficiency and large area cost. Furthermore, the conventional architecture uses two-step data acquisition, *i.e.* an amplifier followed by an ADC, to repurpose the ADC in different modes. This architecture typically requires at least two high gain amplifiers, and hence higher power and complexity, and less gain accuracy [22].

To integrate more sensing mechanisms to a compound sensor more efficiently, this work demonstrates a unified AFE, which digitizes both resistive and capacitive information for RH/Temp. monitoring applications. As shown in Figure 1.2(b), both transducers interact with the AFE directly, and the AFE converts the inputs into a time information, which is then digitized by a built-in quantizer. By using this 2-in-1 approach, power, area, and circuit complexity can be improved significantly. Meanwhile, other design specifications such as linearity and process, voltage, and temperature (PVT) robustness have also been improved. Those specifications are crucial but oft overlooked in IoT applications, which typically are used under poorly regulated

power supply (from either batteries or power harvesters) and operate in uncontrolled environments (compared to a conventional laboratory setting).

### 1.4 Scope of Dissertation

This dissertation presents the development of the near-zero power WuRXs as well as the RH/Temp. sensor for environmental sensing. The WuRXs presented in this dissertation are categorized into two types: active ED based WuRX and passive ED based WuRX. Although being categorized by the ED types, the difference between them are more than the ED design. The active ED tends to have better driving ability and higher bandwidth, while inferior noise efficiency; on the contrary, the passive ED shows better noise efficiency, at the cost of no driving ability and ultra-high output impedance. Thus, the ED types also influence the BB circuit design, especially, the passive ED demands more stringent requirements on the BB circuits. In Chapter 2 and 3, the two generations of WuRXs, that evolve from the active ED based architecture to passive ED based architecture, are presented. Chapter 4 raises issues of temperature dependence in the WuRX and presents solutions to improve the temperature robustness. Chapter 5 covers the 2-in-1 RH/Temp sensor with a unified front-end that demonstrates state-of-the-art performance. Finally, Chapter 6 presents concluding remarks and future research directions.

# Chapter 2

# N-zero WuRXs with Active Envelope Detection

#### 2.1 Introduction

WuRXs are low-power radios that continuously monitor the RF environment to wake up a higher power radio upon detection of a pre-determined RF signature. Prior-art WuRXs have 100s of kHz of bandwidth with low signature-to-wake-up-signal latency to help synchronize communication amongst nominally asynchronous wireless devices [23], [24]. However, applications such as unattended ground sensors and smart home appliances wake-up infrequently in an event-driven manner, and thus WuRX bandwidth and latency are less critical; instead, the most important metrics are power consumption and sensitivity, as the power of always-on WuRXs ultimately determines the battery life of low-activity devices, while sensitivity determines the communication distance and therefore deployment cost via the total number of nodes required to achieve a given network coverage. Typically, sensitivity and power consumption trade-off with

one another, making the design of WuRXs that simultaneously achieve both challenging. Fortunately, the relaxed wake-up latency and data rate requirements of low-average-throughput applications can help improve both power consumption and sensitivity by minimizing baseband bandwidth, as will be shown shortly.

There are two primary classes of applications where WuRXs can be useful: 1) high-average-throughput applications, where WuRXs are used to eliminate the need for precision watch-dog timers used to perform network synchronization; and 2) low-average-throughput applications where the network is largely idle, waiting for an event to occur (e.g., infrastructure and perimeter monitoring). In high throughput applications it is important to minimize wake-up detection latency, set in part by the WuRX data rate, so as to not adversely affect the average network throughput. In low throughput applications, wake-up latency (and thus data rate), is less important, as long latency may not adversely affect the overall needed throughput. As an emerging research direction, this thesis focuses on the design of WuRXs used in low-average-throughput applications.

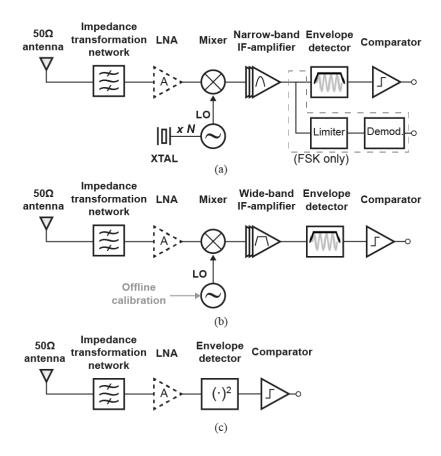

Figure 2.1. Wake-up radio architectures: (a) mixer-based low-IF, (b) mixer-based uncertain-IF, and (c) direct envelope detection.

### 2.2 Prior WuRX Architectures

Most low-power WuRXs demodulate non-coherent OOK or FSK using one of two general architectures illustrated in Fig. 2.1: a) mixer-based low-or b) uncertain-IF architectures, and c) direct envelope detection architectures.

#### 2.2.1 Low-or Uncertain-IF Architectures

Most conventional radio architectures utilize a LO, often stabilized via a low-frequency crystal by means of injection locking or a PLL, to mix the incoming RF signal down to a known IF prior to demodulation via an ED or other means [Figure 2.1(a)]. Since it is much more power-

efficient to amplify and filter signals at a low IF than at RF, mixer-first low-IF architectures, where an LNA is not included, can consume relatively low power while achieving good sensitivity. For example, achieve -70 dBm and -87 dBm at 200 kbps and 50kbps, respectively. However, even though OOK and FSK are demodulated in a non-coherent manner, the generated LO must be frequency-stable in order to limit bandwidth (and therefore noise) at IF; this requires ~10s of  $\mu$ W when operating between 400-900 MHz, and even more at 2.4 GHz. Thus [25], [26] each consume 44  $\mu$ W, which is higher than desired for many WuRX applications. For this reason, mixer-based low-IF architectures are typically reserved for WuRX applications operating below 1GHz, and/or where sensitivity is more important than power.

The power consumption of LO generation can be reduced substantially if the frequency stability specifications are relaxed. For example, by replacing a frequency-locked oscillator with a simple free-running digitally controlled ring oscillator, LO generation has consumed 13/20 µW at 2.0/2.45 GHz in prior work [23], [27], respectively. However, mixing an incoming RF waveform with a free-running oscillator whose precise frequency is not well controlled or known requires a large IF bandwidth to guarantee proper reception after envelope detection. Thus, such architectures are called "uncertain-IF" WuRXs. Since even far away interferers can potentially end up in the wideband IF, and these interferers would be demodulated to baseband via the ED, high-Q filtering at RF prior to down conversion is required. This can be accomplished using mechanical resonant structures (e.g., BAW or FBAR filters), or via N-path filters [28]. Generally, uncertain-IF WuRXs should achieve lower power operation than conventional low-IF WuRXs with similar, though typically slightly worse, sensitivity due to increased noise bandwidth. Recent work on multi-stage N-path filters have improved sensitivity via enhanced filtering, albeit at higher power (e.g., -97 dBm at 10 kbps and 99 µW). Thus, mixer-based uncertain-IF WuRXs are capable of

operating at lower power and higher frequencies than mixer-based low-IF WuRXs, with similar, though often slightly poorer, sensitivities.

#### 2.2.2 Direct Envelope Detection Architectures

Many applications such as unattended ground sensor networks, smart home automation, and wearables demand sub-μW power consumption to enable ultra-long battery life. Since LO generation and IF amplification dominate the power consumption of mixer-based architectures, an impactful way to reduce power is to eliminate mixers altogether and directly demodulate to baseband via an envelope detector [Figure 2.1(c)]. Envelope detection can be performed passively by a rectifier [29], or actively via an amplifier biased to maximize second-order non-linearities [24]. The latter approach typically exploits the non-linear exponential *V-I* relationship of a subthreshold MOSFET.

Nominally a passive rectifier offers poor conversion gain; however, multi-stage charge pumps can be employed to achieve similar conversion gain as low-power active EDs, though they suffer from low input impedances, making large passive RF voltage gain structures difficult to implement. However, since EDs demodulate all energy present at their inputs to baseband, such architectures tend to accumulate significant noise and interference, making their sensitivity generally inferior to mixer-based architectures.

### 2.3 Proposed WuRX Architecture

The architecture of the proposed WuRX is shown in Figure 2.2. The primary optimization objective of this design was to minimize power. This motivated the use of a direct-ED WuRX architecture operating at a low supply voltage (0.4 V in this work). However, the secondary objective was to achieve sensitivity that approaches that of a mixer-based WuRX architecture,

while not significantly compromising tolerance to interferers. This was accomplished through a number of architectural and circuit design techniques described below.

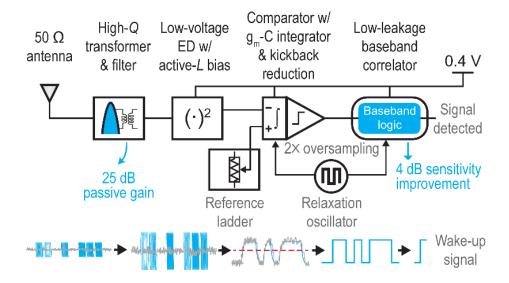

Figure 2.2. Overview of the proposed WuRX.

#### 2.3.1 Direct-ED RF Front-End Optimization

Direct ED architectures demodulate all input RF energy to baseband, and thus any interferers within the input RF bandwidth can inhibit proper reception. In addition, the lack of an LNA together with very low-power demodulating circuits means that the baseband circuit noise often dominates, thereby ultimately limiting the WuRX sensitivity. Fortunately, these two problems, *i.e.* interference and baseband circuit noise, can be overcome via the following techniques:

#### 1) Minimizing the influence of interference via high-Q filtering:

To reduce the impact of in-band blockers in direct-ED or uncertain-IF mixer-based architectures, a high-Q narrow-band filter is needed to minimize RF bandwidth and block

interferers. Most prior-art low-power radios accomplish narrow-band filtering by utilizing high-Q mechanical resonators, which offer attractive narrow filtering capabilities at 1-3 GHz [23]. In this design, however, to attain the highest possible Q for sharp filtering, and, as will be seen shortly, to achieve a large impedance transformation ratio from a 50  $\Omega$  source as well as wide communication range, a carrier frequency in the 100 MHz range was selected for use near the FM radio band. Therefore, a high-Q filter (and, as will be described shortly, transformer) was designed out of lumped components directly.

#### 2) Minimizing baseband circuit noise via passive RF voltage amplification:

Envelope detectors are inherently non-linear elements. Unlike linear mixers used for down-conversion, the squaring operation of an ED converts pre-ED noise down to baseband via two mechanisms: self-mixing of noise and noise convolved with the input signal [30]. Since most ultra-low-power WuRXs forgo active gain before the ED, sensitivity is typically limited by baseband noise. Therefore, to improve sensitivity without a power penalty, most direct-ED WuRX designs strive to achieve as much passive voltage gain in the matching network as possible. This is typically achieved by designing the ED to have a large input impedance and matching this large impedance to  $50~\Omega$  via an impedance transformation network. Prior work has shown 5 dB and 12 dB of passive voltage gain which, when coupled to either a rectifier or an active ED, achieved sensitivities of -45.5 dBm and -41 dBm at 12.5 kbps and 100 kbps at powers of 116 nW and 98 nW, respectively [24], [29]. Thus, direct ED systems can achieve ultra-low-power operation, yet without large RF voltage gain and low-noise baseband circuits, do so at limited sensitivities.

To address the aforementioned issues, the proposed WuRX incorporates an ED with a high input impedance that, combined with a high-Q impedance transformer, facilitates up to 25 dB of passive voltage gain at RF before being demodulated by the ED, thus directly resulting in a 25 dB

improvement in sensitivity compared to the exclusion of this transformer. Furthermore, the ED is designed to support high conversion gain to further reduce the impact of baseband circuit noise (*i.e.* to increase SNR).

#### 2.3.2 Baseband Bandwidth Consideration

In high throughput applications it is important to minimize wake-up detection latency, set in part by the WuRX data rate, so as to not adversely affect the average network throughput. In low throughput applications, wake-up latency (and thus the data rate of the WuRX), is less important, as long latency does not adversely affect the overall throughput needed. Most conventional WuRX designs target the first class of applications; this work instead focuses on the design of WuRXs used in low-average-throughput LPWAN applications. One of the key ideas of a LPWAN is to leverage the reduced data rate (and thus integrated baseband noise) to improve sensitivity and enable wide communication range. For example, LoRaWAN utilizes a 300 bps to 50 kbps data rate, whereas Sigfox is only 100 bps to 600 bps. Therefore, a 300 bps data rate was selected for this design.

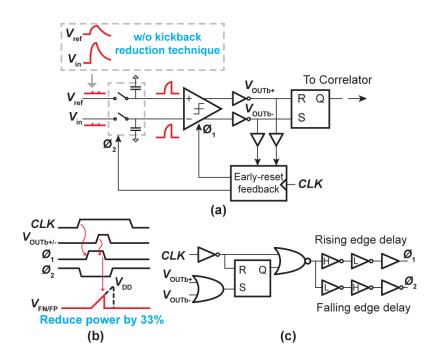

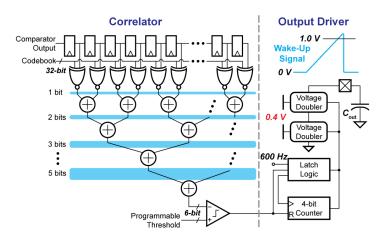

#### 2.3.3 Digital Baseband Processing

The received RF signal employed in this design is modulated with a custom designed 16-bit sequence. After envelope detection in the proposed architecture, the demodulated signal is  $2\times$  oversampled and digitized by a 1-bit regenerative comparator. The output of the comparator feeds a digital correlator that computes the Hamming distance between the received and stored sequence. When the Hamming distance is below a programmable threshold ( $H_{th}$ ), a wake-up signal is generated. It will be shown later that the use of this wake-up sequence provides additional coding gain that improves the sensitivity of the proposed WuRX. Moreover, the correlator prevents false

alarms caused by unwanted jammers. An on-chip relaxation oscillator provides the required 600 Hz clock.

# 2.4 System Analysis & Modelling

#### 2.4.1 Sensitivity Analysis

Due to the inherent nonlinearity of the direct-ED method, it is difficult and inconvenient to analyze the receiver sensitivity with a conventional noise figure (NF) based approach, which refers the all the noise to the RF input, with respect to the ambient thermal noise (*i.e.* -174 dBm/Hz at room temperature). A more convenient approach, as shown in [30], is referring both noise and signal to the baseband at voltage domain and computing the signal-to-noise ratio (SNR). Generally, there are four steps in calculating the sensitivity:

- 1) Computing the signal amplitude after the ED, using parameters such as the RF front-end voltage gain,  $A_V$ , and the ED scaling factor, k.

- Computing the BB referred RF noise,  $\sigma_{n,RF}$ , including the ambient thermal noise floor and RF amplifier (optional) noise. Due to the nonlinear operating, those noise sources mix with either themselves or the signal. Thus, the RF noise shown in the BB is signal dependent if the signal is large or the RF bandwidth is narrow. The method to compute the BB referred RF noise is elaborated in [30].

- Computing the BB noise,  $\sigma_{n,BB}$ , which includes the output referred ED noise and the input referred BB amplifier/comparator noise. Note, it is relatively easy to compute/simulate the ED output noise with its small-signal BB model by ignoring all the nonlinear effects [31].

Computing the sensitivity by comparing the SNR versus the minimum required SNR,  $SNR_{mim}$ , which is determined by the coding. If no coding is used,  $SNR_{mim}$  is 11 dB for a biterror rate (BER) of  $10^{-3}$ .

In the direct-ED method in this work, *i.e.* high-Q RF filtering and no active RF amplification, it is most likely always true that the BB noise is dominating. Thus, the step (2) shown above can be skipped for simplicity. The simplified direct-ED WuRX sensitivity is

$$P_{\text{sen}} = \frac{\sqrt{SNR_{\min} \times \sum \sigma_{n,BB}^2}}{50kA_V^2},$$

2.1

whose unit is in milliwatt (mW). This equation works as a guidance to all WuRX design: higher RF gain, higher conversion gain, lower BB noise, and a longer code lead to better sensitivity collectively.

The noise and sensitivity breakdown of this work is shown in Table 2.1. It can be observed that the RF noise has nearly no effect on the overall sensitivity, while the BB referred ED noise dominates the noise, followed by the comparator.

Table 2.1. WuRX sensitivity breakdown

| Noise @ Comparator  | Sensitivity Limitation by |

|---------------------|---------------------------|

| Input Node          | Noise Source @ BER=10-3   |

| Signal ⊗ RF Noise   | -126.7dBm                 |

| Self-Mixed RF Noise | -122.1dBm                 |

| ED Noise            | -67.3dBm                  |

| Comparator Noise    | -69.2dBm                  |

| Ref. Ladder Noise   | -75.2dBm                  |

| Total Noise         | -66.5dBm                  |

| Measurement Result  | -65.0dBm                  |

#### 2.4.2 Simulink Behavior Model

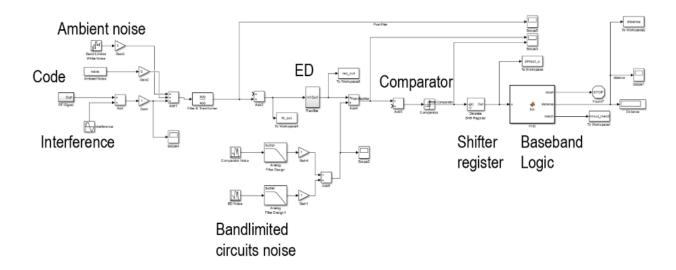

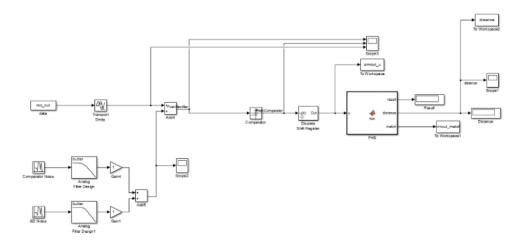

To model the WuRX system behavior, a Simulink model was established (Figure 2.3). Signal sequence, ambient thermal noise and interference serve as the model inputs. The ED is modeled by a square function, followed by a  $1^{st}$  order low-pass filter. The BB noise is modelled as bandlimited white noise. A fast version was also built by using a stored rectified signal sequence as the input (Figure 2.4). Since RF noise is negligible, by removing the RF and conversion operations, only modelling the BB behavior, the simulation speeds up by  $\sim 10^6 \times$ . With the fast version, Monte Carlo simulation was applied to the system for a large run numbers (>10<sup>4</sup>) to obtain the statistics of missed detection and false alarms.

This model validates some the sensitivity analysis shown above and the codeword effectiveness. It also helps to choose an appropriate sampling rate, *i.e.* 2× the data rate, which is a tradeoff between power and possibility of missing bits. Some nonidealities (difficult for analytical analysis), such as asynchronous operating, clock drift, and comparator threshold voltage drift have been applied to this model.

Figure 2.3. WuRX Simulink model.

Figure 2.4. WuRX BB Simulink model.

# 2.5 Circuits Implementation

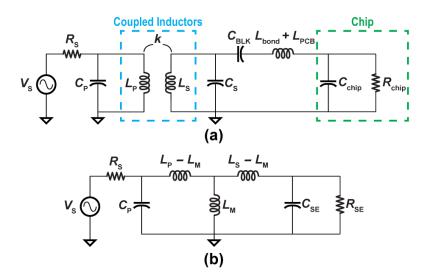

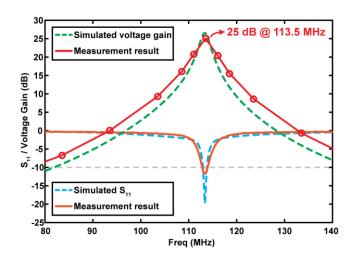

#### 2.5.1 Transformer/Filter

The purposes of the transformer/filter is to impedance transform a 50  $\Omega$  source impedance to a much larger value to facilitate passive voltage gain, while also performing high-Q RF filtering. The schematic of the implemented transformer/filter is shown in Figure 2.5(a) were  $R_s$  is the 50  $\Omega$  source impedance. The primary stage resonator is formed by  $L_P$  and  $C_P$ , while the secondary stage is formed by  $L_S$  and  $C_S$ , with k denoting the coupling coefficient between  $L_P$  and  $L_S$ .  $C_{\text{chip}}$  and  $R_{\text{chip}}$  are the equivalent input impedance of the chip at the carrier frequency, which connects to the transformer/filter via a large ac-coupling capacitor,  $C_{\text{BLK}}$ , and a small parasitic inductor from the PCB trace and bondwire. The primary and secondary stage tanks both resonate at the same operating frequency,  $f_{\text{RF}}$ =113.5 MHz. Departing from a traditional 2-port RF filter, which has 50  $\Omega$  matching at both ports, the proposed transformer/filter not only provides a  $2^{\text{nd}}$  order filter response for interference rejection, but also realizes impedance transformation between the two

ports to achieve passive voltage gain. To analyze the circuit, an equivalent circuit model is derived as shown in Figure 2.5(b).  $L_{\rm M}$  is determined by k and can be written as:

$$L_{\rm M} = k\sqrt{L_{\rm P}L_{\rm S}} = kL_{\rm S}\sqrt{\frac{1}{N}},$$

2.2

where N is the turn ratio between  $L_P$  and  $L_S$ .  $C_{SE}$  and  $R_{SE}$  are the equivalent capacitor and resistor of the secondary stage, with  $C_{SE}=C_S+C_{\text{chip}}$  and  $R_{SE}=R_{EQ,P}||R_{\text{chip}}$ , where  $R_{EQ,P}$  is due to the finite Q of  $L_S$ . Therefore, the maximum passive voltage gain the transformer/filter can achieve at  $f_{RF}$  is:

$$Gain_{\text{max}} = \sqrt{\frac{R_{\text{SE}}}{R_{\text{S}}}} = \sqrt{\frac{R_{\text{EQ,P}} \| R_{\text{chip}}}{R_{\text{S}}}}.$$

To get large passive voltage gain, a large  $R_{\rm EQ,P}$  must be achieved by either increasing Q or  $L_{\rm S}$  for a given  $C_{\rm SE}$ . Since Q can only be pushed so high using practical inductors,  $L_{\rm S}$  is the only practical tunable parameter. There are two things that limit the achievable value of  $L_{\rm S}$ : 1) the chip input capacitance,  $C_{\rm chip}$ , and 2) the self-resonant frequency of the inductor. With  $C_{\rm S}$ =0 and  $C_{\rm chip}$ =1.8 pF, the maximum  $L_{\rm S}$  is 1.06  $\mu$ H. Due to the size of the required inductor, it must be off-chip. For commercial inductors with high Q, self-resonance typically occurs when  $\omega L\approx$ 1,400  $\Omega$ . To account for variation in  $C_{\rm chip}$  and on-board parasitics,  $\omega L\approx$ 520  $\Omega$  was chosen. From the datasheet [32], a Q of 150 can be obtained at 115 MHz, and thus  $R_{\rm EQ,P}<$ 78 k $\Omega$ .

Figure 2.5. Schematic of (a) transformer/filter and (b) equivalent circuit model.

Figure 2.6. Plot of (a)  $S_{11}$  vs. k; (b) voltage gain vs. k; (c)  $S_{11}$  vs. N; (d) voltage gain vs. N.

After determining the value of  $L_S$  and  $C_S$ , we considered the coupling coefficient k and the turn ratio N, both of which affect the input matching and passive voltage gain. To have a sharper

filter response for out-of-band interference rejection, k should be small and Q should be large [33]. Figure 2.6(a) and (b) show calculated  $S_{11}$  and voltage gain of the transformer/filter varying k with N fixed to be 30. When k is increased from 0.02 to 0.06, the input matching gets better and the voltage gain increases. However, the filter bandwidth also increases. Figure 2.6(c) and (d) show calculated  $S_{11}$  and voltage gain varying N with k=0.05. When N is increased from 20 to 60, the voltage gain does not increase much, but with considerably larger filter bandwidth. Therefore, k=0.05 and N=30 were chosen as a compromise between input matching, voltage gain, and filter bandwidth. Calculations show that  $S_{11}$  is better than -10 dB with a passive voltage gain of 28.9 dB and a 3-dB bandwidth of 2.4 MHz.

The key challenge in implementing the proposed transformer/filter is to control the coupling despite the large difference in inductance (720 nH and 24 nH). Implementing the inductors using only lumped elements would make it very hard to control the coupling through positioning, whereas only distributed inductors would take too much area. As such, we used a combination of lumped inductors (220 nH and 160 nH from Coilcraft) and a distributed inductor to realize  $L_{\rm S}$  and a distributed inductor to realize  $L_{\rm P}$ , which has three advantages. First,  $L_{\rm S}$  is realized by both distributed and lumped inductors, thus the value can be large. Second, the coupling is realized by the distributed parts of  $L_{\rm P}$  and  $L_{\rm S}$ , and thus k is determined by the length and gap of the coupling PCB traces. With modern PCB fabrication techniques, this coupling can be controlled precisely, which is crucial since k affects both passive gain and filter bandwidth. Third, the use of both lumped and distributed inductors provides more freedom to design the transformer. For example, the center frequency can be easily tuned by replacing lumped components, which is an advantage compared to mechanical resonators [23], [34].

Figure 2.7 shows the 3-D model of the transformer/filter. To reduce the dielectric loss, a Rogers RO4003C substrate was used ( $\varepsilon_r$ = 3.55, thickness of 20 mil, and a loss tangent of 0.0027). From HFSS simulations, we found that at 115 MHz,  $L_P$  and  $L_S$  are 28 nH and 756 nH, respectively, and k= 0.05. All of the component values are close to the desired values from calculation. The simulated voltage gain was 26.6 dB with a bandwidth of 2.2 MHz.

Figure 2.7. 3-D model of the transformer/filter.

#### 2.5.2 Envelope Detector

To take full advantage of the gain provided by the transformer/filter, the ED must provide a large enough input resistance  $R_{\text{chip}}$  so as to not to degrade the corresponding  $R_{\text{EQ,P}}$ . Although a passive N-stage RF rectifier [24], [29] is a tempting choice (due to the zero power consumption), it is difficult to achieve high enough  $R_{\text{chip}}$ . Thus, in this work an active ED was selected. A transistor biased in the sub- $V_{\text{t}}$  region can not only operate with a low supply voltage and low power consumption, but also provides an exponential voltage-current relationship. Assuming the transistor is operating in the sub- $V_{\text{t}}$  saturation region (*i.e.*  $V_{\text{DS}}$ >100 mV) with negligible drain-induced barrier lowering (DIBL), the current can be written as [35]:

$$i_{\rm DS} = \mu C_{\rm ox} \frac{W}{L} (n-1) V_{\rm T}^2 e^{\frac{v_{\rm GS} - V_{\rm t}}{n V_{\rm T}}},$$

2.4

where  $\mu$  is the mobility,  $C_{ox}$  is the oxide capacitance, W is the transistor width, L is the transistor length, n is the sub- $V_t$  slope factor,  $V_T$  is the thermal voltage  $(k_BT/q)$ , and  $v_{GS}$  is the gate-to-source voltage. This exponential relationship results in a  $2^{nd}$  order non-linearity used for the desired ED functionality.

The second order transconductance is given by:

$$g_{\rm m2} = \frac{1}{2} \cdot \frac{\partial^2 i_{\rm DS}}{\partial v_{\rm GS}^2} = \frac{I_{\rm DS}}{2(nV_{\rm T})^2}.$$

2.5

In an SOI process, the floating body can be connected to the gate directly without using deep n-well devices, commonly referred to as the DTMOS configuration [36], to achieve additional 2<sup>nd</sup> order non-linearity via threshold voltage modulation. The additional transconductance can be derived as:

$$g_{\text{mb2}} = \frac{1}{2} \cdot \frac{\partial^2 i_{\text{DS}}}{\partial v_{\text{BS}}^2} = (n-1)^2 g_{\text{m2}}.$$

2.6

For the process used in sub- $V_t$ , n $\approx$ 1.4, meaning that the DTMOS configuration provides an additional 16% transconductance compared to gate input only.

Conventional common source ED biasing schemes use either a diode-connected load or a resistive load. Unfortunately, the diode connected load results in a low output resistance (similar to a source follower ED) and only achieves high conversion gain with large input signals, while a resistive load has limited conversion gain with a 0.4 V supply voltage. Other techniques such as a cascode level shifter provide high output resistance, but require extra voltage headroom [24] not compatible with the employed 0.4 V supply.

Figure 2.8. (a) Schematic of proposed active-L biased ED; (b) active-L biasing circuit model and Bode plot of ED output impedance.

To address the aforementioned issues, an active-L self-biased ED was designed [Figure 2.8(a)]. The feedback resistor sets the DC voltage for both the gate and drain nodes of the input transistor and serves as the output impedance. The output impedance can be written as:

$$Z_{\text{out}} = \left(\frac{g_{\text{m1}} + sC_{\text{BLK}}}{1 + sC_{\text{BLK}}R_{\text{FB}}} + \frac{1}{r_{\text{o}}} + sC_{\text{L}}\right)^{-1},$$

2.7

where  $g_{\rm m1}$  is the transconductance of the NMOS,  $C_{\rm BLK}$  is the AC-coupling capacitor,  $R_{\rm FB}$  is the feedback resistor,  $r_{\rm o}$  is the small-signal intrinsic output resistance of the transistor, and  $C_{\rm L}$  is the capacitance at the output node. Assuming  $r_{\rm o}\gg 1/g_{\rm m1}$  and  $R_{\rm FB}$  because of the low current (5 nA in this design, which results in  $r_{\rm o}\approx 1$  G $\Omega$  and  $1/g_{\rm m1}\approx 7$  M $\Omega$ ),  $C_{\rm BLK}\gg C_{\rm L}$ , and  $C_{\rm BLK}/g_{\rm m1}\gg C_{\rm L}R_{\rm FB}$ , thus it can be simplified to:

$$Z_{\text{out}} \simeq \frac{1}{g_{\text{m1}}} \cdot \frac{1 + sC_{\text{BLK}}R_{\text{FB}}}{\left(1 + s\frac{C_{\text{BLK}}}{g_{\text{m1}}}\right)\left(1 + sC_{\text{L}}R_{\text{FB}}\right)},$$

$$2.8$$

which contains two poles and one zero. The equivalent circuit model and Bode plot of  $Z_{\rm out}$  are shown in Figure 2.8(b). It can be seen that the output impedance is boosted to  $R_{\rm FB}$  within the signal passband due to the active-L biasing, which leads to higher conversion gain. Since non-return-to-zero (NRZ) signaling is used, the high pass corner must be low enough to not attenuate the signal power and is set to 20 mHz in this design for < 0.01 dB SNR degradation from baseline wander. Therefore, an off-chip  $C_{\rm BLK}$  was used as a DC block and incorporated into the bias network.

Figure 2.9. Full schematic of the proposed low-voltage active-L biased DTMOS ED with boosted binary-weighted SPI control.

The full ED schematic is shown in Figure 2.9. Due to significant process variation in sub- $V_t$  circuits, both  $M_N$  and  $M_P$  were designed to have 8-bit binary-weighted tuning capability. To reduce the leakage of unused  $M_N$  via super-cutoff biasing, and to turn on  $M_P$  strongly, a voltage doubler [37] was designed to provide -0.4 V, saving up to 3 nA in simulation (at the TT corner). Because of the high required value of the feedback resistor, a MOS-bipolar-pseudo-resistor was used instead of a poly resistor to prevent high capacitive loading of the input node at RF, which

ultimately limits the achievable inductor value of the second stage of transformer/filter, and therefore passive voltage gain. For the same reasons as above, and to make the baseband bandwidth tunable, the pseudo-resistor was implemented with 5 binary-weighted bits. Since the baseband bandwidth is 300 Hz, all critical transistors were sized to trade-off the contributions of 1/f noise while minimizing parasitic capacitance at the output node, the latter of which ultimately limits the achievable  $R_{\rm FB}$  to ~100 M $\Omega$ .

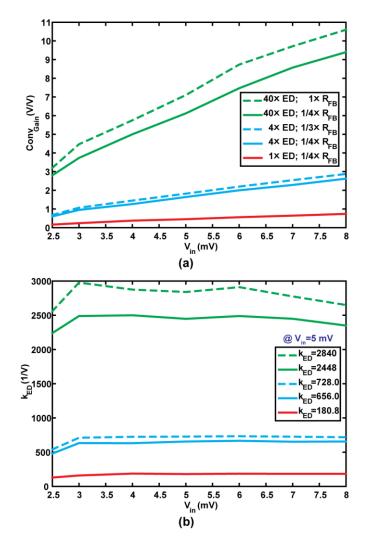

The demodulated output signal of the ED is:

$$v_{\text{out}} = Conv_{\text{Gain}} \cdot v_{\text{in}} = \frac{k_{\text{ED}}}{2} \cdot v_{\text{in}}^2,$$

2.9

where  $Conv_{Gain}$  is the conversion gain of the ED,  $v_{in}$  is the input signal amplitude, and  $k_{ED}$  is the ED scaling factor (in units of 1/V). Thus, the  $k_{ED}$  of the designed ED in the signal passband is given by:

$$k_{\rm ED} = (g_{\rm m2} + g_{\rm mb2}) \cdot Z_{\rm out} \approx [1 + (n-1)^2] \cdot \frac{I_{\rm DS}}{2(nV_{\rm T})^2} \cdot R_{\rm FB},$$

2.10

which is only dependent on design parameters.

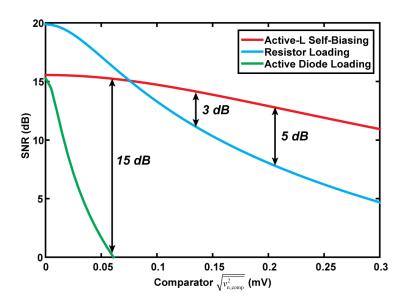

To compare the two conventional biasing schemes with the proposed active-*L* biasing scheme, the SNR at the ED output was calculated. Assuming all three biasing schemes use the same DTMOS configuration as the input stage, the SNR can be written as:

$$SNR = \frac{(g_{\text{m2}} + g_{\text{mb2}})^2 \cdot \frac{v_{\text{in}}^4}{4} \cdot R_{\text{out}}^2}{i_{\text{n,eD}}^2 \cdot R_{\text{out}}^2 + v_{\text{n,comp}}^2},$$

2.11

where  $\overline{i_{n,ED}^2}$  is the total integrated noise current of the ED input transistor,  $R_{\text{out}}$  is the output resistance in the passband, and  $\overline{v_{n,\text{comp}}^2}$  is the total input-referred noise of the comparator. It can be shown that if the ED loading and comparator are noiseless, the SNR is independent of  $R_{\text{out}}$  and

all the biasing schemes would have the same SNR. However, if  $\overline{v_{n,comp}^2}$  is significant compared to the ED noise, higher  $R_{out}$ , and therefore higher  $k_{ED}$  lead to better SNR. Simulation with an ED current of 5 nA and a 3.2 mV input signal for these three bias schemes is depicted in Figure 2.10. If the comparator noise is large, the active-L self-biased scheme achieves the highest SNR.

Figure 2.10. Simulated ED output SNR vs. integrated comparator noise voltage for different biasing schemes.

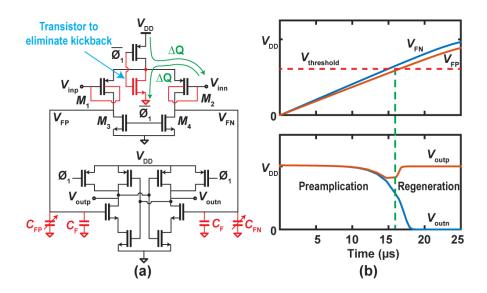

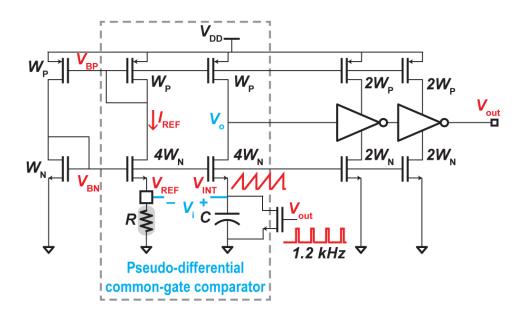

## 2.5.3 Comparator and S/H Stage

The output of the ED is digitized by a comparator, which serves as a 1-bit quantizer. Due to the  $2\times$  oversampling, the comparator operates at 600 Hz. As shown in Figure 2.11(a), the comparator is implemented with a  $g_{\rm m}C$  integrator as a preamplifier followed by a regenerative latch [38]. The operation is as follows: 1) Once  $\overline{\phi}$  goes low, a current determined by the inputs is integrated on  $C_{\rm F}$  until 2) the voltage crosses the latch threshold voltage,  $V_{\rm threshold}$ , after which 3) the positive feedback latch regenerates producing complementary rail-to-rail outputs [Figure

2.11(b)]. The two-stage dynamic comparator is then reset by the other phase of the clock and ready for the next cycle.

Figure 2.11. (a) Schematic of the dynamic two-stage comparator, and (b) simulation showing  $1^{st}/2^{nd}$  stage output voltages.

This two-stage comparator has three dominant noise sources: 1) thermal noise from the input transistors  $M_{1,2}$ , 2) sampling noise from the reset switches  $M_{3,4}$ , and 3) the input-referred noise from the latch. If the input common-mode voltage of the preamplifier is mid-supply (200 mV), the input transistors operate in subthreshold. Therefore, the input-referred thermal noise of the input pair can be written as

$$\overline{v_{\rm n1}^2} = 2 \frac{2qn^2 V_{\rm T}^2}{I_{\rm ds1}} NBW, \qquad 2.12$$

where  $I_{ds1}$  is the DC current of  $M_{1,2}$ , n is the subthreshold slope factor (typically ~1.4-1.6),  $V_T$  is the thermal voltage, and NBW is the noise bandwidth. The NBW is inversely proportional to the integration time  $T_{int}$  of the first stage [38], and given by

$$NBW = \frac{1}{2T_{\text{int}}} = \frac{I_{\text{ds1}}}{2V_{\text{threshold}}C_{\text{F}}}.$$

2.13

Since the 1/f noise corner in subthreshold design is typically much lower than the NBW, it does not significantly contribute to the overall noise. When the differential input signal is small,  $V_{\text{threshold}}$  is relatively constant at a fixed input common-mode voltage and can be extracted from simulation.

Transistors  $M_{3,4}$  introduce sampling noise during the reset phase, and this input-referred noise is

$$\overline{v_{\rm n2}^2} = \frac{1}{A_{\rm Y}^2} \frac{2k_{\rm B}T}{C_{\rm E}}.$$

2.14

The differential gain  $A_{\rm V}$  of the preamplifier is given by

$$A_{\rm V} = \frac{g_{\rm m1}T_{\rm int}}{c_{\rm F}} = \frac{V_{\rm threshold}}{nV_{\rm T}},$$

2.15

where  $g_{m1}=I_{ds}/nV_T$  in subthreshold region. The gain is independent of  $C_F$  in the conventional  $G_{m-1}$  C integrator.

Lastly, the latch also has noise, although the calculations require accounting for the significant nonlinearity and time-varying behavior. As such, the latch input-referred noise is expressed as

$$\overline{v_{n3}^2} = \frac{1}{A_V^2} \frac{2\alpha k_B T}{C_L},$$

2.16

where the scaling factor  $\alpha$  depends on the latch sizing and  $C_L$  is the load capacitance [39]. Since  $V_{\text{threshold}}$  is typically 200-300 mV,  $\overline{v_{\text{n2}}^2}$  is always much smaller than  $\overline{v_{\text{n1}}^2}$ , and can be neglected.

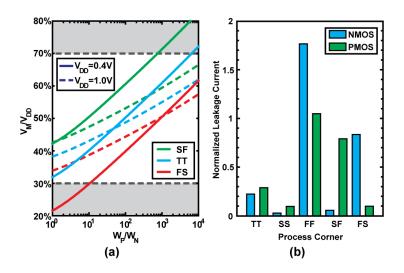

The preamplifier is typically designed with a moderate integration gain of  $\sim$ 5 V/V to suppress the latch input-referred noise. Therefore, the preamplifier usually dominates the noise performance of the entire comparator. As can be observed, adding matched capacitance at the