# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

From Ptides to PtidyOS, Designing Distributed Real-Time Embedded Systems

#### **Permalink**

https://escholarship.org/uc/item/6j00z45c

#### **Author**

Zou, Jia

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

## From Ptides to PtidyOS, Designing Distributed Real-Time Embedded Systems

by

Jia Zou

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electrical Engineering and Computer Science

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Edward A. Lee, Chair

Professor Alberto L. Sangiovanni-Vincentelli

Professor Lee W. Schruben

Spring 2011

# From Ptides to PtidyOS, Designing Distributed Real-Time Embedded Systems

Copyright 2011 by Jia Zou

#### **Abstract**

From Ptides to PtidyOS, Designing Distributed Real-Time Embedded Systems

by

Jia Zou

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Edward A. Lee, Chair

Real-time systems are those whose correctness depend not only on logical operations but also on timing delays in response to environment triggers. Thus programs that implement these systems must satisfy constraints on response time. However, most of these systems today are designed using abstractions that do not capture timing properties. For example, a programming language such as C does not provide constructs that specify how long computation takes. Instead, system timing properties are inferred from low-level hardware details. This effectively means conventional programming languages fail as a proper abstraction for real-time systems.

To tackle this problem, a programming model called "Ptides" was first introduced by Yang Zhao. Ptides builds on a solid foundation in discrete-event (DE) model of computation. By leveraging the temporal semantics of DE, Ptides captures both the functional and timing aspects of the system. This thesis extends prior work by providing a set of execution strategies that make efficient use of computation resources and guarantees deterministic functional and timing behaviors. A complete design flow based on these strategies is then presented.

Our workflow starts with a programming environment where a distributed real-time application is expressed as a Ptides model. The model captures both the logical operations of the system and the desired timing of interactions with the environment. The Ptides simulator supports simulation of both of these aspects. If execution times are available, this information can be annotated as a part of the model to show whether desired timing can be achieved in that implementation. Once satisfied with the design, a code generator can be used to glue together the application code with a real-time operating system called PtidyOS. To ensure the responsiveness of the real-time program, PtidyOS's scheduler combines Ptides semantics with earliest-deadline-first (EDF). To minimize scheduling overhead associated with context switching, PtidyOS uses a single stack for event execution, while still enables event preemptions. The first prototype for PtidyOS is implemented on a Luminary microcontroller. We demonstrate the Ptides workflow through a motion control application.

To my parents Zhen Zou and Ling Wang, my wife Eda Huang, and everyone else whom I've had the pleasure of running into for the first twenty-seven years of my life.

# **Contents**

| List of Figures iv |                |                                                                  |          |  |  |  |  |

|--------------------|----------------|------------------------------------------------------------------|----------|--|--|--|--|

| Li                 | List of Tables |                                                                  |          |  |  |  |  |

| 1                  | 1.1            | Oduction  Design of Real-Time Systems                            | <b>1</b> |  |  |  |  |

|                    | 1.2<br>1.3     | Design of Distributed Systems                                    | 3        |  |  |  |  |

| 2                  | Rela           | ated Work                                                        | 6        |  |  |  |  |

|                    | 2.1            | Logical and Physical Time in Distributed Systems                 | 6        |  |  |  |  |

|                    | 2.2            | Distributed Discrete Event Simulation                            | 7        |  |  |  |  |

|                    | 2.3            | Synchronous Languages                                            | 7        |  |  |  |  |

|                    | 2.4            | Giotto                                                           | 8        |  |  |  |  |

|                    | 2.5            | Scheduling Aperiodic Tasks                                       | 8        |  |  |  |  |

| 3                  | Background 1   |                                                                  |          |  |  |  |  |

|                    | 3.1            | Ptides Model Formuations                                         | 10       |  |  |  |  |

|                    |                | 3.1.1 Actor-Oriented Programming                                 | 10       |  |  |  |  |

|                    |                | 3.1.2 Notions of Time and Their Relationships                    | 11       |  |  |  |  |

|                    |                | 3.1.3 Real-Time Ports                                            | 13       |  |  |  |  |

|                    | 3.2            | Causality Relationships Between Ports                            | 15       |  |  |  |  |

|                    | 3.3            | Baseline Execution Strategy                                      | 16       |  |  |  |  |

|                    |                | 3.3.1 Example Illustrating the Baseline Execution Strategy       | 17       |  |  |  |  |

|                    |                | 3.3.2 Formal Definition for Baseline Execution Strategy          | 18       |  |  |  |  |

| 4                  | Ptid           | es Execution Strategies                                          | 20       |  |  |  |  |

|                    | 4.1            | Event Ordering                                                   | 20       |  |  |  |  |

|                    | 4.2            | Simple Strategy                                                  | 21       |  |  |  |  |

|                    | 4.3            | Parallel Strategy                                                | 22       |  |  |  |  |

|                    | 4.4            | Integrating Ptides with Earliest-Deadline-First                  | 23       |  |  |  |  |

|                    |                | 4.4.1 Ptides Execution Strategies with Model-Time-Based Deadline | 24       |  |  |  |  |

|                    |                | 4.4.2 Event Ordering with Deadlines                              | 25       |  |  |  |  |

|                    | 4.5            | Generalization of Ptides Strategies for Pure Events              | 27       |  |  |  |  |

|                    |                | 4.5.1 Causality Marker                                           | 29       |  |  |  |  |

|    | 4.6    | 4.6.1          | Limitations with Models with Pure Events     | 30<br>31<br>31 |

|----|--------|----------------|----------------------------------------------|----------------|

|    | 4.7    | 4.6.2<br>Summa | Strategy Assuming Events Arrive in Tag Order | 31<br>33       |

| 5  | Ptid   | es Desig       | gn Flow                                      | 35             |

|    | 5.1    | Ptides         | Simulator in Ptolemy II                      | 35             |

|    | 5.2    | Backgi         | round                                        | 36             |

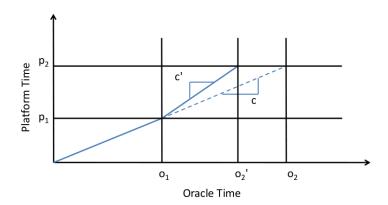

|    | 5.3    | Models         | s of Time                                    | 37             |

|    | 5.4    | Specia         | 1 Actors and Ports in Ptides Simulator       | 38             |

|    |        | 5.4.1          | Ptides Execution Time Simulation             | 39             |

|    | 5.5    | Ptides         | Strategy Implementations in Ptolemy II       | 42             |

|    | 5.6    |                | Generation Into PtidyOS                      | 43             |

|    |        | 5.6.1          | Sensors and Actuators                        | 43             |

|    |        | 5.6.2          | PtidyOS Scheduler                            | 44             |

|    | 5.7    | PtidyO         | OS                                           | 45             |

|    |        | 5.7.1          | Design Requirements                          | 45             |

|    |        | 5.7.2          | Memory Management                            | 45             |

|    |        | 5.7.3          | Ptides Scheduler                             | 46             |

|    |        | 5.7.4          | Concurrency Management                       | 47             |

|    |        | 5.7.5          | Meeting of the Key Constraints               | 57             |

| 6  | Desi   | gn Flow        | v Experimentation                            | 61             |

|    | 6.1    | Execut         | tion Time Simulation                         | 61             |

|    | 6.2    | Applic         | ation Example                                | 63             |

|    |        | 6.2.1          | Application Setup                            | 63             |

|    |        | 6.2.2          | Implementations                              | 65             |

|    |        | 6.2.3          | Application Analysis                         | 66             |

| 7  | Con    | clusion        | and Future work                              | 70             |

|    |        | 7.0.4          | Summary of Results                           | 70             |

|    |        | 7.0.5          | Future Work                                  | 70             |

| Bi | bliogr | aphy           |                                              | 72             |

# **List of Figures**

| 1.1 | Comparison Between Current Approach and the Ptides Approach for the Design of Real-time Systems | 2  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 1.2 | Ptides Design Flow Visualization                                                                | 2  |

| 2.1 | Giotto Schema                                                                                   | 8  |

| 3.1 | Actor Oriented Programming                                                                      | 11 |

| 3.2 | Model Time Delay                                                                                | 15 |

| 3.3 | Causality Relation Example                                                                      | 16 |

| 3.4 | Simple Ptides Example                                                                           | 17 |

| 4.1 | Ptides Example Showing Depth                                                                    | 21 |

| 4.2 | Two Layer Execution Strategy                                                                    | 24 |

| 4.3 | Deadline Calculation Through Model Time                                                         | 25 |

| 4.4 | Deadline Example                                                                                | 26 |

| 4.5 | Actor with Causality Interface Decomposed                                                       | 28 |

| 4.6 | Event Trace for Accumulator Actor                                                               | 29 |

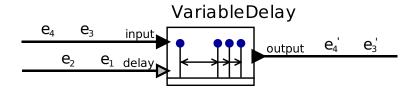

| 4.7 | Variable Delay Actor With Event Sequences                                                       | 30 |

| 4.8 | Example Illustrating Strategy with Events Arrive in Tag Order                                   | 32 |

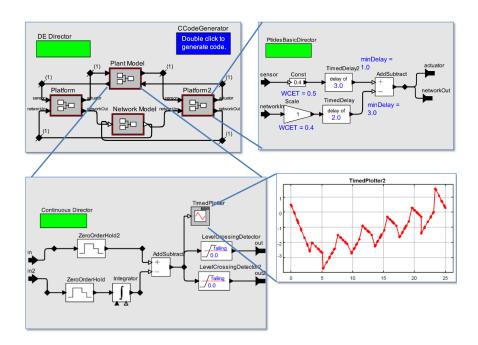

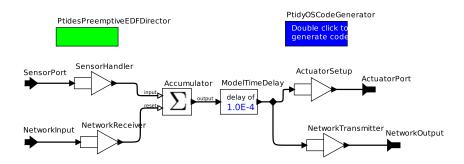

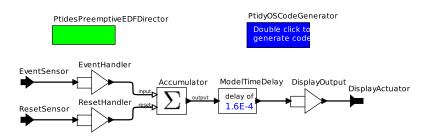

| 5.1 | Ptides Design Flow Example                                                                      | 36 |

| 5.2 | Clock Drift and the Relationship Between Oracle Time and Platform Time                          | 37 |

| 5.3 | Sensor, Actuator and Network Ports                                                              | 43 |

| 5.4 | Simple Ptides Example                                                                           | 44 |

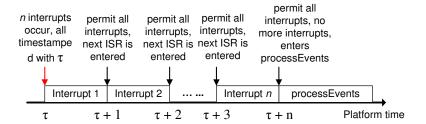

| 5.5 | Interrupt Chaining                                                                              | 49 |

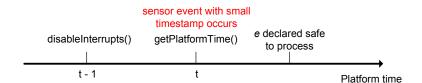

| 5.6 | Counter Example Illustrating Possible Violation of DE Semantics                                 | 50 |

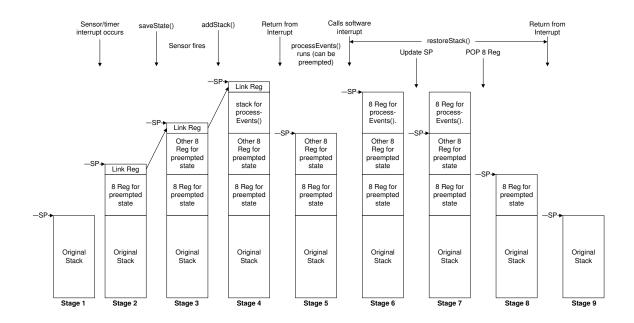

| 5.7 | Stack Manipulation Visualization                                                                | 56 |

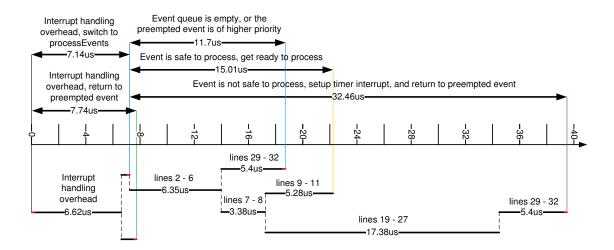

| 5.8 | Scheduling Overhead Timing Diagram                                                              | 60 |

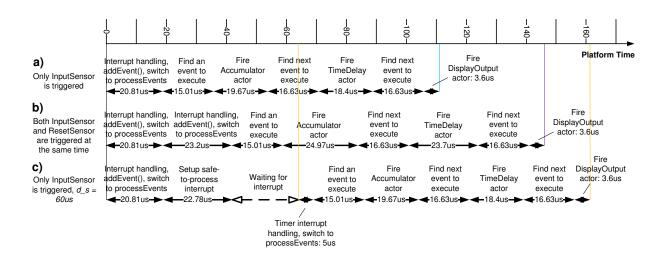

| 6.1 | Event Trace Timing Diagram                                                                      | 62 |

| 6.2 | Tunneling Ball Device                                                                           | 64 |

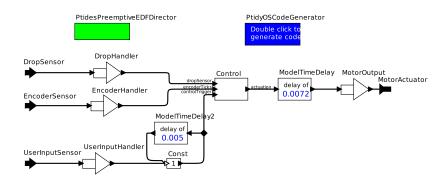

| 6.3 | Ptides Model For Tunneling Ball Device                                                          | 66 |

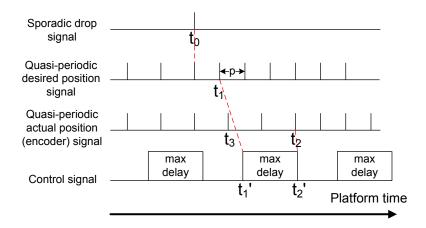

| 6.4 | Control Signals For the Tunneling Ball Device                                                   | 67 |

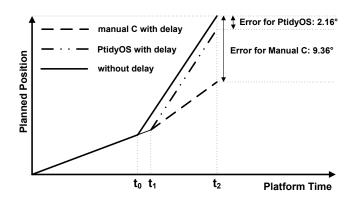

| 6.5 | Position Errors For PtidyOS vs. Manual C Implementation                                         | 68 |

# **List of Tables**

| 4.1 | Summary of Ptides Execution Strategies | . 3 |

|-----|----------------------------------------|-----|

| 6.1 | Ball Drop Success Rates                | . 6 |

#### Acknowledgments

I want to thank my parents, Zhen Zou and Ling Wang for bring up me and making me the kind of person I am today. I'll be eternally grateful for all the sacrifices they made to get me to where I am today. I want to thank Eda, my wife for supporting me throughout my 5 years of study. Even though we have our share of fights, I cannot imagine how I could have pulled it off without her.

I want to thank my advisor, Professor Edward A. Lee, for his mentorship through my years at graduate school. Without his suggestions and encouragements, I can't imagine how I could have completed my Ph.D. I'm also grateful for others on my dissertation committee. Professor Alberto Sangiovanni-Vincentelli's charisma and energy for research is always a great source of inspiration for me. Professor Lee Schruben's timely responses even while he is injured is especially heartening.

I want to thank Slobodan Matic, my main collaborator on the Ptides project. Many of the interesting ideas for my thesis stem from our discussions in the (freezing) embedded lab. I would also like to thank John Eidson and Janette Cardoso for reading my thesis and providing me with timely comments. I want to thank Patricia Derler for her first implementation of the Ptides director in Ptolemy II, her hard work is also a great inspiration for me. I also want to thank Jeff Jensen, who put his heart and soul into the creation of the tunneling ball device.

I would also like to thank the rest of the Ptolemy group. Sharing an office with Ben Lickly has been fun. I really enjoyed all the discussions we had on topics both about research, and also about life in general. I want to thank all those who kept attending the code reviews for the Ptides director implementation, including, but not limited to Mike Zimmer, Christos Stergious, Ilge Akkaya, Christopher Brooks and others I've mentioned earlier. I want to thank Christopher Brooks for forcing good coding habits on me. I didn't get it at first, but he really pointed out the importance of having a good habit for software development to me.

Finally, I want to thanks others in the Ptolemy group, especially Issac Liu and Shanna Shaye Forbes for all the fun we had for the last four years. I had a blast!!

# **Chapter 1**

# Introduction

This thesis considers distributed real-time embedded systems in applications such as factory automation, large-scale instrumentation, and network supervision and control. Implementations of such systems consist of networked computers ("platforms") with sensors and actuators distributed throughout a network. Orchestrated actions are required from the platforms. Current practices in designing both the real-time and the distributed aspects of these systems are examined. We identify some fundamental flaws in the design process, and motivate our approach for a new design methodology.

## 1.1 Design of Real-Time Systems

Real-time systems are those whose correctness of operation depend not only on the logical correctness, but also on the amount of time it takes to perform that logic [3]. These systems can be divided into two categories, *hard real-time* and *soft real-time* systems. Hard real-time systems are those where deadline violations result in immediate system failures, while soft real-time systems are able to tolerate deadline violations to some extent. For example, in a vehicle, the subsystems that control the steering and airbags are generally considered hard real-time systems, while audio control is considered a soft real-time system, since missed beats in the sound track are not safety-critical. A data logging subsystem that runs in the background is usually considered a non-real-time system. We focus on hard real-time systems in this work.

Real-time systems are prevalent in embedded environments since interactions with the physical world are generally only meaningful if performed within a bounded period of time. However, to program these real-time systems, engineers use tools that do not offer the necessary abstractions. Specifically, programming languages such as C are often used for embedded system design, yet these languages only provide constructs for the programmer to specify systems' logic, not their timing. Programmers are forced to step outside of the programming language in order to specify real-time behavior. A common practice is to control timing using priorities. A real-time operating system (RTOS) is a prime example of this practice. RTOSs are used to perform resource allocation and schedule real-time programs. Most RTOSs, such as VxWorks [51], RTLinux [16], FreeRTOS [48], allow programmers to assign priorities to system tasks. These priorities are used to formulate a schedule, and the timing of the system is a consequence of this schedule. There are two major disadvantages with this approach.

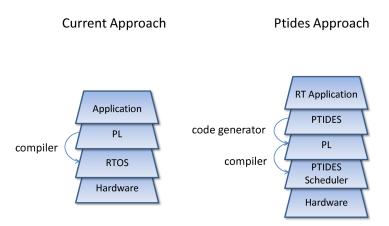

Figure 1.1: Comparison Between Current Approach and the Ptides Approach for the Design of Real-time Systems

- 1. Along with priorities, execution times are needed to infer the timing delays of a system. However execution time is hardware-dependent information.

- 2. Sometimes it is unintuitive for programmers to define whether some task is "more important" than another, and it is even more obscure to understand how the priority assignments affect the schedulability of the system.

Since the timing of the system is a consequence of the priority assignments and execution times, the hardware characteristics must be known right from the start of the design process. Another consequence is that once the design is completed for a particular platform, the entire hardware-software stack must be frozen, and cannot be easily upgraded, debugged, or ported to another platform. Any change to even the most minuscule detail of the system may result in timing anomalies. Zhao first introduced a new programming model, called Ptides, which addresses this problem by allowing programmers to fully specify the logic and the timing of the system within the model, without the knowledge of execution times [53]. This approach decouples the software design from the hardware platform. Another way to view Ptides is that it's an additional abstraction layer that captures both the logic and the timing of a system. Fig. 1.1 visualizes and compares these two approaches.

To address the second point, system timing constraints are defined between sensors and actuators. That is, from an environment point of view, the only delays that are of interest are end-to-end delays. For example, a real-time requirement for the safety system of a vehicle would be something in the form of: when the system senses the car has hit a tree, the airbags must pop out (actuate) within n milliseconds. Let us assume multiple tasks are involved to pop out the airbag. Notice the real-time constraint says nothing about the priorities of these tasks, yet the priorities have a direct effect on whether the timing constraint will be satisfied. This can make priority assignments unintuitive and difficult to understand. Ptides takes a different approach. Since the timing requirements are usually defined between sensors and actuators, those are the only timing delays programmers assign in a Ptides model. The Ptides scheduler then uses this information to *infer* event

priorities and perform real-time scheduling. We will explain in more detail in the following chapters about how one specifies timing delays in a Ptides model, but to summarize, conventional RTOS allows programmers to specify task priority. The end-to-end timing behavior is a consequence of these priorities. Ptides on the other hand, allows programmers to explicitly define the timing of the system, and the system event priority is then a consequence of the timing.

### 1.2 Design of Distributed Systems

Not only is Ptides an abstraction for real-time systems, its scheduling scheme is especially useful in distributed environments. We consider distributed systems consisting of independent computing platform with sensors and actuators, As early as 1978, Lamport pointed out that a "happensbefore" relationship between system events could be easily defined if components share a global notion of time [29]. This was the first indication that network time synchronization has the potential to significantly change how we design distributed systems. Clock synchronization protocols such as NTP [40] have been around for a while, however these services only offer time synchronization precision on the order of milliseconds, which is too loose for some applications. However, recently, techniques such as GPS [27] and IEEE 1588 [22] have been developed to deliver synchronization precision on the order of hundreds of nanoseconds, and in certain cases even down to the order of nanoseconds [1]. Such precision offers truly game-changing opportunities for distributed embedded software.

The deterministic semantics of Ptides benefits greatly from a global notion of time. As we will explain in Chap. 3, by relating model time to physical time at specific points in the model, Ptides guarantees deterministic order of event processing in local platforms. By sharing a global notion of physical time across platforms, this deterministic order can be expanded to events arriving through networked components. Thus we envision Ptides to be useful both in single platform and distributed systems that are time synchronized.

## 1.3 Ptides Model and Design flow

Due to the Ptides programming model's ability to capture system timing properties, as well as the inherent property of maintaining timed semantics in a networked, time-synchronized environment, we argue it is advantageous to program distributed real-time systems as Ptides models. This is contrary to the typical approach where software tasks are defined as threads with periods, priorities, and deadlines.

Ptides (pronounced "tides," where the "P" is silent), is an acronym for *programming tem- porally integrated distributed embedded systems*. Ptides builds on the solid semantic foundation of

Discrete Event (DE) models [8, 19]. DE specifies that each actor should process events in timestamp

order, and thus the order of event processing is independent of the physical times at which events

are delivered to the actors. The particular variant used in Ptides provides a determinate semantics

without requiring actors to introduce time delays between inputs and outputs [33]. Whereas classically DE would be used to construct *simulations* of such systems, in Ptides, the DE model is an

executable specification. By leveraging network time synchronization [25, 14], Ptides provides a

mechanism for distributed execution of DE models [20, 9, 41, 23] that requires neither backtracking

(as in [23]) nor null messages (as in [9, 41]).

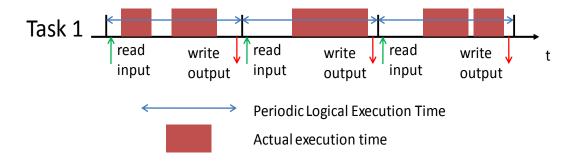

Figure 1.2: Ptides Design Flow Visualization

The objective with Ptides is to compile (or code generate) this specification into a deployable implementation. Hence Ptides follows the principles of model-based design [28]. This approach shortens the design cycle for real-time embedded applications. It also allows the programmer to separate the design from the implementation, where applications can be easily ported from one platform to another while retaining system logical and timing determinacy.

This thesis presents a design flow that encompasses a simulator, a code generator, and an ultra-lightweight real-time operating system, as shown in Fig. 1.2. The simulator is built on the Ptolemy II framework [15]. Since the timing of the program is captured as a part of the Ptides model, distributed real-time applications can be designed and simulated without the knowledge of execution times. Once execution times are known, the Ptides simulator can simulate physical time and event preemption. This in turn allows the programmer to check for scenarios in which deadline misses occur. Once satisfied with the design, a target-specific code generator can be used to transform the model into a C implementation. This implementation runs on a real-time operating system called PtidyOS. In order to ensure logical and timing determinism, as well as responsiveness of the real-time program, PtidyOS's scheduler combines Ptides semantics with traditional scheduling methods such as earliest-deadline-first (EDF). To minimize scheduling overhead associated with context switching, PtidyOS performs all event processing in interrupt service routines, while only using a single stack for event execution.

The remaining chapters are organized as follows. Chapter 2 presents work related to the Ptides programming model. Chapter 3 reviews basic concepts such as notions of time and the relationships between them, as well as a baseline execution strategy. Chapter 4 defines a family of execution strategies for Ptides that assures compliance with DE semantics and support distributed scheduling and control. Each of these strategies is based on different assumptions, and each has different scheduling properties. Chapter 5 then talks about the Ptides design flow, from simulator to code generator to PtidyOS. Chapter 6 applies this design flow on an application called the tunneling

ball device. We conclude and provide pointers for future work in Chapter 7.

# **Chapter 2**

# **Related Work**

This chapter explores previous work that is related to either the Ptides programming model or the real-time operating system PtidyOS.

### 2.1 Logical and Physical Time in Distributed Systems

There exists history dating back to the 1970's concerning the use of logical (model) and physical time to schedule distributed systems. In [29], Lamport famously introduced the use of logical time to define a "happened-before" relationship between two events. He also presented an algorithm that uses logical time to totally order system events. Lamport then gave an example showing that by maintaining a total order, certain anomalous event processing behaviors can be avoided. Namely, logical determinism can be preserved. However, having totally ordered events may lead to inefficient scheduling, since events that are inherently concurrent are forced to process in order. This makes Lamport's scheme largely inapplicable to real-time system.

In [9], Chandy and Misra introduced an algorithem based on a discrete-event (DE) model of computation, which also uses logical time, but ensures determinacy while allowing inherently concurrent elements to execute independently. Their algorithm is widely used in the area of circuit simulation. However, since their algorithm focuses on simulation, only logical, but not physical time is used.

Lamport on the other hand, defines another "happened-before" relationship between system events by assuming an upper bound on network transmission delay, as well as an upper bound on the time synchronization error between physical clocks on distributed platforms. By utilizing physical clocks as part of the execution semantics, Lamport's scheduling mechanism can be applied to implementations. The Ptides approach is similar to [9] but is used for distributed real-time system scheduling instead of simulation. Moreover, Ptides uses physical clocks in its scheduling scheme, thus eliminating the need for "null messages" [9] or backtracking [23]. Like [29], by assuming bounded network delay and clock synchronization error across distributed physical clocks, and by conforming to DE semantics, Ptides ensures logical determinism.

Ptides also offers interesting fault tolerance properties. Lamport noted in [29] that:

The problem of failure is a difficult one... Without physical time, there is no way to distinguish a failed process from one which is just pausing between events. A user can tell that a system has "crashed" only because he has been waiting too long for a response.

As we will show in later sections, the Ptides framework, by using physical clocks, makes the problem of failure identification a simple one, and we can define formally what constitutes "waiting too long".

#### 2.2 Distributed Discrete Event Simulation

Chandy and Misra started a field of work on distributed DE simulation, with the goal of accelerating simulation by exploiting distributed computing resources. The approach described in [9] is one of the so-called "conservative" techniques, which process timestamped events only when it is sure that no earlier timestamped event will be delivered to the same software component. So-called "optimistic" techniques [23] speculatively process events even when there is no such assurance, and roll back if necessary.

For distributed embedded systems, the potential for roll back is limited by actuators (which cannot be rolled back once they have had an effect on the physical world) [17]. Established conservative techniques, however, also prove inadequate. In the classic Chandy and Misra technique [9], each compute platform in a distributed simulator sends messages even when there are no data to convey in order to provide lower bounds on the timestamps of future messages. The messages that only carry time stamp information and no data are called "null messages." This technique carries an unacceptably high price in our context. In particular, messages need to be frequent enough to prevent violating real-time constraints due to waiting for such messages. Not only do these messages increase networking overhead, but the technique is also not robust. Failure of a single component results in no more such messages, thus blocking progress in other components. Ptides is related to several efforts to reduce the number of null messages, such as [20], but makes much heavier use of static analysis, thus minimizing network communication overhead.

## 2.3 Synchronous Languages

Considerable research activity has been devoted to exploring high-level MoCs for embedded systems, and Ptides is not the first to incorporate timed semantics into system models. Synchronous languages such as Esterel, Lustre, Signal, SCADE, and various dialects of Statecharts have long been used for the design of embedded systems [4], however, there are major differences between synchronous languages and Ptides. In Synchronous languages, logical time (also called model time) is expressed as a member of the natural numbers. At every tick, all system components execute until a fixed point is reached, and the program steps to the next tick. When implementing applications, it is intuitive to map this logical time (ticks) to the period at which data is sampled. This allows for a mapping from synchronous models to a time-triggered architecture (TTA) or loosely time-triggered architecture (LTTA) [50, 5, 7], where the system is time-triggered at each tick. Ptides on the other hand, expresses logical time as the superdense model of time [39]. i.e., logical time is expressed as a pair of timestamp and microstep, where timestamps are members of the Real number set. Thus it is much more intuitive to map Ptides's timestamps to physical time. The finer granularity of logical time makes Ptides much more suitable for event-triggered applications. Since time-triggered is a special case of event-triggered architecture, we argue Ptides can be used to design a more general class of systems.

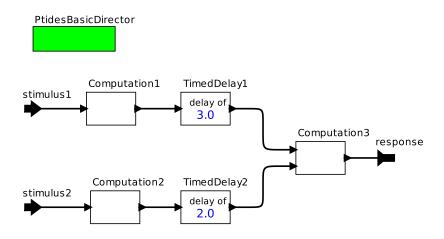

Figure 2.1: Giotto Schema

### 2.4 Giotto

Another high level MoC used for the design for real-time systems is Giotto. The notion of logical time in Giotto is "logical execution time" (LET) [21]. An example is shown in Fig. 2.1. Each task in Giotto has a LET of a fixed period. Giotto specifies that data reads must happen at the beginning of the LET, while data writes must occur at the end. Task executions must occur during LET, and the end of the LET is effectively the deadline for that task. However, the execution does not need to span the entire LET, i.e., tasks can be preempted during the LET.

Ptides is different from Giotto in two regards: 1) Giotto assumes periodic tasks, while Ptides takes an event trigger approach, and 2) Giotto relates logical time and physical time at points of data transfer between tasks. Ptides relates them at points where communication with the outside world occurs. In other words, Giotto enforces deadlines for every periodic task in the system, including those that do not interact with the physical environment. Ptides takes a different approach, where deadlines are only enforced at points where interactions with the physical environment occur. Our intuition is that since from the environment point of view, the only places where timing is relevant are at sensors and actuators, these are the only points where timing of the interactions with the outside world should be enforced.

# 2.5 Scheduling Aperiodic Tasks

Finally, we review previous work that deals with real-time scheduling of aperiodic events. Periodic scheduling scheme such as rate-monotonic (RM) has been widely adopted in the industry [45], mainly for its simplicity in implementation. To build on its success, the research community has worked on extending periodic scheduling scheme to allow aperiodic tasks [49, 35, 46]. These approaches use a special purpose process called a "server" to schedule aperiodic tasks. These servers take a "slack-stealing" approach, where aperiodic tasks can "steal" as much processing power as possible, without causing periodic tasks to miss their deadlines. This approach is based on the assumption that periodic tasks have hard deadlines, while aperiodic tasks have soft or "firm" deadlines. Tasks with firm deadlines are those whose executions can be rejected by the scheduler, but the scheduler will meet deadlines for the accepted tasks. However, this assumption is not true in many real-world applications. For example, faults are inherently aperiodic, and they usually re-

quire hard real-time processing in order to guarantee safety of the system. Ptides takes a purely event-triggered approach, and treats all periodic and aperiodic tasks equally as hard real-time tasks. Processing power is allocated purely based on events' deadlines, where these deadlines are inferred from the real-time specifications of the system.

Another difference between classic scheduling approaches and Ptides is that with its timed semantics, Ptides schedulers ensure not only the timeliness of event processing, but also logical determinacy of the system. Ptides defines a "safe-to-process" analysis, which releases events only if they are processed in logical time order. This aspect is absent from the classic scheduling theory, where the deterministic behavior of the system is ignored, even though it can be directly affected by the scheduling scheme used.

# **Chapter 3**

# **Background**

#### 3.1 Ptides Model Formulations

Ptides, an acronym for Programming Temporally Integrated Distributed Embedded Systems, is a programming model based on the discrete-event (DE) model of computation. DE is used for hardware simulation in languages such as VHDL, for network simulation, and for complex system simulations [52]. It has the advantages of simplicity, time-awareness, and determinism. Ptides takes advantage of DE semantics and offers a programming model that ensures logical and timing determinacy. By logical determinacy, we simply mean given the same sequence of timestamped inputs, the same sequence of timestamped outputs will always be produced. In addition, depending on the implementation of the actuators, Ptides models can be specified to guarantee timing determinacy, i.e., the outputs will always be produced after the same physical time delay, assuming no deadline misses occur [54, 17].

Ptides has been formally defined in [56]. Here, we will review the basic formulation as well as a baseline execution strategy. All execution strategies in the following chapter are based on this baseline strategy.

First, we introduce some basic background about the Ptides formulation. The detailed formulations are given in [56] and [17], but here we will try to focus on examples that demonstrate the intuitive ideas behind each formulation.

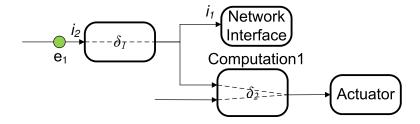

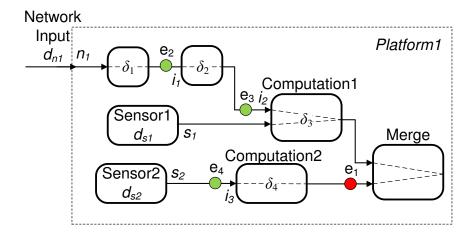

#### 3.1.1 Actor-Oriented Programming

We present Ptides in the context of actor-oriented programming methodology [31]. In this methodology, the most primitive software component is called an *actor*, which one can interpret as a block of code. Actors communicate with each other through explicit connections. An example is shown in Fig. 3.1.

In this work we assume actors cannot have underlying communications that are not explicitly expressed in the model. Take the example shown in Fig. 3.1, Computation1 and Computation2 cannot access shared variables. By explicitly specifying the points where communication occurs between code blocks, potential data race conditions for shared variables are eliminated (which is a major source of bugs in thread based approaches [30]), and the entire model becomes much easier to analyze.

Figure 3.1: Actor Oriented Programming

#### 3.1.2 Notions of Time and Their Relationships

This section explores notions of time in a Ptides model, as well as their relationships with each other.

#### **Physical Times**

In a distributed system context, we assume each platform has a local clock that keeps track of the physical time. This clock could be implemented, for example, using a hardware timer in a microcontroller. The time maintained by this clock is called "platform time". In a system that is not time synchronized, the platform times of distributed platforms are completely independent from each other. As mentioned in the introduction, this work is mainly concerned with platforms that share a global notion of time. In other words, we assume platform times across the distributed system to be synchronized within some bounded error.

We also introduce a notion of "oracle time". We assume there exists an all-knowing oracle that keeps track of the "correct" physical time in a distributed system. Special relativity tells us that this notion of oracle time does not exist, but for all practical purposes we assume it exists for the applications we are interested in. Most time-synchronization protocols implement a master-slave scheme. In this scheme, one platform is chosen to be the master, while slaves try to synchronize their clocks with respect to the master clock. Here the oracle time can be interpreted the time of the master clock.

We now define a function  $\mathbb{F}_i$ , which converts oracle time  $t_o$  to platform time  $t_i$  for a particular platform i,

$$t_i = \mathbb{F}_i(t_o). \tag{3.1}$$

In other words,  $t_i$  is the time of the platform clock at oracle time  $t_o$ . We assume  $\mathbb{F}_i$  to be a bijection. This means the platform clock can only drift with respect to the oracle clock at a rate greater than zero, where a rate of one would indicate the platform clock drifts at the same rate as the oracle clock. Another consequence of this assumption is that platform clock cannot be reset backward

to an arbitrary value. With this function, we can define the clock synchronization error bound  $\epsilon_{i,j}$  between two platforms i, j,

$$\epsilon_{i,j} = \max_{t_o \in \mathbb{R}} \{ |\mathbb{F}_i(t_o) - \mathbb{F}_j(t_o)| \}. \tag{3.2}$$

Notice this error bound could be unbounded. For example, if two platforms drift at different rates with respect to the oracle clock, and this rate is never updated, then the error bound would be infinity.

We can then deduce the *maximum clock synchronization error bound* for a distributed system:

$$\epsilon = \max_{i,j \in P} \{ \epsilon_{i,j} \},\tag{3.3}$$

where P is the set of all platforms in this system.

#### **Model Time**

In DE and Ptides, actors communicate through explicit links by sending events. An event is a pair with a data value and a tag. In this case, Ptides' tag uses the superdense model of time [34], which means the tag is a tuple of a timestamp and a microstep.

With these tags, we can define an ordering between two events. The order we are interested in is a lexicographical ordering of the following tuple: < T, I>, where  $T=\mathbb{R}$  represents the set of event timestamps.  $I=\mathbb{N}$  represents the set of events' microsteps. For  $e_1=<\tau_1,i_1>$ ,  $e_2=<\tau_2,i_2>$ , and  $e_1,e_2\in< T,I>$ , the ordering is defined as:

$$e_1 < e_2 \Leftrightarrow (\tau_1 < \tau_2) \lor$$

$(\tau_1 = \tau_2 \land i_1 < i_2)$

These tags are also referred to as "model time" (also called logical time). Specifically, if an event of a certain tag is currently being processed in a platform, then that tag is the current model time of that platform. Notice here we assume each platform has a single processor, and only one event is actively processed at a time. The Ptides formulation can be extended to work in a multi-core environment, however we will restrict ourselves to single core CPUs in this thesis. Actors can manipulate event tags, with the constraint that all actors must be causal. i.e., the tag of an output event must be larger than or equal to that of the triggering input event.

Each of the actors may also have a state associated with them. DE semantics specifies that each actor state must be accessed by events in tag order. For example, if the processing of an input event results in the read and/or write of the state of the actor, then that actor must process input events in tag order.

Note the notion of model-time is distinctly different from time in the physical world. For example, while time in the physical world has a total order, model time in Ptides does not have to observe a total order. The scheduler may schedule an event of bigger tag before processing one of smaller tag, as long as these events do not access the same actor's state.

#### 3.1.3 Real-Time Ports

#### **Sensor and Actuator Ports**

As mentioned before in Chap. 2, there is a long history behind distributed discrete event simulation. In that context DE is used as a simulation tool, the simulation runs entirely in model time. The Ptides model however, relates model time to platform time. These relations are introduced at points where interactions between the computer and the physical environment occur. We call these points *real-time ports*. The definitions for these ports were first introduced in [56], and we review them here.

Sensor ports are inputs to a Ptides platform. When sensing occurs, measurements are taken, and the measured data value is timestamped with the current platform time. In other words, a sensor event is created. Its value is the measured data, and its tag consists of microstep 0, and timestamp equal to the platform time of when sensing occurred. This event is sent to the Ptides scheduler and made visible to the rest of the platform. Let the sensor event's timestamp be  $\tau$ , and the platform time at which the event is visible to the scheduler is t, then the following equation must be true:

$$t \ge \tau,\tag{3.4}$$

Also if we assume an upper bound on the worst-case-response-time of a sensor actor, then:

$$t < \tau + d_s, \tag{3.5}$$

where  $d_s \in \mathbb{R}^+ \cup \{\infty\}$  is a parameter of the port called *maximum physical time delay* (also referred to as the *real-time delay*).

On the actuator side, we enforce the following rule: an event e with timestamp  $\tau$  must be delivered to the environment at platform time equal to  $\tau$ . This implies e must be sent to the actuator at platform time  $t-d_a$ , where  $d_a$  is again the worst-case-response-time for the system to deliver an actuation signal to the environment. In other words, let t be the delivery time of an event to the actuator, the following constraint must hold:

$$t \le \tau - d_a. \tag{3.6}$$

This constraint imposes a platform time deadline for each event delivered to an actuator, where the timestamp  $\tau-d_a$  serves as the deadline. If there exists multiple actuation events of the same timestamp  $\tau$ , the microsteps of the tags are used to define the order by which actuations occur.

Notice here, we only defined what each element of the tag means at actuators, but we do not specific how the system enforces these deadlines and actuation orderings defined by the tags. These are application-dependent concepts. For example, if two actuation events have timestamps whose difference is less than  $d_a$ , then the second actuation event will not be delivered to the environment on time. We leave it to the application programmer to decide what to do in such a scenario. The programmer might enforce certain rules at other parts of the model to ensure such a scenario does not occur, or he/she might decide the delay is small enough such that the real-time properties of the system is not affected, or he/she might decide to throw an exception. In any case, we only present the semantic meaning of the tag at actuators, but the actual implementation is application-dependent.

#### **Network Input and Output Ports**

Since we envision Ptides as a programming model for distributed systems, we must properly define timed semantics for data transmitted across distributed platforms. Two alternatives are first considered:

- 1. only data is transmitted; data is timestamped with the local platform time at the receiving platform.

- 2. a data and tag pair is transmitted; the event retains its original tag at the receiving platform.

The first alternative considers network inputs as sensor ports. The advantage of this scheme is that each platform is essentially independent of the other, and the safe-to-process analysis of Ptides (which we will introduce in the next section) can be performed in each platform independently, without the knowledge of execution time in other platforms. The major disadvantage of this scheme is that the model's behavior becomes dependent on the network delay. i.e., a model will only produce deterministic data outputs if the network delay does not change during different runs. Notice most commonly used network transmission schemes do not guarantee such behavior.

The second scheme, on the other hand, preserves the original timestamps as events travel across network boundaries. This means the logical output of the model will always be deterministic regardless of the network delay, provided DE semantics is preserved. However, if the network delay can be arbitrarily large, preserving DE semantics becomes a challenge. The related work section mentioned so-called conservative and optimistic approaches to deal with this problem. Inspired by [29], Ptides steps away from these approaches. Instead, the following assumptions about network and clocks are made:

- 1. maximum clock synchronization error between platforms is bounded by  $\epsilon$ .

- 2. maximum network communication delay is bounded by  $d_n$ .

The first assumption has already been described in Sec. 3.1.2. The second assumption simply states that if platform i sends a packet to platform j at oracle time t, then platform j must receive this packet no later than oracle time  $t + d_n$ .

From these assumptions we infer the following property: If data is transmitted from platform i at its platform time  $t_1$ , then it must reach the receiver platform j, at Platform j's time, no later than

$$t_1 + d_n + \epsilon. (3.7)$$

We then make the same requirement at network outputs as actuators: The platform time t at which an event e must be delivered to an network output device must be no later than  $\tau$ , where  $\tau$  is the timestamp of e. I.e.,

$$t < \tau$$

(3.8)

Combining Eq. 3.7 and 3.8, we have the following property at the sink network input device: when platform j receives a network input event of timestamp  $\tau$  at platform time  $t_j$ :

$$t_i \le \tau + d_n + \epsilon. \tag{3.9}$$

Notice that Eq. 3.9 is in the same form as Eq. 3.5, with  $d_s = d_n + \epsilon$ . This effectively allows us to treat network inputs the same way as sensor inputs, thus retaining the advantage of

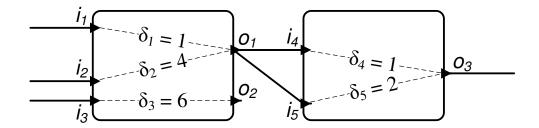

Figure 3.2: Model Time Delay

treating each platform separately when formulating the Ptides execution strategies. The details of this is discussed in Sec. 3.3.

## 3.2 Causality Relationships Between Ports

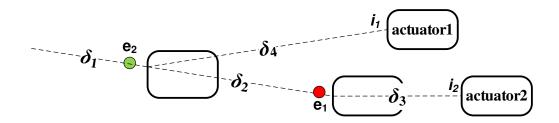

Before describing the Ptides execution strategies, we first review the concept of model time delay.

Intuitively, model time delay is the amount by which tag value is incremented by an actor as it consumes and produces events. For example, If an actor provides a model time delay of x, then after consuming an input event of tag  $(\tau,0)$ , the actor should produce an output event of tag  $(\tau+x,0)$ .

Here we review two model time delay functions  $\delta_0$  and  $\delta$ , which were first defined in [56]. These functions are rooted in causality interface theories [55], and both take a pair of ports as arguments. The first function  $\delta_0(i,o)$  takes a pair of ports as argument, and i,o are input and output ports, respectively.  $\delta_0$  represent the *minimum* model time delay between this pair of ports. If these ports do not belong to the same actor, or if there is no causality relationship between these ports, then  $\delta_0(i,o)=\infty$ . For example in Fig. 3.2, the dotted lines within an actor indicate that the pairs of input and output ports are causally related, while  $\delta_i$  is the minimum timestamp delay between these ports. For simplicity, we ignore the microsteps field of the delays, which are all assumed to be zero. In this example, consumption of an input event at  $i_1$  leads to the production of an event at  $o_1$ , and  $\delta_0(i_1,o_1)=\delta_1=1$ , while  $\delta_0(i_1,o_2)=\delta_0(i_1,o_3)=\delta_0(i_3,o_1)=\infty$ . Since all actors are assumed to be causal,  $\delta_0(i,o)$  takes a minimum value of 0.

The second delay function  $\delta(p_1,p_2)$  takes a pair of arbitrary ports (can both be input or output ports) in the system. Intuitively,  $\delta(p_1,p_2)$  is the minimum model time delay from  $p_1$  to  $p_2$ . Note unlike the  $\delta_0$  function, ( $\delta(p_1,p_2)$  can take a value less than  $\infty$  even if  $p_1$  and  $p_2$  do not reside in the same actor). Again using the example shown in Fig. 3.2,  $\delta(i_1,o_3)=\min\{\delta_1+\delta_4,\delta_1+\delta_5\}=2$ , while  $\delta(i_3,o_3)=\infty$ .

We also review the definition of input port groups. The formal definition of an input port group is as follows:

Let I be the set of all input ports on all actors in the system, and O be the set of all output ports in the system.  $i', i'' \in I$  belong to the same input port group if and only if:

$$\exists o \in O \mid (\delta_0(i', o) < \infty) \land (\delta_0(i'', o) < \infty)$$

Figure 3.3: Causality Relation Example

Note the causality function used here is  $\delta_0$  instead of  $\delta$ . In other words, two input ports reside in the same input port group if and only if they reside in the same actor, and they are both causally related to the same output port. Again take Fig. 3.2 as example,  $i_1, i_2$  belong in one input port group, while  $i_3$  belongs to another input port group all by itself. We use the notation  $\mathbb G$  to denote input port groups, where  $\mathbb G_{i_1} = \mathbb G_{i_2} = \{i_1, i_2\}$ , and  $\mathbb G_{i_3} = \{i_3\}$ .

Armed with the above definitions, we are ready to define the baseline strategy.

### 3.3 Baseline Execution Strategy

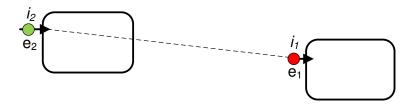

All Ptides strategies presented in this work take an event (here on referred to as the *event* of interest) in the system as argument. If the strategy returns true, the destination actor can "safely" process this event. By "safe," we mean the same input port group will not receive an event of smaller tag at a later physical time. If an event e could potentially render the event of interest unsafe, then we say e causally affects the event of interest. This term is inspired by Lamport in [29]. Take Fig. 3.3 for example, where  $e_2$  causally affects  $e_1$  if the processing of  $e_2$  will produce a future event  $e_2$  such that  $e_2$  and  $e_1$  have destination ports that reside in the input port group, and  $e_2$  may have a tag that is less than or equal to that of  $e_1$ . In other words,

$e_2$  causally affects  $e_1$  if and only if:

$$\exists i_x \in \mathbb{G}(i_1) \mid \tau(e_2) + \delta(i_2, i_x) \le \tau(e_1),$$

(3.10)

where  $i_2$  and  $i_1$  are the destination ports of  $e_2$  and  $e_1$ , respectively, and  $\tau(e)$  is a function that maps an event e to its tag.

As Yang Zhao pointed out in [54], our problem formulation of an execution strategy is very much the same as distributed discrete event simulation. Chandy and Misra defined a strategy in [9] that solves this problem using "null messages." In the Ptides formulation however, by relating model time to physical time, and by assuming a global notion of time across all computation platforms, and a bounded network delay, the transmission of "null messages" can be replaced by a comparison between the timestamp of the event and physical time to check whether events are safe [54].

In summary, the strategies presented in this thesis: 1) leverage network time synchronization to eliminate the need for null messages, 2) improve fault isolation in distributed systems by making it impossible for components to block others by failing to send messages, and 3) allow causally independent events to be processed out of tag order, thus increasing concurrency and allowing more models to become schedulable w.r.t real-time constraints.

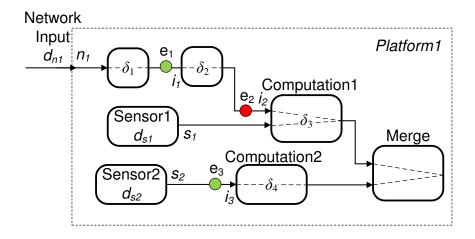

Figure 3.4: Simple Ptides Example

A general execution strategy that is the basis for all execution strategies presented in this thesis was presented in [56]. Instead of reviewing the general execution strategy, a baseline execution strategy is described. This baseline strategy is similar to the general strategy, but it makes an explicit assumption about the selection of the dependency cut [17]. The dependency cut is used to separate the general strategy into two parts. Based on where the cut is defined, two different schemes are used to determine whether the event of interest can be causally affected by events inside and outside of the cut. Interesting readers can refer back to [56] for the definition of the dependency cut and its significance, however we only identified a single significant use of the cut, and that is the cut used in this thesis. This cut is defined at the "boundary" of the platform. By "boundary," we mean points at which communications (both input and output) with the outside of the platform occur. This output may include the rest of the distributed system or the physical environment, or both. Since each platform receives inputs from the outside through sensors and network input devices, we assume the cuts are always made at the real-time sensor and network input ports in the platform. Let us denote all these input ports as  $\mathbb{I}_p$ , where p is the platform in which these ports reside. Using Fig. 3.4 as an example,  $\mathbb{I}_p = \{n_1, s_1, s_2\}$ . This definition is used to separate the baseline strategy into two parts.

#### 3.3.1 Example Illustrating the Baseline Execution Strategy

Recall that the goal of the baseline strategy is to define whether an event of interest can be causally affected by other events in the system. We separate the baseline strategy into two parts, based on the location of the other events.

The first part checks for events outside of this platform. We again use Fig. 3.4 to demonstrate our strategy. Let  $e_2$  be our event of interest. Let the tag of this event be  $\tau_2$ . The first part of the strategy should return true if neither Sensor1 nor the Network Input can produce events arriving at the Computation1 with smaller tag.

Let's look at the bottom path from Sensor1 to Computation1, and assume real-time delay  $d_{s1}=0$  for now. Recall that a sensor relates model time and platform time by producing

events with a timestamp that is exactly equal to the platform time at which sensing occurred and a microstep 0. This implies that at a later platform time t, the sensor cannot produce an event of timestamp  $\tau < t$ . Thus we know after platform time  $\tau_2$ , Computation1 will not receive an event of timestamp smaller than  $\tau_2$  from Sensor1. If  $d_{s1} > 0$ , then Eq. 3.5 says an event of timestamp  $\tau$  will be produced at a platform time t no later than  $\tau + d_{s1}$  from the sensor. Thus we can modify our formulation to be: After platform time  $\tau_2 + d_{s1}$ , Computation1 will not receive an event of timestamp smaller than  $\tau_2$  from Sensor1.

The same holds for the path from the Network Input; the only difference is that model time delays  $\delta_1$  and  $\delta_2$  are present. This implies each event received at the Network Input will have its timestamp incremented by at least  $\delta_1 + \delta_2$  when it arrives at Computation1. Thus our formulation becomes: after platform time  $\tau_2 - \delta_1 - \delta_2 + d_n + \epsilon$ , Computation1 will not receive an event of timestamp smaller than  $\tau_2$  from Network Input.

Finally, notice we do not need to worry about any events sensed at Sensor2. This is because events produced by Sensor2 do not causally affect  $e_2$ ; i.e.,  $\delta(s_2, i_2) = \infty$ .

Combining the above formulations, we know events from outside of platform cannot causally affect  $e_2$  when platform time passes  $\max\{\tau_2 - \delta_1 - \delta_2 + d_n + \epsilon, \tau_2 + d_{s1}\}$ .

The second part of the baseline strategy checks to see whether any event from *inside* of the platform can causally affect the event of interest. Again take Fig. 3.4 for example. To determine whether  $e_2$  is safe-to-process, we need to check whether  $e_1$  will result in future events of smaller timestamp than  $e_1$  at the inputs of the Computation1 actor. Since the minimum model time delay between  $i_1$  and  $i_2$  is  $\delta_2$ , we can conclude  $e_1$  is safe to process if  $\tau_1 + \delta_2 > e_2$ , where  $\tau_1$  is the timestamp of  $e_1$ .

#### 3.3.2 Formal Definition for Baseline Execution Strategy

We now give a formal definition of the baseline strategy, but first we define a *physical-time* delay function  $d \colon I \to \mathbb{R}^+ \cup \{-\infty\}$  that maps each port  $p \in I$  as follows:

$$d(p) = \begin{cases} d_o & \text{if } p \text{ is a sensor input port,} \\ d_n + \epsilon & \text{if } p \text{ is a network input port,} \\ -\infty & \text{otherwise.} \end{cases}$$

Recall from Sec. 3.2 I is the set of actor input ports in this system. In other words, all inputs that are not sensor or network input ports have  $d(p) = -\infty$ . Notice the following strategy does not assume events are produced in tag order. In other words, for an event with timestamp  $\tau$  residing at input port i, there is still the possibility of another event of tag smaller than  $\tau$  arriving at i at a later platform time. Sec. 4.6 introduces a strategy that assumes events are produced in tag order. A formal definition of the baseline strategy is as follows:

**Baseline Strategy.** An event with timestamp  $\tau$  on platform f and on actor input port  $i \in I$  is safe to process when:

Part 1: platform time exceeds:

$$\tau + \max_{p \in \mathbb{I}_f, i' \in \mathbb{G}_i} \{ d(p) - \delta(p, i') \}, \tag{3.11}$$

and

Part 2: for each port  $p' \in I$  in platform f, each event at the input queue of p' has time stamp

1. greater than

$$\tau + \max_{i' \in \mathbb{G}_i} \{-\delta(p', i')\} \ if \ p' \notin \mathbb{G}_i. \tag{3.12}$$

2. greater than or equal to

$$\tau \ if \ p' \in \mathbb{G}_i. \tag{3.13}$$

Recall  $\mathbb{G}_i$  denotes the input port group for port i, while  $\mathbb{I}_f$  denotes the set of sensor and network input ports for platform f. Eq. 3.11 makes sure that no input port  $p \in \mathbb{I}_f$  (sensors and network inputs) will produce an event with timestamp greater than  $\tau$  at a later physical time. Note the second part of baseline strategy is again divided into two sections. Going back to the example in Fig. 3.4, Eq. 3.12 would check to see whether  $e_1$ ,  $e_3$  causally affects  $e_2$ , while Eq. 3.13 would check to see whether there exist events at other input ports of the Computation1 actor that causally affect  $e_2$ . If, say, the bottom input of Computation1 has another event of the same tag as  $e_2$ , then both events are safe-to-process, and Computation1 would consume both input events during the same firing.

Note this baseline strategy is very similar to **Strategy A** defined in [56]. The only difference is that strategies as presented in [56] ensures events are always *produced* in tag order, however this baseline strategy ensures that all events are *processed* in tag order. In Sec. 4.5, we generalize our strategies such that actors will *both* process inputs as well as produce outputs in tag order.

Finally, note the first part of the strategy (Eq.3.11) is enforced through a check of the tag of the event against the platform time subtracted by some offset, which is calculated statically. From now on we will be referring to this offset as the *delay-offset*. Also notice the inherent fault-tolerant property of Ptides, where the safety of an event execution is checked by comparing against platform time. This implies the execution of an event can never be stalled due to the absence of another event in the system. [13] showed an example that exploits this fault-tolerant property, and implemented a heart-beat detector that identifies system failures by simply observing for missed events. The safe-to-process analysis is used to identify the amount of platform time we need to wait before it is assured that fault has occurred.

# **Chapter 4**

# **Ptides Execution Strategies**

In this chapter a family execution strategies are presented, all of which are based on the baseline strategy as described in Chap. 3. In all cases, the first part of the strategies is the same as Part 1. of the baseline strategy, i.e., to ensure no events from outside of the platform can causally affect the event of interest, a comparison between the tag of the event of interest and platform time is performed. However, all strategies differ in the second part. By making certain assumptions about the system, and by making careful choices about the order of event executions, the second part of the baseline strategy can be simplified. We first describe an event ordering scheme used in discrete event simulation, and discuss how this ordering could simplify the strategies.

## 4.1 Event Ordering

In Ptides or DE, each platform maintains a pool of events. The schedulers analyze these events and determines which one to process. If these events are sorted in a particular order, the ordering could potentially simplify the scheduling analysis. The order we are interested in is a lexicographical ordering of the following tuple:  $\langle T, I, D \rangle$ , where  $T = \mathbb{R}$  represents the set of event timestamps.  $I = \mathbb{N}$  represents the set of events' microsteps, and  $D = \mathbb{N}$  represents the set of events' depths (explained below). For  $e_1 = \langle \tau_1, i_1, d_1 \rangle, e_2 = \langle \tau_2, i_2, d_2 \rangle$ , and  $e_1, e_2 \in \langle T, I, D \rangle$ , the ordering is defined as:

$$e_1 < e_2 \Leftrightarrow (\tau_1 < \tau_2) \lor$$

$(\tau_1 = \tau_2 \land i_1 < i_2) \lor$

$(\tau_1 = \tau_2 \land i_1 = i_2 \land d_1 < d_2)$

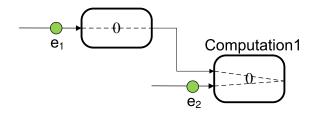

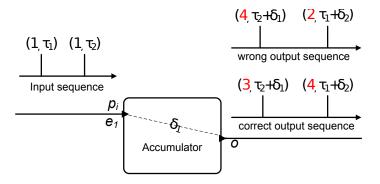

We have already introduced timestamp and microstep as the tag of an event, but in case two events have the same timestamp and microstep, there still might be a need to define an ordering between these events. An example is shown in Fig. 4.1. In this case, even if  $e_1$  and  $e_2$  have the same timestamps and microsteps,  $e_1$  still causally affects  $e_2$ . i.e.,  $e_1$  needs to be processed first, which results in an output event, call it  $e_1'$ . Computation1 can then process both  $e_1'$  and  $e_2$  during the same firing. To capture this property, actor "depths" are assigned through a topological sort algorithm [42].

From here on, we refer to this ordering as the *tag order* or *model time order*, where a tag is expanded to the tuple of < T, I, D >.

Figure 4.1: Ptides Example Showing Depth

The simple strategy, which we discuss now, assumes the platform maintains the events in tag order.

## 4.2 Simple Strategy

The simple strategy is based on the observation that the Part 2 (Eq. 3.12 and Eq. 3.13) of the baseline strategy's checks all events in the event queue, and ensures these events do not causally affect the event of interest. This operation is rather expensive. The complexity is of order O(n), where n is the maximum number of events in the event queue at any given time. To simplify this algorithm, we assume the event queue is sorted in the order described earlier. Since there is a total order for events within the system, and since all actors are assumed to be causal (see Sec. 3.1.2), we are assured no other events in the event queue can causally affect the earliest event (event with the smallest tag). Thus this strategy is simplified to:

**Simple Strategy.** For a platform f, the earliest event in the queue is safe-to-process when physical time exceeds:

$$\tau + \max_{p \in \mathbb{I}_f, i' \in \mathbb{E}_i} \{d(p) - \delta(p, i')\}$$

where i is the destination port of this event, and  $\tau$  is its timestamp.

As the formulation shows, the advantage of this strategy lies in its simplicity, where a single check against physical time is needed. Since the delay-offset can be calculated at compile time, the runtime does not need to access causality information of the model to determine whether an event is safe to process.

The disadvantage of this strategy is that it does not exploit concurrency in the model. Specifically, if the earliest event is not safe to process, the scheduler simply waits until physical time exceeds a value. During this time, the processor remains idle, even though there might be other events in the queue that are safe.

Note this strategy is similar to **Strategy C** presented in [56]. The only difference is that this strategy ensures events are *processed* in tag order, while **Strategy C** ensures events are *produced* in tag order.

### **4.3** Parallel Strategy

One way to avoid the unnecessary stall of event execution in the Simple Strategy is to not constrain ourselves to analyze the earliest event in the queue. However it would be nice if the Part 2 of the Baseline Strategy (Eq. 3.12 and 3.13) could be avoided as in the Simple Strategy case. Here we present an approach that achieves both goals.

Without loss of generality, we use Fig. 3.4 to demonstrate how one determines when events are safe to process. Let us assume for this case that **Sensor1** is broken and we cannot receive any events from it. Then using the baseline execution strategy (Eq. 3.11 to 3.13), we can determine  $e_1$  is safe to process if given a physical time t:

$$t > \tau(e_1) + d(n_1) - \delta_1 \tag{4.1}$$

and there is no other event in the same platform that causally affects  $e_1$ .

Following the same reasoning,  $e_2$  is safe to process if given a physical time t:

$$t > \tau(e_2) + d(n_1) - \delta_1 - \delta_2 \tag{4.2}$$

and there is no other event in the same platform that causally affects  $e_2$ .

Here  $\tau(e)$  gives the timestamp of the event.

For simplicity, let us also assume  $e_1, e_2$  are the only events in this platform. This means we can conclude  $e_2$  is safe to process if Eq. 4.2 is true and

$$\tau(e_2) \ge \tau(e_1) + \delta_2 \quad \text{is false;} \tag{4.3}$$

i.e.,  $e_1$  does not causally affect  $e_2$ , thus satisfying Part 2 of the baseline strategy.

Here we make a key observation:

**Lemma 1.** If  $e_1$  causally affects  $e_2$ , and the first part of the safe-to-process analysis as defined in the baseline strategy returns false for  $e_1$ , then it must return false for  $e_2$ .

In other words, we want to prove that if Eq. 4.3 is true, then Eq. 4.2 implies Eq. 4.1. The proof is simple:

Lemma 1 Proof. Since Eq. 4.3 is true, we replace  $\tau(e_2)$  in Eq. 4.2, and obtain

$$t > \tau(e_1) + \delta_2 - \delta_1 - \delta_2 + d(n_1)$$

which simplifies to Eq. 4.1.

Lemma 1 says if  $e_1$  causally affects  $e_2$ , then at all points of physical time, if there are potential events from outside of the platform that can causally affect  $e_2$ , then the same events will causally affect  $e_1$ . i.e., the first part of the strategy cannot be true for  $e_2$  unless it is true for  $e_1$ .

Armed with Lemma 1, we can scan the entire event queue, and a later event will not pass the physical time check unless all earlier events that causally affect it do so first.

Another way to look Lemma 1 is: Given the set of events in the system as the set E, let the set of events that satisfy Part 1 (Eq.3.11) of the baseline strategy be in  $E_s \subseteq E$ , then Lemma 1

proves that the second part of the strategy must be satisfied for the smallest event in  $E_s$ . Thus, the Parallel Strategy simply picks the smallest event in  $E_s$  to process.

Based on Lemma 1, we give the operational semantics of the Parallel Strategy. The Parallel Strategy makes two assumptions:

- 1. each platform has an event queue that is sorted by the order described in Sec. 4.1.

- 2. the earliest event in the queue that becomes safe-to-process is processed before events of larger tags. In the previous example, this means  $e_2$  is always processed before  $e_1$ , since it resides at the front of the event queue.

#### Parallel Strategy.

Step 1. Let e be the earliest event in the event queue for platform f.

Step 2. Say e resides at port i, and has timestamp  $\tau$ . If physical time exceeds

$$\tau + \max_{p \in \mathbb{I}_f, i' \in \mathbb{E}_i} \{ d(p) - \delta(p, i') \}$$

then e is safe to process, and it is processed. Otherwise, let e be the next sorted event in the queue, and repeat step 2.

Like the Simple Strategy, the Parallel Strategy is simplified to a simple check against physical time. Moreover, Parallel Strategy exploits parallelism inherent in the model, and never wastes processor cycles as long as a safe event exists, while the Simple Strategy may block the execution of other events if the smallest one is not safe to process.

## 4.4 Integrating Ptides with Earliest-Deadline-First

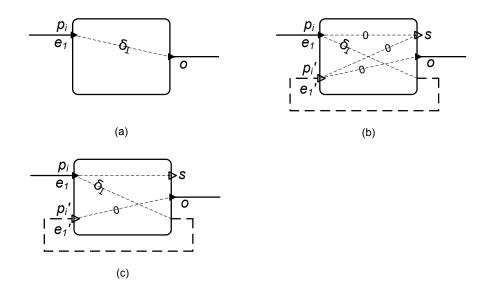

As we indicated before, the baseline strategy does not enforce any event ordering between system events. Both the Simple and Parallel Strategies optimize the scheduling algorithm by assuming an event ordering by model time. In this section we explore other possible priority orderings.

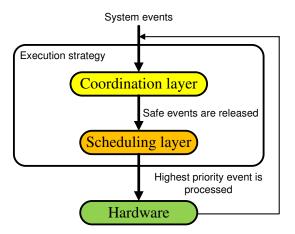

As Fig. 4.2 shows, we add another scheduling layer in addition to the safe to process analysis as defined in the baseline strategy. Here, the safe to process analysis is referred to as the *coordination layer*. This layer takes all events in the platform as inputs. When an event is declared safe to process, that event is "released" to the *scheduling layer*, which chooses among all released events, and picks one to process based on their priorities. The next question is, what kind of scheme should be implemented in the scheduling layer?

A natural choice is the famous earliest-deadline-first (EDF) scheme, where the scheduling layer would simply pick the event of earliest deadline to process. This makes it possible for Ptides schedulers to take advantage of some of the interesting properties of the previously studied real-time scheduling scheme, such as EDF's optimality with respect to feasibility [47].

The EDF algorithm contains a notion of "release times," which is the physical time at which this event becomes available to process in the system. By integrating Ptides with EDF, we simply define the release time of an event as the physical time at which that event becomes *safe-to-process*. In addition, traditional EDF scheme assumes the programmer would statically annotate

Figure 4.2: Two Layer Execution Strategy

deadlines for each system task. By integrating EDF with Ptides, the deadlines of system events are inferred from timed semantics. We define these deadlines next.

#### 4.4.1 Ptides Execution Strategies with Model-Time-Based Deadline

The execution strategy we present in this section uses model times to calculate deadlines for system events. This carefully chosen set of deadlines allows a simple safe-to-process analysis, while enabling earliest-deadline-first processing, exploiting model parallelism, and guarantying Ptides semantics.

#### **Deadline Calculation**

The deadline calculation presented in this subsection is only dependent on model times delays, while making no use of execution times. The deadline of an event is defined by how "far away" the event of interest is from the nearest actuator.

To understand how deadlines are defined, recall that events arriving at actuator and network output ports have deadlines associated with them, where the timestamp of the event is effectively the deadline. Thus for any any event e that is  $\delta$  model time away from the nearest actuator or network output, the deadline of e is  $\tau(e) + \delta$ , where  $\tau(e)$  is the timestamp of e. Take Fig. 4.3 as an example, the deadline for  $e_1$  is  $\tau(e_1) + \delta_1$ , where the closest actutor/network output port is  $i_1$ , and the delay between  $i_2$  and  $i_1$  is  $\delta_1$ .

To aid the deadline calculation for events, we define a relative deadline for each actor input port. This relative deadline captures the minimum model time delay between the input port and its reachable actuator/network output ports. In the previous example,  $rd(i_1) = 0$ ,  $rd(i_2) = \delta_1$ .

The relative deadline for each input port can be calculated with a simple shortest path algorithm starting from each input port of actuators, and traversing backwards until the entire graph is visited. Here ports are nodes, and connections between actors as well as causality relationships within actors are edges. By default, any connection between actors has a weight of zero, while the

Figure 4.3: Deadline Calculation Through Model Time

model time delays between input and output actor ports are weights on those edges. The shortest path algorithm annotates relative deadlines for each node that is an input port.

With the definition of relative deadlines, the absolute deadline of an event can be written as:

$$AD(e) = \tau(e) + rd(port(e))$$

Here, AD(e) is the absolute deadline of an event e,  $\tau(e)$  is the tag of e, port(e) is the destination input port of e, and rd(port(e)) is the relative deadline at port(e). Next, we define a new event ordering based on the absolute deadlines.

#### 4.4.2 Event Ordering with Deadlines

The new event ordering is based on the one presented in Sec. 4.1, yet adds one more element into the event tuple. The order we are interested in is a lexicographical ordering of the following tuple:  $\langle AD, T, I, D \rangle$ , where again T, I, D are the sets of timestamps, microsteps, and depths.  $AD = \mathbb{R}$ , represents the set of absolute deadlines. For  $e_1 = \langle ad_1, \tau_1, i_1, d_1 \rangle, e_2 = \langle ad_2, \tau_2, i_2, d_2 \rangle$ , and  $e_1, e_2 \in \langle AD, T, I, D \rangle$ , the ordering is defined as:

$$e_1 < e_2 \Leftrightarrow (ad_1 < ad_2) \lor$$

$$(ad_1 = ad_2 \land \tau_1 < \tau_2) \lor$$

$$(ad_1 = ad_2 \land \tau_1 = \tau_2 \land i_1 < i_2) \lor$$

$$(ad_1 = ad_2 \land \tau_1 = \tau_2 \land i_1 = i_2 \land d_1 < d_2).$$

This event ordering is used in our later strategies.

#### **Strategy using Model Time Deadlines**

Earlier in this section we introduced a two-layer scheduling strategy. If applied to this case, the baseline strategy can be used as the coordination layer and the event ordering with deadlines can be used to select the earliest deadline event among all those that are safe. However this approach is relatively expensive. Our goal in this section is to simplify this algorithm.

Recall from Sec. 4.3, we proved that if both  $e_2$  and  $e_1$  reside in the same platform, and if  $e_2$  causally affects  $e_1$ ,  $e_1$  will not pass the physical time check for safe-to-process at an earlier platform time than  $e_2$ . Moreover,  $e_2$  is placed at an earlier position than  $e_1$  in an event queue sorted

Figure 4.4: Deadline Example