### UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Accelerating Irregular Applications Using Latency Masking Multithreaded Techniques

Permalink https://escholarship.org/uc/item/62428630

Author Budhkar, Prerna

Publication Date 2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

### Accelerating Irregular Applications Using Latency Masking Multithreaded Techniques

### A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Prerna Budhkar

September 2018

Dissertation Committee:

Dr. Walid Najjar, Chairperson Dr. Vassilis Tsotras Dr. Laxmi Bhuyan Dr. Rajiv Gupta

Copyright by Prerna Budhkar 2018 The Dissertation of Prerna Budhkar is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

The pursuit of Ph.D. has been a period of fruitful learning experience for me, not only in the academic arena, but also on a personal level. I would like to reflect on the many people who have supported and helped me to become who I am today. First and foremost, I would like to thank my advisor, **Dr. Walid Najjar**. He has given my research a direction and a push at every step. Throughout these five years, he has been supportive of me in every situation, academic or otherwise.

I would also like to express my gratitude to **Dr. Vassilis Tsotras**. His technical and editorial advice has been invaluable to my research. I have always felt comfortable in approaching him with the silliest of my doubts.

I would like to thank my other dissertation committee members, Dr. Rajiv Gupta and Dr. Laxmi Bhuyan for taking their time to review this dissertation.

During graduate school, I have met many wonderful fellow graduate students and friends whom I am grateful to. Skyler Windh is a great friend and is always warm and welcoming when I approached him with ideas and problems. I really admire the way he is able to cut through red tape and accomplish what needs to be done. Jose Rodriguez, thank you for being a patient friend. Our long technical discussions have saved me tons of time in my projects.

Graduate school is a long journey that sometimes suddenly hits you the hardest when things don't go your way. I feel very grateful for the many friends who were there to help me grind through it. Thank you *Sayali, Vidya and Divya* for keeping a check on me all the time. Finally, thank you *Jason Ott* for being such a good friend. Our evening walks back home and the discussion about life and philosophy were the best part of my day.

I would like to thank my family for their enormous support and sacrifices that they made. My grandmother, *Aaji*, has been a pillar of support throughout my life. I am grateful to her strong belief in education. My mother, *Aai*, has always been there kindly supporting me with unwavering love. I owe all of my success to these two strong women in my life. I would like to thank my grandfather, *Aajoba*, for his love and support. I am still stumped by my father, *Baba*, for nonchalantly trusting me with all my life decisions - thank you. Thanks to my brother, *Vaibhav*, who is always available to talk to me at any hour of the day. I am also forever indebted and grateful to my in-laws for their love, understanding and constant prayers. Also, special thanks to my extended family: *Aaji*, *Ajoba*, *Smita Aatya*, *Ramesh Kaka, Jyotsna Aatya, Anant Kaka, Mama and Mami*. You have always stood by us in good and bad times. Thanks to all my cousins for keeping me connected to the family back in India.

None of this would have been possible without the unconditional love, co-operation and belief from my better-half, *Vineet*, for understanding and putting up with me through my grad-student life of classes, publications, accepts, rejects, missing out on family and the many, many little pleasures. I hope to make it up to you!

Finally, this thesis contains one of my previously publish works. This work is included in Chapter 3 of this thesis. The full citation is:

Ildar Absalyamov, Prerna Budhkar, Skyler Windh, Robert J. Halstead, Walid A. Najjar, and Vassilis J. Tsotras. 2016. FPGA-accelerated group-by aggregation using synchronizing caches. In Proceedings of the 12th International Workshop on Data Management on New Hardware (DaMoN '16). ACM, New York

To my parents for all the support.

### ABSTRACT OF THE DISSERTATION

### Accelerating Irregular Applications Using Latency Masking Multithreaded Techniques

by

Prerna Budhkar

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2018 Dr. Walid Najjar, Chairperson

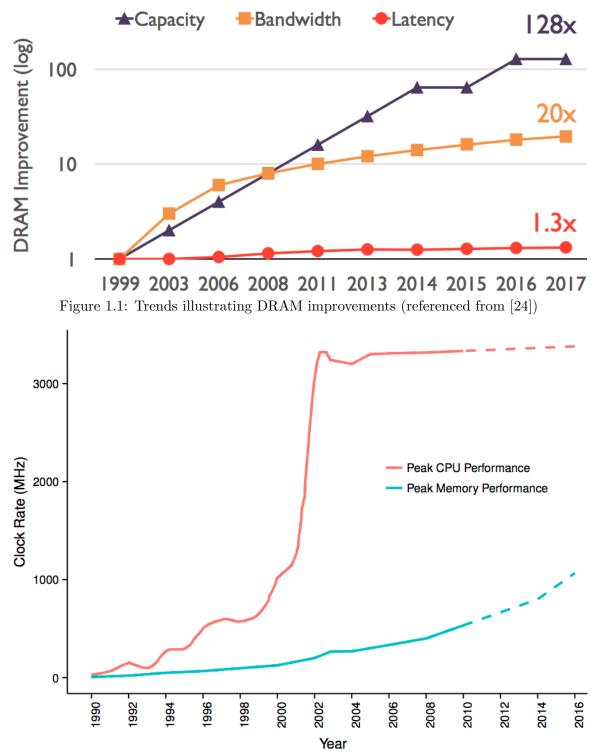

The last two decade has witnessed two opposing hardware trends where the DRAM capacity and the access bandwidth has rapidly increased by 128x and 20x respectively. In stark contrast with capacity and bandwidth, DRAM latency has almost remained constant, reducing by only 1.3x in the same time frame. Therefore, long memory latency continues to be a critical performance bottleneck in modern systems. Another emerging trend is the stagnating processor clock speeds due to the end of Dennard scaling. Parallel architectures, like CPUs and GPUs, resolved this problem by increasing parallelism, but developed architectures that rely extensively on *data locality* in the form of large cache hierarchies for multicores, and vectorized execution for SIMD-enabled CPUs and GPUs.

At the same time, many data-intensive applications are moving away from data locality towards irregular memory access behavior. This behavior is observed either because of dataflow (caused by indirection in data access) or control flow (caused by branch instructions) irregularity. Such applications are often memory bound and their performance is primarily determined by the memory latency (also known as the memory wall). An alternative approach to mask long memory latencies is by using *multithreaded* execution where a running thread relinquishes execution to a ready thread as soon as it performs a long-latency memory access. This dissertation explores how custom hardware accelerators using memory masking multithreaded techniques can be used to improve performance of irregular applications. In hardware multithreaded designs thread states are maintained on-chip, and with enough application parallelism they can fully mask memory latency without storing data in caches.

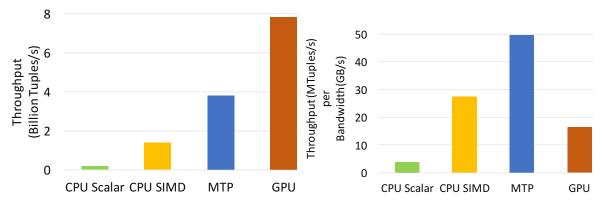

This thesis explores latency masking hardware multithreading on three different applications to achieve better performance on irregular applications. The first two applications, namely selection and group-by aggregation are relational database operators. The selection operator examines different conditions on various row attributes. Depending on the evaluation, a row is either qualified or disqualified. This operator, therefore, exhibits a control flow irregularity. The proposed selection design shows an improvement of 1.8x over CPU Similarly, it is 3.2x more bandwidth efficient than GPUs. Overall, this dissertation provides the first direct comparison study of selection operator on all three architectures. The group-by aggregation, on the other hand, is a hash-based implementation that exhibits dataflow irregularity. Results show that the FPGA-accelerated approach significantly outperforms CPU-based implementations and yields speedup up to 10x. The third application considered for evaluation is a popular sparse linear algebra operation namely *Sparse Matrix and Vector multiplication* (SpMV). Our results show that the multithreaded SpMV implementation achieves up to 95% of the theoretical upper bound performance whereas GPUs, like Titan GV100, can achieve upto 69% of its peak performance.

## Contents

| List of Figures |                |                                                   |    |  |  |  |

|-----------------|----------------|---------------------------------------------------|----|--|--|--|

| List of Tables  |                |                                                   |    |  |  |  |

| 1               | Inti           | roduction                                         | 1  |  |  |  |

| <b>2</b>        | $\mathbf{Rel}$ | ated Work                                         | 8  |  |  |  |

|                 | 2.1            | Reconfigurable and Heterogeneous Architectures    | 9  |  |  |  |

|                 | 2.2            | Multithreaded Architectures                       | 10 |  |  |  |

|                 |                | 2.2.1 Latency Masking Multithreaded Architectures | 12 |  |  |  |

|                 |                | 2.2.2 Custom Multithreaded Architecture           | 13 |  |  |  |

|                 |                | 2.2.3 Convey HC-2ex: Target Platform              | 15 |  |  |  |

|                 | 2.3            | Query Processing on FPGAs                         | 18 |  |  |  |

|                 |                | 2.3.1 Group-by Aggregation                        | 20 |  |  |  |

|                 |                | 2.3.2 Selection Scan Operator                     | 24 |  |  |  |

|                 | 2.4            | Sparse Matrix-Vector Multiplication               | 28 |  |  |  |

|                 |                | 2.4.1 Sparse Matrix Formats                       | 29 |  |  |  |

|                 |                | 2.4.2 GPU Approaches                              | 32 |  |  |  |

|                 |                | 2.4.3 FPGA Approaches                             | 33 |  |  |  |

| 3               | Mu             | ltithreaded Group-by Aggregation                  | 35 |  |  |  |

|                 | 3.1            | Using CAMs on FPGA                                | 36 |  |  |  |

|                 | 3.2            | Aggregation Engine Workflow on FPGA               | 38 |  |  |  |

|                 | 3.3            | FPGA design and Optimizations                     | 41 |  |  |  |

|                 | 3.4            | Evaluating Group-by Aggregation                   | 43 |  |  |  |

|                 |                | 3.4.1 Software Implementations                    | 43 |  |  |  |

|                 |                | 3.4.2 Throughput Evaluation                       | 45 |  |  |  |

|                 |                | 3.4.3 Merge Overhead on FPGA                      | 48 |  |  |  |

|                 |                | 3.4.4 Performance Analysis                        | 50 |  |  |  |

|                 | 3.5            | FPGA Area Utilization                             | 50 |  |  |  |

|                 | 3.6            | Conclusion                                        | 51 |  |  |  |

| <b>4</b>     | Mu  | ltithreaded Selection Operator                     | <b>53</b> |  |  |

|--------------|-----|----------------------------------------------------|-----------|--|--|

|              | 4.1 | MTP Selection Engine                               | 54        |  |  |

|              |     | 4.1.1 Engine Design                                | 54        |  |  |

|              |     | 4.1.2 Engine Workflow                              | 56        |  |  |

|              |     | 4.1.3 MTP Performance Analysis                     | 57        |  |  |

|              | 4.2 | Evaluating Selection Operator                      | 63        |  |  |

|              |     | 4.2.1 Throughput Evaluation                        | 63        |  |  |

|              |     | 4.2.2 Throughput Efficiency                        | 66        |  |  |

|              |     | 4.2.3 Multithreaded Execution of Selection         | 68        |  |  |

|              |     | 4.2.4 TPC-H Query Evaluation                       | 69        |  |  |

|              |     | 4.2.5 Datalayout Independence                      | 72        |  |  |

|              |     | 4.2.6 Power Utilization                            | 74        |  |  |

|              | 4.3 | FPGA Area Utilization                              | 75        |  |  |

|              | 4.4 | Conclusion                                         | 76        |  |  |

| <b>5</b>     | Spa | urse Matrix and Vector Multiplication              | 78        |  |  |

|              | 5.1 | SpMV Architecture Overview                         | 79        |  |  |

|              | 5.2 | Performance Bound                                  | 82        |  |  |

|              | 5.3 | Experimental Results                               | 85        |  |  |

|              |     | 5.3.1 Experimental Setup                           | 85        |  |  |

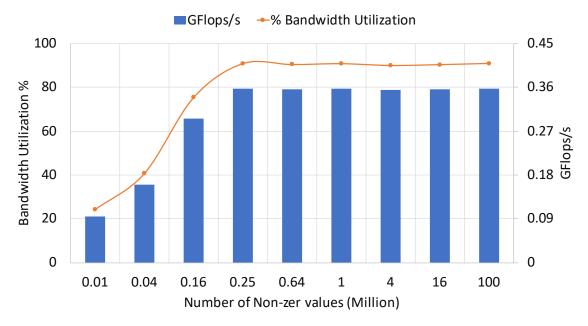

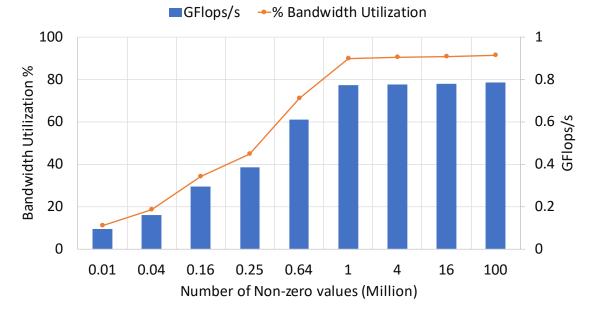

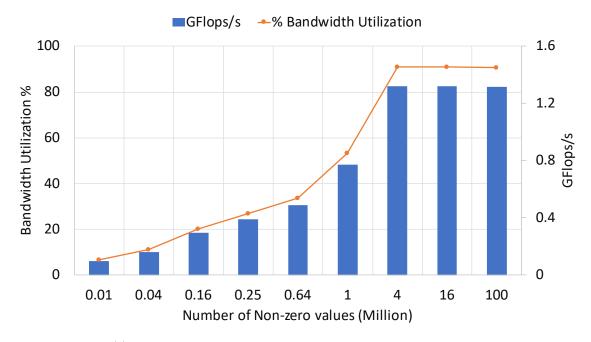

|              |     | 5.3.2 NNZ Vs Sustained Bandwidth                   | 87        |  |  |

|              |     | 5.3.3 Performance Evaluation of Multithreaded SpMV | 92        |  |  |

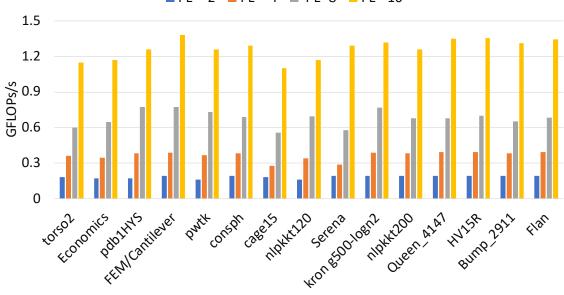

|              |     | 5.3.4 Performance Comparison to GPUs               | 95        |  |  |

|              |     | 5.3.5 Scalability                                  | 99        |  |  |

|              |     | 5.3.6 Existing FPGA-based SpMV Accelerators        | 100       |  |  |

|              | 5.4 | Conclusion                                         | 101       |  |  |

| 6            | Con | nclusions                                          | 103       |  |  |

| Bibliography |     |                                                    |           |  |  |

# List of Figures

| 1.1 | Trends illustrating DRAM improvements (referenced from [24])                                                                                                                                                                       | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

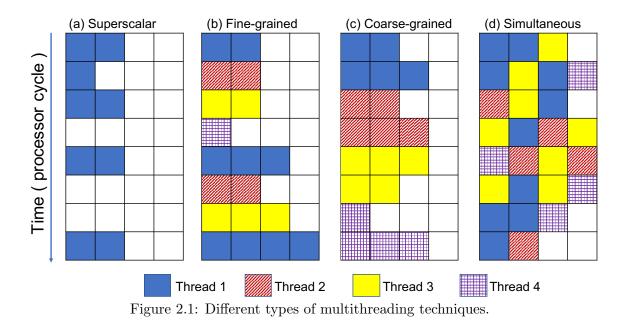

| 1.2 | Trends illustrating peak clock rate for memory access and the CPU perfor-<br>mance (referenced from [15])                                                                                                                          | 2  |

|     | $\operatorname{Hance}\left(\operatorname{referenced}\operatorname{Hom}\left[15\right]\right) \ldots \ldots$ | 2  |

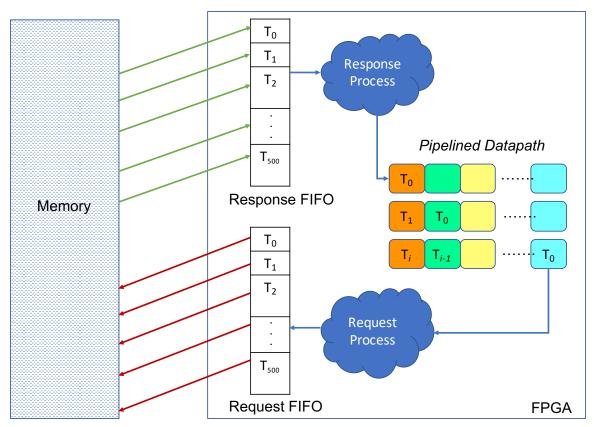

| 2.1 | Different types of multithreading techniques.                                                                                                                                                                                      | 11 |

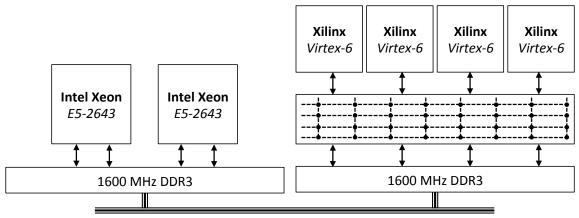

| 2.2 | Custom Multithreaded Architecture                                                                                                                                                                                                  | 14 |

| 2.3 | The Convey HC-2ex architecture is divided into software and hardware re-                                                                                                                                                           |    |

|     | gions as shown in (a). Each FPGA has 8 memory controllers, which are split                                                                                                                                                         |    |

|     | into 16 channels for the FPGA's logic cells as shown in (b)                                                                                                                                                                        | 16 |

| 2.4 | Example matrix                                                                                                                                                                                                                     | 29 |

| 2.5 | Coordinate Sparse Matrix Format                                                                                                                                                                                                    | 30 |

| 2.6 | Compressed Sparse Row (CSR) Matrix Format                                                                                                                                                                                          | 30 |

| 2.7 | ELLPACK sparse matrix format                                                                                                                                                                                                       | 31 |

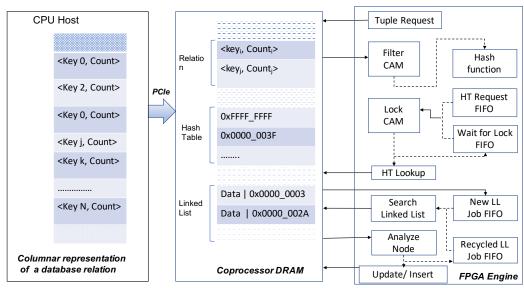

| 3.1 | Engine Internal Blocks.                                                                                                                                                                                                            | 38 |

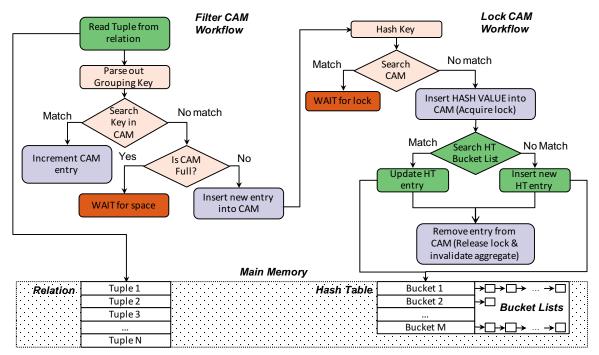

| 3.2 | A state diagram for jobs in the aggregation engine                                                                                                                                                                                 | 39 |

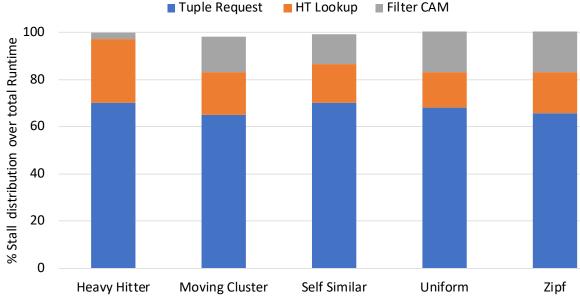

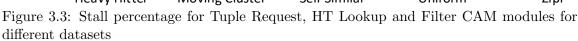

| 3.3 | Stall percentage for Tuple Request, HT Lookup and Filter CAM modules for                                                                                                                                                           |    |

|     | different datasets                                                                                                                                                                                                                 | 41 |

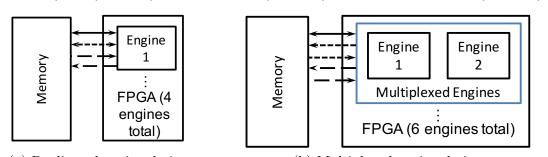

| 3.4 | Alternative engine placement strategies on a single FPGA with 16 memory                                                                                                                                                            |    |

|     | channels                                                                                                                                                                                                                           | 43 |

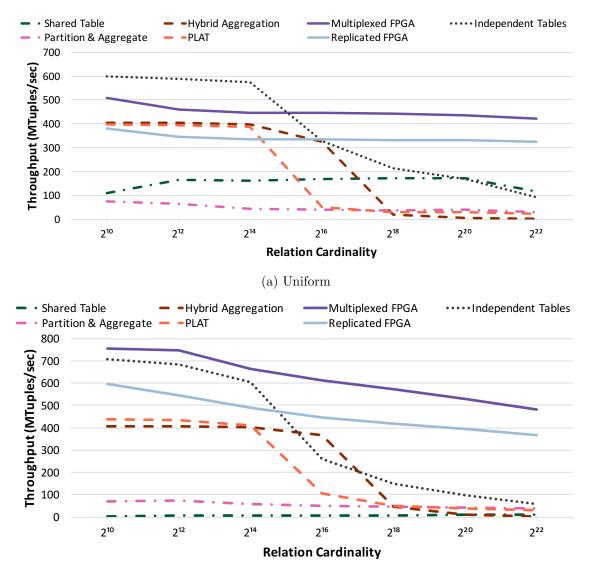

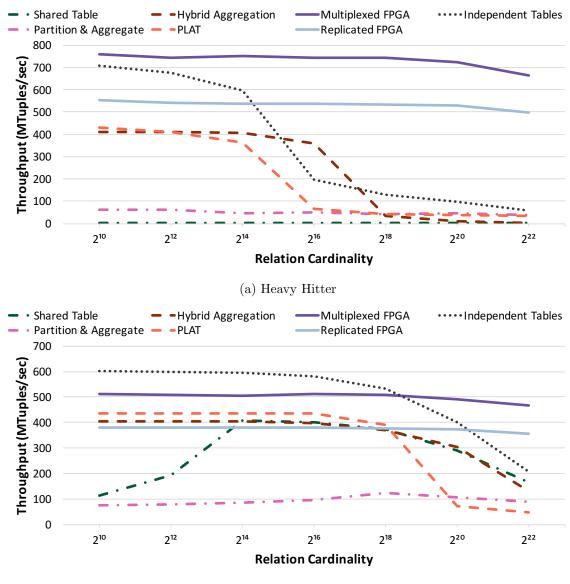

| 3.5 | Aggregation throughput of hardware and software approaches for datasets                                                                                                                                                            |    |

|     | with $256M$ tuples.                                                                                                                                                                                                                | 46 |

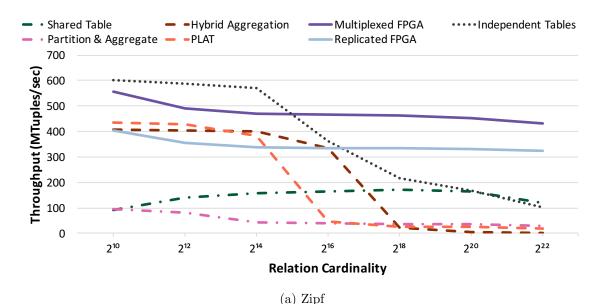

| 3.7 | Aggregation throughput of hardware and software approaches for datasets                                                                                                                                                            |    |

|     | with $256M$ tuples.                                                                                                                                                                                                                | 48 |

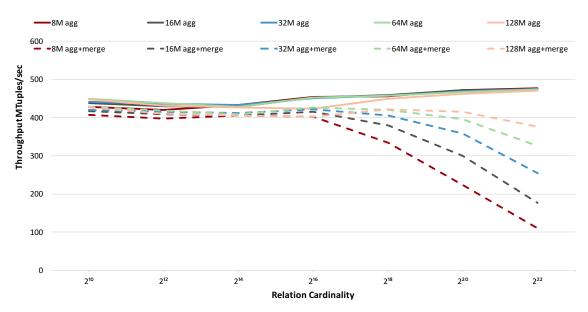

| 3.8 | Effect of varying relation sizes on the FPGA aggregation throughput for                                                                                                                                                            |    |

|     | datasets with Uniform key distribution. Solid lines represent throughput of                                                                                                                                                        |    |

|     | the aggregation step (without merge operation), while dashed lines represent                                                                                                                                                       |    |

|     | end-to-end (aggregation followed by the merge) throughput                                                                                                                                                                          | 49 |

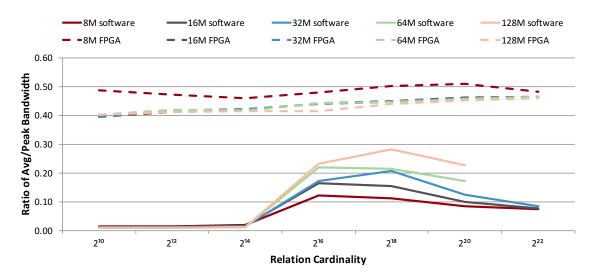

| 3.9 | Ratio of average effective memory bandwidth to peak theoretical bandwidth                                                                                                                                                          |    |

|     | achieved by the Independent Tables software algorithm and the Multiplexed                                                                                                                                                          |    |

|     | FPGA design for varying dataset sizes and key cardinalities                                                                                                                                                                        | 49 |

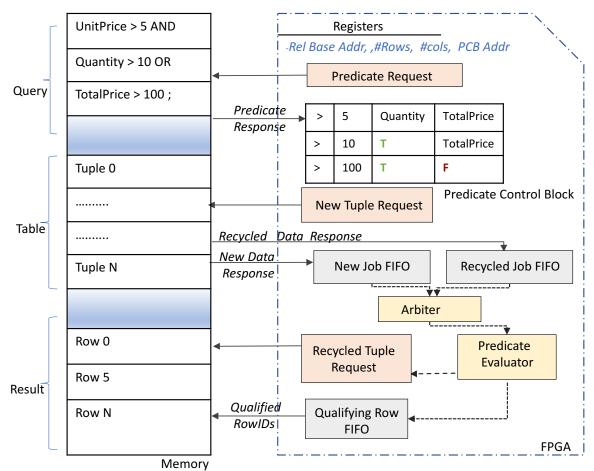

| 4.1  | Figure (a) represents the sample SQL query which is used as an example query in this section. Figure (b) present the corresponding <i>predicate control</i> |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | block (PCB) for the sample query                                                                                                                            | 55  |

| 4.2  | Selection Accelerator Engine: showing different building blocks and memory channels that read/write from memory                                             | 56  |

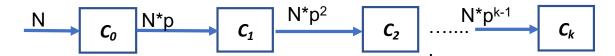

| 4.3  | Number of qualified rows after each predicate for a conjunctive query. $N$                                                                                  | 50  |

| 4.0  | is the total number of rows, $p$ is a predicate probability, $C_0, C_1, C_2,, C_k$                                                                          |     |

|      | designate $k$ different predicates                                                                                                                          | 59  |

| 4.4  | Number of qualified rows after each predicate for a disjunctive query. $N$ is the                                                                           |     |

|      | total number of rows, p is a predicate probability, $C_0, C_1, C_2, \dots, C_k$ designate                                                                   |     |

|      | k different predicates                                                                                                                                      | 61  |

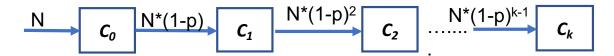

| 4.5  | Variance in predicate probability with respect to selectivity for conjunctive                                                                               |     |

|      | (a) and disjunctive(b) query.                                                                                                                               | 62  |

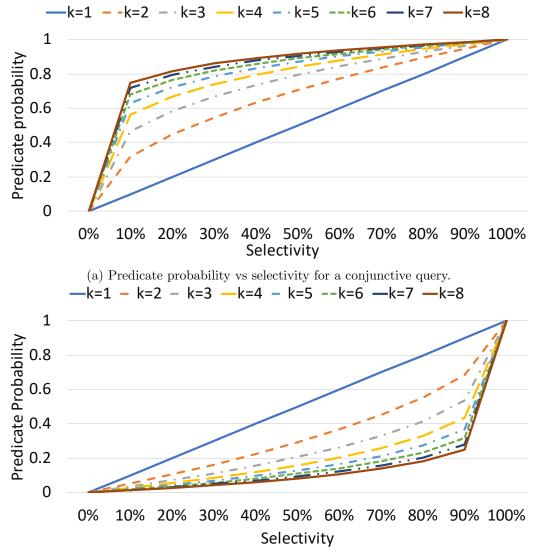

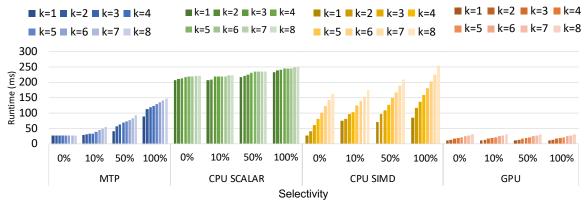

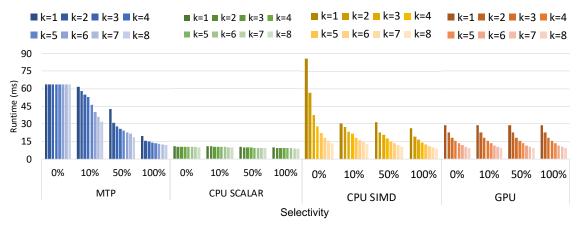

| 4.6  | Query evaluation runtime measured on MTP, CPU and GPU with varying                                                                                          |     |

|      | selectivity and number of predicates                                                                                                                        | 64  |

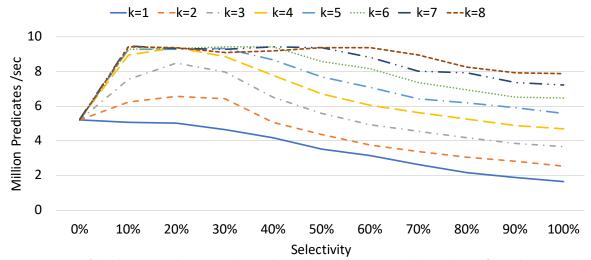

| 4.7  | Throughput achieved by MTP, CPU and GPU implementation normalized                                                                                           |     |

|      | to their respective bandwidth. Note that the legend description is same as                                                                                  |     |

|      | that of Figure 4.6.                                                                                                                                         | 64  |

| 4.8  | Absolute attributes evaluated as the selectivity and number of predicates are                                                                               |     |

|      | varied for (a) conjunctive                                                                                                                                  | 68  |

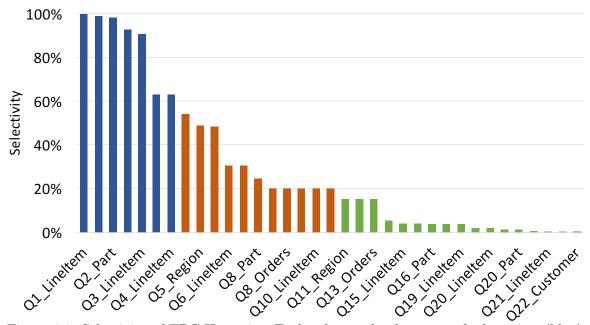

| 4.9  | Selectivity of TPC-H queries. Each color marks the range of selectivity:                                                                                    |     |

|      | (blue) above $60\%$ , (orange) $50\%$ - $20\%$ , (green) below $10\%$ .                                                                                     | 70  |

| 4.10 | TPC-H Query6                                                                                                                                                | 70  |

| 4.11 | TPC-H query Q6 performance evaluation                                                                                                                       | 71  |

| 4.12 | Performance comparison of the CPU and the MTP implementations with                                                                                          |     |

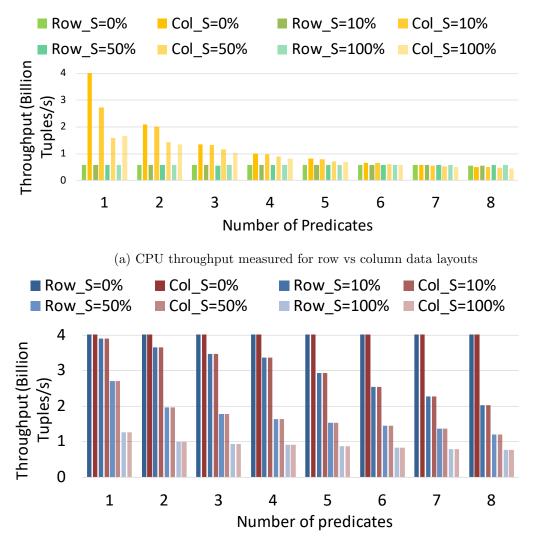

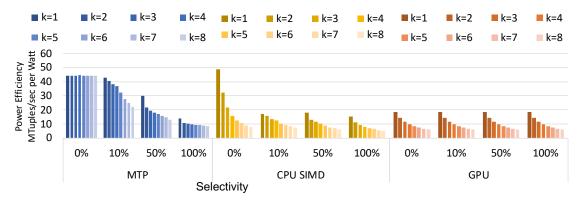

|      | row-major and columnar data layouts.                                                                                                                        | 73  |

| 4.13 | Comparison of Power Efficiency on MTP, CPU and GPU systems                                                                                                  | 74  |

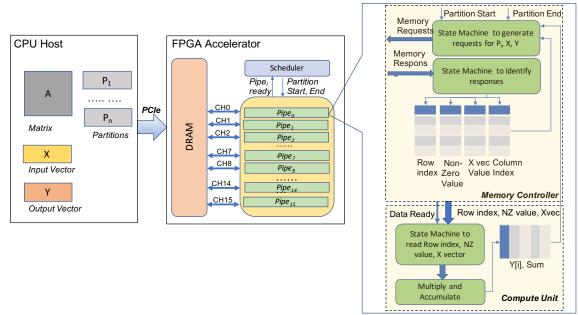

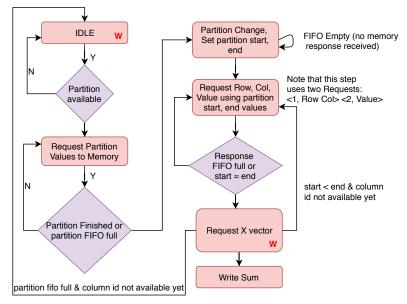

| 5.1  | SpMV design on FPGA.                                                                                                                                        | 79  |

| 5.2  | Memory controller state machine                                                                                                                             | 80  |

| 5.3  | Minimum number of non zeros as number of engines (channels) are increased                                                                                   | 89  |

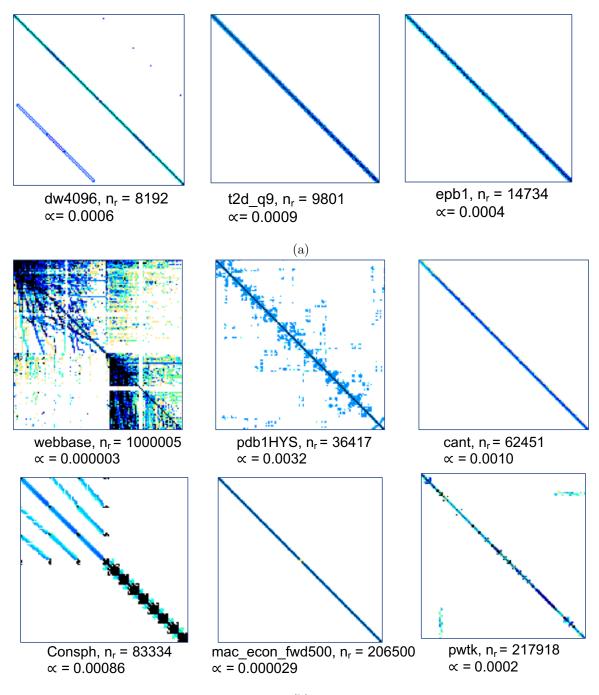

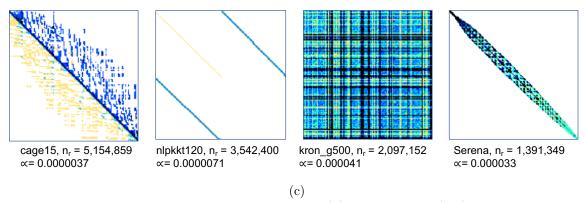

| 5.4  | Sparse matrix structure for (a) Group 1 and (b,c) Group2                                                                                                    | 92  |

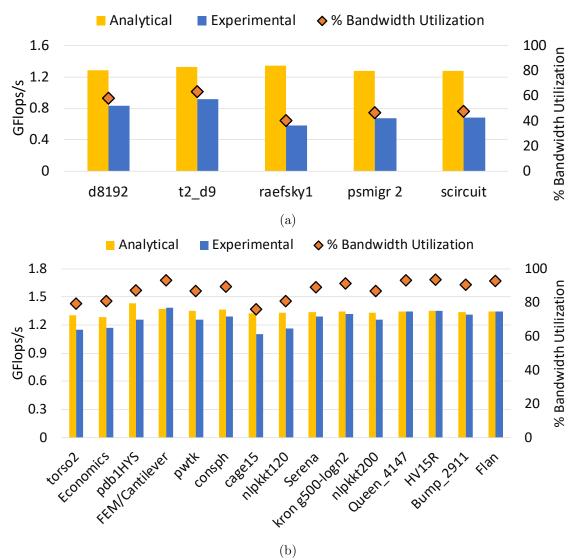

| 5.5  | Analytical and Experimental Performance Comparison for Group 1 and Group 2 sparse matrices                                                                  | 93  |

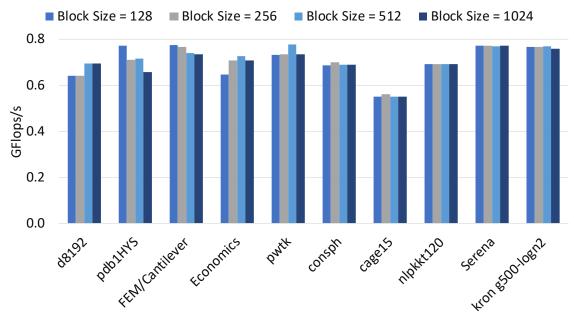

| 5.6  | Effect of block size on the achieved SpMV performance when ran with 8 PEs.                                                                                  | 00  |

| 0.0  | As long as number of partitions $\gg$ than number of PEs, the block size does                                                                               |     |

|      | not affect the performance                                                                                                                                  | 95  |

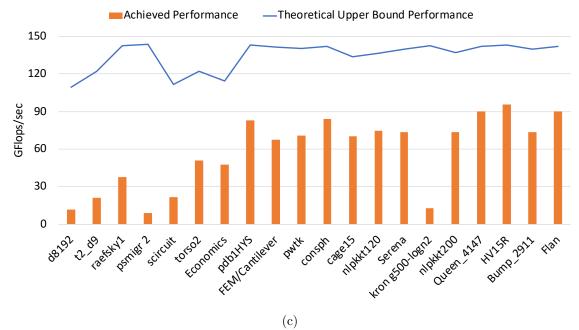

| 5.7  | Comparison between the achieved and the theoretical upper bound perfor-                                                                                     |     |

| -    | mance for (a) multithreaded SpMV (b) Tesla K40 (c) Titan GV100.                                                                                             | 98  |

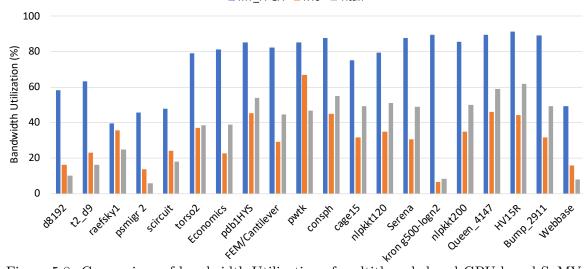

| 5.8  | Comparison of bandwidth Utilization of multithreaded and GPU-based SpMV                                                                                     |     |

|      | implementation                                                                                                                                              | 99  |

| 5.9  | SpMV performance scaling with number of PEs                                                                                                                 | 100 |

## List of Tables

| 3.1 | Contents of the Filter CAM, Lock CAM and HashTable (HT) and modifica-            |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | tions altering all of them, while relation with the following keys is processed: |     |

|     | A, C, A, B, A. Assume hash(A)=hash(C). Initially both CAMs are empty.            |     |

|     | Filter CAM maintains the occurrence of duplicate keys, while Lock CAM            |     |

|     | locks the hash bucket, holding the bucket list's head pointer                    | 40  |

| 3.2 | FPGA resource utilization for aggregation engines.                               | 51  |

| 4.1 | Query and input relation parameters used in the analytical model $\ldots$ .      | 58  |

| 4.2 | Summary of relationships between $S, k, W_e$ and $W_{wr}$                        | 61  |

| 4.3 | System Configuration of different architectures used for evaluation              | 63  |

| 4.4 | Performance Evaluation of TPC-H query Q6 on CPU, GPU and MTP im-                 |     |

|     | plementations.                                                                   | 71  |

| 4.5 | FPGA area utilization for the selection engine                                   | 75  |

| 5.1 | FPGA resource utilization for SpMV engines.                                      | 87  |

| 5.2 | Benchmarks used for performance evaluation of multithreaded SpMV design          | 90  |

| 5.3 | Prior FPGA-based SpMV designs and implementation. '*' and '**' presents          |     |

|     | Group 1 and Group 2 data respectively                                            | 101 |

|     |                                                                                  |     |

### Chapter 1

## Introduction

The main factors influencing in-memory processing performance are the high DRAM latency and the growing gap between the memory bandwidth and the speed of the processing unit aka, the memory wall. The performance bottleneck due to high DRAM latency becomes more evident by observing the historical trends of DRAM-chip. The work presented in [24] illustrates the historical trends of DRAM-chip. As shown in Figure 1.1, DRAM-based main memory has made rapid progress on capacity and bandwidth, improving 128x and 20x respectively over the past two decades. These improvements mainly follow Moore's Law and Dennard Scaling, which enable more and faster transistors along with more pin. On the contrary, DRAM latency has improved (i.e., reduced) by only 1.3x, a negligible change compared to changes in DRAM capacity and bandwidth during the same time period. As a result, long DRAM latency remains as a significant system performance bottleneck for many modern applications such as in-memory databases [71, 14, 66, 84], graph traversals [28, 82, 89] and Google's datacenter workloads [51].

Figure 1.2: Trends illustrating peak clock rate for memory access and the CPU performance (referenced from [15])

The second major performance issue, as mentioned before, is the growing gap between the memory bandwidth and the speed of the processing unit, the so-called 'memory wall'. The term "memory wall" was coined in [88] by Wulf and McKee in 1995. They predicted that the growing disparity between processor and the memory speed would, in the future, lead to a situation where memory access time will outweigh any performance improvements in the processor. The aforementioned behavior was more accurately modeled using Equation 1.1 that calculates the average memory access time. In this equation  $t_c$  and  $t_m$  are the cache and DRAM access times and p is the probability of cache hit.

$$t_{avg} = p * t_c + (l - p) * t_m \tag{1.1}$$

Wulf and McKee showed that greater the divergence between  $t_c$  and  $t_m$ , longer is the memory access time. Memory references eventually dominate the overall system performance and further improvements to CPU performance will have no impact.

A decade after the original paper was published, McKee reflected upon their predictions in [59]. They reported that some commercial applications such as transaction processing workloads were seeing 65% processor idle times and scientific computing applications were suffering from memory bottlenecks with up to 95% node idle times. Much of this behavior was observed because of the memory bottlenecks where the processor was stalled waiting for data to be returned from memory. It was obvious that handling off-chip memory accesses would become critical in achieving better system performance. This growing gap between the processor and the memory is also depicted in Figure 1.2(taken from [15]). It can be seen that even though the CPU growth halted at around 2003, the memory speed has a lot to catch up. Modern processors can now generate 3 orders of magnitude more requests than the memory architectures can fulfill. This high request rate coupled with long access latencies means that processors spend the majority of their time idle.

The problem of high DRAM latency and the memory wall is more important for multicore CPUs given their higher clock speeds. Multicore CPUs addressed this problem by introducing large *cache hierarchies* that rely on data locality. Caches leverage the spatial and temporal locality within an application to reduce the number of requests back to main memory. Temporal locality exists when a data that is currently accessed by an application is very likely to be accessed again. Similarly, spatial locality exists if a piece of data that has been accessed recently, it is likely that the adjacent pieces of data will be accessed in the near future. Caches exploit these properties to keep values closer to the processing core where the latency is much lower. Hardware accelerators, such as FPGAs and GPUs, deal differently with long memory latencies. FPGA based accelerators rely, mostly, on streamed data; hence the latency cost is paid once for the first element. GPUs on the other hand, offer a different solution leveraging on massive SIMD parallelism and high bandwidth specialized memory (i.e. GDDR). However these architectural solutions still inherently rely on data locality.

The aforementioned locality based solutions work well for many applications, but there exists an important category of applications that do not work well on caches. We call them irregular applications and by definition they have poor locality. There are two measures of irregularity: (1) *Dataflow irregularity* is caused by the indirection in the data access, leading to cache misses. Example applications include sparse linear algebra, hashing based applications etc; (2) *Control flow irregularity* is caused by the dynamic control flow and leads to branch mis-prediction; this contributes to a large fraction of stall time on CPUs [68, 79] or thread divergence on GPUs [74]. Some of the applications that exhibit control flow irregularity are SQL selection operation, building histograms, breadth first search etc. As a consequence of these irregularities, an application tends to pull data from many different memory locations jumping around memory in seemingly random ways. This behavior introduces a long latency to fetch data from memory.

Over the past few years, many real world applications are drifting towards irregularity, making it difficult for the cache-centric architectures to achieve the maximum performance. However, with the advent of new heterogeneous architectures like Convey HC-2ex, Intel HARP, Stratix 10 with HBM2, it has become easy for the hardware architects to prototype designs without relying on any cache support. Moreover, the applications can enjoy best of both worlds. Caches can be used for regular applications while irregular application can be offloaded to the accelerators.

Without relying on caches, an alternative approach to mask long latencies is by using hardware *multithreading* [70, 50, 80]. Several multithreading models (*simultaneous*, *fine-grained*, *coarse grained*) have been proposed. They can be categorized by how temporally close, instructions from different threads may be executed. On general purpose processors, executing multiple threads concurrently requires saving the full context of each thread. This limits the amount of parallelism that can be achieved on these systems.

In a custom architecture (e.g., FPGA) where the datapath is designed for a small number of predefined operations, the required context for each thread is much smaller than in a general-purpose CPU and hence more threads can be supported. In this model, parallelism is limited only by the number of active threads (ready, executing or waiting).

In this thesis, we explore custom hardware *multithreading* that masks long memory latencies incurred by both data flow irregularity and control flow irregularity. The applications used for data flow irregularity are *group-by aggregation* and *Sparse Matrix and Vector Multiplication (SpMV)* and the *relational select operator* is used for control flow irregularity. We prototype our proof-of-concept on the Convey HC-2ex FPGA machine.

There are two possible implementations of group-by aggregation, hash-based and sort-based. The former is generally preferred because it avoids the high penalty of sorting the input relation. Hence, in this thesis we focus on an in-memory hash-based implementation for group-by aggregation. Hash tables rely on good hashing functions that randomly distribute keys across a range of values, thereby exhibiting a dataflow irregularity.

On the other hand, selection operator is generally used to select rows from a table (relation) that satisfies some given conditions. While selection has a seemingly regular execution pattern (i.e., exhibits spatial locality), it often leads to control flow irregularity while evaluating the selection predicates. In most cases, selection appears early on within a query plan - right above the data scan operator - its performance directly affects the total runtime of the whole query.

Similarly, Sparse Matrix-Vector Multiplication (SpMV) has also received significant attention due to its increasingly important applications in scientific and commercial applications. Although SpMV is a highly parallelizable, the real world sparse matrices often restrict realizable parallelism. The reasons are two fold. On one hand, low compute to memory ratio makes SpMV a memory bound problem and on the other hand, it exhibits a data flow irregularity while fetching an input or output vector from a memory space which is far too big for cache. Hence, it becomes difficult to utilize the main memory bandwidth which is already scarce.

The rest of the dissertation is organized as follows. Chapter 2 discuss literature survey relevant to this thesis. It includes historical memory trends, multithreading techniques, query processing and SpMV implementations on accelerators. In Chapter 3, we present multithreaded in-memory group by aggregation. Our results demonstrate a speed up of up to 10x over the best multicore software algorithms. In Chapter 4, we present a detailed comparison study of the selection operator on multi-core CPUs, GPU and multithreaded FPGA implementation. In an important parameter space, the multithreaded design achieves a speed of 1.4x-4.6x over CPU SIMD and 1.4x-6.7x over GPU implementations. Unlike other architectures, this design is independent of the data layout. In Chapter 5, we explore the multithreaded implementation of the SpMV kernel. Using a classical roofline model, we theoretically derive the upper bound performance of the SpMV implementation and compare it to our experiments. Our results show that the model is accurate up to 95%. We also demonstrate that the multithreaded SpMV implementation achieves much higher fraction, up to 95%, of the upper bound performance when compared to GPU that achieves up to 69% of their respective upper bound.

### Chapter 2

### **Related Work**

Custom architectures like FPGAs are becoming increasingly attractive platforms for many applications. FPGAs provide cheaper solution and faster time to market as compared to ASICs which normally require a lot of resources in terms of time and money to obtain first device. FPGAs are generally used for streaming applications and are therefore known to perform well on regular applications. However, this streaming paradigm again implicitly assumes the existence of some form of locality within the stream since the on-chip memory on most FPGA devices is very limited.

This thesis suggests an alternative approach that expands the application domain of FPGAs by considering applications that cannot be streamed. Techniques like latency masking and multithreadding accompanied by a custom pipelined datapath, allow FPGAs to decide the memory locations it needs at runtime. We apply our designs to SpMV and database applications.

### 2.1 Reconfigurable and Heterogeneous Architectures

When the performance of algorithms is insufficient on general purpose processors, the architecture community turn towards hardware implementations specifically designed to implement the desired algorithm. Application Specific Integrated Circuits (ASICs) are hardware chips designed to implement one specific algorithm and are able to provide fast and efficient execution. However, the ASIC fabrication process is time consuming and a small change in the design will require fabrication of a whole new ASIC. This process also involves high implementation and deployment costs. Reconfigurable computing, on the other hand, allows relatively easy development cycle of hardware circuits. The hardware can be incrementally improved whilst maintaining a greater degree of flexibility than ASICs.

Field Programmable Gate Array (FPGA) is the most common reconfigurable platform. The way FPGAs typically implement combinatorial logic is with LUTs (LookUp Tables). In general terms LUT is basically a table that determines what the output is for any given input(s). In the context of combinational logic, it is the truth table. This truth table effectively defines how your combinatorial logic behaves. They are also often coupled with coarser-grained functional units such as dedicated multipliers or Digital Signal Processing (DSP) blocks as well as small internal memories, called as BRAMs. As their name suggests, they can be reconfigured with new logic designs even 'in the field' after deployment without the costly tooling overheads of ASICs.

The conventional wisdom dictates that pointer intensive, or sparse applications are not well suited for FPGA-based code acceleration as these algorithms are often memory bound rather than compute bound and therefore will see limited benefit from the massive parallelism offered by reconfigurable hardware. However, heterogeneous architectures provide some unique opportunities for improving memory performance thanks to low latency links between a general purpose CPU and customizable hardware, both sharing high speed links to external memory. This thesis seeks to examine how the alternative data paths and processing options provided by these platforms can be used to improve memory access performance of irregular algorithms over other platforms.

### 2.2 Multithreaded Architectures

A multithreaded processor concurrently executes instructions from different threads of control within a single pipeline. Figure 2.1 presents different multithreaded architectures. Each row represents the issue slots for a single execution cycle: a filled box indicates that the processor found an instruction to execute in that issue slot on that cycle; an empty box denotes an unused slot. Figure 2.1(a) shows a sequence from a conventional superscalar, executing a single program, or thread, from which it attempts to find multiple instructions to issue each cycle There are two basic types of multithreaded processors: those that issue instructions only from a single thread in a cycle, and those that issue instructions from multiple threads in the same cycle. Many advanced out-of-order superscalar processors such as the IBM Power7 and Power8 [73] or the latest Intel architectures, like Nehalem [54], support the simultaneous multithreading (SMT) technique. SMT keeps multiple threads active in each core. The processor identifies independent instructions and simultaneously issues them to the cores various execution units, thereby maintaining high utilization of the processor resources.

Figure 2.1(d) shows how each cycle an SMT processor selects instructions for execution from all threads. It exploits instruction-level parallelism by selecting instructions from any thread that can (potentially) issue. The processor then dynamically schedules machine resources among the instructions, providing the greatest chance for the highest hardware utilization. If one thread has high instruction-level parallelism, that parallelism can be satisfied; if multiple threads each have low instruction-level parallelism, they can be executed together to compensate. In this way, SMT can recover issue slots lost to both horizontal and vertical waste.

On the other hand, processors that issue instructions from a single thread every clock cycle are known as temporal multithreaded processors. The execution alternate between different threads to keep the (usually in-order) pipeline filled and avoid stalls. This technique was used in the SUN UltraSparc T5 [37] and Tera MTA [8, 7] (now Cray XMT [48]). Temporal multithreaded architectures are generally better suited for irregular applications because they can tolerate long latency memory accesses by switching to other ready threads while the memory subsystem loads or writes the data, thereby not necessarily requiring caches to reduce access latencies [80].

#### 2.2.1 Latency Masking Multithreaded Architectures

Memory masking multithreaded architectures have existed since the beginning of the computer architecture field. It is a simple idea. Research scientists measured the number of clock cycles it took to fulfill a memory request. In the Horizons case [77] most requests averaged between 50 to 80 cycles, but almost all requests could be handled within 128 cycles. The architects then built custom processors to supported that many outstanding requests; 128 threads in the case of the Horizon. The processors had very fast context switching (one clock cycle) so that once a request was issued by a thread it could immediately switch to another thread. In this way the processor was fully utilized. In the worst case all 128 threads would issue a memory request. However, by the time the 128th request was issued the 1st request would be fulfilled, and the processor could continue running without interruption. This technique is called memory masking, and is integral to a multihreaded architectures performance.

Similarly, the Tera Computer Company released its Tera MTA [8, 7] machine. Each of its processors could run at 300 MHz, and they could support 128 hardware threads. The only physical machine, that we are aware of, was installed at the San Diego Supercomputer Center [1] and it contained 4 processors. Therefore, It could support 512 threads. To lower the network traffic the MTAs instructions were fetched through a shared cache. However, it had no data cache and relied purely on multithreading to mask the memory latency. Starting in 2005 Sun produced a line of multithreaded multicore processors based on its UltraSPARC architecture. The first processor (UltraSPARCT1) had 8 cores that could support 4 threads concurrently. Each core would context switch between active threads each cycle. This increased the overall latency of a single thread, but allowed the cores to be better utilized. Threads did not need to be from the same application, but cache performance improved if the threads were accessing the same data locations. Sun steadily improved the architecture by adding more floating-point units, memory bandwidth, and increased the number of cores. However, when the UltraSPARC T4 was released they decreased the number of cores, but dramatically increased the clock frequency. This was a move to broaden their target audience by improving the single thread performance.

Nevertheless, these architectures support a relatively *small* and predetermined number of threads (up to 128 on the MTA and up to eight threads per core on the UltraSparc T5). This is because the CPU has to save a huge hardware context (in the form of registers, program counters, stack pointers, etc) for each ready/waiting thread. This context is saved every time the execution switches between threads and is read later when a thread resumes. As a result, the number of threads that can be run in parallel is limited by the total number of physical cores (or hardware contexts for CPUs with hyper-treading).

#### 2.2.2 Custom Multithreaded Architecture

The customized multithreaded architecture exploited in this thesis can be considered as a blend of SMT and the temporal multithreading (discussed in Chapter 2). The structure of the data-path and the number of thread states are designed for the specific target application. Like SMT, in this architecture too, a running thread relinquishes exe-

Figure 2.2: Custom Multithreaded Architecture

cution to a ready thread as soon as it performs a long-latency operation. Additionally, the deeply pipelined datapath on FPGA allow different threads to enter the pipeline on each cycle. Moreover, the datapath in a custom architecture (e.g. FPGA) is designed for a small number of predefined operations. As a result, the required context for each thread is much smaller than in a general-purpose CPU and hence more threads can be supported.

In any multithreaded setup there are typically three states of execution: (1) buildup state (2) steady state and (3) drain state. In a build-up state, threads are generated in a such a way that number of memory accesses in flight is sufficient enough to cover the bandwidth delay product. In an ideal setup, As soon as the last request is sent, the responses are received that fills the pipeline of a custom datapath. In a steady state, a kernel/core can maintain sufficient in-flight requests that can hide the memory latency. However, towards the end of execution, threads start terminating either because the job is done or all the input data is processed. When this happens, the number of in-flight requests also start decreasing and can no longer mask the latency. If the steady state execution is longer than other two states, the build-up and the drain costs are amortized.

Figure 2.2 describes different components of this model. The execution starts by generating multiple threads (requests) by 'request process' module. Assuming a fully pipelined datapath and a buffered memory interface, the expected parallelism in such a system equals to memory bandwidth  $\times$  memory latency (Little's Law). The number of threads that are generated should commensurate with the memory latency. For instance, the average memory latency on Convey HC-2ex, our target machine, is 500 cycles. Therefore, we generate 500 threads. The idea is simple. As soon as the last memory request is sent, the memory response for the first request is received and is fed to the pipelined datapath. This imply that the parallelism is limited only by the number of outstanding requests that can successfully mask the memory latency.

### 2.2.3 Convey HC-2ex: Target Platform

The Convey HC-2ex is a heterogeneous platform that offers a shared global memory space between the CPU and FPGA regions, allowing us to directly compare the FPGA and CPU in-memory implementations on the same memory architecture. The coprocessor supports multiple instruction sets (referred to as "personalities"), which are optimized for

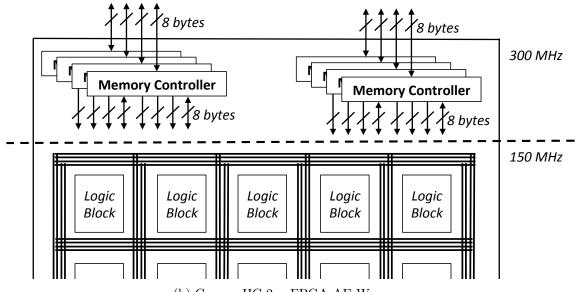

(a) The Convey HC-2ex software and hardware regions

(b) Convey HC-2ex FPGA AE Wrapper

Figure 2.3: The Convey HC-2ex architecture is divided into software and hardware regions as shown in (a). Each FPGA has 8 memory controllers, which are split into 16 channels for the FPGA's logic cells as shown in (b)

different workloads and dynamically reloaded when an application is run. Each personality includes a base set of instructions that are common to all personalities, as well as extended instructions that are designed for a particular workload. As shown in Figure 2.3a, the memory is divided into regions connected through PCIe with portions closer to the CPU, and portions closer to the FPGAs. Each processor (CPU or FPGA) can access data from both regions, but data accesses across PCIe are significantly longer. The software region has 2 Intel Xeon E5-2643 processors running at 3.3 GHz with a 10 MB L3 cache.

The hardware region has 4 Xilinx Virtex6-760 FPGAs, called application engines (AE), connected to the global memory through a full crossbar. The crossbar not only interfaces the AEs to the memory modules but also supports the in-order return of all memory requests. Our multi-threaded designs utilizes this re-ordering to serve all the concurrent threads in the order of their arrival. Each AE also has 8 64-bit memory controllers (MC) running at 300MHz (Figure 2.3b). The MCs translate virtual to physical addresses on behalf of the AEs, and include snoop filters to minimize snoop traffic to the host processor. The Memory Controllers support standard DIMMs as well as Convey designed Scatter-Gather DIMMs, which are optimized for transfers of 8-byte bursts and provide near peak bandwidth for non-sequential 8-byte accesses. The coprocessor therefore provides a much higher peak bandwidth, and often can deliver a much higher percentage of that bandwidth, than what is available to commodity processors.

The hardware logic on each AE run in a separate 150 MHz clock domain to ease timing and is connected to the memory controllers through 16 *memory channels*. On the HC-2ex, all the reads and writes to the memory are done through these channels. Each channel supports independent and concurrent read-write accesses to memory. The memory latency varies, according to the target memory bank and traffic congestion, between 400 and 800 cycles. Assuming all the channels are used for reads and an average latency of 500 cycle this means there are 8000 (8\*400) outstanding memory requests per accelerator FPGA or 32,000 for the whole system. Obviously, stalls in the pipeline and other hazards reduce the throughput. However, these numbers provide a good estimate of the possible parallelism and the massive number of threads.

### 2.3 Query Processing on FPGAs

Many research works in the early 1980s were dedicated to the design and architecture of *database machines* - specialized hardware, designed solely for the purpose of storing and processing large amounts of data. These architectures were utilizing parallel data processing by tightly coupling processing units with disk-based storage. The stagnated growth of disk bandwidth coupled with the continuous increase of storage density implied that data management systems were mostly IO bound. At the same time the rapid performance advances of off-the-shelf processors (due to Moore's law) made the database machine very cost-ineffective [19]. This allowed a handful of processors to operate on a large number of parallel disk I/O operations thus avoiding the rigid pairing of storage and compute units. The interest gradually shifted from intra-node database machine-style parallelism to shared-nothing systems, providing effective easy to scale inter-node parallelism [33, 32]. The depletion of the processing frequency growth finally discontinued the "free ride" on performance scaling. Abundance of cheap main memory diminished the role of I/O-related overhead as a main bottleneck. Nevertheless, the growing gap between memory access latency and the processor's computational capabilities ("memory wall") brings up the data access overhead, but on a different level ("memory is the new I/O"). At the same time, the limited bandwidth of current network technology has restricted the scaling potential of the shared-nothing systems. The aforementioned hardware trends as well as The availability of new generation of data processing hardware (GPUs, FPGAs, ASICs) revived the interest in specialized hardware-accelerated database systems. Recently several research projects proposed building hybrid CPU-GPU systems [92, 21, 42, 83, 40]. These systems are deployed on a traditional CPU architecture, but use the GPUs as a co-processor to accelerate easy-to-parallelize parts of the query processing.

Several academic projects have worked towards simplifying the use of custom hardware for query processing. For instance, the Glacier library [62] implements a component library that generates query-specific FPGA circuits for various streaming queries. This approach is suitable for scenarios with few queries that are known in advance. Queries that fall under typical stream processing applications run longer which justifies invoking a timeconsuming synthesis process for every new query. The synthesis time to build an engine is high, and needs to be amortized over many runs to be practical. The technique has been shown useful for event processing systems like high frequency trading [69]. The Q100 [87] architecture is a fixed platform with many ASIC database processing units. A query stream is scheduled through the necessary units. Resources may go unused for a given query, but the platform avoids long build times.

Netezza [3] is a complete DBMS that uses FPGAs as a filter between the hard disk and main memory. Customizable queries are sent to the FPGAs which utilize their close proximity to the hard disk to quickly filter relations before sending them to memory. The platform tries to reduce the costly data transfers from disk to main memory [75]. The trade off for this approach is that all requests must start on disk. In-memory databases cannot leverage the addition hardware FPGAs. Another full DBMS, Kickfire [2], uses FPGA hardware accelerators connected through either PCIe or hyper transport. It defines various database operations as HARP logic that consists of a hardware circuit and a large memory systems. All queries are analyzed by Teradatas C2 software, which decides if it should handle the job itself, send it back the the DBMS, or offload it to HARP logic. The customized hardware supports many common relational database operations [20, 47, 60].

#### 2.3.1 Group-by Aggregation

The performance characteristics of the aggregation operator differs very much depending on the number of groups (distinct keys). If there are few groups, aggregation is very fast because all groups fit into cache. If, however, there are many groups, many cache misses happen. Contention from parallel accesses can be a problem in both cases (if the key distribution is skewed). To achieve good performance and scalability in all these cases, without relying on query optimizer estimates, multi-core CPU architectures provide two main alternatives. The *hardware-conscious* algorithms are tightly tailored to the underlying hardware and perform preliminary data partitioning to reduce cache misses. Instead, the *hardwareoblivious* solutions try to mask latency by relying on hardware-provided multithreading. These contrasting approaches were extensively studied in the context of in-memory hash joins [17, 11] as well as sort-merge joins [12, 53]. Hardware-oblivious implementations of the group-by aggregation were explored by Cieslewicz et al. [25], who showed that performance largely depends on input characteristics (key cardinality). This work examined aggregation in a multi-core environment on the Sun UltraSPARC T1, a chip multiprocessor. We now discuss the state-of-the-art multithreaded CPU aggregation algorithms. A typical aggregation operator has three phases. The first phase is the startup phase that initializes all data structures. The second phase is the computation phase in which the input data is consumed and used to update the data structures. In the third phase data structure elements are merged to generate a single final result. For example, if each thread has its own private hash table, then those tables must be merged during this stage.

(i) Sort-Based Aggregation: Sort-based aggregation [25] has higher complexity (O(nlogn)) than hash-based aggregation. The complexity of the hash-based method is linear in the number of records n. Additionally, materializing sorted input records is an I/O intensive operation. It should be noted that sorting is a blocking operator. On the contrary, hash-based approach can be easily pipelined from other database operators. The only time that sort-based aggregation is likely to be competitive is when the input stream is already in sorted order.

(ii) Independent Hash Tables: In this approach [25] each thread is given its own hash table that prevents memory collisions. As a result, the aggregation operator can avoid expensive synchronization primitives. The obvious disadvantage of this approach is memory consumption.

(iii) Shared Table with Locking or atomic synchronization: [25] splits the tuples evenly between threads, but all threads aggregate their results into a single hash table, hence no extra merge step is required. The algorithm could use different synchronization primitives: either pthread mutex implementation or Intel specific hardware atomic instructions. Preliminary experiments showed that atomic primitives are significantly better on low key cardinalities, and dont have any difference from mutexes on medium and large cardinalities, so we choose atomics as a default synchronization primitive in all further experiments. To simplify processing, locks are provide for each bucket, rather than for each cell. Locks are not required during the search phase in which the input records key is compared against keys in the bucket. Once a match is found, the bucket is locked to guarantee the atomicity of the update to the aggregate value. Locking is also needed when inserting a new element into a hash bucket.

(iv) Hybrid Aggregation [25] is a combination of two previous approaches. This algorithm allocates a small hash table for each thread. The size of the table is calculated based on the processors L2 size to avoid cache misses. If the local table has enough space for a new value, or the value already exists in the table, that tuple is locally aggregated. Once the local table is filled and the next tuple requires a new slot, the oldest entry in the cached table will be spilled into larger shared table, residing in main memory, thus maintaining only "hot" data in L2 cache. Once aggregation is complete all small cached tables are merged into the large shared table. Merge step is synchronized as in Independent Tables case.

(v) Partition & Aggregate [90] (also known as count then-move [26]) uses individual tables per thread, but before aggregation is performed the tuples are partitioned, in contrast to all aforementioned approaches. Separate partitioning step makes sure that all threads will work on non-overlapping values, hence aggregation could be done without any synchronization and the final tables are simply concatenated, rather than merged. As with the partitioned join implementations radix clustering algorithm is a backbone of this preliminary step.

(vi) PLAT (Partitioning with Local Aggregation Table) [90] is a combination of two previous techniques. The algorithm takes advantage of the fact that we are performing an additional data scan, while doing a preprocessing step. While partitioning tuples into groups with mutually exclusive keys, each thread tries to aggregate values into its own small L2-resident table, as in Hybrid Aggregation approach. Values that do not fit into the small table are partitioned using radix clustering algorithm. Once preprocessing is done standard lock-free aggregation is applied. In the end all tables, which were produced during aggregation, are concatenated together, while local aggregation tables are synchronously merged in.

Follow up work [26] explored the partitioning step of hash aggregation and concluded that the thread coordination is a key component influencing the performance of this step. Finally, Ye et al. [90] proposed hybrid algorithms and showed that they outperform pure hardware-conscious and -oblivious implementations.

An FPGA-accelerated implementation of group-by aggregation was first considered by Mueller et al. [61]. This work utilized CAMs in the implementation of the aggregation operator, but in a very narrow scope, i.e. using CAMs to match an incoming tuple with the appropriate group. Hence the work continued long tradition of using CAMs to answering set-membership queries (previously explored in applications like click-fraud, online intrusion detection [13]). Our design also uses CAMs, but is different from previous approaches in two ways: (i) in addition to the key we store and update the aggregate value locally in the CAM, and (ii) we use CAMs as a synchronization primitive to resolve conflicts during updates. It was shown that implementing fully-associative matching logic for CAMs on both Altera and Xilinx FPGAs introduces a 60x overhead compared to regular BRAMs [91]. This drawback makes implementing large CAMs on reconfigurable fabrics notoriously hard. Dhawan et al. [34] explored various designs of CAMs and introduced a trade-off between CAM size and update time.

#### 2.3.2 Selection Scan Operator

There are three commonly used selection evaluation algorithms. In this discussion, we assume that selection operates directly on the input array of records and writes qualified tuples into a new output array. Listing 2.1 presents the most straightforward way of implementing selection. It shows the *branching scan* method for a conjunctive query using '<' comparison. This technique is often called a 'short-circuit evaluation' because the computation of further predicates can be skipped when the first predicate is already evaluated to false. The logical-AND (&&) operator is typically compiled into k conditional branch instructions.

for  $(i=0; i < number_of_tuples; i++)$ if  $((t_i[0] < v_1) \&\& (t_i[1] < v_2) \&\& \dots (t_i[k] < v_k))$ { out [j++] = i; }

Listing 2.1: Algorithm - Branching Scan

Assuming that the predicates have increasing selectivity, this method is optimal in terms of processing cycles. However, it was shown that on CPUs it leads to heavy branch mispredictions, causing considerable performance penalties [68, 22]. An alternative implementation, presented in Listing 2.2, uses bitwise-AND (&) instead of logical-AND (&&). This approach reduces k conditionals to a single branch.

for

$$(i=0; i < \text{number_of_tuples}; i++)$$

if  $(t_i[0] < v_1 \& t_i[1] < v_2 \& \dots t_i[k] < v_k$ )

{ out  $[j++] = i;$ }

Listing 2.2: Algorithm - Predicate Scan with Bitwise-AND (&)

Here all predicates for a given tuple,  $t_i$ , are evaluated and then, depending upon the result of the evaluation, a branch is executed. This method reduces branch misprediction penalties at the cost of higher computational work. Finally, a no-branch implementation [68] is shown in Listing 2.3. This approach completely eliminates penalties caused by branch mispredictions by increasing computation costs.

for

$$(i=0; i < number_of_tuples; i++)$$

$out[j] = i;$

$j += (t_i[0] < v_1 \& t_i[1] < v_2 \& \dots t_i[k] < v_k)$

Listing 2.3: Algorithm - No-Branch

The techniques presented in Listing 2.2 and 2.3 either reduce or completely eliminate the branches. Yet, both approaches process all predicates and miss the opportunity to skip irrelevant evaluation as in the *branching scan*.

#### Selection on Parallel Architectures

An efficient implementation of Listings 2.1-2.3 must be designed for a specific data layout to effectively leverage the extensive cache hierarchy. Many efficient algorithms have been proposed for both row [68] and column [66, 96, 36] storage layouts. Moreover, columnar format allows effective compression and increases the throughput by more than an order of magnitude over traditional CPU row-store database systems [36]. However, all these approaches require an overhead of converting data in row-major format to a columnar layout either in the background or keeping two separate representations of the same record.

In addition to thread-parallelism, modern architectures support data-level parallelism and provide new opportunities for *vectorized* implementations. All modern CPUs are equipped with SIMD registers that can be used to accelerate many database operations [94, 84], including selection. All three algorithms described above can be vectorized. However, algorithm in Listing 2.1 requires additional bookkeeping to track which row should be dropped from future evaluation. This can be achieved by using non-contiguous loads/store (scatter/gather) operations[67] available only in the latest processors supporting AVX2 vectorization which make the design less portable. However, *branching scan* still can be implemented using older SIMD intrinsics but it will be sensitive to small predicate selectivity.

Likewise, GPUs implement *no-branch* algorithm because conditional execution (Listings 2.1 and 2.2) results in thread divergence and reduces the overall system performance. Selection is executed in two steps: (1) evaluating the predicate conditions and (2) gathering the indices of the qualifying rows [46]. During processing, all threads within a warp execute in lock-step irrespective of the predicate selectivity. However, being oblivious to predicate selectivity can lead to wasted memory bandwidth since it does not provide any opportunities to stop fetching new predicates based on the last evaluation (Listing 2.1).

For low selectivity, GPUs may overcome this limitation by relying on indexes [46], thus reducing the overall tuple evaluation latency at the expense of processing throughput. Overall, maintaining an index can be costly when frequent updates are expected thus in this work, we focus on throughput optimization thus avoiding the use of indexes.

#### Selection on FPGA

The work presented in [75] focused on row decompression and predicate evaluation. In this technique, pre-generated bit files are produced (for different types of queries and for various hardware configurations) and the one that is best-matched to the given workload is loaded. Stream processing applications typically processes long-running queries which justifies invoking a time-consuming synthesis process for every new query.

In contrast to stream processing, in a data warehouse scenario, the query workload is unpredictable and queries are not always long-running. Thus, it is important to avoid time consuming synthesis process in such cases. This problem was addressed in [31] by applying a special FPGA technique called *partial reconfiguration*, which allows them to build query plans from pre-compiled components at runtime. It is a useful technique to time-multiplex circuits that do not fit on the same chip. Another work in [86], employs an FPGA between a DB system (MySQL) and SSDs to offload filter and aggregation queries. A complex WHERE clause is broken into individual base predicates and compared to the fixed size constant. The result is stored in a truth table which is transmitted to a BRAM. However, the memory consumption grows exponentially with the number of predicates. Our MTP selection engine also maintains the query in a BRAM; however, the on-chip memory consumption is linear to the number of predicates in the query. Finally, [23] explores FPGAs as accelerators for join operations in columnar main-memory databases. Recently, a custom hardware multithreading design was applied to hash-joins [43].

# 2.4 Sparse Matrix-Vector Multiplication

Sparse Matrix-Vector Multiplication (SpMV) is a highly exercised scientific kernel that solves y = Ax, where x and y are dense vectors, while A is a sparse matrix. (SpMV) has received significant attention due to its increasingly important applications in scientific and commercial applications. Although SpMV is a highly parallelizable, the real world sparse matrices often restrict realizable parallelism. It is mostly treated as a memory bound application [28]. Therefore, its performance on platforms like CPUs and GPUs depends on the memory bandwidth or the amount of cache on the respective platform. Our target architecture (the Convey HC2-ex) provides a peak bandwidth of 19GB/s memory bandwidth per FPGA, whereas current CPUs have 100 GB/s and current GPUs have 870 GB/s of memory bandwidth. However, it's a bit of a simplified justification of the problem.

There is a small niche where FPGAs can excel. When the matrix and vector sizes become large, around 10 million values [78], CPU performance drastically decreases. When this happens the CPU experiences a lot of x vector cache misses. To address this issue many turn to GPUs. GPUs are well known to be sensitive to sparsity and therefore to achieve better performance on SpMV, they expand the storage size of the matrix. This means that matrices that surpasses the GPU RAM size perform badly due to the transfer overheads. It has been shown time and again that an *improper* sparse matrix format can degrade performance by an order of magnitude or more [16]. Therefore, to avoid excessive waste in bandwidth and storage, the sparse matrix is typically encoded using a sparse format, which stores only the non-zero values of the matrix along with meta-data that identifies a non-zeros location in the matrix.

#### 2.4.1 Sparse Matrix Formats

Using the right sparse matrix format is essential because at runtime, the metadata must be decoded for each non-zero, which is used to identify the corresponding x vector value for calculating the dot product. Many different approaches have been proposed throughout the years, and we highlight the most general ones here. As an example, consider the nonsymmetric matrix defined by

|      | a | 0 | $egin{array}{c} 0 \\ 0 \\ m \\ q \end{array}$ | 0 | b | 0 |  |

|------|---|---|-----------------------------------------------|---|---|---|--|

|      | x | y | 0                                             | 0 | 0 | z |  |

|      | 0 | l | m                                             | 0 | 0 | 0 |  |

|      | p | 0 | q                                             | 0 | 0 | 0 |  |

| Figu |   |   |                                               |   |   |   |  |

## **Coordinate Format**

The simplest sparse format is the Coordinate format (COO). This format stores the row index, column index along with the non-zero values. It is simple and for any pattern of sparsity the storage required is dependent on the number of non-zero values. It is implemented with three 1-dimensional arrays, one to store the non-zero values and the other two to hold the row and column index of the corresponding nonzero values. Even though it is not quite as efficient from the memory requirement point of view, it is attractive because of its simplicity. In particular, the sparse matrix-vector product routine in the CMSSL library adopts a slight variant of the COO format.

| row index                                   | 0 | 0 | 1 | 1 | 1 | 2 | 2 | 3 | 3 |

|---------------------------------------------|---|---|---|---|---|---|---|---|---|

| col index                                   | 0 | 4 | 0 | 1 | 5 | 1 | 2 | 0 | 2 |

| matrix value                                | a | b | X | у | Z | 1 | m | p | q |

| Figure 2.5. Coordinate Sparce Matrix Format |   |   |   |   |   |   |   |   |   |

Figure 2.5: Coordinate Sparse Matrix Format

#### **Compressed Storage Format**

Compressed Storage Format (CSR) is the most popular and general format that provides excellent compression for both structured and unstructured sparse matrices in high performance architecture. SpMV with CSR format shows good performance improvement when implemented on CPUs and all algorithms like BLAS, LAPACK and CUSparse supports this format only. It uses three 1-dimensional arrays, one to hold the non-zero values, the second one holds the number of non-zero values per row and the third one holds the column index of the non-zero values. The CSR format of the example matrix is as follows: The compressed sparse column format (CSC) is almost identical to CSR, but instead of

| row          | row pointer |   |   |   | 5 | 7 | 9 |   |   |

|--------------|-------------|---|---|---|---|---|---|---|---|

| col index    | 0           | 4 | 0 | 1 | 5 | 1 | 2 | 0 | 2 |

| matrix value | a           | b | x | у | Z | 1 | m | р | q |

|              |             |   |   | _ |   |   | \ |   |   |

Figure 2.6: Compressed Sparse Row (CSR) Matrix Format

compressing the row array it compresses the column array. The CSC format is less widely used because its workloads are harder to distribute evenly. SpMV has one output per row (not per column), and with CSR each output can be computed within a single process-

| a | b | 0 |

|---|---|---|

| х | у | z |

| 1 | m | 0 |

| р | 1 | 0 |

| 0 | 4 | * |

|---|---|---|

| 0 | 1 | 5 |

| 1 | 2 | * |

| 0 | 2 | * |

(a) Value Vector (b) Column Vector Figure 2.7: ELLPACK sparse matrix format

ing element (PE). CSC would require synchronization across multiple PEs to prevent race conditions.

# **ELLPACK** Format

The ELLPACK (ELL) format rose in popularity with GPUs. Peak performance required each processor to run the same workload. The traditional ELL format compresses the matrix data into a rectangular dense matrix, and adds zeros to force each column in the matrix to have the same number of elements. The matrix data is then stored column by column, followed by their column indices in the original sparse matrix. Since each column is aligned to a 32-element boundary, the format is able to fully utilize the mechanism of the memory coalescing on a GPU. This leads to a significant increase in the loading throughput and improved performance of the SpMV for some matrices. The format handles matrices with similar short row lengths well because of the local column storage. However, if the row length for a matrix varies significantly and many zeros are needed, the ELL format becomes inefficient. A major challenge in computing y = Ax is the irregularity of accesses to the x vector (for row-wise traversal) or y vector (for column-wise traversal) as a result of the non-zero access patterns in the matrix. Hardware accelerators, such as FPGAs and GPUs, deal differently with this situation.

# 2.4.2 GPU Approaches

GPGPUs are known to be throughput-oriented processors. Therefore harnessing the best performance out of them requires exposing substantial fine-grained parallelism as well as sufficient regularity on execution paths and memory access patterns.