## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

## Title

Area-efficient Neuromorphic Silicon Circuits and Architectures using Spatial and Spatio-Temporal Approaches

Permalink https://escholarship.org/uc/item/61x78103

Author Payvand, Melika

**Publication Date** 2016

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Santa Barbara

Area-efficient Neuromorphic Silicon Circuits and Architectures using Spatial and Spatio-

**Temporal Approaches**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Melika Payvand

Committee in charge:

Professor Luke Theogarajan, Chair

Professor Forrest Brewer

Professor Dmitri Strukov

Professor K.-T. Tim Cheng

Professor Wei Lu

December 2016

The dissertation of Melika Payvand is approved.

Forrest Brewer

Dmitri Strukov

K. -T. Tim Cheng

Wei Lu

Luke Theogarajan, Committee Chair

December 2016

Area-efficient Neuromorphic Silicon Circuits and Architectures using Spatial and Spatio-

Temporal Approaches

Copyright © 2016

by

Melika Payvand

#### ACKNOWLEDGEMENTS

The past 6 years in UCSB has truly been a life journey in many different aspects. It was a process of scientific, philosophical, intellectual, psychological and social growth for me. When I think back I cannot believe how far I've come as a person and I owe this to the fantastic people I've met here, in Santa Barbara. I want to dedicate my thesis to them as they formed these unforgettable years for me.

My advisor, professor Luke Theogarajan, who was always a source of inspiration and a true mentor, in science and in life. He truly cared about the well-being of all of his students and I'm honored to have been one of them.

Professor Forrest Brewer who always encouraged curiosity and his breadth of knowledge was inspirational. He always made me feel that there is so much to learn.

Professor Dmitri Strukov, Professor Tim Cheng and Professor Wei Lu who provided other perspectives in MURI project and they were always happy to help and listen to me.

Bruno Silva, whose perspective in life changed me to my core. His peace calmed me down, made me believe that any achievement in life requires patience and good things happen to people who wait. He brought a sense of meaning and gratitude to my life which nobody has ever had.

Advait Madhavan, who always offered a hand when I was falling. Who believed in me when I didn't and who listened to me when no-one else did. Can't thank him enough. Doing tape-out with him is my favorite part of grad school ©

Amirali Ghofrani, who was family. His support, warmth and positivity always fueled me. He never failed to bring happiness.

iv

Doing a tape out with Amirali, Advait and Miguel Lastras was an incredible experience. We worked together as a team and learned so much from each other. I very much appreciate Miguel's drive in that project for if it wasn't for his belief in memristors, that chip would have never got to where it did.

Danielle Morton, who patiently taught me all she thought I should know when I joined the group and was always happy to help. Her perseverance was always a source of admiration for me.

Anahita Mirtabatabayi for when she is around everything is better. She shaped the structure of my life in Santa Barbara and was always a role model for me as a strong woman.

Tanya Das and Oana Catu who never failed to bring joy to my life. They were there when I needed them the most and gave me so much love.

All of my current and past colleagues in Biomimmetic Circuits and Nano Systems group for providing such a friendly environment to discuss circuits, science and life and to share laughter and joy. I appreciate each and every one of them.

Colleen and Alf, who were my family. Can't thank them enough. They care for me as their daughter and never failed to give their support.

And, to my family. For they gave me all they had not for the past 6 years but since I started existing.

My parents who ignited the flames of desire for achievement and success in me.

My sister whose unconditional love warms my heart.

My grandma who is happy with my happiness and sad with my sadness.

My aunt and uncle who embraced me with all they had when I moved to the US.

THANK YOU all for being part of my life and forming my great years of graduate school. I couldn't have asked for more.

"The science of the mind can only have for its proper goal the understanding of human nature by every human being, and through its use, brings peace to every human soul."

—Alfred Adler

### VITA OF MELIKA PAYVAND

### December 2016

### **EDUCATION**

PhD, University of California Santa Barbara, Electrical and Computer Engineering Advisor: Prof. Luke Theogarajan, December 2016

M.S. University of California Santa Barbara, Electrical and Computer Engineering, Septermber 2012

B.S. University of Tehran, Iran. Electrical and Computer Engineering, July 2010

### SUMMARY OF SKILLS

o IC Design, Layout and Test: Full design flow of chip design from transistor level to layout to post-layout simulations and testing: Neuromorphic VLSI, Analog/ Digital/ Mixed Signal Circuit Design, FPGA Design, PCB Design

Machine Learning: Logistic/Softmax Regression, Supervised/Unsupervised Learning,

Convolutional Neural Networks, Auto-encoders, PCA, Sparse Coding, etc.

o Computational Neuroscience: Spike Encoding/Decoding, Information Theory

o Resistive Switching and Memristive Device and Application

### RESEARCH AND WORK EXPERIENCE

o Developed A Novel Spatio-Temporal Coding Algorithms for Neuromorphic Chip Applications: This algorithm uses a combinatorial scheme in spiking patterns of neurons which learn to recognize patterns in a completely unsupervised fashion. This results in significantly reducing the number of connections required to do similar tasks using other counterpart algorithms, Summer 2015-Present

o Tape-out: Configurable CMOS Spiking Neurons for 3D-Memristive Synapses Design, layout and tape-out of a neuromorphic chip containing an array of CMOS spiking neurons. Spike shapes are engineered to enable STDP for memristive crossbars and are fully configurable. The circuit is designed fully asynchronously to enable online unsupervised learning. The chip is designed in Silterra 180nm. Winer 2015

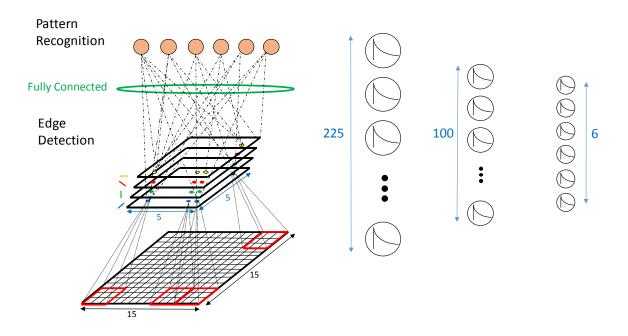

o Developed a Mapping from Connectivity Domain Available in CMOL Architecture to Localized Neural Receptive Fields: Explored the use of large fan-in locally connected spiking silicon neurons readily available in CMOL architecture to solve edge recognition in images via unsupervised learning. Spring 2015

o Tape-out: Configurable CMOS Memory Platform for 3D Memristor Integration Involved in a collaborative CMOL (CMOS-Molecular devices) memory development project. Design, layout and test of the first CMOS memory controller platform for the memristive memory array in a hybrid/3D architecture. Testing resulted in full functionality of the chip which was fabricated in On-Semi 3M2P 0.5um occupying 2X2mm2. Summer 2014-Winter 2014

o Tape-out: Floating Gate Transistor and Photodiode Characterization

ix

Design, layout and tape-out of a chip to characterize floating gate transistor current as a result of hot electron injection into the floating gate. A current sensing scheme using a WTA circuit was utilized to detect the change in current. Photo-diode current sensing circuit was designed using a current to frequency conversion for a digital read out. Winter-Spring 2013

### PUBLICATIONS

M. Payvand, L. Theogarjan "Winners-Share- All: Towards Exploiting the Information Capacity in Temporal Codes", In Manuscript 2016

M. Payvand, L. Theogarajan, "Exploiting Local Connectivity of CMOL Architecture for Highly Parallel Orientation Selective Neuromorphic Chips", IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), Boston, Massachusetts, USA, July 2015

M. Payvand, A. Madhavan, M. Lastras, A. Ghofrani, J. Rofeh, T. Cheng, D. Strukov, L. Theogarajan, "A configurable CMOS memory platform for 3D integrated memristors", ISCAS 2015

M. Payvand, J. Rofeh, A. Sodhi, L. Theogarajan, "A CMOS-memristive self -learning neural network for pattern classification applications", Nanoarch, July 2014, Paris, France

J. Rofeh, A. Sodhi, M. Payvand, M. Lastras, A. Ghofrani, et al, "Vertical integration of memristors onto foundry CMOS dies using wafer-scale integration", ECTC 2015, IEEE 65th.

A. Ghofrani, M. Lastras, S. Gabba, M. Payvand, W. Lu, L. Theograjan, T. Cheng, "A low-power variation-aware adaptive write scheme for access-transistor-free memristive memory", JETC, 2015

### AWARDS

Awarded University of California Doctoral Student Travel Grant, July 2015

Awarded Graduate Student Researcher Fellowship (GSR), UC Santa Barbara, 2012-Present

Awarded Best Teaching Assistant Award, Spring 2011

Picked Among the 5% Exceptional Students, Department of ECE, University of Tehran,

2008-2010

Ranked 164 among 500,000 participants nationwide in "University Entrance Exam", Iran, Summer 2005

### ABSTRACT

## Area-efficient Neuromorphic Silicon Architectures using Spatial and Spatio-Temporal

Approaches

by

### Melika Payvand

In the field of neuromorphic VLSI connectivity is a huge bottleneck in implementing braininspired circuits due to the large number of synapses needed for performing brain-like functions. (E.g. pattern recognition, classification, etc.). In this thesis I have addressed this problem using a two pronged approach namely *spatial* and *temporal*.

**Spatial**: The real-estate occupied by silicon synapses have been an impediment to implementing neuromorphic circuits. In recent years, memristors have emerged as a nano-scale analog synapse. Furthermore, these nano-devices can be integrated on top of CMOS chips enabling the realization of dense neural networks. As a first step in realizing this vision, a programmable CMOS chip enabling direct integration of memristors was realized. In a collaborative MURI project, a CMOS memory platform was designed for the memristive memory array in a hybrid/3D architecture (CMOL architecture) and memristors were successfully integrated on top of it. After demonstrating feasibility of post-CMOS integration of memristors, a second design containing an array of spiking CMOS neurons was designed in a 5mm x 5mm chip in a 180nm CMOS process to explore the role of memristors as synapses in neuromorphic chips.

**Temporal**: While physical miniaturization by integrating memristors is one facet of realizing area-efficient neural networks, on-chip routing between silicon neurons prevents the complete realization of complex networks containing large number of neurons. A promising solution for the connectivity problem is to employ spatio-temporal coding to encode neuronal information in the time of arrival of the spikes. Temporal codes open up a whole new range of coding schemes which not only are energy efficient (computation with one spike) but also have much larger information capacity than their conventional counterparts. This can result in reducing the number of connections to do similar tasks with traditional rate-based methods.

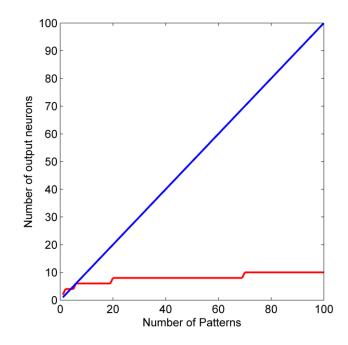

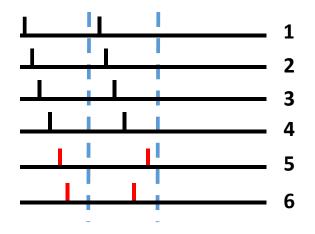

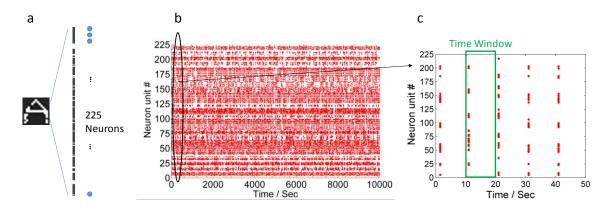

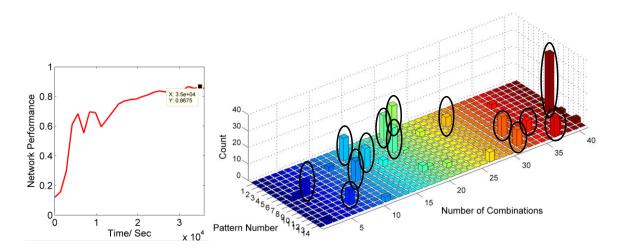

By choosing an efficient temporal coding scheme we developed a system architecture by which pattern classification can be done using a "Winners-share-all" instead of a "Winner-takes-all" mechanism. Winner-takes-all limits the code space to the number of output neurons, meaning n output neurons can only classify n pattern. In winners-share-all we exploit the code space provided by the temporal code by training different combination of k out of n neurons to fire together in response to different patterns. Optimal values of k in order to maximize information capacity using n output neurons were theoretically determined and utilized. An unsupervised network of 3 layers was trained to classify 14 patterns of 15 x 15 pixels while using only 6 output neurons to demonstrate the power of the technique. The reduction in the number of output neurons results in the reduction of number of training parameters and results in lower power, area and memory required for the same functionality.

# Table of Contents

| I. Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1.1 Silicon Neurons                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                                                            |

| 1.2 Silicon synapses                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                            |

| 1.2.1 Capacitors                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                            |

| 1.2.2 Flash                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                            |

| 1.2.3 Multiple SRAMs                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                            |

| 1.3 Overview                                                                                                                                                                                                                                                                                                                                                                                           | 8                                                                                            |

| 1.3.1 Spatial approach: Memristors                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                            |

| 1.3.2 Spatio-temporal Coding Approach                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                            |

| II. Chapter 2: Memristors and Memristive Architectures                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                           |

| 2.1 What is a memristor?                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                                           |

| 2.2 Memristors as Memory Elements                                                                                                                                                                                                                                                                                                                                                                      | 14                                                                                           |

| 2.2.1 Crossbar                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                           |

| 2.2.2 CMOL Architecture                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| III. Chapter 3: Memory Access controller for Memristor Applications                                                                                                                                                                                                                                                                                                                                    | (MAMA)                                                                                       |

| Chip                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                           |

| Cinp                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 3.1 Chip Architecture                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.1 Chip Architecture                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| <ul><li>3.1 Chip Architecture</li><li>3.2 Writing Circuitry (CMOS Cell Design)</li></ul>                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li> <li>3.2 Writing Circuitry (CMOS Cell Design)</li> <li>3.3 Sensing Circuitry</li> <li>3.4 Measurement Results</li> <li>3.4.1 Writing Circuitry Characterization</li> <li>3.4.2 Sensing Circuitry Characterization</li> </ul>                                                                                                                                        |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li> <li>3.2 Writing Circuitry (CMOS Cell Design)</li> <li>3.3 Sensing Circuitry</li> <li>3.4 Measurement Results.</li> <li>3.4.1 Writing Circuitry Characterization</li> <li>3.4.2 Sensing Circuitry Characterization</li> <li>3.4.3 Memristor Characterization Results</li> <li>IV. Chapter 4: Spiking CMOS Neurons Chip</li> </ul>                                   | 22<br>23<br>25<br>27<br>29<br>30<br>31<br>32<br>32<br>32                                     |

| <ul> <li>3.1 Chip Architecture</li> <li>3.2 Writing Circuitry (CMOS Cell Design)</li> <li>3.3 Sensing Circuitry</li> <li>3.4 Measurement Results.</li> <li>3.4.1 Writing Circuitry Characterization</li> <li>3.4.2 Sensing Circuitry Characterization</li> <li>3.4.3 Memristor Characterization Results</li> <li>IV. Chapter 4: Spiking CMOS Neurons Chip</li> <li>4.1 Network Architecture</li> </ul> | 22<br>23<br>25<br>27<br>29<br>30<br>31<br>32<br>32<br>32<br>32<br>32                         |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               | 22<br>23<br>25<br>27<br>29<br>30<br>31<br>32<br>32<br>34<br>34<br>36                         |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               | 22<br>23<br>25<br>27<br>29<br>30<br>31<br>32<br>32<br>34<br>34<br>36<br>38                   |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| <ul> <li>3.1 Chip Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                               | 22<br>23<br>25<br>27<br>29<br>30<br>31<br>32<br>32<br>32<br>34<br>36<br>38<br>38<br>47<br>48 |

| 5.2 Temporal Codes                                                      |

|-------------------------------------------------------------------------|

| 5.3 Time as Basis for Information Encoding                              |

| 5.4 Rank Order Code                                                     |

| 5.5 Winners-Share-All (WSA)                                             |

| VI. Chapter 6: Applying WSA to a Classification Problem                 |

| 6.1 Network Architecture                                                |

| 6.1.1 Neuron's Model                                                    |

| 6.1.2 Synapse Model                                                     |

| 6.2 Layer 1: Converting Pixel Intensity into Spikes                     |

| 6.3 Layer 2: Extracting features from the Images                        |

| 6.4 Layer 3: Classification                                             |

| 6.4.1 Challenge 1: Learning71                                           |

| 6.4.2 Challenge 2: Inhibition                                           |

| 6.4.3 Challenge 3: Correlation in the input patterns                    |

| 6.4.4 Challenge 4: Greedy Attractor77                                   |

| 6.5 Results                                                             |

| 6.5.1 Weight Evolution                                                  |

| 6.5.2 Output Neurons Output                                             |

| 6.5.3 Classification                                                    |

| VII. Conclusion and Future Work                                         |

| 7.1 Conclusion                                                          |

| 7.2 Future Directions                                                   |

| References                                                              |

| Appendix I: MATLAB Code developed for Layer 1: Image Intensity to Spike |

| Conversion                                                              |

| Appendix II: MATLAB Code developed for Layer 2: Extracting Features98   |

| Appendix III: MATLAB Code Developed for Layer 3: Classification101      |

# List of Figures

| Figure I-1 Axon Hillock Neuron Model [34]                                                         |

|---------------------------------------------------------------------------------------------------|

| Figure I-2 The bistability circuit will drive the w node towards one of its two stable            |

| states.Figure adopted from [3]5                                                                   |

| Figure I-3 P-type Synapse Transistor [35]6                                                        |

| Figure II-1Memristor realization and typical hysteretic I-V behavior. (a) OFF state: An           |

| initial fil- ament is formed during a one-time formation process. No conductive channel           |

| exists; thus the device is in high resistance state. (b) Set process: positive voltage drifts the |

| dopants toward the filament, forming a channel, and decreasing the resistance. (c) ON state: a    |

| low-resistance channel is formed between the two electrodes. (d) Reset process: Applying a        |

| negative voltage repels the dopants and ruptures the channel, increasing the resistance.          |

| Adopted from [10]                                                                                 |

| Figure II-2 Memristors' main operating regions; Green: Diode region where tiny current            |

| passes through the device under the application of electric field. Yellow: Red region where       |

| enough current passes through the memristors to sense the state of the device without             |

| changing its state. Red: Switching region where the memristor switches from one state to          |

| another                                                                                           |

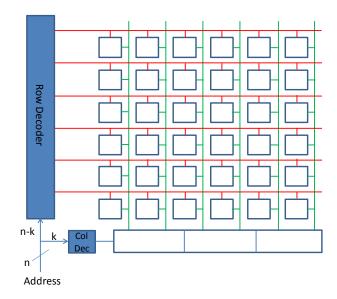

| Figure II-3 Standard memory architecture14                                                        |

| Figure II-4 1T-1R architecture. Memristors are accessed through selecting the series              |

| transistor15                                                                                      |

| Figure II-5 Crossbar memristor array with selected bits for reading and writing [11]16            |

| Figure II-6 CMOS Level Chip Architecture [11]17                                                   |

| Figure II-7 Cutting large crossbars into many small ones. Decoding the crossbar is                |

| equivalent to decoding a "blue pin" and decoding a memristor within that mini crossbar is         |

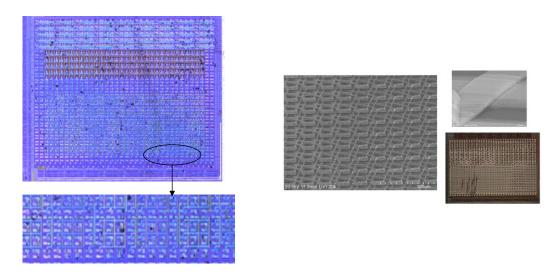

Figure III-4 a) Chip micrograph. Different parts of the chip are shown. b) Individual

devices integrated on the chip......27

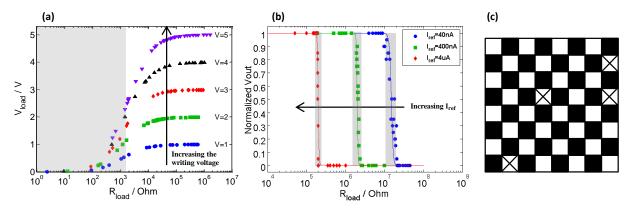

Figure III-6 a) Write circuitry characterization. As the resistive load decreases, the writing voltage drop across the load also decreases. b) Read circuitry characterization. The

Figure III-7 3D-integrated memristors on top of MAMA chip. on the left,

Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Ti/Pt memristors are used from Prof. Strukov's group. On the right, there are Pd/WO<sub>x</sub>/W memristors fabricated by Prof. Lu's group......31

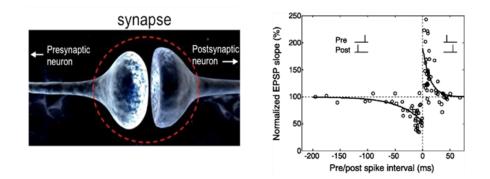

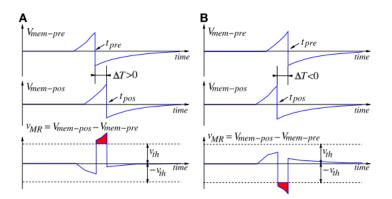

Figure IV-4 Membrane voltage waveforms. Pre-and post-synaptic membrane voltages for the situations of positive  $\Delta T$  (A) and negative  $\Delta T$  (B). Figure is taken from [18]......35

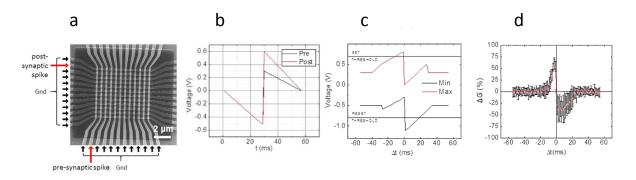

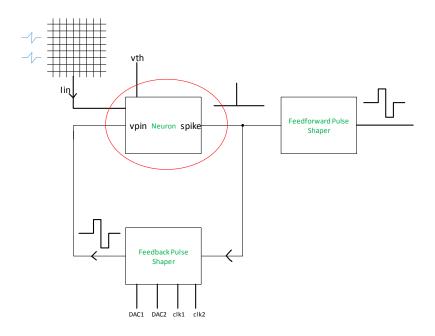

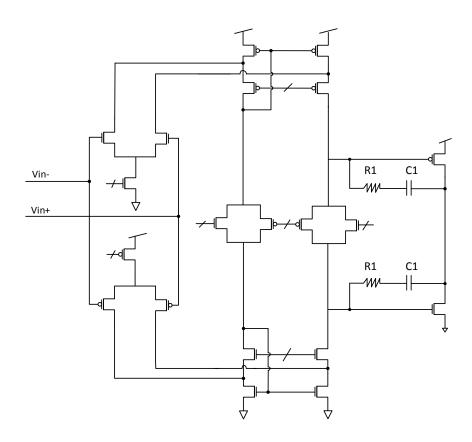

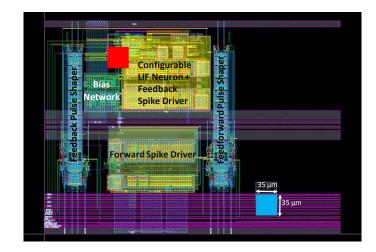

Figure IV-7 Complete neuron's model with feedforward and feedback pulse shapers. ....38

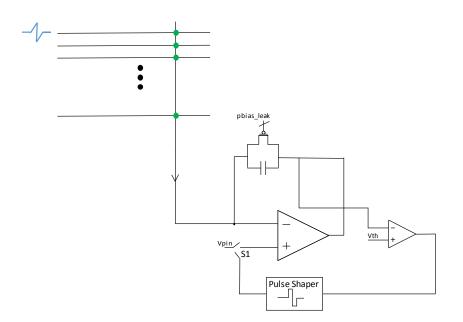

| Figure IV-8 Leaky integrate and fire neuron (1)                                             |

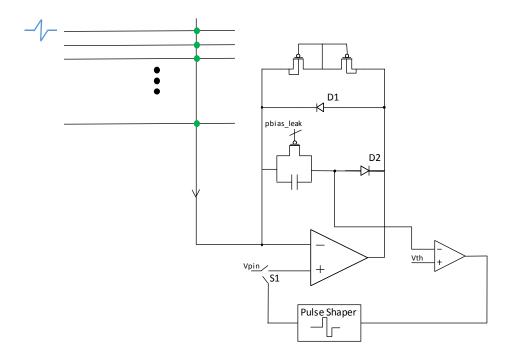

|---------------------------------------------------------------------------------------------|

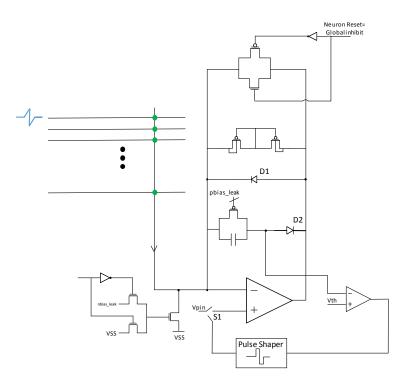

| Figure IV-9 Leaky integrate and fire neuron (2)40                                           |

| Figure IV-10 Complete leaky integrate and fire model41                                      |

| Figure IV-11 OpAmp topology employed for the integrator in the LIF neuron. The              |

| OpAmp has an extended common mode range at the input with a class A-B push pull at the      |

| output to drive the memristive crossbar array42                                             |

| Figure IV-12 Amplifier stay stable for more than 2 orders of magnitude to support the       |

| current needed to program the memristors in the crossbar array43                            |

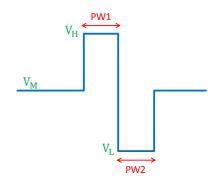

| Figure IV-13 Desired pulse shape with configurable parameters44                             |

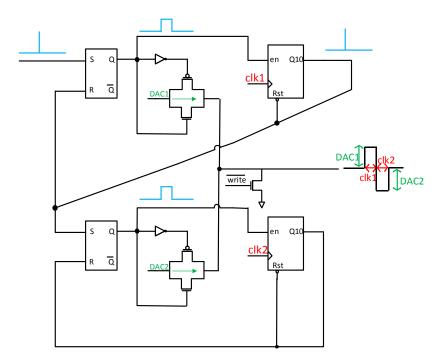

| Figure IV-14 pulse shaper design. Configurability is enabled through the use of DACs        |

| and clks                                                                                    |

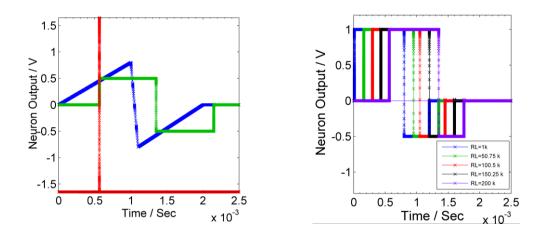

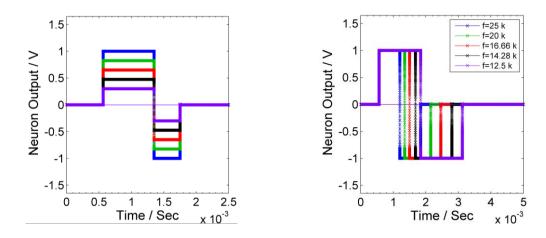

| Figure IV-15 Spectre simulation results illustrating the configurability of the pulse shape |

| through DAC (left) and clk (right)46                                                        |

| Figure IV-16 Complete layout of the LIF neuron with feedforward and feedback pulse          |

| shapers. Red and Blue pins are placed to enable CMOL implementation of memristors for 3D    |

| integration47                                                                               |

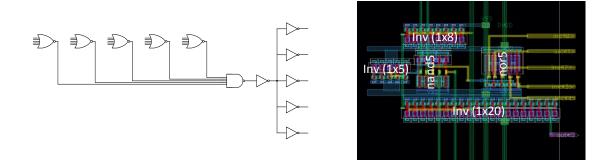

| Figure IV-17 Inhibition block schematic (left). Layout of one of the 5 sections (right)48   |

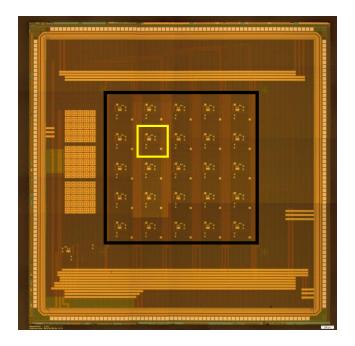

| Figure IV-18 Complete layout of the LIF neurons 5x5 array. Each neuron takes an area of     |

| 500 x 500 μm <sup>2</sup>                                                                   |

| Figure IV-19 Chip Micrograph in Silterra 180 nm49                                           |

| Figure V-1 Simple model of the biological neurons (left). First mathematical model of the   |

| neurons (right). Figure is taken from [26]                                                  |

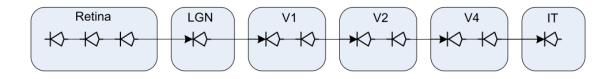

| Figure V-2 Neural pathway from the retina to the inferotemporal cortex, where visual            |

|-------------------------------------------------------------------------------------------------|

| objects are recognized. Figure taken from [36]                                                  |

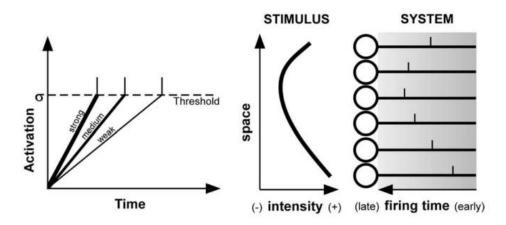

| Figure V-3 Intensity to latency conversion. The stronger the input, the faster the neuron       |

| spikes. Figure is taken from [30]52                                                             |

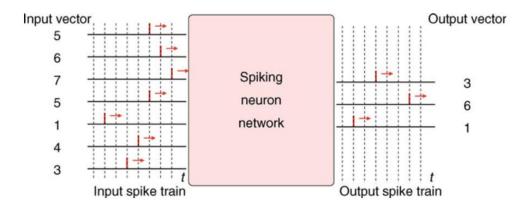

| Figure V-4 Illustration of using temporal codes for computation. Time is divided into           |

| time windows and information can be encoded depending on which neurons spike in each            |

| time window. Figure is taken from [26]53                                                        |

| Figure V-5 Possible neural codes provided by the temporal coding. Figure is taken from          |

| [37]                                                                                            |

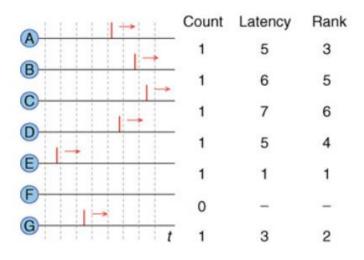

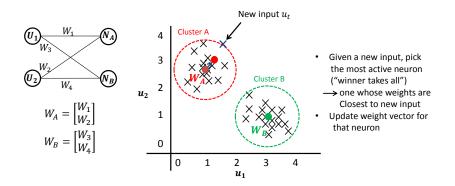

| Figure V-6 Competitive Learning- Each output neuron represents a cluster. N_A and               |

| N_B represent cluster A and B respectively and $W_A$ and $W_B$ are the centers of the clusters. |

| Upon the arrival of every input pattern, the winner neuron's weights adjust themselves to get   |

| closer to the input pattern                                                                     |

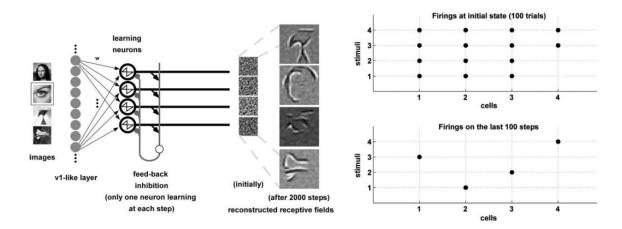

| Figure V-7 Emergence of selective responses of each neuron to a specific pattern. Lateral       |

| inhibition is applied as a winner takes all mechanism and competitive learning results in the   |

| assignment of each pattern to the emission of one spike from one neuron. Figure is taken        |

| from [30]59                                                                                     |

| Figure V-8 Comparison of the number of output neurons required to recognize patterns            |

| between WTA (blue) and WSA (red) mechanism. As the number of patterns increase, the             |

| efficiency of using WSA becomes more apparent60                                                 |

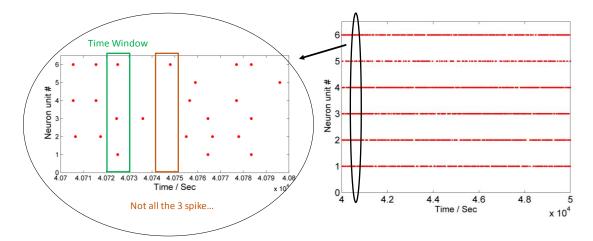

| Figure V-9 The case with two similar rank codes in which only the rank of two last              |

| spikes are different61                                                                          |

| Figure VI-1 Training set and Test set patterns used for the classification problem63            |

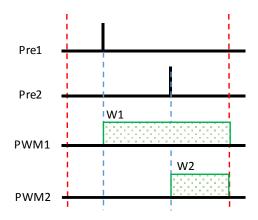

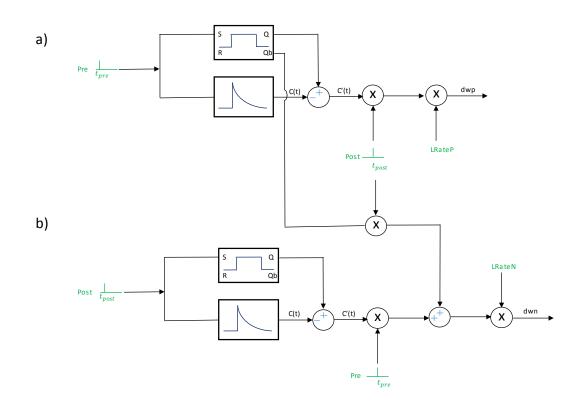

Figure VI-7 Spiking learning algorithm developed for WSA. Calcium concentration models are used as part of the Anti-STDP rule to calculate dwp and dwn......73

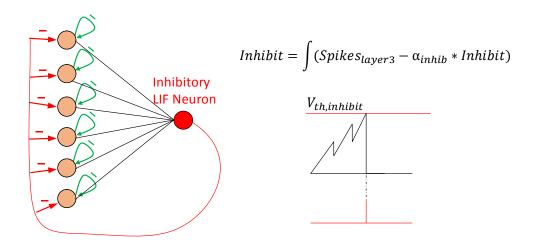

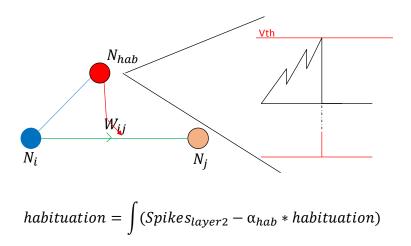

Figure VI-9 Habituation neuron designed to ignore the similarities between the input patterns and look for the differences between patterns which helps to separate patterns.......76

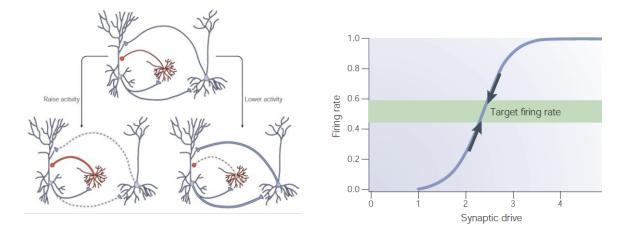

| Figure VI-10 Concept of homeostatic plasticity in the brain. Feedback mechanisms are           |

|------------------------------------------------------------------------------------------------|

| applied in order to keep the firing rate of a neuron in a target range. Figures are taken from |

| [32]                                                                                           |

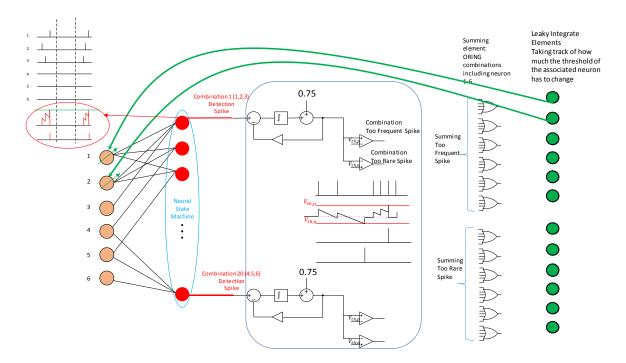

| Figure VI-11 Neural State Machine (NSM) designed to control the appearance frequency           |

| of the WSA codes                                                                               |

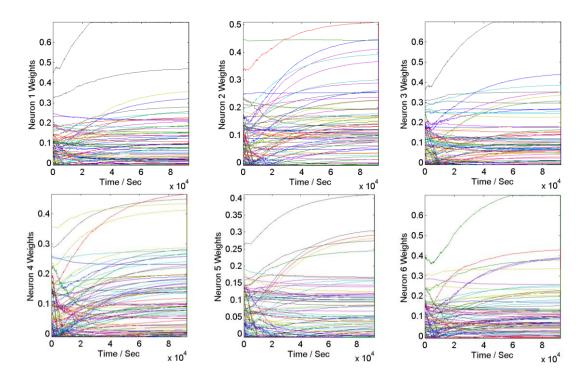

| Figure VI-12 Weight evolution showing the weights converging to analog values83                |

| Figure VI-13 Network performance on the test set. On the left, the network accuracy            |

| converges to 87%. On the right, each pattern gets assigned to a unique combination from a      |

| set of 41 codes in the code space                                                              |

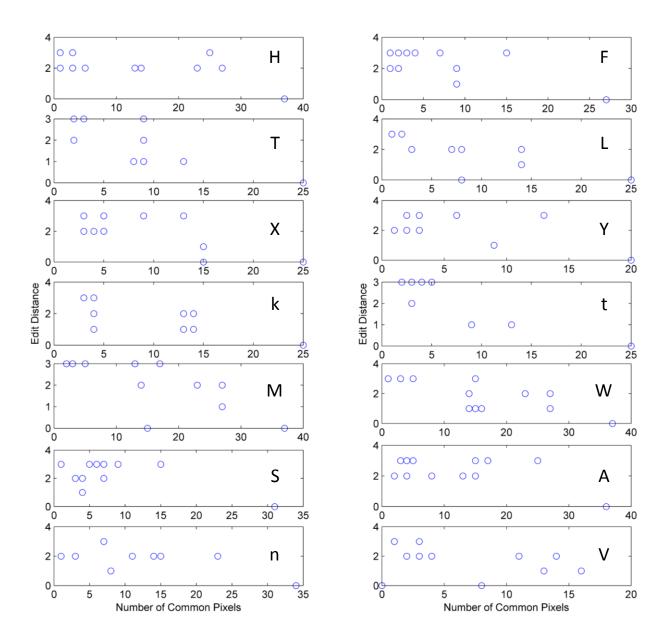

| Figure VI-14 Edit distance vs Pattern similarity for all the patterns                          |

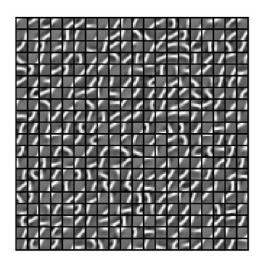

| Figure VII-1 400 features extracted from MNIST training set by training an                     |

| autoencoder                                                                                    |

## I. Chapter 1: Introduction

There has been a long standing dream to make computers that work like the brain and scientist have been working on this problem for decades now. However, the gap between the state-of-the-art computers and the brain is still very large. The most important reasons why are because:

1) Computers and the brain have a fundamentally different way of computing. Computers have a deterministic approach in processing the input data. There are well-defined logic gates which take 0 and 1 logic levels as inputs, and output appropriate 0s and 1s depending on the logic function. Whereas the brain takes a self-organizing method of computation, meaning that it *learns* from mistakes. Let me give the example of throwing a ball into the basket. If we were to *program* a conventional computer to achieve this, all the physical laws of gravity would have had to be defined in the program, taking into account details such as the size of the ball, and also environmental factors such as the wind or rain and ask the computer to *calculate* the initial velocity and direction of throwing the ball in order to make it to the basket. The brain, however, has a completely different approach. The ball is thrown and if it does not make it to the basket, it *learns* from its mistake. The solution to the problem of targeting the ball into the basket overshoots and undershoots until the goal is reached. That's how the brain *self-organizes* the solution to an unknown problem, by trial and error.

2) In computers the execution of instructions is *rather* sequential. The reason why I say "rather" is because today's computers take advantage of a lot of parallelization using GPUs. However, the parallelization works as dividing tasks between different processing cores but execution of each task at a specific core is still sequential. This is while the brain

processes information massively in parallel: millions of processing units all working *at the same time*.

3) While brain uses these millions of processing units in parallel, which are connected to each other through billions of connections, it only consumes a few tens of watts. If we were to run "human-scale" simulations of the brain running in real time, using the best supercomputers, that would consume about 12 Giga watts of power. [1]

The reasons mentioned above makes it clear why building a "brain-inspired" computer is the next computing paradigm. These computers will be

- a) Efficient in terms of energy and space

- b) Scalable to large networks

- c) Flexible enough to run complex behavioral model

Considering how far we have come in silicon industry and all the advances in the field of neuroscience and AI, could make us wonder what is stopping us from making these computers? The answer lies of course in limitations we face because of the physical properties of silicon chips. Below I will talk about the major bottlenecks of building such computers.

#### **Bottlenecks of implementing brain-inspired computers**

Centralized von Neumann architecture is fundamentally not suitable for representing massively interconnected neural networks. In this type of architecture, used in conventional computers, the processing unit and the memory are separated from each other. When there is an instruction to be executed, special part of the memory is addressed, the data is fetched and is processed in the CPU. This is fundamentally in contradiction with how the brain performs the computation where the memory is localized to the processing unit and is distributed all across the brain. In order to make brain-like computers we should also use these distributed computing-memory agents, namely **neurons** and **synapses.**

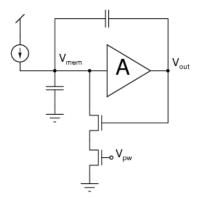

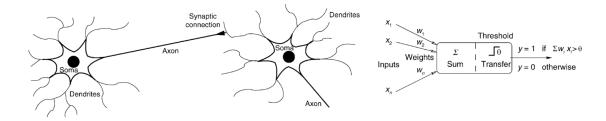

Figure I-1 Axon Hillock Neuron Model [34].

## 1.1 Silicon Neurons

Silicon neurons emulate the electro-physiological behavior of real neurons. This may be done at many different levels, from simple models (like leaky integrate-and-fire neurons) to models emulating multiple ion channels and detailed morphology. Depending on the application and the level of sophistication required, different models could be used. Leaky integrate and fire models are less realistic and do not take into account many of the details of what's going on inside a neuronal cell. But they are simple and need very small area since the number of transistors used in the circuit is minimal.

The first leaky integrate and fire model which was proposed by Carver Mead in the late 1980s is shown in Figure I-1. In this circuit, a capacitor that represents the neuron's membrane lipid bilayer integrates input current into the neuron. As soon as the capacitor reaches the neuron's threshold, a pulse  $V_{out}$  is generated, the membrane potential  $V_{mem}$  is reset through the NMOS transistors and the neuron will be ready for the next current injection.

## 1.2 Silicon synapses

Conceptually, synapses can be modeled as the connection between neurons with an associated strength (weight). In fact, synapses are the adaptive learning agents in the brain: Neurons receive inputs and fire, so they have a very specific task: when the membrane potential is above a threshold, they fire. However, the synapse's strength has dynamics and will change in the process of learning. These changes are continuous and *analog* rather than digital. Therefore, in order to mimic the synaptic behavior into the silicon we need nonvolatile *analog* memory storage with locally computed memory updates. Note that in order to perform brain-like functions, a large number of artificial synapses are needed.

Throughout the history of neuromorphic engineering, circuit designers tried many different options as analog memory for artificial synapses. I'll briefly go over each of them below.

### 1.2.1 Capacitors

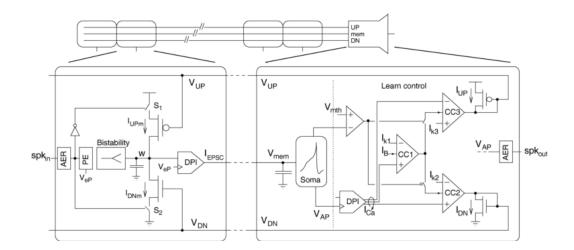

Capacitors are the first obvious choice for analog memory. They accumulate the charge and develop a voltage across their capacitive plate. The only important problem is that they leak. So they are not truly non-volatile as they slowly lose the charge. However, different solutions have been proposed to overcome this problem. For example, using techniques such as generating negative gate-source voltage across the series transistor in order to reduce the leakage below the "off subthreshold current" [2], or using them only as an analog memory while learning ,and then register the value as a single digital bit depending on the analog value of the capacitor voltage. This is called Fusi learning [3]. The idea is presented in Figure I-2 shown below.

Figure I-2 The bistability circuit will drive the w node towards one of its two stable states. Figure adopted from [3].

In other words, the synapse value is analog in the short term and digital in the long run. The positive feedback loop in the circuit will drive the capacitive charge towards a digital 1 or zero depending on the current value of the capacitor voltage. If the capacitor voltage is higher than a positive V<sub>th,p</sub> it will slowly charge the capacitor through a small subthreshold current to VDD and if that's lower than a negative V<sub>th,n</sub> it will discharge it towards VSS. Although this is a prominent solution, there are two issues rising from it: i) Although some neuromorphic engineers argue that for neural network applications, a few number of bits are enough [4], employing a true analog memory has advantages which I will talk about some of them later in the thesis. Simply put, since digital synapses are a big approximation we could easily end up with relatively large errors on applications such as pattern recognition. ii) One limitation of using one capacitor for each synapse is that it takes a large area on chip. If the technology process does not provide MIM (Metal-Insulator-Metal) capacitor structures, then having a capacitive memory means we need to have a memory array at one part of the chip and having neurons in another part which is employing the von Neumann architecture. For reasons we discussed before using this architecture is fundamentally different from what the brain does

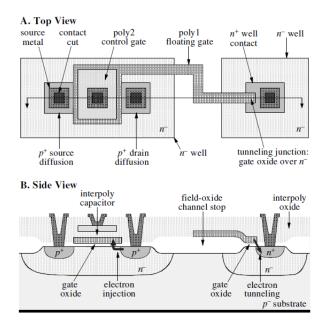

Figure I-3 P-type Synapse Transistor [35].

and will limit us in parallelizing the structure. Even if the technology process provides a MIM capacitor structure, the supporting circuity needed for each synapse in order to enable online-learning is very area-hungry and will only work for small networks.

### 1.2.2 Flash

In the late 90s, C. Diorio and his colleagues in Carver Mead's lab fabricated synapse transistors that not only possessed nonvolatile analog storage, and compute locally their own memory updates, but also allowed local computation of the product of their stored memory value and the applied input. To ensure nonvolatile storage, they used standard floating-gate MOS technology, but adapted the physical processes that write the memory to perform a local learning function [5]. Figure I-3 shows the p-type of this synapse transistor.

The underlying process of non-volatility of the memory lies in trapping electrons in the floating gate by employing hot-electron injection which is a well-known process in MOSFETs.

It occurs in short-channel devices with continuous channel currents, when a high gate voltage is combined with a large potential drop across the short channel. Injecting electrons into the floating gate will cause a negative voltage to develop on the gate and hence it will decrease the threshold voltage of the PMOS, increasing the "weight" of the synapse transistor. On the contrary, in order to remove charge from the floating gate and decrease the synaptic "weight", positive high voltages should be applied to the tunneling implant to remove electrons from the floating gate, thereby increasing the floating gate voltage.

The advantage of this method is that the weight multiplication by the input is done locally and without any extra circuity. So it's area-efficient and local. The disadvantages of using these synapse transistors are i) There is not a full-blown model of these transistors available in CAD tools such as Cadence virtuoso. Therefore, when laying out these devices, the standard CMOS process transistors cannot be used and hence the functionality of these devices cannot be ensured before their fabrication. ii) Increasing and decreasing the weights are not trivial. High voltages are needed in order to facilitate hot-electron-injection and tunneling mechanisms. These high voltages need to be generated on chip (or by connecting from an I/O whose ESD protection diodes have been removed) and will decrease the oxide life time.

### 1.2.3 Multiple SRAMs

Yet another method of building electronic synapses employed by researcher throughout the years have been to use multiple SRAMS [6]. In this method, few bits of memory are devoted to each synapse. Analog values of synapse are digitized using a DAC and are kept in the SRAM. When reading, the SRAM memory bits are fed into an ADC and the analog value is used in the circuit. The advantage of this method is that it's very robust since the memory is kept digitally. The disadvantages are i) it's volatile. So with the loss of power the memory will

be reset. ii) It's very computationally expensive and area inefficient to use an ADC and a DAC for *every* synapse. These ADCs and DACs can be shared but that serializes the process and also needs extra circuitry in order to priority encode which synapse will take use of the shared DAC and the ADC.

## 1.3 Overview

As stated above, one of the most important bottlenecks of building computers that work like the brain, is to make artificial synapses. Although there have been many attempted solutions for this problem, packing a large number of silicon synapses in a small area enabling the local learning remains an issue. In this thesis, I have investigated a two pronged approach namely *spatial* and *temporal* to tackle this problem.

### 1.3.1 Spatial approach: Memristors

In recent years, memristors have emerged as a solution for the connectivity problem. These nano-devices can be densely integrated on top of CMOS chips and can serve as analog memory needed to imitate synapses. What makes memristors a perfect candidate as an artificial synapse is not only because they have a nano-size footprint and they take no silicon space, but also they are non-volatile analog memory. Also, they imitate biological synapses very well since the multiplication of the weight (Memristor's conductance G) to the input current (I) occurs automatically through Ohm's law (I=GV). The adaptive conductance of the material could serve as "analog weights" which develop voltages across the devices, depending on the current passing through them as inputs to the network.

As a first step in realizing integrated memristors as artificial synapses, we designed a programmable CMOS chip enabling direct integration of memristor. In a collaborative MURI

project, a CMOS memory platform was realized for the memristive memory array in a hybrid/3D architecture (CMOL architecture [7]) and memristors were successfully integrated on top of it. After demonstrating feasibility of post-CMOS integration of memristors, we designed a second chip containing an array of spiking CMOS neurons with an area of 5mm x 5mm in a 180nm CMOS process to explore the role of memristors as synapses in neuromorphic chips.

### 1.3.2 Spatio-temporal Coding Approach

While physical miniaturization by integrating memristors is one facet of realizing areaefficient neural networks, on-chip routing between silicon neurons prevents the complete realization of complex networks containing large number of neurons. A promising solution for the connectivity problem is to employ spatio-temporal coding to encode neuronal information in the time of arrival of the spikes. Temporal codes open up a whole new range of coding schemes which not only are energy efficient (computation with one spike) but also have much larger information capacity than their conventional counterparts. This can result in reducing the number of connections to do similar tasks with traditional rate-based methods.

By choosing an efficient temporal coding scheme, I have developed a system architecture by which pattern classification can be done using a new algorithm dubbed "Winners-share-all" instead of a "Winner-takes-all" mechanism. Winner-takes-all limits the code space to the number of output neurons, meaning n output neurons can only classify n pattern. In winnersshare-all we exploit the code space provided by the temporal code by training different combination of k out of n neurons to fire together in response to different patterns This thesis will be divided into two major parts: Spatial and Spatio-Temporal approach. In Chapter 2,3, and 4, I cover the spatial approach which studies the role of memristors as synapses in neuromorphic chips. In chapter 2, I briefly introduce memristors and talk about some of the background work on different memristive architectures. Chapter 3 will cover the details of the first chip we taped out which incorporated a means for 3D-integrating Memristive Arrays for Memory Applications (MAMA). After demonstrating the feasibility of post-CMOS integration of memristors on MAMA chip, I then explain, in chapter 4, how we took the next step to design an array of spiking CMOS neurons on a second chip to explore the role of memristors as synapses in neuromorphic chips.

The second part of this thesis is devoted to the Spatio-temporal coding approach to reduce the number of connectivity needed on chip by exploring the code space provided by the temporal codes. Chapter 5 will introduce the concept of information encoding in time and a summary of background work on this area. I will then propose the Winners-Share-All (WSA) algorithm using the temporal code and compare it to the conventional Winner-Takes-All (WTA) counterpart. In chapter 6, I describe how I used this new algorithm to perform a rather simple recognition task to cluster 14 letters of English alphabet. And finally chapter 7 will summarize the work of this PhD thesis and discuss the future directions.

## II. Chapter 2: Memristors and Memristive Architectures

As the basic building block of electronics, field effect transistor (FET), approaches the 10nanometer regime, a number of fundamental and practical issues start to emerge due to difficulties in nanometer-resolution fabrication, electrostatic control and power management. New devices and architectures are expected to continue the scaling trend the semiconductor industry has enjoyed in the past decades. Two-terminal resistive switches (also called memristive devices or memristors) have attracted increasing interest as a suitable alternative to complement transistors. [8]. In this chapter I introduce memristors and explain its underlying mechanism. I will also talk about the architectures developed for these nano-devices and how they can be used for neuromorphic applications.

### 2.1 What is a memristor?

As can be guessed by the name, it's a memory resistor: A two-terminal switch which can retain its resistive state based on the history of the applied field and hence it's an analog nonvolatile memory. They are simple passive circuit elements, but their function cannot be replicated by any combination of fundamental resistors, capacitors and inductors [9].

Memristors are typically based on a Metal-Insulator-Metal (MIM) structure. An otherwise insulating film is sandwiched between two conductive electrodes. The choice of material for this MIM structure has been under extensive research with different stacks. The underlying switching mechanism seems to differ for a variety of electrode and memristive materials:

The mechanism can be attributed to a) phase change due to Joule heating in chalcogenidebased phase-change memories. b) conductive filament formation due to Joule heating observed in certain oxides such as TiO2. c) conductive filament formation due to electrochemical redox

Figure II-1Memristor realization and typical hysteretic I-V behavior. (a) OFF state: An initial fil- ament is formed during a one-time formation process. No conductive channel exists; thus the device is in high resistance state. (b) Set process: positive voltage drifts the dopants toward the filament, forming a channel, and decreasing the resistance. (c) ON state: a low-resistance channel is formed between the two electrodes. (d) Reset process: Applying a negative voltage repels the dopants and ruptures the channel, increasing the resistance. Adopted from [10].

processes observed in binary oxides (e.g. NiO, CuO<sub>2</sub>, TiO<sub>2</sub>) or chalcogenides, and polymers d) field-assisted drift/diffusion of ions in amorphous films and e) possible conformational changes in molecules. [8]

Figure II-1 shows an example of a memristors in which Pt is used as the electrode and  $TiO_2$  as the switching material. There are also some oxygen vacancies in the form of  $TiO_{2-x}$  which act as charged dopants and can respond to the electric field. In the initial state, a filament of conductive  $TiO_{2-x}$  is formed in the non-conductive  $TiO_2$  film in an irreversible forming step. However, the formed filament does not connect the two electrodes together and thus the device is in a High Resistance State (HRS). In order to switch the device ON, a sufficiently high positive voltage is applied across the device which attracts positively charged vacancies in the

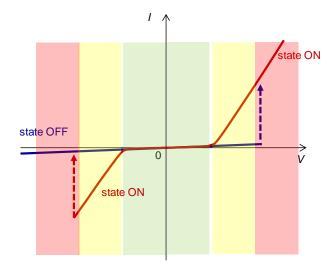

Figure II-2 Memristors' main operating regions; Green: Diode region where tiny current passes through the device under the application of electric field. Yellow: Red region where enough current passes through the memristors to sense the state of the device without changing its state. Red: Switching region where the memristor switches from one state to another.

oxide to the top electrode. This will cause the filament to grow since the vacancies start to drift through the most favorable diffusion paths in the presence of the electric field and hence they form a channel between the two electrodes. Once such highly conductive channels are formed, the device is in Low Resistance State (LRS) and considered as ON [10].

The onset of the figure is illustrating the I-V characteristics of the memristors which exhibits an inherent memory with a "pinched hysteresis" which can be used for information storage. For example, in the case of resistive memory RRAM, by assigning LRS="1" and HRS="0", or in the case of analog memristors, a spectrum of resistive values ranging from a HRS to a LRS.

The I-V characteristic of memristors have 3 main operating regions which are highlighted in Figure II-2. The green region in the middle is called a "diode region" where the device acts like a reverse biased diode. In the diode region, there is very little current passing by for the voltage being applied across the device. The region shown in yellow is the "read region" in which the state of the device can be read without changing or disturbing its value, since the

Figure II-3 Standard memory architecture.

voltage is not high enough to surpass the device threshold for switching. The voltage range in the yellow region is "read voltage" which is applied across the device and by sensing the current passing through, the resistance of the memristor can be measured. The region illustrated in Red in Figure II-2 is where the device switches to the other state. This "write region" consists of voltage levels which are greater than the threshold voltage of the device and hence are strong enough to move the dopants and change its resistance.

These three main operating regions provide a design tool in order to use these devices as memory elements and perform the desired operation on them.

## 2.2 Memristors as Memory Elements

As a first step in using memristors as memory elements we can think of replacing them with conventional memory elements in standard memory platforms. Figure II-3 shows such platform in which each memory device has an access transistor in series and a certain address

Figure II-4 1T-1R architecture. Memristors are accessed through selecting the series transistor.

in the array accessible by its row and the column. The address is fed serially to the array, the row and the column are decoded and the desired operation (read/write) is performed.

Replacing these memory devices with memristors, we end up with an architecture dubbed "1T-1R", shown in Figure II-4, which consists of one resistive memory in series with one access transistor at each row and column.

However, having a series transistor defeats the purpose of using these nano-devices for high-density packing of the memory since for each memory element, the limitation is still the size of the transistor. Moreover, the current needed for switching of these devices, depending on the range of the memristor can range anywhere from 10s of  $\mu$ As to 10s of mAs which applies a constraint on the size required for the series transistor having to be able to drive the required current for switching of its corresponding memristor. So can we somehow remove the access transistor? The problem raised by doing so is addressability of the memory elements. The reason why the transistor is addressable is because it's a 3 terminal device; However, by removing the access transistor we are now left with a completely resistive array which is called

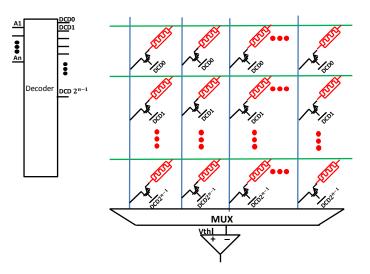

Figure II-5 Crossbar memristor array with selected bits for reading and writing [11].

the "crossbar array". The crossbar array can be implemented using 2 perpendicular layers of parallel nanowires where a memristor is formed at each cross section. In the following section I will explain how crossbar arrays can be used to replace conventional memory for a highly dense memory array.

#### 2.2.1 Crossbar

As was discussed in the previous section, in order to gain from the density of memristors, cross bar arrays are used, however, their use comes with challenges since the array is fully passive which I will be addressing in this section.

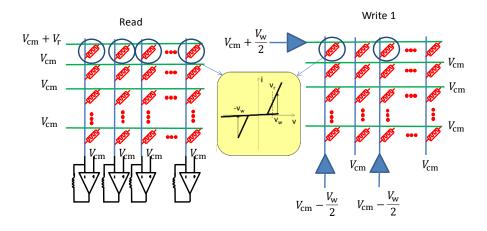

Selecting the devices in the crossbar array is performed through the application of appropriate voltages across the horizontal and vertical nanowire of the desired memristor. Figure II-5 illustrates this idea for the read and the write mode.

One row can be read simultaneously by applying  $V_r$ , a voltage in the read region of the memristor, on the horizontal line and pinning the other side, the vertical line, to zero and reading off the current using a trans-impedance amplifier. To program an individual memristor to a HRS ("0") or to a LRS ("1") -V<sub>w</sub> or V<sub>w</sub> should be applied across the memristor

Figure II-6 CMOS Level Chip Architecture [11].

respectively. However, having  $V_w$  on one side and 0 on the other side, will cause unwanted memory elements to get programmed which is undesirable. In order to solve that problem, to program a certain memristor,  $V_w/2$  is applied to one side and  $-V_w/2$  is applied to the other side. This way, the non-selected devices have half of the  $V_w$  across them which is designed to lie in the read region and therefore it does not cause a state change in the device [11].

Figure II-6 depicts the CMOS level chip architecture to support the crossbar array. 3 level muxes at row and column are used to determine the read/write mode, the row/column select and Write 0 or Write 1 for the write mode. By choosing these 3 bits, desired operation is done on the desired memristors.

Overall, the memristor-based crossbar network structure can offer the following advantages: 1) it allows ultra-high density memory storage with relatively small number of control electrodes: n2 cross-points can be accessed by n-rows and n-columns in the crossbar; 2) it offers large connectivity between devices; and each column or row is connected to n-rows or columns through n different devices. However, a new challenge rises as the size of the

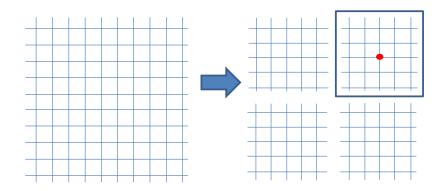

Figure II-7 Cutting large crossbars into many small ones. Decoding the crossbar is equivalent to decoding a "blue pin" and decoding a memristor within that mini crossbar is equivalent to decoding a "red pin". Every combination of red and blue chooses a unique memristor.

crossbars gets larger and larger since the parasitic resistance of the nano-wire becomes comparable to the memristance and the applied voltages to the crossbars will drop across the parasitic resistance instead of the memory device. Moreover, the speed of the write or read deteriorates a lot because of the large capacitances on the nanowire caused by the large size of the crossbar. In the next section of this chapter I introduce CMOL architecture which tackles this problem to enable high density 3D memory in CMOS chips.

#### 2.2.2 CMOL Architecture

CMOL architecture was first introduced by Strukov. et al in [12] as a solution for densely packing memristive devices on top of CMOS chips and I'll be explaining it from my own point of view in this section.

As I mentioned before, the problem with large crossbars becomes the undesired parasitic on the nano-wires. Therefore, instead of having a large crossbar we could instead use multiple smaller crossbars. This idea is shown in Figure II-7. In order to address an individual device, one row and column is required to address the crossbar in which the device is located in, and one row and column is required to address the device within the crossbar. Therefore, a double

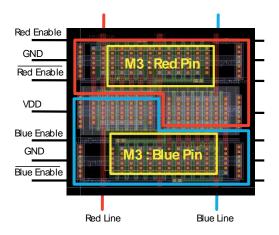

Figure II-8 CMOL architecture consists of reds and blue pins in an area distributed interface.

decoding scheme is asked for in order to access the device. In CMOL terminology, we call addressing the crossbar, selecting the "blue pin" and selecting the device inside the crossbar, decoding the "red pin".

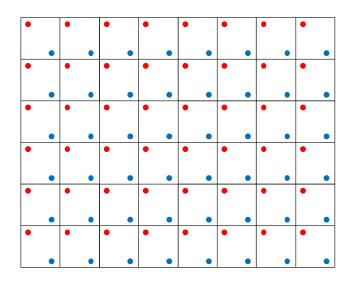

If these red and blue pins are distributed in the CMOS surface, we end up with an area distributed interface as is shown in Figure II-8 .Addressing each blue pin will select an area of crossbars and addressing the red pin within that region selects the desired device. Each square containing one blue and one red pin is a "CMOS Cell" which contains the supporting CMOS circuitry for addressing the memristive devices. The red and the blue pin are the interface connecting the underlying CMOS to the integrated top and bottom crossbar nanowires, respectively.

This seems to be solving all the problems, however, if the crossbars are fabricated in a Manhattan grid fashion, the pitch between the crossbars are dictated by the CMOS cells pitch which is much larger than the memristive nano-size and it defeats the purpose of employing memristors. Therefore, in order to exploit the intrinsic nanoscale dimensions of memristors, decoupling the underlying CMOS feature size from the device is required. One method of

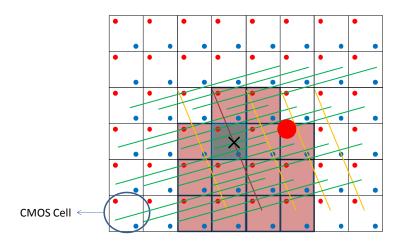

Figure II-9 Every red and blue pins are embraced inside a CMOS Cell. Every CMOS Cell is connected to a neighborhood of CMOS Cells thorough a mini-crossbar. This is shown in pink in this figure and is dubbed the connectivity domain of the CMOS Cell shown in gray.

decoupling is to rotate the nanowires. Such rotation ensures that a shift by one nanowire corresponds to the shift from one interface pin to the next one (in the next row of similar pins), while a shift by r nanowires leads to the next pin in the same rows (Figure II-9). The bottom nanowires are passed through blue pins and the perpendicular top nanowires are passed through red pins. At the cross-point of these nanowires memristors are formed which are addressable through the red and the blue pin connecting to its corresponding nanowires. This is demonstrated in Figure 2.9. The colored region highlights the crossbar selected by addressing the blue pin shown with a larger blue circle. The CMOS cell containing this blue pin is connected to all the CMOS cells in the highlighted region through the memristive cross points inside this region. Therefore, the colored area is the "connectivity domain" of the selected CMOS cell. The device marked by X inside the colored region can be selected by addressing its corresponding red pin illustrated with the large red circle in Figure II-9.

CMOL tackles fabrication issues such as interlayer alignment accuracy and integration of nanoscale devices over a CMOS sub-system with larger scale feature size. Moreover, it provides high- density memory with less parasitics by sharing select circuitry between multiple memristors (1T-1R vs 1T-NR).

How can we use this architecture in order to design functional memory arrays? This is the question I will be answering in the next chapter by describing the CMOS memory platform we designed in CMOL architecture for 3D memristor integration.

# III. Chapter 3: Memory Access controller for Memristor Applications (MAMA) Chip

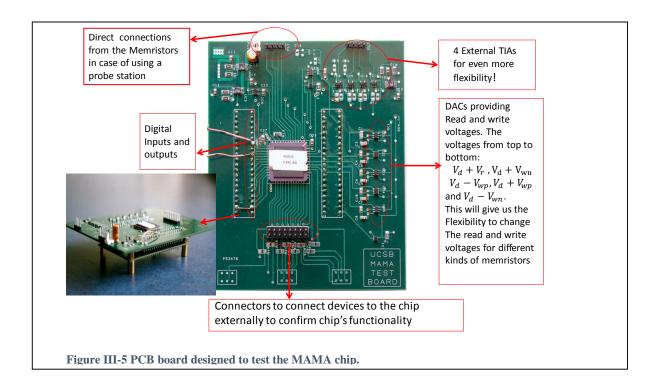

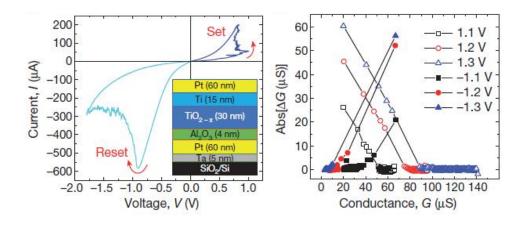

With this vision of a monolithic, 3D-integrated CMOL memory platform in mind, we have designed and tested the first prototype of the CMOL architecture complete with integrated memristors. This chapter focuses on the challenges involved from a circuit design perspective and the steps taken to support memristors with different ranges of resistance, threshold voltages, on/off ratio etc. More in-depth analysis of the architectural trade-offs can be found in [13] and details of the memristor integration is discussed in [14].

The plethora of memristive device designs, each with their unique advantages, requires a flexible supporting circuit architecture. The circuit design is strongly influenced by the connectivity imposed by the area-distributed interface and also the chip architecture which is designed to reflect the CMOL idea. We term this versatile chip the Memory Access controller for Memristor Applications (MAMA). A key circuit requirement for the MAMA chip is the ability to handle memristors with different  $R_{on}/R_{off}$  values, and provide the appropriate write and read voltages. This chapter explains the configurable architecture and circuits designed as a platform for integrating different kinds of memristors.

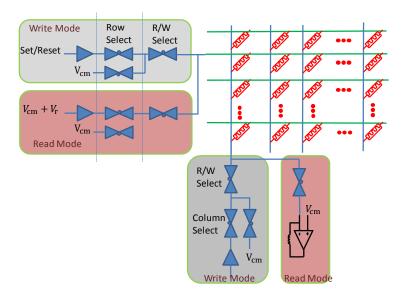

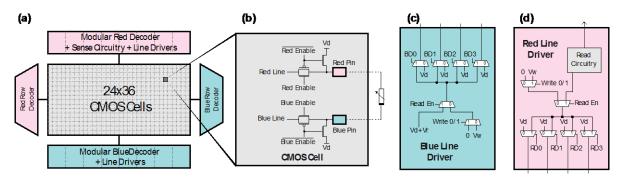

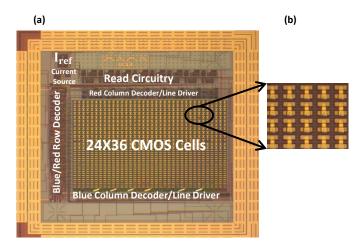

## 3.1 Chip Architecture

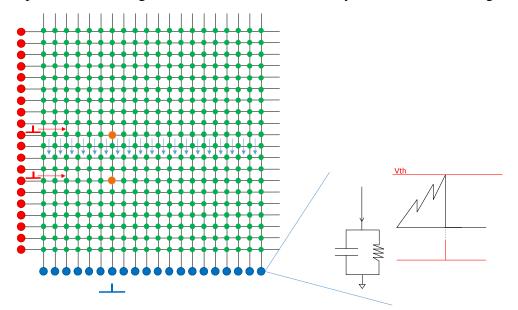

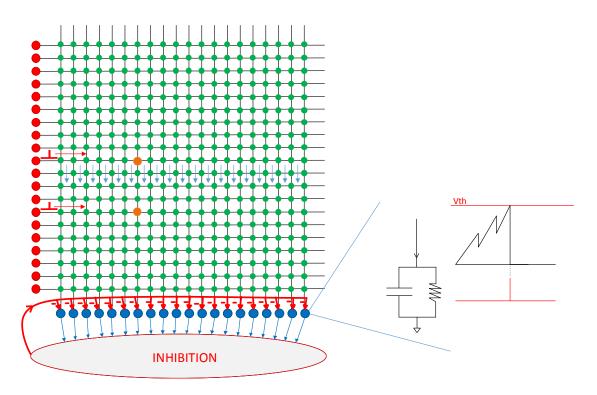

The chip consists of an array of CMOS cells, double decoders, programming drivers and sensing circuitry shown in blocks in Figure III-1 a. Each CMOS cell houses select circuitry including Red and Blue pins required by the area-distributed interface (Figure III-1 b).

Figure III-1 a) Overall chip architecture. b) CMOS cell. When the transmission gates are selected by Red/Blue enable signals, they connect the Red/Blue lines to the Red/Blue pins which are the interface to the integrated memristors. c,d) Blue and Red line drivers which places the appropriate voltages on the Red/Blue lines [15].

Selecting two of these Red and Blue pins accesses two of the segmented nanowires and hence a unique memristive device at the cross-point. A row-column decoder in turn accesses these pins. Thus it requires a double decoding scheme. The double decoders surround the CMOS cell array and have their function split among the Blue/Red row/column decoders. Depending on the desired operation (Read/Write) the Blue/Red line drivers place appropriate voltages on the Red and Blue lines (*Figure III-1*. c,d) which connects to the Red/Blue pins through the CMOS Cell select circuitry (*Figure III-1* b). For example, during the read operation, V<sub>r</sub> is applied across the desired memory cell and the sensing circuitry makes a binary decision regarding the memristor state and the data is shifted out serially. In the following sections the details of the circuitry in these blocks are described.

## 3.2 Writing Circuitry (CMOS Cell Design)

To write on a particular memristor, the device is addressed and the appropriate write voltages are applied across it. This is done through CMOS cells shown in Figure III-1 b. It includes two transmission gates controlled by Blue/Red enable signals routed from the double decoder. When the gates are asserted, they drive the Red and Blue pins with the appropriate

Figure III-2 CMOS cell layout. Metal 3 is used as the interface with integrated memristors. This cell occupies an area of  $32 \times 32 \mu m2$  in a 0.5 $\mu m$  process.

voltages on the Blue/Red lines. De-assertion connects the pins to a default voltage,  $V_d$ , in order to avoid floating problems such as leakage or unpredictable state-changes due to unwanted noise sources.

The transmission gates together with the memristors comprise a voltage divider. To ensure the memristor's operation in the desired region (i.e. the write region), the voltage drop across the transmission gates must be negligible. Therefore, these pass gates need to be sized accordingly.

However, the size of the transmission gates imposes a limitation on the number of CMOS Cells which can fit in the chip and hence the size of the memory supported by the chip. As a result, there is a trade-off between the maximum current drive and the size of the integrated memory on the chip.

Given these constraints, a size of W/L= $42\mu$ m/0.6µm in 0.5 µm process is chosen for the pass gate transistors. The maximum current supported by these transmission gates for a range of input voltages is reported in the next section. This maximum current can be considered as the compliance current limiting the current passing through the memristors and hence

preventing device break down [9]. Depending on the required write voltage, the minimum resistance supported by the chip can be calculated.

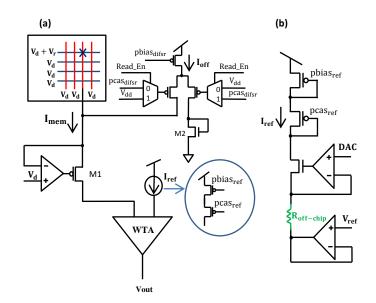

Figure III-3 Sensing circuitry. a) The current-sensing scheme. The memristor's current from the crossbar is compared against a reference current by the winner-take-all (WTA) circuit. b) A tunable reference current. The current can be changed by tuning the Roff-chip.

Layout realization of a CMOS cell is shown in Figure III-2. Since this CMOS chip needs to be post-processed for 3D memristor integration, the last metal layer in the On-Semi 0.5 $\mu$ m process (Metal 3) is crucial to the area-distributed interface. General power and ground routing cannot be done on this metal layer as it risks exposing and damaging these lines, therefore they are routed in Metal 2. The size of the pins comprising this area-distributed interface has been intentionally made large (24×8  $\mu$ m<sup>2</sup>) to reduce the effect of cumulative alignment error.

### 3.3 Sensing Circuitry

In order to make a binary decision regarding the memristor state, a current-sensing scheme is chosen over a voltage-sensing counterpart. In a conventional voltage-sensing scheme, a transimpedence amplifier (TIA) is utilized to convert the signal into a voltage which is then compared against a threshold voltage. However, the TIA needs at least a two stage op-amp with an appropriate output stage in order to drive the resistive load. Moreover, for a high resistive gain of the TIA, a large feedback resistor is needed, which takes up a large silicon area. Therefore, for a more compact design, the current-sensing scheme is utilized. Also, a current-sensing scheme has the advantage of a much larger dynamic range, which is required for the configurability.

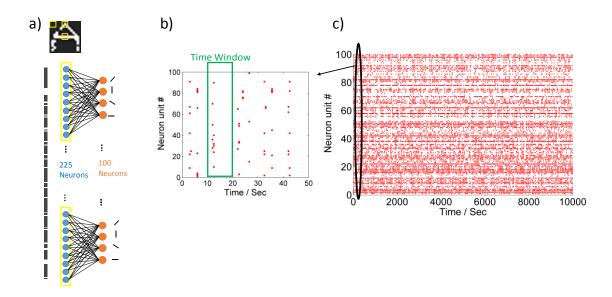

Figure III-3 a shows the schematic of the current-sensing circuitry. The current drawn by the device in response to a small read voltage,  $V_r$ , is compared against a reference current. The read voltage should be picked in a region where the memristor's state does not change. This read voltage is applied by pinning one terminal of the memristor of interest to the default voltage,  $V_d$ , by an op-amp, while the other terminal is driven by the blue line driver to  $V_d+V_r$ . This read current is then compared against a reference current using a winner-take-all (WTA) circuit.