## **UCLA**

## **UCLA Electronic Theses and Dissertations**

## **Title**

High Speed DSP Circuits and Systems for 60 GHz Wireless Communication

## **Permalink**

https://escholarship.org/uc/item/5z42835j

## **Author**

Hsiao, Frank

## **Publication Date**

2013

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA Los Angeles

High Speed DSP Circuits and Systems for 60 GHz Wireless Communication

A dissertation submitted in partial satisfaction

of the requirements for the degree Doctor of Philosophy

in Electrical Engineering

by

Frank Hsiao

© Copyright by

Frank Hsiao

2013

## ABSTRACT OF THE DISSERTATION

High Speed DSP Circuits and Systems for 60 GHz Wireless Communication

by

#### Frank Hsiao

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2013

Professor M. –C. Frank Chang, Chair

The unlicensed 60 GHz band provides new opportunities for short ranged indoor Gb/s wireless communication applications. Compared with III-V semiconductor process technologies, nanometer CMOS based 60 GHz transceivers are attractive from the manufacturing cost and low power consumption point of view but these sensitive mm-Wave transceivers are highly susceptible to process variations thus they face a big challenge in achieving high

yield performance. This suggests DSP based calibration circuits and algorithms to compensate for the performance loss due to process variations. In the first part of the dissertation, DSP based "Self-Healing" circuits and systems are presented to perform concurrent calibration on multiple RF transceiver parameters such as noise figure, image, transmitter IQ mismatch, and DC offset to optimize the 60 GHz CMOS transceiver performance. Digital baseband circuits applied to probe and measure the RF parameters such as direct digital frequency synthesizer, FFT based spectrum analyzer, and self-healing calibration controller will be discussed for a 4 Gb/s 60 GHz self-healing transceiver SOC in 65nm CMOS process.

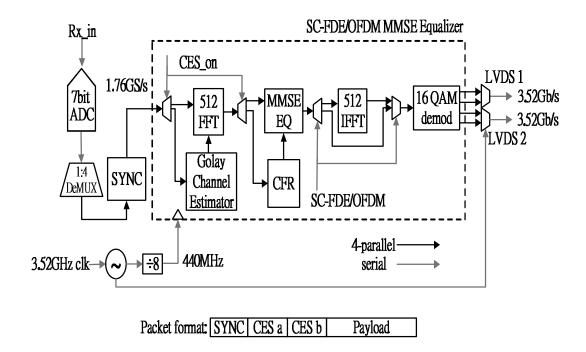

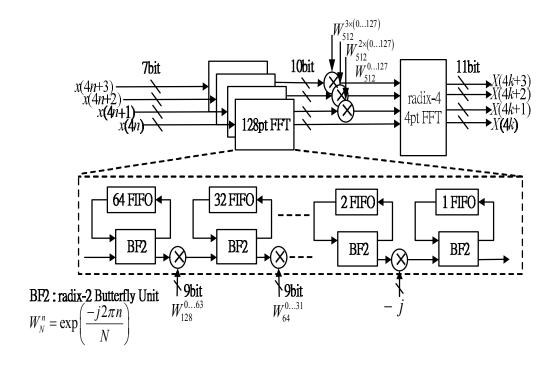

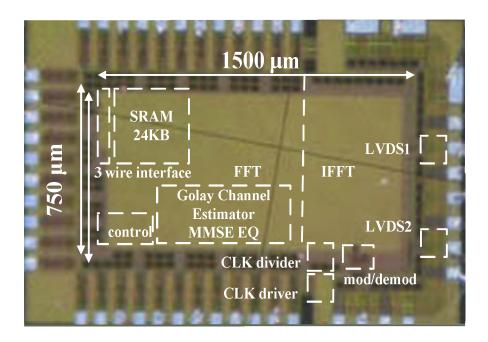

In the second part of the dissertation, the focus will be on the implementation aspects of a digital modem for a muti-Gb/s 60 GHz SOC radio. A 7 Gb/s OFDM/Single-Carrier frequency domain equalizer in 65 nm will be presented as an example. 4-parallel signal processing architecture allows this equalizer chip to achieve a symbol sampling rate of 1.76 GS/s while the core DSP circuits are clocked at 1/4 the input symbol rate. This equalizer chip is equipped with a 512pt FFT processor and a 512pt IFFT processor to demodulate the received OFDM and single-carrier signals. It includes a time domain Golay correlator based channel estimator to obtain the multipath channel impulse response, and it also includes a MMSE equalizer for channel correction in frequency domain.

| The dissertation of Frank Hsiao is approved. |                                   |

|----------------------------------------------|-----------------------------------|

|                                              |                                   |

|                                              |                                   |

|                                              | Sudhakar Pamarti                  |

|                                              |                                   |

|                                              |                                   |

|                                              | Kung Yao                          |

|                                              |                                   |

|                                              |                                   |

|                                              | Lixia Zhang                       |

|                                              |                                   |

|                                              |                                   |

|                                              | M.C. Frank Chang, Committee Chair |

|                                              |                                   |

|                                              |                                   |

University of California, Los Angeles

2013

## **Table of Contents**

| List O | F FIGURES                                                              | vii    |

|--------|------------------------------------------------------------------------|--------|

| LIST ( | OF TABLES                                                              | X      |

| ACKN   | OWLEDGEMENTS                                                           | xi     |

| VITA.  |                                                                        | xii    |

| PUBLI  | CATIONS                                                                | xiii   |

| Chapte | er 1 Introduction                                                      | 1      |

| Chapte | er 2 60 GHz Wireless Communication and 60 GHz Wireless Transceiver     | r6     |

| 2.1.   | 60 GHz Wireless Communication                                          | 6      |

| 2.2.   | 60 GHz Wireless Transceiver                                            | 10     |

| 2.3.   | Nanometer CMOS Process Variations Effects and Circuit Impairments      | 13     |

| Chapte | er 3 Self-Healing 60 GHz Transceiver                                   | 22     |

| 3.1.   | Top Level View of the Self Healing Controller.                         | 22     |

| 3.2    | Circuits and Sensors for Self-Healing.                                 | 26     |

| 3.3.   | Self-Healing Algorithms                                                | 31     |

| Chapte | er 4 DSP Circuits for 60 GHz Self-Healing Transceiver and Self-Healing | ;<br>, |

| Transc | eiver Implementation Results                                           | 35     |

| 4.1.   | DAC Control and IQ Unit                                                | 38     |

| 4.2.   | Parameter Estimator                                                    | 61     |

| 4.3.   | Self-Healing Transceiver Implementation Results                        | 71     |

| Chapte | er 5 Baseband Modem Design for 60 GHz System                           | 90     |

| <b>Chapter 7 References</b> |                                                          |     |

|-----------------------------|----------------------------------------------------------|-----|

| Chapter 6 Conclusion11      |                                                          | 112 |

| 4.3.                        | Equalizer Implementation and Measurement Results         | 104 |

| 5.2.                        | Channel Estimator and MMSE Equalizer                     | 98  |

| 5.1.                        | Dual Mode OFDM/Single-Carrier Frequency Domain Equalizer | 91  |

## LIST OF FIGURES

| Fig. 2.1(a) Unlicenced 60 GHz band around the world and (b) Channelization of IE | EE |

|----------------------------------------------------------------------------------|----|

| 802.15.3c                                                                        | 7  |

| Fig. 2.2 Baseline 60 GHz transceiver                                             | 12 |

| Fig. 2.3 Baseline 60 GHz transceiver                                             | 14 |

| Fig. 2.4 Thermal noise contributing to SNDR degradation                          | 17 |

| Fig. 2.5 Measuring IQ mismatch by measuring the IRR                              | 19 |

| Fig. 2.6 Intermodulation impairments contributing to SNDR degradation            | 20 |

| Fig. 3.1 High-level block diagram of the self-healing transceiver system         | 24 |

| Fig. 3.2 Yield increase by applying self-healing                                 | 25 |

| Fig. 3.3 DDFS two tone generation                                                | 26 |

| Fig. 3.4 (a) Dual DAC implementation strategy (b) Combined signal and auxiliary  |    |

| DAC                                                                              | 28 |

| Fig. 3.5 Measuring the receiver output noise                                     | 34 |

| Fig. 4.1 Architecture of the 4.0 Gb/s 60 GHz self-healing trnasceiver            | 35 |

| Fig. 4.2 Block diagram of the DDFS with uncompressed ROM                         | 40 |

| Fig. 4.3 Block diagram of Taylor series approximation for sine wave output       | 41 |

| Fig. 4.4 DDFS core unit architecture                                             | 45 |

| Fig. 4.5 Block diagram of the I/Q unit                                           | 48 |

| Fig. 4.6 Block diagram of the 2.0 GHz DDFS with I/Q output control               | 50 |

| Fig. 4.7 Schematic of the clock divider                                          | 51 |

| Fig. 4.8 DAC control unit layout in Cadence SoC Encounter                       | 53 |

|---------------------------------------------------------------------------------|----|

| Fig. 4.9 Layout of DDFS with I/Q output control                                 | 54 |

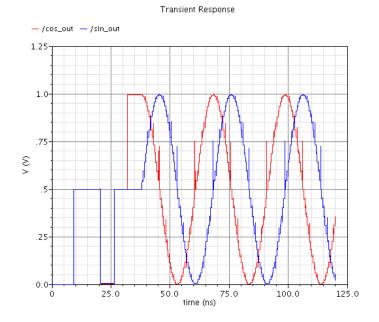

| Fig. 4.10 DAC control with single tone output                                   | 56 |

| Fig. 4.11 DAC control with two-tone output                                      | 56 |

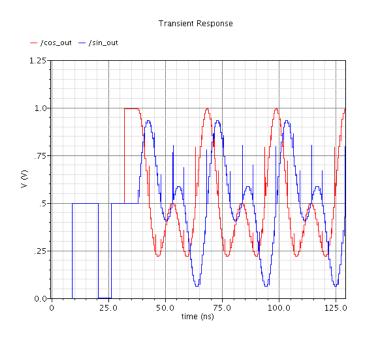

| Fig. 4.12 SFDR simulation of the DAC control unit                               | 57 |

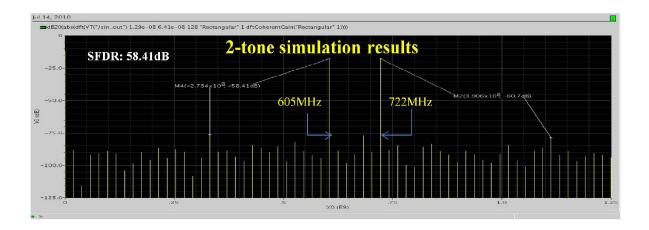

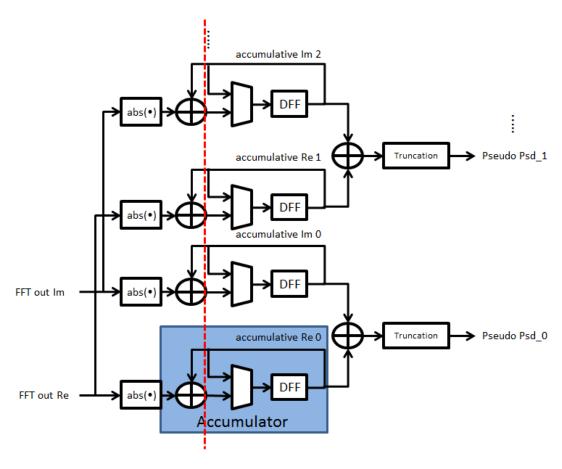

| Fig. 4.13 (a) Parameter estimator (b) 128pt FFT processor (c) FFT Averaging     | 62 |

| Fig. 4.14 The block diagram of the estimated PSD processing                     | 68 |

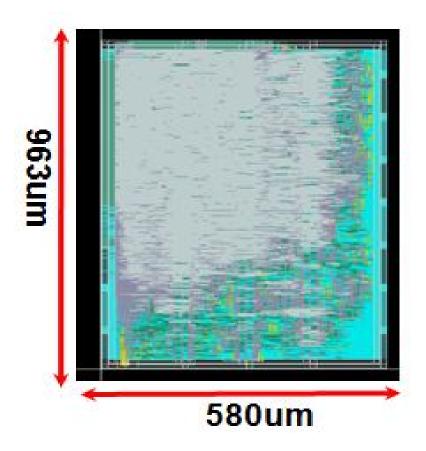

| Fig. 4.15 Layout of the parameter estimator                                     | 69 |

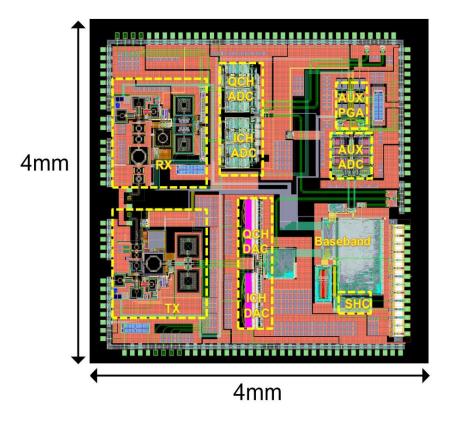

| Fig. 4.16 4 Gb/s 60 GHz Self-Healing transceiver architecture                   | 71 |

| Fig. 4.17 Self-Healing transceiver layout                                       | 73 |

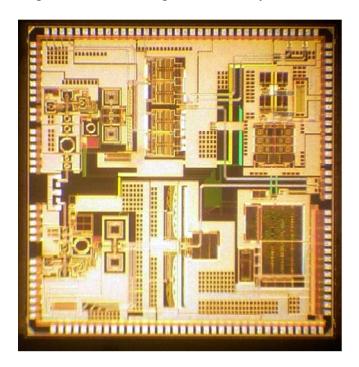

| Fig. 4.18 Self-Healing transceiver die photo                                    | 73 |

| Fig. 4.19 DAC controller unit and DAC test setup                                | 75 |

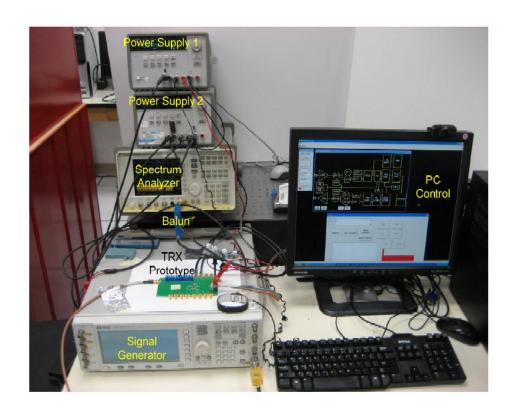

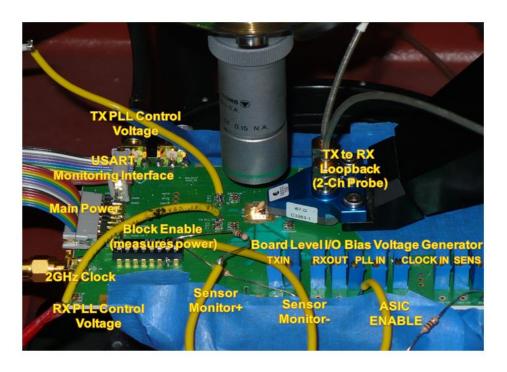

| Fig. 4.20 Self-Healing Testing probe setup with the PCB board                   | 75 |

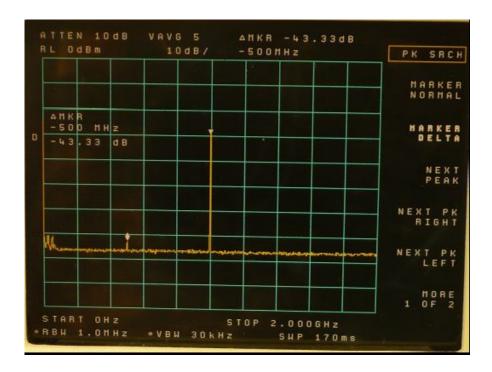

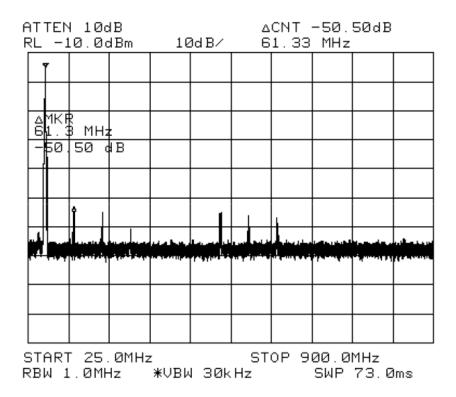

| Fig. 4.21 SFDR performance of the DAC control and the DAC, achieving 40dB       |    |

| SFDR                                                                            | 76 |

| Fig. 4.22 SFDR performance of the DAC control and the DAC, achieving            |    |

| 50dB SFDR at 60 GHz on                                                          | 77 |

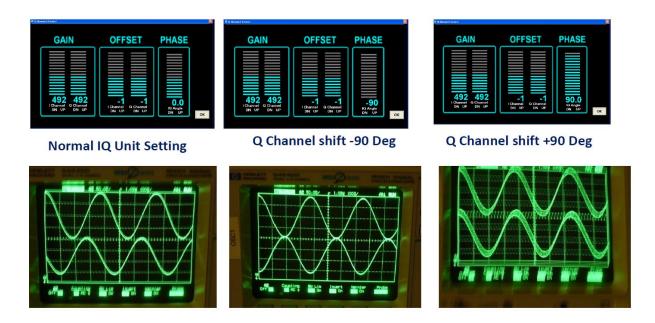

| Fig. 4.23 The DAC control output with 0 degree, -90 degree, and 90 degree phase |    |

| rotation on the Q channel.                                                      | 78 |

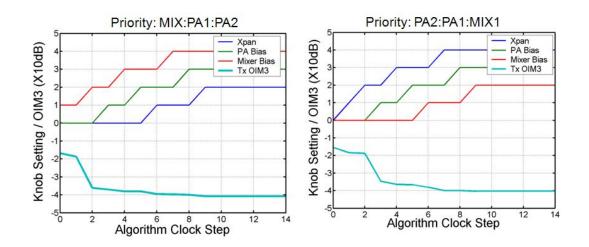

| Fig. 4.24 Convergence of the OIM3                                               | 79 |

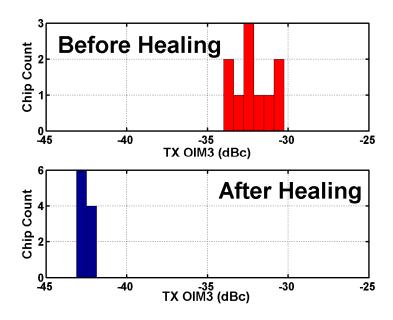

| Fig. 4.25 Yield performance after OIM3 self-healing for 10 chips                | 80 |

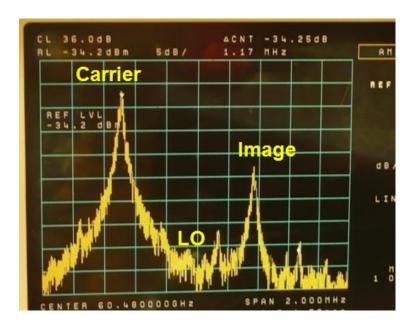

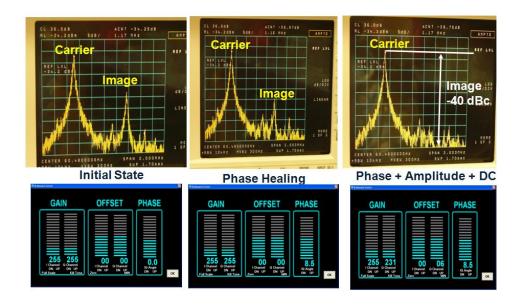

| Fig. 4.26 The transmitter output spectrum of a single-tone test, this shows     |    |

| the carrier signal, the image tone, and the LO leakage tone.                    | 81 |

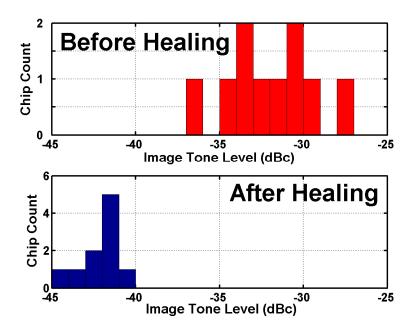

| Fig. 4.28 The transmitter spectrum output before and after IQ a            | ınd image |

|----------------------------------------------------------------------------|-----------|

| healing                                                                    | 83        |

| Fig. 4.29 Yield performance before and after IQ self-healing               | 83        |

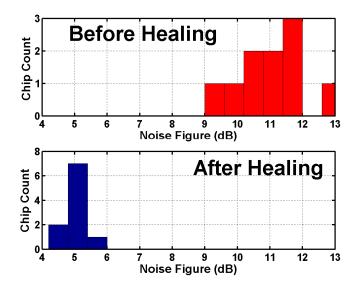

| Fig. 4.30 Noise figure self-healing results                                | 85        |

| Fig. 4.31 Yield result before and after receiver noise figure self-healing | 86        |

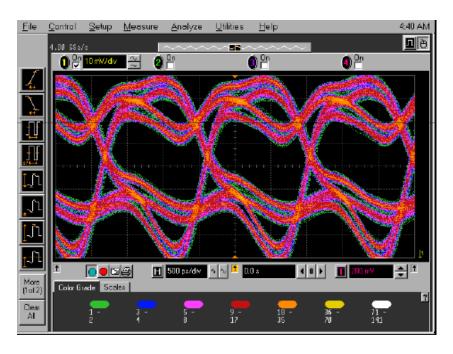

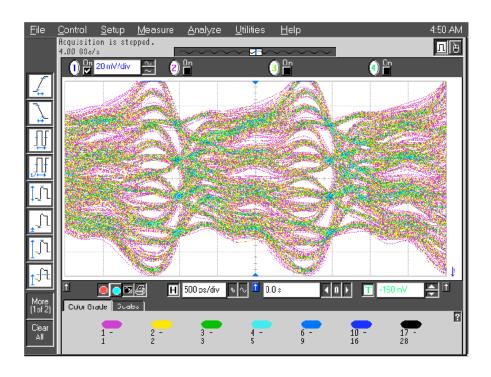

| Fig. 4.32 QPSK modulation eye diagram                                      | 87        |

| Fig. 4.33 16-QAM modulation eye diagram                                    | 87        |

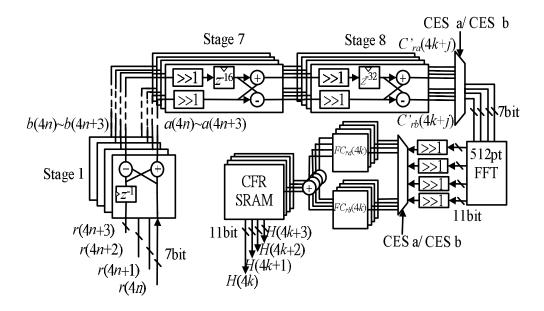

| Fig. 5.1 Frequency domain equalizer system                                 | 96        |

| Fig. 5.2 512pt FFT processor architecture                                  | 97        |

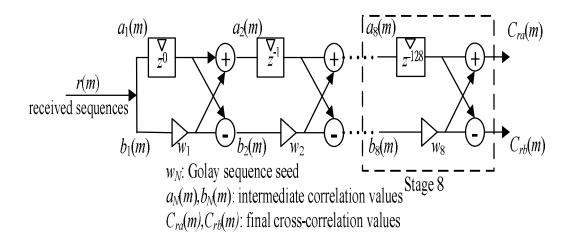

| Fig. 5.3 Serial Golay correlator                                           | 100       |

| Fig. 5.4 Parallel Golay correlator based channel estimator                 | 101       |

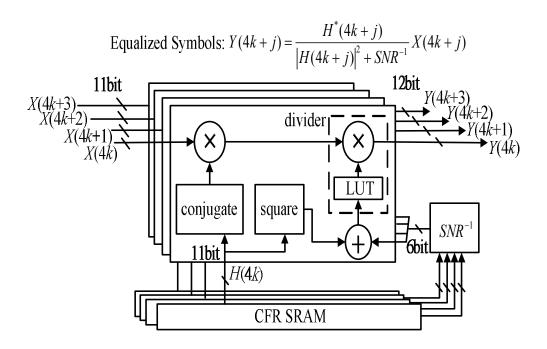

| Fig. 5.5 MMSE equalizer architecture                                       | 102       |

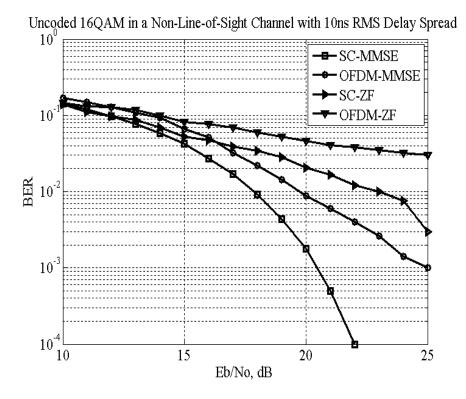

| Fig. 5.6 BER performance plot                                              | 104       |

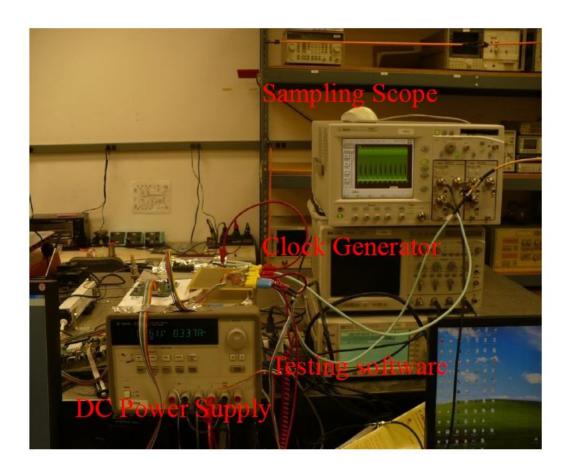

| Fig. 5.7 Equalizer testing setup                                           | 105       |

| Fig. 5.8 Equalizer chip die-photo                                          | 106       |

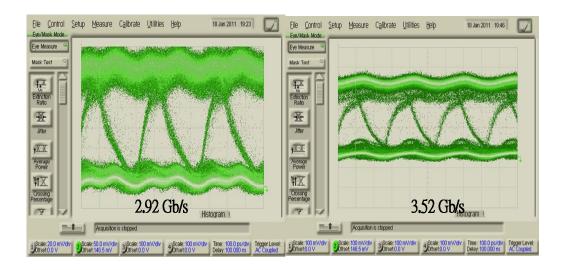

| Fig. 5.9 Measured Eye Diagrams with 16-QAM modulation                      | 108       |

## LIST OF TABLES

| Table 4.1 SFDR performance of various compression techniques     | 42  |

|------------------------------------------------------------------|-----|

| Table 4.2 Summary of DDFS control signals                        | 47  |

| Table 4.3 DAC control unit design summary                        | 58  |

| Table 4.4 Comparison of DAC control unit with other DDFS designs | 60  |

| Table 4.5 Summary of the parameter estimator                     | 70  |

| Table 4.6 Self-Healing transceiver features                      | 72  |

| Table 5.1 Equalizer chip summary                                 | 109 |

| Table 5.2 Equalizer chip comparison                              | 110 |

## ACKNOWLEDGMENTS

First, I would like to thank my adviser, Professor Frank M.C. Chang, for his guidance, encouragements, and support throughout the many years during my doctoral studies. I would like to extend my appreciation to Professor Pamarti, Professor Yao, and Professor Zhang for serving on my committee, and for their comments and advice on the dissertation.

I would like to thank to all my colleagues in UCLA HSEL lab and everyone I had the privilege to work with at UCLA throughout the years. I learned everything I know here.

## VITA

| 2002 | B.S., Applied Mathematics National Chiao Tung University, Hsinchu ,Taiwan |

|------|---------------------------------------------------------------------------|

| 2005 | M.S., Computer Science                                                    |

|      | National Chiao Tung University,                                           |

|      | Hsinchu, Taiwan                                                           |

|      |                                                                           |

| 2007 | M.S., Electrical Engineering                                              |

|      | University of Southern California,                                        |

|      | Los Angeles                                                               |

|      |                                                                           |

| 2009 | Research Assistant and Teaching Assistant                                 |

|      | University of California, Los Angeles                                     |

## **PUBLICATIONS**

Sandeep D'Souza, **Frank Hsiao**, Adrian Tang, Sai-Wang Tam, Roc Berenguer, and M. F. Frank Chang, "A 10-bit, 2GS/s, DAC-DDFS-IQ-Controller Baseband enabling a Self-Healing 60GHz Radio-on-Chip" IEEE Transactions Circuits and Systems II, 2013

H. Wu, N.-Y. Wang, Y. Du, Y.-C. Kuan, **F. Hsiao**, S.-J. Lee, M. H. Tsai, C. P. Jou, and M. F. Chang, "A Current-Mode mm-Wave Direct-Conversion Receiver to Break Trade-offs among Bandwidth (7.5GHz), Noise-Figure (3.8dB) and Linearity (P1dB=1dBm) for High Data Rate Communications," IEEE RFIC Symposium 2013

A. Tang, G. Virbila, **F. Hsiao**, D. Murphy, I. Nehdi, P. H. Siegel, M. F. Chang, A 2x2 W-Band Reference Time-Shifted Phase-Locked Transmitter Array in 65nm CMOS Technology" IEEE International Microwave Symposium 2013

C. Chien, A. Tang, **F. Hsiao**, and M. F. Chang, "Dual Control Self-Healing Architecture for High Performance Radio SoC's", IEEE Design & Test of Computers, Nov. 2012

A. Tang, D. Murphy, **F. Hsiao**, G. Virbila, Y.-H. Wang, H. Wu, Y. Kim, and M. F. Chang, "A D-Band CMOS Transmitter with IF-Envelope Feed-Forward Pre-Distortion and Injection-Locked Frequency Tripling Synthesizer," IEEE Transactions on Microwave Theory and Techniques 2012

**Frank Hsiao**, A. Tang, Derek Yang, Mike Pham, and Mau-Chung Frank Chang, "A 7Gb/s SC-FDE/OFDM Baseband MMSE Equalizer for 60GHz Wireless Communications", IEEE Asian Solid-Sate Circuits Conference 2011

A. Tang, Frank Hsiao, David Murphy, I-Ning Ku, Jenny Y. Liu, Ning-Yi Wang, Sandeep D'Souza, Hao Wu, Yen-Hsiang Wang, Yen-Cheng Kuan, Mandy Tang, Mike Pham, Gabriel Virbila, Derek Yang, Qun Gu, Charles Chien and Mau-Chung Frank Chang, "A Low Overhead Self-Healing Embedded System for Ensuring High Performance Yield and Long-Term Sustainability of a 60GHz 4Gbps Radio-on-a-Chip" IEEE International Solid-State Circuits Conference 2012

A. Tang, G. Virbila, D. Murphy, **F. Hsiao**, Y. Wang, Q. Gu, Z. Xu, Y. Wu, M. Zhu, M-C F. Chang, "A 144 GHz 0.76 cm Resolution Sub-Carrier Phase Radar for 3D Imaging Applications" IEEE International Solid-State Circuits Conference 2012

A. Tang, David Murphy, Gabriel Virbila, **Frank Hsiao**, Sai-Wang Tam, Hsing-Ting Yu, Yanghyo Kim, Alden Wong, Alex Wong, Yi-Cheng Wu, Mau-Chung Frank Chang, "D-Band Frequency Synthesis Using a U-band PLL and Frequency Tripler in 65nm CMOS Technology" IEEE International Microwave Symposium 2012

A. Tang, D. Murphy, **F. Hsiao**, Qun Gu, Z. Xu, G. Virbila, Y.H. Wang, H. Wu, L. Nan, Y. Wu, and Frank Chang, "A CMOS 135-150 GHz 0.4 dBm EIRP Transmitter with 5.1dB P1dB Extension Using IF Envelope Feed-Forward Gain Compensation" IEEE International Microwave Symposium 2012

**Frank Hsiao**, J.W Guo, S.-L. Lo, and T.-Y. Hsu, "A DSSS Receiver for dual-mode DSSS/OFDM Wireless Lan Systems," IEEE International Symposium on Microwave, Antenna, Propagation and EMC Technologies for Wireless Communications, 2006. MAPE 2006

**Frank Hsiao** and T.-Y. Hsu, "A frequency domain equalizer for WLAN 802.11g single-carrier transmission mode," IEEE International Symposium on Circuits and Systems, ISCAS 2006

## **Chapter 1 Introduction**

The unlicensed 7 GHz of bandwidth at 60 GHz have brought a lot of opportunities for short ranged multi-Gb/s wireless communication systems. Standards like IEEE 802.15.3c and 802.11ad have been established to promote wireless LAN or WPAN communication applications in the 60 GHz band [1],[[2]. In these applications, it is highly desirable to reduce the power consumption and manufacturing cost so as to have an economically viable product. CMOS process technologies then becomes an evident solution for implementing the circuits for these 60 GHz communication applications. However, in ultra-deep-sub-micron CMOS process technologies, to maintain low cost and high manufacturing yield of the integrated circuits is often a very challenging task when the process statistical variations are high. Sensitive mm-Wave circuits will suffer a signification loss in yield due to the variations in linearity of the RF amplifiers. This implies some sort of circuit calibration or compensation to compensate the transceiver circuit parameters to improve the yield performance. These calibration mechanisms are usually DSP based digital circuits estimating some analog circuit impairment parameters and then performing compensation in either digital domain or analog domain. In this work, collective digital calibration or "SelfHealing" of multiple circuit parameters on a RF transceiver is presented. On-chip Calibration or Self-Healing 60GHz circuits poses several additional challenges. At the system level, wide bandwidth and linear 'sensors' and circuit control 'knobs' are required to sense and tune or 'heal' the transceiver impairments. Digital Self- Healing algorithms must be able to correctly capture the characteristics of the transceiver and the digital circuits applied for Self-Healing algorithms must also be high-speed and wide bandwidth in order to accommodate the 60 GHz transceiver system. At the same time, the power consumption of these Self-Healing digital circuits and processors must be minimized so the extra overhead of installing the Self-Healing processing functions would be minimal and be suited for on-chip integration.

In the first part of the dissertation, 60 GHz communication and the radio impairments of a 60 GHz transceiver will be introduced. These RF circuit impairments along with nano-scale CMOS process variations causing the manufacturing yield loss will provide strong motivation for a Self-Healing based 60GHz transceiver. In this first part of the dissertation, the DSP Self-Healing algorithm will be presented and the details on the digital circuit implementations will be discussed.

In the second part of the dissertation, digital baseband signal processing for 60 GHz wireless communication will be presented. For standards such as IEEE 802.15.3c and IEEE 802.11ad, they both adopt Single-Carrier and OFDM modulation methods. For high throughput multi-Gb/s 60 GHz wireless systems, multipath channel equalization is one of the most challenging and area/power

consuming functions in the digital baseband modem. To compensate the channel induced ISI effects for these systems, OFDM modulation or time domain channel equalizers are widely applied. Single-Carrier modulation techniques usually apply time domain channel equalizer like DFE (Decision-Feedback Equalizers) and OFDM modulation typically apply a 1-tap channel frequency response inversion in the frequency domain. An equalizer applying OFDM-like 1-tap channel frequency response inversion process is preferred over time domain DFEs when transmitting in a 60GHz non-line-of-sight (NLOS) multipath channel environment where the root-mean-square (RMS) channel delay spread may exceed over 10ns or over 100 symbols when the transmission symbol rate is at 1GS/s. In this kind of a multipath channel environment, designing DFEs for single-carrier transmission systems requires a large number of feedback filter taps to compensate the multipath fading. The number of filter taps for these kind of DFEs used in wireless channel environment are usually proportional to the number of complex multipliers necessary to implement them since the wireless channel impulse response will change over time. In addition, the extra loop unrolling and the parallel look-ahead symbol decision hardware necessary to support multi-Gb/s throughput with complex modulations, e.g., 8PSK and 16QAM, makes DFEs impractical to apply in terms of area and power consumption. As a result, most previously reported Gb/s baseband DFEs for wireless baseband modems support only simple modulation methods like QPSK or MSK.

From the baseband system integration point of view, when implementing a combo OFDM and single-carrier modulation modem, it is highly desirable to have

an equalization hardware architecture that would fully utilize the FFT processor already required in the OFDM receiver to perform channel estimation, equalization, and other modem signal processing functions for the demodulation of single-carrier signals. Single-carrier frequency domain equalization (SC-FDE) then becomes an attractive and feasible low-cost implementation solution as its concepts and datapath are similar to those of an OFDM modem receiver.

In this dissertation, a 7Gb/s frequency domain minimum mean squared error (MMSE) equalizer chip for 60 GHz wireless communication system is demonstrated. 4-parallel signal processing architecture allows this equalizer chip to achieve a symbol sampling rate of 1.76 GS/s while the core DSP circuits are clocked at ½ (1.76 GHz/4=440 MHz) the input symbol rate. This 1.76 GS/s symbol sampling rate achieves the sampling rate required by IEEE 802.15.3c and IEEE 802.11ad standard and it is the first implemented equalizer to achieve this target symbol rate specification in 65nm technology node. This equalizer chip is equipped with a 512pt FFT processor and a 512pt IFFT processor to demodulate the received OFDM and single-carrier symbols. It also includes a time-domain Golay correlator based channel frequency response (CFR), and it also includes a MMSE equalizer for channel multipath compensation in the frequency domain. To verify the proposed equalizer chip at Gb/s throughput, differential input clock driver and low voltage differential signaling (LVDS) output drivers are also implemented in this chip.

The content of this dissertation is as follows. Different aspects of radio system design for 60 GHz radios are addressed in Chapter 2. In Chapter 2, a

baseline 60 GHz radio system is also addressed and it will be used as a comparison with the Self-Healing 60 GHz radio SOC presented later. In Chapter 3, RF impairments of the 60 GHz radios will be introduced and the concepts including the high level Self-Healing algorithms and architectures will be discussed. Chapter 4 will discuss the details on the DSP circuits applied for Self-Healing 60 GHz radio. The circuit specifications, design considerations, and architectures will be discussed. Also in Chapter 4, the Self-Healing 60 GHz radio SOC implementation results will also be presented. Chapter 5 focuses on the baseband modem implementation aspects of 60 GHz radio. The frequency domain equalizer will be applied as the main example on the data-path of a 60 GHz baseband modem. The performance and implementation results of the frequency domain equalizer will also be presented in Chapter 5. Finally, Chapter 6 summarizes the results and main conclusions of the dissertation and provides some thoughts for future research topics.

## Chapter 2: 60 GHz Wireless Communication and 60 GHz Transceiver

This chapter introduces 60GHz wireless communication and the motivation for high short ranged data rate wireless communication is first addressed. This is then followed by an introduction of 60GHz transceivers. Different architectures and major transceiver circuit blocks will be briefly discussed. The challenges of the transceiver operation at 60GHz are then highlighted. This is followed by a discussion on the design challenges of nanometer CMOS mm-Wave RF circuits due to process variations. The analog RF impairments are then summarized. Finally, a baseline 60GHz transceiver will be introduced this baseline transceiver will be used as a comparison with the Self-Healing 60GHz transceiver.

#### 2.1 60 GHz Wireless Communication

Over the past few years, advances in CMOS process technology and the need for wide bandwidth high-data rate wireless transmission have made mm-Wave technologies to attract a great deal of interest from university research groups and industry. 60 GHz mm-Wave technology offers several advantages over the current communications systems for high data rate wireless transfer. One of the main reasons is the 7 GHz of unlicensed bandwidth centered around 60GHz. This large unlicensed bandwidth brings potentials for Gb/s wireless applications like wireless uncompressed high-definition video transfer or high-speed wireless

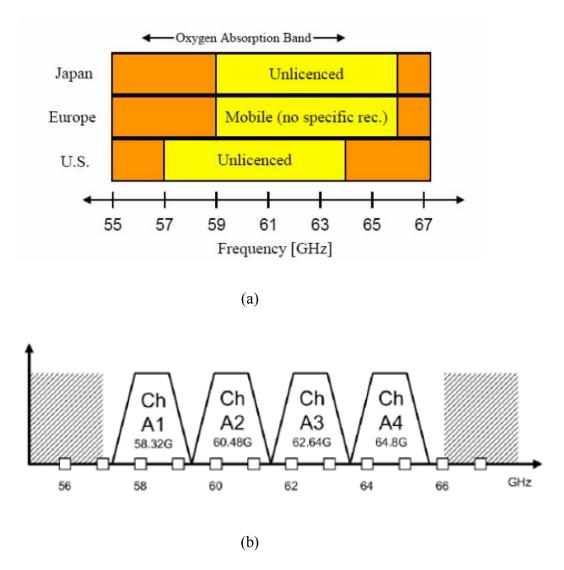

data docking stations that allow multiple electronic devices to be connected without the actual need for the physical cable wires. Fig. 2.1 shows the unlicensed 60 GHz band in different regions of the world and the channelization of the 60 GHz for IEEE 802.15.3c standard.

Fig. 2.1 (a) Unlicensed 60 GHz band around the world and (b) Channelization of IEEE 802.15.3c

From the US Federal Communications Commission (FCC) regulations, 60 GHz communications are allowed with a much higher transmit power. The

equivalent isotropic radiated power (EIRP) for 60GHz communications are higher compared with 2.4GHz WLAN or 3.1 GHz UWB systems. This higher transmit power allows 60GHz wireless communication to overcome the higher path loss at 60GHz and confines the transmission environment to an indoor environment limiting a transmission link distance to around 10 meters or so. This also means that the effective interference levels for 60GHz are less than the WLAN systems located around 2.4 GHz and 5.2 GHz.

With this huge 7 GHz bandwidth available for 60 GHz communication applications, it makes system modulation design simpler. Low spectral efficiency modulation methods like BPSK, QPSK, or 16 QAM can be applied and making these systems easily achieve over 1 Gb/s. This makes a 60 GHz system an ideal candidate to support Gb/s wireless data transfer applying digital modulation. In standards like IEEE 802.15.3 or IEEE 802.11ad the total bandwidth at 60 GHz are further channelized into channels of around 2 GHz. Since 60 GHz operates at such a high RF carrier frequency, this allows multiple-antenna solutions to be implemented on-chip easily compared with the lower frequency WLAN systems. This will enable multi-antenna beamforming solutions to be implemented on CMOS offering higher integrated system at lower costs.

Of course, with all these benefits and advantages, short ranged communication at 60 GHz does not come without price and challenges. First of all, the design and modeling of 60 GHz building blocks of a transceiver becomes much more complex and delicate compared with lower frequency systems. At 60 GHz, small deviation in local oscillator (LO) frequency offset means a huge

timing and phase offset for the baseband modulation symbols and more effort is necessary for the baseband timing/frequency recovery algorithms. Also at 60 GHz or other mm-Wave frequencies, the design of active and passive devices in CMOS becomes more complicated [3]. The effects of layout parasitic must be carefully modeled or else a frequency down-shift between simulation and measurement results would occur decreasing the performance of the circuits.

One other major reason that is challenging for the 60 GHz wireless applications to become widely adopted in commercial mobile electronics is the power consumption. Since 60 GHz communication aims to target Gb/s throughput with simple low spectral efficiency modulation, this means that the mixed-signal circuit blocks like ADC (analog-to-digital converters) or DAC (digital-to-analog converters) will be power hungry running at an order of GS/s. For the digital baseband modem, even at advanced CMOS technology nodes like 65nm or 40nm, 4-parallel DSP processing or 8-parallel DSP processing must be implemented to meet the symbol sampling rate requirements of 1.76 GS/s defined by IEEE 802.15.3c or IEEE 802.11ad. Parallel processing means multiplication of datapath hardware by 4 or by 8; this implies the increase of power and area consumption to accommodate the Gb/s transmission link. How to effectively come up with datapath architectures with low power consumption will be a major challenge before 60 GHz wireless applications can be widely adopted in the indoor mobile electronic devices.

#### 2.2 60 GHz Wireless Transceiver

In this subsection, the 60 GHz transceiver designed at UCLA HSEL and its major circuit block will be briefly described. This transceiver will be used as the baseline transceiver and be later on compared with the Self-Healing 60 GHz transceiver to demonstrate the effectiveness and the necessity of Self-Healing on mm-Wave 60 GHz circuit blocks to increase the effective yield.

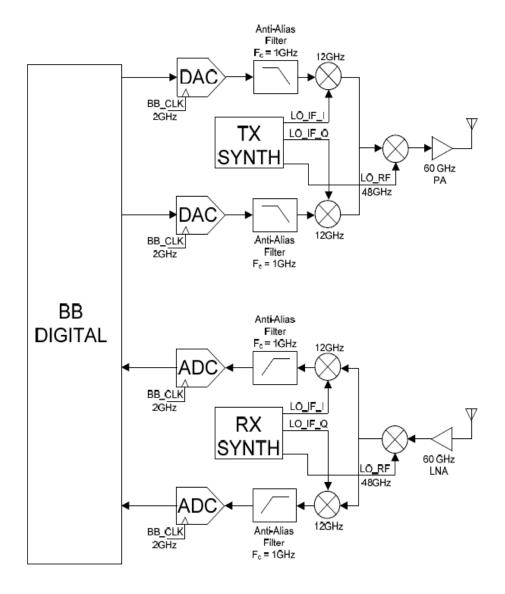

The baseline 60 GHz transceiver designed by various members of UCLA HSEL is shown in Fig. 2.2. [4], [5], [6], [7]. At the baseband transmitter side, the input digital data bits are first modulated and then converted to analog voltage signals by driving the I/Q quadrature DACs. Following the DACs are the 3rd order inverse Chebyshev antialiasing filters with 1GHz cut off frequency. This means that the DACs has to operate at 2GHz and the symbol signaling at the digital baseband modulator also has to transmit at 2GHz clock frequency to avoid signal aliasing. At the baseband receiver side, to cope with the transmitted signal, the baseband analog signal is converted to digital by applying a 4-parallel timeinterleave 7b ADC also clocked at 2GHz. The baseline 60 GHz transmitter and receiver have been designed using a 2-stage heterodyne architecture. Although direct conversion (DC) based architecture would greatly reduce the system hardware complexity by removing the IF (intermediate frequency) stage and image reject filters. However, the stringent amplitude and phase mismatch requirements on the I and Q channels makes it very hard to achieve the targeted 0.1 dB gain mismatch and 10° degree phase mismatch at 60 GHz in the implemented design considering layout and circuit matching. Therefore the

traditional 2-stage heterodyne transceiver architecture is adopted in the baseline 60 GHz transceiver. In the baseline 60 GHz transceiver the intermediate frequency (IF) state is at 12 GHz followed by RF mixers to convert the signals up and down from 12 GHz to 60 GHz carrier frequency. On the transmitter side, the I/Q DAC outputs are first converted to 12 GHz by applying quadrature upconversion mixers. In the second stage, a single mixer up converts the 12 GHz IF signal to 60 GHz. Then, the 60 GHz up converted signal is amplified by a 3-stage fully differential transformer based power amplifier (PA) with a saturated output power (PSAT) of 14.85dBm and power-added-efficiency (PAE) of 16%. On the receiver side, the LNA is followed by an single-side-band RF-mixed converting the signal from 60GHz to 12GHz IF, followed by quadrature IF mixers that further mix down the 12 GHz signals to baseband. The 60 GHz RF synthesizer that generates the 12 GHz and the 48 GHz LO signals are generated by a wideband and low phase noise integer-N PLL. In the baseline 60 GHz transceiver, two identical PLLs are included on the transmitter and the receiver to support the frequency duplex division (FDD) operation which is defined by the 802.15.3c standard. The block diagram of the baseline 60 GHz transceiver is shown in Fig.

2.2

Fig. 2.2 Baseline 60 GHz transceiver

## 2.3 Nanometer CMOS Process Variations Effects and 60 GHz RF Circuit Impairments

This section will discuss the CMOS process variation effects and its impact to 60 GHz circuits design followed by the discussion of 60 GHz RF circuit impairments. This will bring out the motivation of digital calibration to aid the analog circuits to overcome the process variation and inherent circuit impairments.

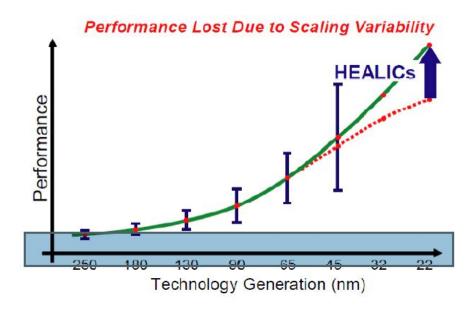

With the advances of CMOS transistor scaling, integrated SOC systems have become more and more popular. However, with the performance increase of the transistors at the nanometer process technology, it also brings increased statistical process variations in and decreased their yield performance. One common example would be the drift of transistor threshold voltage (Vt). These process variations across the wafer will lead to die- to -die performance differences which increases the circuit design efforts to cope with these process variations. Fig.2.3 shows the performance lost due to scaling variability [9]. This scaling variability caused from process variations resulted from the manufacturing variations such as threshold voltage, gate length of transistors, and wiring interconnect process variations will lower the yield performance of the integrated circuits as CMOS process scales.

Fig. 2.3 Performance lost due to scaling variability

The performance loss due to scaling variability for nanometer highperformance circuits has resulted Defense Advanced Research Projects Agency

(DARPA) to formulate a research program on 'Self-Healing of RF/Mixed-Signal

Integrated Circuits' or the 'Healics' program. The main motivation for this

Healics program is to introduce the process invariant digital circuits and systems

to correctly calibrate or 'heal' the analog impairments caused by the process

variations. Therefore, in a Self-Healing transceiver, it would include some digital

and analog circuits that could sense or measure the circuit impairments, and these

undesired circuit impairments can be corrected or healed by the self-healing

circuits in presence of process variations and different operating environments.

With self-healing functions included in a 60 GHz transceiver, the effective

manufacturing yield would increase compared with a baseline 60 GHz transceiver

and in result the approach of adding self-healing functions to the baseline transceiver would lower the overall manufacturing cost.

Recently, the self-healing or autonomous calibration concepts have been applied in smaller scaled circuit blocks like PLL or in a power amplifier [10]. They do not optimize the various analog circuit impairments concurrently, and tradeoffs of calibrating each circuit parameters are not well considered as a system. Therefore, as the major part of the dissertation and also the research work of various UCLA HSEL members, the research of a self-healing transceiver that considers the analog RF transceiver impairments concurrently which is suitable for calibrating a complete transceiver is investigated.

To summarize Chapter 2, the radio impairments generated by non-ideal circuits in a 60 GHz radio are discussed and they serve as the main parameters the self-healing 60 GHz radio is trying to correctly calibrate. In here, we begin with the system link budget and discuss the impacts of radio impairments on the system link budget. In the system link budget, one of the final performance factors we care in the system is the bit error rate (BER) or the packet error rate (PER). With the targeted BER, one can determine the required  $E_b/N_o$  for this system. This  $E_b/N_o$  is defined as the energy per bit normalized against noise. With the information about the data rate R and the transmission bandwidth  $B_T$  the link signal-to-noise ratio (SNR) as:

$$\frac{S}{N} = \frac{E_b}{N_0} \left(\frac{R}{B_T}\right) \tag{2.1}$$

This SNR is required for a given modulation to achieve the targeted BER. By accounting the circuit impairments into the SNR the signal-to-noise-and-distortion (SNDR) ratio can be defined. And SNDR is defined as:

$$SNDR = \frac{S^2}{N_0 + \sum_{k=1}^{M} D_k^2}$$

(2.2)

Where in (2.2),  $S^2$  is the signal power, M is the number of different impairments,  $N_0$  is the thermal noise power, and  $D_k^2$  is the distortion power contributed from various different impairments. From (2.2), it can be seen that with more impairment distortion power it will result in lower SNDR making the system harder to achieve the targeted BER.

In the following, some of the circuit impairments the Self-Healing transceiver targets to correct or heal on will be discussed [11], [12], [13].

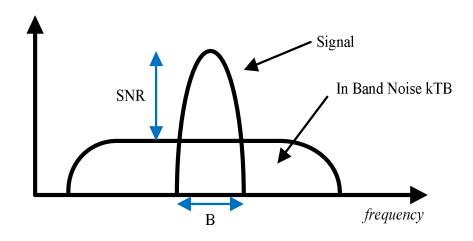

#### **Thermal Noise:**

Thermal nose can be found in all physical electronic devices. The power spectral density can be represented by kT, where k is the Boltzmann's constant  $k = 1.38 \times (10^{-23} \text{ W}_s/\text{K})$  and T is the temperature in Kelvin (K). Thermal noise is the main limitation on the RF receiver's sensitivity, and the receiver sensitivity is defined as:

Receiver sensitivity = Receiver Noise Floor + SNR

= Thermal Noise + Receiver Noise Figure + SNR (2.3)

In (2.3), the receiver noise figure NF= $SNR_{in}/SNR_{out}$  is defined as the ratio of the output SNR to the input SNR for a functional block in the receiver. Lowering the

receiver noise figure is one of the key factors in lowering the SNDR. By tuning the gain stages of the receiver low noise amplifier (LNA), the receiver noise figure (NF) can be adjusted at the cost of receiver gain and linearity performance which also impacts on the overall SNDR. Fig. 2.4 shows the effect of the thermal noise on the signal degrading the overall SNDR.

Fig. 2.4. Thermal noise contributing to SNDR degradation

## IQ mismatch:

IQ mismatch is a circuit impairment that happens during the up conversion or down conversion of the baseband or IF signals to the RF band. The conversion process shifts the local oscillator (LO) by 90 degrees to produce the quadrature sinusoidal components. It is impossible to achieve a perfect matching in layout or devices on both the I-branch and Q-branch of the LO and this gain and phase imbalance is the source to IQ mismatch. IQ mismatch is much more severe for direct-conversion (DC) receiver architectures since the conversion process

happens at 60GHz. Although, in the baseline 60 GHz transceiver the conversion is done at IF 12 GHz, the effects of IQ mismatch cannot be neglected and must be compensated for in the self healing transceiver. Assuming that the gain mismatch error is defined as  $20\log\frac{1+\alpha}{1-\alpha}$  dB and the phase error is  $\phi$  degrees. Then the IQ imbalance of the mismatched LO output signals can be represented as

$$2(1+\alpha)\cos(2\pi f_c t - \phi/2)$$

$$-2(1-\alpha)\sin(2\pi f_c t + \phi/2)$$

(2.4)

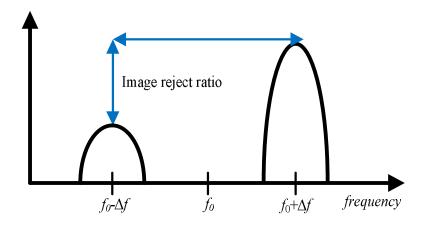

where in  $(2.4) f_c$  is the carrier frequency. IQ mismatch will cause the modulation symbol constellation to expand or compress in amplitude due to gain error and the constellation to rotate due to the phase error. The implications to self-heal this IQ mismatch would be some sort of gain adjustment at either transmitter side or receiver side to correct the gain mismatch. For 60 GHz systems, to correct the phase mismatch, rotating the initial signal constellation in the digital baseband transmitter side, or rotating the constellation in the baseband modem side would be the solution. Trying to correct the gain or phase mismatch in the analog domain and at 60 GHz would be very difficult. Designing high resolution and high frequency phase shifters themselves would face the problem of insufficient granularity. Also, the analog phase shifter themselves also suffer from process variations making the calibration at 60 GHz RF domain more difficult compared with digital baseband calibration. To measure the IQ mismatch, the image-reject ratio (IRR) is measured. A tone can be sent through the transceiver chain and based on the magnitude of the image signal the IQ mismatch of the transceiver can be estimated. Fig. 2.5 shows the spectrum of the fundamental signal and the IRR that depicts the IQ mismatch.

Fig. 2.5. Measuring IQ mismatch by measuring the IRR

## Nonlinearity and Intermodulation distortion

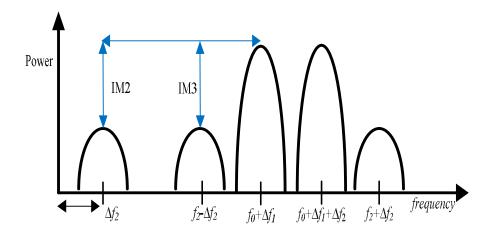

The RF amplifiers exhibit nonlinear behavior and saturating gain at large input levels. The nonlinearity of a RF amplifier is characterized by P1dB and 3rd-order-input-intercept (IIP3). When the RF transmitter or RF receiver amplifies different signals with different frequencies, intermodulation products raised from circuit nonlinearity lead to in-band distortion. This intermodulation effect must be decreased to an acceptable level to meet the required SNDR and BER specification. Other undesirable effects of intermodulation include spectral regrowth at the transmitter causing the spectral mask regulations to fail or large unwanted energy leakage at adjacent channels or interference to other electronics device occupying in the nearby spectrum. Fig. 2.6 shows the spectrum of the 2nd

order intermodulation (IM2) and 3rd order intermodulation (IM3) with input frequencies of  $f_0+\Delta$   $f_1+\Delta f_2$  and  $f_0+\Delta$   $f_1+\Delta f_2$ . To self-heal the intermodulation distortion, the self-healing transceiver must be able to first estimate the OIM2 and OIM3 and then be able to control the RF transceiver's bias, or amplifier gain to get a good tradeoff between non-linearity, noise, and gain performances.

Fig. 2.6. Intermodulation impairments contributing to SNDR degradation

## **DC Offset**

The origin of DC offset comes from nonlinearity and self-mixing of the LO and RF input ports of a mixer. The leakage from LO can come back to the mixer input ports and mix with the LO itself. When the circuits have even-order nonlinearity, large DC offsets can arise. DC offset will saturate the different stages of the receiver, lowering the receiver dynamic range and eventually make the receiver fail. To heal the DC offset, the self-healing transceiver can first measure its nonlinearity by applying 1-tone or 2-tone test and then by applying

some offset cancelling technique by adding additional offset at the digital transmitter side

# **Chapter 3 Self-Healing 60 GHz Transceiver**

In this chapter the self-healing 60 GHz transceiver is discussed and the circuits necessary for self-healing functions as well as the algorithms to perform self-healing will be introduced.

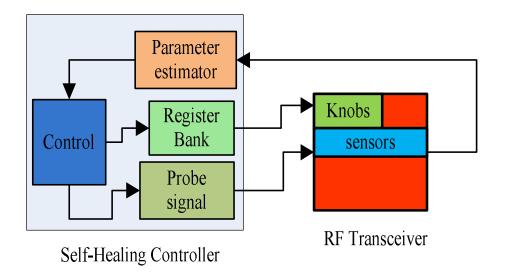

#### 3. 1 Top Level View of the Self-Healing Controller

From Chapter 2, the concepts and motivations of self-healing for a RF transceiver to perform multiple parameter calibration were discussed. In this chapter, the architecture and the circuits for the self-healing transceiver will be introduced. From a top-level view, to calibrate multiple transceiver circuit parameters and monitor its performance and address statistical process variations, it would require some sort of a digital signal processor or 'controller' that acquires transceiver parameter information [11]. And based on the signal processor's distortion analysis, the self-healing controller would be able to take actions and control the RF transceiver to impair with the impairment effects and perform transceiver optimization. The whole self-healing optimization loop would involve in digital, mixed-signal, and analog RF circuits to achieve these tasks. The self-healing controller itself would be in a form of a finite-state-machine equipped with different circuit calibration algorithms.

In summary, the basic flow of the circuit self-healing process is as follows:

- (1) Send out some probe testing signals through the transceiver chain.

- (2) RF Sensors to sense the environmental changes and be able to accurately respond to these environmental changes for the self-healing controller to monitor after the probe signals have been excited.

- (3) The transceiver circuit blocks have control 'knobs' for the self-healing controller to compensate for the process and environment variations. These knobs can be used to adjust various transceiver circuit parameters like bias, gain, capacitance, or current.

- (4) The self-healing controller continues on monitoring the transceiver and tune the circuit control knobs until the targeted circuit or microsystem achieve the final performance specification.

The whole self-healing optimization loop in the higher level can be summarized into 4 steps: (1) probe testing signal (2) sensors sense environmental changes (3) self-healing controller monitor the sensor changes (4) adjusting the circuit control knobs to optimize transceiver performance. A block diagram of the self-healing optimization loop is shown in Fig.3.1.

Fig. 3.1. High-level block diagram of the self-healing transceiver system

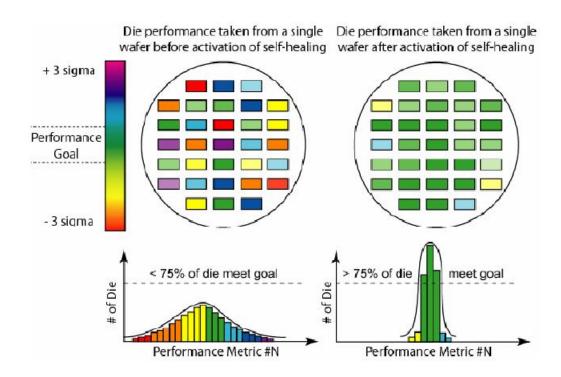

The goal of the self-healing system targeted by UCLA HSEL's Healics project is shown in Fig. 3.2. Prior to the self-healing, less than 75% of the transceiver dies would meet the target performance. After applying self-healing and calibrating for the process and environmental variations, more than 7% % of the dies would meet the target performance. By applying self-healing, the total effective yield of the dies would increase thereby reducing the total fabrication costs.

Fig. 3.2. Yield increase by applying self-healing

Now that the optimization flow of the self-healing controller has been introduced the circuits and datapath necessary for the self-healing controller can be investigated.

## 3.2 Circuits and Sensors for Self-Healing

### Test tone generator

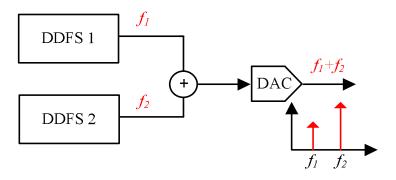

The self-healing controller needs to probe the mm-Wave 60 GHz transceiver before the transceiver status can be monitored [14]. This would mean some sort of a signal generator to send out test signals and excite the transceiver. Since the monitoring of the 60 GHz RF transceiver would involve in intermodulation and harmonics, a signal generator suited for this purpose would be one that can generate arbitrary 1-tone or 2-tone sinusoidal waveforms. Direct digital frequency synthesizer (DDFS) would serve this purpose of 1-tone/2-tone generation. One DDFS unit can generate a single tone. By combing the outputs of two DDFS together, two tone probe signals can be generated. Fig. 3.3 shows schematic of DDFS two tone generation.

Fig. 3.3. DDFS two tone generation

#### Parameter estimator

To monitor and the environmental changes and the spectrum of image or intermodulation signals, parameter estimator is needed in the self-healing controller. This parameter estimator is a FFT based spectrum analyzer that can estimate the output spectrum of the transmitter or receiver or various different RF sensors on the transceiver. To combat thermal noise, this parameter estimator can average over multiple FFT processing's to achieve the targeted SNR requirements. The design of the parameter estimator is further discussed in Chapter 4.

## **Auxiliary Mixed-Signal Data Converters**

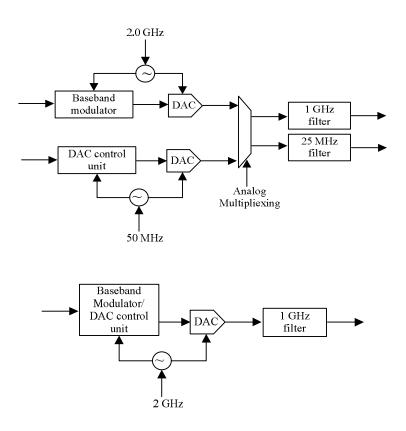

To convert the digital outputs of the DDFS based signal probe generator to analog waveform, a digital-to-analog (DAC) is necessary. Initially an auxiliary high resolution but low speed and low powered DAC is desired to drive the probe signals. Having an auxiliary DAC has several benefits. First, the probe signal generator and the auxiliary DAC can be clocked at low frequency to save the power for self-healing. Second, at low frequency, it makes the DDFS probe signal generator design much easier. Third, high SFDR and effective number of bits (ENOB) on the auxiliary DAC can be easily achieved at low clock frequency thereby improving the overall sensing resolution of the self-healing controller. However, with the auxiliary DAC and the wide bandwidth signaling DAC both present on the integrated SOC, it makes the antialiasing filter solution complicated. Two sets of passive filters are necessary on the self-healing transceiver SOC, one for low frequency but high linearity 7 bit auxiliary DAC.

And one 5b DAC for high frequency 16-QAM complex modulation, but the linearity requirements are more relaxed for the signaling DAC. Also, a high linearity analog multiplexer is necessary to switch between the high resolution and the low resolution DACs making the dual DAC implementation impractical. Instead, the auxiliary DAC and the signaling DAC are combined together and replaced with a high speed 10b (7b ENOB) DAC to save power/area and the implementation efforts of the analog multiplexer and extra anti-aliasing filters. Fig. 3.4 shows block diagram of the two implementation strategies and (a) is chosen over (b).

Fig. 3.4. (a) Dual DAC implementation strategy (b) Combined signal and auxiliary DAC

On the receiver side there are both a 10 bit 10 MHz auxiliary ADC for monitoring the changes of the RF sensors for self-healing purposes, and a 7b 2 GHz signaling ADC for 16 QAM signal demodulation. Trying to merge the auxiliary ADC and the signaling ADC together to a 10b 2 GHz ADC is much harder and the power consumption is much higher than keeping them separate. So for the 60 GHz self-healing transceiver, there are two sets of ADCs, the auxiliary ADC for self-healing and the signal ADC for demodulation.

## Sensors and Tuning Knobs for Self-Healing

Different RF sensors are placed at the 60 GHz self-healing transceiver for monitoring the system and environmental changes [15]. Temperature sensors are placed near the temperature sensitive circuits like the power amplifier (PA) or the receiver low noise amplifier (LNA). PA consumes a major portion of the transmitter power, overheating the PA will degrade the performance of the PA and the circuits close to PA. The temperature sensor on the receiver side is used to measure the noise power or kTB and this noise power can be applied to measure the noise figure (NF) thereby healing the receiver noise figure by tuning the gain stages of the LNA. To account for the temperature sensor's resolution fluxuation, the temperature sensor resolution is set to less than 1° C in order to be applied as noise reference. The analog outputs of temperature sensors are quantized by the auxiliary ADC to static digital codes and can be read directly by the self-healing controller.

To sense the intermodulation and nonlinearity behavior at the transmitter side, an envelope detector sensor is applied. The envelope detector is a squaring device which can down-covert the intermodulation distortion and the images to the baseband. With envelope detector, the transmitter IQ mismatch can be measured independent of the receiver chain. It's worth noting that the envelope detector's dynamic range must be larger than the intermodulation and IQ mismatch specifications which was defined at 40 dB and – 40dB. Once the probe signal is sent through the transmitter chain, the envelope detector output with the intermodulation can be digitized by the auxiliary ADC and its spectrum can be analyzed by the FFT based spectrum analyzer on the self-healing controller. By analyzing the intermodulation spectrum, the gain or the bias on the transmitter PA stages can be adjusted until it meets the targeted specification.

Power detector sensor is applied on the transmitter and coupled to PA output to measure the PA output gain and measure the P1dB. Again, the output of the power detector is digitized by the auxiliary ADC and the gain stages of the PA and can be adjusted until the transmitter meets the output P1dB requirements. The dynamic range of the power detector need not to be very strict in design, it only needs to detect  $\pm$  5 dB of the power centered on the output P1 dB.

The design of the tuning knobs on the transceiver circuit blocks like transmitter, PA, LNA, receiver programmable gain amplifier are critical to effectively heal the circuit parameters. Tuning knobs can be either analog or digital control knobs. For analog control knobs, based on the monitored results

like intermodulation spectrum or temperature output code, the self-healing controller can adjust the tuning knobs to change the settings of the analog RF transceiver circuits. These knobs include fine-grained biasing, capacitor bank tuning and varactors in an LC tank. These tuning knobs are present at the input of LNA and are adjusted to heal the noise figure or tune the frequency of the VCO on the PLL to optimize the phase noise performance. Digital control knobs can be regarded as the digital tuning of the DC offset, gain tuning, IQ phase rotation on the digital probe signals that drive the DAC. This predistortion or initial digital signal tuning can be applied to heal the intermodulation and the IQ mismatch effects of the 60 GHz self-healing transceiver.

### 3.3 Self-Healing Algorithms

In this section we go into the algorithm and sequencing flow to heal each circuit or microsystem performance parameter of the self-healing 60 GHz transceiver [11].

#### **Transmitter Image Healing**

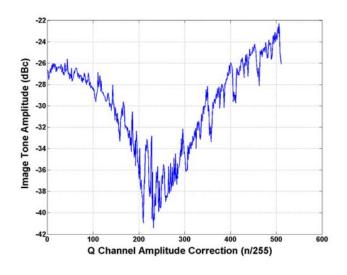

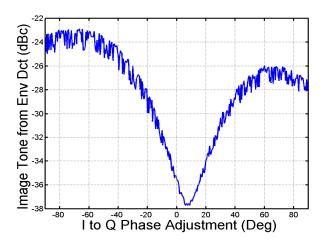

Transmitter image healing is the first step of the self-healing process. Once the image signal is suppressed it will make the transmitter output power measurement much straightforward. If the image issue is not resolved, the image signal cannot be distinguished from the actual signal. Transmitter image healing is accomplished by sending single-tone testing signals through the probe signal generator. The transmitter envelope detector is applied to capture the image signal

power. Since the envelope detector is connected to the auxiliary ADC, the spectrum of the transmitter and image signal information is captured by running FFT analysis on the on-chip PSD processor. The transmitter image is healed by adjusting the amplitude and phase control knobs on the DAC input or the DDFS IQ unit.

## Transmitter Local Oscillator Leakage Healing

To heal the local oscillator (LO) leakage, a single-tone probe signal is applied through the transmitter to the envelope detector. By measuring the spectrum of the envelope detector output, the LO leakage can be calculated by summing out the energy leakage on the FFT bins. To heal for the LO leakage, the IQ unit on the digital probe is adjusted until the LO leakage is below the required specification.

# **Transmitter P1dB Healing**

To heal the transmitter P1dB, a ramping signal with increasing power is sent from the DDFS probe signal generator. The increasing signal power level of the test tone is accomplished by tuning the digital gain control codes on the DDFS IQ unit. The output power information is captured through the power detector which is coupled with the PA. The transmitter gain can then be measured by computing the ratio between transmitter input power to the transmitter output power. The P1dB is the point where the output gain drops by 1dB.

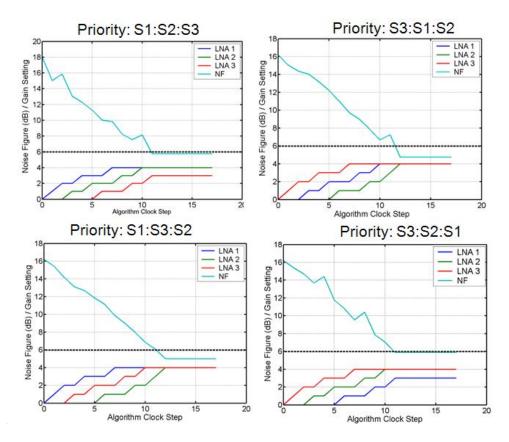

#### **Transmitter and Receiver OIM3 Healing**

To heal the transmitter or receiver's output third order intermodulation is to apply two tone signal generation on the DDFS probe to the transmitter or to the receiver. For transmitter OIM3 healing, once the two-tone signals are sent, the self-healing FFT PSD processor measures the spectrum on the output of the transmitter envelop detector. By tuning the control knobs of the PA bias and output gain stages, the OIM3 level can be adjusted. For the receiver OIM3, two-tone testing signals are generated from the DDFS and to the transmitter chain and sent to the receiver. The transmitter and the receiver are connected using a fixed power attenuator and the receiver OIM3 can be measured. Once the transmitter OIM3 is measured, the receiver OIM3 can be calculated. To heal the OIM3 on the receiver, the LNA knobs are adjusted to achieve the specification requirements.

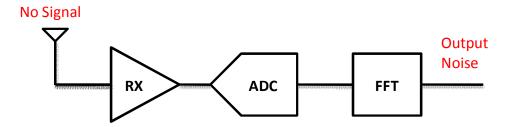

## **Receiver Noise Figure Healing**

The receiver noise figure (NF) is defined as:

$$NF = \frac{SNR_{in}}{SNR_{out}} = \frac{S_{in}/N_{in}}{S_{out}/N_{out}} = \frac{N_{in}}{A_{RX}/N_{out}}$$

(3.1)

Where in (3.1)  $A_{RX}$  is the gain of the receiver,  $N_{in}$  is the noise at the receiver input, and  $N_{out}$  is the noise at the receiver output. The input noise is equal to kTB, where k is Boltzmann's constant, T is the temperature, and B is the bandwidth. The temperature sensor on the transceiver can provide the value of T, and the bandwidth of the receiver is determined by the RX filter which is 1.2GHz. To calculate the receiver noise figure, only the output noise is left to be measured. To measure the output noise, the configuration shown in Fig. 3.5 is applied. When

no signal is present at the receiver, the output noise of the receiver can be measured by summing all values of the FFT bins on the parameter estimator. With this information, the noise figure of the receiver can be calculated, and then used to perform the NF healing. And to heal the receiver noise figure, the LNA input and output stage knobs are adjusted.

Fig.3.5. Measuring the receiver output noise

# **Chapter 4 DSP Circuits for 60 GHz Self-Healing**

# **Transceiver and Self-Healing Transceiver**

# **Implementation Results**

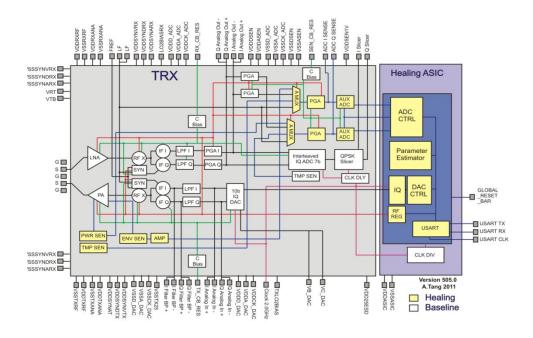

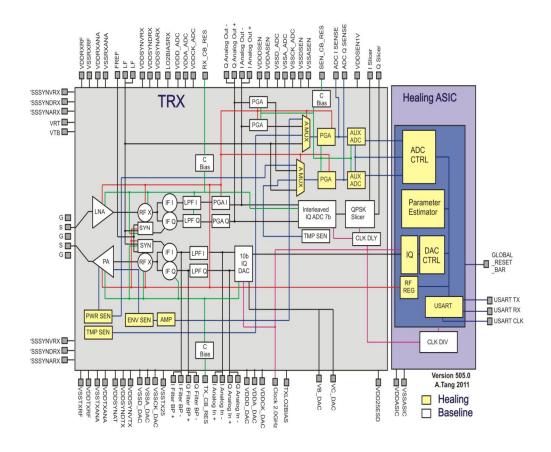

In this chapter, the DSP circuits applied to implement the algorithms for self-healing are discussed more in detail. This chapter will also present the system level measurement results of the 4 Gb/s self-healing 60 GHz mixed-signal transceiver SOC. Fig 4.1 shows the architectural details of the 60 GHz self-healing transceiver.

Fig.4.1. Architecture of the 4.0 Gb/s 60 GHz self-healing transceiver

The signaling rate on this transceiver is designed at 1 GS/s. The DAC and the signaling ADC are both clocked at 2GHz. The modulation formats supported by this transceiver are BPSK, QPSK, and 16QAM. This translates to 4 Gb/s throughput. The digital circuits and systems collectively called as the self-healing controller on the self-healing 60 GHz transceiver are implemented in application specific integrated circuit (ASIC) style and this self-healing ASIC includes:

**ADC CTRL unit:** The ADC control unit is used to acquire the cyclic 10 MS/s auxiliary ADC digital outputs, and the digital outputs can provide the parameter estimator to perform spectral analysis or statistical averaging to aid on the monitoring of the RF transceiver sensors.

Parameter estimator unit: The parameter estimator unit is a 128pt FFT processor based spectrum analyzer. The bandwidth of this FFT processor is determined by the sampling rate of the auxiliary ADC which is 10 MS/s and this translates to a Nyquist frequency of 5 MHz. The frequency resolution of each FFT bin is 10MHz/128 = 0.78 kHz. Besides performing FFT analysis, the parameter estimator also computes the periodogram which is the estimated spectrum of the RF sensor outputs. The FFT processing within the parameter estimator unit can be configured to perform averages in any 2's power number from 32~1024. The outputs of the estimated spectrum are saved in the on-chip registers for read out.

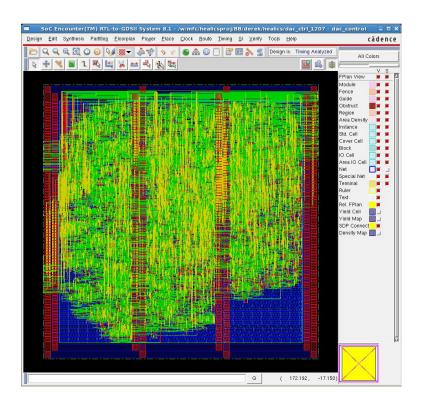

**DAC CTRL unit:** The DAC control unit is a multimode signal function generator to drive the mixed-signal DAC. The DAC control unit throughput is at 2 GHz which is the same as the auxiliary/signaling DAC. The DAC control unit can

generate 1-tone or 2-tone sinusoidal signals for self-healing purposes or on-chip pseudo-random-bit-sequence (PRBS) based BPSK, QPSK, or 16 QAM modulation signals for transceiver loop back testing. Although the overall throughput of the DAC control unit is at 2 GHz, the internal architecture of the DAC control unit is running at 500 MHz and then time interleaved to 2 GHz to meet the timing requirements of the 65nm process.

**IQ unit:** The IQ unit is the digital predistortion and phase rotation unit of the DAC control unit. The IQ unit can add additional DC offset, gain control, and lookup table mapping for the digital outputs from the DAC control unit. By applying digital predistortion or phase rotation, it aids the self-healing controller in RF parameter monitoring and IQ mismatch correction.

**RF REG unit:** The RF register unit is a 256 register bank that stores the transceiver knob values in digital codes. It works with the self-healing controller as a storage unit that saves the current settings of the RF circuit control knobs. And by assigning different digital codes through the USART unit, the RF register unit can be reprogrammed into different knob settings.

**USART unit:** The universal serial asynchronous receiver transfer (USART) unit is the serial interface in which through the PC the self-healing transceiver can be configured and the self-healing algorithms can be initiated and sequenced. Also, all the control knob digital codes are written through USART, and the parameter estimator values can be read through USART to the PC for further post processing. The USART is clocked by a low frequency digital clock (<1 MHz)

provided by the PC to save the area and power for on-chip clock sources. Basically through USART all the complex self-healing algorithms can be initiated, reconfigured, and transceiver parameter values can be read out. The USART is the main platform for the self-healing transceiver testing and functional verification.

## 4.1 DAC Control and IQ Unit

The DAC control unit is a direct digital frequency synthesizer (DDFS) based 1-tone or 2-tone generator that can be used to generate probe signals for the 60 GHz self-healing transceiver and also provide modulation signals for transceiver loop-back tests. The high speed 2.0 GHz DAC can achieve 43 dB SFDR at Nyquist (1 GHz), this sets the limit on the SFDR performance of the DAC and DDFS combined chain. Therefore, the SFDR of the DDFS in this DAC control has to be kept larger than 50 dB SFDR to avoid signal degradation over the whole transmitter chain. Since this DAC control unit has to be clocked at 2.0 GHz using the CMOS 65nm process, the DDFS design is mainly challenged by the area available on chip and the strict timing constraint requirements [16],[17]. Therefore, the DDFS requires an architecture that applies simple and fast logics while maintaining SFDR above 50 dB.

The presented DDFS is a 2.0 GHz DDFS with I/Q quadrature output control. This DDFS design is able to generate quadrature signals with one-tone or two-

tones. These two quadrature carriers are out of phase with each other by 90°, and it is extremely useful in nonlinearity performance verification of wireless communication applications. Not only the frequency of the output waveforms is configurable, the amplitude scaling of the waveform amplitude can also be modified, and an offset to the amplitude can be added to either output by the IQ unit. These features are added to reduce the LO leakage for the RF transceiver. In addition, phase rotation can be added to the quadrature component. The I/Q rotation is implemented to compensate or predistort the I/Q mismatch effects in the transceiver.

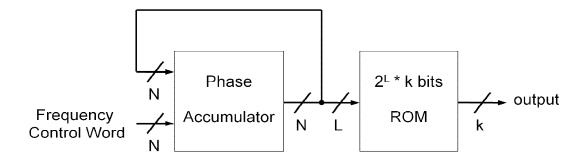

The basic concepts for a DDFS are as follows [18]. Assuming that an N-bit frequency control word goes into the input of the phase accumulator and the output of the phase accumulator is an L-bit number where L is smaller than N. The L-bit code is used to select an entry in the ROM look up table. This means that the look up table will have  $2^L$  entries. The block diagram of the DDFS with uncompressed ROM is shown in Figure 4.2. The frequency tuning resolution and the SFDR of the DDFS can be increased by increasing L, but the number of entries in the look up table will increase exponentially consuming more area and power. If each entry in the look up table has a length of K bits, then the ROM has a size of  $2^L x K$  bits. The higher the number of K is, the higher the SFDR the DDFS achieves.

Figure 4.2. Block diagram of the DDFS with uncompressed ROM

In order to implement a DDFS with a fine resolution and high SFDR, a very large ROM size is required when the brute force look up approach is applied. A large ROM would imply a circuit with large area, large power, and computation delay. Therefore, aggressive compression and interpolation algorithms are desired in a DDFS design to reduce the size of the ROM look up table [19], [20].

# **Taylor Series Approximation**

In the proposed DDFS, Taylor series approximation based look up table is applied. The Taylor series is a representation of any function as the sum of infinite amount of terms calculated from the derivatives of this function at a given point [21]. If f(x) is the function, and point "a" is the given point that the Taylor series is expanding from, then the Taylor series representation of this function is:

$$f(x) = \sum_{n=1}^{\infty} \frac{f^{(n)}(a)}{n!} (x - a)^n$$

(4.1)

where in (4.1)  $f^{(n)}$  denotes the n-th derivative of the function f.

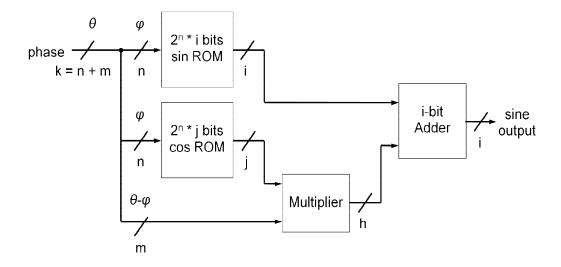

Assuming that the DDFS generates a k-bit phase input  $\theta$ , the n MSB's of the phase input is denoted as  $\varphi$ , and the m LSB's of the phase input is denoted as  $(\theta-\varphi)$ . Then the sine and cosine values with the input phase  $\theta$  can be represented with the Taylor series expanding at point  $\varphi$

The first two terms in the Taylor series provides a very accurate approximation of the sine and cosine function. Instead of using a full sized ROM with  $2^k$  entries, only two ROM's are needed to store the values of  $\sin(\varphi)$  and  $\cos(\varphi)$  with size  $2^m$  and  $2^n$  respectively. The only drawback for this approach is that extra adder and multiplier are needed to implement this technique, and conventional multipliers are slow and area consuming. The block diagram of the Taylor series approximation based phase-to-sine converter on the DDFS is shown in Fig. 4.3. The cosine wave is also generated with a similar architecture.

Figure 4.3. Block diagram of Taylor series approximation for sine wave output

Different ROM compression methods have been proposed in the literatures in the past and their compression ratio and SFDR performance are summarized in Table 4.1.

Table 4.1 SFDR performance of various compression techniques

| References                 | Compression | SFDR      |

|----------------------------|-------------|-----------|

| Ballaouar [22]             | 21:1        | 65 dBc    |

| Conventional Taylor Series | 64:1        | 97.04 dBc |

| Essenwanger [23]           | 67:1        | 97.23dBc  |

| Eltawil [24]               | 157:1       | 64.6dBc   |

In the proposed DDFS architecture, the proposed ROM compression approach is modified from the Taylor series approximation and similar to the Taylor series linear interpolation technique referenced from [21]. With a phase input  $\theta$ , the sine and cosine values can be calculated as follows:

$$\sin(\theta) = \sin(\theta_i) \pm \alpha(\theta - \theta_i) + \delta_{\sin}$$

$$\cos(\theta) = \cos(\theta_i) \mp \beta(\theta - \theta_i) + \delta_{\cos}$$

(4.2)

where  $\theta_i$  is the MSB of the phase input  $\theta$ , and  $(\theta - \theta_i)$  represents the LSB of the phase input  $\theta$ . The phase input  $\theta$  is a value between  $\theta_i$  and  $\theta_{i+1}$ , which are the two consecutive phase address used for the coarse ROM's that store the predetermined sine and cosine values.  $\alpha$  and  $\beta$  are the pre-determined interpolation coefficients used to generate the fine correction to the sine and cosine values.  $\delta_{sin}$  and  $\delta_{cos}$  are the small errors introduced in the Taylor series linear interpolation method. Two coarse ROM's are used to store the sine and cosine values from 0 to

$\pi/4$ . The sine and cosine values were previously determined and translated into binary codes. 5 bits are used to access the coarse ROM and each ROM has  $2^5 = 32$  entries. With a 10b DDFS output, each entry in the ROM have a length of 9b because the MSB is the sign bit of the output, which can be determined by the MSB of the phase bits. Each ROM has a size of  $2^5 x9 = 288$  bits, and a total of 576 bits are used for the coarse ROM in the DDFS design, which leads to a compression ratio 142:1.

The pre-determined interpolation coefficients  $\alpha$  and  $\beta$  need to be multiplied by  $(\theta - \theta_i)$  to obtain the fine correction to the sine and cosine values generated by the coarse ROM's. The complex multiplier and the ROM required are replaced by hardwired shift-and-add based constant multiplier to reduce the circuit complexity and operating frequency. Since only the first two terms in (4.2) are implemented to approximate the sine and cosine values, the Taylor series linear interpolation error  $\delta_{sin}$  and  $\delta_{cos}$  are introduced. These two values are closely approximated by the third term in (4.2)

$$\delta_{\cos} \approx -(\theta - \theta_i)^2 \frac{\cos(\theta_i)}{2}$$

(4.3)

Since the maximum values of  $sin(\theta_i)$  and  $cos(\theta_i)$  are 1, the terms  $\delta_{sin}$  and  $\delta_{cos}$  have the following upper limit:

$$\left| \delta_{\sin \max} \right| = \frac{(\theta - \theta_i)^2}{2}$$

$$\left| \delta_{\cos \max} \right| = \frac{(\theta - \theta_i)^2}{2} \tag{4.4}$$

The maximum value of  $(\theta - \theta_i)$  is equal to the difference between two of the consecutive phase addresses used for the coarse ROMs. With m=5 bits, the interpolation error for phases between 0 to  $\pi/4$  is  $(\theta - \theta_i) = \pi/4/2^5 = 0.02454$ . Then  $|\delta_{sinmax}| = |\delta_{cosmax}| = 3.012 \times 10^{-4}$ , which translates to an achievable SFDR of 70.4 dBc theoretically.

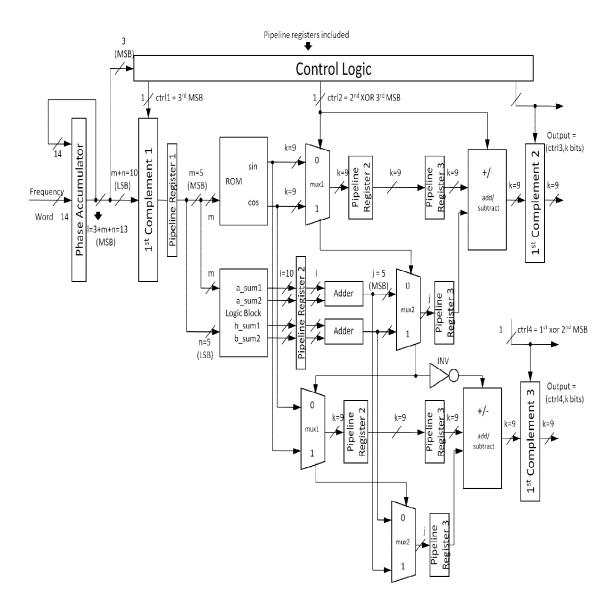

### **DDFS Core Unit Architecture**

The DDFS core unit architecture that is shown in Figure 4.4. The input to the DDFS is a 14-bits frequency control word, which goes into the 14-bit phase accumulator. 13 bits of the phase accumulator are used for the phase-to-amplitude conversion. The 3 MSB of the phase accumulator output are feed into a control logic, which is used to generate the full sine and cosine function from the ROM's that only store 0 to  $\pi/4$  of the sine and cosine values. The middle m=5 bits are used to address the coarse ROM, and the n=5 LSB are used to generate the fine correction values. The outputs of the adder/subtractor go through the second one's complement logic block, and the MSB of the output of the phase accumulator are added in the beginning to generate the final DDFS sine and cosine output.

Figure 4.4. DDFS core unit architecture

In order to meet the time constraint requirements of 500 MHz for a single sub-DDFS, the proposed architecture needs to be split into several pipeline stages by inserting registers in between blocks with long computation paths. The pipeline registers are added before and after the phase accumulators, the adders/subtractors, and the fine interpolation logic blocks that generates the waveform fine correction. Another extra stage of pipeline registers are added after the ROM output to let all

the input samples of the last adders/subtractors arrive at the same clock cycle. Extra pipeline registers are added within the control logic to ensure that the logic signals are synchronized with the data signals. The drawbacks of adding pipeline registers are the area/power consumed by the pipeline registers and the additional signal delays in the system [25].

The 3 MSB of the phase bits determines which quadrant the phase is located in, and the control logic block takes the 3 MSB and distributes control signals too all the blocks in the system. The 1<sup>st</sup> MSB is used to control the one's complement block at the sine output, and the 1<sup>st</sup> MSB XOR 2<sup>nd</sup> MSB is used to control the one's complement block at the cosine output. The 3<sup>rd</sup> MSB is used to control the one's complement block after the phase accumulator, then it is XOR with 2<sup>nd</sup> MSB to control the outputs of the MUX's after the ROM's. Table 3.1 summarizes the output signals generated by the control logic block. These control signals provides this DDFS architecture to generate the full sine and cosine quadrature waveforms with only storing phase address of 0 to  $\pi/4$  in the ROM's.

Table 4.2. Summary of DDFS control signals

| 3 MSB        | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|--------------|---|---|---|---|---|---|---|---|

| one's        | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| one's        | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| one's        | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| MUX 1        | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| MUX 2        | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| sine add/sub | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| cosine       | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

The phase accumulator in the proposed DDFS is a 14-bit phase accumulator with no pipeline stages added. This phase accumulator is the circuit with the longest signal path in this architecture, and it should be optimized in logic synthesis and place and route to meet the timing requirements of the overall system.

The sine and cosine functions from phase 0 to  $\pi/4$  are broken into 32 intervals and stored in one physical ROM. These 32 sine and cosine values are analyzed in MATLAB and converted into binary representations for Verilog RTL coding. The coarse ROM has a total of 32 entries with 5-bit access address, and each entry is a 9-bit data. The total size of the DDFS ROM is 576 bits.

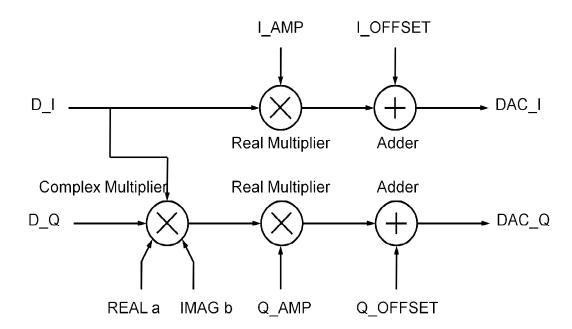

# DDFS with I/Q Output Control

The I/Q unit is a block that can change the gain, DC offset, and phase output of the DAC control core unit, and this is added between the DDFS core unit and the DAC. I/Q unit block can adjust the magnitude and the scaling of the waveform, and it can be used to fix the LO leakage in the RF transceiver [11],[4]. In addition, the I/Q unit can add a phase offset to compensate the I/Q mismatch effects of the transceiver. Figure 4.5 shows the block diagram of the I/Q unit. It consists of two adders and two real multipliers for both quadrature real and imaginary branch, and one complex multiplier for the imaginary signal branch. Pipelines stages are added between each operation to accommodate the required timing constraints.

Figure 4.5. Block diagram of the I/Q unit

D\_I and D\_Q are the quadrature cosine and sine outputs from the DAC control core unit. The signal D\_Q (sine output) then goes through a complex multiplier that rotates the phase of the D\_Q waveform by a specified degrees, which is controlled by the variables a and b. The phase rotated output D\_Q<sub>rotated</sub> value can be calculated with the following equation:

$$D_{Q_{rotated}} = D_{Q} \times a + D_{I} \times b$$

(4.5)

Where the D\_Q<sub>rotated</sub> is the output of the complex multiplier. Assuming that the signal D\_Q is rotated by a phase  $\theta$ , the inputs a and b is determined by  $a = \cos(\theta)$  and  $b = \sin(\theta)$ . The values of a and b can calculated on the PC side and assigned through the USART interface and stored in the on-chip control registers.

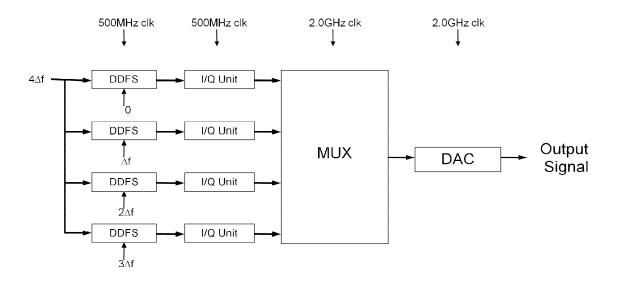

Even with interpolation optimization techniques to reduce the ROM size and pipelining to reduce the computation critical path, it's still not enough to meet the timing constraints of 2.0 GHz clock frequency. Parallel interleaving technique is applied to increase the processing throughput of the DDFS to 2.0 GHz by multiplexing 4 paths of sub-DDFS each operating at 500 MHz [25]. The block diagram of the 4-parallel time interleaved DDFS is shown in Fig. 4.6. For a frequency control word of  $\Delta f$ , a shift operation is applied to generate  $4*\Delta f$  signal, which is then feed to the inputs of four identical DDFS core units that are each clocked by 500 MHz. Each sub-DDFS unit has a different starting phase in the phase accumulator. The I/Q unit following the DDFS core are also 4-parallel interleaved and each clocked at 500MHz. The outputs signals of these four I/Q units are finally feed into a high speed multiplexer clocked at 2 GHz. The 2 GHz

digital output of this multiplexer (MUX) then drives the DAC that converts the digital waveforms into analog ones.

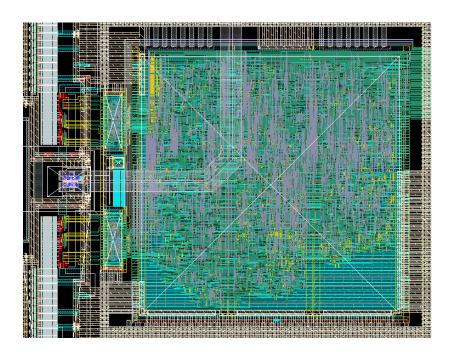

Figure 4.6. Block diagram of the 2.0 GHz DDFS with I/Q output control

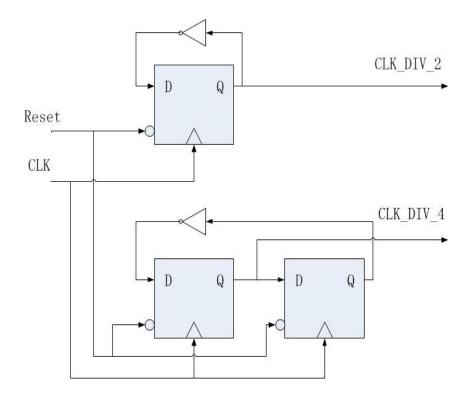

The system is provided with a 2.0 GHz master clock from external signal generator instrument, and a divided-by-4 clock divider is required to generate the 500MHz clock for the DDFS core units and the sub-I/Q units. The divide-by-4 clock divider is implemented by a 2-bit synchronous counter. Fig. 4.7 shows the circuit schematic of the clock divider. In Fig.4.7, CLK\_DIV\_4 and CLK\_DIV\_2 are respectively the divided by 2 and divided by 4 clock signals.

Fig. 4.7. Schematic of the clock divider