# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Compact Modeling of Advanced CMOS and Emerging Devices for Circuit Simulation

#### **Permalink**

https://escholarship.org/uc/item/5qn6m735

#### **Author**

Lin, Yen-Kai

#### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

By

#### Yen-Kai Lin

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu, Chair Professor Sayeef Salahuddin Professor Junqiao Wu

Spring 2019

# Compact Modeling of Advanced CMOS and Emerging Devices for Circuit Simulation

Copyright 2019 by Yen-Kai Lin

#### Abstract

Compact Modeling of Advanced CMOS and Emerging Devices for Circuit Simulation

by

#### Yen-Kai Lin

${\it Doctor\ of\ Philosophy\ in\ Engineering\ -\ Electrical\ Engineering\ and\ Computer\ Sciences}$   ${\it University\ of\ California,\ Berkeley}$

Professor Chenming Hu, Chair

Compact model plays an important role in designing integrated circuits and serves as a bridge to share the information between foundries and circuit designers. Since various flavors of transistor architectures like FDSOIs and FinFETs are proposed to improve device performances, the accurate, fast, and robust compact models, which are capable of reproducing the very complicated transistor characteristics like transconductance, are urgently required. Novel device concept, such as tunnel FETs (TFETs) and negative capacitance FETs (NCFETs), needs new device modeling methodology and understanding of device physics. In addition to transistors, memory device like magnetic tunnel junction (MTJ) compact model is also crucial for circuit designs. This dissertation presented the advanced research on compact models for the state-of-the art transistor and memory technologies: FDSOIs, FinFETs, TFETs, NCFETs, and MTJs.

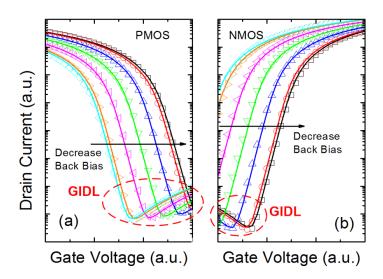

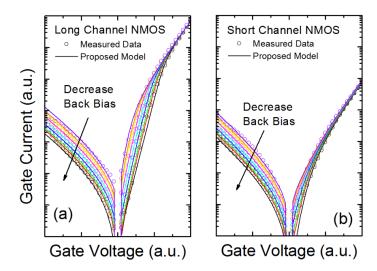

Due to the limitations in the aggressively scaled planar transistors, the devices with good electrostatic control are discussed and modeled into the industry standard model — BSIM-IMG for FDSOIs and BSIM-CMG for multi-gate FETs. Although the dynamic back-gate bias change help reduce the static power in FDSOIs, the leakages, overlap capacitance, and carrier transport are thus showing back-gate bias-dependence. The enhanced gate-related leakage, overlap capacitance, and mobility compact models are validated against the silicon data and incorporated into BSIM-IMG. The leakages through subsurface path and source-to-drain direct tunneling due to extremely short channel are also included in this work, which are in excellent agreement with the technology computer-aided design (TCAD) and atomistic simulations. The computationally efficiency of these models are the key solutions for evaluating the circuit performance of future technology nodes.

Two paradigms of steep subthreshold slope transistors — TFETs and NCFETs as the promising candidates for future Internet of Things (IoT) and logic/analog applications are also presented in this thesis. TFET has a gated p-i-n diode structure, where the current relies on direct band-to-band tunneling in source/channel junction. Such tunneling mechanism breaks the tradition limitation of MOSFET turn-ON characteristics called the Boltzmann tyranny. The improvements in power consumption and delay of circuits are thus the emphasis and attention of device community, where the need of TFET compact model is fulfilled with the developed model in this work. NCFET is rapidly emerging as a preferred replacement for traditional MOSFET since the recent discovery of ferroelectric (FE) materials to amplify the voltage suggests

that further scaling supply voltage is possible with the CMOS-compatible fabrication process of NCFET. The short channel effect, ferroelectric variability, and spacer optimization design are the focus in this thesis. The compact model of NCFET is improved to be more predictive for ferroelectric properties with verification against TCAD simulations. Monte-Carlo method is carried out in FE variability study, where the main finding is that the dielectric phase is critical but fortunately is theoretically possible to be absent. The spacer design reveals that further engineering the capacitance matching via parasitic capacitance is the key solution for future technology nodes.

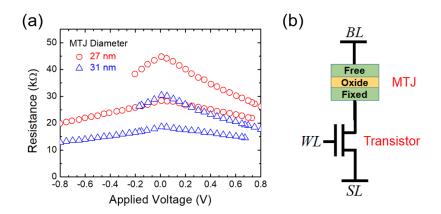

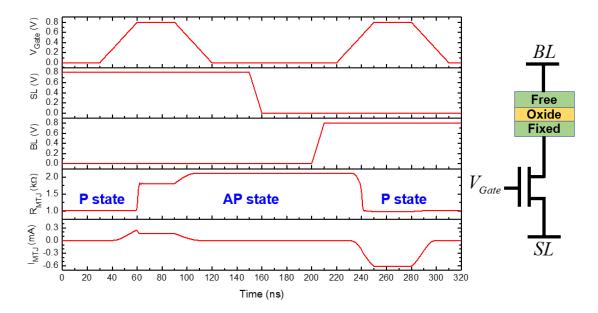

In addition to transistor compact models and physics, the memory device — spin-transfer-torque magnetic tunnel junction (STT-MTJ) is also presented. The resistances and critical currents are derived from the Landau-Lifshitz-Gilbert (LLG) equation and modeled analytically. The RC sub-circuit is found to describe the dynamic switching behavior of MTJ due to the precession and thermal fluctuation. The proposed MTJ compact model has been validated with silicon data from the industry and is capable of simulating a memory circuit with previously mentioned BSIM models.

# Dedicated to my family

# Contents

| Co       | onter | nts                                                     | i  |

|----------|-------|---------------------------------------------------------|----|

| Li       | st of | Figures                                                 | iv |

| Li       | st of | Tables                                                  | xi |

| 1        | Intr  | roduction                                               | 1  |

|          | 1.1   | Why Compact Model Is Needed?                            | 1  |

|          |       | 1.1.1 TCAD and Compact Model                            | 1  |

|          |       | 1.1.2 Overview of BSIM                                  |    |

|          | 1.2   | Advanced CMOS and Emerging Devices                      |    |

|          |       | 1.2.1 Challenges in CMOS Scaling                        |    |

|          |       | 1.2.2 State-of-the-Art Devices                          |    |

| <b>2</b> | Mod   | deling Back-Gate Bias Effects in FDSOIs                 | 8  |

|          | 2.1   | Introduction                                            |    |

|          | 2.2   | Back-Gate Bias Dependent Leakages Models                |    |

|          |       | 2.2.1 Gate-Induced Drain Leakage (GIDL)                 | 8  |

|          |       | 2.2.2 Gate Leakage                                      | 10 |

|          | 2.3   | Dual Mobility Model                                     | 13 |

|          |       | 2.3.1 Transconductance Behavior                         | 13 |

|          |       | 2.3.2 Modeling and Parameter Extraction                 | 15 |

|          |       | 2.3.3 Results and Discussion                            | 18 |

|          | 2.4   | Non-Monotonic DIBL                                      | 21 |

|          |       | 2.4.1 Device Characterization                           | 21 |

|          |       | 2.4.2 Discussions                                       | 26 |

|          | 2.5   | Back Gate Bias Dependent Overlap Capacitance Model      | 29 |

|          |       | 2.5.1 Model Description                                 | 29 |

|          |       | 2.5.2 Results and Discussion                            | 32 |

|          | 2.6   | Conclusion                                              | 33 |

| 3        | Mod   | deling Leakages in Advanced CMOSFETs                    | 35 |

|          | 3.1   | Introduction                                            | 35 |

|          | 3.2   | Sub-Surface Leakages in MOSFETs                         | 36 |

|          |       | 3.2.1 Model Description                                 | 36 |

|          |       | 3.2.2 Results and Discussion                            | 41 |

|          | 3.3   | Source-to-Drain Tunneling Leakages in Sub-10 nm Devices | 43 |

|          |       | 3.3.1 Model Description                                 | 43 |

# CONTENTS

| 4 Compact Model of Tunnel FETs       52         4.1 Introduction       52         4.2 Core Model       52         4.2.1 Surface Potential and Charge       52         4.2.2 WKB-Based Tunneling Probability       55         4.2.3 Band Tail Effect       56         4.2.4 Gaussian Quadrature Method       57         4.3 Validation with Atomistic Simulations       59         4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.2.1 Landau-Lifshitz-Gilbert (L                                                                   |    | 3.4         |                                                | 47<br>50 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|------------------------------------------------|----------|

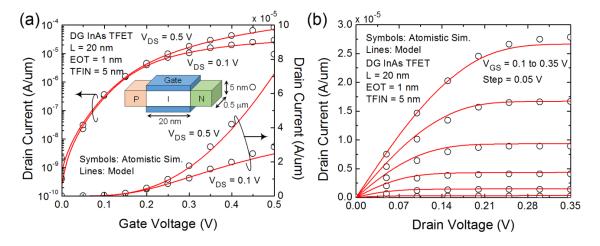

| 4.1 Introduction       52         4.2 Core Model       52         4.2.1 Surface Potential and Charge       52         4.2.2 WKB-Based Tunneling Probability       55         4.2.3 Band Tail Effect       56         4.2.4 Gaussian Quadrature Method       57         4.3 Validation with Atomistic Simulations       59         4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.2 Core Model       93 </td <td>4</td> <td>Con</td> <td>npact Model of Tunnel FETs</td> <td>52</td> | 4  | Con         | npact Model of Tunnel FETs                     | 52       |

| 4.2. Core Model       52         4.2.1 Surface Potential and Charge       52         4.2.2 WKB-Based Tunneling Probability       55         4.2.3 Band Tail Effect       56         4.2.4 Gaussian Quadrature Method       57         4.3 Validation with Atomistic Simulations       59         4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95                                                                            |    |             | •                                              | 52       |

| 4.2.1       Surface Potential and Charge       52         4.2.2       WKB-Based Tunneling Probability       55         4.2.3       Band Tail Effect       56         4.2.4       Gaussian Quadrature Method       57         4.3       Validation with Atomistic Simulations       59         4.3.1       Accuracy, Smoothness, and Speed       59         4.3.2       Model Validation       59         4.4       Conclusion       62         5       Negative Capacitance FETs: Analysis and Modeling       63         5.1       Introduction       63         5.1       Introduction       63         5.2       Compact Model       65         5.2.1       Review       65         5.2.2       Short Channel Effects       66         5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic M                                                                                                                             |    | 4.2         |                                                | 52       |

| 4.2.2       WKB-Based Tunneling Probability       55         4.2.3       Band Tail Effect       56         4.2.4       Gaussian Quadrature Method       57         4.3       Validation with Atomistic Simulations       59         4.3.1       Accuracy, Smoothness, and Speed       59         4.3.2       Model Validation       59         4.4       Conclusion       62         5       Negative Capacitance FETs: Analysis and Modeling       63         5.1       Introduction       63         5.1.1       NCFET Operation       63         5.2       Compact Model       63         5.2.1       Review       65         5.2.2       Short Channel Effects       66         5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.2.1                                                                                                                          |    |             |                                                |          |

| 4.2.3       Band Tail Effect       56         4.2.4       Gaussian Quadrature Method       57         4.3       Validation with Atomistic Simulations       59         4.3.1       Accuracy, Smoothness, and Speed       59         4.3.2       Model Validation       59         4.4       Conclusion       62         5       Negative Capacitance FETs: Analysis and Modeling       63         5.1       Introduction       63         5.1.1       NCFET Operation       63         5.2       Compact Model       65         5.2.1       Review       65         5.2.2       Short Channel Effects       66         5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.2.1       Landau-Lifs                                                                                                                             |    |             |                                                |          |

| 4.2.4 Gaussian Quadrature Method       57         4.3 Validation with Atomistic Simulations       59         4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.2.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98                                                           |    |             | O V                                            |          |

| 4.3 Validation with Atomistic Simulations       59         4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion                                                                           |    |             |                                                |          |

| 4.3.1 Accuracy, Smoothness, and Speed       59         4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       99         7 Conclusions       100         7.1 Chapters Summary       100                                                                                      |    | 4.3         | ·                                              |          |

| 4.3.2 Model Validation       59         4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100     <                                                                                 |    | 1.0         |                                                |          |

| 4.4 Conclusion       62         5 Negative Capacitance FETs: Analysis and Modeling       63         5.1 Introduction       63         5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100     <                                                                                 |    |             |                                                |          |

| 5.1       Introduction       63         5.1.1       NCFET Operation       63         5.2       Compact Model       65         5.2.1       Review       65         5.2.2       Short Channel Effects       66         5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.1.1       STT-MTJ Operation       92         6.2       Core Model       93         6.2.1       Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2       Tunneling Magnetoresistance       95         6.2.3       Dynamic Switching Model       96         6.2.4       Model Structure and Parameter Extraction       97         6.2.5       Model Validation       98         6.3       Conclusions                                                                                                                                      |    | 4.4         |                                                |          |

| 5.1       Introduction       63         5.1.1       NCFET Operation       63         5.2       Compact Model       65         5.2.1       Review       65         5.2.2       Short Channel Effects       66         5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.1.1       STT-MTJ Operation       92         6.2       Core Model       93         6.2.1       Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2       Tunneling Magnetoresistance       95         6.2.3       Dynamic Switching Model       96         6.2.4       Model Structure and Parameter Extraction       97         6.2.5       Model Validation       98         6.3       Conclusions                                                                                                                                      | _  | <b>N</b> .T |                                                | 00       |

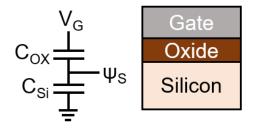

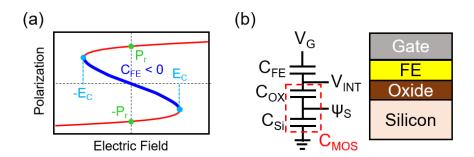

| 5.1.1 NCFET Operation       63         5.2 Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                          | Э  | _           | , 1                                            |          |

| 5.2. Compact Model       65         5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                |    | 5.1         |                                                |          |

| 5.2.1 Review       65         5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                    |    | r 0         | 1                                              |          |

| 5.2.2 Short Channel Effects       66         5.3 Polycrystallinity Variability       74         5.3.1 Simulation Methodology       74         5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                  |    | 0.2         | 1                                              |          |

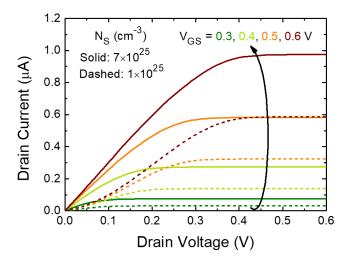

| 5.3       Polycrystallinity Variability       74         5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.1.1       STT-MTJ Operation       92         6.2       Core Model       93         6.2.1       Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2       Tunneling Magnetoresistance       95         6.2.3       Dynamic Switching Model       96         6.2.4       Model Structure and Parameter Extraction       97         6.2.5       Model Validation       98         6.3       Conclusions       100         7.1       Chapters Summary       100         7.2       Future Works       101                                                                                                                                                                                                                                                           |    |             |                                                |          |

| 5.3.1       Simulation Methodology       74         5.3.2       Results and Discussion       75         5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.1.1       STT-MTJ Operation       92         6.2       Core Model       93         6.2.1       Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2       Tunneling Magnetoresistance       95         6.2.3       Dynamic Switching Model       96         6.2.4       Model Structure and Parameter Extraction       97         6.2.5       Model Validation       98         6.3       Conclusions       99         7       Conclusions       100         7.1       Chapters Summary       100         7.2       Future Works       101                                                                                                                                                                                                                                                                               |    | <b>F</b> 0  |                                                |          |

| 5.3.2 Results and Discussion       75         5.4 Spacer Optimization       84         5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 5.3         |                                                |          |

| 5.4       Spacer Optimization       84         5.4.1       Simulation Methodology       84         5.4.2       Analysis and Discussion       85         5.5       Conclusion       90         6       Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1       Introduction       92         6.1       Introduction       92         6.1       STT-MTJ Operation       92         6.2       Core Model       93         6.2.1       Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2       Tunneling Magnetoresistance       95         6.2.3       Dynamic Switching Model       96         6.2.4       Model Structure and Parameter Extraction       97         6.2.5       Model Validation       98         6.3       Conclusion       99         7       Conclusions       100         7.1       Chapters Summary       100         7.2       Future Works       101                                                                                                                                                                                                                                                                                                                                                  |    |             | S.√                                            |          |

| 5.4.1 Simulation Methodology       84         5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | - 1         |                                                |          |

| 5.4.2 Analysis and Discussion       85         5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 5.4         | 1 1                                            |          |

| 5.5 Conclusion       90         6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |             | 0,                                             |          |

| 6 Magnetic Memory Compact Model: STT-MTJ MRAM       92         6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |             | v                                              |          |

| 6.1 Introduction       92         6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 5.5         | Conclusion                                     | 90       |

| 6.1.1 STT-MTJ Operation       92         6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6  | Mag         | gnetic Memory Compact Model: STT-MTJ MRAM      | 92       |

| 6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 6.1         | Introduction                                   | 92       |

| 6.2 Core Model       93         6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation       93         6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |             | 6.1.1 STT-MTJ Operation                        | 92       |

| 6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 6.2         |                                                | 93       |

| 6.2.2 Tunneling Magnetoresistance       95         6.2.3 Dynamic Switching Model       96         6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |             | 6.2.1 Landau-Lifshitz-Gilbert (LLG) Equation   | 93       |

| 6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |             |                                                | 95       |

| 6.2.4 Model Structure and Parameter Extraction       97         6.2.5 Model Validation       98         6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |             | 6.2.3 Dynamic Switching Model                  | 96       |

| 6.3 Conclusion       99         7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |             | 6.2.4 Model Structure and Parameter Extraction | 97       |

| 7 Conclusions       100         7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |             | 6.2.5 Model Validation                         | 98       |

| 7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.3         | Conclusion                                     | 99       |

| 7.1 Chapters Summary       100         7.2 Future Works       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7  | Con         | aclusions 1                                    | ეი       |

| 7.2 Future Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •  |             |                                                |          |

| Bibliography 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |             |                                                |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bi | blio        | graphy 1                                       | 03       |

# List of Figures

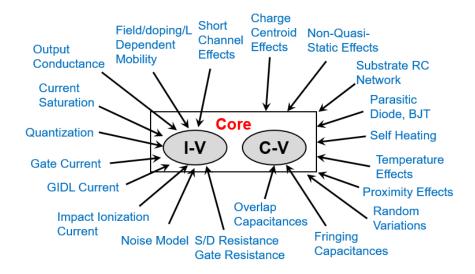

| 1.1 | Structure of BSIM compact model, including core model for current and capacitance calculations and real device (non-ideal) effects                                                                                                                                                                                                | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

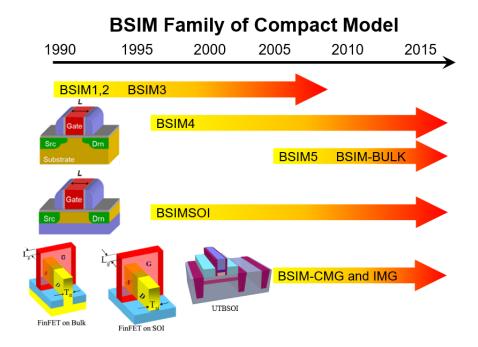

| 1.2 | Evolution and timeline of BSIM family of compact models. BSIM1,2,3,5 now are not supported by BSIM group, while BSIM4, BSIM-BULK, -SOI, -CMG, and -IMG are maintained and updated by BSIM group                                                                                                                                   | 3  |

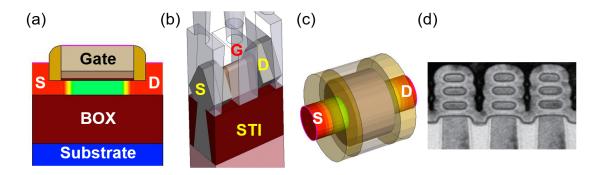

| 1.3 | Illustrations of various flavors of multi-gate transistors: (a) UTBSOI (FDSOI), (b) FinFET, (c) Gate-all-around (GAA) nanowire FET, (d) Stacked nanosheet GAA FET.                                                                                                                                                                | 4  |

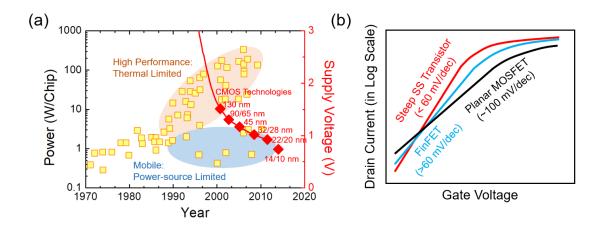

| 1.4 | (a) Power density on chip over time for high performance and mobile CPUs and supply voltage scaling for CMOS technologies. (b) Turn-on characteristics of steep SS transistor, FinFET, and planar MOSFET                                                                                                                          | 6  |

| 1.5 | (a) A typical resistance hysteresis loop of MTJ. (b) 1Transistor-1MTJ MRAM cell                                                                                                                                                                                                                                                   | 7  |

| 2.1 | $I_{DS} - V_{GS}$ characteristics of FDSOI (a) P-MOSFET and (b) N-MOSFET. The GIDL currents show back-gate dependent behaviors. The lines and symbols represent models with BSIM-IMG and measured data, respectively. The drain is biased at saturation region. Back-gate bias is from positive (left) to negative (right) values | 9  |

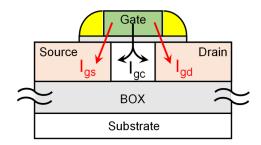

| 2.2 | Schematic of leakage current components. $I_{\rm gs}$ and $I_{\rm gd}$ are the leakage currents at the overlap region. $I_{\rm gc}$ is flowing between the gate and the channel                                                                                                                                                   | 10 |

| 2.3 | $I_{GS}-V_{GS}$ characteristics of FDSOI (a) long- and (b) short-channel N-MOSFETs. The source and drain are shorted when measuring. The ratio of long and short gate length is 100 with the same gate width                                                                                                                      | 11 |

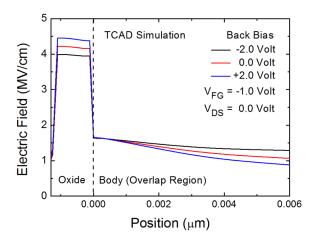

| 2.4 | Simulated electric field at $V_{GS} < 0$ with various back biases in the overlap region. The front gate oxide electric filed increases with back bias                                                                                                                                                                             | 12 |

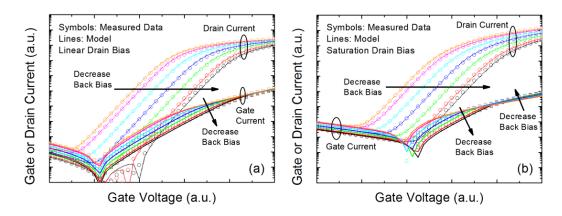

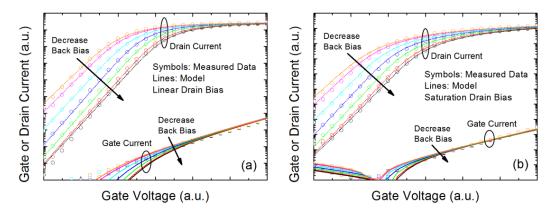

| 2.5 | Gate and drain currents versus gate voltage at various back-gate biases and at (a) linear and (b) saturation drain biases in a long-channel N-MOSFET. The back-gate bias varies from positive to negative values                                                                                                                  | 13 |

| 2.6 | Gate and drain currents versus gate voltage at various back-gate biases and at (a) linear and (b) saturation drain biases in a short-channel N-MOSFET.                                                                                                                                                                            | 10 |

| 2.7 | The back-gate bias varies from positive to negative values                                                                                                                                                                                                                                                                        | 13 |

|     | The electron distribution is uniform in short-channel device                                                                                                                                                                                                                                                                      | 14 |

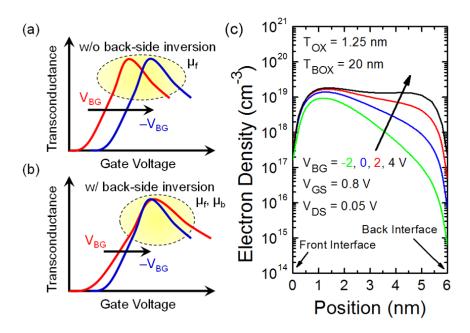

| 2.8  | (a) Typical and (b) anomalous transconductances of the FDSOI nMOSFETs. Due to the back-side inversion, both the front- and backside mobilities affect |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the transconductance behavior. (c) TCAD simulated electron density with                                                                               |    |

|      | various $V_{BG}$                                                                                                                                      | 14 |

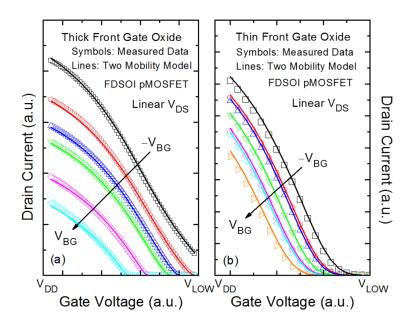

| 2.9  | $I_{DS}-V_{GS}$ curves of FDSOI pMOSFETs with (a) thick and (b) thin front-gate                                                                       |    |

|      | oxides at linear drain bias region. The same BOX and body thicknesses are                                                                             |    |

|      | used in both devices. The back-gate bias is applied from negative to positive.                                                                        | 15 |

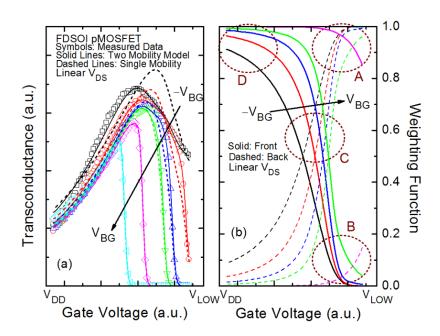

| 2.10 | (a) Transconductance and (b) extracted weighting function of an FDSOI                                                                                 |    |

|      | pMOSFET with thick front-gate oxide at linear drain bias region. The back-                                                                            |    |

|      | gate bias is applied from negative to positive                                                                                                        | 16 |

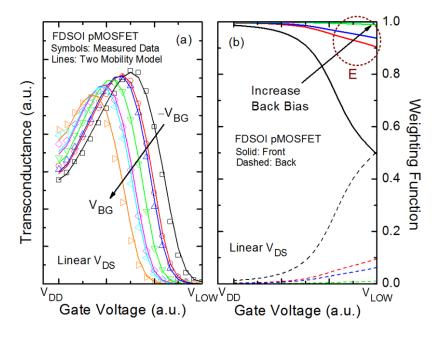

| 2.11 | (a) Transconductance and (b) extracted weighting function of an FDSOI                                                                                 |    |

|      | pMOSFET with thin front-gate oxide at linear drain bias region. The back-                                                                             |    |

|      | gate bias is applied from negative to positive                                                                                                        | 16 |

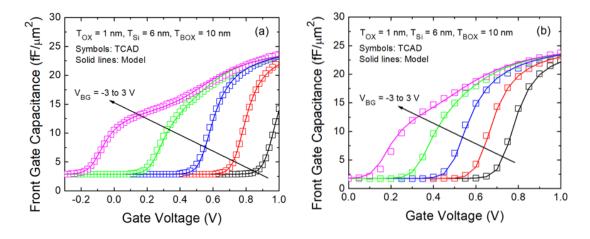

| 2.12 | The TCAD simulated front-gate capacitances with the BOX thicknesses of                                                                                |    |

|      | (a) 10 and (b) 20 nm. The core model for the charges and surface potentials                                                                           |    |

|      | accurately captures the back-side inversion effect                                                                                                    | 18 |

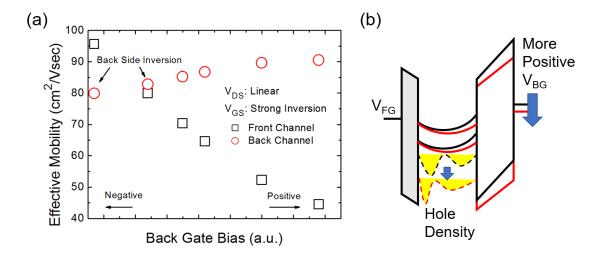

| 2.13 | (a) Extracted effective mobility of the front and back channels from Fig. 2.9                                                                         |    |

|      | (a). The back-side inversion occurs when the back-gate bias is negative in                                                                            |    |

|      | FDSOI pMOSFET. (b) Illustration of hole density distribution due to applied                                                                           |    |

|      | $V_{BG}$                                                                                                                                              | 19 |

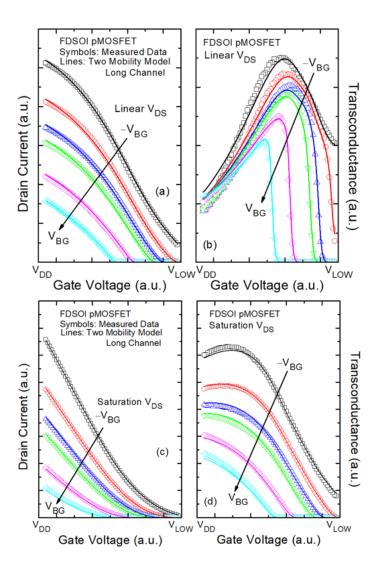

| 2.14 | $I_{DS} - V_{GS}$ at (a) linear and (c) saturation drain biases, and transconduc-                                                                     |    |

|      | tance at (b) linear and (d) saturation drain biases of a long channel FDSOI                                                                           |    |

|      | pMOSFET with the same body and BOX thicknesses as the device shown in                                                                                 | 20 |

| 0.15 | Fig. 2.10                                                                                                                                             | 20 |

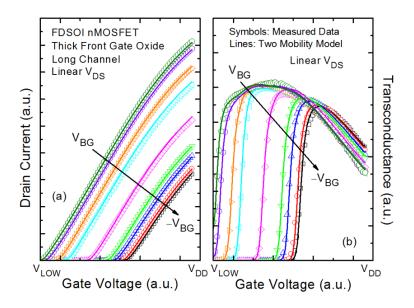

| 2.15 | (a) $I_{DS} - V_{GS}$ and (b) transconductance of a long-channel FDSOI nMOSFET                                                                        |    |

|      | with thick front-gate oxide and similar device structure as the pMOSFET shown in Fig. 2.14                                                            | 21 |

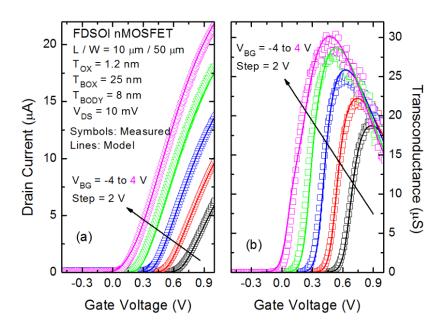

| 2 16 | (a) $I_{DS} - V_{GS}$ and (b) transconductance of an FDSOI nMOSFET with $L = 10$                                                                      | 21 |

| 2.10 | $\mu$ m, $W = 50 \ \mu$ m, $T_{OX} = 1.2 \ \text{nm}$ , $T_{BOX} = 25 \ \text{nm}$ , and $T_{BODY} = 8 \ \text{nm}$ .                                 |    |

|      | Measurement data are from the LETI device                                                                                                             | 22 |

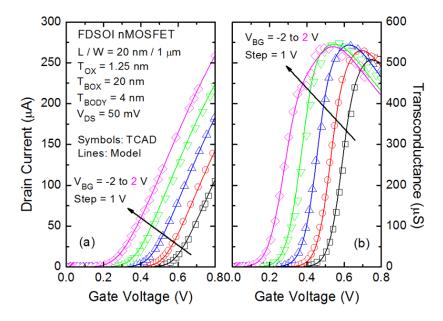

| 2 17 | TCAD simulated (a) $I_{DS} - V_{GS}$ and (b) transconductance of an FDSOI                                                                             |    |

| 2.11 | nMOSFET with $L=20$ nm, $W=1$ $\mu\text{m}$ , $T_{\text{OX}}=1.25$ nm, $T_{\text{BOX}}=20$ nm,                                                        |    |

|      | and $T_{\text{BODY}} = 4 \text{ nm}$ at various $V_{BG}$                                                                                              | 22 |

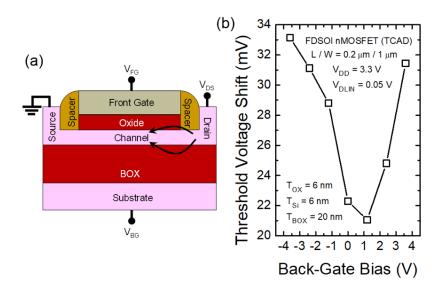

| 2.18 | (a) TCAD simulated structure of a FDSOI MOSFET with thick front gate                                                                                  |    |

|      | oxide. The arrows represent the fringing fields through the BOX and front                                                                             |    |

|      | gate oxide. (b) The threshold voltage shift versus back-gate bias plot                                                                                | 23 |

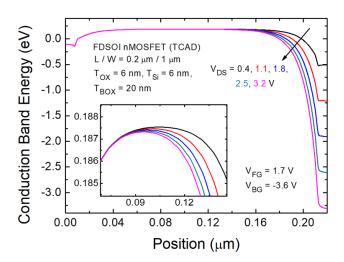

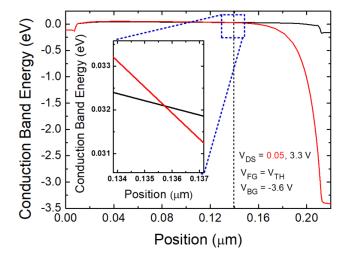

| 2.19 | Simulated conduction band energy profile along source-channel-drain direc-                                                                            |    |

|      | tion, which is cut at 0.5 nm below the front surface. The front gate is biased                                                                        |    |

|      | at $\approx 0.25V$ below the threshold voltage. The inset shows barrier height                                                                        |    |

|      | difference for various $V_{DS}$ is less than $1meV$                                                                                                   | 24 |

| 2.20 | Simulated conduction band energy profile in linear and saturation drain bias                                                                          |    |

|      | regions at threshold voltage, where is at the maximum current flowing path                                                                            |    |

|      | along the channel. The dashed line is the boundary of the $\Delta L$ . The inset                                                                      |    |

|      | shows the crossing of the conduction band. The device dimensions are the                                                                              |    |

|      | same as shown in Fig. 2.19                                                                                                                            | 24 |

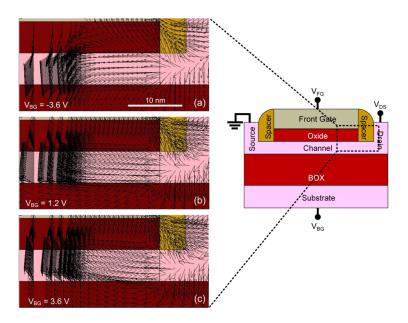

| 2.21 | Electric field lines at $V_{DS} = 3.3V$ , $V_{FG} = V_{TH}$ , and $V_{BG} = (a) -3.6$ , (b) 1.2,                                                      |    |

|      | and (c) 3.6V. The device dimensions are the same as shown in Fig. 2.19                                                                                | 25 |

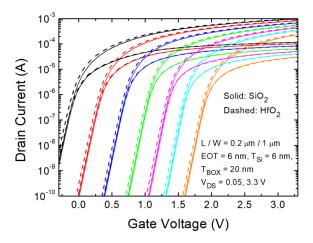

| 2.22 | $I_{DS} - V_{FG}$ characteristics of the devices with SiO <sub>2</sub> and HfO <sub>2</sub> as the front gate oxide of EOT = 6 nm. The $V_{BG}$ is biased from $-3.6V$ (right) to $3.6V$ (left) with the step of $1.2V$                                                                                                                                                                                                      | 26 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

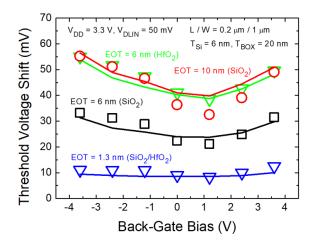

| 2.23 | Threshold voltage shift of the devices with various front gate oxide configurations. [Symbols: extracted from TCAD; lines: calculated from $(2.14)$ ]                                                                                                                                                                                                                                                                        | 27 |

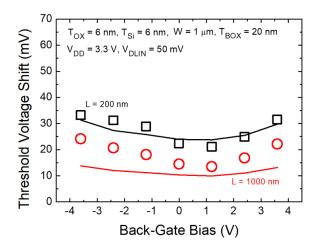

| 2.24 | Threshold voltage shift of the devices with $L=200$ and 1000 nm. The front gate oxide is 6 nm $SiO_2$                                                                                                                                                                                                                                                                                                                        | 27 |

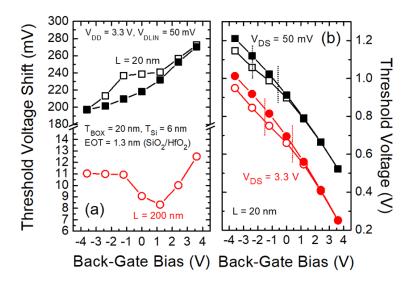

| 2.25 | (a) Threshold voltage shift of devices with EOT of 1.3 nm and $L=20$ and 200 nm. (b) Threshold voltage of $L=20$ nm device at $V_{DS}=50mV$ and 3.3 $V$ . The dashed lines represent the regions where the substrate depletion happens in moderately doped substrate. (Solid symbols: heavily doped substrate $6.5\times10^{18}~{\rm cm}^{-3}$ ; Open symbols: moderately doped substrate $6.5\times10^{17}~{\rm cm}^{-3}$ ) | 28 |

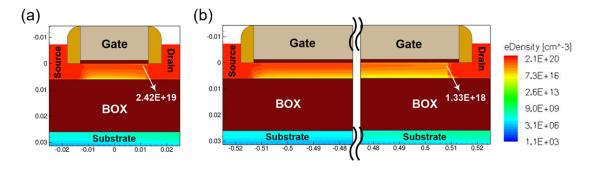

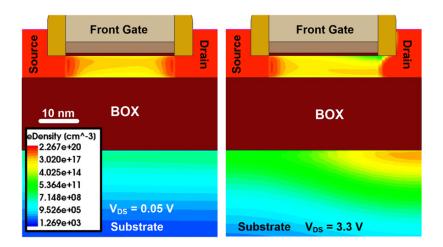

| 2.26 | Electron density distribution for $L=20$ nm with EOT = 1.3 nm device. The back-gate bias for both cases is $-1.2V$ . At $V_{DS}=3.3V$ , the region under the drain is inverted and affects the center of channel, suggesting that the substrate depletion happens at more positive $V_{BG}$ compared to that at $V_{DS}=50mV$                                                                                                | 29 |

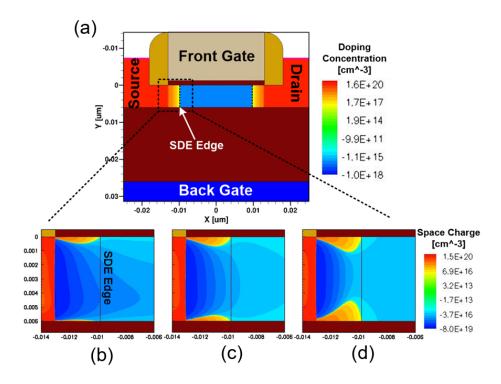

| 2.27 | (a) Doping concentration profile in the simulated FDSOI MOSFET with front and back gate oxide thicknesses of 1.25 and 20 nm, respectively. The space charges in the source/drain extension (SDE) regions at (b) $V_{BG} = 2V$ , (c) $V_{BG} = 0V$ , and (d) $V_{BG} = -2V$ , are with $V_{FG} = -0.1V$ (OFF state) and $V_{DS} = 0V$                                                                                         | 30 |

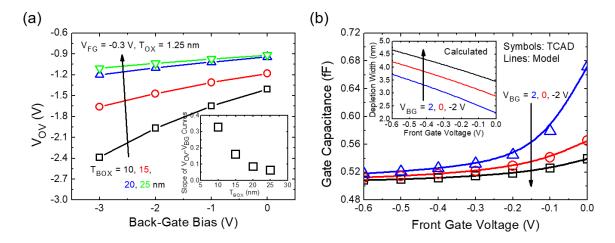

| 2.28 | (a) Extracted $V_{OV}$ with various $T_{\rm BOX}$ from the simulated capacitances. The inset shows the slope of $V_{OV}-V_{BG}$ curves. (b) Comparison of TCAD data (symbols) and BSIM-IMG model (lines) with equation (2.16). The inset shows the calculated depletion width                                                                                                                                                | 31 |

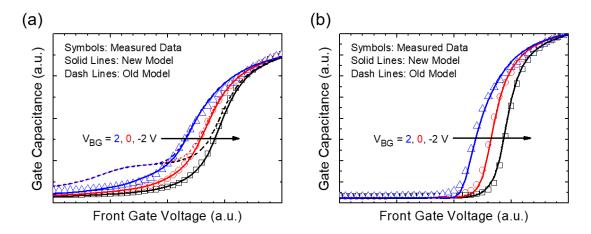

| 2.29 | Comparison of measured data and BSIM-IMG model for FDSOI MOSFETs with (a) short and (b) long channels. The solid and dash lines are for new and old models. There is no $V_{BG}$ -dependency in gate capacitance in the old model                                                                                                                                                                                            | 32 |

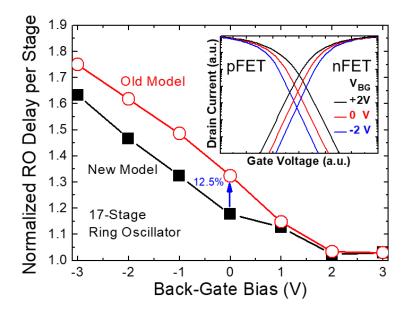

| 2.30 | Delays per stage of an 17-stage ring oscillator (RO) at various back gate biases with new and old back gate bias-dependent overlap capacitance. The CMOS inverter consists of the short channel FDSOI MOSFETs with the same parameters used Fig. 2.29 (a)                                                                                                                                                                    | 33 |

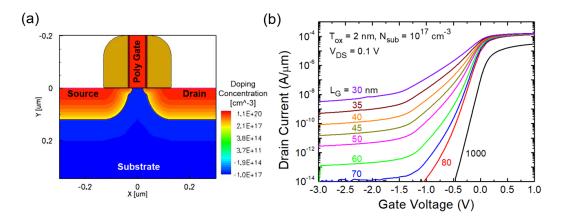

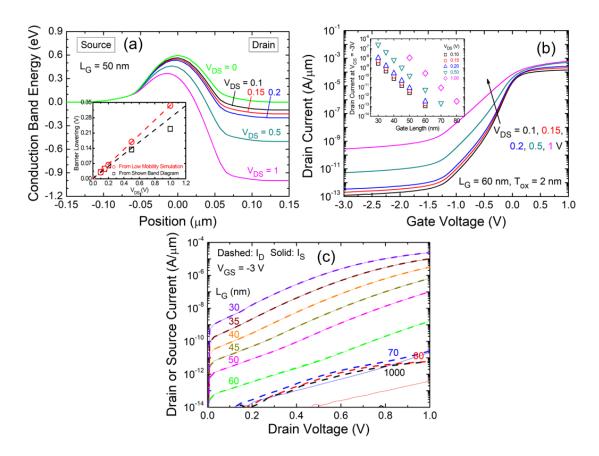

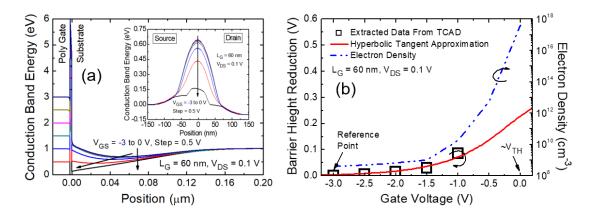

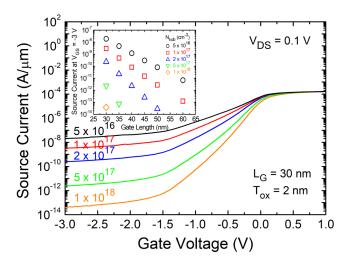

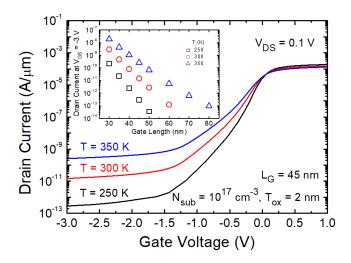

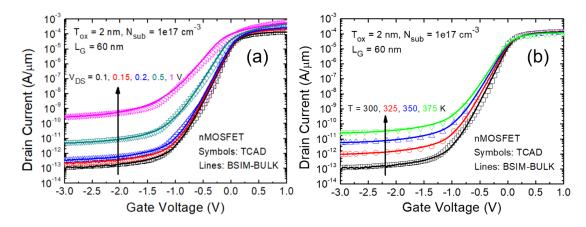

| 3.1  | (a) Simulated structure of nMOSFET with doping concentration. (b) Simulated $I_{DS}-V_{GS}$ curves for different values of $L_G$ at $V_{DS}=0.1V$ and $V_S=V_B=0V$ . It shows that the subsurface leakage current at the accumulation bias region increases as the value of $L_G$ reduces                                                                                                                                    | 36 |

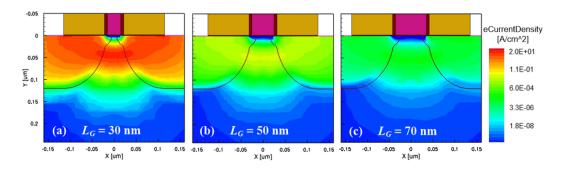

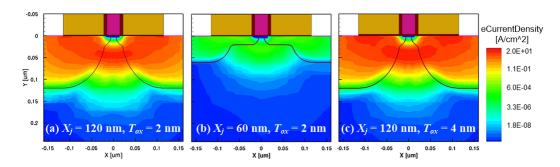

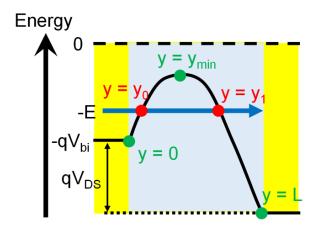

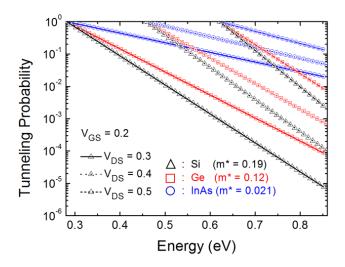

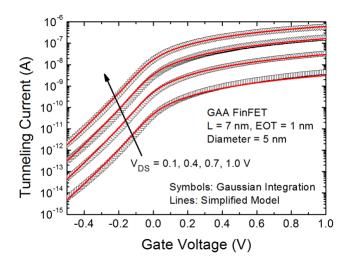

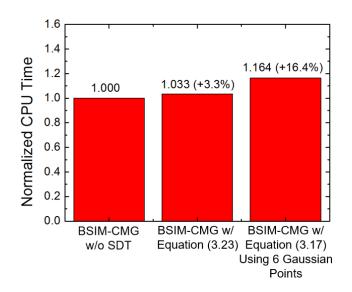

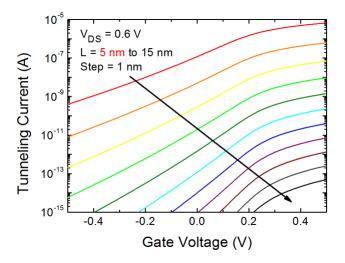

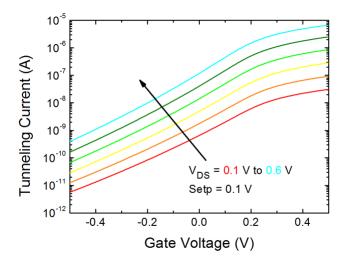

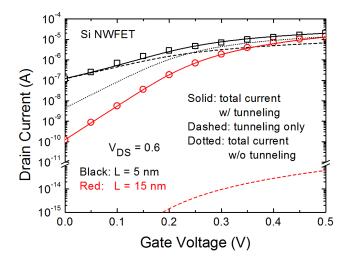

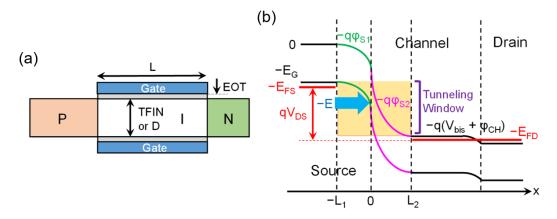

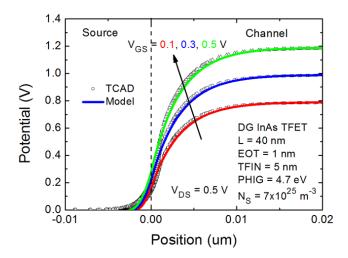

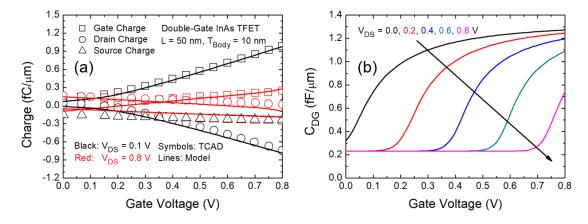

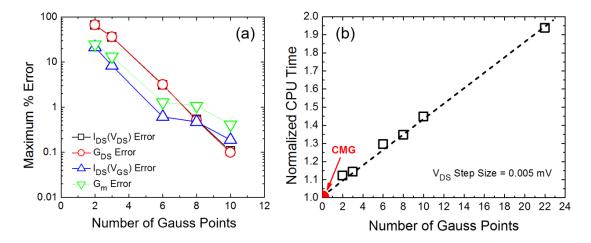

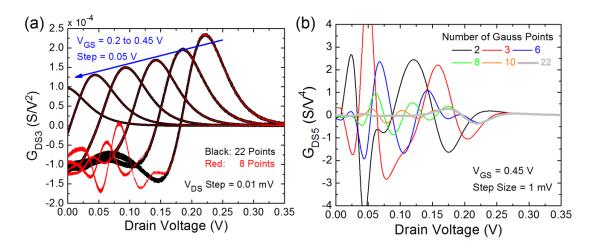

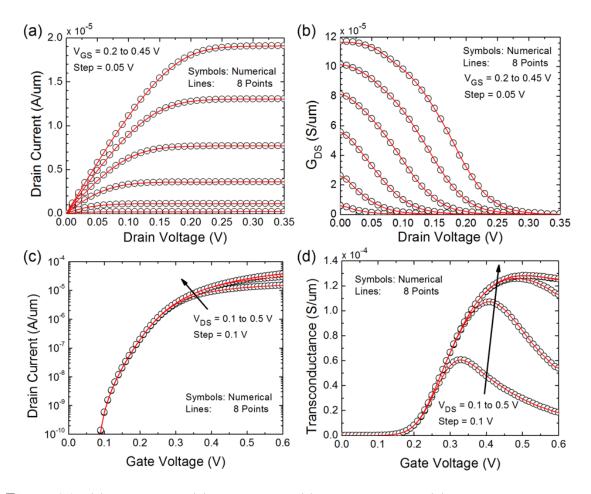

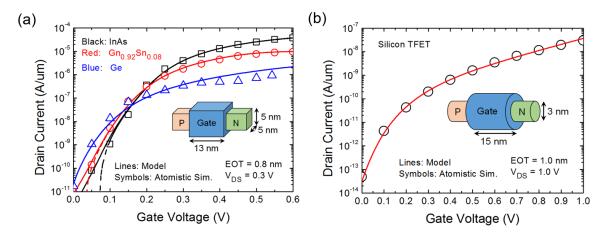

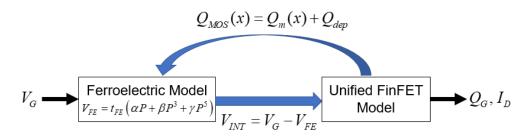

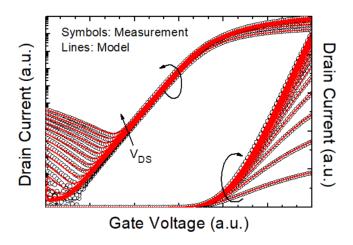

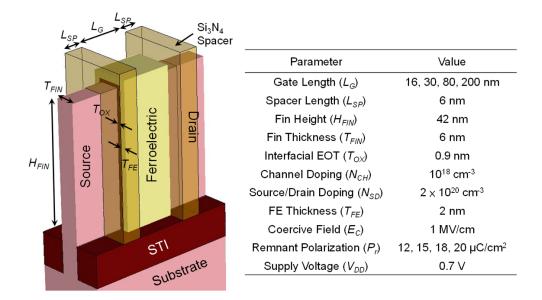

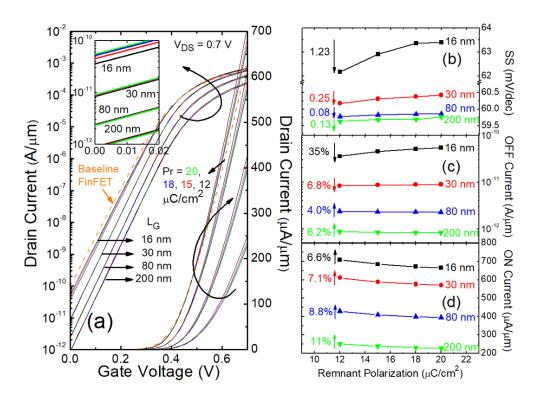

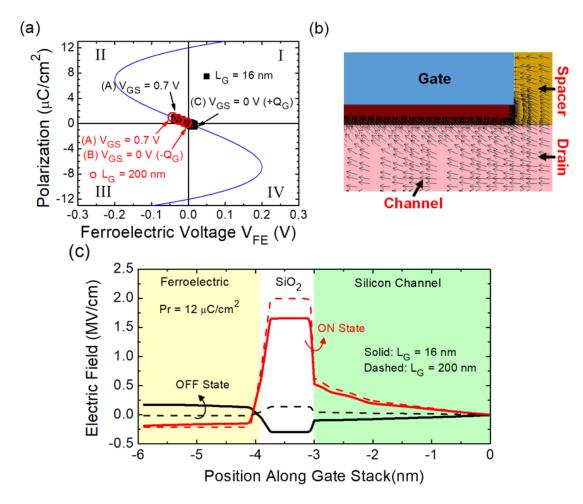

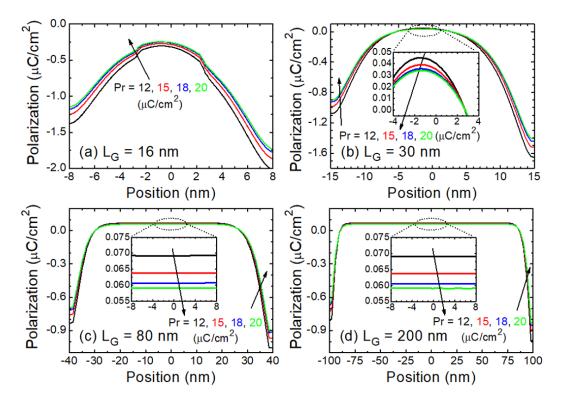

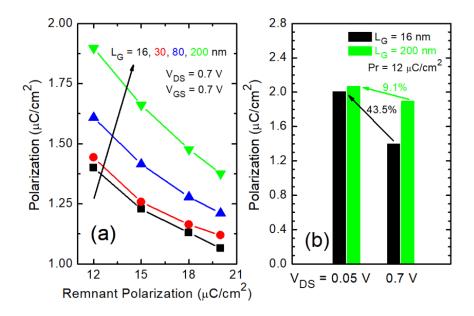

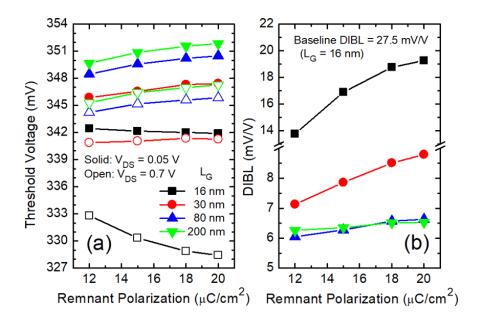

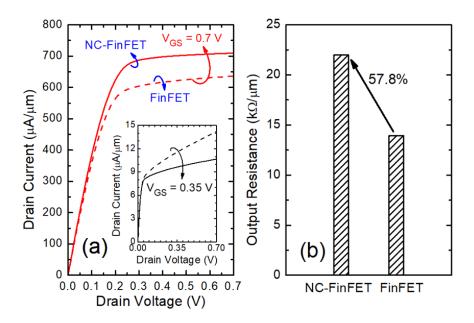

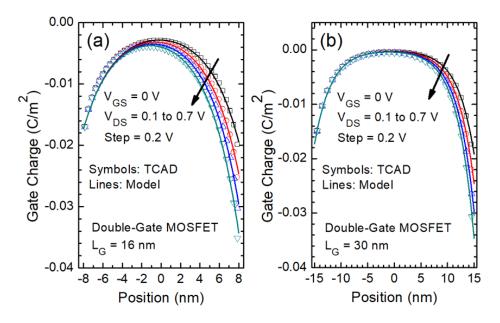

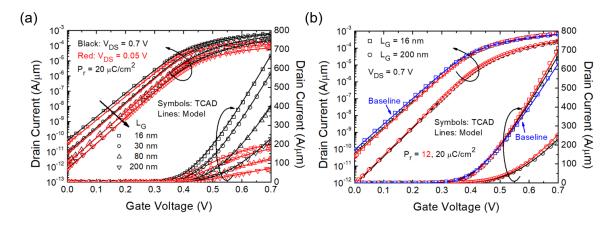

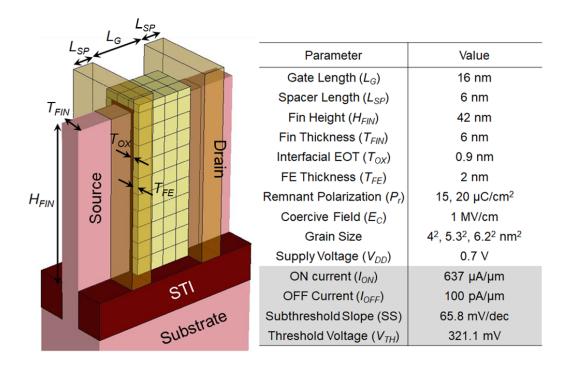

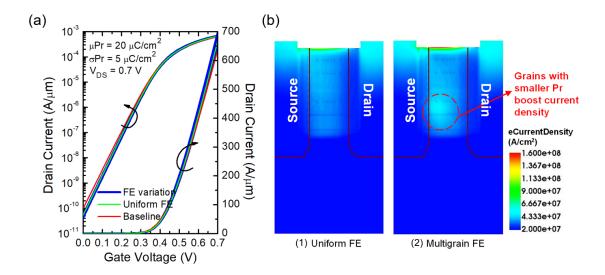

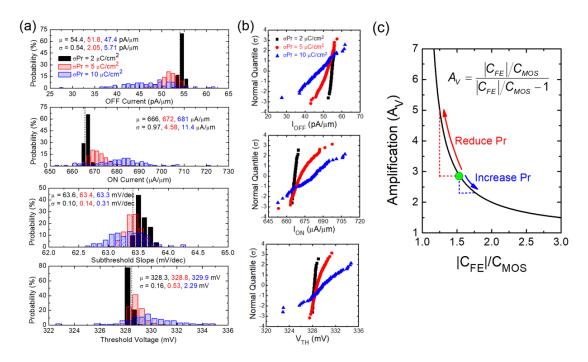

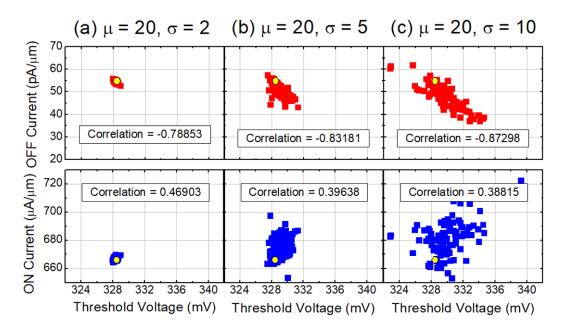

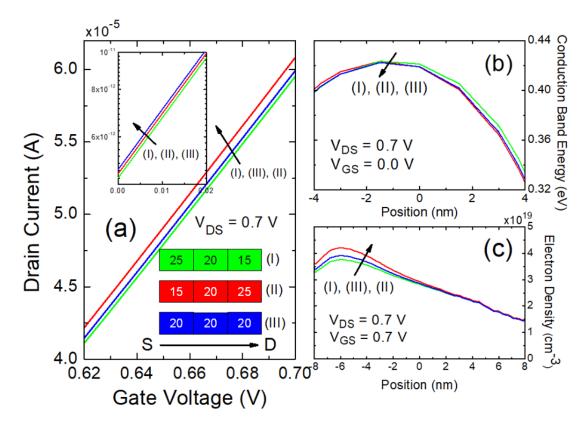

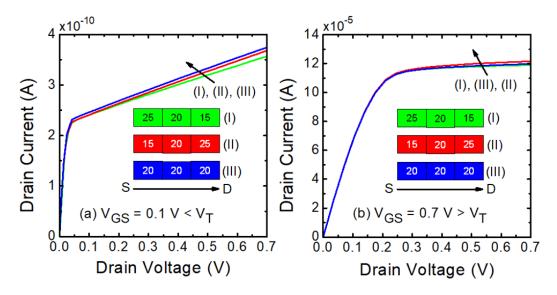

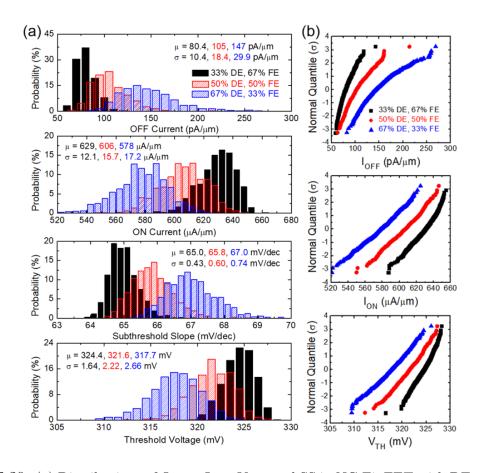

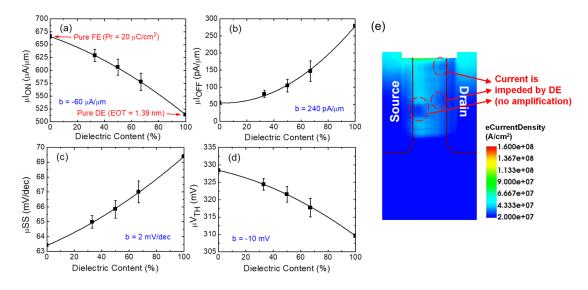

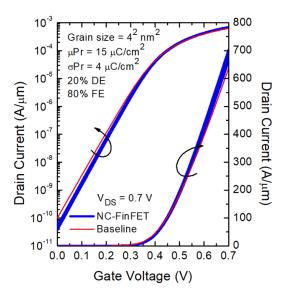

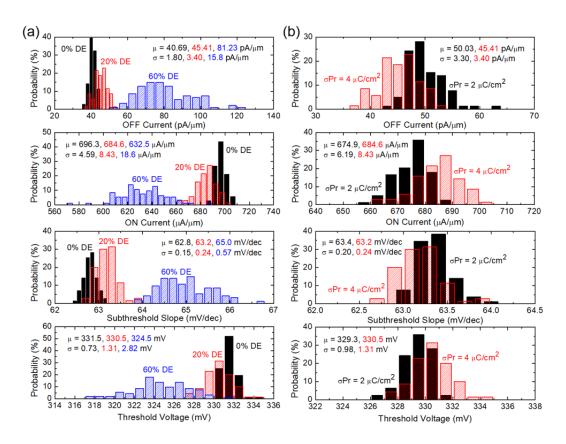

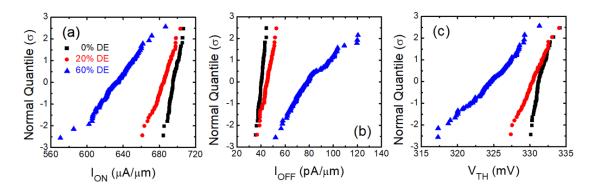

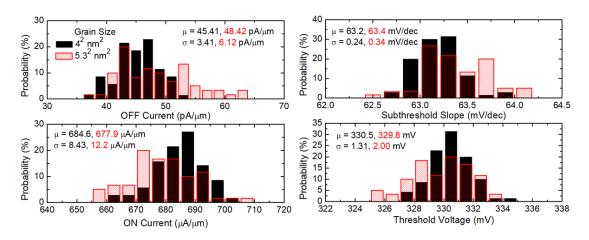

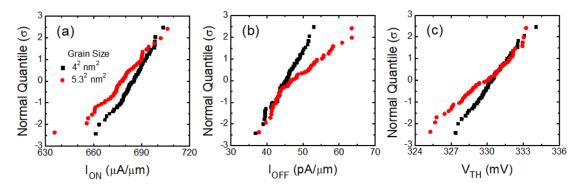

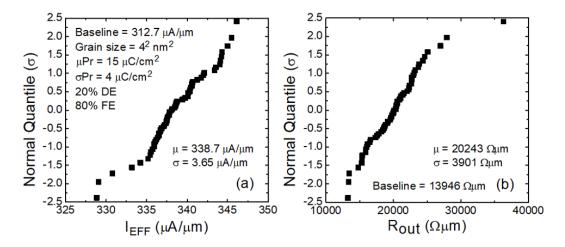

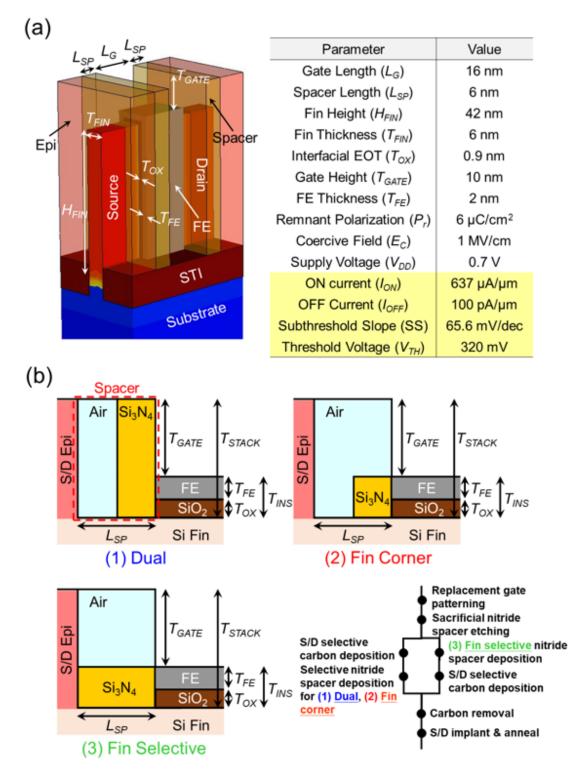

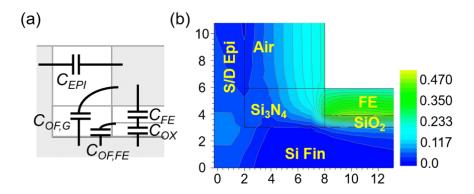

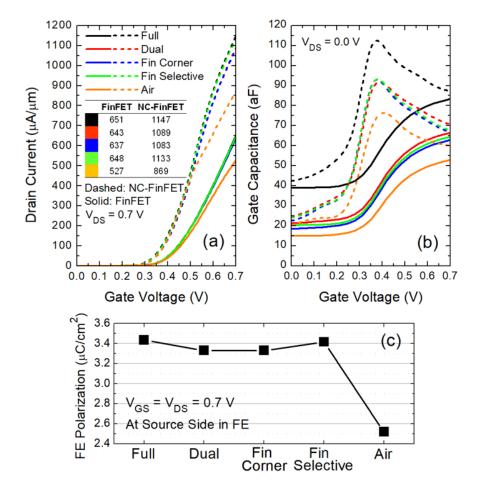

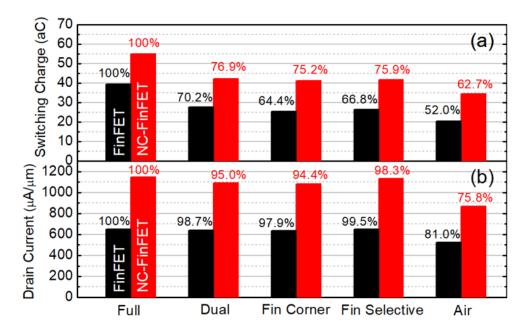

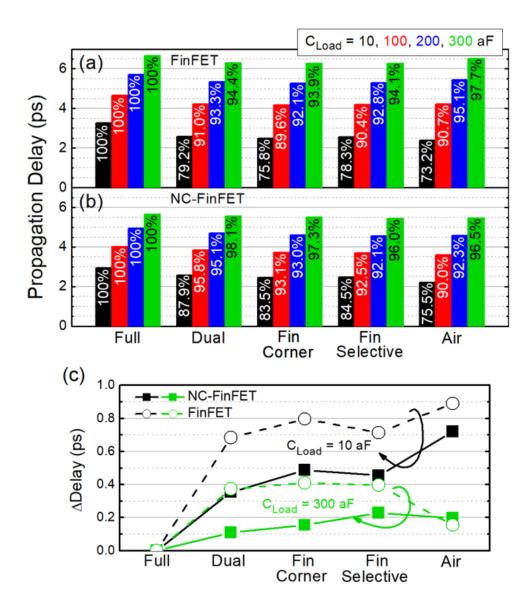

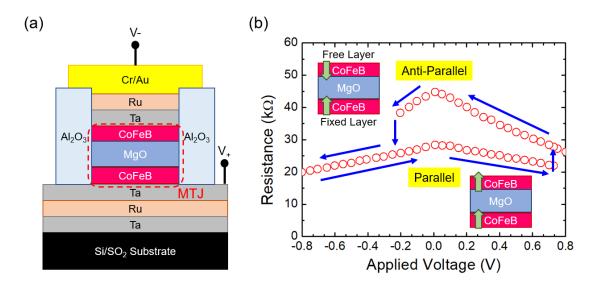

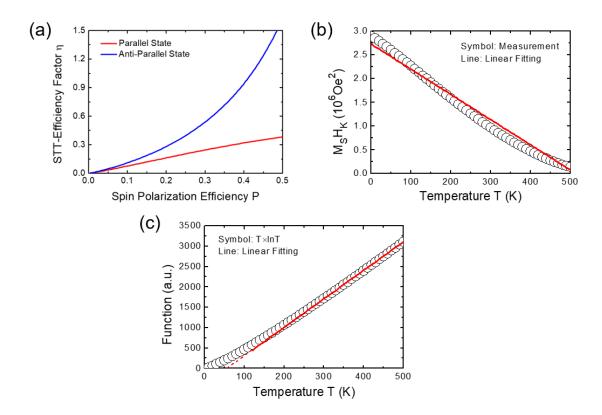

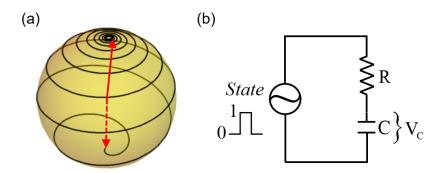

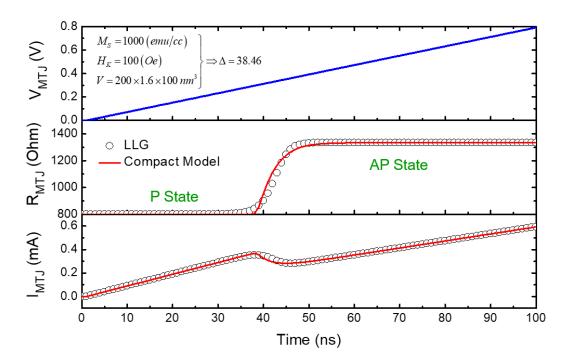

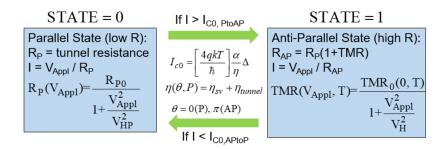

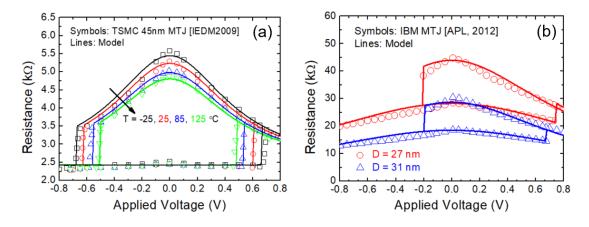

| 3.2  | Contour plots of the electron current density for nMOSFET with the gate length of (a) 30, (b) 50, and (c) 70 nm at $V_{GS} = -3V$ , $V_{DS} = 0.1V$ , and $V_S = V_B = 0V$ . The junction depths of source/drain and their extensions are 120 and 20 nm, respectively                                                                                                                                                        | 37 |