# **UCLA**

# **UCLA Previously Published Works**

#### **Title**

ENDURANCE CHARACTERIZATION AND IMPROVEMENT OF FLOATING GATE SEMICONDUCTOR MEMORY DEVICES

#### **Permalink**

https://escholarship.org/uc/item/5jx528v0

#### **Author**

Khan, Faraz

#### **Publication Date**

2009-05-01

Peer reviewed

### © 2009

## **FARAZ KHAN**

### ALL RIGHTS RESERVED

"All our knowledge has its origin in our perceptions."

- Leonardo da Vinci

# ENDURANCE CHARACTERIZATION AND IMPROVEMENT OF FLOATING GATE SEMICONDUCTOR MEMORY DEVICES

$\mathbf{BY}$

#### **FARAZ KHAN**

A thesis submitted to the

Graduate School – New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in

**Electrical and Computer Engineering**

written under the direction of

**Professor Kuang Sheng**

and approved by

New Brunswick, New Jersey

May, 2009

#### **ABSTRACT OF THE THESIS**

# ENDURANCE CHARACTERIZATION AND IMPROVEMENT OF FLOATING GATE SEMICONDUCTOR MEMORY DEVICES

#### **By FARAZ KHAN**

#### **Thesis Director:**

#### **Professor Kuang Sheng**

Low power consumption, virtually zero latency, extremely fast boot-up for OS and applications, fast data access, portability, and high shock resistance are some of many reasons that make Flash memory devices an ideal choice for a vast variety of consumer electronics. Flash memory is a specific type of non-volatile EEPROM. A typical Flash memory cell looks similar to a MOSFET, except that it has a dual-gate structure. Flash memory cells use the principle of threshold voltage modulation to alter the channel current ( $I_{ds}$ ) when a reference read voltage ( $V_{read}$ ) is applied to the control gate. Different levels of  $I_{ds}$  are, in turn, interpreted as unique logic states. Fowler-Nordheim tunneling is used to achieve threshold voltage modulation in NAND Flash memory cells.

Despite its high performance potential, NAND Flash memory suffers from the drawback of limited program/erase endurance. High field/current stress caused by Fowler-Nordheim tunneling (during program/erase cycling) leads to tunnel oxide degradation, which eventually limits the endurance characteristics of NAND Flash

memory cells. One of the most significant tunnel oxide degradation mechanisms is charge trapping. This work is devoted to the study of charge trapping and its effects on the endurance characteristics and reliability of NAND Flash memory devices. Cell threshold voltage shift and memory window narrowing, a direct consequence of tunnel oxide degradation caused by charge trapping, are typical failure modes in NAND Flash memory cells.

In this work, endurance characterization of NAND Flash memory devices and a detailed analysis has been conducted reconfirming the issue of limited program/erase endurance. Subsequently, a novel NAND Flash memory cell design has been proposed which eliminates tunnel oxide degradation caused by Fowler-Nordheim tunneling. Device simulations (using the Sentaurus TCAD tool suite by Synopsys®, Inc.) and corresponding analysis show that, as compared to conventional cells, the proposed cell design offers a 10 times reduction in intrinsic threshold voltage shift. That, according to the measured endurance characteristics of cells fabricated in this work, translates to an improvement of over 200 times in program/erase endurance. In a nutshell, the proposed cell design offers superior reliability and endurance as compared to conventional NAND Flash memory cells.

<sup>\*</sup> All work in this thesis is copyrighted.

# **DEDICATION**

This work is dedicated to my mother and father, with love and thanks for all they have done for me.

#### **ACKNOWLEDGEMENTS**

I take this opportunity to express my sincere gratitude to Professor Kuang Sheng for his invaluable guidance throughout my research work. His active interest and encouragement have been the driving force for the successful completion of my research and thesis.

I am very thankful to Professor Yicheng Lu and Professor Wei Jiang for taking time out of their busy schedules to do a critical review of this thesis and serve as my committee members.

I am deeply grateful to Dr. Behnam Moradi (Quality and Reliability Assurance Lead Engineer-Micron Technology, Inc.) for his guidance and counsel through out my research work. He always shared his unparalleled technical knowledge and offered his expertise and experience to help me out. I thank him for always being very patient and taking time out for mentoring me despite his very busy schedule.

I am very thankful to my manager Mr. Roger Faul (Yield Enhancement/Real Time Defect Analysis Manager-Micron Technology, Inc.) for extending his help and support whenever I needed it. He always encouraged me at every step of the way and gave me invaluable advice. I am thankful to him for always sharing his inestimable technical expertise throughout the course of my research work.

I would like to extend my gratitude to Mr. Rahil Hasan (Product Integration Engineering Manager-Micron Technology, Inc.) who always encouraged me and provided constructive advice. I am grateful to him for providing me with the necessary

resources, without which it would have not been possible to successfully conduct this research work.

I am grateful to Dr. Haitao Liu (Device Engineer-Micron Technology, Inc.) for sharing his technical expertise in TCAD device design and helping me with device simulation issues.

I wish to express my appreciation for Dr. Mehdi Mansouri (Process Instructor/Trainer-Micron Technology, Inc.) for always taking time out to answer my questions and offering his extensive technical knowledge.

I am tempted to thank all my friends individually for always being there for me but from fear of leaving someone out, I will simply say *thank you* to all of them. However, I would like to especially thank my friend Dr. Gaurav Saraf for guiding me throughout this research.

Finally, and most importantly, I express my deep sense of gratitude and thankfulness to my parents, brother, and sister. This work would not have been possible without their irreplaceable love, patience, encouragement, and moral support.

# TABLE OF CONTENTS

| Abstractii                                                           |

|----------------------------------------------------------------------|

| Dedicationiv                                                         |

| Acknowledgementsv                                                    |

| Table of Contentsvii                                                 |

| List of Tablesix                                                     |

| List of Illustrationsx                                               |

| Chapter 1: Introduction1                                             |

| 1.1 Motivation1                                                      |

| 1.2 Objective3                                                       |

| 1.3 Thesis Organization4                                             |

| Chapter 2: Technical Background5                                     |

| 2.1 NOR Flash vs. NAND Flash6                                        |

| 2.2 Cell Structure of the NAND Flash Memory cell                     |

| 2.3 Principles of Operation of the NAND Flash Memory Cell            |

| 2.4 Electrical Conduction Through Thin Dielectrics39                 |

| 2.4.1 Fowler-Nordheim Tunneling40                                    |

| Chapter 3: Reliability Issues in NAND Flash Memory47                 |

| 3.1 Tunnel Oxide Degradation caused by Fowler-Nordheim Tunneling48   |

| 3.1.1 Charge Trapping in Tunnel Oxide49                              |

| 3.2 Reliability Concerns caused by Charge Trapping in Tunnel Oxide57 |

| 3.3 Some Prior Work for Improving Charge Trapping in Tunnel Oxide66  |

| Chapter 4: Characterization and Improvement of Flash Memory Endurance | .69 |

|-----------------------------------------------------------------------|-----|

| 4.1 Endurance Characterization of MLC NAND Flash Memory Cells         | .69 |

| 4.1.1 Endurance Characterization using Fixed Program/Era              | ase |

| Conditions                                                            | .69 |

| 4.1.2 Endurance Characterization using Program/Erase Ver              | ify |

| Schemes                                                               | .74 |

| 4.2 A Novel Method for Endurance Improvement                          | .78 |

| 4.2.1 Simulation Software - Background Information                    | .82 |

| 4.2.2 Device Simulations                                              | .91 |

| 4.2.3 Design Challenges                                               | .97 |

| 4.2.4 Potential Concerns and Corresponding Solutions                  | 106 |

| Chapter 5: Conclusions and Suggestions for Future Work                | 111 |

| References                                                            | 113 |

# LIST OF TABLES

| Table 1.1 | Comparison of average specifications between HDDs, SSDs, and       |     |

|-----------|--------------------------------------------------------------------|-----|

|           | HHDs                                                               | 2   |

| Table 2.1 | A comparison of basic advantages, disadvantages and applications   |     |

|           | of NAND vs. NOR Flash memories                                     | 9   |

| Table 2.2 | Basic advantages of SLC vs. MLC Flash devices                      | 17  |

| Table 2.3 | Relative cell conditions of programmed vs. erased cells in an SLC  |     |

|           | device                                                             | 35  |

| Table 4.1 | Comparison of operation conditions between the conventional and    |     |

|           | proposed NAND Flash memory cell                                    | 81  |

| Table 4.2 | Comparison of $V_T$ shift between conventional and proposed cell   | 96  |

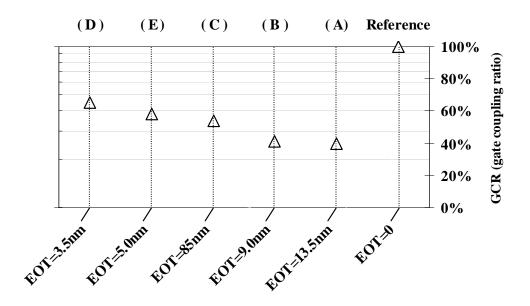

| Table 4.3 | GCRs achieved using IPD films with various dielectric              |     |

|           | constants                                                          | 102 |

| Table 4.4 | Relative dielectric constants and corresponding breakdown electric |     |

|           | fields of several typical dielectric materials                     | 105 |

# LIST OF ILLUSTRATIONS

| Figure 2.1  | Volatile vs. Non-volatile semiconductor memory                       | 5  |

|-------------|----------------------------------------------------------------------|----|

| Figure 2.2  | NAND vs. NOR Flash                                                   | 6  |

| Figure 2.3  | (a) Programming of a NOR Flash memory cell (CHE Injection),          |    |

|             | and (b) Erasing of a NOR Flash memory cell (FN Tunneling)            | 7  |

| Figure 2.4  | Basic structure of a NAND Flash memory cell                          | 10 |

| Figure 2.5  | 3D view of a typical NAND Flash memory cell                          | 11 |

| Figure 2.6  | Scanning electron microscope (SEM) cross-sections of typical         |    |

|             | SLC NAND Flash memory cells                                          | 12 |

| Figure 2.7  | Gate stack of the Flash Memory cell can be replaced by               |    |

|             | capacitors in series to understand the effect of capacitive          |    |

|             | coupling                                                             | 13 |

| Figure 2.8  | Schematic view of a conventional NAND Flash memory array             |    |

|             | structure                                                            | 13 |

| Figure 2.9  | 3D view of a conventional NAND Flash memory array                    | 14 |

| Figure 2.10 | Threshold voltage modulation                                         | 15 |

| Figure 2.11 | $V_T$ distributions of programmed ("0") vs. erased ("1") cells in an |    |

|             | array                                                                | 15 |

| Figure 2.12 | $V_T$ distributions in MLC devices                                   | 16 |

| Figure 2.13 | The erased Flash memory cell turns "on" when $V_{\it read}$ is       |    |

|             | applied                                                              | 20 |

| Figure 2.14 | The programmed Flash memory cell is "off" when $V_{read}$ is         |    |

|-------------|----------------------------------------------------------------------|----|

|             | applied                                                              | 21 |

| Figure 2.15 | Distributions of acceptable ranges for the $V_T$ 's of programmed    |    |

|             | ("0") and erased ("1") cells                                         | 21 |

| Figure 2.16 | Energy band diagram of an erased (left) and a programmed             |    |

|             | (right) Flash memory cell                                            | 23 |

| Figure 2.17 | Voltage conditions during programming a NAND Flash memory            |    |

|             | cell                                                                 | 24 |

| Figure 2.18 | Cell conditions after (a) step 1 of the boosting process, (b) step 2 |    |

|             | of the boosting process, (c) step 3 of the boosting                  |    |

|             | process                                                              | 27 |

| Figure 2.19 | Final cell conditions at the end of the boosting process             | 28 |

| Figure 2.20 | Cross-section view and respective voltage conditions within the      |    |

|             | selected string                                                      | 29 |

| Figure 2.21 | Cross-section view and respective voltage conditions within a        |    |

|             | program inhibited string                                             | 29 |

| Figure 2.22 | A timeline of the boosting process                                   | 30 |

| Figure 2.23 | Voltage conditions during erasing a NAND Flash memory                |    |

|             | cell                                                                 | 32 |

| Figure 2.24 | Cross-section view and respective voltage conditions of a string     |    |

|             | that has been selected for erase                                     | 33 |

| Figure 2.25 | Voltage conditions of an erase inhibited string                      | 34 |

| Figure 2.26 | $V_T$ distribution of programmed vs. erased cells relative to             |    |

|-------------|---------------------------------------------------------------------------|----|

|             | $V_{ev}$ , $V_{read}$ , $V_{pv}$ , and $V_{pass}$                         | 35 |

| Figure 2.27 | Capacitive components of a generic floating gate device                   | 36 |

| Figure 2.28 | Energy band diagram for the $Si - SiO_2$ interface                        | 40 |

| Figure 2.29 | Energy band representation of Fowler-Nordheim tunneling                   |    |

|             | through thin oxides                                                       | 41 |

| Figure 2.30 | Fowler-Nordheim tunneling I-V characteristics                             | 43 |

| Figure 2.31 | Energy band representation of Fowler-Nordheim tunneling (a) at            |    |

|             | zero bias, (b) from substrate to floating gate (Program                   |    |

|             | Operation), and (c) from floating gate to substrate (Erase                |    |

|             | Operation)                                                                | 44 |

| Figure 3.1  | Electron trap density as a function of Hydrogen concentration in          |    |

|             | the oxide                                                                 | 51 |

| Figure 3.2  | (a) C-V and (b) I-V measurements before and after the                     |    |

|             | Polysilicon-SiO <sub>2</sub> -Si capacitors were stressed for a short     |    |

|             | time                                                                      | 52 |

| Figure 3.3  | Positive charge concentration plotted against various stress fields       |    |

|             | for different oxide thicknesses                                           | 53 |

| Figure 3.4  | Positive and negative I-V curves taken before and after the               |    |

|             | Polysilicon-SiO <sub>2</sub> -Si capacitors were stressed for a prolonged |    |

|             | period of time (10 minutes)                                               | 55 |

| Figure 3.5  | Leakage current changes in a constant current stressing test of       |

|-------------|-----------------------------------------------------------------------|

|             | SiO <sub>2</sub>                                                      |

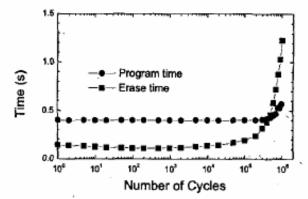

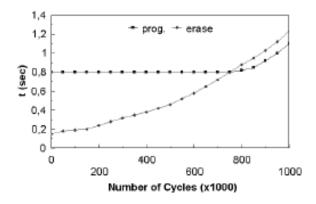

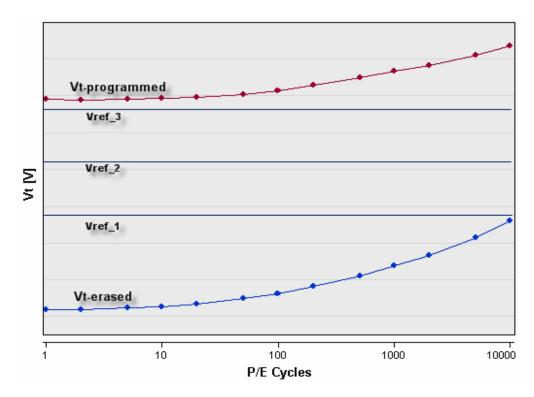

| Figure 3.6  | SLC Flash memory cell endurance characteristics                       |

| Figure 3.7  | Programmed and erased $V_T$ as a function of the number of            |

|             | cycles for a cell under fixed program and erase conditions            |

| Figure 3.8  | Program and erase times increasing as a function of number of         |

|             | program/erase cycles in NOR Flash memory cells                        |

| Figure 3.9  | Program and erase times increasing as a function of the number        |

|             | of cycles                                                             |

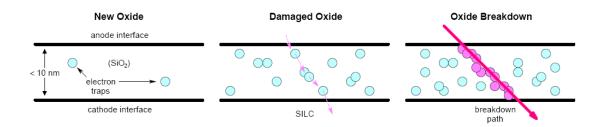

| Figure 3.10 | A percolation model for stress-induced leakage current (SILC)         |

|             | and eventual oxide breakdown                                          |

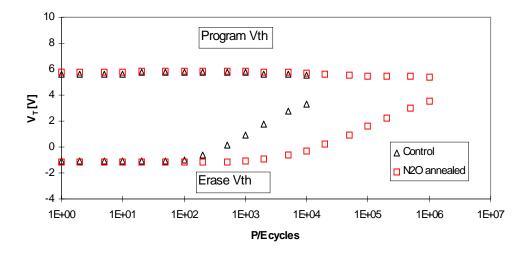

| Figure 3.11 | Reduction in memory window closure caused by N2O                      |

|             | annealing                                                             |

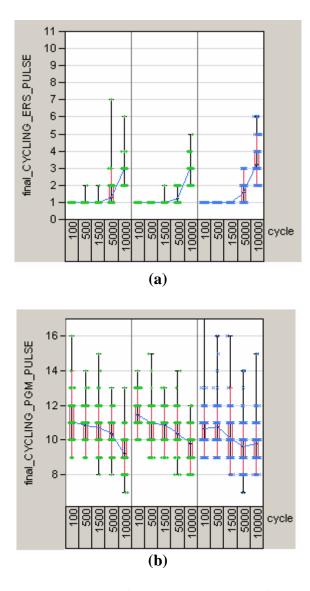

| Figure 4.1  | Typical endurance characteristics of MLC NAND Flash memory            |

|             | cells                                                                 |

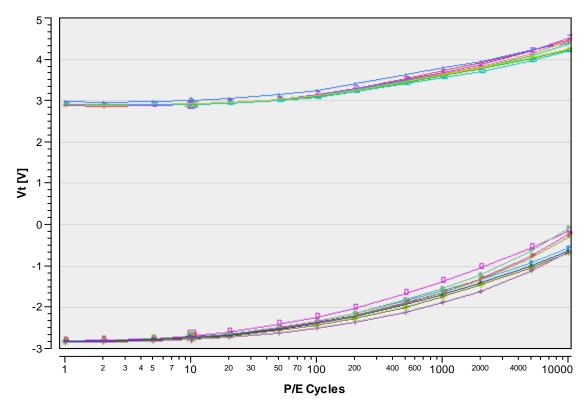

| Figure 4.2  | Endurance characteristics of MLC NAND Flash memory cells              |

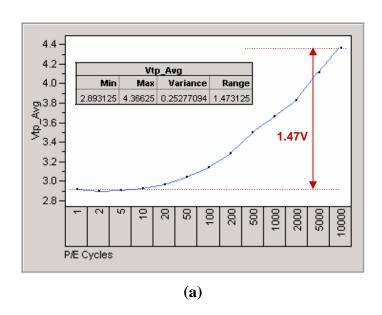

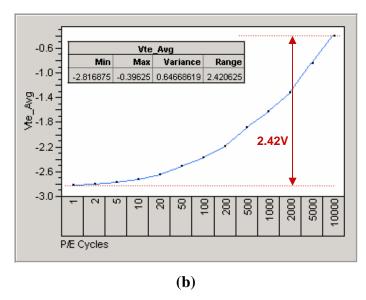

| Figure 4.3  | (a) Average as a function of program/erase cycles and (b)             |

|             | Average as a function of program/erase cycles                         |

| Figure 4.4  | Variability chart showing a slight initial decrease in $V_{T-erased}$ |

| Figure 4.5  | Variability chart for (a) the number of erase pulses needed as a      |

|             | function of the number of cycles and (b) the number of program        |

|             | pulses needed as a function of the number of cycles                   |

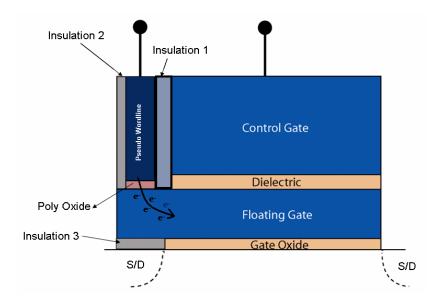

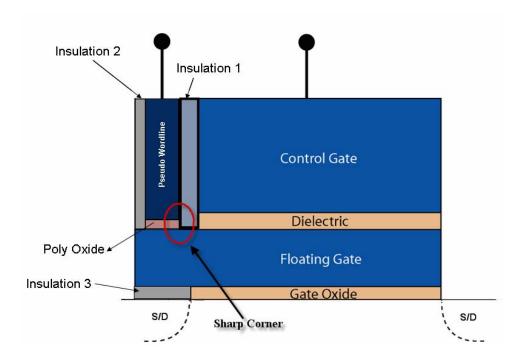

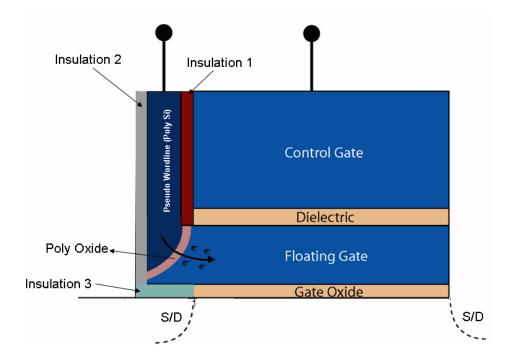

| Figure 4.6  | NAND Flash Memory cell with Pseudo Wordline                     | 79  |

|-------------|-----------------------------------------------------------------|-----|

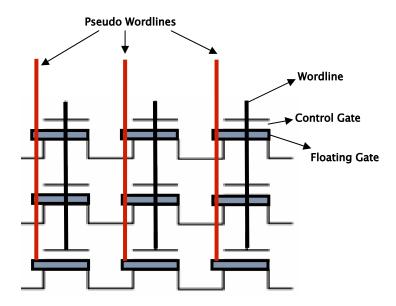

| Figure 4.7  | Schematic view of the proposed NAND Flash memory array          |     |

|             | structure                                                       | 79  |

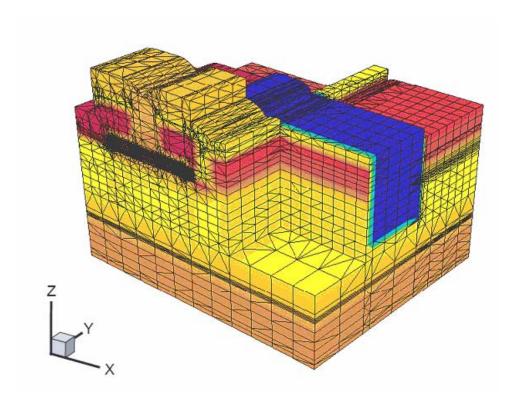

| Figure 4.8  | Visualization of a 3D mesh structure and associated doping      |     |

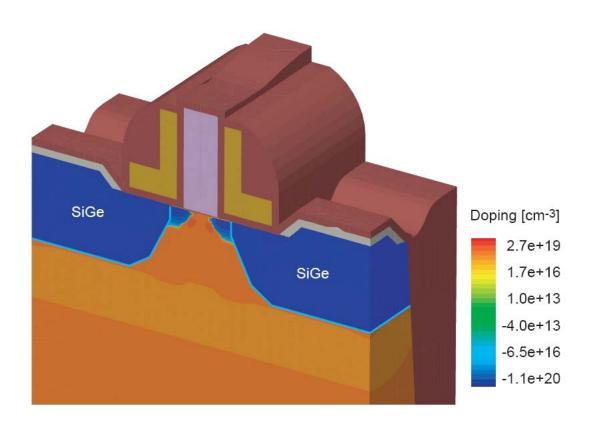

|             | distribution                                                    | 89  |

| Figure 4.9  | Doping profile of a 3D PMOS transistor with SiGe source/drain   |     |

|             | pockets                                                         | 90  |

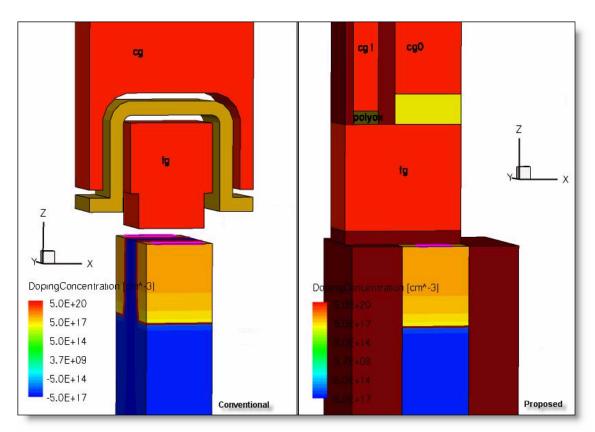

| Figure 4.10 | Conventional Flash memory Cell (left) compared to the           |     |

|             | proposed Flash memory cell (right)                              | 91  |

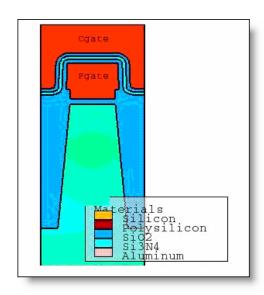

| Figure 4.11 | 2D simulation structure of the conventional NAND Flash          |     |

|             | memory cell                                                     | 92  |

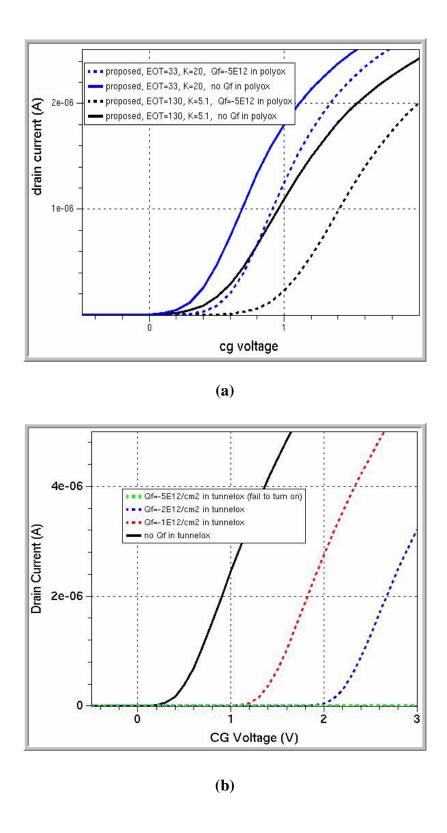

| Figure 4.12 | Shift in the I-V curve of (a) the proposed memory cell and (b)  |     |

|             | the conventional memory cell caused by charge                   | 94  |

|             | trapping                                                        |     |

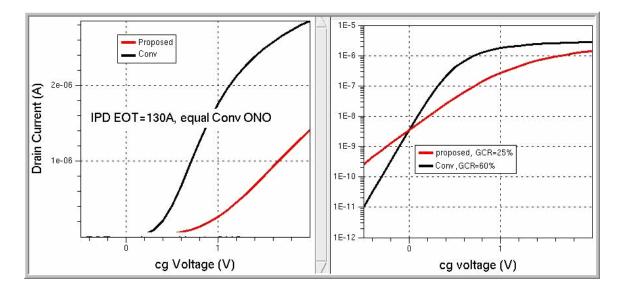

| Figure 4.13 | Comparison of gate coupling ratio between the conventional and  |     |

|             | the proposed Flash memory cell                                  | 98  |

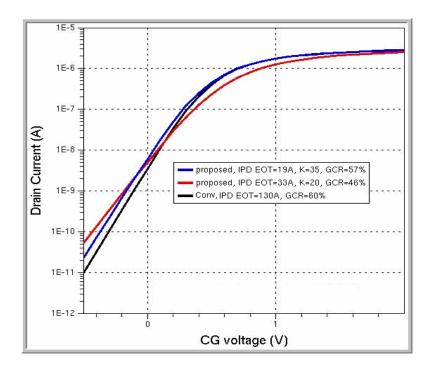

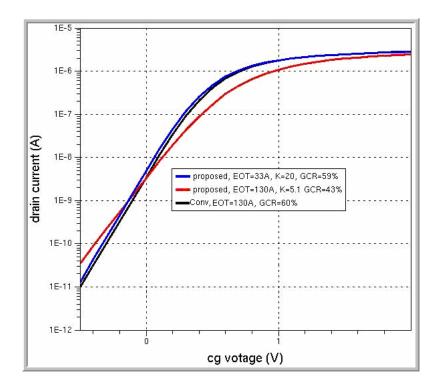

| Figure 4.14 | Gate coupling ratio as a function of IPD EOT                    | 99  |

| Figure 4.15 | IV curves and respective GCRs using various IPD thicknesses     |     |

|             | and dielectric constants.                                       | 100 |

| Figure 4.16 | IV curves and respective gate coupling ratios of the NAND       |     |

|             | Flash memory cells using various IPD thicknesses and dielectric |     |

|             | constants, with the pseudo wordline floating                    | 101 |

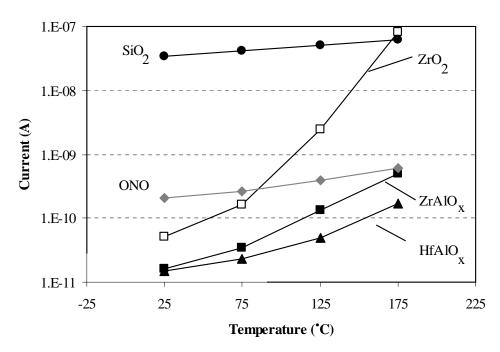

| Figure 4.17 | Temperature dependence of leakage current                       | 104 |

| Figure 4.18 | The originally proposed NAND Flash memory cell has a sharp        |     |

|-------------|-------------------------------------------------------------------|-----|

|             | corner between the pseudo wordline and the floating gate          | 107 |

| Figure 4.19 | Pseudo wordline recessed into the floating gate in order to avoid |     |

|             | current crowding and improve tunneling efficiency                 | 108 |

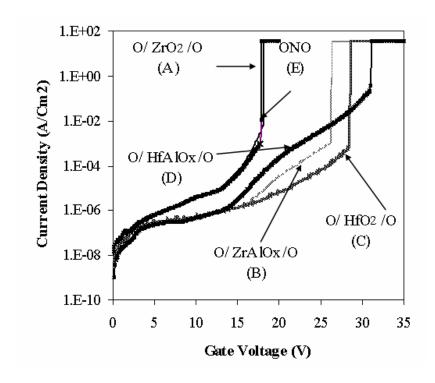

| Figure 4.20 | I-V stress curves for various dielectric materials                | 109 |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 MOTIVATION

Semiconductor memory is an important component of modern microelectronics and an integral part of a vast variety of computing systems and consumer electronics. Its applications are rapidly growing with improving device capabilities. Non-volatile semiconductor memory is an increasingly popular type of semiconductor memory because of its ability to retain data without external power. A very important member of the non-volatile semiconductor memory family is Flash memory because of its high performance capabilities and applications in a wide range of popular consumer products representing a considerable amount of the overall semiconductor market [1].

Low power consumption, high shock resistance (physical resilience/ruggedness), small size, light weight, and fast data access are few of the many reasons why Flash memory devices are continually increasing in popularity and demand as a non-volatile memory storage solution for portable electronics such as wireless phones, personal digital assistants (PDAs), portable music players, keychain USB drives, digital cameras, secure digital (SD) cards, CompactFlash® cards, multimedia cards (MMCs), and many other applications. Another very important Flash memory application is the solid state drive (SSD). SSDs offer low power consumption, virtually zero latency, extremely fast boot-up for OS and applications, fast data access, smaller size, light weight, and high shock resistance (physical resilience/ruggedness) as compared to the conventional magnetic media such as hard disk drives (HDDs). Flash memory is also used in Hybrid Hard Drives (HHDs). HHDs employ a large buffer of non-volatile flash memory used to cache

data during normal use due to which the platters of the hard drive are at rest almost at all times, instead of constantly spinning as is the case in HDDs. This feature offers several benefits such as decreased power consumption, improved reliability, and a faster boot process. A comparison of a few average specifications between HDDs, SSDs, and HHDs is shown in table 1.1 [2].

It must be noted that table 1.1 contains data reported in 2007 and that the performance of SSDs has improved significantly since then. SSDs being currently manufactured by Micron Technology, Inc. offer capacities of up to 256GB and read/write speeds of up to 250MB/s.

Table 1.1: Comparison of average specifications between HDDs, SSDs, and HHDs.

| Average                            | Hard Disk<br>Drive | Solid State<br>Drive | Hard Disk<br>Drive | Hybrid Hard<br>Drive |

|------------------------------------|--------------------|----------------------|--------------------|----------------------|

| Specifications                     | 1.8" HDD           | SSD(1.8"/2.5")       | 2.5" HDD           | 2.5" HHD             |

| Capacity                           | 30-80 GB           | 4-32GB               | 40-160GB           | Up to 160GB          |

| Data Rate<br>(Max Sustain)<br>Read | 25MB/s             | 57MB/s               | 44MB/s             | -                    |

| Write                              | 25MB/s             | 32MB/s               | 44MB/s             | -                    |

| Spindle Speed                      | 4200 RPM           | None                 | 5400 RPM           | 5400 RPM             |

| Seek                               | 15 ms              | None                 | 12 ms              | 12.5 ms              |

| Non-Op Shock                       | 1500 G             | 2000 G               | 900 G              | 900 G                |

According to a presentation at WinHEC 2007, the projected NAND chipset adoption by 2010 will be approximately 75% in notebook PCs and 50% in desktop PCs [2]. The rapidly increasing demand makes Flash memory a major contributor to the evolution of the semiconductor memory industry.

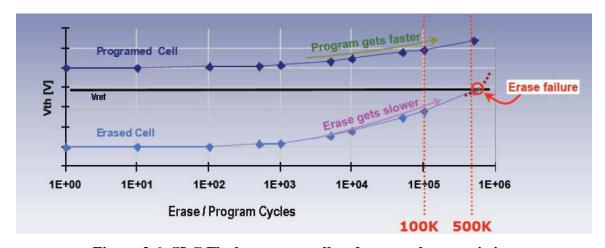

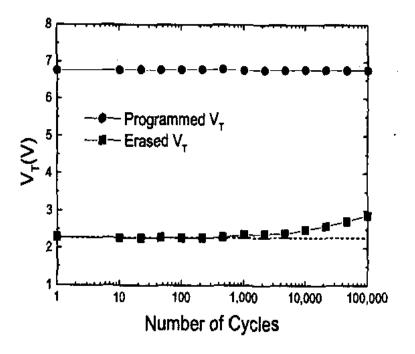

Despite its superior performance potential, Flash memory suffers from the drawback of having limited program/erase endurance. As opposed to an HDD, there is a limit to the number of times NAND Flash memory cells can be programmed and erased. Nominally, each block survives 100,000 program/erase cycles in an SLC NAND Flash device and approximately 10,000 cycles in an MLC NAND Flash device [3,4], implying that long-term reliability and endurance is one of the major concerns in NAND Flash memory technology. Amongst the reliability and endurance concerns, cell threshold voltage shift and memory window narrowing caused by oxide degradation (owed to charge trapping caused by electronic stress during program/erase cycling) is of great interest since it is the main failure mechanism in Flash based memory devices [5]. The issue of tunnel oxide degradation is expected to increase as the oxide thickness is downscaled and the projected number of program/erase cycles is increased [6]. This would put severe limitations to thickness reduction and Flash memory scaling. Thus research in this direction is of significant importance. This work focuses on studying and resolving the reliability concerns related to tunnel oxide degradation in Flash memory cells.

#### 1.2 OBJECTIVE

The objective of this work is to study tunnel oxide degradation in Flash memory cells and propose solutions to the problem in order to improve their long-term reliability and endurance. In this work, a novel NAND Flash memory cell design has been proposed which significantly improves the long-term reliability and endurance of NAND Flash memory cells. Device simulations and analysis have been provided to show that the

proposed cell design offers more endurance and reliability as compared to the conventional NAND Flash memory cell.

#### 1.3 THESIS ORGANIZATION

The motivation and objective of the current research are discussed in chapter 1. Chapter 2 provides an overview of the technical background of Flash memory including the structure, function and principles of operation of NAND Flash memory devices. Chapter 3 includes a detailed review of the reliability issues affecting Flash memory devices and some prior research work done in attempt to address these issues. In chapter 4, endurance characterization and analysis of NAND Flash memory cells have been included. Subsequently, a novel NAND Flash memory cell design has been proposed. Device simulations and corresponding analysis has been provided to show that the proposed cell design offers superior program/erase endurance and reliability as compared to conventional NAND Flash memory cells. The conclusions and suggested future work have been presented in chapter 5.

#### **CHAPTER 2: TECHNICAL BACKGROUND**

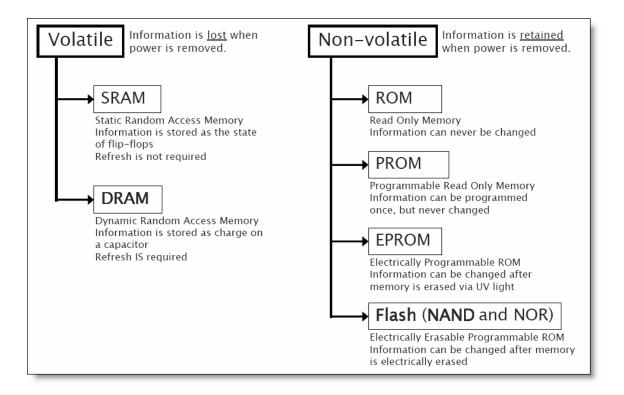

Semiconductor memory can be divided into two main categories: Volatile and Non-volatile. Volatile semiconductor memory loses stored information once the power supply is switched off such as DRAM. On the other hand, non-volatile semiconductor memory maintains stored information even when the power supply is switched off such as Flash memory. Figure 2.1 shows the two families of semiconductor memory (Volatile and Non-volatile) and a few examples of technologies belonging to each family.

Figure 2.1: Volatile vs. Non-volatile semiconductor memory.

#### 2.1 NOR FLASH VS. NAND FLASH

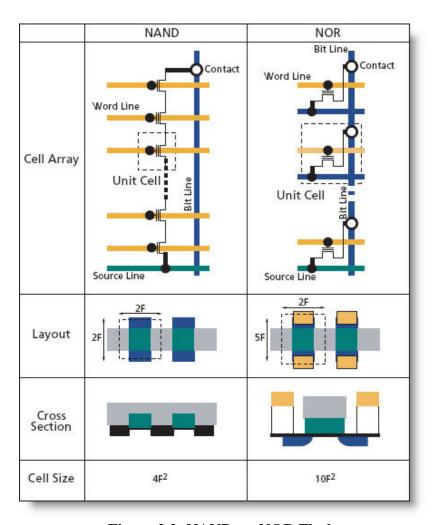

Flash memory is further divided into two main categories: NOR and NAND Flash. Figure 2.2 shows a comparison between the array and cell architecture of NAND and NOR Flash [3]. NAND Flash is more efficient as compared to NOR Flash due in part to the small number of metal contacts in the NAND Flash string. NAND Flash cell size  $(4F^2)$  is much smaller compared to NOR Flash cell size  $(10F^2)$  because NOR Flash cells require a separate metal contact for each cell.

Figure 2.2: NAND vs. NOR Flash.

Another major difference between NOR and NAND Flash is that NOR Flash memory cells use Channel Hot Electron (CHE) injection in the floating gate at the drain side for the program operation where as NAND Flash memory cells use Fowler-Nordheim (FN) Tunneling. Both NOR and NAND Flash cells use Fowler-Nordheim Tunneling for the erase operation [7]. The programming and erasing mechanisms in NOR Flash memory cells are shown in figure 2.3 [8]. The program and erase operations in NAND Flash memory cells have been discussed in detail in a later section.

Figure 2.3: (a) Programming of a NOR Flash memory cell (CHE Injection), and (b)

Erasing of a NOR Flash memory cell (FN Tunneling).

#### Advantages and disadvantages of NOR Flash [3]:

The primary advantage of NOR Flash is fast random access which makes it ideal for program code storage. Random access gives NOR Flash its execute-in-place (XiP) functionality (code execution), which is often required in embedded applications. However, an increasing number of processors include a direct NAND Flash interface and can boot directly from the NAND Flash device (without NOR Flash). Another advantage of NOR Flash is its byte write capability. A few of the most popular applications of NOR Flash today include BIOS, Mobile Phones, Routers, Set-Top Boxes, and Video Games.

The main disadvantage of NOR Flash is its slow program and erase performance.

Another significant disadvantage of NOR Flash is the high programming current (since CHE programming is used) [7].

#### Advantages and disadvantages of NAND Flash [3]:

The most prominent advantage of NAND Flash memory over NOR Flash is its faster program and erase times. Moreover, NAND Flash cells are 60% smaller as compared to NOR Flash cells providing higher densities required for today's low-cost consumer devices in a significantly reduced die area. NAND Flash typically incorporates a string of 32 cells per contact in contrast with one contact per every cell in NOR Flash. This results in smaller cells, and greater bit density at a lower cost. The fast program and erase times, lower cost per bit, and small size make NAND Flash ideal for large amount of data storage e.g. hard drives for personal computers. NAND Flash is very similar to a hard disk drive. It is sector-based (page-based) and well suited for storage of sequential data such as pictures, video, audio, or PC data. NAND Flash is used in virtually all

removable cards, including USB drives, secure digital (SD) cards, memory stick cards, CompactFlash® cards, and multimedia cards (MMCs). The NAND Flash multiplexed interface provides a consistent pinout for all recent devices and densities. This pinout allows designers to use lower densities and migrate to higher densities without any hardware changes to the printed circuit board. Other important applications of NAND Flash memory include Mobile Phones, Digital Audio/Voice, Still & Video Cameras, Mass Data Storage, and PDAs.

The main drawback of NAND Flash is its slower random access as compared to NOR Flash. A comparison of basic advantages, disadvantages and applications of NAND vs. NOR flash memories is shown in Table 2.1 [3].

Table 2.1: A comparison of basic advantages, disadvantages and applications of NAND vs. NOR Flash memories.

|               | NAND                        | NOR                               |

|---------------|-----------------------------|-----------------------------------|

| Advantages    | Fast WRITEs                 | Random access                     |

|               | Fast ERASEs                 | Byte WRITEs possible              |

|               | •                           | •                                 |

| Disadvantages | Slow random access          | Slow WRITEs                       |

|               | Byte WRITEs difficult       | Slow ERASEs                       |

|               | •                           | •                                 |

| Applications  | File (disk) applications    | Replacement of EPROM              |

|               | Voice, data, video recorder | Execute directly from nonvolatile |

|               |                             | memory                            |

|               | Any large sequential data   |                                   |

#### 2.2 CELL STRUCTURE OF THE NAND FLASH MEMORY CELL

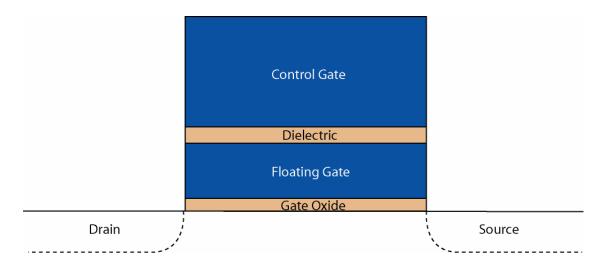

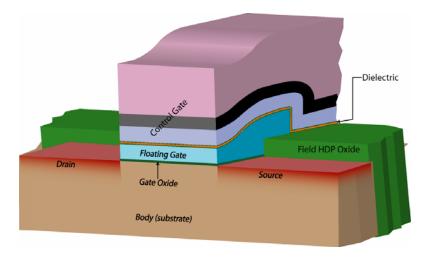

The basic structure of a NAND Flash memory cell is similar to that of a MOSFET, as shown in figure 2.4. It is composed of a dual-gate transistor. The dual-gate functionality allows charge storage on the floating gate and thereby alteration of the device threshold voltage (threshold voltage modulation). This enables programming and erasing the transistor by adding or removing charge from the floating gate in order to produce distinct logical values.

Figure 2.4: Basic structure of a NAND Flash memory cell.

The various components of a NAND Flash memory cell and their respective functions are as follows:

- *Gate Oxide*: The gate oxide is also often referred to as "tunnel oxide" and has two primary functions:

- It is used to tunnel electrons during the "program" and "erase" operations.

The thickness of the oxide determines the tunneling current density.

- o It determines the threshold voltage of the cell during the "read" operation.

- *Floating Gate:* A polysilicon layer that is completely surrounded by a dielectric used to store charge and alter the threshold voltage of the device.

- *Dielectric:* This is simply an insulator, typically ONO (Oxide Nitride Oxide). The function of this dielectric is to inhibit charge stored on the floating gate from leaking into the control gate.

- Control Gate: The conductor of the wordline used to access the transistor.

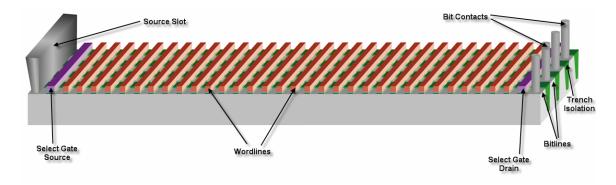

A 3D view of a typical NAND Flash memory cell is shown in figure 2.5 [9].

Figure 2.5: 3D view of a typical NAND Flash memory cell.

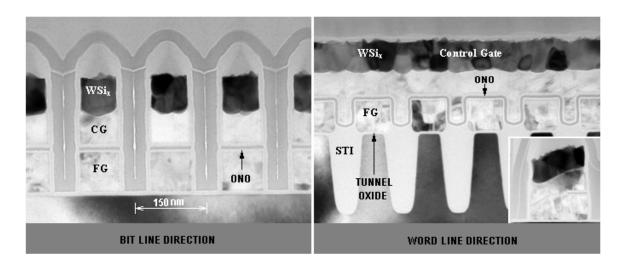

Scanning Electron Microscope (SEM) cross-sections of typical SLC NAND Flash memory cells is shown in figure 2.6 [4].

Figure 2.6: Scanning electron microscope (SEM) cross-sections of typical SLC NAND Flash memory cells.

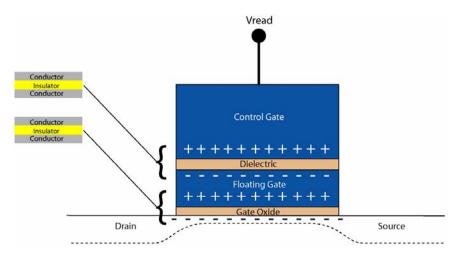

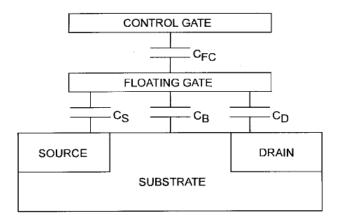

Since the floating gate is electronically isolated, voltage can not be directly applied to it. A fraction of the voltage applied to the control gate is "seen" by the floating gate due to capacitive coupling. In other words, capacitive coupling is used to indirectly control the floating gate. The voltage seen by the floating gate then plays its role in bending the energy bands at the Floating Gate-Tunnel Oxide interface. The voltage seen by the floating gate in a Flash memory cell is analogous to the voltage applied to the gate of a MOS transistor. The gate stack of a Flash Memory cell can be thought of as two capacitors in series as shown in figure 2.7.

Figure 2.7: Gate stack of the Flash memory cell can be replaced by capacitors in series to understand the effect of capacitive coupling.

The basic capacitive components of the Flash memory cell and respective calculations are further discussed in the next section.

#### 2.3 Principles of Operation of the NAND Flash Memory Cell

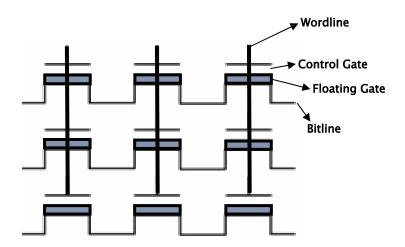

Flash Memory stores information in an array of transistors also called 'cells'.

Figure 2.8 shows the schematic view of a conventional NAND Flash memory array.

Figure 2.8: Schematic view of a conventional NAND Flash memory array structure.

A 3D view of a conventional NAND Flash memory array is shown in figure 2.9 [9].

Figure 2.9: 3D view of a conventional NAND Flash memory array.

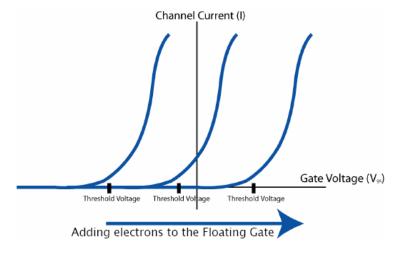

As discussed before, each NAND Flash memory cell looks similar to a standard MOSFET, except that it has two gates instead of just one. One is the control gate (CG) and the other is the floating gate (FG) that is electrically isolated on all sides. The FG is located between the CG and the substrate. Information is stored by adding/removing charge on the FG. Adding or removing electrons from the floating gate allows alteration of the transistor threshold voltage. Altering the threshold voltage of a device allows programming a cell such that current will flow or will not flow, depending on the threshold voltage of the cell, from drain to source when a reference voltage is applied to the control gate. This presence or absence of current is sensed and translated into "1"s and "0"s by the sense amp, reproducing the stored data. The phenomenon of altering the threshold voltage is also known as 'threshold voltage modulation'.

Figure 2.10: Threshold voltage modulation.

As shown in figure 2.10, the threshold voltage of the Flash Memory Cell is altered or "modulated" simply by adding or removing electrons from the floating gate.

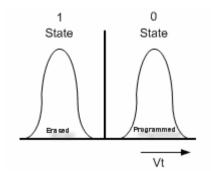

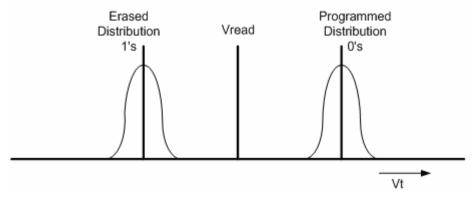

Figure 2.11 shows the  $V_T$  distributions of programmed ("0") vs. erased ("1") cells in an array.

Figure 2.11:  $V_T$  distributions of programmed ("0") vs. erased ("1") cells in an array.

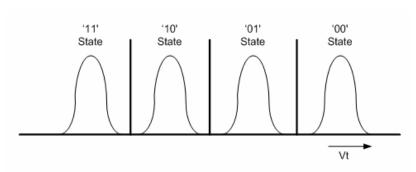

Some modern Flash memory devices, referred to as multi-level cell (MLC) devices, can store more than 1 bit per cell (typically 2 bits per cell for current technology) by varying the number of electrons placed on the FG, as compared to single-level cell

(SLC) devices that can store only one bit per cell at a time. In other words, in MLC devices, one threshold voltage level represents two bits. Figure 2.12 shows the  $V_T$  distributions in MLC devices.

Figure 2.12:  $V_T$  distributions in MLC devices.

However, since the delta between each state is decreased in MLC devices compared to SLC devices, the margins between the threshold voltages of subsequent logic states is significantly reduced. Thus, more rigidly controlled programming is needed to manipulate a more precise amount of charge stored on the floating gate. At the same time, precise charge sensing is required as well.

Multi-level cell devices have some advantages and some disadvantages over single-level cell devices. The basic advantages of each of the two types of Flash memory cells have been summarized in table 2.2 [3].

|                         | SLC      | MLC      |

|-------------------------|----------|----------|

| High Density            |          | <b>√</b> |

| Low Power Consumption   | <b>√</b> |          |

| Program/Erase Speeds    | <b>√</b> |          |

| Program/Erase Endurance | <b>√</b> |          |

| Low Cost per Bit        |          | <b>√</b> |

Operating Temperature

Endurance

Table 2.2: Basic advantages of SLC vs. MLC Flash devices.

The threshold voltage shift,  $\Delta V_T$ , caused by charge stored on the floating gate of a NAND Flash memory cell is given by [10],

$$\Delta V_T = \frac{N.q}{C_{IPD}} \tag{2.1}$$

where q is the electronic charge, N is the number of electrons stored on the floating gate, and  $C_{IPD}$  is the control gate to floating gate capacitance.  $C_{IPD}$  is given by,

$$C_{IPD} = \frac{\varepsilon_0 . S_{IPD}}{EOT_{IPD}}$$

(2.2)

where  $EOT_{IPD}$  is the equivalent oxide thickness of the interpoly dielectric (IPD) and  $S_{IPD}$  is the floating gate area covered by the control gate.

The threshold voltage of the floating gate memory cell at any given time,  $V_{\scriptscriptstyle T}$  , can therefore be written as

$$V_T = V_{T0} + \Delta V_T \tag{2.3}$$

where  $V_{T0}$  is a constant that depends on the gate and substrate material, doping, and gate oxide thickness.  $V_{T0}$  is given by the expression

$$V_{T0} = 2\Phi_F + \Phi_{ms} - \frac{Q_{ox}}{C_{ox}} - \frac{Q_{dm}}{C_{ox}}$$

(2.4)

where

$\Phi_F$  is the Fermi potential of the substrate at the surface at inversion

$\Phi_{\it ms}$  is the work function difference between the gate metal and the substrate

$Q_{ox}$  is the fixed charge in the tunnel oxide

$Q_{\rm dm}$  is the maximum charge held by the depletion layer at inversion

$C_{ox}$  is the capacitance of the tunnel oxide

It can be seen that the effective threshold voltage of the transistor can be altered by changing the amount of charge stored on the floating gate i.e. altering the  $\Delta V_T$  term.

The basic operations performed on a Flash Memory Cell include reading, programming, program inhibiting, program verifying, erasing, erase inhibiting, and erase verifying. The mechanisms involved in reading, programming, program inhibiting, erasing, and erase inhibiting an MLC device are essentially the same as for an SLC device. For the reason of simplicity, the above mentioned basic operations are discussed for the case of an SLC device.

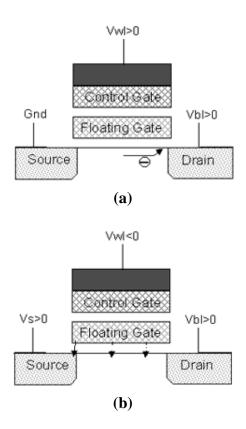

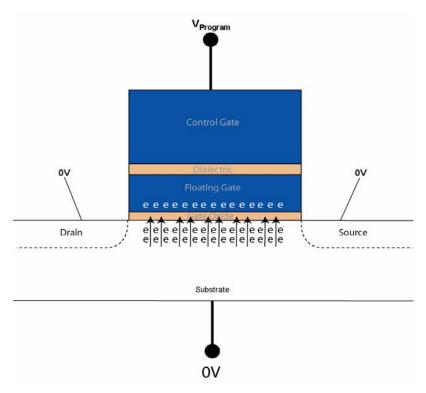

A NAND Flash memory cell is programmed (set to a "0" state) by applying a large voltage,  $V_{program}$ , on the CG (Control Gate).  $V_{program}$  provides an electric field strong enough to tunnel electrons from the substrate to the FG (Floating Gate), through the tunnel oxide. This process of field assisted tunneling is called Fowler-Nordheim (FN) Tunneling. To erase the cell (reset to "1"), a large voltage differential,  $V_{erase}$ , is placed between the substrate and the gate.  $V_{erase}$  provides an electric field strong enough to tunnel electrons from the floating gate back to the substrate, through the tunnel oxide.

The read, program, program inhibit, program verify, erase, erase inhibit, and erase verify operations are subsequently discussed in detail.

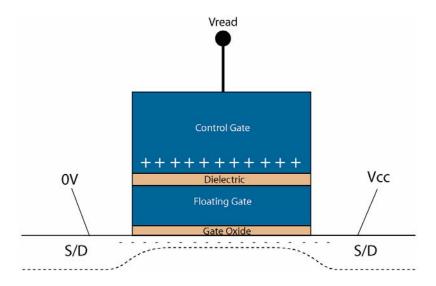

- Read: The "read" operation is performed to determine whether the cell is in a "programmed" ("0") or "erased" ("1") state. A reference voltage,  $V_{read}$ , is applied to the control gate, where  $V_{T-erased} < V_{read} < V_{T-programmed}$ .  $V_{T-erased}$  is the threshold voltage of an erased cell and  $V_{T-programmed}$  is the threshold voltage of a programmed cell.

- o Reading An erased cell ("1"): When the cell is in the un-programmed or "erased" state, the floating gate is depleted of electrons. In order to read the cell,  $V_{read}$  is applied to the control gate and a source to drain voltage potential is also applied. Since the floating gate in the erased state is depleted of electrons, the applied voltage is sufficient to drive the cell into inversion, since  $V_{T-erased} < V_{read}$ . The cell is now turned "on" and there is a current flow from drain to source that is sensed by the sense amp and the cell is read as a "1".

Figure 2.13: The erased Flash memory cell turns "on" when  $V_{\it read}$  is applied.

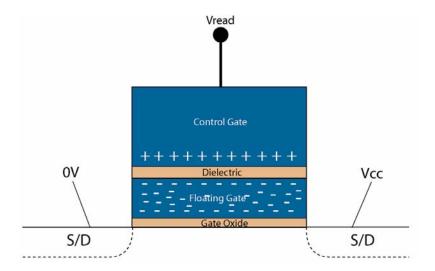

O Reading a Programmed Cell ("0"): When the cell is in the "programmed" state, the floating gate is charged i.e. it has electrons stored in it. A programmed cell is read by applying the same read voltage,  $V_{read}$ , to the control gate as is applied for reading an erased cell. However, for a programmed cell,  $V_{read}$  is not enough to drive the cell into inversion, since  $V_{read} < V_{T-programmed}$  due to the accumulation of electrons on the floating gate. With a large number of electrons stored on the floating gate, the threshold voltage of the device is increased i.e. it now requires a higher positive voltage applied to the control gate to induce a channel under the tunnel oxide, as compared to an erased cell. Consequently, there is no current flow from drain to source in response to the applied voltage,  $V_{read}$ . No current flow is interpreted as logic "0" by the sense amp.

Figure 2.14: The programmed Flash memory cell is "off" when  $V_{\it read}$  is applied.

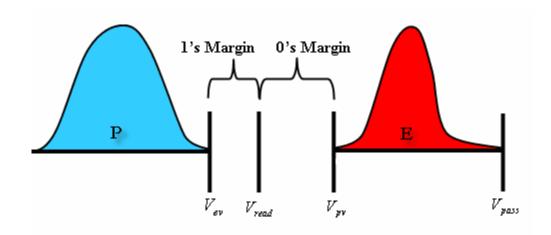

An SLC Flash memory device is engineered such that it has two statistical distributions of threshold voltages in the array (i.e. for programmed and erased cells). Figure 2.15 shows the distributions of acceptable ranges for  $V_T$ 's of programmed ("0") and erased ("1") cells.

Figure 2.15: Distributions of acceptable ranges for the  $V_T$  's of programmed ("0") and erased ("1") cells.

As seen in figure 2.15,  $V_{read}$  sits between the two distributions of threshold voltages. This is done so that if the cell has not been programmed,  $V_{read}$  will induce a conductive channel allowing current flow from drain to source and is interpreted as a "1" stored in the cell.

At the same time,  $V_{read}$  is smaller than the  $V_T$ 's of the programmed distribution, therefore there is no current flow from drain to source and is interpreted as a "0" stored in the cell.

The effect of electrons stored on the floating gate on the threshold voltage of the cell can be expressed by the following equation [11]:

$$V_{T-programmed} = V_{T-erased} - \frac{Q_{FG}}{C_{IDD}}$$

(2.5)

where

$V_{T-erased}$  is the threshold voltage of an erased cell.

$V_{T-programmed}$  is the threshold voltage of a programmed cell.

$Q_{\rm FG}$  is the charge stored on the floating gate.

$C_{\it IPD}$  is the interpoly dielectric capacitance or the control gate to floating gate capacitance.

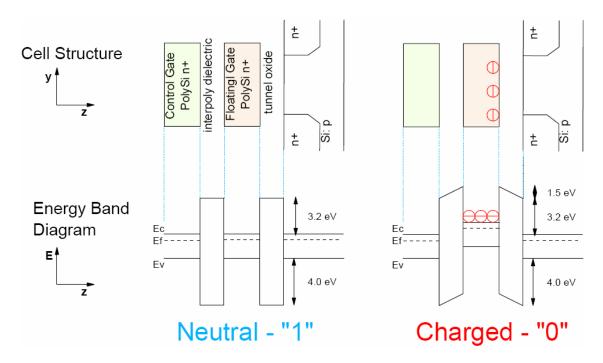

A simplified schematic energy band diagram of an erased (left) and a programmed (right) Flash memory cell are shown in figure 2.16 [8].

Figure 2.16: Energy band diagram of an erased (left) and a programmed (right)

Flash memory cell.

• Program: Programming or "writing" to an un-programmed cell simply means charging the floating gate. This is done using Fowler-Nordheim Tunneling. A large positive voltage,  $V_{program}$ , is applied to the control gate while the substrate is grounded. When the oxide barrier between the substrate and the floating gate becomes thin enough, electrons tunnel from the substrate to the floating gate through the gate oxide. Fowler-Nordheim Tunneling has been discussed in detail in a later section.

Figure 2.17: Voltage conditions during programming a NAND Flash memory cell.

Program Inhibit: The programming voltage that is applied to the selected wordline is carried to all cells sharing the wordline. If a high potential such as  $V_{program}$  is applied to the wordline, all cells sharing the wordline would get programmed rather than just the selected cell. In order to prevent unselected cells from being programmed, they must be "inhibited" from being programmed. The program inhibit process is also often referred to as "boosting".

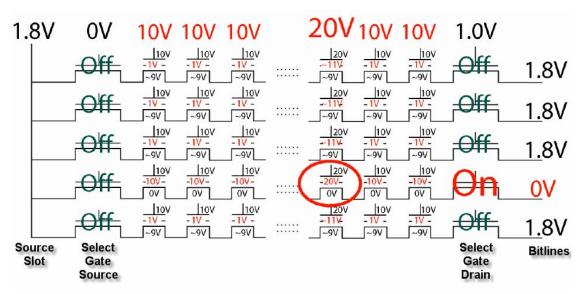

Before proceeding to a detailed explanation of the process of boosting, the following device parameters are assumed for the purposes of demonstration:

$$V_{cc} = 1.8 \text{V}$$

$$V_T$$

of SGD and SGS = 0.8V

$$V_{pass} = 5V$$

$$V_{inhibit} = 10V$$

$$V_{program} = 20V$$

The following are the basic steps involved in the boosting process:

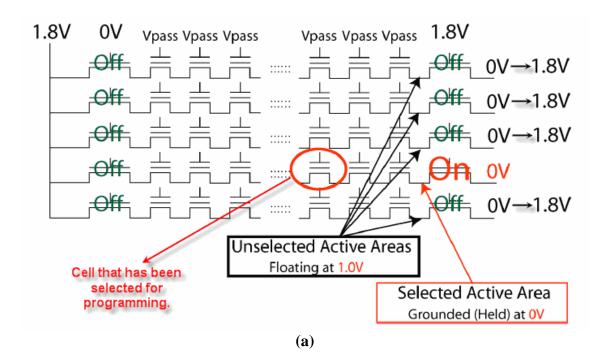

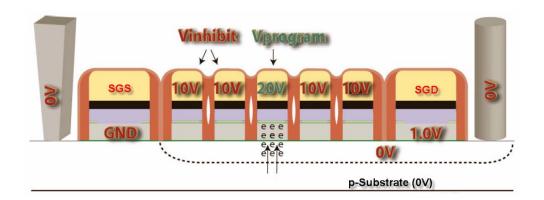

o Step 1: The SGD voltage is driven to  $V_{CC}$  (1.8V) and all wordlines to  $V_{pass}$ . This opens a continuous channel from the bitline down the length of the string. The unselected bitlines (all strings except for the ones in which the cell to be programmed exists) are ramped to  $V_{CC}$  (1.8V). The selected bitline (string in which the cell selected for programming exists) is kept grounded. The cells in the unselected strings are now off and the channels floating at ~1V (1.8V- $V_T$ ), while the channels of the cells in the selected string are still at 0V. The source slot is ramped to  $V_{CC}$ . This stops current from flowing through the string. Since no current is flowing, but all channels are open, the source, drain, and channel of all cells in the string will be at the same potential. Figure 2.18 (a) shows the cell conditions after step 1 of the boosting process [9].

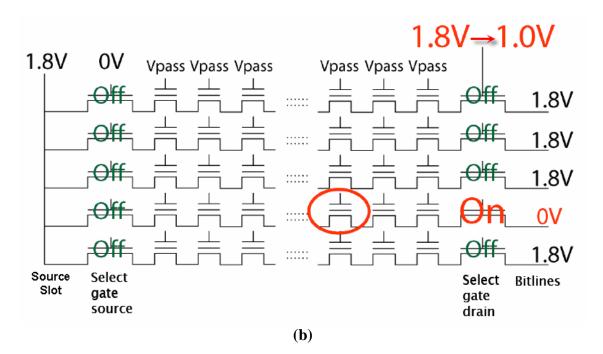

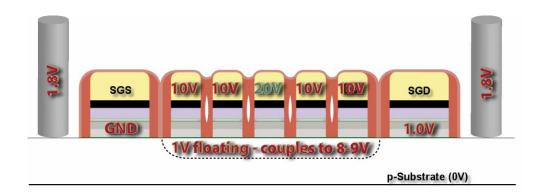

- o *Step 2:* The potential on SGD is dropped from 1.8V to 1.0V. Since the  $V_T$  of these cells is 0.8V, this guarantees that the SGD transistor of all unselected strings are shut off ( $V_{GS} < V_T$  or 1.0V-1.8V<0.8V), while the SGD of selected strings remain on ( $V_{GS} > V_T$  or 1.0V-0V>0.8V). The source, drain and channel of the unselected strings are therefore floating, while those of the selected string still have a path to ground. Figure 2.18 (b) shows the cell conditions after step 2 of the boosting process [9].

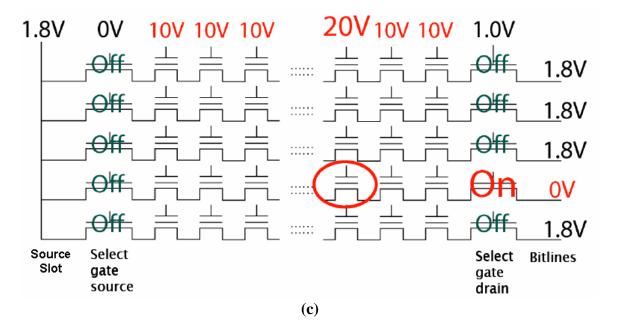

- o *Step 3:* All wordlines in the block are raised to  $10V(V_{inhibit})$ . The floating channels of the unselected strings will capacitively couple to the gate and float up to approximately 8-9V, thereby reducing the gate-to-well potential to approximately 10-12V. That is not enough potential to induce tunneling, so these cells will not be programmed. The selected wordline is then raised to 20V. Since the selected string is still grounded, the gate-to-well potential on the selected wordline is 20V, while the potential across the cells on the unselected wordlines is only 10V. Therefore, only the cell on the selected wordline and bitline will be programmed. Figure 2.18 (c) shows the cell conditions after step 3 of the boosting process [9].

Figure 2.18: Cell conditions after (a) step 1 of the boosting process, (b) step 2 of the boosting process, (c) step 3 of the boosting process.

Figure 2.19 shows a final cell conditions at the end of the boosting process.

Figure 2.19: Final cell conditions at the end of the boosting process.

A cross-section view and respective voltage conditions within a selected (5 cell) string are shown in figure 2.20 [9].

Figure 2.20: Cross-section view and respective voltage conditions within the selected string.

A cross-section view of a program inhibited (5 cell) string and the respective voltage conditions is shown in figure 2.21 [9].

Figure 2.21: Cross-section view and respective voltage conditions within a program inhibited string.

Select Gate Drain

Select Gate Source

Vpass

Vpass

Vcc

Vpass

Vcc

Vpass

Vcc

Source Slot

Vcc

Source Slot

Vcc

Source Slot

Select fold

Select hold

A timeline of the boosting process is shown in figure 2.22 [9].

Figure 2.22: A timeline of the boosting process.

It must be noted that even though the representations above show 20V being applied as the programming voltage, in modern NAND Flash devices, program verify operations (discussed later in this section) are performed at fixed intervals during the ramping of the wordline to 20V. In other words, the applied program pulses are ramped up starting from a small voltage and increased gradually, with program verify operations performed intermittently. The single cell programming algorithm can be broken down into the following steps:

- Apply a low voltage program pulse to the selected wordline (and, in turn, to the selected gate).

- 2. Check the cell  $V_T$  (Program Verify operation).

- 3. If cell  $V_T \ge \text{Target } V_T$ , end programming loop.

- 4. If the cell  $V_T$  < Target  $V_T$ , increment the gate voltage (stepped WL voltage).

- 5. Repeat steps 2-3.

In summary, the starting gate voltage needs to be low enough to ensure the cell does not over program in the first pulse. The key to programming a cell, without over-programming the selected cell, is to move the threshold voltage up as gently as possible yet hard enough to minimize the time to program. Another reason for not applying higher than necessary program pulse voltage is to avoid inadvertently programming neighboring cells ('Program Disturb' mechanism).

• Program Verify: After the program operation, a program verify is done with slight guard band. That means that we apply slightly higher voltage to the wordline than a typical read operation to guarantee margin. This voltage is known as the program verify voltage,  $V_{pv}$ . Each sense amp tries to detect the state of the cell in a program verify operation. Internally, the sense amp maintains a latched state of the expected data and does a compare vs. the sensed data.

If the cell in question has been "programmed" enough, it will have a  $V_T$  greater than  $V_{pv}$ , and no current flow will be detected by the sense amp and the cell is read as a "0". On the other hand, if the  $V_T$  of the cell in question is below the

expected  $V_{T-programmed}$ , and the string discharges, the sense amp will detect the current and the cell is read a "1", which indicates the program operation has not completed yet. Another program pulse is then applied to the cell followed by another program verify operation. This algorithm is repeated until the cell in question is verified to have been programmed or we have a program verify failure (program fail status).

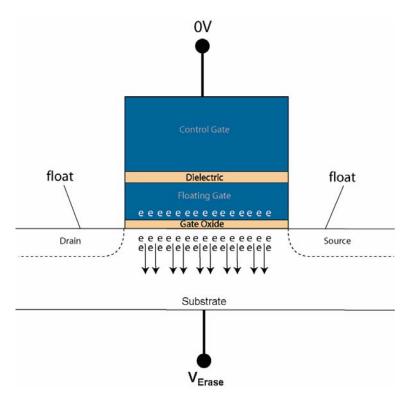

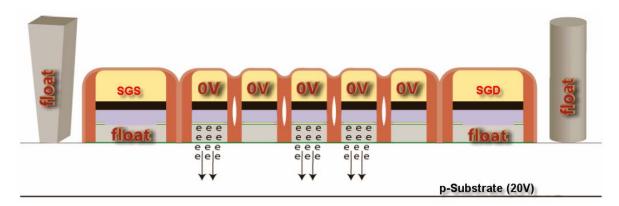

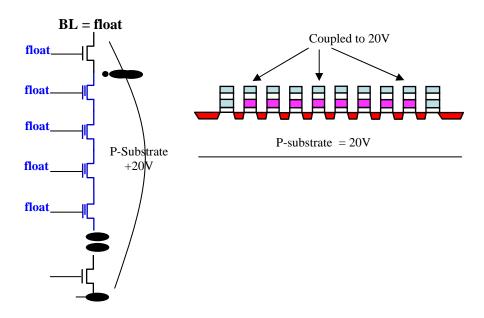

• Erase: Erasing a programmed cell is the reverse process of programming an erased cell, i.e. instead of tunneling electrons from the substrate to the floating gate, we now tunnel electrons from the floating gate back to the substrate. A sufficiently large positive voltage,  $V_{erase}$ , is applied to the substrate while the control gate is grounded and electrons tunnel from the floating gate to the substrate through the gate oxide, again, by the process of Fowler-Nordheim tunneling.

Figure 2.23: Voltage conditions during erasing a NAND Flash memory cell.

• Erase Inhibit: For die-size reasons, all blocks share the same p-well, which is the reason why the erase operation is typically done one block at a time. To inhibit blocks other than the selected blocks from being erased, the wordlines in the unselected blocks are floated. The positive p-well bias capacitively couples to the wordlines, raising them close to  $V_{erase}$  (~20V). As a result, a very low voltage is dropped across the gate stack, and therefore no tunneling takes place.

A cross-section view and respective voltage conditions of a (5 cell) string that has been selected for erase is shown in figure 2.24 [9].

Figure 2.24: Cross-section view and respective voltage conditions of a string that has been selected for erase.

The voltage conditions of a string that has been erase inhibited are shown in figure 2.25 [9].

Figure 2.25: Voltage conditions of an erase inhibited string.

Erase Verify: Erase verify is not performed cell-by-cell as opposed to a program verify. Instead, each string is verified, with all wordlines set to Erase Verify voltage,  $V_{ev}$ . If the string current detected by the sense amp is lower than the expected current (i.e. the current when all cells in the string are erased), it indicates that one or more cells in the string have not been completely erased. More erase pulses are then applied followed by another erase verify. This algorithm is repeated until all cells in the string are verified to have been erased or we have an erase verify failure (erase fail status).

Figure 2.26 shows the  $V_T$  distribution of programmed vs. erased cells, in an SLC device, relative to  $V_{ev}$ ,  $V_{read}$ ,  $V_{pv}$ , and  $V_{pass}$ .

Figure 2.26:  $V_T$  distribution of programmed vs. erased cells relative to  $V_{ev}$  ,  $V_{read}$  ,  $V_{pv}$  , and  $V_{pass}$  .

The relative characteristics and conditions of programmed and erased cells in an SLC device have been summarized in table 2.3.

Table 2.3: Relative cell conditions of programmed vs. erased cells in an SLC device.

| Cell state        | # of e <sup>-</sup> 's in Floating Gate | Cell $V_T$ | Current in Channel (when $V_{read}$ is applied)? | Logic State |

|-------------------|-----------------------------------------|------------|--------------------------------------------------|-------------|

| Not<br>Programmed | Low                                     | Low        | Yes                                              | 1           |

| Programmed        | High                                    | High       | No                                               | 0           |

The electronic characteristics of a Flash memory cell are essentially like those of a MOSFET. Once the potential of the floating gate is determined, the current equations for a MOS transistor can be used to compute the IV characteristics of the Flash memory cell [12].

In order to determine the potential of the floating gate, the capacitive coupling needs to be considered. The capacitive components of a generic floating gate device such as a Flash memory cell is shown in figure 2.27, where  $C_s$  is the capacitance between the source and the floating gate,  $C_B$  is the capacitance between the substrate and the floating gate,  $C_D$  is the capacitance between the drain and the floating gate and  $C_{FC}$  is the capacitance between the floating gate and the control gate (also referred to as  $C_{IPD}$  earlier) [12].

Figure 2.27: Capacitive components of a generic floating gate device.

As can be seen from figure 2.27, the total capacitance of the floating gate,  $C_{\it Total}$ , is the sum of the individual capacitive components i.e.

$$C_{Total} = C_S + C_B + C_D + C_{FC}$$

(2.6)

The total charge on the floating gate,  $Q_{FG}$ , can then be written as  $Q_{FG} = (V_{FG} - V_S) \times C_S + (V_{FG} - V_B) \times C_B + (V_{FG} - V_D) \times C_D + (V_{FC} - V_{CG}) \times C_{FC}$  (2.7) where  $V_{FG}$  is the potential on the floating gate,  $V_{CG}$  is the potential on the control gate, and  $V_S$ ,  $V_B$ , and  $V_D$  are potentials on source, substrate, and drain, respectively. The potential of the floating gate is given by

$$V_{FG} = \frac{Q_{FG}}{C_{Total}} + \alpha_G V_{GS} + \alpha_D V_{DS} + \alpha_S V_S + \alpha_B V_B$$

(2.8)

where

$$\alpha_G = \frac{C_{FC}}{C_{Total}}$$

, the coupling coefficient relative to the control gate (2.9)

$$\alpha_D = \frac{C_D}{C_{Total}}$$

, the coupling coefficient relative to the drain (2.10)

$$\alpha_S = \frac{C_S}{C_{Total}}$$

, the coupling coefficient relative to the source (2.11)

$$\alpha_B = \frac{C_B}{C_{Total}}$$

, the coupling coefficient relative to the source (2.12)

Due to its near identical structure and function as a MOS transistor, the current-voltage equations for a Flash memory cell can be derived from the current-voltage equations of the MOS transistor. This is done replacing the MOS gate voltage  $V_{\rm GS}$  with

the floating gate voltage  $V_{FG}$  and transforming the device parameters such as threshold voltage  $(V_T)$  and conductivity factor  $(\beta)$ , to values measured with respect to the control gate [12]. If we define for  $V_{DS}$  =0,

$$V_T^{FG} = \alpha_G V_T^{CG} \tag{2.13}$$

and

$$\beta^{FG} = \frac{1}{\alpha_G} \beta^{CG}, \qquad (2.14)$$

the current–voltage (I–V) equations of a floating gate transistor can be compared to those of a conventional MOSFET in the triode region and the saturation region. The derived current-voltage equations for a Flash memory cell are as follows:

In the triode region,

$$|V_{DS}| < \alpha_G |V_{GS} + fV_{DS} - V_T^{CG}|$$

(2.15)

and

$$I_{DS} = \beta^{CG} \left[ \left( V_{GS} - V_T^{CG} \right) V_{DS} - \left( f - \frac{1}{2\alpha_G} \right) V_{DS}^2 \right]$$

(2.16)

In the saturation region,

$$|V_{DS}| \ge \alpha_G |V_{GS} + fV_{DS} - V_T^{CG}|$$

(2.17)

and

$$I_{DS} = \frac{\beta^{CG}}{2} \alpha_G (V_{GS} + fV_{DS} - V_T^{CG})^2$$

(2.18)

where

$$f = \frac{\alpha_D}{\alpha_G} \left( = \frac{C_D}{C_{FC}} \right) \tag{2.19}$$

### 2.4 ELECTRICAL CONDUCTION THROUGH THIN DIELECTRICS

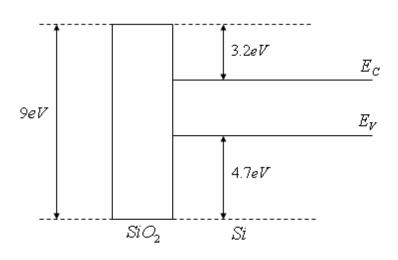

Electrical conduction through dielectrics can be divided into two main categories: bulk-limited conduction and electrode-limited conduction [5]. In bulk limited conduction, the electrical current is determined by the properties and characteristics of the dielectric itself, and is independent of the characteristics of the electrodes where the current is originating from. On the other hand, in electrode-limited conduction, the current is determined by the properties and characteristics of the electrodes where the current is originating from [13]. In the case of  $SiO_2$ , the conduction current is electrode-limited. That is because of the very large energy barrier of about 9eV and a high energy barrier of about 3.2eV at its interface with silicon. An example of bulk-limited conduction can be seen in the case of  $Si_3N_4$  which has an energy gap of only about 5eV and an energy barrier of 2eV at its interface with silicon. Another point to be noted is that since  $SiO_2$  has a smaller barrier for electrons in the conduction band (~3.2eV) compared to the holes in the valence band (~4.7eV), the current through  $SiO_2$  will be composed primarily of electron conduction [5].

The proof that the current through  $SiO_2$  is electrode limited was observed by Lezlinger et al. by studying the current-voltage characteristics of different electrode materials [13]. For a metal-oxide-silicon system, it was observed that for a positive bias on the metal, the current was independent of the metal used. At the same time, for a negative bias on the metal, the current was dependent on the particular metal used.

However, it has been shown in a study [14] that in an oxide containing a high density of charge traps, the conduction process can change from being electrode-limited

to being bulk-limited. Charge trapping is a form of oxide degradation that may be caused by high electronic field/current stress during the tunneling process.

Figure 2.28: Energy band diagram for the  $Si-SiO_2$  interface.

#### 2.4.1 FOWLER-NORDHEIM TUNNELING

Fowler-Nordheim tunneling is a field-assisted electron-tunneling mechanism [5]. It is the tunneling of electrons from the vicinity of the electrode Fermi level through the forbidden energy gap into the conduction band of the oxide in the presence of a high electric field [13]. Fowler-Nordheim tunneling is one of the most important injection mechanisms used in floating gate devices.

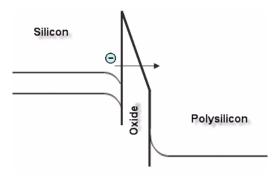

Due to the high electric field, the electrons in the conduction band of silicon see a steep triangular energy barrier as shown in figure 2.29. The magnitude of the barrier slope is directly proportional to applied electric field. The width of the energy barrier is, therefore, determined by the applied electric field. The height of the barrier is determined by the electrode material and the band structure of  $SiO_2$ . As the electric field is increased

by increasing the applied voltage at the control gate, the barrier slope becomes steeper and hence the barrier width is decreased.

Figure 2.29: Energy band representation of Fowler-Nordheim tunneling through thin oxides.

At sufficiently high fields, the width of the barrier becomes sufficiently small for the electrons to tunnel through the barrier from the silicon conduction band into the oxide conduction band [5]. In the Fowler-Nordheim regime, the value of the oxide electric field becomes larger than  $\frac{\Phi_b}{t_{ox}}$ , where  $\Phi_b$  is the barrier height and  $t_{ox}$  is the thickness of the tunnel oxide [16]. This mechanism was originally demonstrated by Fowler and Nordheim for electrons tunneling through a vacuum barrier and a modified version of that was later presented by Lezlinger and Snow for oxide tunneling. The Fowler-Nordheim current density is given by the following equation [5]:

$$J = \alpha E_{inj}^2 \exp(\frac{-E_C}{E_{inj}})$$

(2.20)

with

$$\alpha = \frac{q^3}{8\pi h \Phi_b} \frac{m}{m^*}$$

(2.21)

and

$$E_C = 4\sqrt{2m^*} \frac{\Phi_b^{\frac{3}{2}}}{3\hbar q}$$

(2.22)

where  $h = \text{Plank's constant} (4.13567 \times 10^{-15} \text{ eV.s})$

$\Phi_b$  = The energy barrier at the injecting interface (3.2eV for  $Si-SiO_2$ )

$E_{\it inj}$  = The electric field at the injecting interface (V/cm)

$q = \text{Electronic charge } (-1.602 \times 10^{-19} C)$

m =The mass of a free electron  $(9.109 \times 10^{-31} kg)$

$m^*$  = The effective mass of an electron in the band gap of  $SiO_2$  (0.42m [17])

$$\hbar = \frac{h}{2\pi}$$

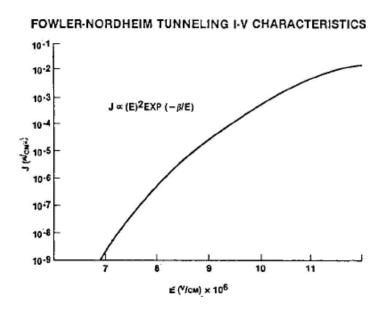

The I-V characteristic of Fowler-Nordheim tunneling is shown in figure 2.30 [18]. It can be seen that the current density is approximately exponentially dependent on the electric field within the oxide.

Figure 2.30: Fowler-Nordheim tunneling I-V characteristics.

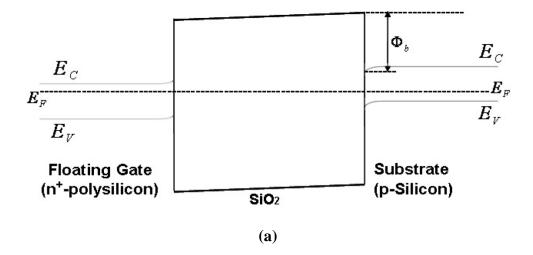

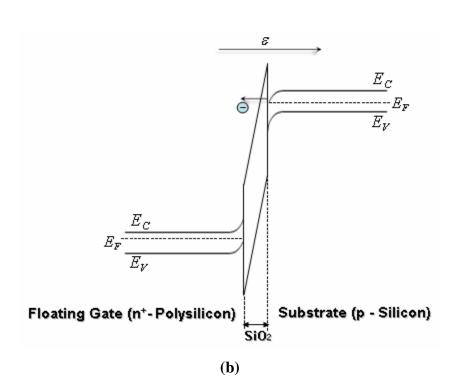

The energy band representation of the Floating Gate (polysilicon)-Tunnel Oxide  $(SiO_2)$ -Substrate (Si) system for a Flash memory cell at zero bias is shown in figure 2.31(a). The energy band representations of the Floating Gate (polysilicon)-Tunnel Oxide  $(SiO_2)$ -Substrate (Si) system during the program and erase operations are shown in figures 2.31(b) and 2.31(c), respectively.

Figure 2.31: Energy band representation of Fowler-Nordheim tunneling (a) at zero bias, (b) from substrate to floating gate (Program Operation), and (c) from floating gate to substrate (Erase Operation).

It is important to note that at very high voltages, the silicon surface will be degenerate n-type regardless of the bulk doping [13]. For an electrode with donor density of  $5 \times 10^{17} \, cm^{-3}$  and an oxide electric field of 7.5 MV/cm at the interface, the Fermi level is calculated to be about 0.25eV above the bottom of the silicon conduction band at the surface [15].

# Summary:

This chapter reviewed the two types of semi-conductor memories i.e. volatile semiconductor memory and non-volatile semiconductor memory while focusing on non-volatile semiconductor memory, Flash in particular. The basic differences between NOR Flash and NAND Flash, their respective advantages and disadvantages, and applications were briefly discussed. Finally, a detailed discussion of the structure and function and principles of operation of the NAND Flash memory cell were included in this chapter.

## CHAPTER 3: RELIABILITY ISSUES IN NAND FLASH MEMORY

Despite its numerous advantages, Flash memory suffers from the disadvantage of limited endurance [19]. There is a limit to the number of times the memory cells can be programmed and erased. High electric fields and, in turn, high current densities are applied to the tunnel oxide ( $SiO_2$ ) during the program/erase cycling of a Flash memory cell. Program/erase cycling is known to cause a fairly uniform wear-out of the cell performance, mainly due to tunnel oxide degradation, which eventually limits the endurance characteristics [20]. The intrinsic limitation of the tunnel oxide to withstand the high field/current induced stress is of significant importance as it directly translates to the endurance and reliability of the cell. The reliability and performance of a Flash memory cell are evaluated using device characteristics such as transient characteristics, endurance characteristics and retention characteristics [5].

The transient characteristics of a Flash memory cell include the shifting of the cell threshold voltage (threshold voltage modulation) as a function of time during programming and erasing. These characteristics, in turn, determine the values of the voltages and the time needed to program and erase the cell. The cell threshold voltage and, in turn, the program and erase time is altered by charge trapping in the tunnel oxide caused by the tunneling current passing through it during the program and erase operations.

The endurance of a Flash Memory cell is defined as the number of program and erase cycles that can be performed before the device breaks down due to damage or degradation of the tunnel oxide (owed to high field/current stress during Fowler-

Nordheim tunneling). Tunnel oxide degradation caused by Fowler-Nordheim tunneling has been discussed in detail in a later section.

The retention of a Flash Memory Cell is defined as the time it takes for the charge stored on the floating gate to be lost through leakage. The retention characteristic of a Flash Memory cell is, again, dependent on tunnel oxide degradation caused by Fowler-Nordheim tunneling during programming and erasing.

The combined effect of all the device characteristics i.e. transient, endurance, and retention define the reliability and performance of a Flash memory cell. Moreover, as mentioned before, these characteristics are strongly dependent on tunnel oxide degradation caused by high field/current induced stress during Fowler-Nordheim tunneling.

## 3.1 TUNNEL OXIDE DEGRADATION CAUSED BY FOWLER-NORDHEIM TUNNELING

Charge trapping in tunnel oxide caused by Fowler-Nordheim tunneling is one of the main causes of degradation in Flash memory cells and therefore one of the limiting factors in their long-term reliability [15]. Tunnel oxide degradation in a Flash Memory cell is much more significant as compared to a typical MOSFET because of the high field/current induced stress during Fowler-Nordheim tunneling. A typical Flash Memory cell is operated at voltages as high as 20V which is considerably higher as compared to the operating voltages of a typical MOSFET.

One of the most significant tunnel oxide degradation mechanisms is stress-induced charge trapping. Charge trapping is directly correlated to the threshold voltage shift during program/erase cycles in Flash memory cells [21] which leads to memory

window  $\Delta V_T (\Delta V_T = V_{programmed} - V_{erased})$  narrowing eventually causing the cell to reach end of its life-time. Charge traps are storage sites for electrons or holes in the oxide created due to degradation caused by high field/current induced stress during Fowler-Nordheim tunneling.

Charge trapping in the tunnel oxide causes transient, endurance and retention failures in Flash memory cells and therefore is an important phenomenon to understand in order to attempt improving the reliability and endurance of Flash memory cells.

#### 3.1.1 CHARGE TRAPPING IN TUNNEL OXIDE

Charges in  $Si - SiO_2$  systems can be broken down into four main categories [22]:

- 1- Interface trapped charge: This is the charge that is located at the  $Si-SiO_2$  interface. These are attributed to intrinsic dangling bonds, oxidation induced structural defects, and physically induced defects.

- 2- Fixed oxide charge: This is the charge located in the oxide near the  $Si SiO_2$  interface and is primarily positively charged. This charge originates from the oxidation process in which ionized silicon is not satisfied with an oxygen bond.

- 3- *Oxide trapped charge:* This is the charge located in the bulk of the oxide and can be negatively or positively charged, depending on the polarity of the charge trapped.

- 4- *Mobile ionic charge:* This type of charge occurs mainly due to ionic contamination such as Na<sup>+</sup>. A source of ionic contamination can be physical contact of the oxide with human skin, which contains Na<sup>+</sup> ions.

Among the above mentioned four categories, interface trapped charge and oxide trapped charge play the most significant role, when it comes to Fowler-Nordheim tunneling and reliability in Flash memory cells [22].

High field/current stressing during Fowler-Nordheim tunneling causes both positive and negative charge trapping in  $SiO_2$  [23]. The origin of charge traps is still not entirely understood and is a current area of interest for researchers. There have been a number of theories and models attempting to explain the phenomenon of charge trap generation in  $SiO_2$ . A few models are based on the relaxation of a bond close to the interface after a hole is captured and others based on the effect of hydrogen liberated by stress [15]. It is believed by researchers that trap generation is a consequence of Si-H bond breaking by high energy electrons [24].

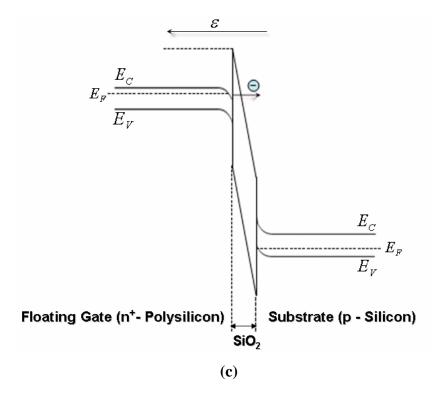

According to Jeno et al. [23], positive charge trapping is believed to be a consequence of direct tunneling between the anode and the trap sites near the  $Si - SiO_2$  interface and negative charge trapping is believed to be caused by the trapping of the injected electrons into the traps that pre-exist in the oxide as well as the traps that are generated during the high field/current stressing of the oxide. According to a study on hole trapping in  $SiO_2$  [25], it was suggested that during Fowler-Nordheim tunneling, some of the high-energy electrons will generate electron-hole pairs in the oxide (by impact ionization) and some of the generated holes will be trapped within the oxide. It was reported in [26] that electron trap sites are related to diffused water into the  $SiO_2$  film, which is in compliance with the conclusions made in [24]. It was shown that negative charge build-up in ultra-dry oxide is  $1/10^{th}$  that of wet oxide. The results in [26] suggest that the hydrogen contained in the oxide strongly affects the generation of

electron traps in  $SiO_2$  as shown in figure 3.1, which are in compliance with the theories and conclusions supported in [24].

Figure 3.1: Electron trap density as a function of Hydrogen concentration in the oxide.

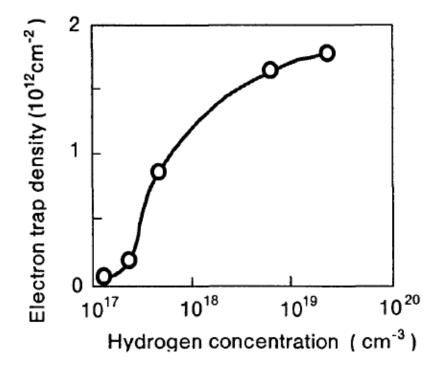

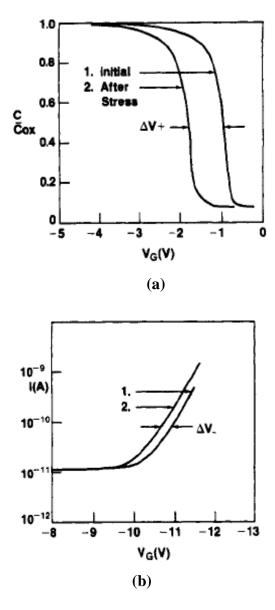

In an experiment conducted by Jeno et al. [23], Polysilicon- $SiO_2$ -Si capacitors were used to study high field/current stress induced charge trapping in  $SiO_2$ . C-V and I-V measurements were used to monitor the concentration as well as the centroid of the charge build-up in the Polysilicon- $SiO_2$ -Si capacitors. Capacitors with p-type substrates were subjected to high current stress for 10 seconds and the C-V and I-V measurements that were obtained are shown in figure 3.2.

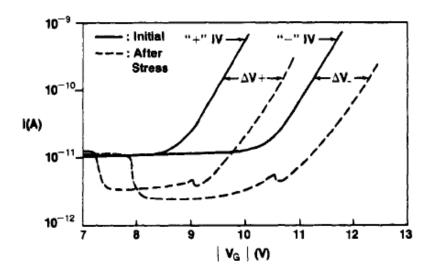

Figure 3.2: (a) C-V and (b) I-V measurements before and after the Polysilicon-SiO<sub>2</sub>-Si capacitors were stressed for a short time.

When gate stress was applied to the p-type capacitors, a negative shift in the C-V curve was observed indicating a net positive charge in the oxide. From the shifts in C-V i.e.  $\Delta V$  + and I-V i.e.  $\Delta V$  -, the centroid of the positive charges, X'+, was calculated using the following equation:

$$\frac{\Delta V -}{\Delta V +} = \frac{X' +}{d_{ox} - X' +}$$

(3.1)

where X'+ is measured from the  $Si-SiO_2$  interface. It was found that the value of X'+ was much smaller compared to the thickness of  $SiO_2$  suggesting that the positive charges are very close to the  $Si-SiO_2$  interface.

It was further observed that the concentration of the positive charges (which can be determined from the C-V or I-V shift using the calculated value of X'+) is independent of the oxide thickness and hence it is indeed an interface phenomenon. Figure 3.3 shows the concentration of positive charges plotted against various stress fields for different oxide thicknesses [23].

Figure 3.3: Positive charge concentration plotted against various stress fields for different oxide thicknesses.

It was further observed that the concentration of trapped positive charges increased exponentially with the applied stress field.

Overall, it was shown that positive charges are formed/trapped near the  $Si-SiO_2$  interface as a consequence of direct tunneling between the anode and the trap sites near the  $Si-SiO_2$  interface and that their concentration is independent of the thickness of the oxide.

As discussed above, initially a negative shift (due to positive charge trapping) of the C-V curve is seen. However, it was observed that after a short duration of continuous high field stress, the curve begins to shift in the positive direction and a net positive shift is seen relative to the initial curve [23]. The obvious deduction is that as more and more electrons get trapped in the oxide, the total number of negative charges trapped out number the total number of positive charges and the oxide at which point the oxide carries a net negative charge trapped.

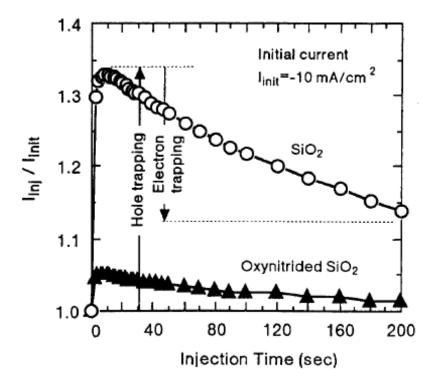

In order to study the concentration and centroid of the negative charges trapped in the oxide, it was made sure that the positive charges initially trapped in the oxide were neutralized. One of the methods that can be used is to apply a reversed gate stress. An initial set of positive and negative I-V curves were recorded. The I-V measurements were made at relatively low current levels (at least two orders of magnitude lower than the stressing current) to make sure a significant amount of electron trapping is not introduced in the oxide. The Polysilicon-  $SiO_2$ -Si capacitors were then stressed and positive and negative I-V curves were taken. It was observed that (given the positive charges are properly neutralized) the positive and negative I-V curves shifted by the same amount i.e.  $\Delta V + \Delta V - 1$ , implying that the centroid of negative charges, X' - 1, is at the center of the

oxide. Figure 3.4 shows the positive and negative I-V curves taken before and after stressing the capacitors for 10 minutes [23]. As in the case of positive charges, the concentration of the negative charges can be determined from the C-V or I-V shift using the calculated value of X'-.

Figure 3.4: Positive and negative I-V curves taken before and after the Polysilicon-SiO<sub>2</sub>-Si capacitors were stressed for a prolonged period of time (10 minutes).