# **UC Irvine**

# **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Fabrication of Metal-Semiconductor Heterostructures in Silicon Nanowires

#### **Permalink**

https://escholarship.org/uc/item/5hq1v3tx

#### **Author**

Yang, Luyun

# **Publication Date**

2015

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

# Fabrication of Metal-Semiconductor Heterostructures in Silicon Nanowires THESIS

submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE in Materials Science

by

Luyun Yang

Thesis Committee:

Assistant Professor Allon Hochbaum, Chair

Associate Professor Daniel Mumm

Associate Professor Regina Ragan

# TABLE OF CONTENTS

|                                                                | Page |

|----------------------------------------------------------------|------|

| LIST OF FIGURES                                                | iv   |

| ACKNOWLEDGMENTS                                                | viii |

| ABSTRACT OF THE THESIS                                         | ix   |

| 1. Introduction                                                | 1    |

| 1.1 History                                                    | 1    |

| 1.2 Basic concepts of thermoelectricity                        | 2    |

| 1.3 Theory of charge carrier and phonon transport at interface | 4    |

| 1.4 Thermoelectric materials                                   | 5    |

| 1.4.1 Bulk semiconductor alloys                                | 5    |

| 1.4.2 Nanostructured materials                                 | 5    |

| 1.5 Thermoelectric applications                                | 9    |

| 2. Methodology                                                 | 11   |

| 2.1 Fabrication of silicon nanowires                           | 11   |

| 2.1.1 Fabrication mechanism                                    | 11   |

| 2.1.2 Influencing factors                                      | 13   |

| 2.2 Silicide heterojunction                                    | 16   |

| 2.2.1 Mechanisms for increasing figure of merit (zT)           | 16   |

| 2.2.2 Metal-semiconductor contacts                             | 18   |

| 2.2.3 Nickel deposition                                        | 19   |

| 2.2.4 Formation of nickel silicide                             | 24   |

| 2.3 Experiment process                                         | 27   |

| 2.3.1 Silicon nanowire array synthesis                         | 27   |

| 2.3.2 Electroless nickel deposition in an aqueous solution     | 27   |

| 2.3.3 Electroless nickel deposition in organic solution        | 28   |

| 2.3.4 Schottky barrier formation (annealing)                   | 28   |

| 2.3.5 Etching residual nickel                                  | 28   |

| 2.3.6 Material characterization                                | 28   |

| 3. Results and discussion                                            | 30 |

|----------------------------------------------------------------------|----|

| 3.1 Fabrication of silicon nanowires                                 | 30 |

| 3.2 Approach to making metal-semiconductor heterostructures in SiNWs | 34 |

| 3.2.1 Electroless nickel deposition in an aqueous solution           | 34 |

| 3.2.2 Other ways to deposit nickel particles on SiNWs                | 41 |

| 3.2.3 Electroless nickel deposition in organic solution              | 44 |

| 4. Conclusions.                                                      | 49 |

| 5. References                                                        | 50 |

# LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Figure 1. 1 Schematic illustrations of a thermoelectric module for (a) power generation (Seebeck effect) and (b) active refrigeration (Peltier effect). (a) An applied temperature difference causes charge carriers in the material (electrons or holes) to diffuse from the hot side to the cold side, resulting in current flow through the circuit. (b) Heat evolves at the upper junction and is absorbed at the lower junction when a current is made to flow through the circuit.</li> <li>Figure 1. 2 Dependence of the Seebeck coefficient (S), electrical conductivity (σ), and the electronic (κ<sub>el</sub>) and lattice (κ<sub>latt</sub>) contributions to the thermal conductivity on the charge carrier concentration n, for a bulk material.</li> <li>Figure 1. 3 Three types of nano bulk structures: (a) single component nanocrystalline material, (b) bulk material with embedded nanoparticles, (c) multicomponent nanocrystalline material.</li> <li>Figure 1. 4 zT of typical n-type and p-type thermoelectric materials at different temperatures</li> </ul> | 2    |

| rigure 1. 4 21 of typical n-type and p-type thermoelectric materials at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

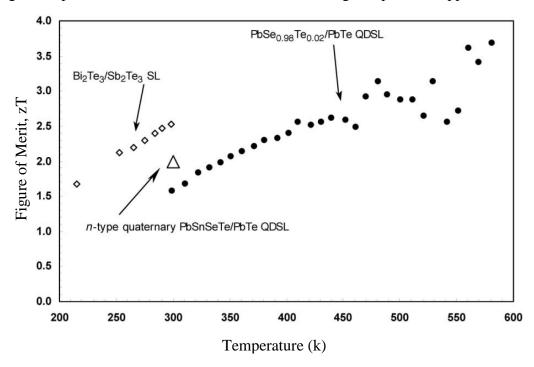

| Figure 1. 5 Thermoelectric figure of merit zT for Bi <sub>2</sub> Te <sub>3</sub> /Sb <sub>2</sub> Te <sub>3</sub> superlattices (SL), PbSnSeTe/PbTe quantum dot superlattices (QDSL), and PbSeTe/PbTe quantum dot superlattices (QDSL)  Figure 1. 6 Crystal structures of layered cobalt oxides. The CoO <sub>2</sub> block, common to each structure, is responsible for electric conduction. Except for Na <sub>x</sub> CoO <sub>2</sub> , the unit cell consists of the NaCl-type block and the CdI <sub>2</sub> -type CoO <sub>2</sub> block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6    |

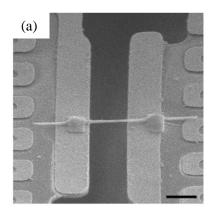

| <b>Figure 1. 7</b> (a) SEM image of a Pt-bonded EE Si nanowire (taken at 52° tilt angle). The Pt thin film loops near both ends of the bridging wire are part of the resistive heating and sensing coils on opposite suspended membranes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

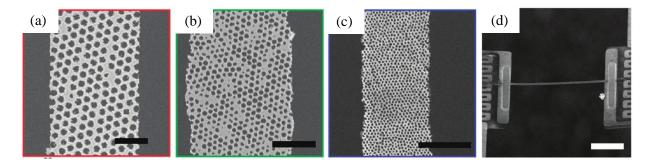

| Figure 1. 8 SEM image of (a) 350 nm pitch, (b) 140 nm pitch, (c) 55nm pitch, (D) SEM image of a single electroless etched NW bonded to two platinum bridges that act as a heater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

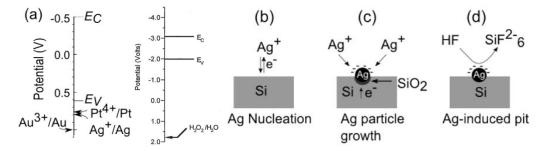

| <b>Figure 2. 1</b> (a) Qualitative diagram of the comparison of electrochemical electron energy levels of Si band edges and the redox systems, AuCl <sub>4</sub> /Au, PtCl <sub>6</sub> /Pt, Ag <sub>4</sub> /Ag, H <sub>2</sub> O <sub>2</sub> in HF solution. E <sub>C</sub> and E <sub>V</sub> are the conduction and valence band of Si, respectively. (b) - (d) Process of electroless silver deposition on a Si substrate immersed in HF/AgNO <sub>3</sub> solution [56]. After Ag nanoparticles are deposited on the Si surface, HF starts to etch the silicon substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Figure 2. 2 SEM images of silicon substrates etched with HF/AgNO <sub>3</sub> with Ag dendrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| structures [57, 59]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14   |

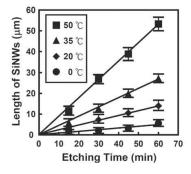

| <b>Figure 2. 4</b> Relationship of length of SiNWs and etching times at different temperatures <b>Figure 2. 5</b> (a) Schematic of the semiconductor host with metallic nanoinclusions. (b) Example of the calculated potential V(r) and the Schottky barrier. (c) Illustrates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| the concept of energy filtering: low energy electrons and phonons scatter strongly                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| due to the potential barrier, but high energy electrons are unaffected16                                                                   |

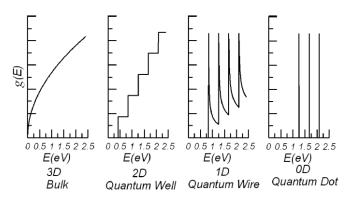

| <b>Figure 2. 6</b> Energy dependence of electron density of states in 3-, 2-, 1- and 0- dimensional                                        |

| crystals                                                                                                                                   |

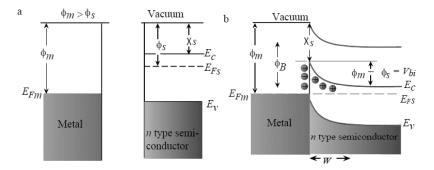

| Figure 2. 7 Energy band diagram of formation of a metal-semiconductor (n-type) (M-S)                                                       |

| contact. (a) before contact, (b) after the contact; the formation of a Schottky                                                            |

| barrier for the case where $\phi_m > \phi_S$ . The M-S interface shown in (b) is at                                                        |

| equilibrium                                                                                                                                |

| <b>Figure 2. 8</b> Relative abundance of the principal elements in the earth's crust, presented using                                      |

| a logarithmic scale [84]                                                                                                                   |

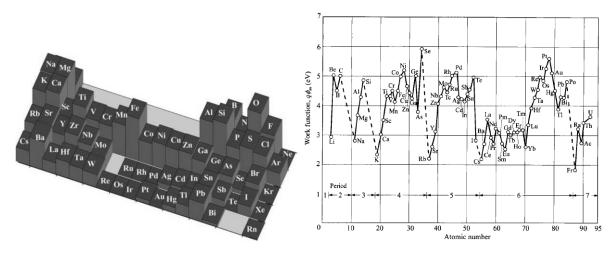

| <b>Figure 2. 9</b> Metal work function for a clean metal surface in a vacuum versus atomic number.                                         |

| Note the periodic nature of the increase and decrease of the work functions within each group [85]                                         |

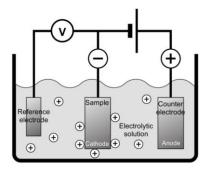

| Figure 2. 10 Schematic of an electrolytic cell used in the electrodeposition of silicon                                                    |

| nanowires                                                                                                                                  |

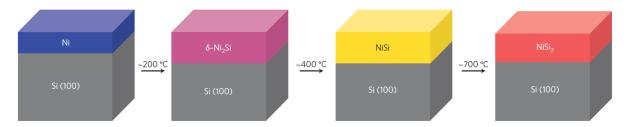

| Figure 2. 11 Formation of the different phases of nickel silicide. Nickel silicide typically                                               |

| observed for a thin Ni film deposited on a (100) oriented Si wafer. As the                                                                 |

| annealing temperature is increased for a thin film on (100) Si, $\delta$ -Ni <sub>2</sub> Si forms first,                                  |

| owing to its large interdiffusion coefficient; NiSi forms at a higher temperature                                                          |

| when all of the $\delta$ -Ni <sub>2</sub> Si is consumed, and remains stable up to ~700°C when the                                         |

| final phase, NiSi <sub>2</sub> begins to nucleate24                                                                                        |

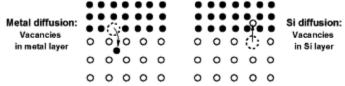

| Figure 2. 12 Simple schematic of vacancy generation depending on diffusing species.                                                        |

| Vacancies are located in the silicon layer if silicon diffuses and in the metal layer                                                      |

| if the metal diffuses24                                                                                                                    |

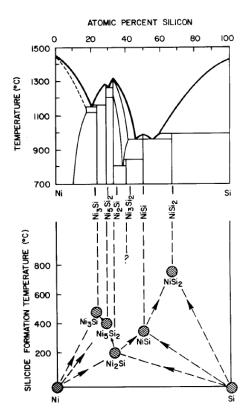

| Figure 2. 13 Formation map of thin film nickel silidides which shows the sequence of phases                                                |

| against their formation temperature. The phase diagram of Ni-Si, as shown on top                                                           |

| of the figure, is for comparison25                                                                                                         |

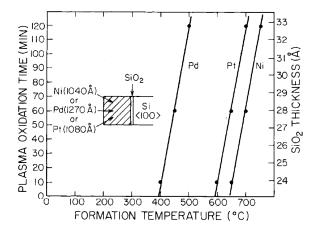

| <b>Figure 2. 14</b> Plot of plasma oxidation time vs. Ni <sub>2</sub> Si, Pd <sub>2</sub> Si and Pt <sub>2</sub> Si formation temperature. |

| The right hand scale shows the SiO <sub>2</sub> thickness corresponding to the oxidation                                                   |

| time. All samples were annealed for 30 min                                                                                                 |

| Figure 2. 15 Model of nickel silicide growth                                                                                               |

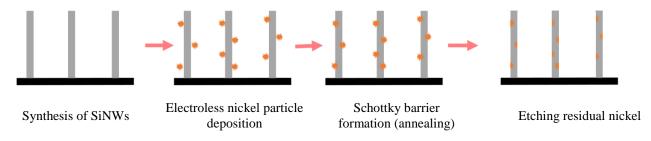

| <b>Figure 2. 16</b> Schematic illustration of the synthesis process of heterostructure SiNWs27                                             |

| <b>Figure 2. 17</b> Schematic illustration of annealing SiNW array samples in tube furnace28                                               |

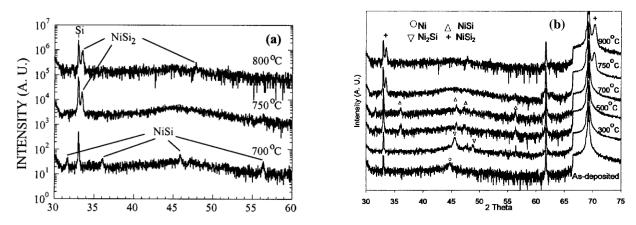

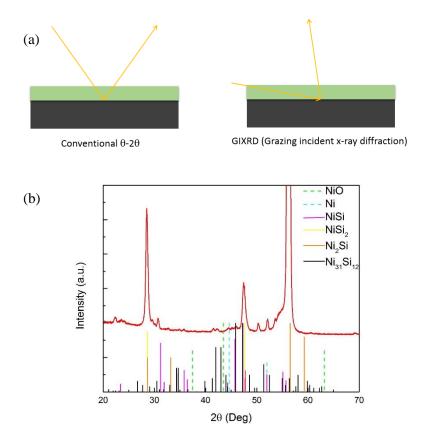

| <b>Figure 2. 18</b> XRD (Cu Kα) pattern of nickel silicide after annealing29                                                               |

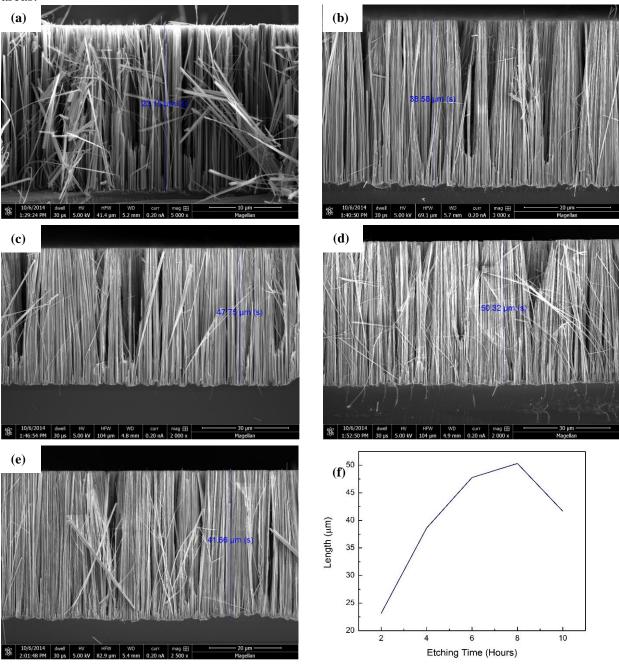

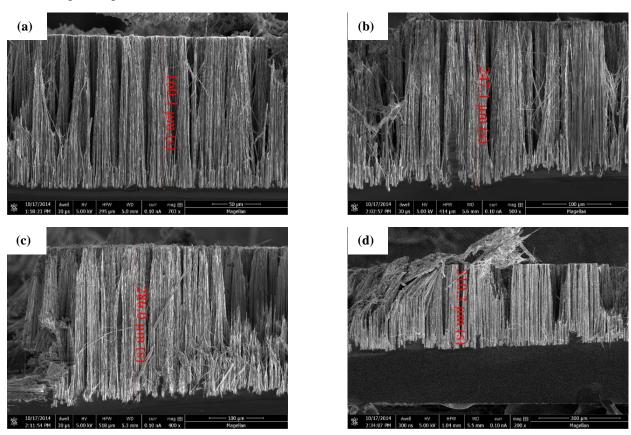

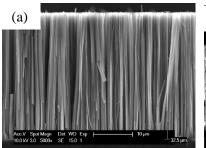

| Figure 3. 1 (a) – (e) cross-section SEM images of SiNWs with different lengths under                                                       |

| different etching times (2hrs, 4hrs, 6hrs, and 8hrs) in 100 mL 0.02M AgNO <sub>3</sub> +                                                   |

| 0.5M HF; (f) length of various SiNWs with different etching time (100 mL                                                                   |

| solution)                                                                                                                                  |

| Figure 3. 2 (a) – (d) cross-Section SEM images after two hours of etching silicon substrate                                                |

| with different lengths under different etching solution concentrations: 0.03M                                                              |

| AgNO <sub>3</sub> , 0.04M AgNO <sub>3</sub> , 0.05M AgNO <sub>3</sub> , and 0.06M AgNO <sub>3</sub> (100 mL solution)31                    |

| Figure 3. 3 (a) – (d) Cross-Section SEM images of SiNWs with longer length under varied                 |    |

|---------------------------------------------------------------------------------------------------------|----|

| etching time longer than 8 hours: 10hrs, 12hrs, 14hrs, 16hrs, in 400 mL 0.02M                           |    |

| AgNO <sub>3</sub> + 0.5M HF (400 mL solution)                                                           | 32 |

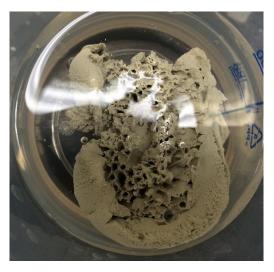

| Figure 3. 4 Large chunk of dendrite silver cloud. The holes on the silver cloud were caused             |    |

| by H <sub>2</sub> produced during etching process                                                       | 33 |

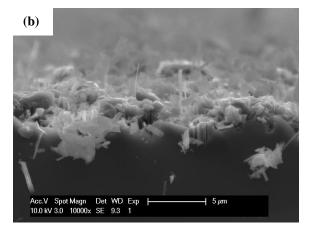

| Figure 3. 5 Morphology of SiNWs after removing dendrite silver during etching process.                  |    |

| The etching solution was 400 mL 0.02M AgNO <sub>3</sub> + 0.5M HF.                                      | 33 |

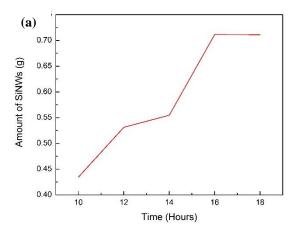

| Figure 3. 6 (a) weight of SiNWs produced after different etching times; (b) substrate after             |    |

| removing SiNWs, showing that almost all nanowires were removed                                          | 34 |

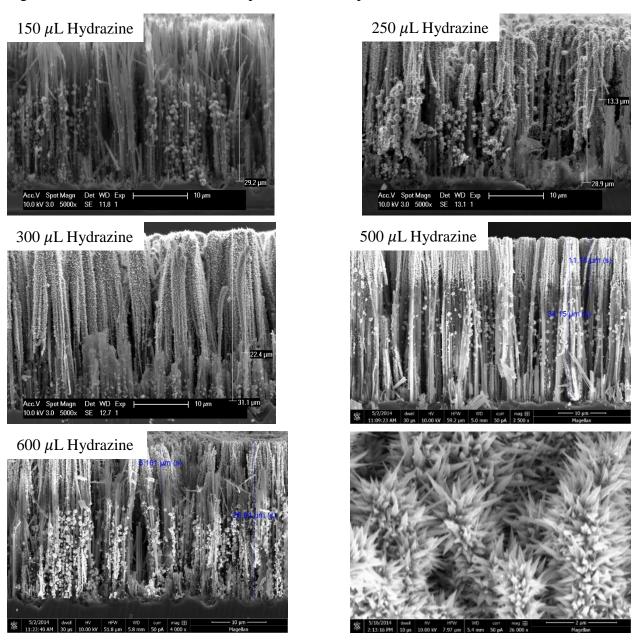

| Figure 3. 7 Morphology of nickel particles on SiNWs when deposited in different                         |    |

| concentrations of hydrazine (Table 3.1 #1, #3, #4, #5, #6)                                              | 35 |

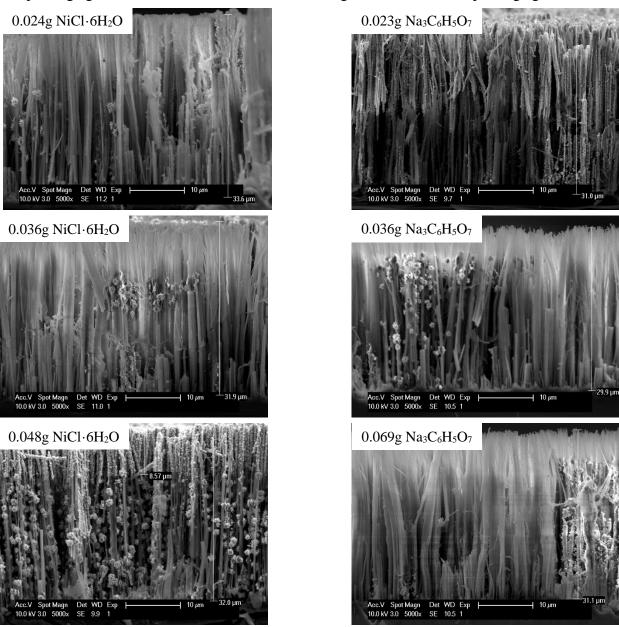

| Figure 3. 8 Morphology of nickel particles on SiNWs when deposited in different                         |    |

| concentrations of nickel chloride hexahydrate and sodium citrate dehydrate (ref.                        |    |

| Table 3.1 #7, #8, #9, #10, #11, #12)                                                                    | 36 |

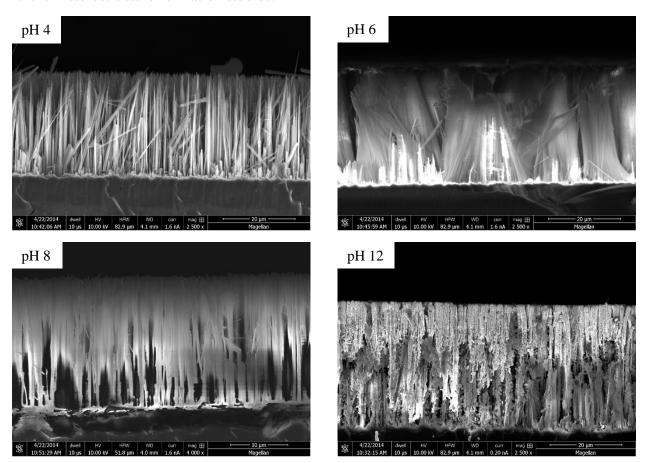

| Figure 3. 9 Morphology of nickel particles on SiNWs when deposited in different pH values               |    |

|                                                                                                         | 37 |

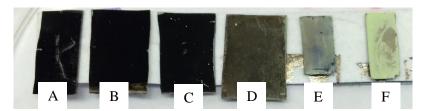

| <b>Figure 3. 10</b> Color of nickel deposition solution in different pH conditions. From left to right: |    |

| pH of 4, pH of 6, pH of 8 and pH of 12.                                                                 | 38 |

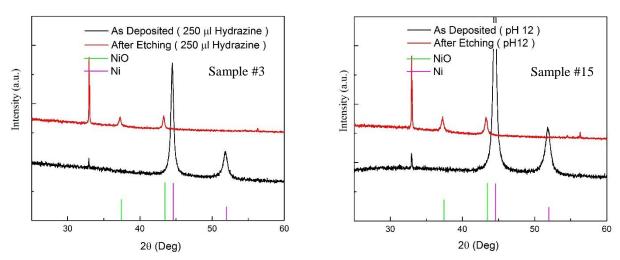

| <b>Figure 3.11</b> XRD (Cu Kα) pattern of SiNWs deposited with nickel particles; SiNWs after            |    |

| 550°C annealed for 15 min and etched for 1.5 hours in nickel etchant                                    | 38 |

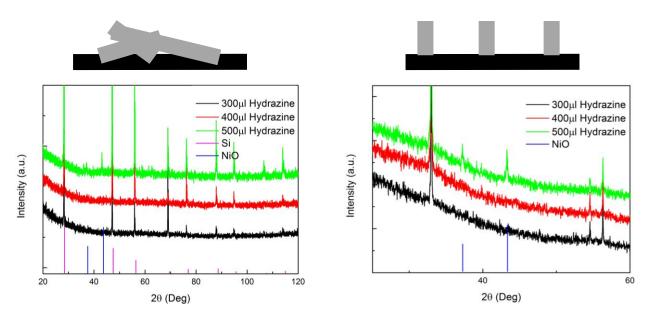

| <b>Figure 3. 12</b> XRD (Cu Kα) pattern of SiNWs from samples #4, #5, #6 (ref. Form 3.1). The           |    |

| patterns on the left are from SiNW powders which were scraped from a SiNW                               |    |

| array substrate; the patterns on the right are from SiNW array samples before                           |    |

| being scraped.                                                                                          | 39 |

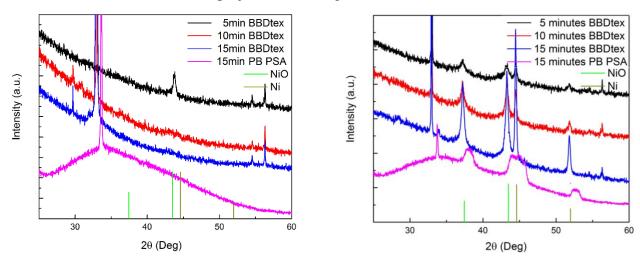

| <b>Figure 3.13</b> XRD (Cu K $\alpha$ ) pattern of SiNWs deposited under same condition but different   |    |

| annealing times and temperatures (left figure, 350°C, and right figure, 550°C)                          | 40 |

| Figure 3. 14 Color of samples changed depending on the thickness of NiO                                 |    |

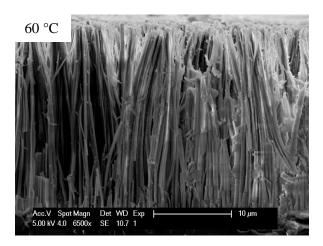

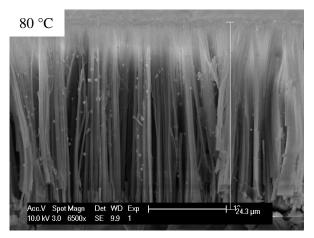

| <b>Figure 3. 15</b> SEM images of SiNWs after nickel deposition at temperatures lower than 90°C         |    |

| 11gure 3. 12 SEEM images of Sirviv's area meker deposition at temperatures lower than 50 °C             | 41 |

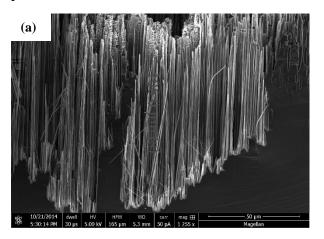

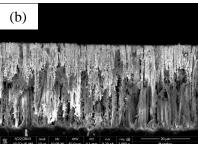

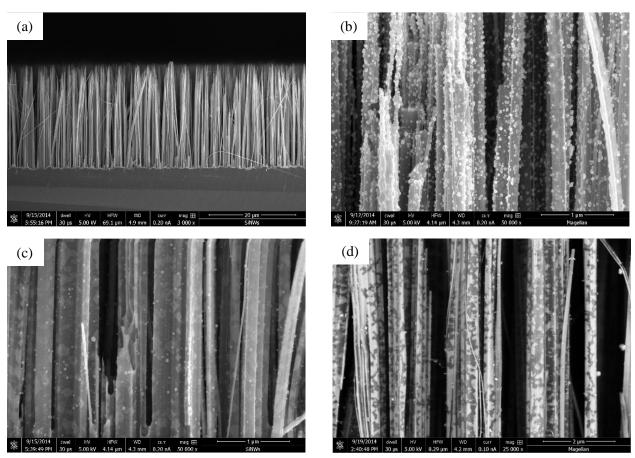

| <b>Figure 3.16</b> Morphology of SiNWs after different processes: (a) synthesis, (b) deposition in      | •  |

| Sample #15 condition (ref. Form 3.1), (c) nickel etching                                                | 41 |

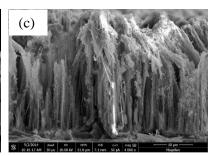

| <b>Figure 3. 17</b> (a) XRD (Cu Kα) pattern of SiNWs deposited by nickel electrodeposition at           |    |

| different time intervals (b) Nickel deposited by thermal evaporation. Both (a) and                      |    |

| (b) samples were annealed at 700°C for 1 hour.                                                          | 42 |

| Figure 3. 18 EDS pattern of electrodeposition on SiNWs                                                  |    |

| Figure 3.19 EDS pattern of thermal evaporation on SiNWs                                                 |    |

| Figure 3. 20 SEM image of sample deposited by E-beam from different angles                              |    |

| <b>Figure 3.21</b> Left: XRD (Cu Kα) pattern of SiNWs deposited by E-beam. Right: schematic             | +3 |

| illustration of nickel being deposited on SiNWs by E-beam                                               | 11 |

| • 1                                                                                                     | +4 |

| <b>Figure 3. 22</b> XRD (Cu Kα) pattern of SiNWs deposited by E-beam from different angles              | 11 |

| and annealed for different times                                                                        | 44 |

| <b>Figure 3. 23</b> (a) SiNW array chip lying flat on the bottom of a vial during deposition; (b) |

|---------------------------------------------------------------------------------------------------|

| SiNW array chips suspended in the middle of vial during deposition; (c) Nickel                    |

| mirror finish on the wall of vial45                                                               |

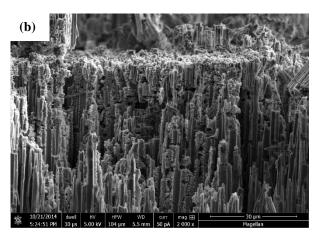

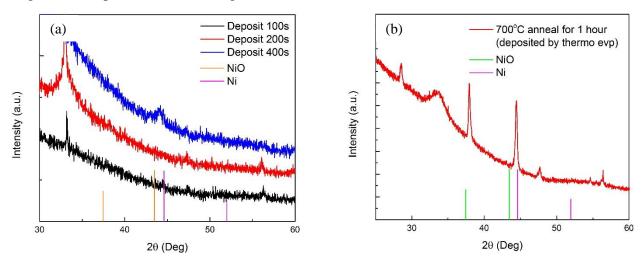

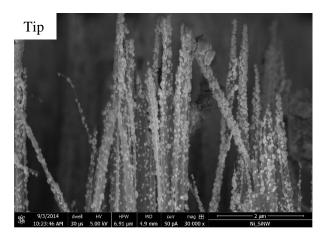

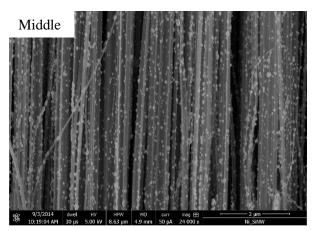

| Figure 3. 24 SEM images of SiNW array with nickel particles deposited in organic solution         |

| 45                                                                                                |

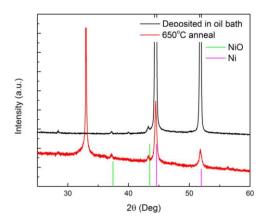

| <b>Figure 3. 25</b> XRD (Cu Kα) pattern of SiNWs deposited in organic solution using oil bath as  |

| the heat source46                                                                                 |

| Figure 3. 26 XRD (Cu Kα) pattern of SiNWs deposited in organic solution inside glove box          |

| using hot plate as heat source46                                                                  |

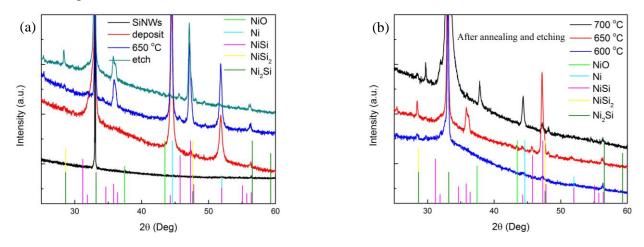

| Figure 3. 27 Sequence for nickel silicide phase formation by using organic solution to            |

| provide nickel source. (a) SiNWs before deposition; (b) nickel particles deposited                |

| on SiNWs; (c) SiNWs annealed at 650°C for one hour; (d) SiNWs with nickel                         |

| silicide phase after etching for 1.5 hours (back scattering electron)47                           |

| Figure 3. 28 Schematic illustration of the difference between conventional θ-2θ XRD               |

| analysis and GIXRD analysis48                                                                     |

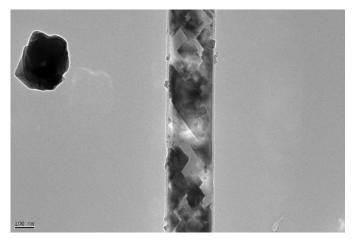

| Figure 3. 29 TEM image of nickel silicide heterostructure on a single nanowire48                  |

#### **ACKNOWLEDGMENTS**

This thesis represents not only my work, but also the guidance, encouragement, and support of many people who made it possible. Upon writing this paper, I realize that I am nearing the end of my journey as a Master of Science candidate. I still remember the first day I entered Engineering Hall 3121, how ecstatic I was when I got the keys for the laboratory, and how cautious and curious I was at the beginning. Gradually, I became familiar with fellow labmates and the workings of the laboratory. Now I can close my eyes and still hear the laughter of labmates, see the layout of the laboratory, and recall things being done there. One year is a short amount of time for research, but I have learned much during this short period.

First and foremost, I want to offer my sincerest gratitude to my advisor, Professor Allon Hochbaum, who has patiently guided and supported me through all my lab work and thesis preparation. I first met Professor Hochbaum when I took his class, Crystalline Solids, and I was captivated by his knowledge and enthusiasm. He always patiently answered our questions after class and during office hours. I am very thankful that Professor Hochbaum offered me the chance to join his lab. I thoroughly enjoyed this project assigned by him. I also discovered that Professor Hochbaum not only cares about his classroom and research, but also about our lives outside of class. He checked on my wellbeing when I broke my leg, assisted me with my job hunting, and help me navigate the road to graduation.

In the laboratory, I most frequently encountered Sun Jun Park. He was the first person who showed me around the lab and helped me get started with my first project. I did not realize how much Sun Jun helped me in the laboratory until I started helping others with their projects. Our occasional differences of opinion on experiment theory and processes gave me a broader understanding about my project. I also want to thank Trevor Cornell, a chemist, who always had many enlightening ideas and provided much help with various chemical experiments.

A big note of thanks goes to my family and friends for supporting me on my way to graduation. I appreciate my parents for continuing to support me financially, even though it has not been easy for them to allocate such a large portion of their finances. I hope that my accomplishments and future will make them proud. Aaron Wong and his father, Ken Wong, spent a great amount of time helping me. Aaron and I sat down daily to work on my thesis. He also helped with day-to-day necessities and encouraged me through difficult times. Ken Wong helped greatly with proofreading on short notice.

There are many more people whom I want to thank including Dr. Qiyin Lin in Calit2 and colleagues in Dr. Penner's lab and Dr. Law's lab. Unfortunately, I cannot list everyone here one by one, and it is hard to express my complete gratitude with only a few sentences. I dedicate this thesis to all whom I have had the pleasure of working with and I wish them continued success in their endeavors.

#### **ABSTRACT OF THE THESIS**

Fabrication of Metal-Semiconductor Heterostructures in Silicon Nanowires

By

Luyun Yang

Master of Science in Materials Science University of California, Irvine, 2015

Professor Allon Hochbaum, Chair

The increasing demand for fossil fuels and the need to reduce greenhouse gases require clean energy sources and more efficient utilization of energy. Thermoelectric materials provide a means toward achieving these goals since they convert heat, including waste heat, directly into an electric potential difference. Metal-semiconductor heterostructures can work as Schottky barriers in thermoelectric materials to increase thermoelectric efficiency.

In this project, nickel silicide phases were introduced into silicon nanowires (SiNWs) to build up the Schottky barrier. SiNW arrays were fabricated using a metal-assisted chemical process, creating SiNWs about 200 nm in diameter and 30µm in length. Different methods were adopted for nickel deposition: electroless nickel deposition, electro nickel deposition, E-beam deposition, and thermal evaporation. The samples were examined by X-ray diffraction (XRD) and scanning electron microscopy (SEM). The results show that depositing nickel on SiNWs in an aqueous solution without electricity is a simple way to deposit nickel particles, and the morphology of nickel particles depends on the concentration of the deposition bath. However, an aqueous solution will cause oxidation of the SiNWs and hinder the formation of nickel silicide. To solve this problem, depositing nickel on SiNWs in organic solutions inside an oxygen-free glove box is a way to prevent oxidation, and nickel can diffuse into silicon substrates easily via annealing when there no oxidation layer on the surface of SiNWs. The dominant phase formed in these samples is NiSi<sub>2</sub> after being annealed at 650°C for one hour in a tube furnace.

Key words: thermoelectric, heterostructure, nickel deposition, silicon nanowires

#### 1. Introduction

The emerging global need for energy production, conservation, and management has intensified interest in more effective means of power generation. Enhancements to existing energy supplies must come from a variety of renewable sources including solar, wind, biomass, and others. Another potential source of energy is electricity from heat sources utilized by thermoelectric materials. Heat can come from the combustion of fossil fuels, sunlight, or as a byproduct of various processes (e.g., combustion, chemical reactions, and nuclear decay). Therefore, thermoelectric materials can play a role in both primary power generation and energy conservation. A hot topic of discussion is how big this role is likely to be and the answer to this question depends solely on how efficient these materials are [1].

By no means should it be expected that thermoelectric energy conversion will solve the world's energy problems. However, it is hoped and expected that it will play a more increasing role than it has in the past and will be one of several technologies working together with other solutions to address energy efficiency issues. Thermoelectric modules are solid-state devices that directly convert thermal energy into electrical energy. This process is based on the Seebeck effect, which is the appearance of an electrical voltage caused by a temperature gradient across a material. The opposite is the Peltier effect which is the appearance of a temperature gradient upon the application of voltage [2].

#### 1.1 History

The term "thermoelectric effect" encompasses three separately identified effects: the Seebeck effect, Peltier effect, and Thomson effect.

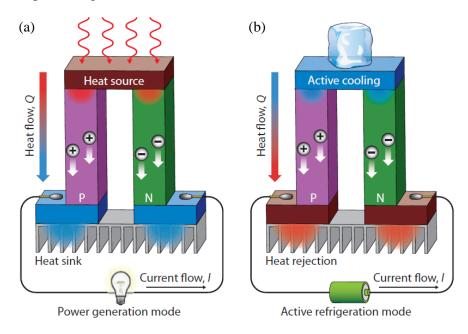

The first discovery of thermoelectric effects was in 1821, by T. J. Seebeck. He showed that an electromotive force could be produced by heating the junction between two different electrical conductors. The Seebeck effect can be demonstrated by making a connection between wires of different metals. The other ends of the wires should be applied to the terminals of a galvanometer or sensitive voltmeter. If the junction between the wires is heated, it is found that the meter records a small voltage. Seebeck found that the magnitude of the thermoelectric voltage is proportional to the difference between the temperature at the thermocouple junction and at the connections to the meter as shown in Figure 1.1(a) [3].

Thirteen years after Seebeck made his discovery, J. Peltier observed the second of the thermoelectric effects. He found that the passage of an electric current through a thermocouple produces a small heating or cooling effect depending on its direction as shown in Figure 1.1(b). The Peltier effect is quite difficult to demonstrate using metallic thermocouples since it is always accompanied by the Joule heating effect. Perhaps, one can do no better than show that there is less heating when the current is passed in one direction rather than the other [3].

It seems that it was not immediately realized that the Seebeck and Peltier phenomena are related to one another. However, this relationship was recognized by W. Thomson in 1855. By applying the theory of thermodynamics to the problem, he was able to establish a relationship between the coefficients that describe the Seebeck and Peltier effects. His theory also showed that there must be a third thermoelectric effect, which exists in a homogeneous conductor. This effect, now known

as the Thomson effect, consists of reversible heating or cooling when there is both a flow of electric current and a temperature gradient [4].

**Figure 1. 1** Schematic illustrations of a thermoelectric module for (a) power generation (Seebeck effect) and (b) active refrigeration (Peltier effect). (a) An applied temperature difference causes charge carriers in the material (electrons or holes) to diffuse from the hot side to the cold side, resulting in current flow through the circuit. (b) Heat evolves at the upper junction and is absorbed at the lower junction when a current is made to flow through the circuit [5].

In the 1920s, Abram Ioffe introduced semiconductors as promising thermoelectric materials. Although metals show a high value of the ratio of electrical to thermal conductivity  $(\sigma/\kappa)$ , the majority of them have a Seebeck coefficient S which does not exceed a few mV/K. In semiconductors S can reach values of up to one or more mV/K, but the ratio of the electrical to the thermal conductivity is smaller than in metals. However, this ratio can be easily manipulated by addition or removal of dopants. This implies that semiconductors are superior to metals in thermoelectric applications [6, 7].

# 1.2 Basic concepts of thermoelectricity

Thermoelectric device performance relies directly on the temperature gradient ( $\Delta T$ ) and an intrinsic material parameter, the thermoelectric figure of merit (zT). For power generation, the thermoelectric efficiency  $\eta$  is defined by combining the Carnot efficiency ( $\Delta T/T_{hot}$ ) and the figure of merit zT as shown in Equation 1.1.

$$\eta = \frac{\Delta T(\sqrt{1+zT_{avg}}-1)}{T_{hot}(\sqrt{1+zT_{avg}}+\frac{T_{cold}}{T_{hot}})}$$

(1.1)

where  $T_{hot}$  and  $T_{cold}$  are the temperatures of the hot and cold ends in a thermoelectric module and  $\Delta T$  is their difference. The term  $\sqrt{1 + zT_{avg}}$  varies with the average temperature  $T_{avg}$ . This equation indicates that an increase in efficiency requires both high zT values and a large

temperature gradient across the thermoelectric material. Thermoelectric devices currently available have a zT of 1 and will operate at an efficiency  $\eta$  of only about 5-6%. By increasing zT by a factor of 4, and depending on  $\Delta T$ , the predicted efficiency  $\eta$  increases to 30%, a highly attractive prospect.

These properties define the dimensionless thermoelectric figure of merit zT:

$$zT = \frac{s^2 \sigma T}{k} \tag{1.2}$$

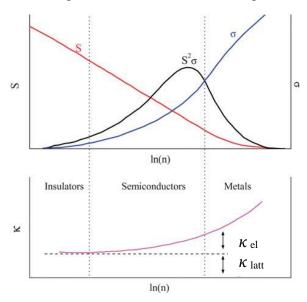

where T is the temperature. Producing high zT thermoelectric materials requires achieving simultaneously high electrical conductivity  $\sigma$ , high Seebeck coefficient S, and low thermal conductivity k in one solid [8]. These parameters are determined by the details of the electronic structure and scattering of charge carriers (electrons or holes), and thus are not independently controllable (ref. Figure 1. 2). The quantity  $s^2\sigma$  is called the power factor (PF) and is the key to achieving high performance. A large PF means that a large voltage and a high current are generated. The thermal conductivity  $\kappa$  has a contribution from lattice vibrations,  $\kappa$  latt, called the lattice thermal conductivity. Thus,

$$\kappa = \kappa_{el} + \kappa_{latt} \tag{1.3}$$

where  $\kappa$  el is the carrier thermal conductivity. As  $\kappa$  el is directly related to the electrical conductivity through the Wiedemann-Franz relationship ( $\kappa$  el = L<sub>0</sub>  $\sigma$ T),  $\kappa$  el and PF cannot be varied independently. Intuitively, the thermal conductivity must be low as a large  $\Delta T$  must be maintained; a large thermal conductivity will short the thermal circuit. zT also shows an opposing dependence on charge carrier density, while a large Seebeck coefficient also requires a high density of states at the Fermi level. As a consequence, the most promising thermoelectric materials are narrow bandgap semiconductors with charge carrier densities in the range of  $10^{19}$ – $10^{21}$  cm<sup>-3</sup>.

**Figure 1. 2** Dependence of the Seebeck coefficient (S), electrical conductivity ( $\sigma$ ), and the electronic ( $\kappa_{el}$ ) and lattice ( $\kappa_{latt}$ ) contributions to the thermal conductivity on the charge carrier concentration n, for a bulk material [9].

#### 1.3 Theory of charge carrier and phonon transport at interface

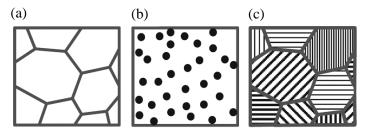

Theoretical studies of phonon transport in superlattices show that reduction in lattice thermal conductivity does not need a well-defined geometry or a perfect interface at an atomic level. The only requirement is having a high density of interfaces, which is present in nano bulk structures. Therefore, to enhance the zT, the phonons have to be scattered more efficiently than charge carriers, which means the size of nanostructures should be smaller than the phonon mean free path and larger than the charge carrier mean free path. In practice, charge carriers have a narrower mean free paths than that of phonons. The interface spacing below which the electrical conductivity is reduced considerably can be estimated through the spectrum of the mean free path. Continued reduction in characteristic lengths in nanostructures has led to increasing importance of interfaces in transport properties of materials. In fact, a large portion of the advances in enhancing zT for nanostructured materials comes from the beneficial effects of the interfaces [10].

In a nano bulk material, grains and interfacial structures may have three distinct types as depicted in Figure 1.3. Type 1 (Figure 1.3a) is a nanocrystalline structure with a single material composition. Type 2 (Figure 1.3b) consists of embedded nanoparticles inside the lattice. Figure 1.3c is a nanocrystalline structure made from a mixture of two or more different materials or phases. In this structure the grains and/or the grain boundary regions are made from different materials. Experimentally, a nano bulk thermoelectric material may have a structure similar to any of these types or a combination of them [11]. For example, a peak zT of 1.4 at 100°C was achieved in a p-type nanocrystalline Bi<sub>0.5</sub>Sb<sub>1.5</sub>Te<sub>3</sub> bulk alloy using the type 1 methods to enhance the efficiency of thermoelectric materials 1 interface, which separates single phase crystallites [12]. Also, the p-type PbTe nanostructured bulk with SrTe precipitates, which demonstrated a zT value of 2.2 at 615°C, took advantage of the combination of Type 1 and 2 structures to more effectively scatter heat-carrying phonons across the integrated length scales [13]. A combination of Type 3 with 1 and/or 2 can make various other structures such as core–shell nanoparticle doped structures, or nanocrystalline structures with embedded nanoparticles [14].

**Figure 1. 3** Three types of nano bulk structures: (a) single component nanocrystalline material, (b) bulk material with embedded nanoparticles, (c) multicomponent nanocrystalline material [11]

The interface potential can also scatter only low energy carriers, which reduce their contribution. This phenomenon is called energy filtering [11]. The interface potential normally comes from the Schottky barriers between metal and semiconductor phases. In a sample, the minority carriers which have lower energy are affected by fabricating a nanostructure which scatters them more strongly than the majority carriers. The successful implementation of this strategy has been reported for InGaAs/InGaAlAs superlattice [15] and PbTe-based nanostructured materials [16, 17].

#### 1.4 Thermoelectric materials

#### 1.4.1 Bulk semiconductor alloys

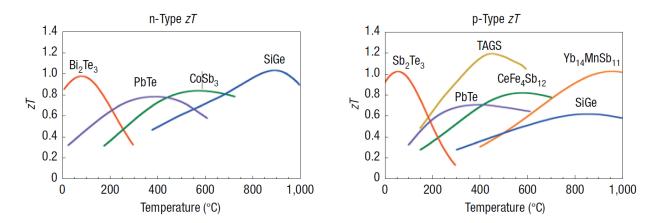

Today, bulk semiconductor alloys are the most widely used thermoelectric materials and the materials with the highest efficiency,  $zT \approx 1$  [18]. Bulk semiconductor alloys are mainly found in three semiconductor compound families: (1) the V-VI compounds based mainly on  $Bi_2Te_3$ , which are used for applications in the room temperature range; (2) the IV-VI compounds based on PbTe, used in the 500 - 900K temperature range and (3) IV-IV compounds based on SiGe alloys. Neither Si nor Ge is a good thermoelectric material [19]. Although they have high electric conductivity, they also have high thermal conductivity, 113 and 63 W/mK at 300K for silicon and germanium, respectively [20], which leads to low zT. SiGe alloy has a high zT at high temperature (>900 K). Figure.1.4 shows the zT of typical n-type and p-type thermoelectric materials at different temperatures [16].

Figure 1. 4 zT of typical n-type and p-type thermoelectric materials at different temperatures [16]

By far the most widely used thermoelectric materials are alloys of Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub>. Bi<sub>2</sub>Te<sub>3</sub> was first investigated as a material of great thermoelectric promise in the 1950s. For near-room-temperature applications, such as refrigeration and waste heat recovery up to 200 °C, Bi<sub>2</sub>Te<sub>3</sub> alloys have been proven to possess the greatest figure of merit for both n- and p-type thermoelectric systems [21].

#### 1.4.2 Nanostructured materials

The main advantage of low-dimensional materials is that their size can be made smaller than the mean free path of phonons, but larger than that of electrons and holes. This brings about a reduced  $\kappa$ , without compromising the other zT parameters [22]. These materials may be classified as nanotubes, nanowires, nanorods, nanoparticles, quantum well, super lattices, and ultra-thin films.

#### Carbon Nanotubes

A carbon nanotube (CNT) is composed of a graphene sheet formed into a seamless cylinder. There are two types of nanotubes, single-walled nanotubes (SWNT) and multi-walled nanotubes (MWNT), with the latter composed of concentric SWNTs. Carbon nanotubes are rich in charge carriers with  $\sigma = 10^6$  S/m, S of 80  $\mu$ V/K for single MWNTs at 300 K [23], and 40  $\mu$ V for SNWTs

[24]. However, they exhibit extremely high  $\kappa$ , 3000 W/mK for MWNT and up to  $10^4$  W/mK for SWNT. This results in a very low zT of  $6.4 \times 10^{-4}$  for MWNTs and  $4.8 \times 10^{-4}$  for SWNTs. In order to decrease the  $\kappa$ , an approach to the nanotube composition has been considered. Introduction of  $C_{60}$  molecules within the core of SWNTs could act as a typical way to a reduced  $\kappa$  [25].

#### **Superlattices**

Superlattices consist of alternating thin layers of different materials stacked periodically. The lattice mismatch and electronic potential differences at the interfaces and resulting phonon and electron interface scattering and band structure modifications can be exploited to reduce phonon heat conduction while maintaining or enhancing the electron transport [19]. Superlattices are anisotropic. Different mechanisms to improve zT along directions both parallel (in-plane) and perpendicular (cross-plane) to the film plane have been explored. Along the in-plane direction, potential mechanisms to increase zT include quantum size effects that improve the electron performance by taking advantage of sharp features in the electron density of states [26], and reduction of phonon thermal conductivity through interface scattering [27]. Along the cross-plane direction, one key idea is to use interfaces for reflecting phonons while transmitting electrons (phonon-blocking/electron transmitting) [28], together with other mechanisms, such as electron energy filtering [29] and thermionic emission [30], to improve electron performance.

Several groups reported in recent years enhanced zT in various superlattices such as Bi<sub>2</sub>Te<sub>3</sub>/Sb<sub>2</sub>Te<sub>3</sub>, as well as Bi<sub>2</sub>Te<sub>3</sub>/Bi<sub>2</sub>Se<sub>3</sub> [31] and PbSeTe/PbTe quantum dot superlattices [32] (ref. Figure 1.5). The large improvements observed in these materials systems, compared with their parent materials, are of great importance for both fundamental understanding and practical applications.

**Figure 1. 5** Thermoelectric figure of merit zT for Bi<sub>2</sub>Te<sub>3</sub> /Sb<sub>2</sub>Te<sub>3</sub> superlattices (SL), PbSnSeTe/PbTe quantum dot superlattices (QDSL), and PbSeTe/PbTe quantum dot superlattices (QDSL) [31][32]

#### Layered Co oxides

Oxides seem hopelessly poor as thermoelectric materials. First, most of them show high lattice thermal conductivity due to a high sound velocity, because light oxygen ions are tightly bound. Second, the electrical conductivity is usually lower than that of other semiconductors [33]. However a new window has opened to oxide thermoelectrics since the discovery in 1997 of a large power factor in a single crystal sample of the layered cobalt oxide  $Na_xCoO_2(NaCo_2O_4)$  [34]. The crystal showed a low resistivity of  $200~\mu\Omega$ cm (5,000 S/cm) with a large thermopower of  $100~\mu$ V/K at room temperature along the in-plane direction. The room-temperature power factor is as large as that of  $Bi_2Te_3$ , which clearly indicates that some oxides can be thermoelectric materials. Later, Fujita et al. [35] found a reasonably low thermal conductivity (50 mW/cmK at 800K) for a single-crystal sample, and evaluated zT to be unity at 1,000K. Ohtaki et al. [36] and Ito et al. [37] reported zT  $\approx 0.8$  at 1,000K, even in polycrystalline samples of  $Na_xCoO_2$ .

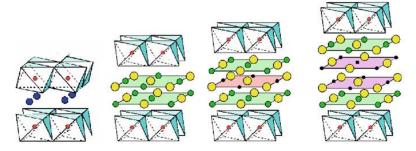

Oxide thermoelectrics have been extensively investigated in the last decade, and a number of new oxides have been synthesized and examined as possible candidates for oxide thermoelectric materials [38]. Figure 1.6 shows the crystal structures of various layered cobalt oxides. All of them have in common the CdI<sub>2</sub>-type CoO<sub>2</sub> block, which alternately stacks with various block layers along the c axis. The CdI<sub>2</sub>-type CoO<sub>2</sub> block is hexagonal, whereas the various block layers, except for the Na layer, crystallize in the NaCl structure with tetragonal symmetry. Their crystal structure is an alternate stack of square and triangle sheets, which causes lattice mismatch at the interface between the blocks.

**Figure 1. 6** Crystal structures of layered cobalt oxides. The  $CoO_2$  block, common to each structure, is responsible for electric conduction. Except for  $Na_xCoO_2$ , the unit cell consists of the NaCl-type block and the  $CdI_2$ -type  $CoO_2$  block [33].

#### Silicon Nanowires

Heavily doped bulk silicon,  $10^{19}$  cm<sup>-3</sup>, has a very poor zT value which approaches 0.01 at 300 K [39] due to a high thermal conductivity  $\kappa = 150$  W/mK at room temperature [40]. However, with reduced dimensions, an increase in zT is expected because the mean free path is reduced due to phonon-boundary scattering.

Hochbaum et al. [41] obtained zT values of 0.60 at room temperature in wires that were approximately 50 nanometers in diameter. They synthesized p-type SiNWs by using a metal-assisted electroless etching method and a vapor-liquid-solid (VLS) grown gold-catalyzed method. The electroless etched SiNWs were rougher than the VLS grown SiNWs, with the former having an average surface roughness of the order of several nm (1-5 nm), which had a lower thermal conductivity  $\kappa$ . To measure the thermal conductivity, a single NW was suspended between two

membranes, one acting as a heater and the other as a heat sink, as shown in Figure 1.7(a) According to Chen et al. [42], the thermal conductance of individual single crystalline silicon nanowires is related to the diameter of the nanowire, which can be explained by the fact that the mean free path is proportional to the diameter and is independent of the phonon frequency.

**Figure 1. 7** (a) SEM image of a Pt-bonded EE Si nanowire (taken at 52° tilt angle). The Pt thin film loops near both ends of the bridging wire are part of the resistive heating and sensing coils on opposite suspended membranes [41].

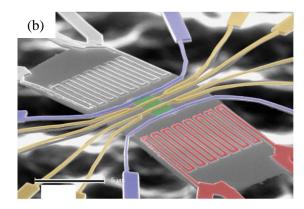

(b) The central green area is the Si nanowire array, which is not resolved at this magnification. The four-lead yellow electrodes are used for thermometry to quantify the temperature difference across the nanowire array. The thermal gradient is established with either of the two Joule heaters (the right-hand heater is colored red). The yellow and blue electrodes are combined to carry out four-point electrical conductivity measurements on the nanowires [42].

Boukai et al. [8] measured the thermal characteristics of ~100 p-SiNWs in parallel. They reported a zT $\approx$ 1 at 200 K, and their measured  $\kappa=0.99$ W/mK is below the theoretical limit for silicon. NWs were fabricated by the superlattice nanowire pattern transfer (SNAP) method. The atomic control over the layer thickness of the superlattice allows manipulation in the spacing and width of the nanowires. NW arrays of several micrometers in length were prepared with lateral width  $\times$  thickness dimensions of 10 nm  $\times$  20 nm and 20 nm  $\times$  20nm. Figure 1.7(b) shows a scanning electron micrograph (SEM) image of the suspended platform used to measure the thermal characteristics of the SiNWs. This is indicated in the figure by the green color.

Tang et al. [43] studied a different form of nanostructure, "holey" silicon. High density nanoscopic holes of p-Si with dimensions of 350, 140 and 55 nm were created in thin 100 nm single crystalline silicon membranes, either by nanosphere lithography or block co-polymer lithography. Holey silicon nanoribbons were characterized by a micro-electromechanical system device, shown in Figure 1.8(d). SEM images of the nanoribbons of 350 nm, 140 mm, and 55 nm are shown in Figure 1.8(a) - (c). The temperature dependence of zT for the 55 nm ribbons achieved a maximum value of ~0.4 was achieved at 300 K. This corresponds to a 40 times increase in the zT compared to their parent bulk Si.

**Figure 1. 8** SEM image of (a) 350 nm pitch, (b) 140 nm pitch, (c) 55nm pitch, (D) SEM image of a single electroless etched NW bonded to two platinum bridges that act as a heater [43]

## 1.5 Thermoelectric applications

There are mainly two types of commercially available multicouple thermoelectric devices. Type A was originally designed for cooling applications and possesses significant inter-thermoelement separation. In this type of device, n- and p-type semiconductor thermoelements are connected electrically in series by highly conducting metal strips and sandwiched between thermally conducting and electrically insulating plates. Type B has been developed more recently for power generation and is densely constructed with very small inter-thermoelement separation to increase the power-per-area. However, the conducting metal strips in the latter device are not insulated and the module cannot be attached directly to an electrical conductor, such as an aluminum heat sink [44].

Thermoelectric devices cannot be used independently. They should be connected to heat exchangers to dissipate heat, forming the basis of thermoelectric systems. The development of thermoelectric systems has been ongoing for many years. Thermoelectric systems are usually small heat pumps or power generators, which follow the laws of thermodynamics in the same manner as mechanical heat pumps, vapor compressors associated with conventional refrigerators, and other apparatus used to transfer energy [45].

Thermoelectric devices offer several distinct advantages over other technologies: Thermoelectric devices have no moving parts and, therefore, need substantially less maintenance. Life testing has shown the capability of thermoelectric devices to exceed 100,000 hours of steady state operation. Thermoelectric devices contain no chlorofluorocarbons or other materials that may require periodic replenishment. Also, the direction of heat-pumping in a thermoelectric system is fully reversible. Changing the polarity of the DC power supply causes heat to be pumped in the opposite direction - a cooler can then become a heater. Precise temperature control to within  $\pm 0.1\,^{\circ}$ C can be maintained using thermoelectric devices and the appropriate supporting circuitry. Thermoelectric devices can function in environments that are too severe, too sensitive, or too small for conventional refrigeration. Thermoelectric devices are not position-dependent. Due to all the above advantages, thermoelectric devices have found very extensive applications in the past decade in wide areas, such as military, aerospace, instrument, industrial, and commercial products. These applications can be classified into three categories: coolers (or heaters), power generators, and thermal energy sensors [46].

#### Applications of thermoelectric devices as coolers

Thermoelectric coolers are widely employed in microelectronics to stabilize the temperature of laser diodes, to cool infrared detectors and charge-coupled devices, and to reduce unwanted noise in integrated circuits. In addition to cooling electronic devices, thermoelectric devices are widely used in other niche applications where the cooling demands are not too great (such as portable cooler boxes) or instances in which the energy cost is not the main consideration (such as military applications). However, their applications in cooling large thermal capacity components or spaces have been limited, due to the relatively low efficiency and high energy cost [45].

For commercial silicon chips, efficient hot spot removal is key for future generations of IC chips. Circulated liquid cooling allows for moving the heat sink away from the processor, thus allowing for a larger heat sink surface area [11]. However, reliability is a big concern, for example, if the system leaks coolant. The other widely used technology is thermoelectric module cooling. Thermoelectric cooling is a silent and environmentally-friendly solution. However, the hot spots in microprocessors are normally on the order of 300-400 µm in diameter, so even the smallest commercial cooling module is still too large to be used for spot cooling. In addition, the introduction of silicon stacked chips and three-dimensional (3D) chips can lead to even smaller and hotter spots. Nanoscale coolers with high efficiency will be key enablers for removing small hot spots in IC chips and for improving future IC thermal management [47].

#### Application of thermoelectric devices for power generation

Electrical power for small, independent and wireless systems for remote sensing, control, safety surveillance, and metering comes mainly from batteries. Since battery life is limited, battery-operated systems have to be maintained or replaced after a few years. Furthermore, batteries contain chemical substances that are harmful to the environment. For this reason, the disposal of battery-operated systems has to be controlled, which can be an expensive procedure. One common alternative is the use of solar cells, such as those used in calculators and watches. In low-light or no-light applications, small temperature differences which are present can be used to operate a small thermoelectric generator. Therefore, small, inexpensive, and efficient thermoelectric generators are gaining importance as replacements for batteries in many systems [48]. One actual example is a small preamplifier and a sensor control system powered by a thermoelectric generator generating an electrical power of 1.5  $\mu$ W from a temperature difference of 10 °C [48].

For low power generation, the low efficiency of thermoelectric generators is not a main drawback. But for high power generation, low efficiency is a disadvantage and has limited its application to specialized areas. In recent years it has been realized that in situations where the supply of heat is inexpensive or free, as in the case of waste heat, efficiency of the thermoelectric generation system is not an overriding consideration. The use of waste heat as an energy source, particularly at temperatures below 140°C, substantially increases the commercial competitiveness of this method of generating electrical power [49].

Currently available is a standard device consisting of 71 thermocouples in a 75 mm<sup>2</sup> package, producing 19 W (www.hi-z.com). The world's largest supplier of thermoelectric generators, Global Thermoelectric Inc., provides thermoelectric generators ranging in output from 15 to 550 W, in module sizes from 508 mm  $\times$  279 mm  $\times$  483 mm to 1549 mm  $\times$  1549 mm  $\times$  1016 mm (www.globalte.com).

# 2. Methodology

In novel nanoscale thermoelectric materials, silicon nanowires (SiNWs) are appealing choices because of their small sizes and ideal interface compatibility with conventional Si-based technology [50-52]. In SiNWs, the electrical conductivity and electron contribution to the Seebeck coefficient are similar to those of bulk silicon, but they exhibit a 100-fold reduction in thermal conductivity [50], showing that electrical and thermal conductivities can be decoupled. Recent experiments have provided direct evidence that an approximately 100-fold improvement of thermoelectric figure of merit zT values over bulk Si is achieved in SiNWs over a broad temperature range. This large increase of zT is attributed to the decrease of thermal conductivity. This has raised the exciting prospect that SiNWs can be used as novel nanoscale thermoelectric materials [53, 54].

The intent of this project was to enhance the thermoelectric performance of SiNW arrays by introducing the heterogeneous silicide phase. The heterogeneous silicide phase acts as a phonon scattering interface to reduce the thermal conductivity of nanowires and increase zT.

#### 2.1 Fabrication of silicon nanowires

In the bottom-up nanowire synthesis approach, the most common methods are vapor-liquid-solid (VLS) growth and, more recently, metal-assisted chemical etching. In the VLS method, a liquid-phase metal nanoparticle catalyst is used to form the SiNW. Silicon precipitation occurs in the nanoparticle, followed subsequently by SiNW growth [55]. The diameter of the nanostructures is a function of the diameter of the alloy droplet at its tip. In recent years, there has been interest in the metal-assisted chemical etching process because of its simplicity and low-cost, which allows control over different parameters, such as diameter, length, orientation, doping type, doping level, and cross-sectional shape.

A disadvantage of metal-assisted chemical etching is the rough surface of the nanowires. However, this may represent an advantage when used for thermoelectricity, due to increased surface scattering of phonons, leading to a reduced thermal conductivity [41, 56]. For this project, the metal-assisted chemical etching process was used.

#### 2.1.1 Fabrication mechanism

In this project, the fabrication of SiNWs by metal-assisted chemical etching was based on a twostep process. In the first step, metal is deposited by electroless deposition or galvanic exchange. In the second step, SiNW etching or formation is achieved in a solution of HF, or a combination of HF and H<sub>2</sub>O<sub>2</sub>. Noble metal ions are reduced at the Si surface through a cathodic process and oxidation of Si atoms at the Si surface occurs, i.e., an anodic reaction. Typically, the metals used consist of Ag in a solution form (AgNO<sub>3</sub>), Au, and Pt. They can be deposited on the Si substrate via various methods, including thermal evaporation, sputtering, electron beam (E-beam) evaporation, electroless deposition, electrodeposition, focused-ion-beam (FIB)-assisted deposition, and spin-coating of particles. Electroless deposition is a simple method that is usually utilized to deposit noble metals if there is no strict demand on the morphology of the resulting etched structures. In this project, the electroless deposition of silver was adopted. As the electrochemical potential of noble metals compared to Si is more positive, a galvanic displacement reaction occurs in Si by injection of holes into the valence band; ref. Figure 2.1(a). Metal ions are further reduced on the Si surface by electrons provided by the Si-Si bonds [57].

The cathodic and anodic reactions taking place on the surface of the Si can be highlighted in the following equations [57]:

$$Ag^+ + e^- \rightarrow Ag^0(0) \tag{1}$$

$$Si(s)+2H_2O \rightarrow SiO_2 + 4H^+ + 4e^-$$

(2)

$$SiO2(s) + 6HF \rightarrow H2SiF6 + 2H2O$$

(3)

where Eq. (1) corresponds to the cathode reaction and Eq. (2) and (3) to the anode reaction. If  $H_2O_2$  is added into the reaction solution, the cathodic reaction of  $H_2O_2$  will occur on the Ag metal surface, with a reaction given by:

$$H_2O_2 + 2H^+ + 2e^- \rightarrow 2H_2O$$

When Ag is used as a metal, Ag<sup>+</sup> ions in the proximity of the silicon surface capture electrons from the valence band of silicon; ref. Figure 2.1(b). Meanwhile, holes are generated in the Si valence band when the Ag<sup>+</sup> is reduced to Ag nuclei. Deposition and growth of Ag nuclei facilitates the formation of SiO<sub>2</sub> underneath the silver nanoparticles; ref. Figure 2.1(c). SiO<sub>2</sub> is then etched away by HF, with the nanoparticles sinking into the silicon and forming SiNWs, as shown in Figure 2.1(d) [58, 59].

**Figure 2. 1** (a) Qualitative diagram of the comparison of electrochemical electron energy levels of Si band edges and the redox systems,  $AuCl_4^-/Au$ ,  $PtCl_6^{2-}/Pt$ ,  $Ag_4^+/Ag$ ,  $H_2O_2$  in HF solution.  $E_C$  and  $E_V$  are the conduction and valence band of Si, respectively. (b) - (d) Process of electroless silver deposition on a Si substrate immersed in HF/AgNO<sub>3</sub> solution. After Ag nanoparticles are deposited on the Si surface, HF starts to etch the silicon substrate [57].

Figure 2. 2 SEM images of silicon substrates etched with HF/AgNO<sub>3</sub> with Ag dendrite structures [58, 60]

An important question is why lateral etching does not occur. According to Peng, Hu et al., the pore diameter is determined by the size of the metal particle. They suggest that the charge exchange and transport between the anodic and cathodic sites would be more favorable at the metal-Si interface than at the pit wall, because the metal-Si interface has the shortest charge-transport distance, and because of the unique catalytic property of the metal particle, which greatly decreases  $E_a$  for the cathodic reaction. Accordingly, oxide formation and the dissolution of silicon would more favorably occur at the pore tips (the metal-Si interface) than at the pit walls. That is, longitudinal etching would be more favored than lateral etching; thus, deep pores would finally be formed, owing to the prolonged longitudinal etching of silicon. However, a puzzling problem is that the pores generated with stable Pt particles are not as straight as those obtained with Ag and Au particles. Therefore, the nature and propagation of the metal-Si interface during Si oxidation and dissolution should be addressed to clarify this etching mechanism.

By varying the concentration of AgNO<sub>3</sub> and HF, the diameter of the resulting SiNWs (arising from overlapping pores) can be roughly tuned.

# 2.1.2 Influencing factors

#### Doping type and doping level

Different conclusions concerning the relationship between etching rates and doping types or doping levels of the Si substrate have been reported. Li et al. found that under identical conditions Au-covered regions on a p<sup>+</sup> (0.01–0.03  $\Omega$  cm) Si substrate and Au-covered regions on a p<sup>-</sup> (1–10  $\Omega$  cm) substrate show only small variations in pore size and etching depth [61], while Cruz et al. reported that the etching depth in Au-covered regions of a p<sup>-</sup> (10  $\Omega$  cm) Si substrate is 1.5 times larger than that of a p<sup>+</sup> (0.01  $\Omega$  cm) Si substrate, under identical conditions [62]. The reason for different etching rates for substrates with different doping levels remains unclear so far. Concerning the doping type, Zhang et al. found that a p-type (7–13  $\Omega$  cm) substrate is etched more slowly than an n-type (7–13  $\Omega$  cm) substrate. This relationship is valid for both (100) and (111) substrates [62]. Besides influencing the etching rate, the doping level of the Si substrate also influences the morphology of the etched structures. With increasing doping levels, Si nanowires resulting from metal-assisted chemical etching become rougher [63] and finally evolve into nanowires containing micro pores.

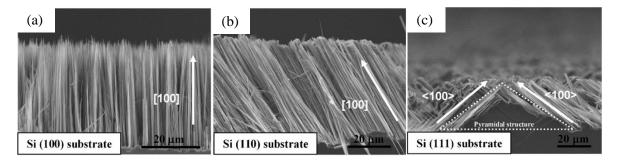

## Orientation of silicon substrate

Experiments in early years showed that, indeed, in (100) and (111) substrates the etching proceeded along the vertical direction [57]. However, it was later revealed that non-vertical etching occurs in (111) and (110) substrates, resulting in slanting, aligned Si nanostructures, as shown in Figure 2.3 [64, 65]. The non-vertical, metal-assisted chemical etching (i.e., the anisotropic etching in certain preferred crystallographic directions) is ascribed to the back-bond breaking theory [66, 67], which has already been used to explain the anisotropy in the anodic HF etching of Si [68] and the etching of Si in an alkaline solution [69]. For the oxidation or dissolution of a Si atom on the surface of a substrate, it is necessary to break the back-bonds of the surface atom that connect to the atoms underneath. The stronger the back-bond strength, the more difficult it is to remove the surface atom. The number of back-bonds in a Si atom on the surface is determined by the crystallographic orientation of the substrate. Each atom on the surface of a (100) substrate has two back-bonds, while an atom on the (110) or (111) surface has three back-bonds [70]. Due to the

different back-bond strength, the Si atom on the (100) surface plane is the most easily removed, and the etching occurs preferentially along the < 100 > directions.

**Figure 2. 3** Cross section SEM images of SiNWs formed on a Si (100) substrate (A), a Si (110) substrate (B) and a Si (111) substrate (C) [64, 65]

However, the influence of the etching anisotropy on the etching rate of a Si substrate (measured as the change in the etching depth vertically to the surface) remains puzzling. Huang et al. found that in the same etchant and for the same etching time, the etching depth of a (110) substrate etched along the <100> directions is almost the same as the etching depth of the same substrate etched along the [110] direction [71]. Zhang et al. found similar phenomena in the etching of (111) and (100) substrates with a different doping type, but the same doping level, despite the different etching direction [63].

#### Etching temperature

It has been reported that the length of Si nanowires fabricated by metal-assisted chemical etching in  $HF/AgNO_3$  solution or  $HF/H_2O_2$  solution increases approximately linearly with the etching time. Cheng et al [72] systematically studied the relationship between the etching time and the lengths of Si nanowires etched at different temperatures.

Figure 2. 4 Relationship of length of SiNWs and etching times at different temperatures [72].

With a temperature in the range of 0°C to 50°C, a linear relationship between the length of nanowires and etching time at all temperatures is confirmed (Figure 2.4). The observed etching rate increases with increasing etching temperature.

#### Type of metal

The morphologies of Pt and Cu electroless deposited from an HF-containing deposition solution look different from those of Ag and Au. With increased etching time, Pt and Cu tend to form a

dense film on the surface of the Si substrate [73] rather than dendrite structures. The dense metal film further hinders the access of HF to the surface of the Si substrate and, therefore, blocks the further etching of the Si substrate [57].

The specific type of noble metal influences the etching rate. The rate of etching assisted by Pt is much faster than that assisted by Au [74]. Moreover, the pores in or wires on substrates etched in the presence of Pt are usually surrounded by a porous layer [75], while no observable porous layer is found about the pores or wires etched from Au-coated [65] or Ag coated [76] substrates under otherwise identical conditions. The difference in the etching rate and morphologies of the etched structures has not yet been well-explained. The difference in the catalytic activity of the noble metal for the H<sub>2</sub>O<sub>2</sub> reduction might be a possible reason, although there is no literature directly comparing the catalytic activities of Pt, Au, and Ag particles on Si substrates for H<sub>2</sub>O<sub>2</sub> reduction. As hole injection is necessary for the etching of Si, when more holes are injected, the etching is faster. When more holes are injected, the possibility that holes diffuse from the etching front to the sidewall of the etched structure (e.g., pores or wires) increases, favoring the formation of a microporous structure on the sidewalls of etched structures.

#### Concentration of etchant

Chartier et al. [77] systematically studied the influence of the HF/H<sub>2</sub>O<sub>2</sub> ratio on the etching rate and on the etched morphologies of Si substrates (p-(100), 1–2  $\Omega$  cm) on which isolated Ag particles were deposited by electroless deposition. The morphologies of the etched structures are determined by the parameter  $\rho$ , defined as [78]/ ([78] + [H<sub>2</sub>O<sub>2</sub>]). With 100% >  $\rho$  > 70%, Ag particles induce straight cylinder pores, the diameters of which match well those of the Ag particles at the bottom. With 70% >  $\rho$  > 20%, cone-shaped pores form. The diameter of the pore tip is the same as the diameter of the Ag particle located there, while the opening of the pore at the surface of the Si substrate has a diameter larger than that of the Ag particle. For  $\rho$  below 30%, the cone-shaped pores are surrounded by microporous Si, which look similar to the structure etched with Pt particles in low HF concentration [65]. With 20% >  $\rho$  > 9%, Si evolves into crater-like structures with opening diameters of several micrometers. With 9% >  $\rho$  > 0%, neither porous nor crater structures form and a macroscopically smooth, but nanoscopically pitted surface, develops.

The relationship between etching morphologies and  $\rho$  is explained as follows [74]: For  $100\% > \rho > 70\%$  (i.e., a high percentage of HF), the etching rate is almost completely determined by the concentration of  $H_2O_2$  and nearly all holes generated at the Ag/Si interface at the pore tip are locally consumed because there is sufficient HF available to dissolve Si (or SiO<sub>x</sub>, if this occurs as an intermediate reaction product). When  $\rho$  is less than 70%, the etching rate is determined by the concentration of HF. In this case, the consumption rate of the holes at the pore tip is lower than the generation rate. Accordingly, unconsumed excess holes can diffuse away from the tip to the side wall of the pore. Hence, microporous Si forms on the sidewall of the pore. With very small  $\rho$ , or very high  $H_2O_2$  concentration, hole diffusion is pronounced and the diffused holes come to every exposed surface of the Si substrate. Consequently, oxidation and dissolution of Si occur everywhere and the etching is isotropic and independent of the location of Ag particles, resulting in a polished surface.

# 2.2 Silicide heterojunction

#### 2.2.1 Mechanisms for increasing figure of merit (zT)

According to  $zT=S^2\sigma T/\kappa$ , there are two approaches to increase zT: the power factor  $(S^2\sigma)$ , which includes the Seebeck coefficient S, is maximized and/or the thermal conductivity  $\kappa$  is minimized.

In this project a theoretical model of the thermoelectric properties of bulk semiconductors containing metallic nanoparticles is introduced. This model considers energy-dependent scattering of electrons and phonons on the band bending at the interfaces between the semiconductor hosts and randomly distributed metallic islands. This leads to an energy filtering effect that increases the Seebeck coefficient. This provides an explicit physical model for the proposed energy filtering effect [79].

While the role of metallic nanoinclusions may appear at first to be similar to that of point defects for which extensive work has been done, the physics is actually quite different. Indeed, in addition to electron scattering, phonon scattering on nanoinclusions occurs in a completely different regime than that on point defects [79].

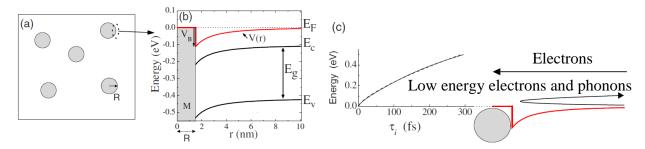

The central idea of Faleev and Léonard is illustrated in Figure 2.5 [80]. There, spherical metallic nanoinclusions with radius R are randomly distributed in a bulk semiconductor material; ref. Figure 2.5(a). In general, at such metal-semiconductor interfaces, charge transfer between the metal and the semiconductor leads to bands bending away from the interface, which is called the Schottky barrier; ref. Figure 2.5(b). The presence of this potential causes energy-dependent scattering of electrons and phonons, as illustrated in Figure 2.5(c). The high energy electrons are unaffected by the potential, but the low energy electrons can be strongly scattered, resulting in decreased thermal conductivity.

**Figure 2. 5** (a) Schematic of the semiconductor host with metallic nanoinclusions. (b) Example of the calculated potential V(r) and the Schottky barrier. (c) Illustrates the concept of energy filtering: low energy electrons and phonons scatter strongly due to the potential barrier, but high energy electrons are unaffected [80]..

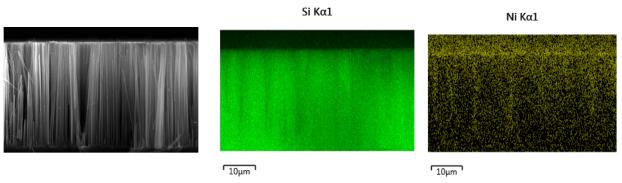

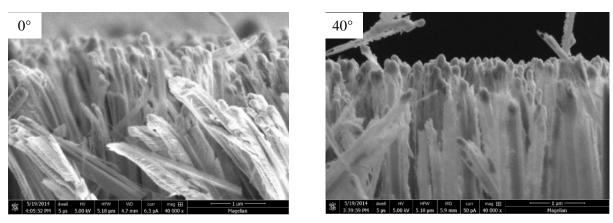

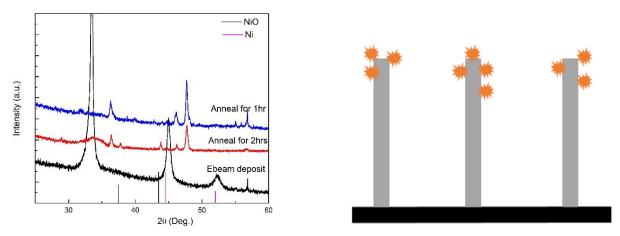

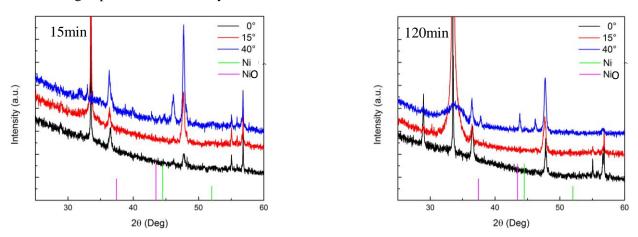

To explain the increase of the power factor  $S^2\sigma$ , the Mott relation for the Seebeck coefficient is used [81]. An electrical conductivity  $\sigma$  (E) is associated with the electrons that fill the energy levels between E and E+dE, irrespective of the mechanism that limits  $\sigma$  (E). The total electrical conductivity is then the integral of this over the entire energy range, moderated by the Fermi distribution function  $f_0(E)$ . Integrating by parts, the total conductivity is: