# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

X- to W-band phased arrays and wafer-scale transmitters using silicon integrated circuits

# Permalink

https://escholarship.org/uc/item/5hp1d22r

# Author

Atesal. Yusuf A., Atesal. Yusuf A.

# Publication Date 2011

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# X- to W-Band Phased Arrays and Wafer-Scale Transmitters using Silicon Integrated Circuits

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Yusuf A. Atesal

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor James Buckwalter Professor Gert Cauwenberghs Professor William S. Hodgkiss Professor Lawrence E. Larson

2011

Copyright Yusuf A. Atesal, 2011 All rights reserved. The dissertation of Yusuf A. Atesal is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2011

# DEDICATION

To my parents, Sebahattin and Nevin

# TABLE OF CONTENTS

| Signature Page  | e            |                 |                                                                                                                      | iii              |

|-----------------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------|------------------|

| Dedication      |              |                 |                                                                                                                      | iv               |

| Table of Conte  | ents.        |                 |                                                                                                                      | v                |

| List of Figures | 5            |                 |                                                                                                                      | vii              |

| List of Tables  |              |                 |                                                                                                                      | xi               |

| Acknowledge     | nents        |                 |                                                                                                                      | xii              |

| Vita and Publi  | catior       | ns              |                                                                                                                      | XV               |

| Abstract of the | e Diss       | ertation        |                                                                                                                      | xvi              |

| Chapter 1       | Intro<br>1.1 |                 | Array Systems                                                                                                        | 1<br>1           |

|                 | 1.2          | 1.1.2<br>1.1.3  | arrays                                                                                                               | 2<br>4<br>4<br>5 |

|                 | 1.3          | 1.2.2<br>Thesis | plifiers                                                                                                             | 6<br>7<br>7      |

| Chapter 2       | med          | iate Free       | nnel 8-20 GHz SiGe BiCMOS Receiver with Selectable Inter-<br>quencies for Multibeam Phased-Array Digital Beamforming |                  |

|                 |              |                 |                                                                                                                      | 10               |

|                 | 2.1          |                 | uction                                                                                                               | 10               |

|                 | 2.2          | •               | Design and Circuit Blocks                                                                                            | 13               |

|                 |              | 2.2.1           | RF-Front-End Design                                                                                                  | 13               |

|                 |              | 2.2.2           | IF-Stage Design                                                                                                      | 14               |

|                 |              | 2.2.3           | LO Distribution Network                                                                                              | 15               |

|                 |              | 2.2.4           | Biasing Network                                                                                                      | 17               |

|                 |              | 2.2.5           | Technology and Chip Performance                                                                                      | 17               |

|                 | 2.3          |                 | ip Measurements                                                                                                      | 22               |

|                 |              | 2.3.1           | S-Parameter Measurements                                                                                             | 22               |

|                 |              | 2.3.2           | RF-Front-End Measurements                                                                                            | 22               |

|                 |              | 2.3.3           | IF-Stage Measurements                                                                                                | 25               |

|                 |              | 2.3.4           | Channel Measurements                                                                                                 | 25               |

|                 |              | 2.3.5           | Temperature Measurements                                                                                             | 31               |

|                 | 2.4          | 8-Elen          | nent Ku-Band DBF Phased-Array Receiver                                                                               | 34               |

|              | 2.4.1 Board Design                                                | 34 |

|--------------|-------------------------------------------------------------------|----|

|              | 2.4.2 Board Measurements                                          | 38 |

|              | 2.5 Conclusion                                                    | 44 |

| Chapter 3    | X/Ku-Band 8-Element Phased Arrays Based on Single Silicon Chips   | 46 |

|              | 3.1 Introduction                                                  | 46 |

|              | 3.2 Design                                                        | 48 |

|              | 3.2.1 8-Element Phased Array Chip Design                          | 48 |

|              | 3.2.2 8-Element Phased Array Board Design                         | 48 |

|              | 3.3 Measurements                                                  | 57 |

|              | 3.3.1 S-parameter Measurements                                    | 57 |

|              | 3.3.2 Gain and Pattern Measurements                               | 57 |

|              | 3.3.3 Temperature Measurements                                    | 62 |

|              | 1                                                                 | 63 |

|              |                                                                   |    |

| Chapter 4    | Milimeter-Wave Wafer-Scale Silicon BiCMOS Power Amplifiers        | 65 |

|              | 4.1 Introduction                                                  | 65 |

|              | 4.2 Design                                                        | 67 |

|              | 4.2.1 $3 \times 3$ Wafer-Scale Power Amplifier Array Silicon Chip | 67 |

|              | 4.2.2 Power Amplifier Unit-Cell Design                            | 70 |

|              | 4.2.3 3×3 Antenna Array                                           | 75 |

|              | 4.2.4 $3 \times 3$ Power Amplifier Array                          | 77 |

|              | · ·                                                               | 78 |

|              | 4.3.1 On-Chip Measurements of Test Amplifier with CPW Input       |    |

|              |                                                                   | 78 |

|              |                                                                   | 78 |

|              |                                                                   | 81 |

|              |                                                                   | 87 |

| Chapter 5    | Conclusion                                                        | 91 |

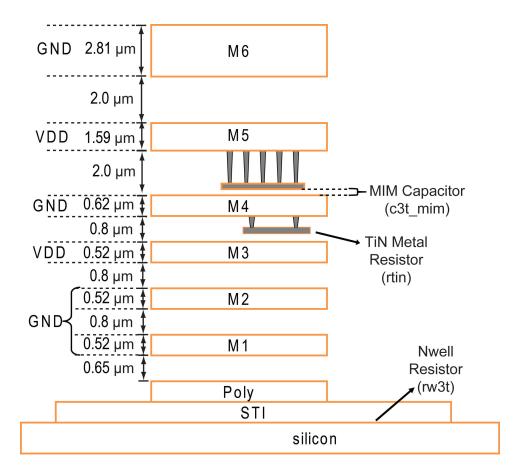

| Appendix A   | JAZZ SBC18HXL and IBM 8HP Process Details and Pad Design          | 93 |

|              | e                                                                 | 93 |

|              |                                                                   | 93 |

|              |                                                                   | 95 |

| Bibliography |                                                                   | 97 |

# LIST OF FIGURES

| Figure 1.1:  | Block diagram of an 8-element phased array.                                                                                                                                                                                  | 2        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

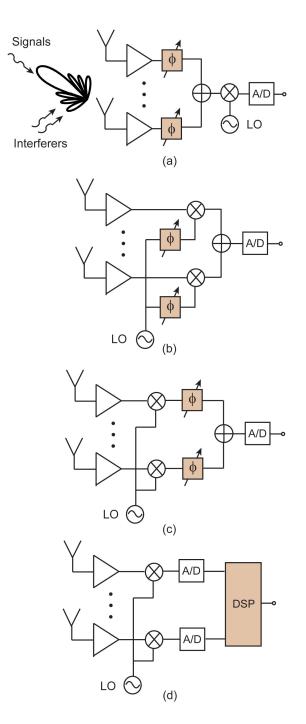

| Figure 1.2:  | Block diagram of phased array architectures (a) RF phase-shifting, (b) LO phase shifting, (c) IF phase shifting, and (d) digital beam-forming                                                                                | 3        |

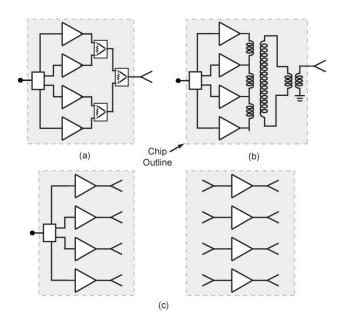

| Figure 1.3:  | Block diagram of (a) Wilkinson, (b) transformer, and (c) quasi-optical power-<br>combining techniques.                                                                                                                       | 6        |

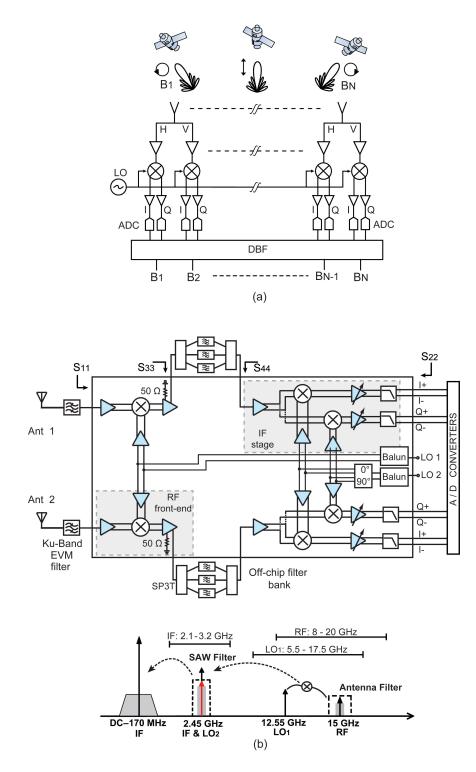

| Figure 2.1:  | (a) Digital beam-forming system, (b) block diagram of the two channel receiver based on a dual-down-conversion architecture and frequency plan.                                                                              | 11       |

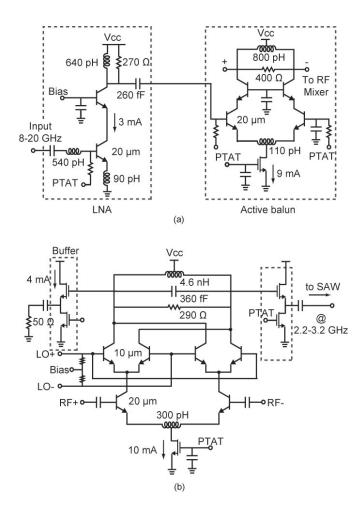

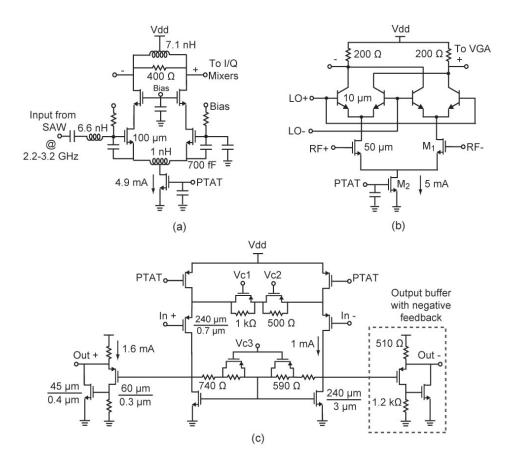

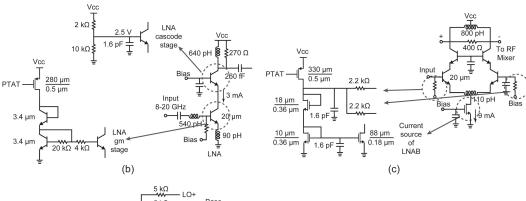

| Figure 2.2:  | Circuit schematics of the RF-front end: (a) LNA and active balun, and (b) double-balanced mixer with a tuned load.                                                                                                           | 13       |

| Figure 2.3:  | Circuit schematics of the IF stage: (a) Active balun, (b) resistive double-<br>balanced mixer, and (c) baseband VGA with 9, 12 and 16 dB gain control.                                                                       | 14       |

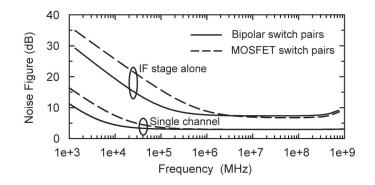

| Figure 2.4:  | Noise figure comparison showing the effect of using bipolar $(10\mu m/0.18\mu m)$ or MOSFET $(25\mu m/0.18\mu m)$ switch pairs in the IF stage mixer core.                                                                   | 15       |

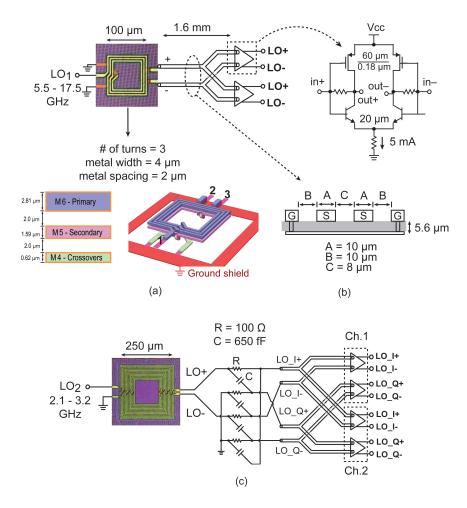

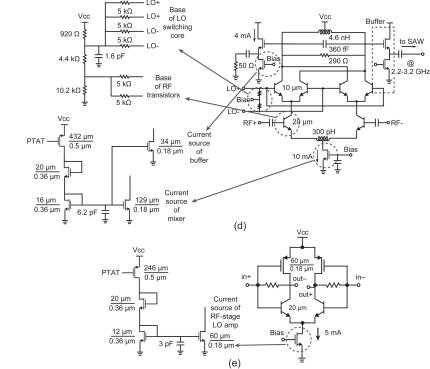

| Figure 2.5:  | LO distribution networks: (a) $LO_1$ at 5.5-17.5 GHz, (b) differential LO driver, and (c) $LO_2$ at 2.1-3.2 GHz.                                                                                                             | 16       |

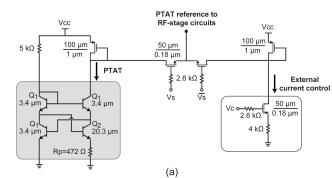

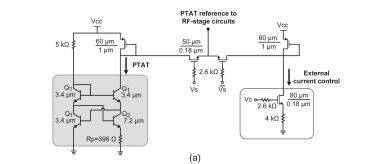

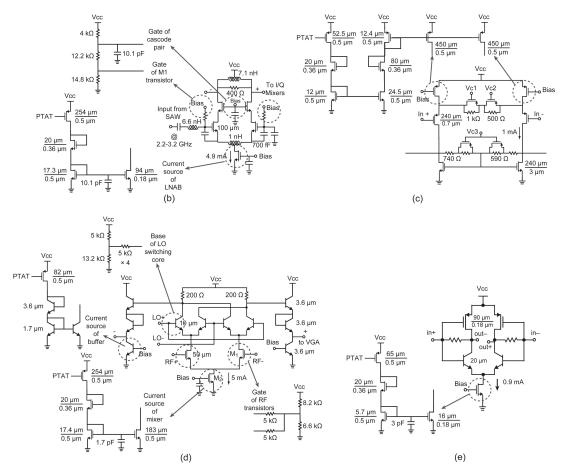

| Figure 2.6:  | Bias networks of RF-front-end: (a) PTAT reference current source, (b) LNA, (c) LNAB, (d) DB-Mixer and (e) LO-amplifiers.                                                                                                     | 18       |

| Figure 2.7:  | Bias networks of IF-stage: (a) PTAT reference current source, (b) Active balun, (c) VGA, (d) Mixer and (e) LO-amplifiers.                                                                                                    | 19       |

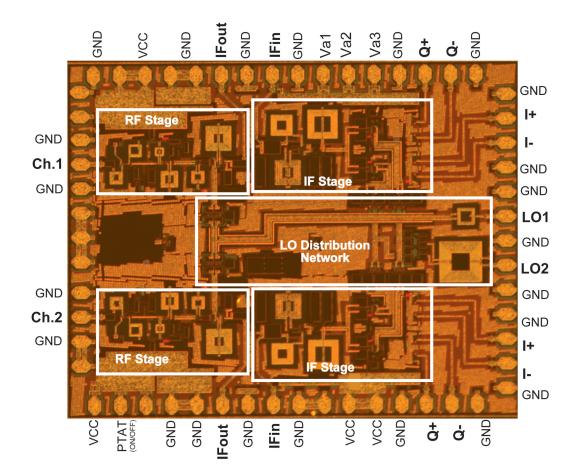

| Figure 2.8:  | (a) Microphotograph of the 8-20 GHz two-channel down-converter ( $2.6 \times 2.2$ mm <sup>2</sup> including all pads).                                                                                                       | 20       |

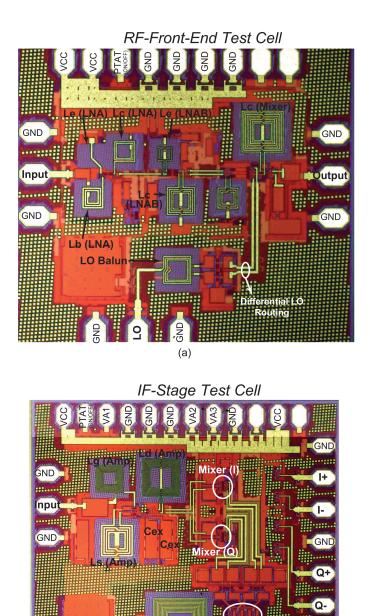

| Figure 2.9:  | Micrograph of the fabricated test cells: (a) RF-front-end $(1.25 \times 1.10 \text{ mm}^2)$ including all pads) (b) IF-stage $(1.40 \times 1.35 \text{ mm}^2)$ including all pads).                                          | 21       |

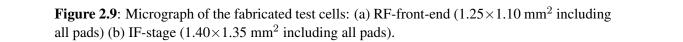

| Figure 2.10: | Measured return losses: (a) RF input $(S_{11})$ , (b) baseband output $(S_{22})$ , (c) IF output $(S_{33})$ and input $(S_{44})$ .                                                                                           | 23       |

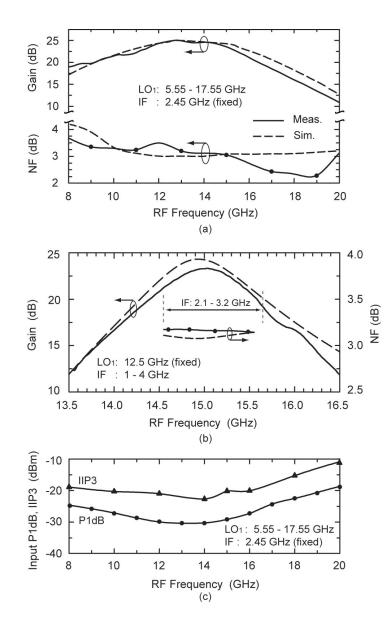

| Figure 2.11: | Measured gain and NF of the RF stage: (a) with fixed IF output at 2.45 GHz, (b) at 15 GHz vs. different IF. (c) Measured input P1dB and IIP3 with IF                                                                         |          |

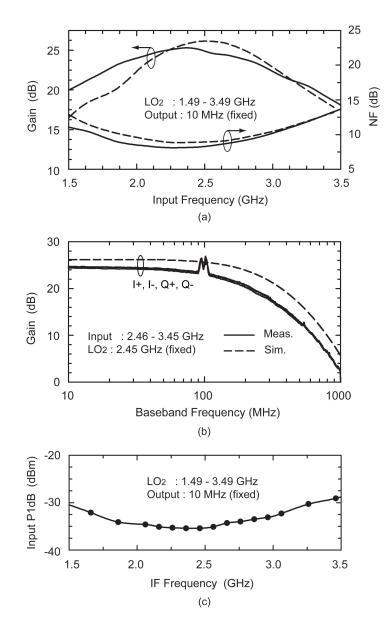

| Figure 2.12: | <ul> <li>fixed at 2.45 GHz.</li> <li>(a) Measured gain and NF of the IF stage with fixed baseband output at 10</li> <li>MHz (b) measured gain of the IF stage with fixed LO at 2.45 GHz.</li> </ul>                          | 24<br>26 |

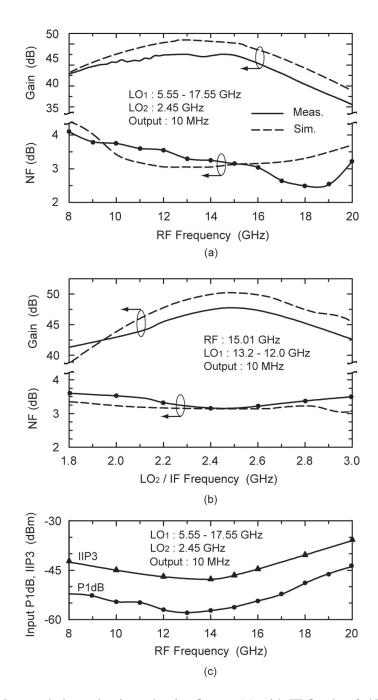

| Figure 2.13: | MHz, (b) measured gain of the IF stage with fixed LO at 2.45 GHz Measured channel gain and noise figure: (a) with IF fixed at 2.45 GHz, (b) at 15 GHz vs. different IF. (c) Measured input P1dB and IIP3 at maximum          | 20       |

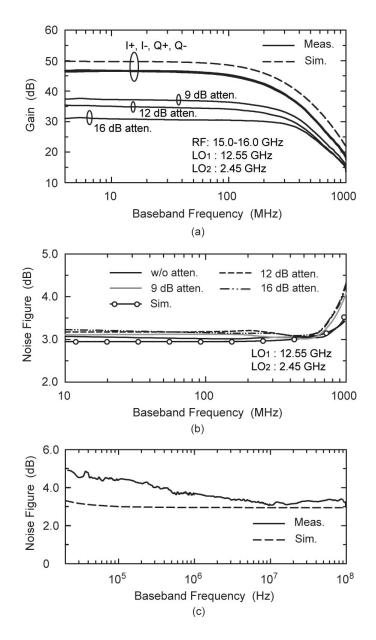

| Figure 2.14: | gain setting with IF fixed at 2.45 GHz. $\dots$ Measured (a) channel gain, (b) noise figure with LO <sub>1</sub> and LO <sub>2</sub> fixed at 12.55                                                                          | 27       |

|              | GHz and 2.45 GHz, respectively. Gain is shown for different attenuation levels, and (c) noise figure below 100 MHz                                                                                                           | 28       |

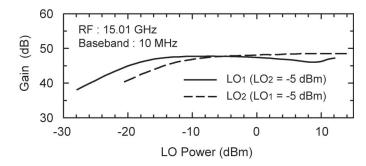

| -            | Measured channel gain versus LO power with $LO_1$ and $LO_2$ fixed at 12.55 and 2.45 GHz, respectively.                                                                                                                      | 29       |

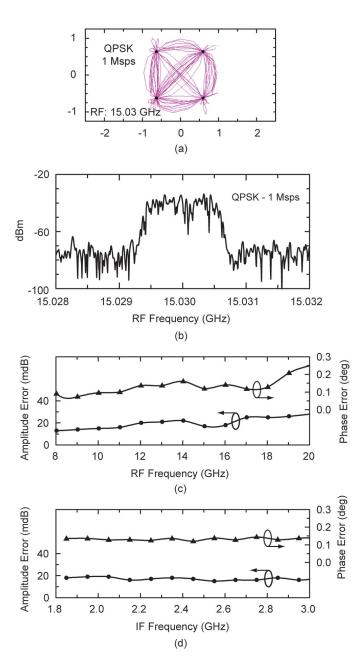

| Figure 2.16: | Performance of single-channel with 1 Msps QPSK modulation: (a) Constel-<br>lation diagram, (b) Spectrum of the output signal, and I/Q gain and phase<br>error (c) for IF fixed at 2.5 GHz, and (d) for RF fixed at 15.03 GHz | 30       |

| Figure 2.17: | Measured EVM performance of the chip with 1 Msps QPSK modulation with (a) fixed IF at 2.45 GHz and (b) fixed RF input at 15.03 GHz.                                                                                          | 30<br>31 |

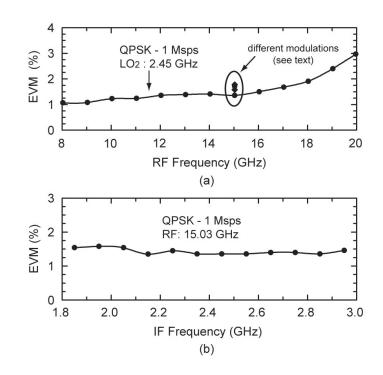

| Figure 2.18: | Measured channel gain and NF vs. temperature from -40°C to 100°C                        | 32 |

|--------------|-----------------------------------------------------------------------------------------|----|

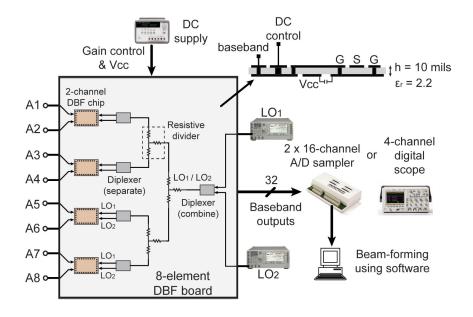

| Figure 2.19: | Layout of an 8-element digital beamformer measurement setup                             | 35 |

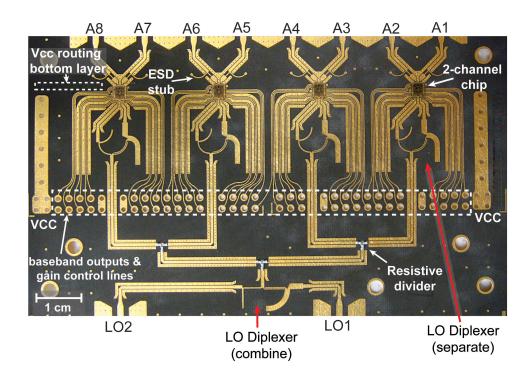

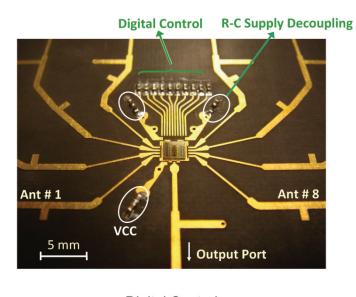

| Figure 2.20: | Picture of the fabricated 8-element Ku-Band DBF board                                   | 35 |

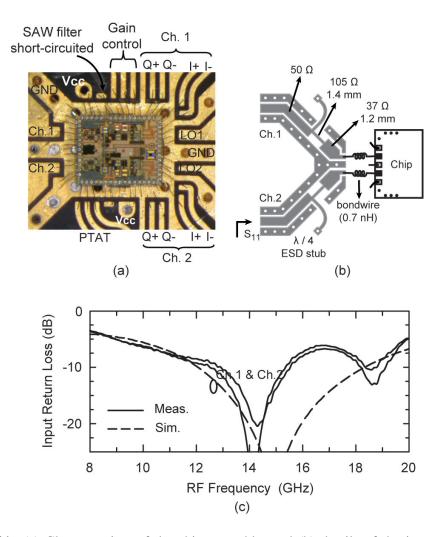

| Figure 2.21: | (a) Close-up view of the chip assembly, and (b) details of the input matching           |    |

|              | network and (d) measured S11 for A1 and A2.                                             | 36 |

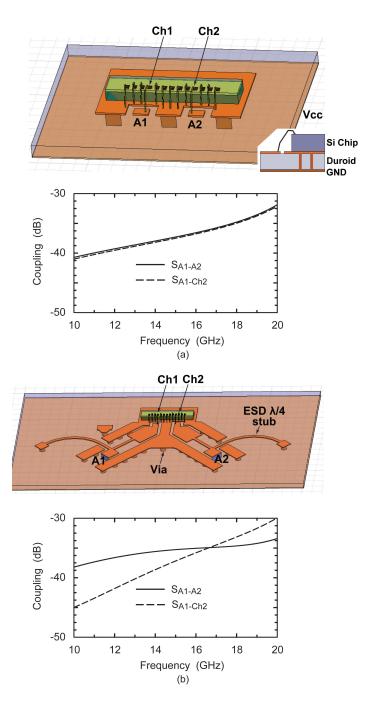

| Figure 2.22: | 3-D chip-on-board packaging model in HFSS: coupling between two chan-                   |    |

|              | nels (a) including bondwires, and (b) including bondwires and matching                  |    |

|              | networks                                                                                | 39 |

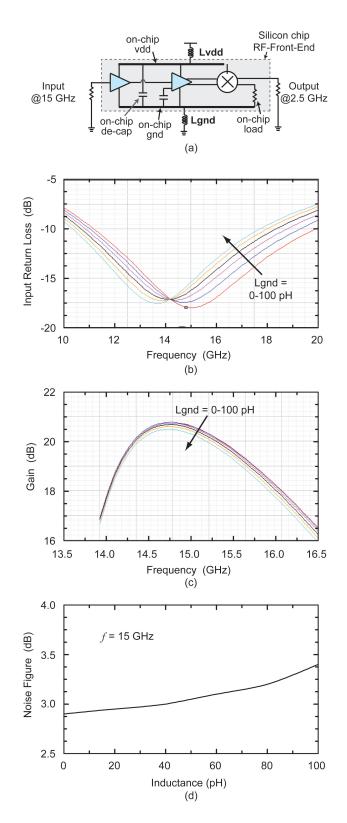

| Figure 2.23: | Effect of parasitic bondwire inductance on channel performance: (a) input               |    |

|              | return loss, (b) gain, and (c) noise figure.                                            | 40 |

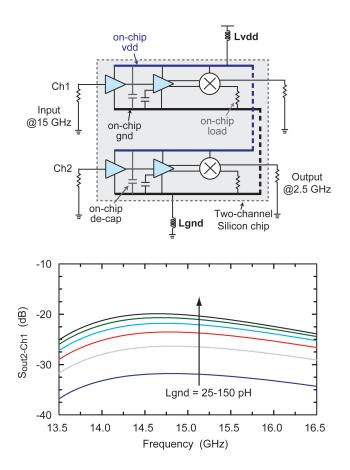

| Figure 2.24: | Coupling between channels with parasitic ground bondwire inductance. Cou-               |    |

|              | pling for Lgnd=0 pH is very low and is not shown                                        | 41 |

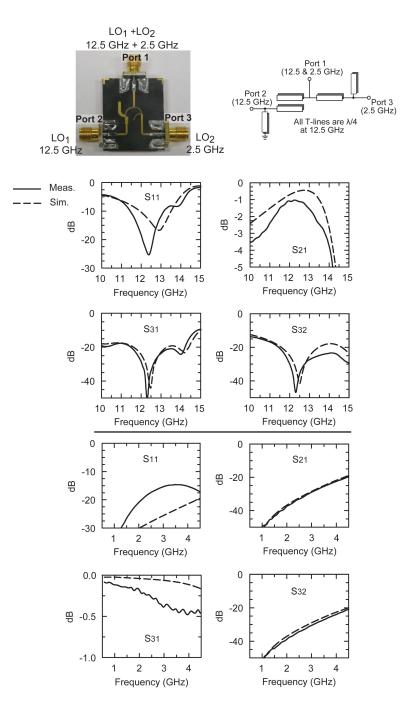

| Figure 2.25: | Measured and simulated S-parameters of the diplexer. Different frequency                |    |

|              | regions are shown for clarity.                                                          | 42 |

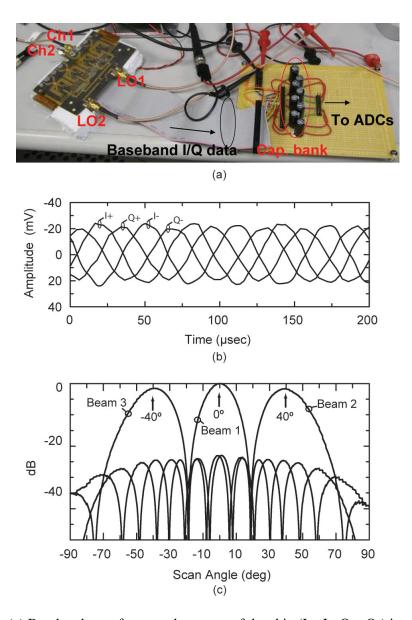

| Figure 2.26: | (a) Baseband waveforms at the output of the chip (I+, I-, Q+, Q-) in a system           |    |

|              | level configuration. The signals are measured using an ADC card at 10 ksps.             |    |

|              | (b) Synthesized patterns with Matlab for three different scan angles using a            |    |

|              | Dolph-Chebyshev distribution with -23 dB sidelobes                                      | 43 |

| Figure 2.27: | Rockwell Collins real-time digital-beam-forming array achieved three si-                |    |

|              | multaneous beams tracking different angles: (a) without null placement,                 |    |

|              | and (b) with null placement [1]                                                         | 44 |

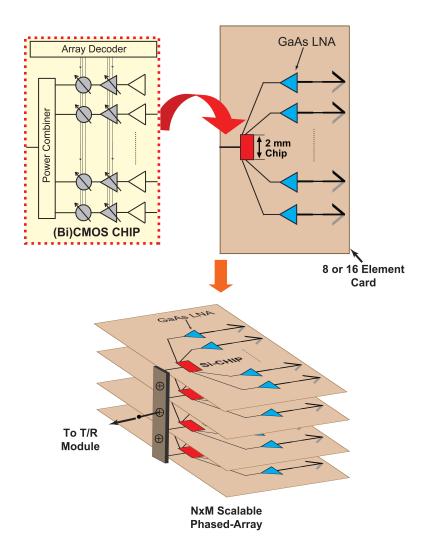

| Figure 3.1:  | Low-cost scalable phased array system using silicon BiCMOS chips                        | 47 |

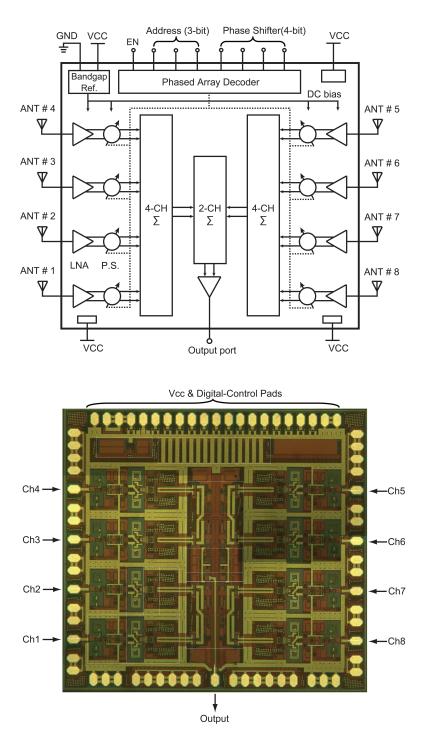

| Figure 3.2:  | Functional block diagram of the 8-element silicon phased array chip $(2.2 \times 2.45)$ | т, |

| 1 iguie 5.2. | $mm^2$ )                                                                                | 50 |

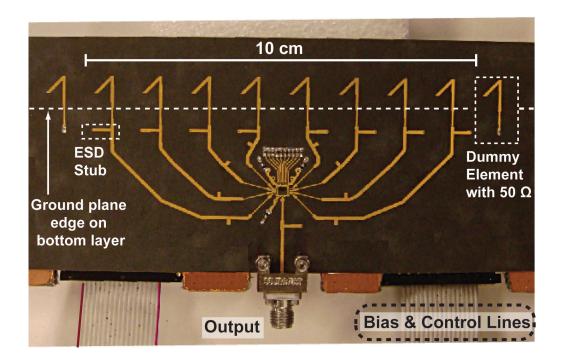

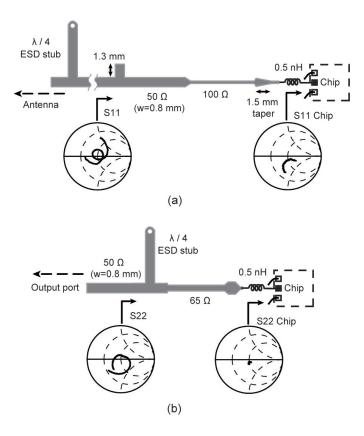

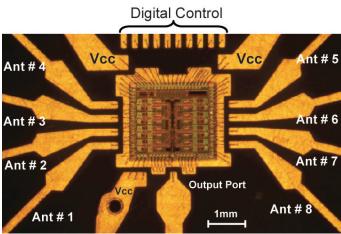

| Figure 3.3:  | The 8-element X/Ku-band phased array with the silicon chip at its center.               | 51 |

| Figure 3.4:  | Matching networks for (a) input RF ports (8 of them) and (b) output RF                  | 01 |

| 1.8010.0111  | port. The frequency span is 10-14 GHz.                                                  | 52 |

| Figure 3.5:  | Input and output transmission lines around the silicon chip, and the chip-              |    |

| 8            | on-board packaging $(2.5 \times 2.2 \text{ mm}^2)$ .                                    | 54 |

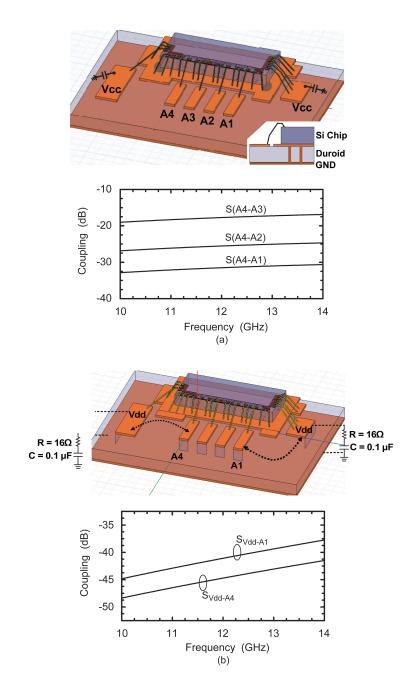

| Figure 3.6:  | 3-D view of the silicon chip, bondwires, grounded pedestal and input RF                 |    |

| U            | transmission lines, and the simulated coupling between the input RF ports.              |    |

|              | Coupling (a) between elements (RF paths), and (b) between Vcc supply                    |    |

|              | lines and the closest RF channel.                                                       | 55 |

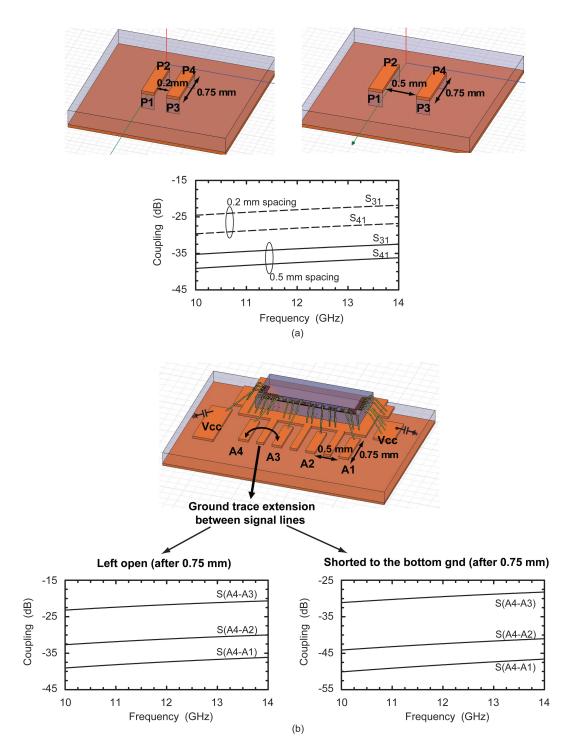

| Figure 3.7:  | 3-D EM coupling simulations of (a) two RF lines separated by 0.2 and 0.5                |    |

| C            | mm, (b) chip-on-board packaging with 0.5 mm spacing between RF signal                   |    |

|              | traces, and ground extensions (two cases are given: when the ground ex-                 |    |

|              | tensions are left open, or when the ground extensions are connected to the              |    |

|              | reference ground plane).                                                                | 56 |

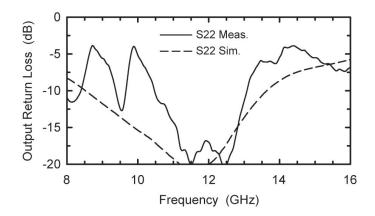

| Figure 3.8:  | Measured output return loss. Measurements include the 3.5 mm connector                  |    |

|              | effects                                                                                 | 57 |

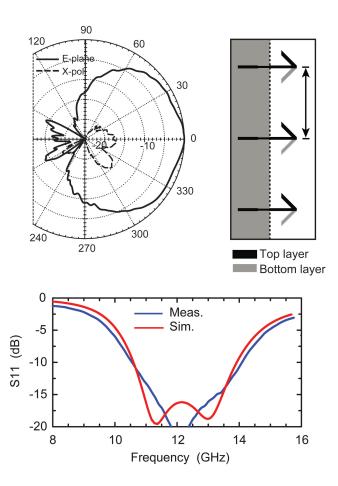

| Figure 3.9:  | Measured angled-dipole antenna pattern at 12 GHz in a 3-element configu-                |    |

|              | ration (center element shown).                                                          | 58 |

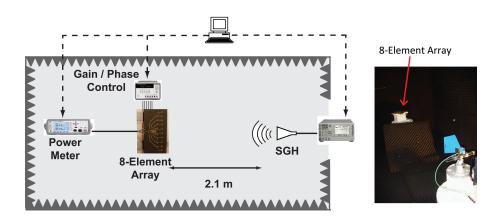

| Figure 3.10: | Block diagram and photo of the gain and pattern measurement setup                       | 58 |

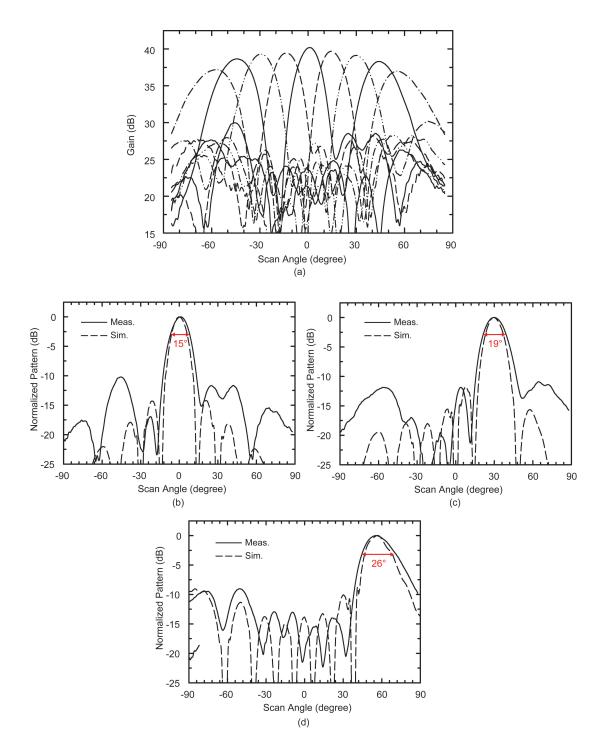

| Figure 3.11:  | (a) Measured patterns at 12 GHz plotted on an absolute gain scale. Compar-<br>ison between measured and simulated normalized patterns of (b) $0^{\circ}$ -, (c) $30^{\circ}$ -, and (d) $60^{\circ}$ -scanned beams at 12 GHz.                                                                                                                                                                                                    | 59       |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

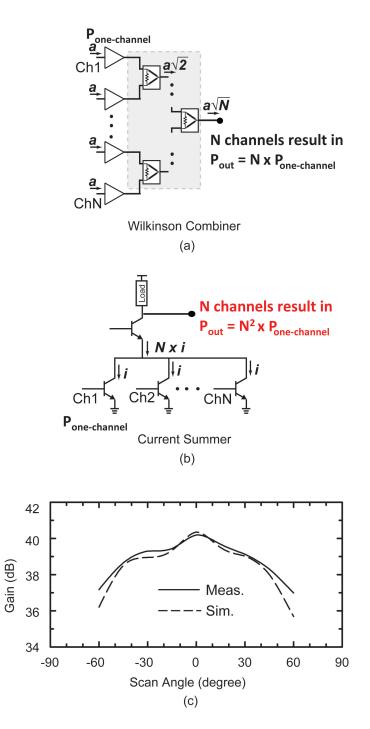

| Figure 3.12:  | Phased array combiners: (a) Wilkinson based, (b) current-summing based.<br>(c) Measured absolute gain vs. scan angle at 12 GHz.                                                                                                                                                                                                                                                                                                   | 61       |

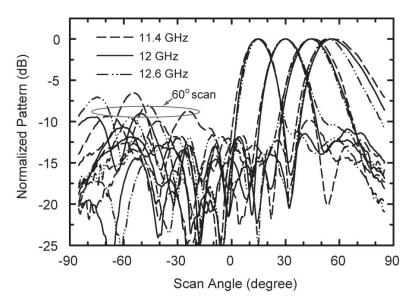

| -             | Measured patterns at 11.4, 12 and 12.6 GHz. The patterns are normalized and only positive beam scans are shown for ease of comparison                                                                                                                                                                                                                                                                                             | 62       |

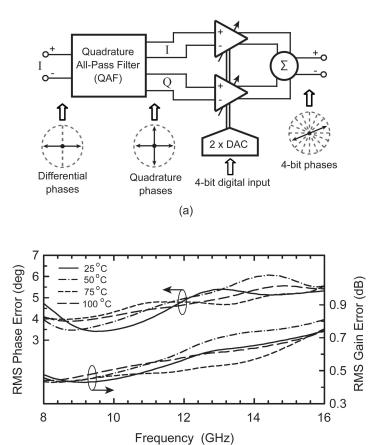

| Figure 3.14:  | (a) Block diagram of the 4-bit active phase shifter, (b) measured RMS phase and gain error vs. temperature. An RMS error $< 6^{\circ}$ is maintained over temperature.                                                                                                                                                                                                                                                            | 63       |

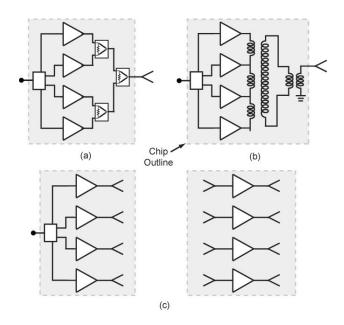

| Figure 4.1:   | Block diagram of (a) Wilkinson, (b) transformer, and (c) quasi-optical power-<br>combining techniques.                                                                                                                                                                                                                                                                                                                            | 66       |

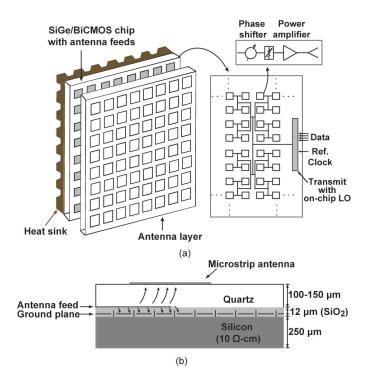

| Figure 4.2:   | (a) Wafer-scale transmit phased array, and (b) electromagnetically-coupled on-chip microstrip antenna.                                                                                                                                                                                                                                                                                                                            | 66       |

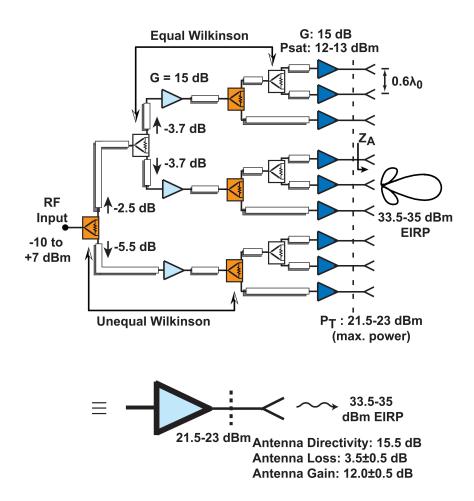

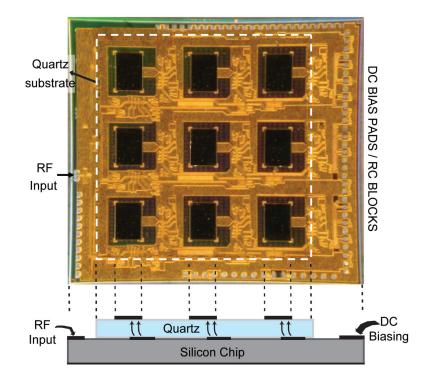

| Figure 4.3:   | Block diagram of the W-band wafer-scale $3 \times 3$ power amplifier array                                                                                                                                                                                                                                                                                                                                                        | 68       |

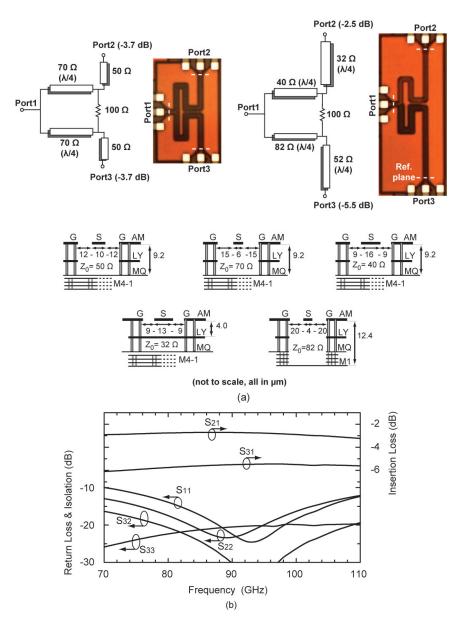

| Figure 4.4:   | (a) Schematic diagram and microphotographs of the equal (-3.7 dB) and unequal (-2.5 dB / -5.5 dB) Wilkinson dividers with associated grounded CPW transmission lines ( $Z_0 = 32 - 82 \Omega$ ), (b) simulated S-parameters of                                                                                                                                                                                                    |          |

|               | the unequal Wilkinson divider                                                                                                                                                                                                                                                                                                                                                                                                     | 69       |

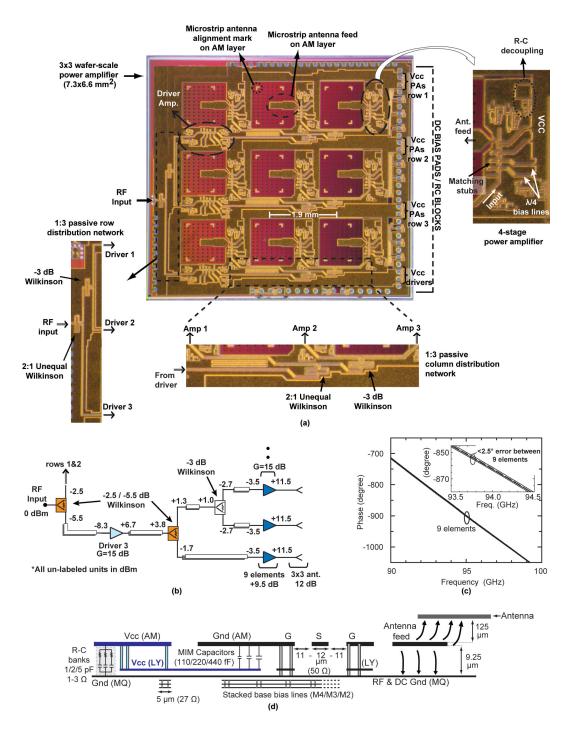

| Figure 4.5:   | (a) Detailed microphotograph of the $3x3$ power amplifier array chip without antennas ( $7.3 \times 6.6 \text{ mm}^2$ including all pads), (b) power division and amplification throughout the array in a small-signal regime, (c) simulated phase from the input port to the 9 antenna ports, (d) above silicon metal layers (M2-AM) with grounded CPW and microstrip lines, decoupling capacitors, and microstrip antenna feed. | 71       |

| Figure 4.6:   | Circuit schematic of the 4-stage W-band power amplifier. Electrical lengths are given at 94 GHz and all non-labeled shunt capacitors are 440 fF                                                                                                                                                                                                                                                                                   | 71       |

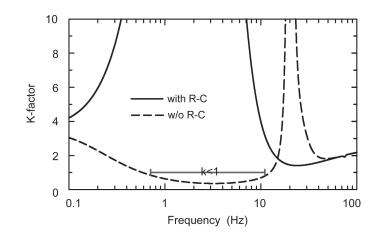

| Figure 4.7:   | Simulated stability factor of the 4-stage power amplifier.                                                                                                                                                                                                                                                                                                                                                                        | 74       |

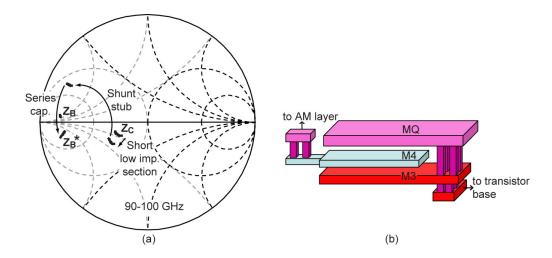

| Figure 4.8:   | (a) Design of the interstage matching network between stage-3 (Q3) and stage-4 (Q4) at 90-100 GHz, (b) custom metal-oxide-metal (MOM) capaci-                                                                                                                                                                                                                                                                                     | 74       |

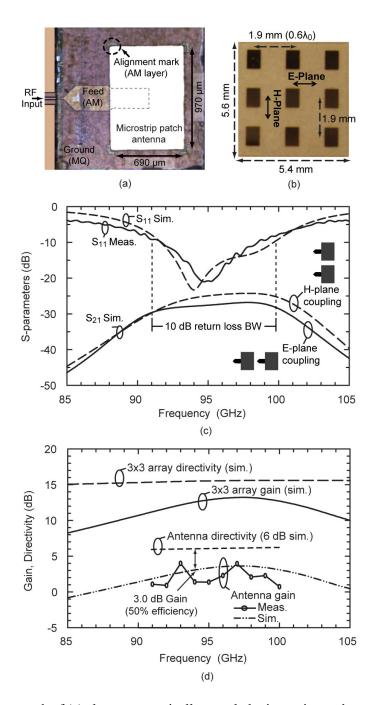

| Figure 4.9:   | tor design                                                                                                                                                                                                                                                                                                                                                                                                                        | 74<br>76 |

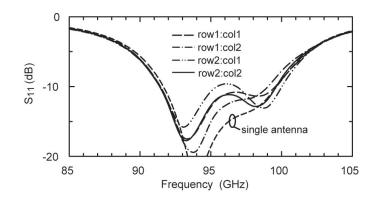

| Figure 4.10:  | Simulated input return loss of four antennas in the 3x3 array environment including the mutual coupling between the elements. The other antennas                                                                                                                                                                                                                                                                                  |          |

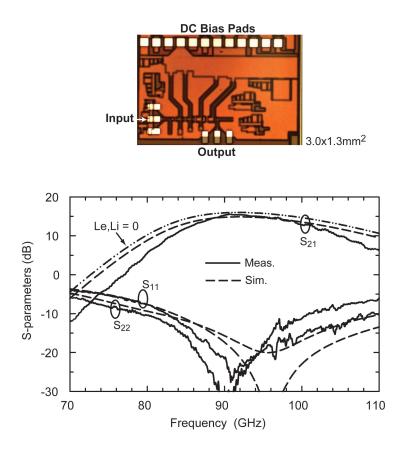

| Figure 4 11.  | have identical response due to symmetry                                                                                                                                                                                                                                                                                                                                                                                           | 77<br>79 |

| ÷             | Measured on-chip S-parameters of the power amplifier unit cell Measured unit-cell on-chip (a) output power and gain versus input power at                                                                                                                                                                                                                                                                                         | 19       |

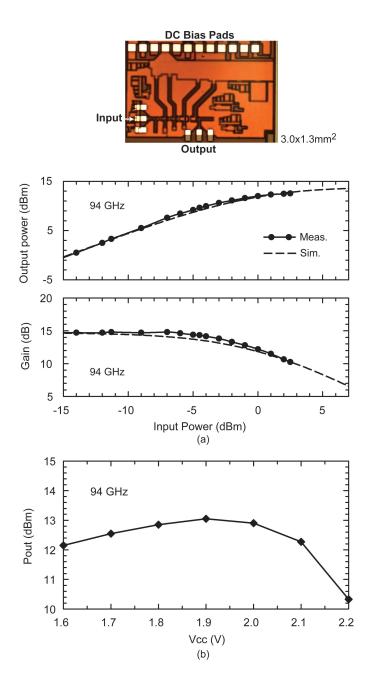

| 1 iguie 7.12. | 94 GHz, and (b) measured Psat vs. supply voltage                                                                                                                                                                                                                                                                                                                                                                                  | 80       |

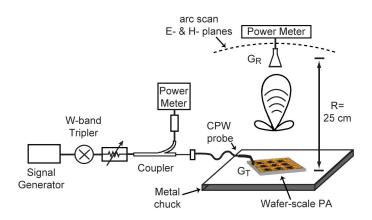

| Figure 4.13:  | W-band EIRP and pattern measurement setup.                                                                                                                                                                                                                                                                                                                                                                                        | 81       |

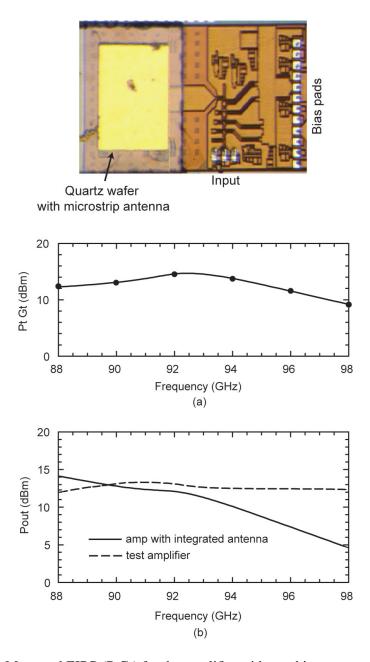

| Figure 4.14:   | (a) Measured EIRP (PtGt) for the amplifier with on-chip antenna. (b) Com-                  |          |

|----------------|--------------------------------------------------------------------------------------------|----------|

|                | parison of measured Pout from the test amplifier and Pout of the amplifier                 |          |

|                | with the on-chip antenna.                                                                  | 82       |

| Figure 4.15:   | Microphotograph of the wafer-scale power amplifier array $(7.3 \times 6.6 \text{ mm}^2)$ . |          |

|                | A quartz substrate with a $3 \times 3$ antenna array is placed on top of the silicon       |          |

|                | chip                                                                                       | 83       |

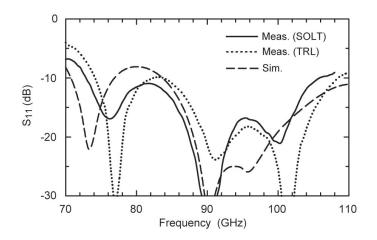

| Figure 4.16:   | Measured input return loss of the wafer-scale $3 \times 3$ array                           | 83       |

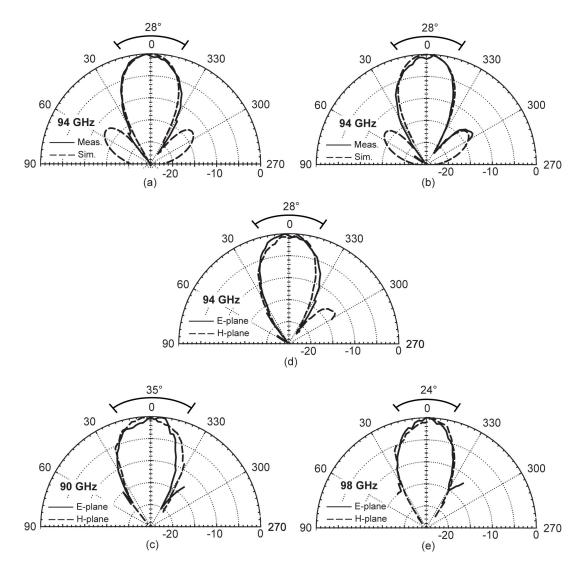

| Figure 4.17:   | Measured and simulated array patterns at 94 GHz (a) E-plane, (b) H-plane.                  |          |

|                | Measured E-/H-plane patterns at (c) 90 GHz, (d) 94 GHz (d) 98 GHz. The                     |          |

|                | 3-dB beamwidth angle is also shown                                                         | 84       |

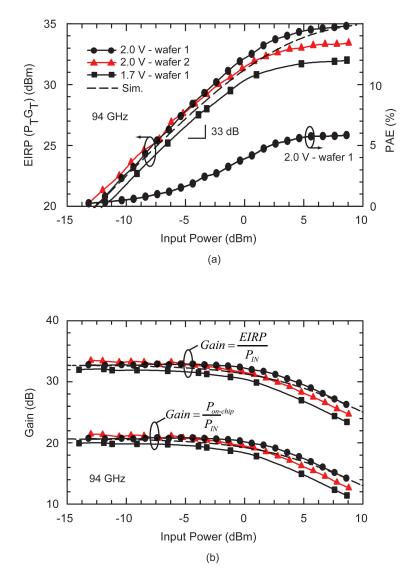

| Figure 4.18:   | (a) Measured EIRP versus input power at 94 GHz, and (b) measured quasi-                    |          |

|                | optical gain at 94 GHz. Measurements are shown for two different wafers.                   | 86       |

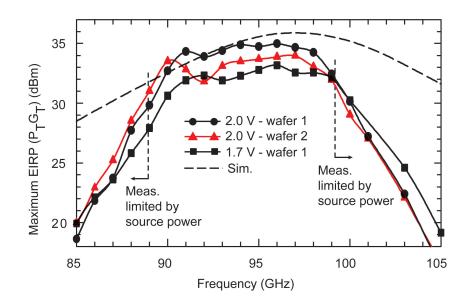

| Figure 4.19:   | Measured maximum EIRP versus frequency. Measurements are shown for                         |          |

|                | two different wafers.                                                                      | 87       |

| Figure A.1:    | JAZZ SBC18HXL process stack-up with 6 metal layers, MIM capacitors                         |          |

| 1 15010 1 1.1. | and TiN resistors.                                                                         | 94       |

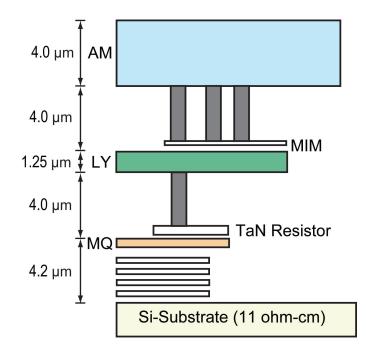

| Figure A.2:    | IBM 8HP process stack-up with 7 metal layers, MIM capacitors, and TaN                      | <i>,</i> |

| 1 15010 1 1.2. | resistors.                                                                                 | 96       |

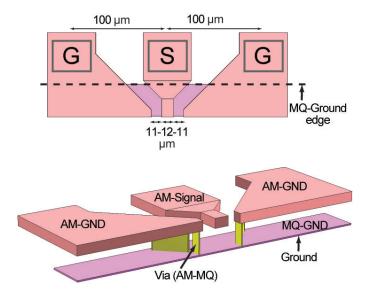

| Figure A.3:    | CPW pad transition design in IBM8HP process.                                               | 96       |

| 1 19010 1 1.5. |                                                                                            | 20       |

## LIST OF TABLES

| Table 2.1: | Single-Channel Performance Summary (On-Chip)                             | 33 |

|------------|--------------------------------------------------------------------------|----|

| Table 2.2: | On-Board System Performance (A1 and A2)                                  | 44 |

| Table 3.1: | Performance Summary of 8-Element Silicon Chip                            | 49 |

| Table 3.2: | Gain of the 8-Element Phased Array                                       | 60 |

| Table 4.1: | Performance Summary                                                      | 88 |

| Table 4.2: | Performance Summary compared to single chips                             | 89 |

| Table 4.3: | Performance Summary Compared to Free-Space (Quasi-Optical) III-V Designs | 89 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to sincerely thank my advisor Prof. Gabriel M. Rebeiz for his guidance and unlimited technical and moral support throughout my doctoral studies. It was a great pleasure to know him and work with him, and it is a great honor for me to be one of his students. With his very well-maintained state-of-the-art labs, and immense technical expertise, Prof. Rebeiz provides an environment for high quality research and deep technical understanding. His motivation, encouragements, and enthusiasm are the main driving force for the success of his students. Prof. Rebeiz taught me so many lessons (both academic and daily life) that I believe will always guide me for the rest of of life. I also would like to thank Prof. Rebeiz so much for helping me to get a nice job as Analog Design Engineer at Intel Corporation, Inc. His support and strong recommendations were the main keys behind my successful job interviews with Intel Corp.

Next, I would like to thank my dissertation committee members, Prof. Lawrence E. Larson, Prof. James Buckwalter, Prof. Gert Cauwenberghs and Prof. William S. Hodgkiss for their time, interest, and valuable comments.

I want to specifically thank to my long time friend Berke Cetinoneri for his help on all the work we have done together. He introduced me to Prof. Rebeiz and started our journey to UCSD. He contributed to my doctoral studies, not only with his technical support but also with his personal/friendly support. I would also like to thank prof. Yasar Gurbuz at Sabanci University, Turkey, who supported and encouraged both Berke and me to do a PhD at UCSD.

I would like to thank Kevin Ho, Michael Chang, Ramadan Alhalabi, Kwangjin Koh, and Berke Cetinoneri for their contribution to the work in this thesis. Additionally, I must thank my fellow graduate students for their support and friendship. My thanks go to all of the TICS group including Michael Chang, Chris Galbraith, Carson White, Byung-Wok Min, Sang-June Park, Jeonggeun Kim, Balaji Lakshminarayana, Mohammad El-Tanani, Tiku Yu, Sangyoung Kim, Kwangjin Koh, Isak Reines, Jason May, Alex Girchner, DongWoo Kang, Jung-Mu Kim, Berke Cetinoneri, Ramadan Alhalabi, Chirag Patel, Kevin Ho, Mehmet Uzunkol, Jennifer M. Edwards, Woorim Shin, Donghyup Shin, Yu-Chin Ou, Ozgur Inac, Yi-Chyun Chiou, Chih-Chieh Cheng, Dr. Rashed Mahameed and Hojr Sedaghat Pisheh. I would also like to thank my closefriends Mehmet Uzunkol, Berke Cetinoneri, Ozgur Inac, and Mehmet Parlak for making my life in San Diego more enjoyable.

Completing my PhD would not have been possible without support and encouragement of my family. My father, Sebahattin Atesal, has always inspired me as an excellent father with a very successful academic career. I know that he is always there whereever/whenever I need him. Love, moral support, and encouragements of my mother, Nevin Atesal, always keeps me strong during my hard days. My sister, Kubra Ceren, is the sun-shine of our family inspiring us all. I sincerely thank my lovely fiancee Ozlem Turgut for her great support and devoted love. Without my family this work would have never existed, I would like to express many thanks to them.

My thanks also extend to George and Carol Hahn, the other part of my family in San Diego. They kindly hosted me (and Berke) during my first days in San Diego starting our friendship. I thank them a lot for taking care of me and for their endless support since we met. They are my family here in USA.

The material in this dissertation is based on the following papers which are either published, or under final process for publication.

Chapter 2 is based on and mostly a reprint of the following papers:

- Y.A. Atesal, B. Cetinoneri, K. Ho, and G.M. Rebeiz, "A Two-Channel 8-20 GHz SiGe BiCMOS Receiver with Selectable Intermediate Frequencies for Multibeam Phased-Array Digital Beamforming Applications," accepted for publication in IEEE Transaction on Microwave Theory and Techniques,

- B. Cetinoneri, Y.A. Atesal and G. M. Rebeiz, A two-channel Ku-band BiCMOS digital beam-forming receiver for polarization-agile phased-array applications, IEEE Radio Frequency Integrated Circuits Symp., June 2009, pp. 127-130.

Chapter 3, is based on and mostly a reprint of the material as it appears in IEEE International Microwave Symposium Digest, 2010 :

Y.A. Atesal, B. Cetinoneri, K.-J. Koh and G. M. Rebeiz, X/Ku-band 8-element phased arrays based on single silicon chips, IEEE Int. Microwave Symp. Dig., May 2010, pp. 23-28.

Chapter 4, is based on and mostly a reprint of the following papers:

- Y.A. Atesal, B. Cetinoneri, M. Chang, R.A. Alhalabi, and G.M. Rebeiz, "Milimeter Wave Wafer-Scale Silicon BiCMOS Power Amplifiers Using Free-Space Power Combining," accepted for publication in IEEE Transaction on Microwave Theory and Techniques,

- Y.A. Atesal, B. Cetinoneri, K.-J. Koh and G. M. Rebeiz, Wafer-scale W-band power amplifiers using on-chip antennas, IEEE Radio Frequency Integrated Circuits Symp. Dig., May 2010, pp. 469-472.

The dissertation author was the primary author of the work in these chapters, and coau-

thors (Prof. Gabriel M. Rebeiz, Dr. Ramadan Alhalabi, Dr. KwangJin Koh, Mr. Kevin Ho, and Mr. Michael Chang) have approved the use of the material for this dissertation.

Yusuf A. Atesal La Jolla, CA January, 2011.

#### VITA AND PUBLICATIONS

| 2001 - 2006 | B. S. in Microelectronics Engineering, Sabanci University, Istanbul, Turkey |

|-------------|-----------------------------------------------------------------------------|

| 2006 - 2008 | M. S. in Electrical Engineering, University of California, San Diego, USA   |

| 2008 - 2011 | Ph. D. in Electrical Engineering, University of California, San Diego, USA  |

#### PUBLICATIONS

Y.A. Atesal, B. Cetinoneri, M. Chang, R.A. Alhalabi, and G.M. Rebeiz, "Milimeter-Wave Wafer-Scale Silicon BiCMOS Power Amplifiers Using Free-Space Power Combining," *IEEE Transaction on Microwave Theory and Techniques*, accepted for publication.

Y. A. Atesal, B. Cetinoneri, K. Ho, and G.M. Rebeiz, "A Two-Channel 8-20 GHz SiGe BiCMOS Receiver with Selectable Intermediate Frequencies for Multibeam Phased-Array Digital Beamforming Applications," *IEEE Transaction on Microwave Theory and Techniques*, accepted for publication.

B. Cetinoneri, Y.A. Atesal, and G.M. Rebeiz, "An 8x8 Butler matrix in 0.13-µm CMOS technology," *IEEE Transactions on Microwave Theory and Techniques*, accepted for publication

Y.A. Atesal, B. Cetinoneri, K.-J. Koh and G.M. Rebeiz, "X/Ku-band 8-element phased arrays based on single silicon chips," *IEEE Int. Microwave Symp. Dig.*, May 2010, pp. 23-28.

Y.A. Atesal, B. Cetinoneri, K.-J. Koh and G.M. Rebeiz, "Wafer-scale W-band power amplifiers using on-chip antennas," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, May 2010, pp. 469-472.

W. Elsallal, D. Jensen, R. Palandech, J. Timmerman, J. West, Y.A. Atesal, B. Cetinoneri, G.M. Rebeiz, "A SiGe-based Ku-band digital beamforming array for high speed on-the-move comm /radar system," *IEEE Int. Symp. on Phased Array Systems and Technology*, Oct. 2010, pp. 868-875.

B. Cetinoneri, Y.A. Atesal, and G.M. Rebeiz, "CMOS 4x4 and 8x8 Butler matrices," *IEEE Int. Microwave Symp. Dig.*, May 2010, pp 69-72.

B. Cetinoneri, Y.A. Atesal, and G.M. Rebeiz, "A microwave-based gamma-ray detector," *IEEE Int. Microwave Symp. Dig.*, May 2010, pp 23-26.

B. Cetinoneri, Y.A. Atesal and G. M. Rebeiz, "A two-channel Ku-band BiCMOS digital beamforming receiver for polarization-agile phased-array applications," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, June 2009, pp. 127-130.

Y.A. Atesal, B. Cetinoneri, and G.M. Rebeiz, "Low-loss 0.13-µm CMOS 50-70 GHz SPDT and SP4T switches," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, June 2009, pp. 43-46.

B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A miniature DC-70 GHz SP4T switch in 0.13-μm CMOS," *IEEE Int. Microwave Symp. Dig.*, June 2009, pp. 1093-1096.

#### ABSTRACT OF THE DISSERTATION

### X- to W-Band Phased Arrays and Wafer-Scale Transmitters using Silicon Integrated Circuits

by

Yusuf A. Atesal

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2011

Professor Gabriel M. Rebeiz, Chair

The thesis presents X- to W-band arrays implemented in silicon technologies for different phased-array applications. An 8-20 GHz two-channel dual down-conversion receiver with selectable IF for interference mitigation is presented for digital beamforming applications. The receiver is fabricated using a 0.18- $\mu$ m SiGe BiCMOS process and results in a channel gain (I and Q paths) of 46-47 dB at 11-15 GHz and > 36 dB at 8-20 GHz with an instantaneous bandwidth of 150 MHz. The measured NF is < 4.1 dB (3.1 dB at 15-16 GHz). The measured OP1dB is -10 dBm and the input P1dB is -56 to -40 dBm at 15 GHz depending on the gain, which is sufficient for satellite applications. The on-chip channel-to-channel coupling is < -48 dB. The measured EVM is < 3% for a 1 Msps QPSK modulation at 8-20 GHz, and < 1.8% for a 0.1, 1 and 10 Msps QPSK, 16QAM and 64QAM modulations at 15 GHz. The chip has ESD protection on the RF and DC pads, consumes 70 mA per channel from a 3.0 V power supply and is 2.6×2.2 mm<sup>2</sup>,

including all pads. A 15 GHz 8-element phased array with a NF < 3.9 dB is also demonstrated with multiple simultaneous beam performance using digital beamforming.

In another project, a silicon-based 8-element phased array based on an All-RF beamforming topology is integrated together with the antennas and digital control circuitry on a single Teflon board. The chip-on-board package, together with 8 X/Ku-band RF inputs and one RF output in a  $2.2 \times 2.5 \text{ mm}^2$  area, and the appropriate grounding and Vcc connections, are modeled using a 3-D EM solver. The design results in a low coupling between the different RF ports, and ensures stability even with a channel gain of 20 dB at 12 GHz. The measured patterns show a near-ideal performance up to a scan angle of  $60^\circ$  with an instantaneous scanning bandwidth of 11.4-12.6 GHz (limited by non true-time delay connections between the antennas and the chip). Temperature tests indicate that the silicon chip maintains excellent phase stability and rms phase error up to  $100^\circ$ C.

Finally, the first mm-wave wafer-scale silicon power amplifier array is implemented using 0.13  $\mu$ m BiCMOS technology. The power combining is done in the free-space using the high efficiency on-chip antennas. First, a W-band SiGe power amplifier is designed and fabricated together with a high-efficiency on-chip microstrip antenna. The power amplifier consumes 120 mA from a 1.7 V supply and the antenna/amplifier results in an effective radiated power  $(EIRP=P_tG_t) > 10 \text{ dBm from 88 to 98 GHz}$ , with a peak of 14.6 dBm at 92 GHz. Then, a  $3 \times 3$  power amplifier array is demonstrated with an equivalent isotropic radiated power (EIRP) of 33-35 dBm at 90-98 GHz. This results in a total on-chip power of 21-23 dBm, and a total radiated power of 17.5-19.5 dBm. The our knowledge, this is the highest power (and EIRP) achieved from a single silicon chip at millimeter-waves. The measured patterns of the array show single-mode operation and  $\sim 100\%$  free-space power-combining efficiency with a 3-dB beamwidth of 28° and a directivity of 15.5 dB (gain of 12 dB). The total power-combining efficiency including the antenna losses is  $45\pm10\%$ . It is shown that by using this technique high power (1-2 W) millimeter-wave transmitters with phased array capabilities can be realized in silicon technologies which will be compatible with best III-V solutions. The application areas are in millimeter-wave transmitters and wafer-scale phased arrays.

# Chapter 1

# Introduction

## **1.1 Phased Array Systems**

Phased arrays are an array of antennas which filters electromagnetic waves in the spatial domain ( [2, 2]) and are widely used in communication and radar systems [3–7]. The signals are received (or transmitted) in desired directions (peaks) by constructive interference between the signals at each antenna, and simultaneously blocked in undesired directions (nulls) by de-constructive interference. The spectral efficiency of the transmit/receive systems are increased by the spatial filtering of the phased arrays (interfere rejection, etc.) result in higher data-rate systems [8]. The total effective radiation pattern (scan angle, peaks, nulls, sidelobe levels, beamwidth, etc) of the antenna array is determined by the signal amplitude and phase (time delay) weighting at each antenna. For electronically scanned arrays, the phase and amplitude weighting is done electronically and hence, the beam steering and beam-forming are much faster than mechanical systems (nearly instantaneous) [8,9]. Fig. 1.1 shows the basic concept of a phased array system with 8 antenna elements in the receive mode. The incoming signal from an angle  $\theta$  arrives at each consecutive antenna pairs with a time difference of  $\Delta T$ , resulting in a phase difference of  $\Delta \phi$ , where

$$\Delta T = \frac{d\cos\theta}{c}, \quad \Delta \phi = kd\cos\theta, \quad k = \frac{2\pi}{\lambda}, \tag{1.1}$$

and d is the distance between the antenna elements.

The antennas are followed with variable time delays and variable attenuators (or variable gain amplifiers), in order to compensate for phase and amplitude difference between the antenna elements so as to have constructive summing in desired directions while having deconstructive summing in undesired directions. Note that transmit phased arrays operate on the

Figure 1.1: Block diagram of an 8-element phased array.

same principles. The variable time delays can be realized with variable phase shifters for narrow band applications or true-time-delay elements for wideband applications. Phased arrays based on silicon technologies have gathered particular interest, since both variable phase-shifters and variable gain control blocks are realizable together with complex transmitt/receive modules on a single silicon chip, and hence can replace complex III-V chipsets.

#### 1.1.1 Phased Array Architectures and Previous Work on Phased arrays

The phase shifting can be realized in the RF, LO, IF or digital paths of the T/R modules (Fig. 1.2). The RF phase shifting topology (all-RF architecture) has been the most commonly used one since the invention of phased arrays due to high signal-to-interferer ratio (since the beamforming is done in the RF domain before the down-conversion, interferers are rejected before the non-linear mixers), lowest layout area, lowest power consumption (especially for large number of elements), and no need for LO distribution. Silicon phased arrays with all-RF architecture have been successfully demonstrated from X- to W-band with 4-16 elements, multiple beams, and multiple polarizations in transmit or receive configurations ([10–16]). The LO and IF phase shifting architectures are also demonstrated using SiGe BiCMOS and CMOS processes [17–20].

**Figure 1.2**: Block diagram of phased array architectures (a) RF phase-shifting, (b) LO phase shifting, (c) IF phase shifting, and (d) digital beam-forming.

#### **1.1.2 Digital Beam-Forming Phased Arrays**

In the digital beam-forming (DBF) architecture, the signals are first digitized, and then the phase shifting (time delaying) is preformed in the digital domain (Fig. 1.2d). The DBF applies the required amplitude and phase (time delay) weighting to each antenna element to result in a number of simultaneous patterns (typically 2-6), each with its own scan angle, sidelobe level and bandwidth [21, 22]. Furthermore, if the antennas are dual polarized, then each beam can have an independent polarization (linear or circular). DBF architecture results in the highest performance systems, especially for more than 4 simultaneous beams. A disadvantage of the DBF is relatively high power consumption.

The DBF architecture is ideal for satellite systems since the required S/N ratio for low bit-error-rate is 12-14 dB at the aperture level. However, at the element level, the S/N ratio is < 0 dB (for 16-32 elements and larger), and the number of bits in the baseband A/D converter is not limited by the S/N ratio but by the interference levels. Therefore, in order to use a low number of A/D bits and to reduce the computational complexity in the DBF, it is essential to employ a large degree of filtering at the element level (a sharp EVM filter is generally used).

The digital beam-former architecture has seen limited use due to the cost, size and power consumption of GaAs-based X and Ku-band down-converters. A two-channel SiGe-BiCMOS solution is presented in this dissertation with selectable IF frequencies and 8-20 GHz operation capability.

#### 1.1.3 Packaging Issues for Silicon Phased Array Chips

The silicon integrated phased array circuits should be packaged for a complete product. A lot of work has been done on creating very high-performance microwave and millimeter wave silicon phased arrays, but packaging of these chips received comparatively little attention. Packaging environment can dramatically affect the RFIC performance, even can render the chip unusable. The degradation can be seen as excessive insertion loss, high return loss or low pinto-pin isolation. As an example, for a single-ended high gain amplifier at 60 GHz (3-4 stages, 20dB gain), 80-100 pH ground inductance would be sufficient for oscillations.

The main challenge comes from the interface between the silicon chip and a board. Different techniques are used for chip-to-board interface (flip-chip, ribbon-bonding, etc) and bondwires are widely-used for connecting the chip to board (outside). A bondwire behaves as an inductor (or high-impedance transmission line) at millimeter-wave frequencies, and the inductance value depends on the diameter, length and shape (spacing to ground, etc) of the bondwire. A widely used rule-of-thumb value for bondwire inductance is 1nH/mm. This inductance by itself degredates matching on the RF paths, which would cause reflections and loss. Therefore, a matching network should be carefully designed so as to compensate for the bondwire inductance.

In addition, on-chip measurements of silicon-chips provides an excellent ground (supply) to the chips through RF-ground pads (de-coupling capacitors). However, when a chip is mounted on a board, the on-chip ground (supply) will not be at perfect ground (supply), but will be an inductive ground (supply) due to the bondwire inductance. This inductance can affect the chip performance greatly: it can change the gain (magnitude and phase), noise-figure, matching and stability. In addition to the bondwire inductance, another issue is the coupling between the bondwires, which would deteriorate the isolation between different pins of the silicon chips.

In chapter 2, a low-cost 8-element phased-array board with a single silicon chip is demonstrated and the affects of packaging environment together with bondwires RF-transitions and matching networks are analyzed and addressed.

### **1.2** Power Amplifiers and Phased Arrays Transmitters

One of the most design-challenging components in transmitters is the power amplifiers. Fully-integrated SiGe (or CMOS) power amplifiers can replace complex GaAs-based transmit/receive modules and results in full system-on-chip solutions for phased-array or pointto-point communication systems. W-band power amplifiers (PAs) have been demonstrated using GaAs and InP-based HEMT monolithic microwave integrated circuit (MMIC) processes [23,24]. Recent works in silicon germanium technology have demonstrated the capability of generating significant millimeter-wave power within W-band (75 to 110 GHz) with reasonable efficiencies [25, 26]. However, generating high output powers is still a bottleneck for silicon designs due to low breakdown voltage limitations. The millimeter-wave designs also suffer from high on-chip losses due to low Q of the on-chip passive components. In addition, at millimeter-waves, transition between power amplifiers and the antennas are considerably lossy and challenging. This makes high-power SiGe amplifiers a crucial and challenging building block for many millimeterwave systems. Recently published works show that 10-100 mW can be achieved using SiGe-BiCMOS, and CMOS processes (21 dBm [26], 19.6 dBm [25], 11 dBm [27], 10dBm [28]).

Figure 1.3: Block diagram of (a) Wilkinson, (b) transformer, and (c) quasi-optical power-combining techniques.

#### 1.2.1 On-Chip Power Combining Techniques for High-Power Amplifiers

On-chip power combining and balanced device operation has been exploited for increased maximum available output power per chip. Balanced amplifiers result in higher power levels, and has been demonstrated [25], however, they suffer from large physical layout size and lossy couplers. In order to generate higher power levels, several on-chip power combining methods have been proposed and demonstrated using SiGe-BiCMOS and CMOS processes. Fig. 1.3 shows block diagram of three different power combining methods: Wilkinson based, transformer based, and free-space (quasi-optical). A 20 dBm (100 mW) power amplifier at 60 GHz is reported in [29] using Wilkinson couplers for power combining. Another Wilkinson-combiner based power amplifier is reported in [27] and achieved 12 dBm output power at 90-100 GHz. At 60 GHz, 14.5 dBm and 23 dBm power amplifiers with using distributed active transformers are reported in [30] and [31], respectively. The Wilkinson and transformer based approaches are adequate for 2-4 amplifiers, but still suffer from high on-chip combining losses especially for large number of elements (8-16 elements), and also from RF output transition losses. In addition, none of these techniques can be scaled to higher power levels, and on-chip designs achieving 0.1-1 W were not proposed or demonstrated.

#### 1.2.2 Free-Space (Quasi-Optical) Power Combining

Quasi-optical (free-space) power combining was developed in the 1980s and is based on two different topologies: The grid and the antenna approach. Grid designs use an interelement spacing of  $0.1-0.2\lambda_0$  and consider the transistor arrays as being imbedded in impedance sheets [32]. Antenna-based designs use an inter-element spacing of  $0.5-1.0\lambda_0$  and each amplifier/antenna element is designed taking into account the mutual coupling between the antennas [32–36]. Both the grid and the antenna approach have been demonstrated at Ka to Wband frequencies, and with excellent results using GaAs or InP components in a hybrid approach [33–42]. The antenna-based approach allows for a planar RF distribution network and is compatible with wafer-scale systems.

For silicon applications using antenna-based free-space power combining, a highefficiency electromagnetically-coupled (EM) antenna can be designed directly on the silicon chip, and each SiGe (or CMOS) amplifier can be connected to the antennas. Unlike the Wilkinson and transformer based power-combining approaches, the free-space power combining has no limitation on the number of elements since the power combining is done in air and is 100% efficient (assuming equal amplitude and phase distribution to the elements, and no antenna losses). Therefore, applying this novel technique to the silicon designs (an NxM power amplifier array) allows for high power transmitters achieving 0.1-1 W at millimeter-waves (W-band and above). Furthermore, wafer-scale phased arrays (NxM, transmit or receive) can be designed by introducing phase shifters at each element together with the amplifier.

### **1.3** Thesis Overview

This thesis presents X- to W-band phased arrays and wafer-scale transmitters using SiGe BiCMOS technologies. First, a two channel X- to Ku-band digital-beam-forming phased array receiver for satellite communications is demonstrated. For a complete phased array receiver, the silicon-chips should be packaged (connected to a board) together with radiating elements (antennas). Therefore, packaging affects are carefully analyzed, and as a demonstration an 8-element phased array is impelemented on a Teflon board by using an 8-element silicon phased array chip with All-RF phase shifting arhitecture. The chip-to-board transitions and raditating elements are designed in HFSS, and real-life pattern measurements of the complete system are presented. The chip-to-board transisitions are lossy, challenging and expensive, especially at millimeter-waves (90 GHz and above) where power generations is already limited by

breakdown-voltages and on-chip losses. By applying a very novel technique -free-space power combining- to silicon-chip design, the first millimeter-wave wafer-scale transmitters (power amplifiers) are implemented. This technique not only eliminates the need for output transitions, but also allows for 1-2 W millimeter-wave transmitters and phased-arrays that are compatible with best III-V solutions.

Chapter 2 presents the first fully integrated two-channel SiGe BiCMOS receiver, capable of operation in the 8-20 GHz, for digital beam forming phased arrays. The receiver is based on a dual-down-conversion architecture with selectable IF for interference mitigation, and the silicon chip is fabricated using a 0.18- $\mu$ m SiGe BiCMOS process. The chip consumes 70 mA per channel from a 3.0 V power supply and is  $2.6 \times 2.2$  mm<sup>2</sup>, including all pads. The receiver achieved excellent performance over the entire 8-20 GHz bandwidth, and theoretical and measurements results are presented. The receiver can be used with selectable IF frequencies from 1.8-3 GHz, and is also characterized versus temperature. An 15 GHz 8-element phased array with a diplexed LO distribution network was demonstrated at 15 GHz using four of these receivers, and achieved results are presented. The chip was also used in a real-time FPGA-based phased array system at 15 GHz to generate three simultaneous beams each with 10.7 Mbps links.

Chapter 3 presents a complete 8-element X/Ku-band phased array based on a single silicon chip. The phased array is built on single-layer Teflon substrate and contains an 8-element silicon phased array chip, the radiating elements, control circuits and all RF transmission lines. Packaging aspects of multi-element phased arrays, such as RF transitions and associated impedance matching networks, coupling between the different RF ports, Vcc decoupling and oscillations - especially in high gain designs, and the creation of a low-inductance ground between the chip and the antenna distribution board are carefully analyzed. It is shown that chip-on-board packaging results in high isolation (low coupling) between the different RF ports, and ensures stability even with a channel gain of 20 dB at 12 GHz. An 8-element phased array card with instantaneous bandwidth of 11.4-12.6 GHz, near ideal measured patterns and scanning up to 60° is successfully demonstrated. To the best of our knowledge, this is the first 8-element phased array based on a single silicon chip.

Chapter 4 presents the first wafer-scale power amplifier/combiner in silicon technology. A mm-wave wafer-scale power amplifier array implemented in a 0.13  $\mu$ m BiCMOS technology fabricated together with high efficiency on-chip microstrip antennas is presented. The power combining is done in the quasi-optical domain using high efficiency on-chip antennas. A 3×3 power amplifier array with 0.6 $\lambda_0$  at 94 GHz spacing between the antenna elements is demonstrated with excellent performance, an output power of 21-23 dBm and highest equivalent isotropic radiated power (EIRP) up-to-date from a silicon-chip (33-35 dBm at 90-98 GHz). The measured patterns of the wafer-scale array are presented and are in excellent agreement with simulations and show single-mode operation. The design is wafer-scalable and it is shown that applying quasi-optical design methodology to silicon-based designs would result in fully integrated millimeter-wave transmitters (with phased array capabilities) which are competitive with the best III-V solutions.

# Chapter 2

# A Two-Channel 8-20 GHz SiGe BiCMOS Receiver with Selectable Intermediate Frequencies for Multibeam Phased-Array Digital Beamforming Applications

# 2.1 Introduction

Satellite systems operating at the 8-21 GHz band and located in different earth orbits are used for communication data links with data bandwidths of 0.1-50 Mbps depending on the receiving aperture size [43]. This system is therefore well suited for a digital beam-forming array due to the low received power levels (Fig. 2.1a). In this architecture, each antenna element is connected to an I/Q down-converter, and the received I/Q signals are digitized and sent to a digital beam-former (DBF) [44]. The DBF applies the required amplitude and phase (time delay) weighting to each antenna element to result in number of simultaneous patterns (typically 2-6), each with its own scan angle, side-lobe level and bandwidth [21,22]. Furthermore, if the antennas are dual polarized, then each beam can have an independent polarization (linear or circular).

The DBF architecture is ideal for satellite systems since the required S/N ratio for low

**Figure 2.1**: (a) Digital beam-forming system, (b) block diagram of the two channel receiver based on a dual-down-conversion architecture and frequency plan.

bit-error-rate is 12-14 dB at the aperture level. However at the element level, the S/N ratio is < 0 dB (for 16-32 elements and larger), and the number of bits in the baseband A/D converter is not limited by the S/N ratio but by the interference levels. Therefore, in order to use a low number of A/D bits and to reduce the computational complexity in the DBF, it is essential to employ a large degree of filtering at the element level. In this case, a narrow-band low-loss evanescent-mode (EVM) band-pass filter is placed at each antenna element [45, 46], and a dual down-conversion architecture with a high degree of IF filtering is required (Fig. 2.1b). Also, due to the very large interferers present on complex platforms, and which can change in frequency and time, a variable IF architecture should be used, and the system can select the most optimal LO frequencies and IF bands so as to minimize the interference levels at baseband frequencies. The phased array system can then employ 2-4 bit A/D converters at each element (depending on the residual interference levels), which greatly reduces the DBF complexity and power consumption. In most cases, the communication data rate is 0.1-10 Mbps, and a DBF connected to a 16-64 element array can synthesize 2-4 simultaneous beams using standard signal processing chips (FPGAs) [47].

The digital beam-former architecture has seen limited use due to the cost, size and power consumption of GaAs-based X and Ku-band down-converters. This chapter presents the first BiCMOS 8-20 GHz dual down-conversion chip with two independent channels, each with differential I/Q outputs (Fig. 2.1b). The chip can operate at a single frequency anywhere in the 8-20 GHz band. The operation of one channel is as follows (Fig. 2.1b): After the first down-conversion, the signal is filtered again using an off-chip filter bank. These filters are typically SAW devices with 4-6 poles, sharp rejection skirts and ultimate rejection of 50-60 dB [48]. The signal is then fed back to the chip for a second down-conversion which creates the I/Q outputs. A baseband VGA is placed before the I/Q outputs for linearity control as well as providing low-pass filtering with a cut-off frequency of 150-200 MHz at maximum gain. The I and Q outputs are then differentially fed into off-chip A/D converters for beamforming.

The LO inputs are single-ended and fed directly into passive baluns for differential on-chip distribution, and the two receiver channels share common LO busses. Both LOs are external due to stringent 1/f noise requirements for satellite communication systems (typically achieved with DROs at 8-18 GHz) [49]. Due to the low RF power per element and the sharp EVM RF filter on each antenna, the system can tolerate a low input P1dB, and a P1dB of -30 dBm per element for RF-front-end (LNA + mixer) is standard. The system-level P1dB can be as low as -60 dBm per element due to the additional filtering in the IF and baseband, and is mostly limited by the chip gain and the output P1dB of the baseband amplifiers.

# 2.2 Chip Design and Circuit Blocks

#### 2.2.1 **RF-Front-End Design**

The chip is composed of an RF-front-end and an IF stage. The RF front-end is designed using 0.18- $\mu$ m SiGe transistors with f<sub>t</sub>=150 GHz for low noise figure (Jazz SBC18HX). The first stage is a cascode low-noise amplifier (LNA) with inductive degeneration and a tuned load providing simultaneous input and noise matching [11, 50] (Fig 2.2a). The second stage is an active single-to-differential converter with a differential cascode pair and a tuned load. A double-balanced mixer with a tuned load at 2.45 GHz is then used in order to prevent LO-IF feed-through (Fig. 2.2b). The mixer is followed by a differential CMOS buffer in order to isolate the mixer load from the external SAW filter and to ensure stability (the SAW filter impedance

**Figure 2.2**: Circuit schematics of the RF-front end: (a) LNA and active balun, and (b) double-balanced mixer with a tuned load.

**Figure 2.3**: Circuit schematics of the IF stage: (a) Active balun, (b) resistive double-balanced mixer, and (c) baseband VGA with 9, 12 and 16 dB gain control.

is reactive for all rejection frequencies). The buffer is a CMOS source follower due to linearity considerations. In order to have a single-ended output for IF filtering, one of the mixer/buffer outputs is internally loaded with 50  $\Omega$ , while the other output is connected to the external filter bank. The RF front-end has a simulated gain of 25.0 dB at 15 GHz, with an input P1dB of -29.4 dBm, and a NF of 3.1 dB. The total current consumption is 37.7 mA from a 3 V power supply (including LO buffers).

#### 2.2.2 IF-Stage Design

A CMOS active balun amplifier in a cascode configuration is used first in the IF stage (Fig 2.3a). In order to achieve wideband input matching and low noise figure at 2-3 GHz with a reasonable amount of current ( $I_{dc}$ = 10 mA for the active balun), additional capacitance is employed between the gate and source of the CMOS transistors in the active balun [51,52]. The differential signal at the output of the active balun is then fed to the I/Q mixers. Again, double-

balanced mixers are used for down-conversion to baseband frequencies. The I/Q mixers employ SiGe transistors in the switching core for lower 1/f noise and are resistively loaded for wideband operation (Fig. 2.3b). Fig. 2.4 presents the simulated noise figure of the IF stage and of the whole single-channel down-converter using MOSFET and bipolar switching cores. As seen, the 1/f noise corner frequency of single channel is reduced to 20 kHz using bipolar switching cores.

**Figure 2.4**: Noise figure comparison showing the effect of using bipolar  $(10\mu m/0.18\mu m)$  or MOSFET  $(25\mu m/0.18\mu m)$  switch pairs in the IF stage mixer core.

The I/Q mixers are followed by DC-coupled differential common-source variable gain amplifiers (VGA) and the gain is controlled by resistive degeneration using  $V_{c1}$ ,  $V_{c2}$  and  $V_{c3}$ (Fig. 2.3c). The VGA's are designed using PMOS transistors with a large device length and optimized for lowest 1/f noise performance. The VGA is followed by a differential source follower with a negative feedback which sets the output impedance of the VGA to 100  $\Omega$  differential in order to drive high-speed off-chip A/D converters [53]. The IF stage has a simulated gain of 25.5 dB, with a simulated bandwidth of 200 MHz, an input P1dB of -34.5 dBm (output P1dB of -10 dBm in a 50  $\Omega$  load, single ended), and a noise figure of 7.2 dB at an input of 2.45 GHz, and consumes 31.2 mA from a 3 V power supply (including two LO<sub>2</sub> buffers).

#### 2.2.3 LO Distribution Network

One of the key aspects of the design is the wideband on-chip LO distribution network for both LO<sub>1</sub> (5.5-17.5 GHz) and LO<sub>2</sub> (2.2-3.2 GHz). Two separate single-ended LO signals are fed into passive baluns and then routed differentially through the LO distribution network located in the middle of the chip (Fig 2.5 and Fig. 2.8). The LO<sub>1</sub> balun is two-layer design with primary turn implemented using M6 and the secondary turn implemented using M5. Both primary and secondary inductors are 3 turns with a metal width of 4  $\mu$ m and a spacing of 3 mum. The balun results in 1.6 dB loss at 12.5 GHz [54]. The LO<sub>2</sub> balun is a single-layer standard library design with 2 dB loss at 2.5 GHz [55]. The LO signals for the I/Q mixers are generated using a one-stage differential R-C polyphase filter which provides a constant 90° phase versus frequency. The LO distribution is done using GSSG transmission lines (simulated loss using Sonnet: 0.62 dB/mm at 12.5 GHz), and the crossovers between LO<sub>1</sub>, LO<sub>2</sub> and the I/Q paths are realized using ground islands between the signals for enhanced isolation (Fig. 2.5b).

The LO division between the two channels is done using T-junctions followed by differential amplifiers so as to enable operation at low LO powers. These LO drivers have a gain of 6 dB at 12.5 GHz, and 9 dB at 2.5 GHz (when loaded with the corresponding mixers), and are driven into saturation. The RF and IF mixers require > -17 dBm ( $\sim 200 \text{ mV}_{p-p}$ ) at the LO switching cores for a saturated gain, and this can be easily achieved with 5 mA drivers. The

**Figure 2.5**: LO distribution networks: (a) LO<sub>1</sub> at 5.5-17.5 GHz, (b) differential LO driver, and (c) LO<sub>2</sub> at 2.1-3.2 GHz.

total distribution loss for LO<sub>1</sub> is 5.6 dB at 12.5 GHz including the 1:2 division, and is 11.0 dB for LO<sub>2</sub> including the polyphase network and 1:2 division. Therefore, for proper operation, an input LO power of > -10 dBm is required for both LO<sub>1</sub> and LO<sub>2</sub>. This means that an off-chip low phase-noise dielectric resonator oscillator (DRO) with an output power of 20 dBm can drive multiple elements without any additional LO distribution amplifiers.

The simulated LO differential phase errors at the input of RF (LO<sub>1</sub>) and IF (LO<sub>2</sub>) mixers are  $< 10^{\circ}$  at 4-18 GHz and  $< 5^{\circ}$  at 2.0-3.3 GHz. Since the RF and IF mixers and the baseband VGA are differential, the phase error at the baseband output port is reduced to  $< 0.5^{\circ}$  over the 200 MHz bandwidth.

#### 2.2.4 Biasing Network

Two PTAT circuits are implemented in order to generate reference currents: one for the RF-front-end, one for the IF-stage. The two channels share the reference PTAT blocks (RF and IF), and all amplifiers and mixers are biased from these reference currents. Shown in Fig. 2.6a and Fig. 2.7a are PTAT reference current generators for RF-front-end (100  $\mu$ A) and IF-stage (50  $\mu$ A), respectively. The PTAT reference current is calculated using:

$$I_{\rm PTAT} = \frac{\rm kT}{\rm q} \frac{\rm ln A}{\rm R_p}$$

(2.1)

where A is the ratio of emitter length of  $Q_2$  to that of  $Q_1$ .

In addition to the PTAT current generator, another control path is included (Vs,  $\overline{Vs}$ ) which can turn off the PTAT generator, and allows for external current control (Vc). PMOS transistors with large lengths (0.5-1  $\mu$ m) are used for current mirroring. Furthermore, 1.6-10.1 pF de-coupling capacitors are placed at the bias sampling nodes for de-coupling the RF-stages from bias network effects. Detailed bias network circuits for RF-front-end and IF stages are shown in Fig. 2.6 and Fig. 2.7, respectively.

#### 2.2.5 Technology and Chip Performance

The chip is fabricated on a 0.18- $\mu$ m SiGe BiCMOS process (Jazz SBC18HX) with 6 metal layers. The 2.8- $\mu$ m-thick top metal layer is used to implement inductors, transmission lines, and input/output pads (see Appendix 1 for detailed process parameters). Metal levels 4-5-6 are used to create a single continuous Vcc plane throughout the chip. A single ground plane for RF and DC ground is also employed on the chip (metal layers 1/4/6). All of the passive components and interconnections in the RF-front-end and the LO distribution network

**Figure 2.6**: Bias networks of RF-front-end: (a) PTAT reference current source, (b) LNA, (c) LNAB, (d) DB-Mixer and (e) LO-amplifiers.

**Figure 2.7**: Bias networks of IF-stage: (a) PTAT reference current source, (b) Active balun, (c) VGA, (d) Mixer and (e) LO-amplifiers.

**Figure 2.8**: (a) Microphotograph of the 8-20 GHz two-channel down-converter ( $2.6 \times 2.2 \text{ mm}^2$  including all pads).

O Balur

GND

(b)

9

are simulated using a full-wave EM analysis software (Sonnet [56]). R-C parasitic extraction simulations are performed for the baseband circuitry. All RF and DC pads are ESD protected using 1.2 kV and 3.6 kV ESD diodes available in the Jazz library. The input and output matching circuits are designed taking into account the pad and ESD capacitance.

Each channel consumes  $\sim 70$  mA of current from 3 V power supply including the LO amplifiers. The simulated overall receiver shows a gain of 49 dB with a 3-dB baseband bandwidth of 200 MHz and a NF of 3.1 dB, all at 15 GHz, and with a very wideband performance (see Section 2.3). A microphotograph of the two-channel receiver ( $2.6 \times 2.2 \text{ mm}^2$ ) is presented in Fig. 2.8. Test-cells of RF-front-end and IF-stage are also fabricated for measurement purposes and are shown in Fig. 2.9a and b, respectively.

## 2.3 **On-Chip Measurements**

#### 2.3.1 S-Parameter Measurements

The on-chip measurements are done using SOLT calibration to the probe tip and dedicated RF and DC probes. All measurements include the RF pad capacitance and the ESD diode loading effects. The measured input reflection coefficient ( $S_{11}$ ) is shown in Fig. 2.10a. An excellent impedance match is achieved at 10-25 GHz, and the difference between the simulation and measurements is attributed to extra parasitics at the RF pad, which de-Q the reflection characteristics. The measured reflection coefficient at the I and Q outputs ( $S_{22}$ ) are given in Fig. 2.10b, showing a good impedance match up to 1 GHz. Fig. 2.10c presents the measured reflection coefficients at the output of the RF stage ( $S_{33}$ ) and at the input of the IF stage ( $S_{44}$ ) agreeing well with simulations.

#### 2.3.2 **RF-Front-End Measurements**

The RF and IF stages of the dual down-converter chip can be measured separately due to the IF filtering cut-out. The RF test cell (Fig. 2.9a) is characterized using CPW probes, Agilent network analyzers, signal sources (LO), and spectrum analyzers (NF measurements). Fig. 2.11a shows the gain and noise figure of the RF stage with a fixed IF output at 2.45 GHz (RF and LO<sub>1</sub> are scanned together). The measured gain is 23.5 dB at 15.0 GHz, with a 3-dB gain bandwidth of 9.2-16.2 GHz, and a NF of < 3.7 dB at 8-20 GHz. The RF stage is also characterized with a fixed LO (LO<sub>1</sub>= 12.55 GHz), and shows a gain and noise figure of 23.5 dB at 15 GHz, respectively (Fig. 2.11b). The input LNA and active balun designs are

**Figure 2.10**: Measured return losses: (a) RF input  $(S_{11})$ , (b) baseband output  $(S_{22})$ , (c) IF output  $(S_{33})$  and input  $(S_{44})$ .

**Figure 2.11**: Measured gain and NF of the RF stage: (a) with fixed IF output at 2.45 GHz, (b) at 15 GHz vs. different IF. (c) Measured input P1dB and IIP3 with IF fixed at 2.45 GHz.

wideband and the gain curve is mainly shaped by the tuned IF response of the double-balanced mixer. The measured input P1dB and IIP3 are shown in Fig. 2.11c and are limited by the RF mixer.

#### 2.3.3 IF-Stage Measurements

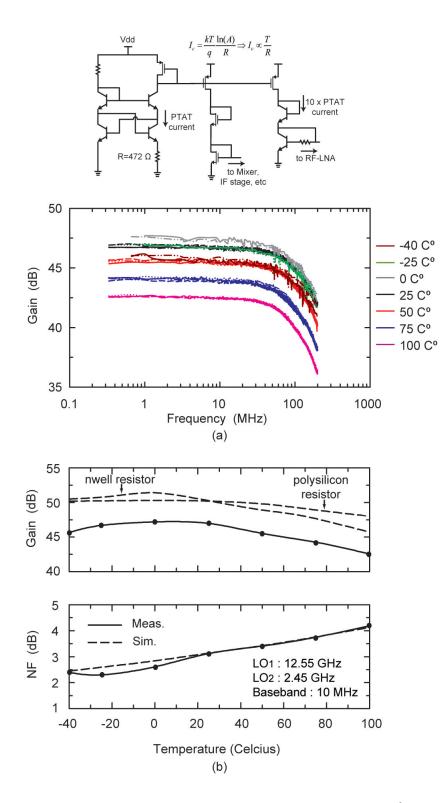

The IF stage is also separately measured with an input at 1.5-3.5 GHz using a test cell (Fig. 2.9b). For a fixed baseband frequency of 10 MHz, the measured gain and noise figure are shown in Fig. 2.12a. The gain is 20.5-24.5 dB and the NF is < 11.5 dB at 2.1-3.2 GHz. The gain of the IF stage with an LO<sub>2</sub> of 2.45 GHz is shown in Fig. 2.12b for all the baseband outputs: I+, I-, Q+ and Q-. Note that the spikes around 100 MHz are due to the coupling of the FM radio stations to the test setup. The measured 3-dB bandwidth is 175 MHz with a gain of 24.5 dB, and is determined mostly by the baseband VGA. The measured P1dB is shown in Fig. 2.12c and is  $\sim -35$  dBm at 2.5 GHz, limited by the baseband VGA. Furthermore, the LO<sub>2</sub> power leakage at the baseband outputs is -53 dBm at 2.45 GHz for an input LO power of -5 dBm.

## 2.3.4 Channel Measurements